# **Optoelectronic Devices and Packaging for Information Photonics**

By

### Srinivasarao Kumpatla

A dissertation submitted for the degree of Doctor of Philosophy

Heriot-Watt University

School of Engineering and Physical Sciences

February 2009

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that the copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author or of the University (as may be appropriate).

#### Abstract

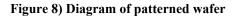

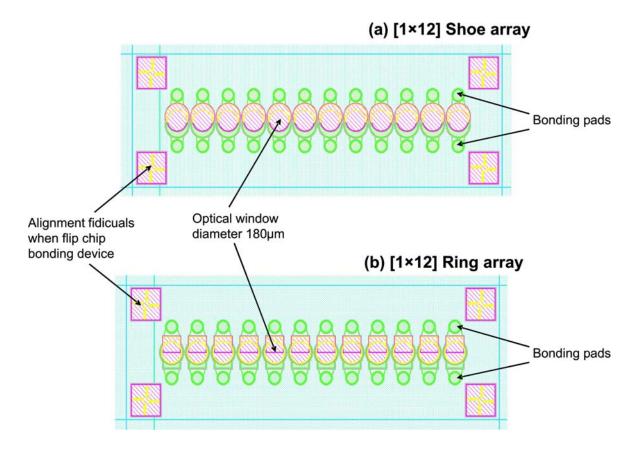

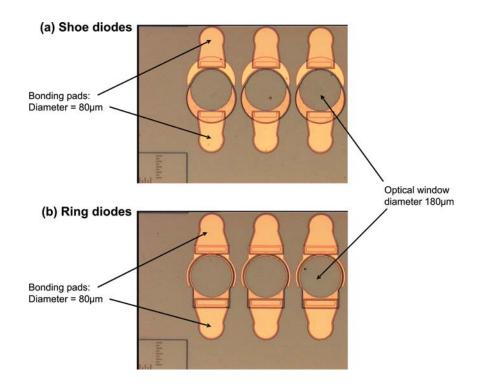

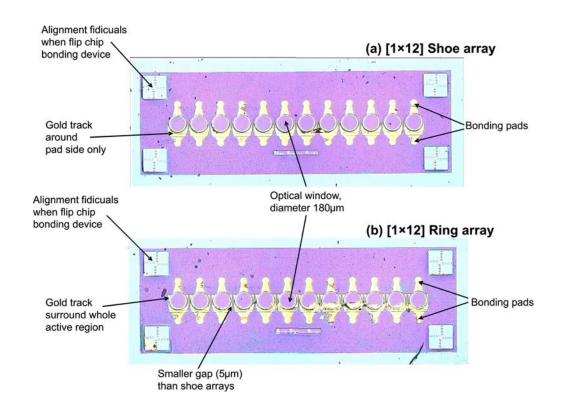

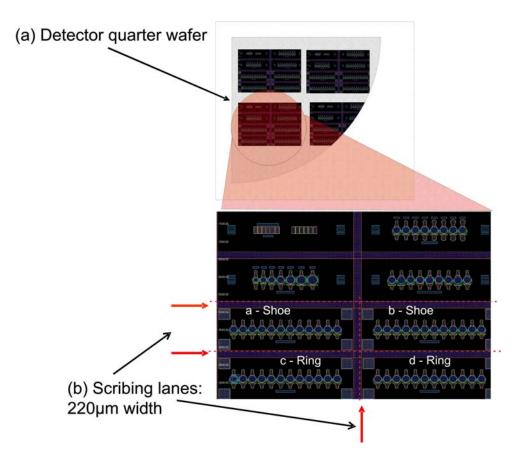

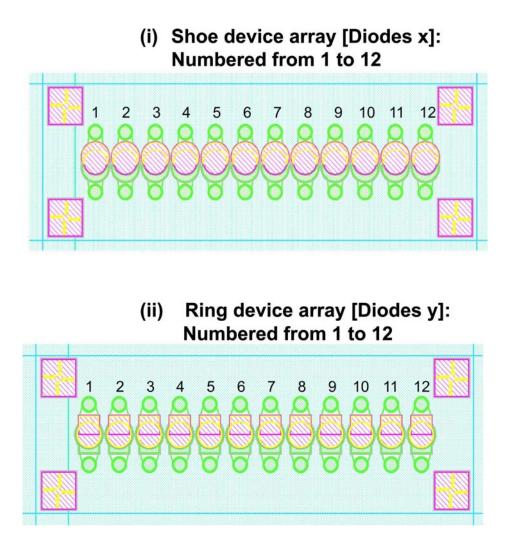

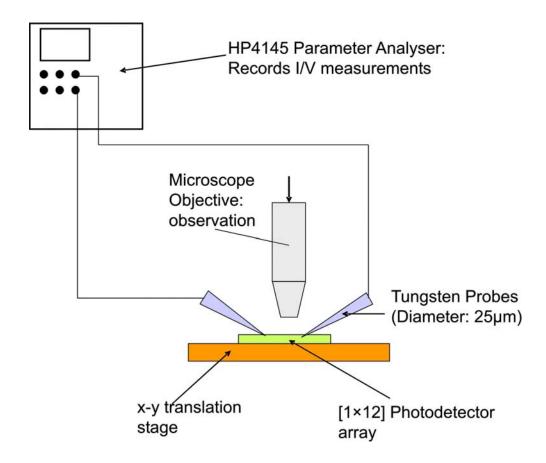

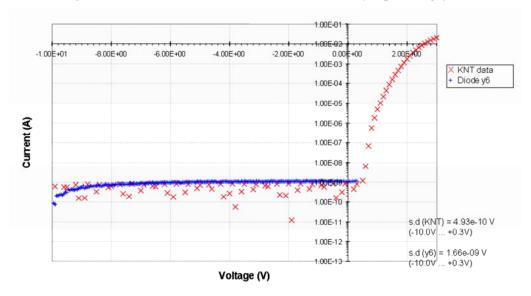

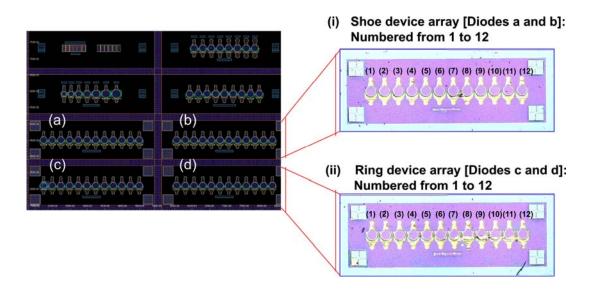

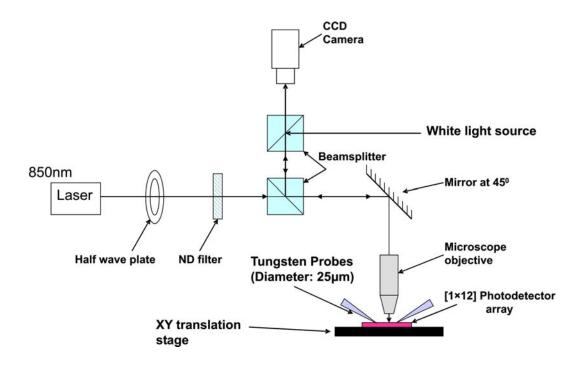

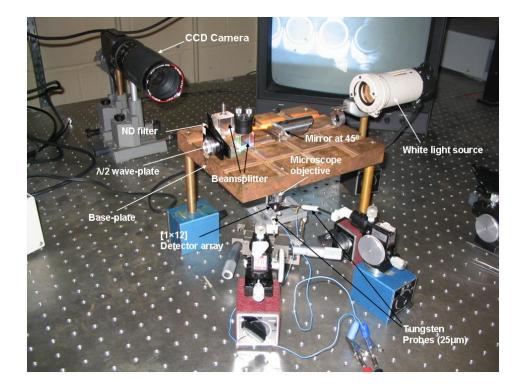

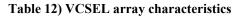

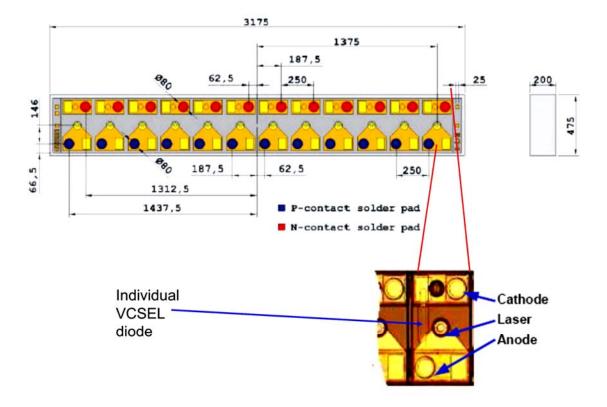

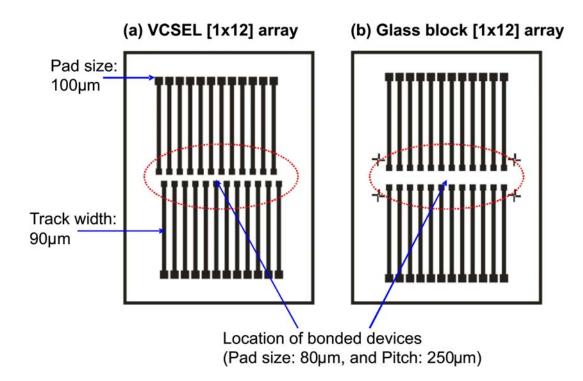

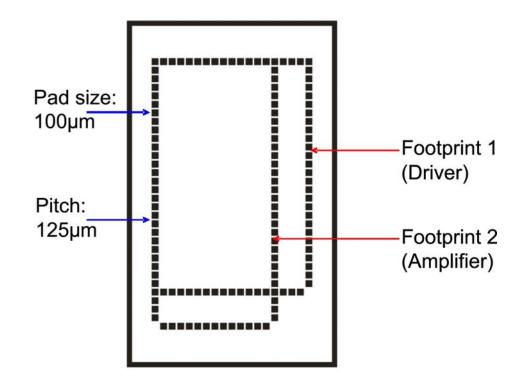

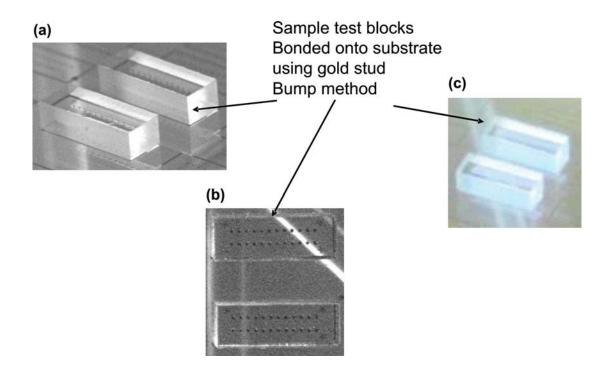

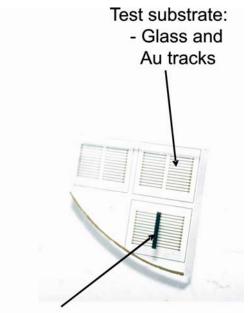

This thesis studies optoelectronic devices and the integration of these components onto optoelectronic multi chip modules (OE-MCMs) using a combination of packaging techniques. For this project, (1×12) array photodetectors were developed using PIN diodes with a GaAs/AlGaAs strained layer structure. The devices had a pitch of 250µm, operated at a wavelength of 850nm. Optical characterisation experiments of two types of detector arrays (shoe and ring) were successfully performed. Overall, the shoe devices achieved more consistent results in comparison with ring diodes, i.e. lower dark current and series resistance values. A decision was made to choose the shoe design for implementation into the high speed systems demonstrator. The (1x12) VCSEL array devices were the optical sources used in my research. This was an identical array at 250µm pitch configuration used in order to match the photodetector array. These devices had a wavelength of 850nm. Optoelectronic testing of the VCSEL was successfully conducted, which provided good beam profile analysis and I-V-P measurements of the VCSEL array. This was then implemented into a simple demonstrator system, where eye diagrams examined the systems performance and characteristics of the full system and showed positive results.

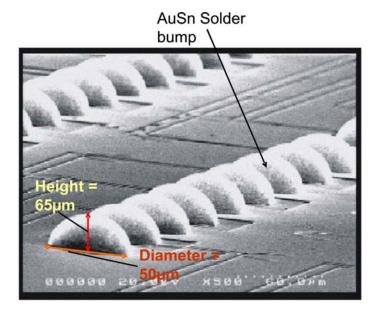

An explanation was given of the following optoelectronic bonding techniques: Wire bonding and flip chip bonding with its associated technologies, i.e. Solder, gold stud bump and ACF. Also, technologies, such as ultrasonic flip chip bonding and gold micro-post technology were looked into and discussed. Experimental work implementing these methods on packaging the optoelectronic devices was successfully conducted and described in detail. Packaging of the optoelectronic devices onto the OE-MCM was successfully performed. Electrical tests were successfully carried out on the flip chip bonded VCSEL and Photodetector arrays. These results verified that the devices attached on the MCM achieved good electrical performance and reliable bonding. Finally, preliminary testing was conducted on the fully assembled OE-MCMs. The aim was to initially power up the mixed signal chip (VCSEL driver), and then observe the VCSEL output.

# Dedication

To my parents, wife and son

## ACADEMIC REGISTRY Research Thesis Submission

| Name:                                         | SRINIVASARAO KUMPATLA           |                                                     |               |

|-----------------------------------------------|---------------------------------|-----------------------------------------------------|---------------|

| School/PGI:                                   | ENGINEERING & PHYSICAL SCIENCES |                                                     |               |

| Version: (i.e. First,<br>Resubmission, Final) | Final                           | Degree Sought<br>(Award <b>and</b><br>Subject area) | PhD - Physics |

#### **Declaration**

In accordance with the appropriate regulations I hereby submit my thesis and I declare that:

- 1) the thesis embodies the results of my own work and has been composed by myself

- 2) where appropriate, I have made acknowledgement of the work of others and have made reference to work carried out in collaboration with other persons

- 3) the thesis is the correct version of the thesis for submission and is the same version as any electronic versions submitted\*.

- 4) my thesis for the award referred to, deposited in the Heriot-Watt University Library, should be made available for loan or photocopying and be available via the Institutional Repository, subject to such conditions as the Librarian may require

- 5) I understand that as a student of the University I am required to abide by the Regulations of the University and to conform to its discipline.

- \* Please note that it is the responsibility of the candidate to ensure that the correct version of the thesis is submitted.

| Signature of<br>Candidate: | Date: |  |

|----------------------------|-------|--|

| Canuluale.                 |       |  |

#### **Submission**

| Submitted By (name in capitals):    |  |

|-------------------------------------|--|

| Signature of Individual Submitting: |  |

| Date Submitted:                     |  |

#### For Completion in Academic Registry

| Date: |       |

|-------|-------|

|       | Date: |

#### Acknowledgements

First and foremost, I would like to thank my academic supervisor Dr John Snowdon for giving me this opportunity to study for my PhD. I am very thankful to John for his invaluable support, guidance and encouragement both as a supervisor and as a friend.

Also, I would like to thank Professor Mohammed Taghizadeh for his support as my primary supervisor during the final phase of writing my PhD Thesis.

I would also like to thank Dr Josh Casswell, who was my proxy for this research. His support, guidance and advice to this work proved valuable. I would like to thank all members of the Optically Interconnected Computing (OIC) group at Heriot-Watt University for their help during my Doctoral Research.

I would like to thank all the HOLMS Project Participants and Dr Geoff Hill from EPSRC National Centre for III-V Technologies, University of Sheffield. Also, I would like to thank Mr Mark Leonard of MIcroSystems Engineering Centre (MISEC), Heriot-Watt University, for his support and guidance using the cleanroom facilities.

I am also thankful to the Engineering and Physical Sciences Research Council (EPSRC) and the European Commission under the Information Society Technologies (IST) program for sponsoring me in my research work. I would also like to thank my office colleagues, Ray Fulton, Peter Harrison and Robert Thomson.

I would like thank Mr Andrew Holland and Mr Peter Robinson from Cambridge Silicon Radio (CSR) for their support and patience, while I was writing up my PhD Thesis.

I would also like to thank my mother and father for their support (both financially and motivationally) and encouragement over the last 35 years. Without them, none of this would have been possible. Finally, I would like to thank my wife, Uma, for her friendship, support and patience.

# Table of Contents

| СНАР         | TER 1                                                                               | 1  |

|--------------|-------------------------------------------------------------------------------------|----|

| BACK         | GROUND AND THESIS OVERVIEW                                                          | 1  |

| 1 1          |                                                                                     | 1  |

| 1.1          | BACKGROUND                                                                          |    |

| 1.2          | MOORE'S LAW                                                                         |    |

| 1.5          | RESEARCH MOTIVATION                                                                 |    |

|              | 4.1 Electronic Limits                                                               |    |

| 1.5          | RESEARCH WORK CONDUCTED ON OPTICAL INTERCONNECTS IN INDUSTRY                        |    |

|              | 5.1 Introduction                                                                    |    |

|              | 5.2 Research by Intel                                                               |    |

| 0            | ptical Interconnects:                                                               |    |

| Si           | licon Photonics:                                                                    | 8  |

| 1.           | 5.3 Terahertz Photonics Ltd                                                         | 9  |

| 1.           | 5.4 Luxtera                                                                         |    |

| 1.6          | RESEARCH WORK CONDUCTED ON OPTICAL INTERCONNECTS IN ACADEMIA                        |    |

| 1.           | 6.1 Introduction                                                                    |    |

| 1.           | 6.2 Optically Interconnected Computing at Heriot-Watt University (HWU)              |    |

|              | 6.3 The Miller Group, Stanford Photonics Research Center, Stanford University       |    |

| 1.           | 6.4 Optoelectronics Research at University of California San Diego                  |    |

|              | 6.5 Optical Interconnection Technology Group (OIT) - C-Lab                          |    |

|              | 6.6 Optical Information Technology (ONT) Group - University of Hagen                | 14 |

|              | 6.7 Optical Interconnects Group - Vrije Universiteit Brussel (VUB)                  |    |

|              | 6.8 Summary                                                                         |    |

| 1.7          |                                                                                     |    |

|              | 7.1 Introduction                                                                    |    |

|              | 7.2 Overview of Project                                                             |    |

| 1.8          | Thesis Overview                                                                     |    |

| 1.9          | CHAPTER 2: RECEIVER DEVICES – PHOTODETECTOR (PD) ARRAYS                             |    |

| 1.10         |                                                                                     |    |

| 1.11<br>1.12 | CHAPTER 4: OPTOELECTRONIC PACKAGING (I)<br>Chapter 5: Optoelectronic Packaging (II) |    |

| 1.12         |                                                                                     |    |

| 1.15         |                                                                                     |    |

| 1.14         | NEFERENCES                                                                          | 20 |

| СНАР         | TER 2                                                                               | 31 |

|              |                                                                                     |    |

| RECE         | IVER DEVICES – PHOTODETECTOR (PD) ARRAYS                                            | 31 |

| 2.1          | INTRODUCTION                                                                        |    |

| 2.2          | BACKGROUND ON PHOTODIODES                                                           |    |

|              | 2.1 PIN Photodiode                                                                  |    |

|              | eal Photodiodes:                                                                    |    |

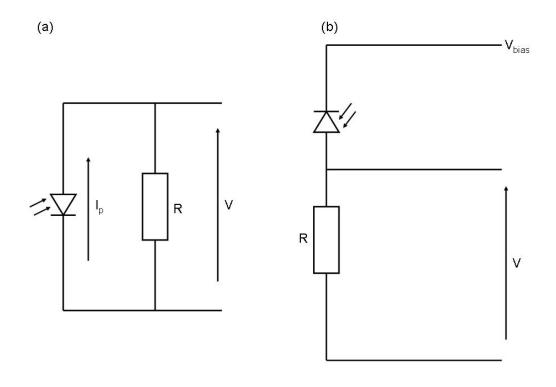

|              | 2.2 Detector Configurations                                                         |    |

|              | assive Load Detector:                                                               |    |

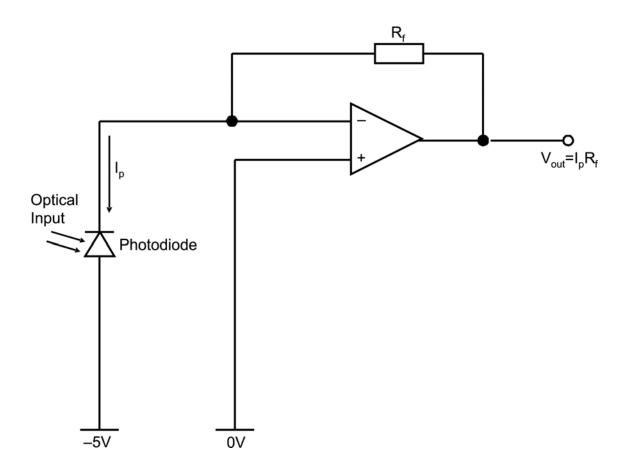

|              | ransimpedance Amplifier:                                                            |    |

|              | 2.3 Noise in Photodetectors                                                         |    |

|              | not Noise:                                                                          |    |

|              | ark Current:                                                                        |    |

|              | hnson Noise:                                                                        |    |

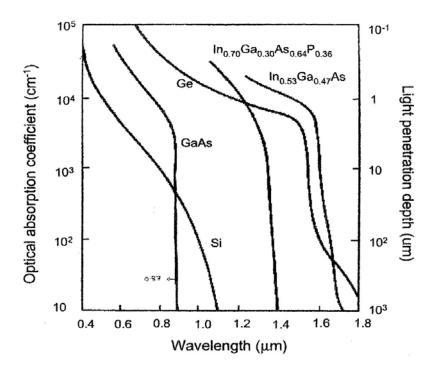

|              | 2.4 Responsivity                                                                    |    |

|              | 2.5 Reverse Bias                                                                    |    |

|              | 2.6 Series Resistance (SR)                                                          |    |

|              | 2.7 Bandwidth Calculation                                                           |    |

| 2.3          | PHOTODETECTOR (PD) ARRAY DEVICES                                                    |    |

| 2<br>2.4     | 3.1 Introduction<br>Type A - Photodetector Array devices                            |    |

|              |                                                                                     |    |

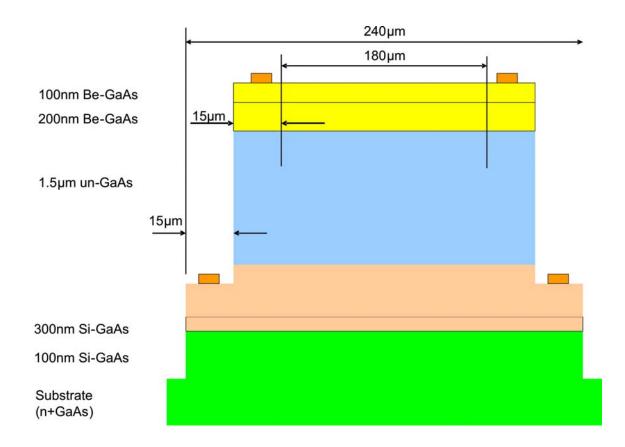

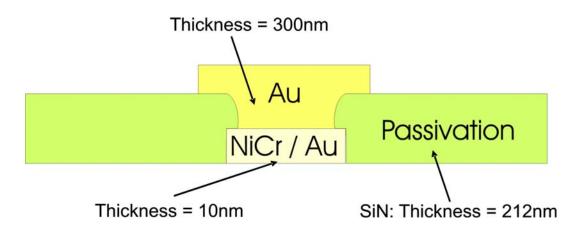

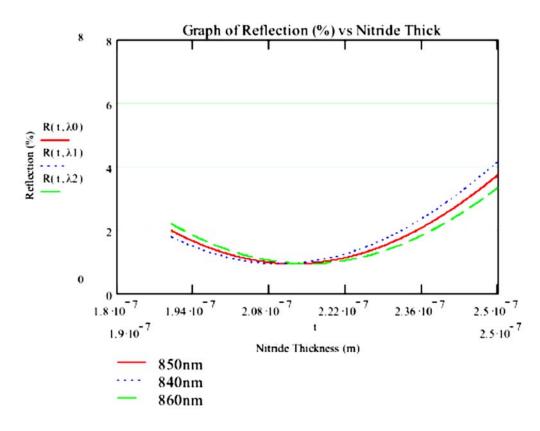

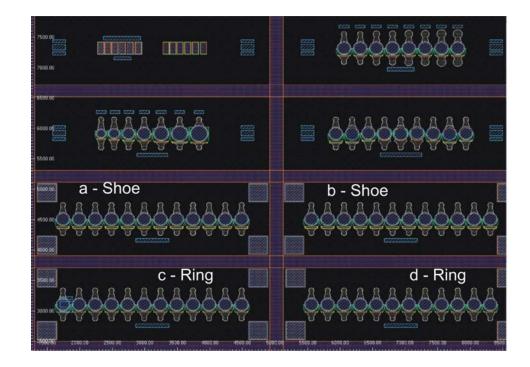

|              | <ul> <li>4.1 Introduction</li> <li>4.2 Device Specifications</li> </ul>             |    |

|              | 4.2 Device specifications                                                           |    |

| 4.           | т. <b>у</b> позино                                                                  |    |

| 2.5   | TYPE B - PHOTODETECTOR ARRAY DEVICES                  | 18 |

|-------|-------------------------------------------------------|----|

|       |                                                       |    |

|       | 5.1 Introduction                                      |    |

|       | 5.2 Cleaving of Type B Detector Wafer                 |    |

| 2.6   | DC CHARACTERISATION OF TYPE A DETECTOR ARRAYS         |    |

|       | 6.1 Introduction                                      |    |

| 2.0   | 6.2 Layout of Type A Photodetectors                   |    |

| 2.0   | 6.3 Experimental Set-up and Procedure                 |    |

| 2.    | 6.4 Results                                           |    |

| 2.    | 6.5 Summary                                           |    |

| 2.7   | DC CHARACTERISATION OF TYPE B DETECTOR ARRAYS         |    |

| 2.    | 7.1 Introduction                                      |    |

| 2     | 7.2 Layout of Type B Photodetectors                   |    |

|       | 7.3 Experimental Set-up                               |    |

|       | 7.4 Experimental Procedure                            |    |

|       | 7.5 Results                                           |    |

|       |                                                       |    |

|       | 7.6 Summary                                           |    |

| 2.8   | CONCLUSION                                            |    |

| 2.9   | References                                            |    |

| СНАР  | TER 3                                                 | 66 |

| UIIAI | 1 EK J                                                |    |

| TDAN  | COMPTED DEVICES AND MIVED SIGNAL CHIDS (MSCS)         | (( |

| IKAN  | SMITTER DEVICES AND MIXED SIGNAL CHIPS (MSCS)         |    |

| 3.1   | INTRODUCTION                                          |    |

| 3.2   | BACKGROUND                                            |    |

| 3.3   | VCSEL ARRAY                                           |    |

|       | 3.1 Introduction                                      |    |

|       | OPTOELECTRONIC CHARACTERISATION OF VCSELS             |    |

| 3.4   |                                                       |    |

|       | 4.1 Introduction                                      |    |

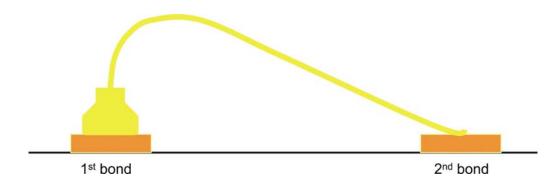

|       | 4.2 Wire bonding of VCSEL onto Pin Grid Arrays (PGAs) |    |

|       | xperimental work:                                     |    |

| 3.4   | 4.3 Characterisation of VCSELs                        |    |

| 3     | 4.4 Experimental Work                                 |    |

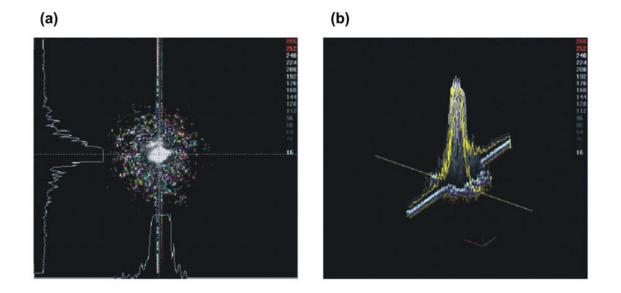

| 3.4   | 4.5 Beam Profile Analysis                             |    |

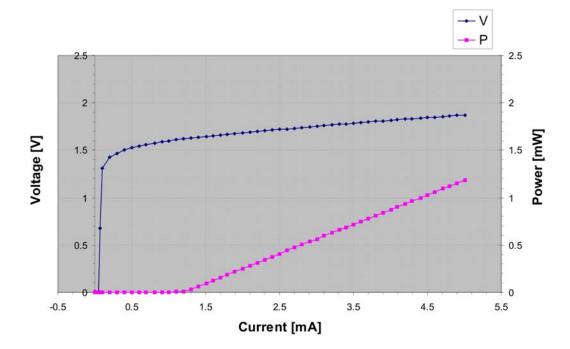

| 3.4   | 4.6 I-V-P Measurements                                |    |

| 3     | 4.7 Assembly of the System                            |    |

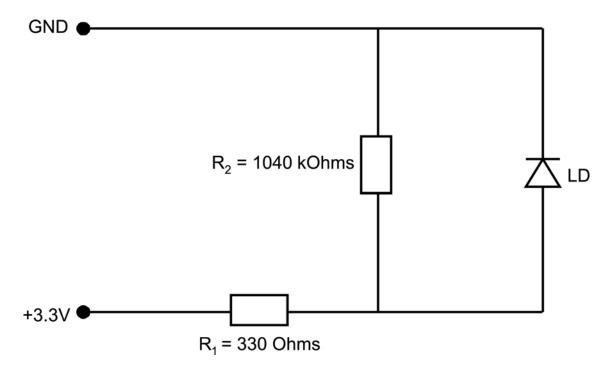

|       | 4.8 Construction of a VCSEL Driver                    |    |

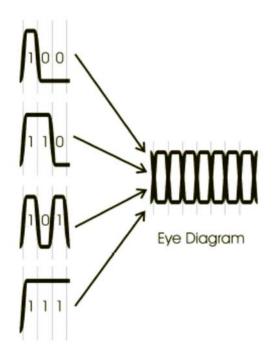

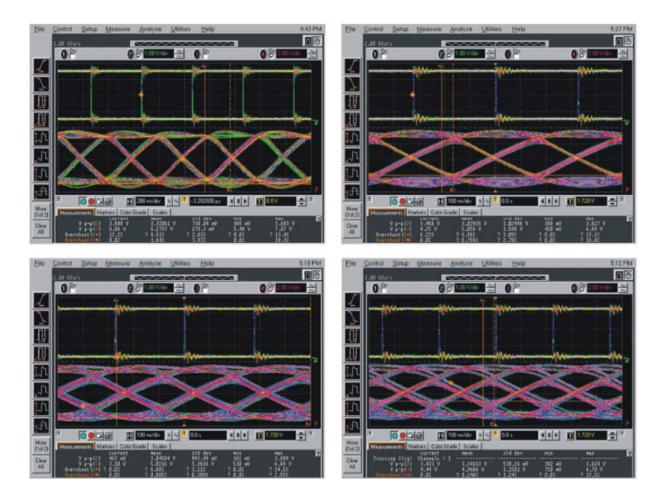

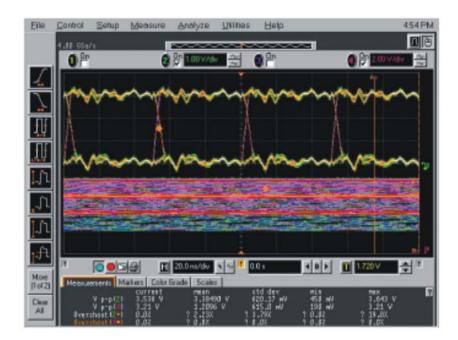

|       | 4.9 Measurements of Eye Diagrams                      |    |

|       | 4.10 Results for the Driver Circuit                   |    |

|       |                                                       |    |

|       | 4.11 Results for the Full System                      |    |

|       | 4.12 Summary                                          |    |

| 3.5   | MIXED SIGNAL CHIPS (MSCS)                             |    |

|       | 5.1 Introduction                                      |    |

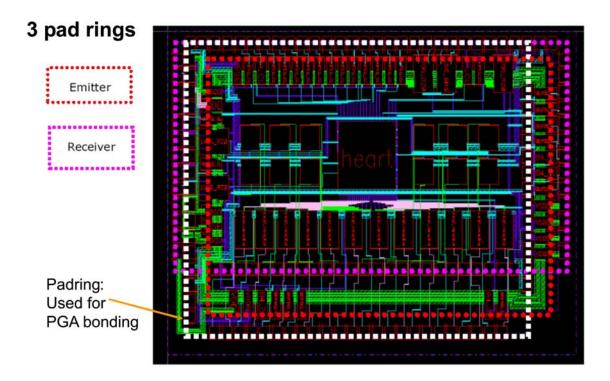

| 3     | 5.2 Chip Layout, Specifications and Pin-out           |    |

| 3     | 5.3 Technology Choice, Design and Modelling           |    |

| Те    | echnology Choice:                                     |    |

|       | esign Kits for Photodiode Amplifier and VCSEL Driver: |    |

|       | 5.4 Fabrication and testing of chips                  |    |

| 3.6   | CONCLUSION                                            |    |

| 3.7   | References                                            |    |

| 5.1   |                                                       |    |

| СНАР  | 'TER 4                                                |    |

|       |                                                       |    |

| орто  | ELECTRONIC PACKAGING (I)                              |    |

| 0110  |                                                       |    |

| 4.1   | INTRODUCTION                                          |    |

| 4.2   | BONDING TECHNIQUES                                    |    |

| 4.3   | BACKGROUND ON FLIP CHIP BONDING                       |    |

|       | 3.1 Introduction                                      |    |

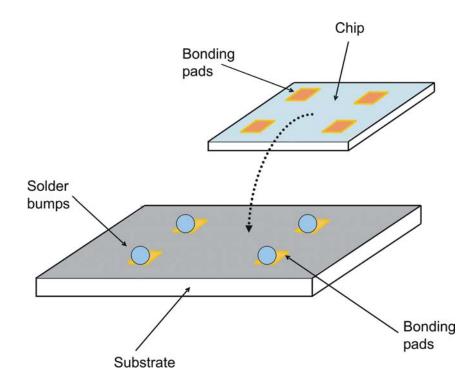

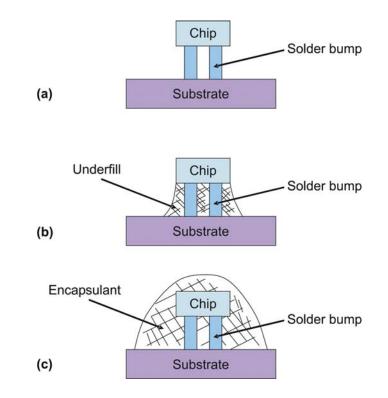

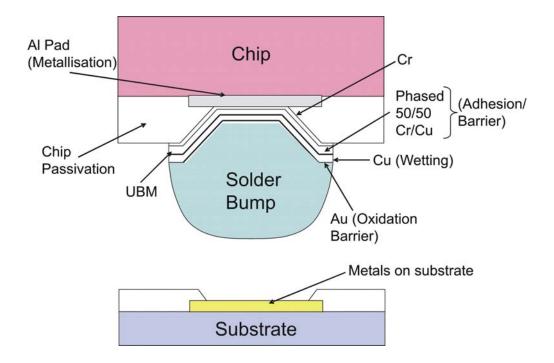

|       | 3.2 Flip chip assembly process                        |    |

|       | 3.3 Under Bump Metallisation (UBM)                    |    |

|       | 1                                                     |    |

|       | 3.4 Bump Materials                                    |    |

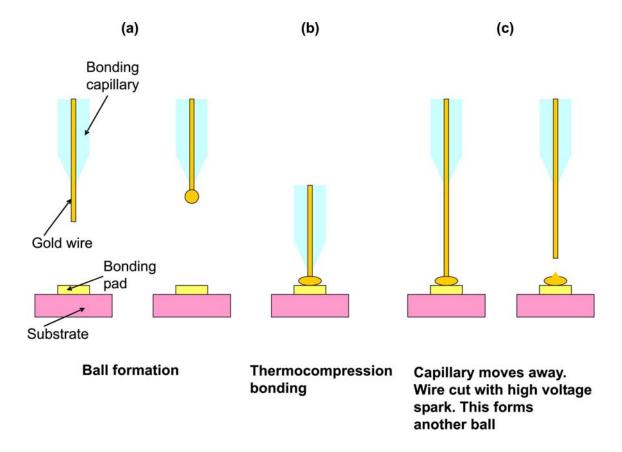

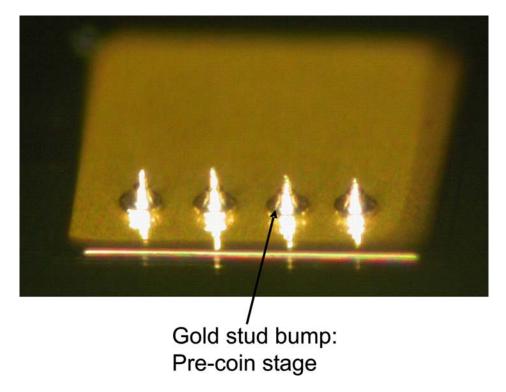

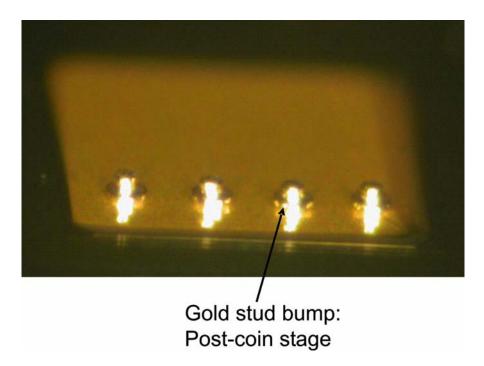

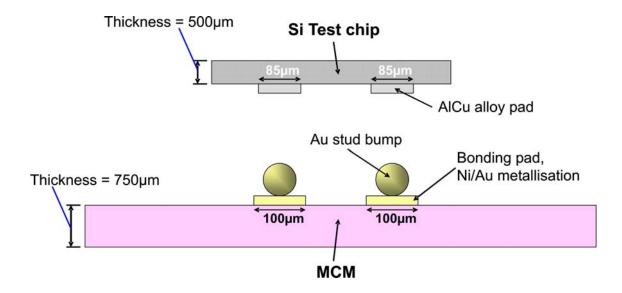

|       | 3.5 Gold Stud Bumping process                         |    |

| 4.4   | ANISOTROPIC CONDUCTIVE FILM (ACF)                     |    |

| 4.4   | 4.1 Introduction                                      |    |

| 4.5  | OPTOELECTRONIC PACKAGING EXPERIMENTS                   |     |

|------|--------------------------------------------------------|-----|

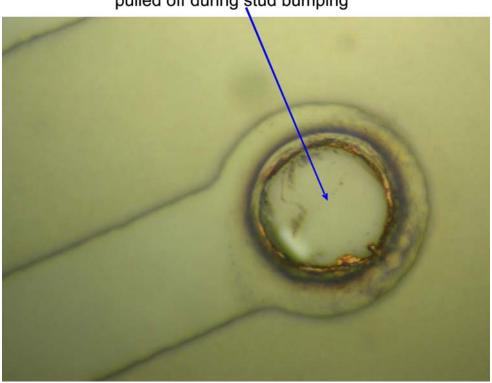

| 4.5  | 5.1 Gold Stud Bump Experiments                         |     |

| 4.5  | 5.2 Flip Chip Bonding Work                             | 110 |

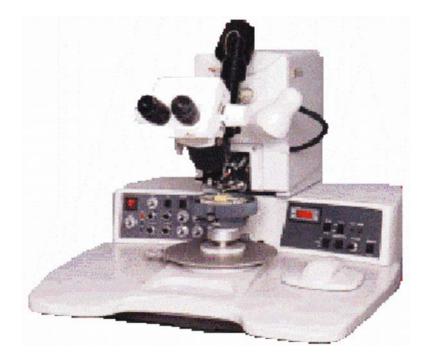

|      | ip Chip Bonder:                                        |     |

| Cı   | ustom Designed Flip Chip Chuck:                        |     |

| 4.5  | 5.3 Design of Test Substrates                          | 111 |

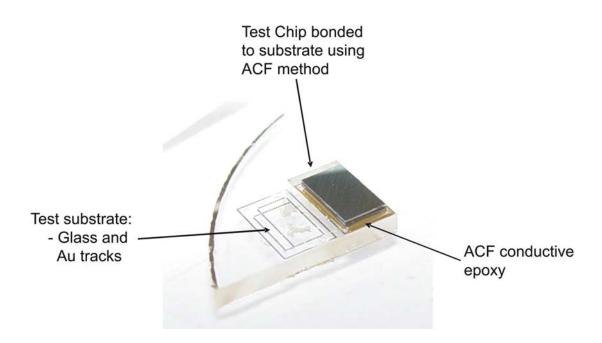

| 4.5  | 5.4 Bonding Experiments                                | 113 |

| 4.6  | CONCLUSION                                             | 116 |

| 4.7  | References                                             |     |

| СНАР | TER 5                                                  |     |

| OPTO | ELECTRONIC PACKAGING (II)                              |     |

| 5.1  | INTRODUCTION                                           |     |

| 5.2  | OPTOELECTRONIC MULTI-CHIP MODULE (OE-MCM)              |     |

| 5.2  | 2.1 Introduction                                       |     |

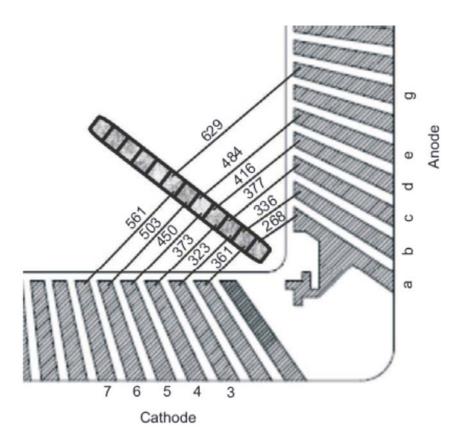

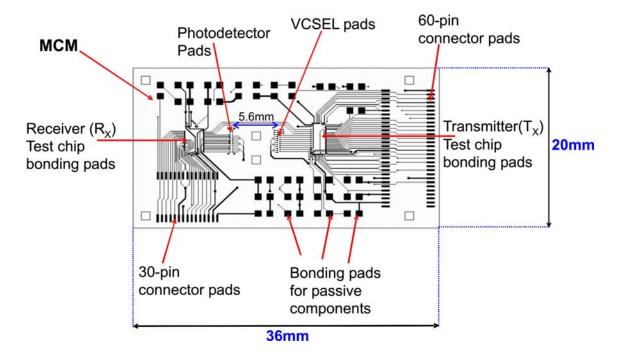

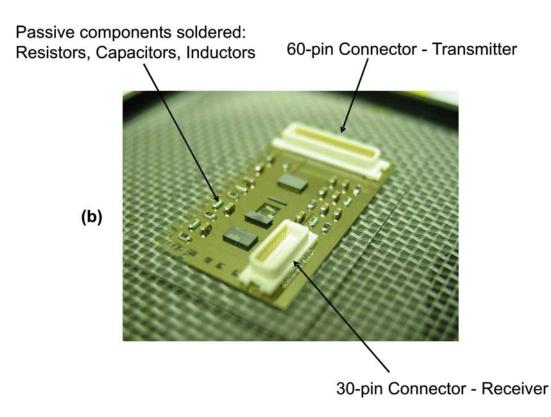

| 5.2  | 2.2 Specifications and Layout of OE-MCM                | 121 |

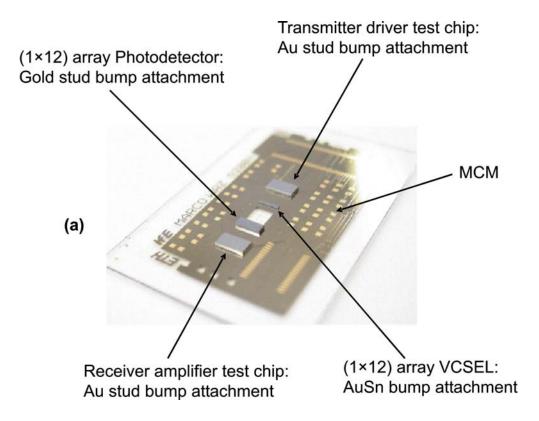

| 5.3  | OPTOELECTRONIC PACKAGING EXPERIMENTS ON OE-MCMS        |     |

| 5.3  | 3.1 Introduction                                       | 123 |

| 5.3  | 3.2 Initial Experiments                                | 123 |

| Ga   | old Stud Bumping Problems on OE-MCM:                   |     |

| 5.3  | 3.3 Flip Chip Bonding Work on OE-MCMs                  |     |

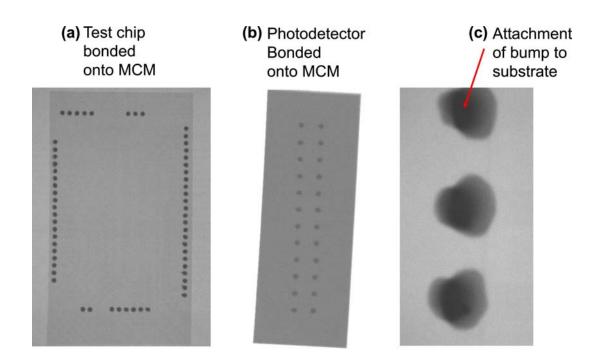

| 5.3  | 3.4 Fully Populated Test Modules – 1 <sup>st</sup> Run | 125 |

| Pr   | oblems faced with bonding the electronic devices:      | 128 |

| Fu   | irther Bonding:                                        |     |

| 5.3  | 3.5 Summary                                            |     |

| 5.4  | FURTHER RESEARCH INTO ALTERNATIVE BONDING TECHNOLOGIES |     |

| 5.4  | 4.1 Lead-free Solder Bumps                             |     |

| 5.4  | 4.2 Gold Micro-Posts                                   |     |

| 5.4  | 4.3 Ultrasonic Flip Chip Bonding                       |     |

| 5.5  |                                                        |     |

|      | 5.1 Test Module Production                             |     |

|      | 5.2 X-ray analysis of bump attachment                  |     |

|      | 5.3 Summary                                            |     |

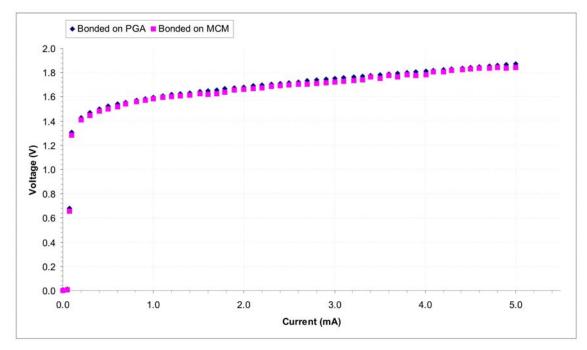

| 5.6  |                                                        |     |

|      | CSEL Arrays:                                           |     |

|      | hotodetector Arrays:                                   |     |

| 5.7  |                                                        |     |

|      | 7.1 Introduction                                       |     |

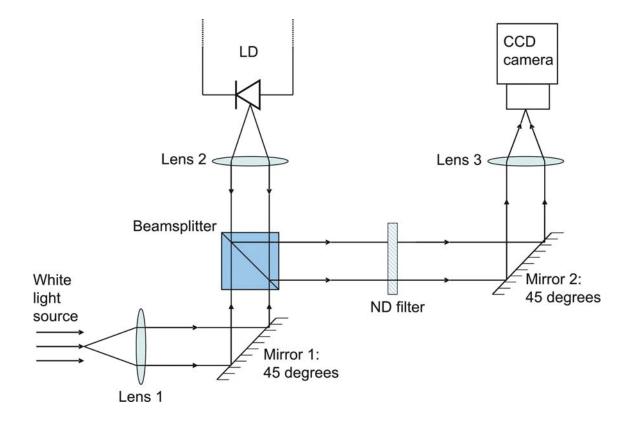

|      | 7.2 Experimental set-up                                |     |

| •••  | 7.3 Results                                            |     |

| 5.8  | Conclusion                                             |     |

| 5.9  | References                                             |     |

| СНАР | TER 6                                                  |     |

| CONC | LUSIONS                                                |     |

| 6.1  | INTRODUCTION                                           |     |

| 6.2  | Assessment of work                                     |     |

| 6.3  | FUTURE DIRECTIONS                                      |     |

| 6.4  | SUMMARY                                                |     |

# Glossary

| ACF   | Anisotropic Conductive Film                      |  |

|-------|--------------------------------------------------|--|

| AMOS  | Analysis and Modelling of Optoelectronic Systems |  |

| ASIC  | Application Specific Integrated Circuit          |  |

| BGA   | Ball Grid Array                                  |  |

| CCD   | Charged Coupled Device                           |  |

| CMOS  | Complimentary Metal-Oxide Semiconductor          |  |

| COTS  | Commercial-Off-The-Shelf                         |  |

| CPU   | Central Processing Unit                          |  |

| CSP   | Chip Scale Packaging                             |  |

| CTE   | Coefficient of Thermal Expansion                 |  |

| DBR   | Distributed Bragg Reflector                      |  |

| DOE   | Diffractive Optical Element                      |  |

| DSP   | Digital Signal Processor                         |  |

| EFO   | Electronic Flame-Off                             |  |

| EMS   | Electronic Manufacturing Services                |  |

| FPGA  | Field Programmable Gate Array                    |  |

| GBP   | Gain Bandwidth Product (GBP)                     |  |

| HOLMS | High-Speed Opto-eLectronic Memory System         |  |

| IOB   | Input/Output Block                               |  |

| LIV   | Optical Power (L) Current (I) Voltage (V)        |  |

| LVDS  | Low Voltage Differential Signalling              |  |

| MBE   | Molecular Beam Epitaxy                           |  |

| МСМ   | Multi Chip Module                                |  |

| MCM-D | Multi Chip Module – Deposited                    |  |

| MEM   | Memory                                           |  |

| MOCVD  | Metal-Organic Chemical Vapour Deposition                               |  |

|--------|------------------------------------------------------------------------|--|

| MPW    | Multi Project Wafer                                                    |  |

| MSC    | Mixed Signal Chip                                                      |  |

| MSM    | Metal Semiconductor Metal                                              |  |

| NEFO   | Negative Electronic Flame-Off                                          |  |

| NEP    | Noise Equivalent Power                                                 |  |

| OCC    | Optoelectronic Chip Carrier                                            |  |

| OE-MCM | Opto-Electronic - Multi Chip Module                                    |  |

| PCVD   | Plasma-enhanced Chemical Vapour Deposition                             |  |

| PGA    | Pin Grid Array                                                         |  |

| PIFSO  | Planar Integrated Free Space Optics                                    |  |

| PIN    | Detector with an active intrinsic region sandwiched into a PN junction |  |

| PLC    | Planar Lightwave Circuit                                               |  |

| PTFE   | PolyTetraFluoroEthylene                                                |  |

| RIE    | Reactive Ion Etching                                                   |  |

| SCIOS  | Scottish Collaborative Initiative in Optical Sciences                  |  |

| SEM    | Scanning Electron Microscope                                           |  |

| SIA    | Semiconductor Industry Association                                     |  |

| SiOB   | Silicon Optical Bench                                                  |  |

| SOI    | Silicon On Insulator                                                   |  |

| SPA    | Smart Pixel Array                                                      |  |

| SPOEC  | Smart Pixels for Opto-Electronic Connections (SPOEC)                   |  |

| STAR   | System for Transparent Avionics Routing                                |  |

| TIA    | Trans-Impedance Amplifier                                              |  |

| UBM    | Under Bump Metallurgy                                                  |  |

| VCSEL  | Vertical Cavity Surface Emitting Laser                                 |  |

### List of Publications

The work in this thesis has been published in the following conference papers and is listed in chronological order.

- S. Kumpatla, J. J. Casswell and J. F. Snowdon, "Solutions to Optoelectronic Interconnect Problems," *Proceedings. PREP 2005 Conference.*, Lancaster University, UK, pp. 106-107, 2005.

- S. Kumpatla, J. J. Casswell and J. F. Snowdon, "Solutions to Optoelectronic Interconnect Problems," *Proceedings. IoP Physics 2005 Conference.*, University of Warwick, UK, April 10-14, 2005.

- [3] S. Kumpatla, J. J. Casswell and J. F. Snowdon, "Solutions to Optoelectronic Interconnect Problems," *Proceedings. Information Photonics 2005 Topical Meeting.*, Charlotte, NC, USA, June 6-9, 2005.

- [4] J. J. Casswell, S. Kumpatla and J. F. Snowdon, "Board Integrated Micro-Optics for divergence management in Opto-Electronic Interconnect Systems," *Proceedings. Information Photonics 2005 Topical Meeting.*, Charlotte, NC, USA, June 6-9, 2005.

- [5] S. Kumpatla, J. J. Casswell and J. F. Snowdon, "Solutions to Optoelectronic Packaging Problems," *Proceedings. CLEO/Europe EQEC 2005 Conference.*, Munich, Germany, June 12-17, 2005.

#### Chapter 1

#### **Background and Thesis Overview**

#### 1.1 Background

With increased development of computer technology, the information processing power grows with each generation. Enhancement in design and fabrication of individual computer chips facilitate devices to operate faster, to consume less electrical power and to execute more complex functions. Essentially, this is accomplished by shrinking the size scale of the transistors and applying a lower voltage swing to assign the digital bits. Although this plan of reducing the transistor size is projected to continue to improve the performance of the chips, the Semiconductor Industry Association (SIA) has predicted that the operation of the overall system in the future will be limited by the metallic wires that connect the chips to each other [1.1]. Albeit, processors and memory may get faster and more efficient, but the ability of these chips to communicate with each other will be made worse by the deficiencies of the electrical interconnections.

Studies have been carried out by several researchers on the fundamental limits of electrical interconnects and have proposed various solutions [1.2]-[1.16]. Possibly, advanced electronic architectures will be sufficient to tackle these problems for the future [1.13], [1.14]. In parallel to these all-electrical approaches, numerous research efforts have been concentrating on substituting wires with optical links. For basic physical reasons, optical interconnects offer many advantages over electrical interconnects for high speed links [1.15]. Conversely, practical concerns, such as design complexity, manufacturability, cost and reliability, must also be taken into consideration whether optical interconnects will break in the marketplace [1.16].

#### **1.2 Optics for Communication**

Light is electro-magnetic (EM) radiation with wavelengths in the ultra-violet to infrared range. It's capability to travel at a high speed and long distances with minimal interaction with its surroundings has long been known and utilized. With the invention of the laser, optical communications came of age. The laser is an application of Einstein's theory in which a photon could stimulate an excited atom to emit another identical photon. Such a device was proposed by Schawlow and Townes [1.17] in 1958, but it was four years before semiconductor based devices were demonstrated by four different research groups roughly simultaneously [1.18]-[1.21].

Modern day versions of these devices have advanced enormously since their early development. This is due to new and more efficient fabrication technologies and also to radical ideas. Long haul fibre optic communications systems have become ubiquitous with almost every call passing through fibre-optic cabling at some point on its route. Optical technologies have begun to invade on areas that were once firmly considered to be the area of electronics.

The advantages of optics are available over increasingly smaller distances and with them the increased bandwidth they offer. Yet, the main recipients of the bandwidth that optical communications can provide, i.e. information systems, computers, homeentertainment, are required to convert this information back into the electrical domain in order to transmit around their internal networks and buses. Therefore, as data rates increase, new bottlenecks occur.

In the microelectronics industry, the mainstream silicon VLSI (Very large scale integration) process used to fabricate the widespread integrated circuit (IC) is a very mature, well developed and high yield process. This is as a result of major investment and research over a number of decades.

In the main, connections between chips, between boards (of chips), and between systems are done electrically. With more and more processing power being compressed into even smaller dimensions, it is the bottleneck of getting data between chips, boards and systems through electrical connections, which is foreseen as the barrier to benefiting from the predicted improvements in VLSI devices. Electrical interconnections do not scale well with diminishing feature sizes. Reduced wire cross-sections and larger die sizes result in increased resistances and consequently larger RC delays. Faster clock rates, increased current-densities and smaller wirer pitches also aggravate crosstalk problems.

The use of "optical interconnects" is seen as an extremely promising option which could provide a viable, cost effective solution to this problem. A large body of research has been carried out over the past 15 years, and is ongoing, into the feasibility of using freespace and guided wave optics for transmitting data over much shorter distances than those in fibre optic telecommunications systems. As a consequence of the advances in technology, the demand for higher data rates increases, and the distance over which optics out-performs electrical transmission gets shorter.

Additionally, there is the fact that demand for bandwidth is predicted to exponentially increase [1.22], and that electronic and memory transistor densities continue to scale according to Moore's Law [1.23], while interconnect technologies do not. At higher speeds, the old limitations of electrical communications previously encountered over long ranges are being experienced at shorter distances. Taking into consideration all these issues, it can be seen that there is clear need for research into ways to counter these electrical bottlenecks and provide an efficient way with which to connect the subsequent systems to the high bandwidth capabilities of long distance optical communications.

#### 1.3 Moore's Law

In 1965, Intel [1.24] co-founder Gordon Moore forecasted the rapid pace of technology innovation. His prediction is known as "Moore's Law" [1.23]. This states that the number of transistors on an integrated circuit roughly doubles every two years. This continued reduction in feature sizes on chips translates to faster devices with increased functionality, at a lower cost per device.

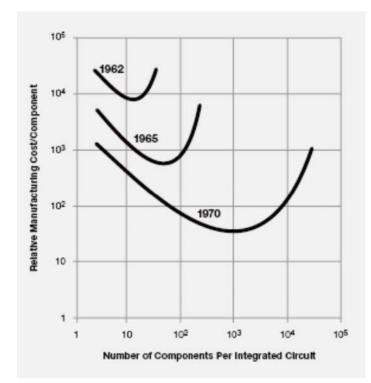

Figure 1 [1.23] shows Moore's estimate of the cost of integrated circuits divided by the number of components in an integrated structure at various times. Further details of Moore's Law can be found in the following references [1.25]–[1.27].

Figure 1) Shows relative manufacturing cost per component versus components in the circuit estimated for various times

#### 1.4 Research Motivation

The motivation for this research comes from limitations of providing, electronically [1.15], [1.16], an interconnection network able to provide the bandwidth required to match the increasing processor performance of commodity processors. Optics is already widespread in the telecommunications industry in high bandwidth applications, but computing applications has different regimes in terms of acceptable latencies than telecommunications.

The following will describe some of the areas where electronic interconnects have known problems, how optics can solve them and why this is a problem for computer systems.

#### 1.4.1 Electronic Limits

Although Moore's Law has held true for the past forty three years, there are fundamental limits to conventional microprocessor scaling, i.e. the quantum limit being the most profound. It is very likely that a technological limit will be reached prior to this, such as the issue of power dissipation or gate insulator breakdown.

#### **Bandwidth:**

Preceding the fundamental Shannon limit, Miller and Özaktas show in [1.28] that there is a constraint, to the amount of information that can be transmitted through a simple wire interconnect. This derived from the Physics of electrical signals travelling along wires. The result is independent of the interconnect design and is dependent on the ratio of the length squared to the total cross-sectional area, i.e. the 'aspect ratio' [1.15]. For electronic interconnects there exists the 'aspect ratio' limit [1.15] to bandwidth. This limit, occurring from skin effects is proportional to  $f^{4/2}$  above a certain critical frequency. The total capacity of any electronic connection,  $B_{MAX}$ , is related to the overall crosssection, *A*, and the length, *L*:

$$B_{MAX} = B_0 \frac{A}{L^2} \tag{1.1}$$

The constant  $B_0$  is related to resistivity of the interconnect and is only weakly dependent on the fabrication technique. For copper, it is about 10<sup>14</sup> bit/s, for co-axial cable, 10<sup>15</sup> bit/s, for multi-chip module (MCM) and cross-chip lines it is 10<sup>16</sup> bit/s. This limit is scale invariant and for a fixed cross-section it is independent of whether interconnect is made of many slow wires or few fast wires until other effects such as dielectric absorption (which is independent of cross-section) dominate.

Due to the dielectric absorption, which increases in proportion to frequency, there is an upper limit on operating speed. For example, standard strip-line on FR4 (this is standard PCB material) is limited to 1m at 1GHz, whereas a good low-loss material such as Polytetrafluoroethylene (PTFE) would reach up to 10m.

There is no equivalent aspect ratio limit for optics. The dispersion of the signal over long distances leads to a fixed bandwidth-distance product for optical transmission lines (1GHz km for typical multimode fibre). For the distances dealt with in this thesis (generally <1m), this is not considered a limiting factor. At the scale in question, the limiting factor for bandwidth will be the speed of the transceiver electronics.

#### **Power:**

A key problem with electronic interconnects is the power dissipated in terminating resistors, especially in conventional complementary metal oxide semiconductor (CMOS) signalling. The application of low-voltage differential signalling (LVDS) technologies can be beneficial, but the drawback is that this results in increased circuit complexity and higher susceptibility to noise.

Even with LVDS, electronic interconnects have power dissipation generally an order of magnitude higher than an optical equivalent. This is generally due to the larger parasitic capacitance of electronic interconnects (order of 1pF compared to 100fF for small optoelectronics). For example, a commercially available 2.5Gbit/s bi-directional electronic transceiver core has a power dissipation of 200mW per channel. In contrast, 1Gbit/s optical transceivers have been demonstrated with lower than 10mW power consumption.

#### **Pin Density:**

The exponential growth in transistor densities, as predicted by Gordon Moore in 1965 has progressed to smaller and faster chips. This has lead to the input/output (I/O) pins connecting the chips to the outside world being a major problem. To avoid increasing the frequency of the I/O pins operation, more pins are required. At the same time, the chips are reducing in size and because of the planar nature of electronic design; the space available around the chip for connections is shrinking. The size of the I/O pins cannot be decreased much further because of the bandwidth limitation imposed by reducing the cross-sectional area and by the increasing difficulty in working with very fine, i.e. ~ microns, metal wire.

Optics could provide a solution to this problem. It is unproblematic to fabricate arrays of optoelectronic devices with their optical I/Os normal to the chip. Also, it is feasible to have the I/O connected across the whole area of the chip by placing electronic I/O pads across the chip's surface and using a bonding technology such as flip chip bonding to stack the optoelectronic chip on top [1.29]. This has the advantage of allowing the surface area and not the edges of the chip to be used for I/O. In this case, the solder links between the electronic chip and optoelectronic chip would be very short so the bandwidth can remain very high.

#### **Other Factors:**

Electronics also suffers from a number of other problems, when high speed interconnects are implemented. These include the cross-talk, caused mainly by the mutual inductance and capacitance of adjacent signal lines, and the finite impedance of a common signal return in a connector or package pin. In addition, interference from other devices can be an issue. Optical signals are immune to electro-magnetic interference from other devices. By providing sufficient spacing between channels, common signal returns and cross-talk from adjacent channels can be prevented.

It is also a major problem to construct electronic transmission lines with uniform characteristic impedance. Discontinuities in the transmission medium caused by package pins, connectors, vias and gaps in the signal return plane lead to unwanted reflections that lead to noise. At high frequencies, this becomes a major issue as even small discontinuities in the impedance can cause large reflections due to the broadband nature of the electronic signal. As optical signals are modulated onto a very high frequency carrier ( $\sim 10^{14}$  Hz), they are considered to be narrowband, and the impedances of the transmission line can be matched to the load (i.e. the detector) and by quarter-wavelength sections of transmission medium. This is in the same manner as narrowbandwidth microwave signals. This is generally achieved with quarter-wavelength dielectric anti-reflection coating.

#### 1.5 Research Work Conducted on Optical Interconnects in Industry

#### 1.5.1 Introduction

A number of companies, such as Intel [1.24], Terahertz Photonics Ltd [1.30] and Luxtera [1.31] have been studying optical interconnects. I will discuss the research conducted by these corporations in the following sections, starting with Intel.

#### 1.5.2 Research by Intel

The Intel Technology Journal (Volume 8, Issue 2, May 2004) [1.32] investigated Intel's work on optical technologies and applications. Optical interconnects were discussed in two papers [1.33], [1.34]. This research was conducted by a team from Intel Components Research Lab. This was led by Intel Senior Fellow, Dr Ian Young.

Also, research on silicon photonics is examined in paper [1.35]. This work was led by Intel Fellow and director of the Photonics Technology Lab, Mario Paniccia. The following sections will discuss these studies.

#### **Optical Interconnects:**

The work from [1.33] examined two feasible options for high performance and costeffective optical interconnect solutions. The first study looked into the silicon optical bench solution (SiOB). The optical design, processing and assembly challenges of this approach were discussed in detail. This method allowed passive alignment of optical components using lithographic definition of fine structures on the silicon substrate and as a result was expected to have a cost reduction. The second study discussed the system architecture and design of (1x12) optical transceiver. This was developed by Intel using a hybrid integration of components on a microprocessor-style package. By using this method, it would have a minimum effect on the existing motherboard technology and so lower costs.

The work from [1.34] examined the capability of on-chip applications of optical interconnects to alleviate the constraints of metal interconnects. Specifically, a comparison of the performance and cost of optical interconnects and copper interconnects for clock distribution and intra-chip global signalling was performed. Their analysis did not show any major benefits for on-die clock distribution using optical interconnects as compared to standard clock distribution. For signalling, it was found that optical interconnects, in combination with wavelength division multiplexing, can possibly offer a low latency-high bandwidth option.

#### Silicon Photonics:

At Intel, silicon photonics is defined as the use of silicon-based materials for the transmission (electrical-to-optical conversion), guidance, control and detection (optical-to-electrical conversion) of light to communicate information over distance.

The work from [1.35] examined the research on optoelectronic integration using siliconbased optical components, which included a tunable external cavity laser, a 2.5GHz optical modulator and a silicon-germanium waveguide-based photodetector. Mario Paniccia's team concentrates on developing silicon-based photonic building blocks for future use in enterprise and data centre communications. They have built the first silicon modulator with bandwidth greater than 1GHz in 2004 [1.36]-[1.38].

They also developed the first continuous wave silicon laser in 2005 [1.39], [1.40] using the Raman Effect [1.41], [1.42]. This enabled silicon to amplify light and create continuous beams of laser light for the first time. Intel's existing CMOS manufacturing processes was used to create this. Applications such as optical amplifiers, lasers and wavelength converters could be used for this device.

Also, in collaboration with Professor John Bowers in the Optoelectronics Research Group at University of California, Santa Barbara [1.43], the first electrically pumped hybrid silicon laser was developed in 2006 [1.44], [1.45]. This device integrated the light-emitting potential of Indium Phosphide with the light-routing and low cost benefits of silicon. With this development, silicon photonic chips containing dozens or even hundreds of hybrid silicon lasers could in the future be created using standard high-volume, low-cost silicon manufacturing techniques.

#### 1.5.3 Terahertz Photonics Ltd

Terahertz Photonics Ltd [1.30] was a start-up company based in Livingston. It specialised in the field of photonic integrated circuits, optical waveguide devices and thin-film optical coatings for telecommunications. It was founded in November 1998 by two academics, Dr Frank Tooley and Professor Gerald Buller, from the Department of Physics at Heriot-Watt University.

One of the key technologies of Terahertz was its use of polymers for planar lightwave circuits (PLC). This had advantages of rapid high-yield processing, high thermal stability, low loss and high reproducibility of thickness and refractive index. In

November 2002, due to difficulties in obtaining further funding, it closed its optical device division and sold its specialist coatings division to Helia Photonics [1.46]. Subsequently, in August 2003, Terahertz Photonics Ltd went into liquidation.

#### 1.5.4 Luxtera

Luxtera [1.31] has developed a CMOS Photonics technology platform [1.47]. The technology integrates two lasers and photodetectors, which are mounted on a monolithic CMOS die. It also includes transimpedance amplifiers (TIAs), Mach-Zehnder modulators and receive Clock and Data Recovery (CDR) circuits.

The monolithic recipe of photonics and electronics in a production CMOS process allows a single CMOS Photonics chip to replace tens to hundreds of discrete optical and electronic components. This reduces size, power consumption and cost of the device. This complete single chip solution is fabricated using the 0.13µm silicon on insulator (SOI) CMOS process.

Implementation of 40Gbit/s interconnection between optical fibre to optoelectronic chip in communications is feasible with this device. Other applications this technology can be used in are optical sensors in infrared cameras, interactive gaming, and medical imaging.

#### 1.6 Research Work Conducted on Optical Interconnects in Academia

#### 1.6.1 Introduction

A number of academic organizations, which includes work in my group [Optically Interconnected Computing (OIC) Group] [1.48] at Heriot-Watt University (HWU), have developed optical interconnect systems in the lab [1.49]-[1.53]. The main differences among the various research projects, is they have a tendency to be in two fields: (1) the choice of optoelectronic devices, i.e. lasers or modulators; PIN or metal semiconductor metal (MSM) detectors and (2) the design of the optical system.

I will discuss in the following sections research conducted on optical interconnect systems by academic groups at HWU, Miller Group at Stanford University [1.54], Optoelectronics Research at University of California San Diego [1.55], [1.56], C-LAB [1.57], University of Hagen [1.58] and Vrije Universiteit Brussel (VUB) [1.59].

#### 1.6.2 Optically Interconnected Computing at Heriot-Watt University (HWU)

The Department of Physics at HWU has been working in the fields of optical computing and optical interconnects for the last 27 years. This section will describe projects successfully completed by the Optically Interconnected Computing (OIC) Group. The achievements of the following projects in this order: SCIOS, SPOEC, AMOS, NOSC, STAR, and POCA, are discussed.

#### The Scottish Collaborative Initiative in Opto-electronic Sciences (SCIOS) project

[1.60], [1.61] was a collaborative effort between the universities of Heriot-Watt, Edinburgh, Glasgow and St. Andrews. This project produced the 1K sorter demonstrator, which was an early example of a system demonstrator using smart-pixels. This was designed to sort 1024 data words using a bitonic sort algorithm. Free-space optics were used to route a  $32\times32$  array of diffractively fan-out optical signals between two optoelectronic chips, i.e. from the modulators of one chip to the detectors of the second and then back via a similar process.

The Smart Pixels for Opto-Electronic Connections (SPOEC) project [1.62], [1.63] successfully developed a demonstrator. It was designed as a crossbar switch that would allow the routing of packet data from any of its inputs to any of its outputs. This used optoelectronic technology, which allowed inter-chip communication at the rate of 1 Tbit/s. In order to demonstrate this level of aggregate Input/Output bandwidth to a single silicon CMOS chip, the free-space paradigm was chosen as the main optical technology, as it was well suited to short range, high bandwidth and parallel interconnection purposes. The successful operation of the demonstrator showed that this approach used was feasible.

### The Analysis and Modelling of Optoelectronic Systems project (AMOS) project

[1.64], [1.65] investigated the use of optics and optoelectronic systems within computer architectures. The project, along with The Informatics Group at University of Leeds whom worked on the high-level algorithmic modelling of the system, continued work previously done in the Department of Physics, Heriot-Watt University, i.e. SCIOS and SPOEC projects.

The aim of the AMOS project was on modelling the close integration of electronic processors, to perform the computation, with free-space optics to provide short range

(~centimetres) communication between the processors. The research conducted concentrated on the optoelectronic interfaces that were required to connect the processors with the optics. Initial studies were performed using computer simulations with later proof-of-concept demonstrators assembled and tested.

The conclusion of the AMOS project was that a completely connected approach provides higher bandwidth per link. This result comes from the high dependence that the performance of the local hop approach has on the electronic, which includes the photocurrent receivers, and optoelectronic components primarily due to power dissipation and yield issues.

In the NOSC (Neural Optoelectronic Switch Controller) project [1.66]-[1.68], HWU developed a demonstrator using optics to perform very high connectivity and offthe-shelf electronics to provide neuron functionality. In the system, arrays of detectors and VCSELs act as neuron inputs and outputs with complex neural interconnection patterns woven through free-space using a single diffractive optical element (DOE). The system constructed consisted of 64 neurons in an  $8 \times 8$  array. A DSP solution was adopted to provide flexibility. The construction of the optoelectronic neural network demonstrator showed the potential of optical interconnection. This allowed architectures to be developed, which were previously prevented by electronics.

**The System for Transparent Avionic Routing (STAR) project** [1.69], [1.70] was collaborated between Heriot-Watt University, Imperial College London, BAE Systems and DERA Malvern. The HWU group was responsible for investigating suitable optoelectronic components as well as the packaging and assembly of the switch.

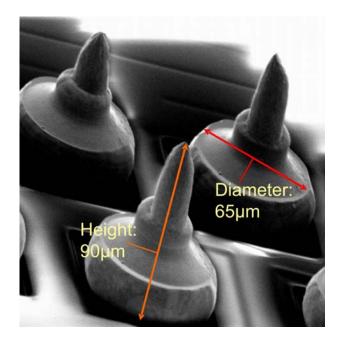

The STAR project investigated the characterisation and integration of suitable devices to form a high-speed optoelectronic crosspoint interconnect demonstrator. The system was based on a novel technique in which an 850nm VCSEL array, GaAs metal-semiconductor-metal (MSM) photodetector array and SiGe crosspoint chip were integrated onto an optoelectronic chip carrier (OCC) substrate using compliant polymer bump flip chip bonding. This used multimode polymer waveguides with total internal reflection, or metallised, 45 degree mirror ends. The waveguides, mirrors and bond bumps were successfully fabricated on glass substrates by direct writing of a custom

polymer material, using a continuous wave (CW) He-Cd laser.  $50 \times 50 \mu m$  multimode waveguide cores were written together with arrays of polymer bumps with diameters and heights of 50 and 100 $\mu m$  respectively.

The Programmable Optoelectronic Computing Architecture (POCA) project [1.71], [1.72] investigated the integration of an optoelectronic communications system with reconfigurable field programmable gate array (FPGA) devices. This was for use in reconfigurable parallel computing architectures based on the analytical results from the previously funded AMOS project, the knowledge of the optoelectronic integration gained through the European Commission funded SPOEC and HOLMS [1.73] projects and digital device characteristics from commercially available FPGAs. The achievements from this project, showed that optoelectronic integration of FPGAs and high bandwidth optical interconnects were feasible.

#### 1.6.3 The Miller Group, Stanford Photonics Research Center, Stanford University

The Miller Group [1.54] led by Professor David Miller have conducted extensive research on optical interconnects, optoelectronic devices and ultrafast all-optical switches. Also, Professor Miller [1.74] and the Miller Group [1.75] have written numerous journal publications and conference proceedings in the field of optoelectronics and photonics.

#### 1.6.4 Optoelectronics Research at University of California San Diego

The OptoElectronic Computing Group (OECG) [1.55] led by Professor Sadik Esener at the University of California San Diego conducts research on parallel optoelectronic computer systems through the optimal utilization of micro-electronic and photonic technologies. The OECG is an integral part of the Optoelectronics Technology Center (OTC) [1.56] at University of California San Diego. This is a centre is funded by DARPA [1.76]. The OTC is led by Professor Larry Coldren and was established to facilitate fundamental advances in photonics and optoelectronics. Specific projects have included work on advanced VCSELs [1.77]-[1.79] and photodetector arrays [1.80] as well as their combination with integrated circuits using new heterogeneous integration technologies [1.81]. This technology should provide new device and material capabilities for the next generation of computer interconnects, communications and optical biosensors.

#### 1.6.5 Optical Interconnection Technology Group (OIT) - C-Lab

The Cooperative Computing & Communication Laboratory (C-LAB) is a joint research and development laboratory managed by Siemens AG [1.82] and the University of Paderborn [1.83] in Germany. It was founded in 1985.

Since 1998, the Optical Interconnection Technology (OIT) Group at C-LAB has conducted extensive research in the field of optical interconnection technology for printed circuit boards. In the project "EOCB" (Electrical-Optical Circuit Board) [1.57], [1.84] basic investigations of optical interconnection technology were performed. The research examined the feasibility of electrical-optical printed circuit boards and assessed their application in areas such as computer technology.

Other projects studied at C-LAB included OptoSys (Optical Interconnections Systems), OptiCon and HOLMS (High Speed Optoelectronic Memory System) [1.57]. The HOLMS project will be discussed in further detail later in this chapter.

#### 1.6.6 Optical Information Technology (ONT) Group - University of Hagen

The Optical Information Technology (ONT) Group led by Professor Jurgen Jahns at the University of Hagen specialises in the area of planar-integrated free-space optics (PIFSO) [1.85]-[1.92].

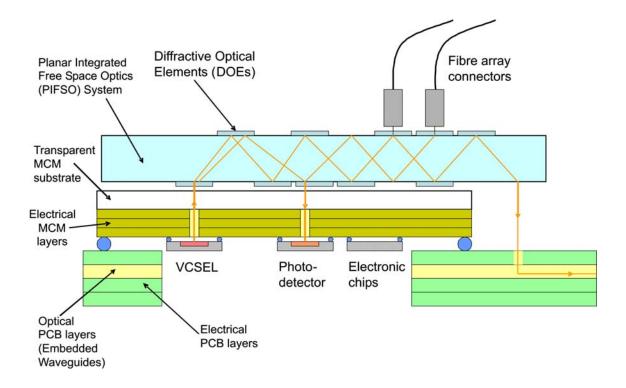

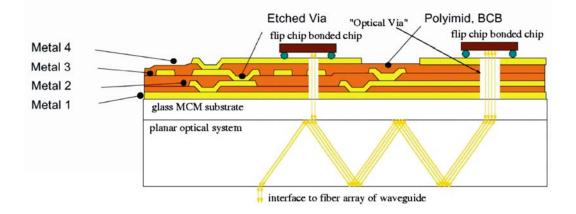

A system developed using PIFSO technology is composed of diffractive optical elements (DOEs), which are etched into the surface of a glass substrate. The diffractive optical systems are capable of carrying out complex routing functions. Also, optoelectronic devices, for example, vertical cavity surface emitting lasers (VCSELs) and Photodetectors (PDs) are bonded onto the substrate by using hybrid integration techniques such as flip-chip bonding. Light propagation takes place inside the substrate along a crisscross path. The substrate, which is usually several millimetres thick, functions both as a medium for light propagation as well as a board onto which other devices can be mounted.

#### 1.6.7 Optical Interconnects Group - Vrije Universiteit Brussel (VUB)

The Optical Interconnects Group led by Professor Hugo Thienpont at Vrije Universiteit Brussel have investigated using parallel optical fibre connections at the inter-board level where their focus was on the fabrication of 2D fibre array configurations [1.93]-[1.96]. Also, work has been done looking into the integration of optical waveguides into Printed Circuit Boards (PCB). This specifically studied the efficiency of coupling and redistribution of light from optoelectronic devices to layers of optical waveguides [1.97]-[1.100]. Other research has worked on the fabrication of very short-distance free-space micro-optical interconnection modules for intra-chip and intra- multi-chip module (MCM) interconnects. This focussed on the packaging, the scalability and the potential to reconfigure the interconnect topology [1.5], [1.101], [1.102].

#### 1.6.8 Summary

Numerous groups, from industry and academia have been investigating optical interconnects as an alternative for electrical interconnects in the near future. There are many challenges remaining for these systems to achieve the marketplace.

The work conducted so far has highlighted the advantages and disadvantages of different designs from optical system level, to optoelectronic devices and CMOS circuits.

#### 1.7 High Speed Optoelectronic Memory Systems (HOLMS) Project

#### 1.7.1 Introduction

The high speed optoelectronic memory system (HOLMS) project [1.73], [1.103] investigated the potential of optical interconnects to reduce memory latency within multiprocessor computer systems. This was conducted using optoelectronics and associated packaging technologies, which will be discussed in the following sections.

This project was funded by the European Commission Framework 5 IST (Information Society Technologies) programme [1.104]. Table 1 provides details of the project participants in the HOLMS consortium.

| Name                                                | Abbreviated<br>Name | Country        | Main Role(s)                                                                                         |

|-----------------------------------------------------|---------------------|----------------|------------------------------------------------------------------------------------------------------|

| Heriot-Watt<br>University                           | HWU                 | United-Kingdom | Project<br>Coordination,<br>Optoelectronics,<br>Bonding                                              |

| Swiss Federal<br>Institute of<br>Technology, Zurich | ETHZ                | Switzerland    | Technical<br>Coordination,<br>Architecture,<br>Memory Protocol,<br>Multi Chip Module<br>(MCM) Layout |

| University of Hagen                                 | Hagen               | Germany        | Planar Integrated<br>Free Space Optics<br>(PIFSO)                                                    |

| Siemens Business<br>Services GmbH &<br>Co, OHG      | SIEMENS             | Germany        | Project<br>Coordination,<br>Waveguides                                                               |

| Universitaet<br>Gesamthochschule<br>Paderborn       | Uni PB              | Germany        | Waveguides                                                                                           |

| ILFA GmbH                                           | ILFA                | Germany        | PCB design and manufacture                                                                           |

| École supérieure<br>d'électricité                   | Supélec             | France         | Mixed Signal Chip<br>(MSC)                                                                           |

| THALES<br>Communications                            | TCFR                | France         | Application,<br>Software                                                                             |

**Table 1) HOLMS Project Participants**

The theory work was achieved under Engineering and Physical Sciences Research Council (EPSRC) funding through the Analysis and Modelling of Optical Systems (AMOS) [1.64], [1.65] and Scottish Collaborative Initiative in Optical Sciences (SCIOS) projects [1.60]. And, through EC funding with the SPOEC project [1.63]. Within the HOLMS project, this knowledge was consolidated at a time when the technology was developed to a level where commercial use could be predicted.

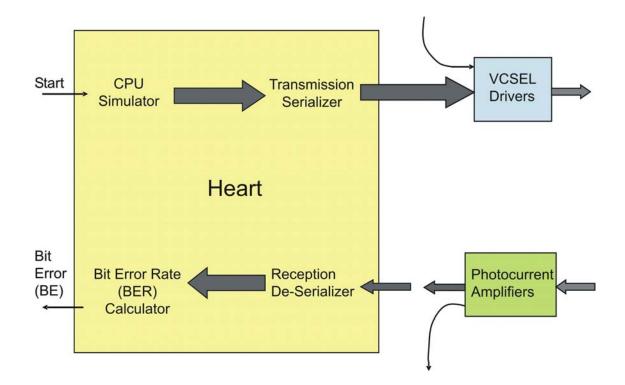

#### 1.7.2 Overview of Project

The project's aim was to construct a four central processing unit (CPU) shared memory multiprocessor with a low latency, optoelectronic memory interconnection [1.105]. The interconnection was based on a combination of waveguide, fibre and free-space optics, which augmented the electronic memory and processor components. This was integrated with conventional electronic assembly through a novel optoelectronic MCM (OE-MCM) packaging technology. The project started in March 2002 and was successfully completed in December 2005 [1.106].

The three main technologies developed in this project were:

- The Planar Integrated Free Space Optics (PIFSO) [1.107]-[1.115]. This work was developed by the Optical Information Technology (ONT) Group [1.58] at University of Hagen. An overview of this system was described earlier in this chapter.

- Optical waveguides integrated in conventional PCBs [1.116]-[1.121]. This work was developed by the Optical Interconnection Technology (OIT) Group [1.57] at C-Lab.

- Multi-Chip Modules (MCM) [1.122]-[1.127]. This was developed by the Computer Architecture Group (CAG) [1.128] at the Swiss Federal Institute of Technology in Zurich (ETHZ).

Figure 2 shows the coupling between the PIFSO, OE-MCM and PCB (optical and electrical layers).

Figure 2) Schematic showing coupling between PIFSO, OE-MCM and PCB

In the HOLMS project, the role of the OIC Group at HWU [1.129]-[1.132] was firstly to design, identify and source suitable optoelectronic devices. And secondly, to integrate these optoelectronic components onto the MCMs using appropriate packaging techniques.

#### 1.8 Thesis Overview

My PhD research involved working on the HOLMS project from October 2003 to its successful completion in December 2005. This thesis studies optoelectronic devices and the integration of these components onto OE-MCMs using a combination of bonding techniques. The thesis layout is described as follows:

#### **1.9** Chapter 2: Receiver Devices – Photodetector (PD) Arrays

This chapter explains details of the background, specifications and design of the receiver devices which were used. Also, characterisation experiments of two types of detectors (Type A and Type B devices) are described.

#### 1.10 Chapter 3: Transmitter Devices and Mixed Signal Chips (MSCs)

This chapter describes details of the background, specifications, and design of the transmitter devices which were used. Characterisation experiments performed on these devices are explained. Also, details of the mixed signal chips (MSCs) used to drive the transmitter devices and amplify the receiver devices are given.

#### 1.11 Chapter 4: Optoelectronic Packaging (I)

This chapter discusses the background of flip chip bonding technologies. Using these techniques, an explanation of the experiments conducted in packaging the components described in chapter 2 and chapter 3 is given.

#### 1.12 Chapter 5: Optoelectronic Packaging (II)

This chapter describes the fully integrated optoelectronic multi-chip module (OE-MCM) developed for my research work. Experimental work conducted on packaging and testing the OE-MCMs is explained.

#### **1.13** Chapter 6: Conclusions

Finally, chapter 6 draws conclusions from the work presented in chapters 2, 3, 4 and 5 and suggests possible future work in the area.

#### 1.14 References

- [1.1] Semiconductor Industry Association, "International Technology Roadmap for Semiconductors," (http://www.itrs.net/Links/2003ITRS/Home2003.htm).

- [1.2] D. A. B. Miller, "Optical interconnects to silicon," IEEE Journal of Selected Topics in Quantum Electronics, Vol. 6, pp. 1312-17, 2000.

- [1.3] J. W. Goodman, F. J. Leonberger, S. Y. Kung, R. A. Athale, "Optical interconnections for VLSI systems," Proceedings of the IEEE, Vol. 72, pp. 850-66, 1984.

- [1.4] A. V. Krishnamoorthy, D. A. B. Miller, "Firehose architectures for free-space optically interconnected VLSI circuits," Journal of Parallel and Distributed Computing, Vol. 41, pp. 109-14, 1997.

- [1.5] H. Thienpont, C. Debaes, V. Baukens, H. Ottevaere, P. Vynck, P. Tuteleers, G. Verschaffelt, B. Volckaerts, A. Hermanne, M. Hanney, "Plastic microoptical interconnection modules for parallel free-space inter- and intra-MCM data communication," Proceedings of the IEEE, Vol. 88, pp. 769-779, June 2000.

- X. Z. Zheng, P. J. Marchand, D. W. Huang, S. C. Esener, "Free-space parallel multichip interconnection system," Applied Optics, Vol. 39, pp. 3516-24, 2000.

- G. Q. Li, D. W. Huang, E. Yuceturk, P. J. Marchand, S. C. Esener, V. H.

Ozguz, Y. Liu, "Three-dimensional optoelectronic stacked processor by use of free-space optical interconnection and three-dimensional VLSI chip stacks," Applied Optics, Vol. 41, pp. 348-360, 2002.

- C. Debaes, M. Vervaeke, V. Baukens, H. Ottevaere, P. Vynck, P. Tuteleers, B. Volckaerts, W. Meeus, M. Brunfaut, J. Van Campenhout, A. Hermanne, H. Thienpont, "Low-cost microoptical modules for MCM level optical interconnections," IEEE Journal of Selected Topics in Quantum Electronics, Vol. 9, pp. 518-30, 2003.

- [1.9] N. M. Jokerst, M. A. Brooke, S. Y. Cho, S. Wilkinson, M. Vrazel, S. Fike, J. Tabler, Y. J. Joo, S. W. Seo, D. S. Wills, A. Brown, "The heterogeneous integration of optical interconnections into integrated microsystems," IEEE Journal of Selected Topics in Quantum Electronics, Vol. 9, pp. 350-60, 2003.

- [1.10] S. K. Lohokare, D. W. Prather, J. A. Cox, P. E. Sims, M. G. Mauk, O. V. Sulima, "Integrated optoelectronic transmitter and receiver multi-chip modules

for three-dimensional chip-level micro-optical interconnects," Optical Engineering, Vol. 42, pp. 2683-2688, 2003.

- [1.11] M. Gruber, "Multi-chip module with planar-integrated free-space optical vector matrix-type interconnects," Applied Optics, Vol. 43, pp. 463-70, 2004.

- [1.12] M. Gruber, R. Kerssenfischer, J. Jahns, "Planar-integrated free-space optical fan-out module for MT-connected fiber ribbons," Journal of Lightwave Technology, Vol. 22, pp. 2218-22, 2004.

- [1.13] J. D. Meindl, "Interconnect opportunities for gigascale integration," IEEE Micro, Vol. 23, pp. 28-35, 2003.

- [1.14] R. H. Havemann, J. A. Hutchby, "High-performance interconnects: an integration overview," Proceedings of the IEEE, Vol. 89, pp. 586-601, 2001.

- [1.15] D. A. B. Miller, "Physical reasons for optical interconnection," International Journal of Optoelectronics, Vol. 11, pp. 155-68, 1997.

- [1.16] D. A. B. Miller, "Rationale and challenges for optical interconnects to electronic chips," Proceedings of the IEEE, Vol. 88, pp. 728-49, 2000.

- [1.17] A. L. Schawlow, C. H. Townes, "Infrared and Optical Masers," Phys. Rev., Vol. 112 (6), pp. 1940-1949, December 1958.

- [1.18] R. N. Hall, G. E. Fenner, J. D. Kingsley, T. J. Soltys, R. O. Carlson, "Coherent Light Emission From GaAs Junctions," Phys. Rev. Lett., Vol. 9 (9), pp. 366-368, November 1962.

- [1.19] N. Holonyak Jr., S. F. Bevacqua, "Coherent (Visible) Light Emission From Ga(As1-xPx) Junctions," Appl. Phys. Lett., Vol. 1 (4), pp. 82-83, December 1962.

- [1.20] M. I. Nathan, W. P. Dumke, G. Burns, F. H. Dill Jr., G. Lasher, "Stimulated Emission of Radiation From GaAs p-n Junctions," Appl. Phys. Lett., Vol. 1 (3), pp. 62-64, November 1962.

- T. M. Quist, R. H. Rediker, R. J. Keyes, W. E. Krag, B. Lax, A. L. McWhorter, H. J. Zeiger, "Semiconductor Maser of GaAs," Appl. Phys. Lett., Vol. 1, (4), pp. 91-92, December 1962.

- P. Kaiser, "Trends and Opportunities for Photonics in Communications," Tech.

Digest, 4<sup>th</sup> Int. Topical Workshop on Contemporary Photonic Technologies, CPT2001, Tokyo, (2001).

- [1.23] G. E. Moore, "Cramming More Components onto Integrated Circuits," Proceedings of the IEEE, Vol. 86 (1), pp. 82-85, January 1998.

- [1.24] Intel, (http://www.intel.com/).

- [1.25] G. E. Moore, "Progress in Digital Integrated Electronics," IEEE, IEDM Tech Digest pp. 11-13, 1975.

- [1.26] R. R. Schaller, "Moore's law: past, present and future," IEEE Spectrum, Vol. 34, (6), pp. 52-59, June 1997.

- [1.27] G. E. Moore, "Lithography and the Future of Moore's Law," Proc. SPIE, Vol. 2437, May 1995.

- [1.28] D. A. B. Miller, H. M. Özaktas, "Limit to the Bit-Rate Capacity of Electrical Interconnects from the Aspect Ratio of the System Architecture," Special Issue on Parallel Computing with Optical Interconnects, J. Parallel and Distributed Computing, Vol. 41, pp. 42-52, (1997).

- [1.29] M.W. Haney, M.P. Christensen, "Fundamental Geometric Advantages of Free-Space Optical Interconnects," Proceedings of the Third International Conference on Massively Parallel Processing Using Optical Interconnections, pp. 16–23, 1996.

- [1.30] Terahertz Photonics Ltd, (http://business.scotsman.com/6983/Terahertz-islooking-good-for.2254826.jp).

- [1.31] Luxtera, (http://www.luxtera.com/).

- [1.32] "Optical Technologies and Applications," Intel Technology Journal, Vol. 8 (2), May 2004.

- [1.33] I. A. Young, et al., "Optical Interconnect System Integration for Ultra-Short-Reach Applications," Optical Technologies and Applications, Intel Technology Journal, Vol. 8 (2), pp. 115-127, May 2004.

- [1.34] I. A. Young, et al., "On-Chip Optical Interconnects," Optical Technologies and Applications, Intel Technology Journal, Vol. 8 (2), pp. 129-141, May 2004.

- [1.35] M. Paniccia, et al., "Silicon Photonics," Optical Technologies and Applications, Intel Technology Journal, Vol. 8 (2), pp. 143-160, May 2004.

- [1.36] A. Liu, R. Jones, L. Liao, D. Samara-Rubio, D. Rubin, O. Cohen, R.

Nicolaescu, M. Paniccia, "A high-speed silicon optical modulator based on a metal-oxide-semiconductor capacitor," *Nature*, Vol. 427, pp. 615-618, February 2004.

- [1.37] M. Paniccia, V. Krutul, S. Koehl, "Introducing Intel's Advances in Silicon Photonics," Research and Development at Intel, White Paper, February 2004.

- M. Paniccia, V. Krutul, S. Koehl, "Intel Unveils Silicon Photonics Breakthrough: High-Speed Silicon Modulation," Technology@Intel Magazine, February 2004.

- [1.39] H. Rong, R. Jones, A. Liu, O. Cohen, D. Hak, A. Fang, M. Paniccia, "A Continuous-Wave Raman Silicon Laser," Nature, Vol. 433, pp. 725-728,17 Feb 2005.

- [1.40] S. Koehl, V. Krutul, M. Paniccia, "Continuous Silicon Laser," Intel White Paper, February 2005.

- [1.41] M. J. Pelletier, "Analytical applications of Raman spectroscopy," Blackwell Science, 1999.

- [1.42] J. R. Ferraro, K. Nakamoto, "Introductory Raman spectroscopy," Academic Press Inc, 1994.

- [1.43] Optoelectronics Research Group, University of California, Santa Barbara, (http://www.ece.ucsb.edu/uoeg/publications/).

- [1.44] M. Paniccia, et al., "A Hybrid Silicon Laser," Research at Intel, White Paper, September 2006.

- [1.45] A. W. Fang, H. Park, R. Jones, O. Cohen, M. Paniccia, J. E. Bowers, "A Continuous Wave Hybrid AlGaInAs-Silicon Evanescent Laser," IEEE Photonics Technology Letters, Vol. 18, pp.1143-1145, 2006.

- [1.46] Helia Photonics, (http://www.helia-photonics.com/).

- [1.47] P. Duran, Luxtera CMOS Photonics Technology, "Blazar 40Gbps Optical Active Cable," White Paper, pp. 10-11, July 2008.

- [1.48] Optically Interconnected Computing (OIC) Group, (http://oic.eps.hw.ac.uk/).

- [1.49] X. Z. Zheng, P. J. Marchand, D. W. Huang, S. C. Esener, "Free-space parallel multichip interconnection system," Applied Optics, Vol. 39, pp. 3516-24, 2000.

- [1.50] N. M. Jokerst, M. A. Brooke, S. Y. Cho, S. Wilkinson, M. Vrazel, S. Fike, J. Tabler, Y. J. Joo, S. W. Seo, D. S. Wills, A. Brown, "The heterogeneous integration of optical interconnections into integrated microsystems," IEEE Journal of Selected Topics in Quantum Electronics, Vol. 9, pp. 350-60, 2003.

- [1.51] S. K. Lohokare, D. W. Prather, J. A. Cox, P. E. Sims, M. G. Mauk, O. V. Sulima, "Integrated optoelectronic transmitter and receiver multi-chip modules for three-dimensional chip-level micro-optical interconnects," Optical Engineering, Vol. 42, pp. 2683-2688, 2003.

- [1.52] M. S. Bakir, T. K. Gaylord, O. O. Ogunsola, E. N. Glytsis, J. D. Meindl,

"Optical transmission of polymer pillars for chip I/O optical interconnections,"

IEEE Photonics Technology Letters, Vol. 16, pp. 117-19, 2004.

- [1.53] G. Q. Li, D. W. Huang, E. Yuceturk, P. J. Marchand, S. C. Esener, V. H. Ozguz, Y. Liu, "Three-dimensional optoelectronic stacked processor by use of free space optical interconnection and three-dimensional VLSI chip stacks," Applied Optics, Vol. 41, pp. 348-360, 2002.

- [1.54] Miller Group, Stanford Photonics Research Center, Stanford University, (http://www.stanford.edu/group/dabmgroup/).

- [1.55] OptoElectronic Computing Group (OECG), (http://soliton.ucsd.edu/).

- [1.56] Optoelectronics Technology Center (OTC), (http://www.ece.ucsb.edu/Faculty/Coldren/OTC/OTC.htm).

- [1.57] Optical Interconnection Technology group, C-LAB, (http://www.clab.de/en/operation-fields/computing/optical-interconnectiontechnology/index.html).

- [1.58] Optical Information Technology (ONT) Group, (http://www.fernunihagen.de/ONT/).

- [1.59] Applied Physics and Photonics Department, Vrije Universiteit Brussel (VUB), (http://tona.vub.ac.be/Tona/).

- [1.60] A. C. Walker, T. Yang, J. Gourlay, J. A. B. Dines, M. G. Forbes, S. M. Prince, D. A. Baillie, D. T. Neilson, R. Williams, L. C. Wilkinson, G. R. Smith, M. P. Y. Desmulliez, G. S. Buller, M. R. Taghizadeh, A. Waddie, I. Underwood, C. R. Stanley, F. Pottier, B. Vogele and W. Sibbett, "Optoelectronic Systems Based on InGaAs Complementary-Metal-Oxide-Semiconductor Smart-Pixel Arrays and Free-Space Optical Interconnects," Applied Optics, Vol. 37 (14), pp. 2822-2830, (1998).

- [1.61] D. T. Neilson, S. M. Prince, D. A. Baillie and F. A. P. Tooley, "Optical design of a 1024-channel free-space sorting demonstrator," Applied Optics, Vol. 36 (35), pp. 9243-9252, 10 December 1997.

- [1.62] A. C. Walker, M. P. Y. Desmulliez, M. G. Forbes, S. J. Fancey, G. S. Buller, M. R. Taghizadeh, J. A. B. Dines, C. R. Stanley, G. Pennelli, A. R. Boyd, P. Horan, D. Byrne, J. Hegarty, S. Eitel, H.-P. Gauggel, K.-H. Gulden, A. Gauthier, P. Benabes, J.-L. Gutzwiller and M. Goetz, "Design and Construction Of An Optoelectronic Crossbar Switch Containing A Terabit Per Second Free-Space Optical Interconnect," IEEE Journal of Selected Topics In Quantum Electronics, Vol.5 (2), pp. 236-249, March/ April 1999.

- [1.63] A. C. Walker, S. J. Fancey, M. P. Y. Desmulliez, et al., "Operation of an optoelectronic crossbar switch containing a terabit-per-second free-space

optical interconnect," IEEE Journal of Quantum Electronics, Vol. 41, Issue 7, July 2005.

- [1.64] G. A. Russell "Analysis and Modelling of Optically Interconnected Computing Systems," PhD thesis, Heriot-Watt University, Edinburgh, UK, July 2004.

- [1.65] K. J. Symington, G. A. Russell, T. Lim and J. F. Snowdon, "Analysis and Modelling of Optical Systems," School of Engineering and Physical Sciences, Heriot Watt University, Edinburgh, UK, February 2003.

- [1.66] R. P. Webb, "Optoelectronic Implementation of Neural Networks,"International Journal of Neural Systems, Vol. 4, pp. 435-4444, December 1993.

- [1.67] R. P. Webb, A. J. Waddie, K. J. Symington, M. R. Taghizadeh and J.F.Snowdon, "An Optoelectronic Neural Network Scheduler for Packet Switches," Appl. Opt., Vol. 39 (5), pp. 788-795, February 2000.

- [1.68] K. J. Symington, "Optoelectronic Neural Networks for Switching," M.Sc Dissertation, Heriot-Watt University, September 1998.

- [1.69] A. Fritze, "Integration of optoelectronic devices, electronic circuitry and optical waveguides", PhD thesis, Heriot-Watt University, 2002.

- [1.70] A. McCarthy, "Free-space and Polymer Waveguided Optical Interconnects for the Integration and Packaging of Optoelectronic Devices", PhD thesis, Heriot-Watt University, 2001.

- [1.71] G.A. Russell, K.J. Symington, R. Raheem and J.F. Snowdon, "Reconfigurable Optics for Reconfigurable Computing," Proceedings, Optics in Computing 2004 (OIC2004), Engelberg, Switzerland, ISBN: 3-00-013069-1, April 2004.

- [1.72] G.A. Russell, C.J. Moir and J.F. Snowdon, "Modelling an Optically Interconnected FPGA for Reconfigurable Computing Architectures," Proceedings, Photonics Europe 2006, Strasbourg, France, April 2006.

- [1.73] P. Lukowicz, J. Jahns, R. Barbieri, et al., "Optoelectronic interconnection technology in the HOLMS system," IEEE Journal of Selected Topics in Quantum Electronics, Vol. 9 (2), March-April 2003.

- [1.74] List of Journal Publications by Professor David Miller, Stanford Photonics Research Center, Stanford University, (http://ee.stanford.edu/~dabm/publications.html).

- [1.75] List of Journal Publications, Conference Proceedings and Theses by the Miller Group, Stanford Photonics Research Center, Stanford University, (http://www.stanford.edu/group/dabmgroup/publications.html#journals).

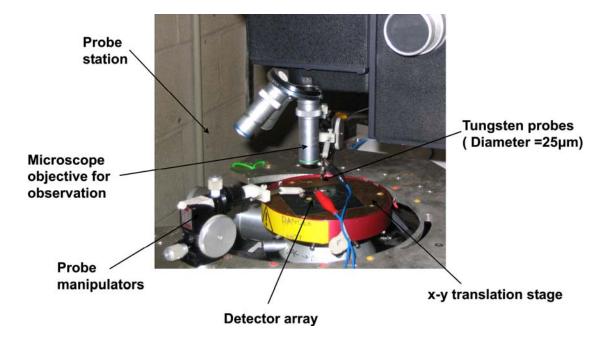

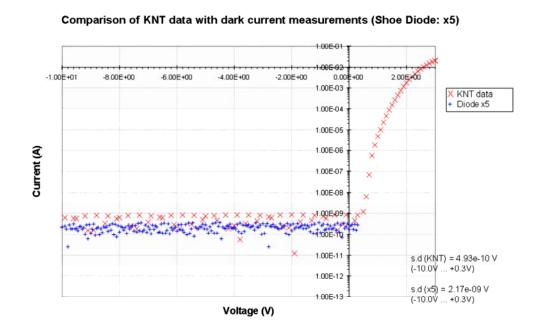

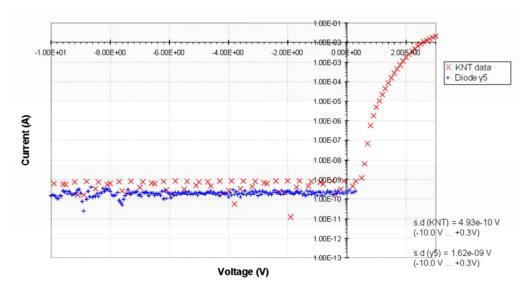

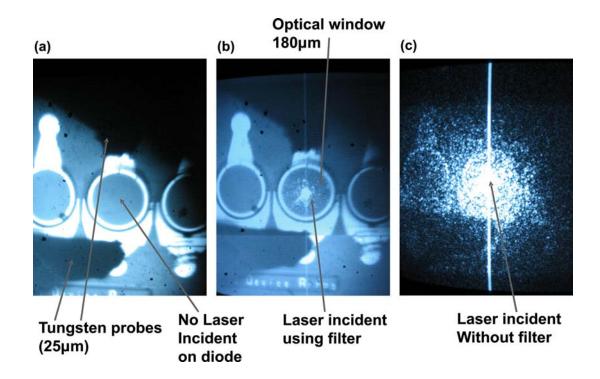

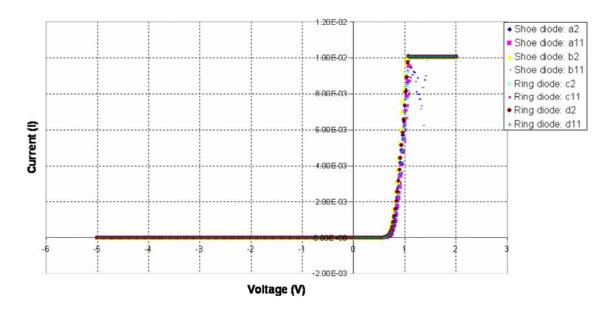

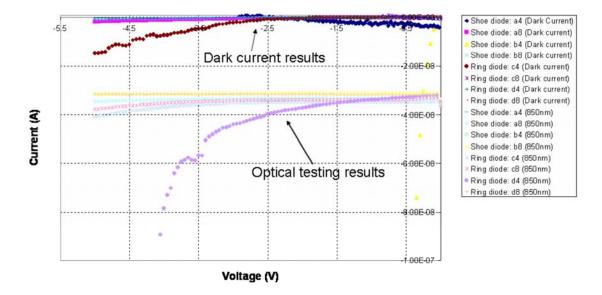

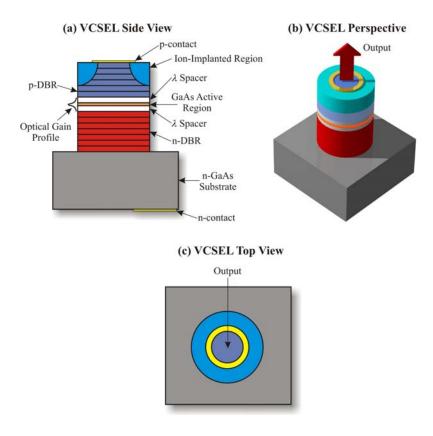

- [1.76] DARPA, (http://www.darpa.mil/).