Characterisation of a Reconfigurable Free Space Optical Interconnect

System for Parallel Computing Applications and Experimental Validation

Using Rapid Prototyping Technology

#### Rafael Gil Otero

Submitted for the degree of Doctor of Philosophy

Heriot-Watt University

Department of Physics

February 2008

This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that the copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author or of the University (as may be appropriate).

#### **ABSTRACT**

Free-space optical interconnects (FSOIs) are widely seen as a potential solution to present and future bandwidth bottlenecks for parallel processing applications.

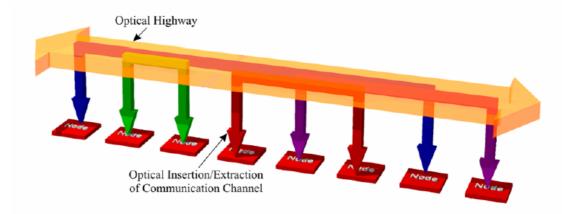

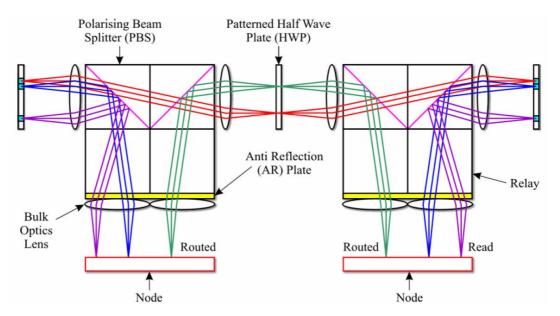

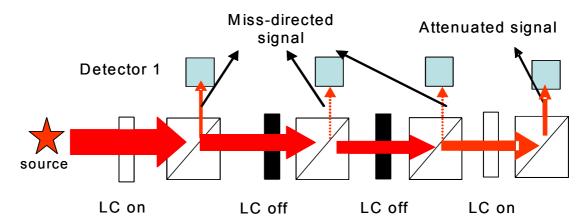

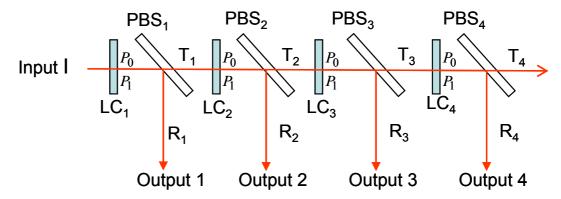

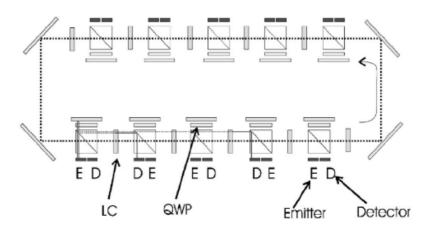

This thesis will be focused on the study of a particular FSOI system called Optical Highway (OH). The OH is a polarised beam routing system which uses Polarising Beam Splitters and Liquid Crystals (PBS/LC) assemblies to perform reconfigurable interconnection networks. The properties of the OH make it suitable for implementing different passive static networks.

A technology known as Rapid Prototyping (RP) will be employed for the first time in order to create optomechanical structures at low cost and low production times. Off-the-shelf optical components will also be characterised in order to implement the OH. Additionally, properties such as reconfigurability, scalability, tolerance to misalignment and polarisation losses will be analysed. The OH will be modelled at three levels: node, optical stage and architecture. Different designs will be proposed and a particular architecture, Optimised Cut-Through Ring (OCTR), will be experimentally implemented. Finally, based on this architecture, a new set of properties will be defined in order to optimise the efficiency of the optical channels.

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor, John Snowdon for giving me the freedom to conduct my research, allowing me to be creative and at the same time offer the necessary support and guidance. I also feel very fortunate to have had the chance to work with and learn from Dr. Theodore Lim from the Mechanical Department. Many thanks to everyone in the OIC group for all their help, especially Spyros, who has helped me a lot with the submission of the thesis and many other occasions.

Special thanks to my parents, my brother and my grandma, whose constant support has been essential.

I would also like to mention some of the friends I have made during these years: Nic, Gonzalo, Abid, Carmen, Sarah, Helen, Luis my partners at lunchtime; Patri, Lucia, Ivona, Kevin, Robert, Gerard, Pablo, and my best friends in Edinburgh Vero, Daniel and Manu.

And last, but by no means least, I thank my girlfriend, Idoya, for putting up with me and for her constant support.

## **ACADEMIC REGISTRY**

1.2E-thesis Submitted

Signature:

| Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Rafael Gil Otero                            |   |          |         |     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---|----------|---------|-----|--|

| School/PGI:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | School of Engineering and Physical Sciences |   |          |         |     |  |

| Version: (i.e. First, Resubmission, Final)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Final                                       |   | Degree S | Sought: | PhD |  |

| <u>Declaration</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |   |          |         |     |  |

| <ol> <li>In accordance with the appropriate regulations I hereby submit my thesis and I declare that:</li> <li>the thesis embodies the results of my own work and has been composed by myself</li> <li>where appropriate, I have made acknowledgement of the work of others and have made reference to work carried out in collaboration with other persons</li> <li>the thesis is the correct version of the thesis for submission and is the same version as any electronic versions submitted*.</li> <li>my thesis for the award referred to, deposited in the Heriot-Watt University Library, should be made available for loan or photocopying and be available via the Institutional Repository, subject to such conditions as the Librarian may require</li> <li>I understand that as a student of the University I am required to abide by the Regulations of the University and to conform to its discipline.</li> </ol> * Please note that it is the responsibility of the candidate to ensure that the correct version of the thesis is submitted. |                                             |   |          |         |     |  |

| Signature of Candidate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             | * |          | Date:   |     |  |

| Submission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |   |          |         |     |  |

| Submitted By (name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e in capitals):                             |   |          |         |     |  |

| Signature of Individual Submitting:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |   |          |         |     |  |

| Date Submitted:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |   |          |         |     |  |

| For Completion in Academic Registry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |   |          |         |     |  |

| Received in the Academic Registry by (name in capitals):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |   |          |         |     |  |

| 1.1Method of Subm<br>(Handed in to Academi<br>through internal/external                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | c Registry; posted                          |   |          |         |     |  |

Date:

## TABLE OF CONTENTS

| Abstractiv                                                                                  |  |  |  |  |

|---------------------------------------------------------------------------------------------|--|--|--|--|

| Acknowledgmentsv                                                                            |  |  |  |  |

| Publications and Presentationsviii                                                          |  |  |  |  |

|                                                                                             |  |  |  |  |

| Chapter 1 – Introduction                                                                    |  |  |  |  |

| 1.1 Introduction and Thesis Outline                                                         |  |  |  |  |

| 1.2 Motivation                                                                              |  |  |  |  |

| 1.2.1 Electrical Interconnect Limitations3                                                  |  |  |  |  |

| 1.2.2 Influence of Electrical Interconnects on Memory Performance                           |  |  |  |  |

| 1.2.3 Influence of Electrical Interconnects on Processor Performance and the New            |  |  |  |  |

| Era of Parallel Processing9                                                                 |  |  |  |  |

| 1.3 Using Optics in Computers 12                                                            |  |  |  |  |

| 1.3.1 Optical Interconnects14                                                               |  |  |  |  |

| 1.4 Conclusion18                                                                            |  |  |  |  |

| References 19                                                                               |  |  |  |  |

|                                                                                             |  |  |  |  |

| <b>Chapter 2 – Free Space Optical Interconnects for Parallel Computer Applications . 21</b> |  |  |  |  |

| 2.1 Introduction                                                                            |  |  |  |  |

| 2.2 Free Space Optical Interconnect Networks and Current State-of-the-Art21                 |  |  |  |  |

| 2.2.1 Technology and Integration of Free Space Optical Interconnected Systems 23            |  |  |  |  |

| 2.2.2 Simulation Tools for Modelling Free Space Optical Networks                            |  |  |  |  |

| 2.2.3 Classification of Optical Networks28                                                  |  |  |  |  |

| 2.3 Optical Highway                                                                         |  |  |  |  |

| 2.3.1 Previous Work on the Optical Highway                                                  |  |  |  |  |

| 2.3.2 Improvements and Limitations of the Optical Highway                                   |  |  |  |  |

| 2.4 Conclusion                                                                              |  |  |  |  |

| References 37                                                                               |  |  |  |  |

|                                                                                             |  |  |  |  |

| Chapter 3 – Experimental Validation of the Optical Highway using Rapid                      |  |  |  |  |

| Prototyping Technique43                                                                     |  |  |  |  |

| 3.1 Introduction 43                                                                         |  |  |  |  |

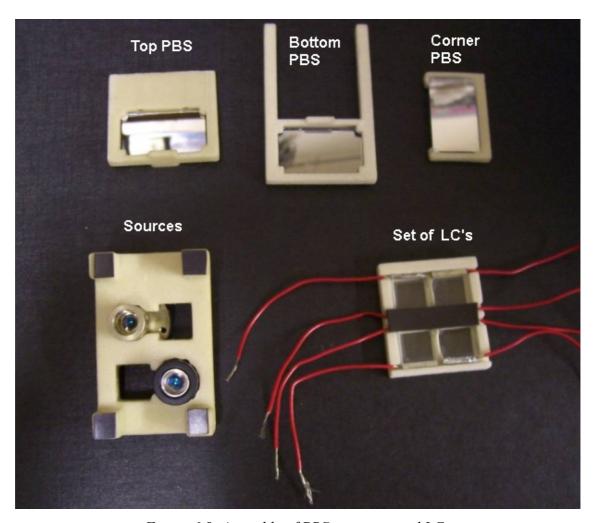

| 3.2 Optical Components used for Implementing an Optical Highway Demonstrator43              |  |  |  |  |

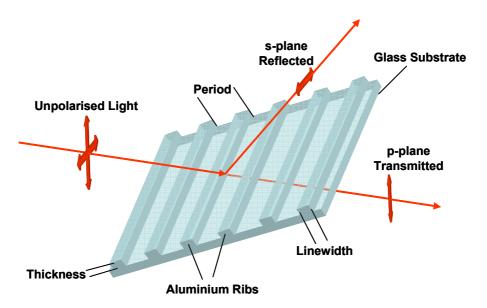

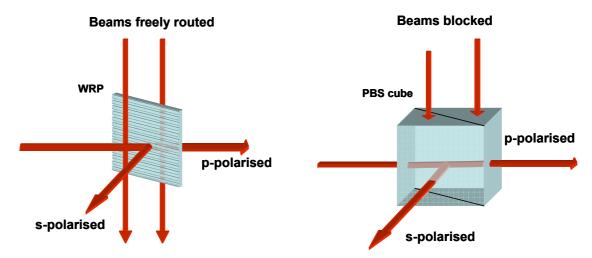

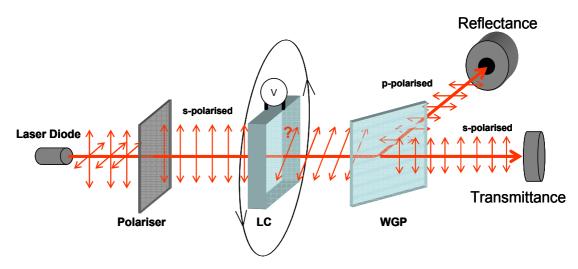

| 3.2.1 Description and Characterisation of Wire Grid Polarising Beam Splitter Plates 44      |  |  |  |  |

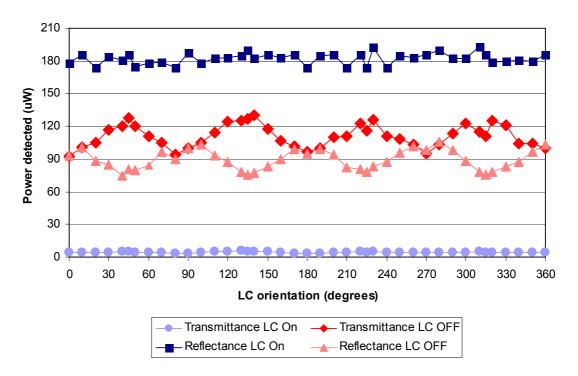

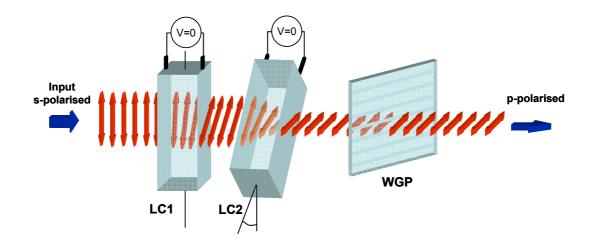

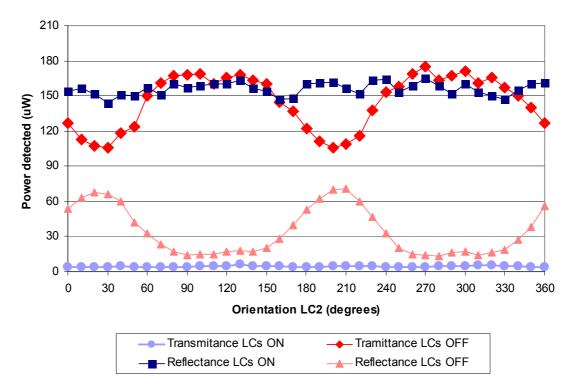

| 3.2.2 Liquid Crystal                                                          | 47  |  |  |

|-------------------------------------------------------------------------------|-----|--|--|

| 3.3 Rapid Prototyping                                                         | 51  |  |  |

| 3.4 Crosstalk-Attenuation Model                                               |     |  |  |

| 3.5 Conclusion                                                                | 64  |  |  |

| References                                                                    | 65  |  |  |

|                                                                               |     |  |  |

| Chapter 4 – Characterisation of a Reconfigurable Free Space Optical Channel   | 66  |  |  |

| 4.1 Introduction                                                              | 66  |  |  |

| 4.2 Characterisation of Optical Components and Signal Used                    | 67  |  |  |

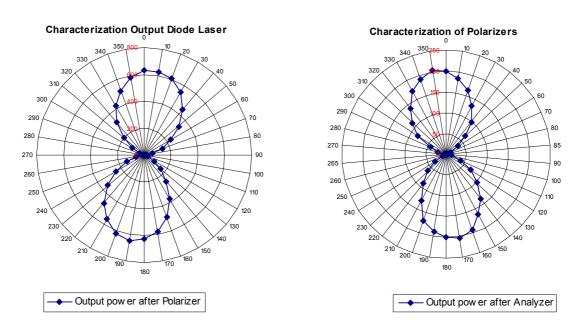

| 4.2.1 Polarisation Characteristics of Diode Laser and Polariser               | 67  |  |  |

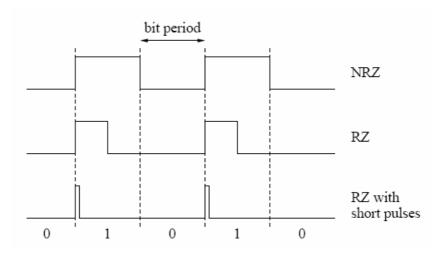

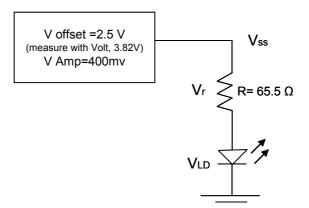

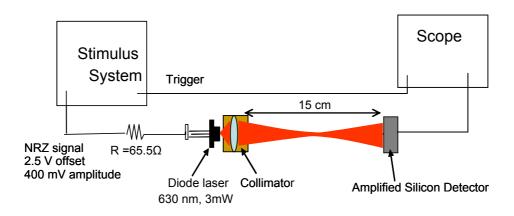

| 4.2.2 Characterisation of the Electrical Signal used to Drive the Laser Diode | 68  |  |  |

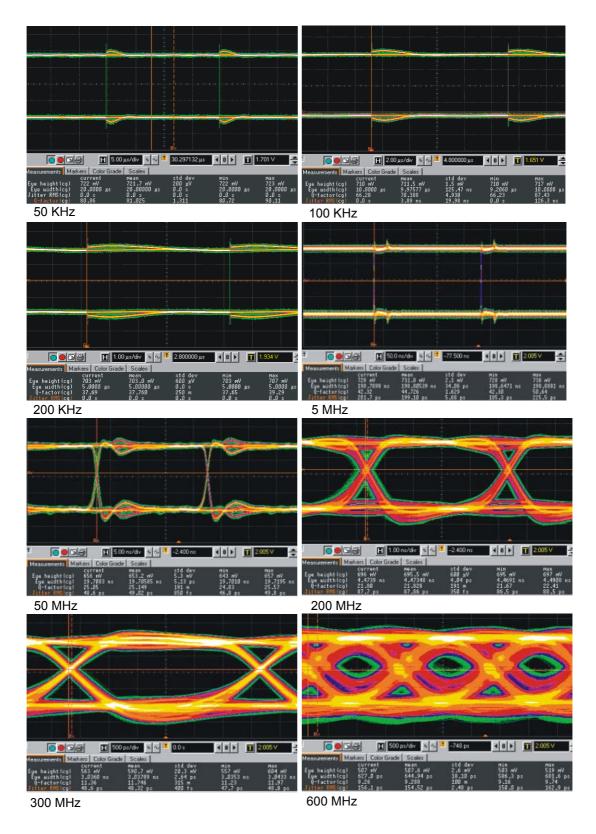

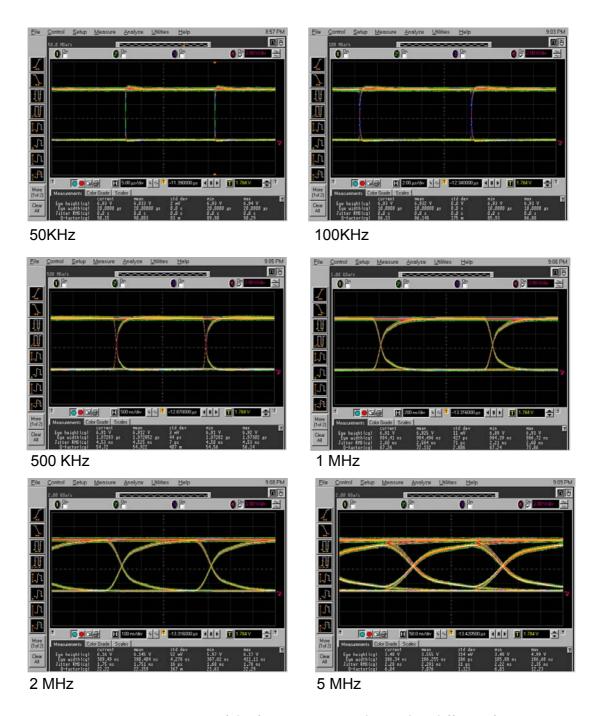

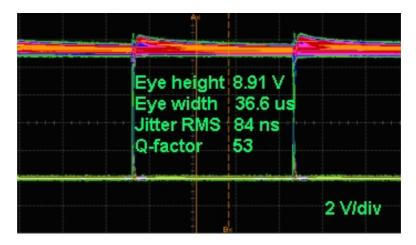

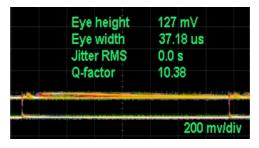

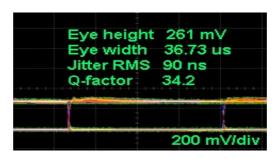

| 4.2.3 Eye Diagram of the Optical Signal                                       | 73  |  |  |

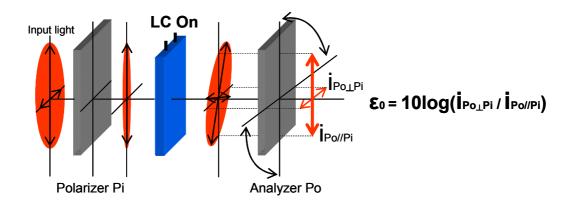

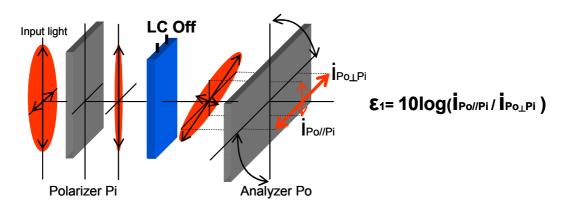

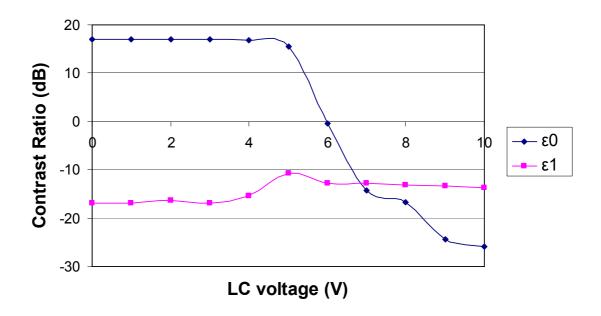

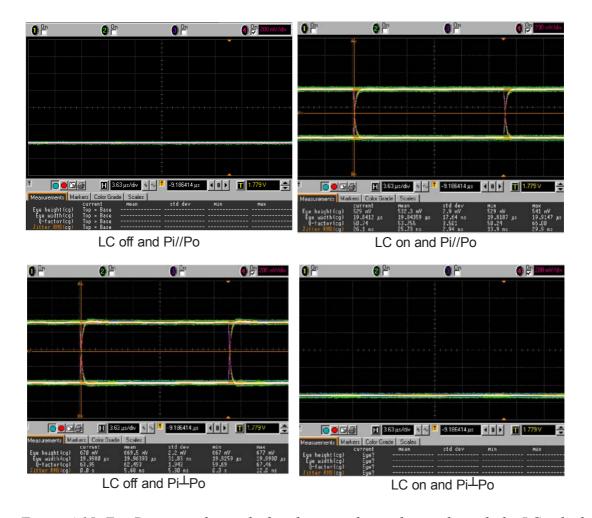

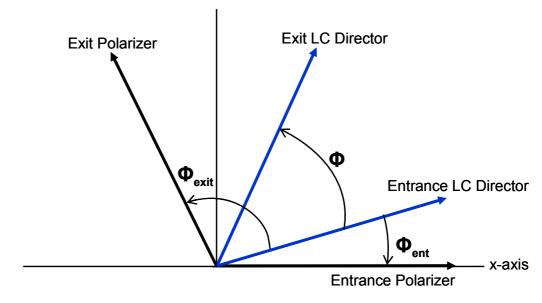

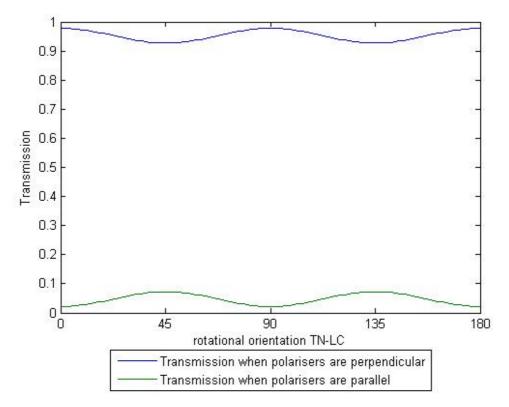

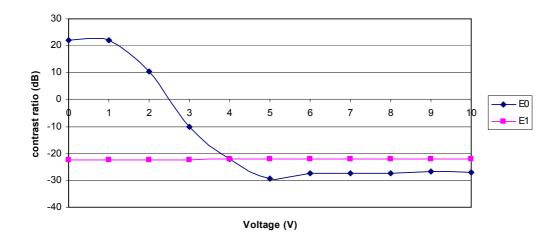

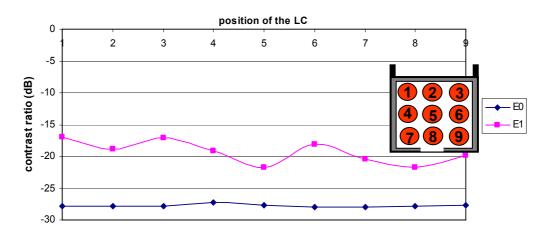

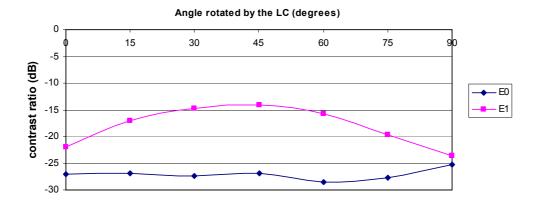

| 4.2.4 Characterisation of the 90° Twisted Nematic Liquid Crystal              | 76  |  |  |

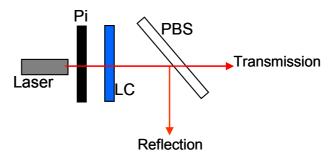

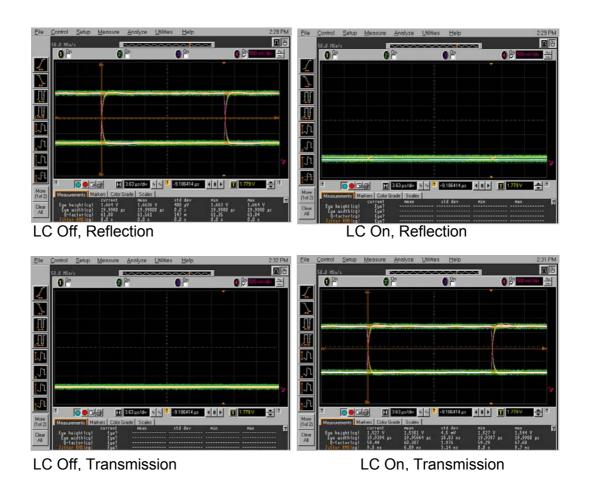

| 4.3 Eye Diagram Characterisation of One Stage of the Optical Highway          | 84  |  |  |

| 4.3.1 Tolerancing of Polarisation Losses in the Optical Highway               | 85  |  |  |

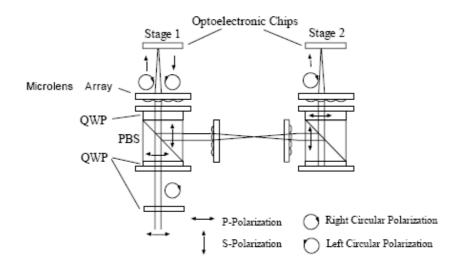

| 4.4 Characterisation of the Three Stage System                                | 91  |  |  |

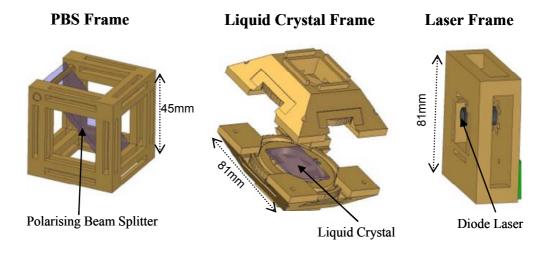

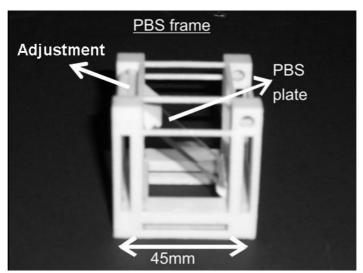

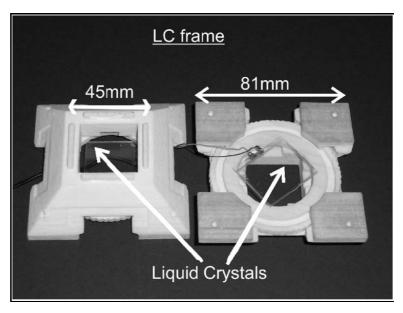

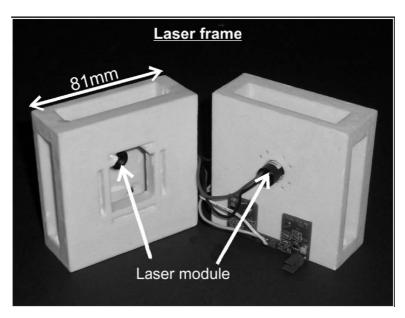

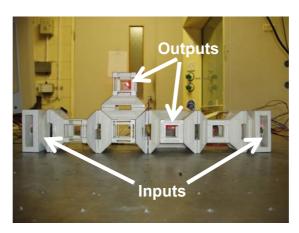

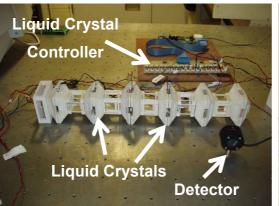

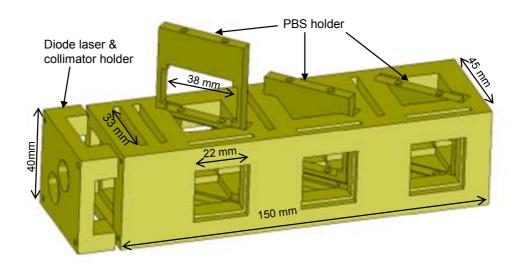

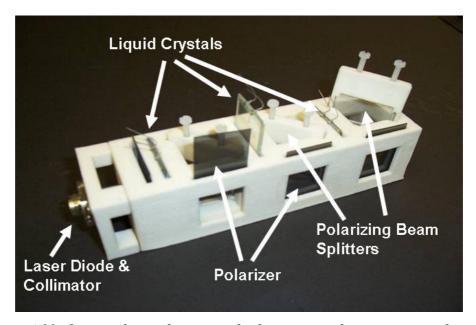

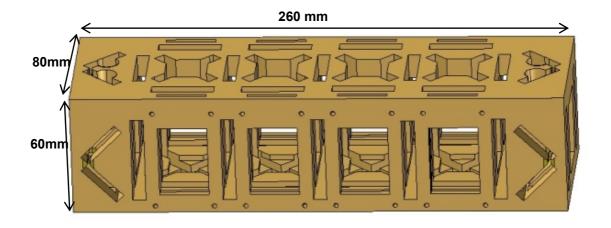

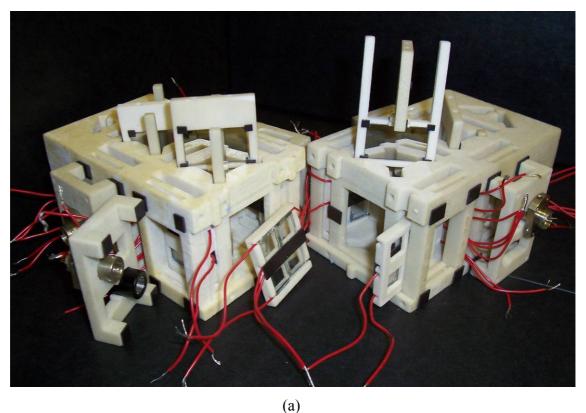

| 4.4.1 Design of the Mechanical Structure using Rapid Prototyping Technology   | 92  |  |  |

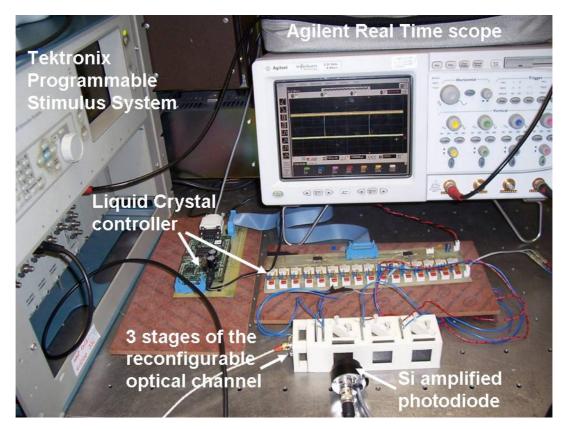

| 4.4.2 Experimental Setup                                                      | 94  |  |  |

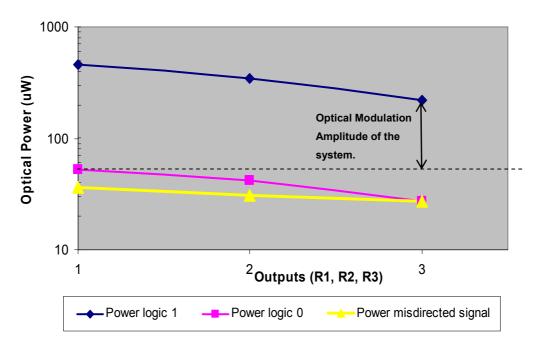

| 4.4.3 Three Stage System Characterisation                                     | 95  |  |  |

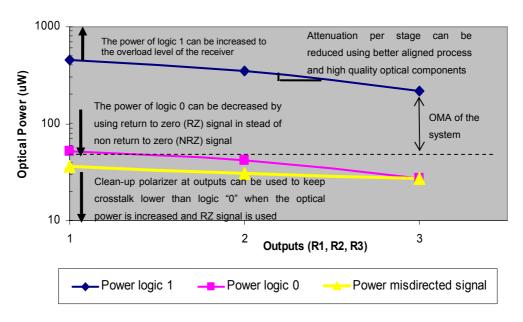

| 4.4.4 Increasing the Optical Quality in the System                            | 100 |  |  |

| 4.5 Conclusion                                                                | 102 |  |  |

| References                                                                    | 103 |  |  |

|                                                                               |     |  |  |

| Chapter 5 – Design of the Optical Highway at Different Levels                 | 104 |  |  |

| 5.1 Introduction                                                              | 104 |  |  |

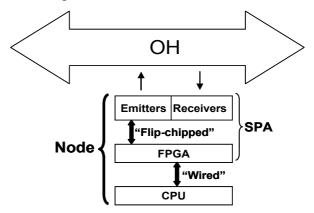

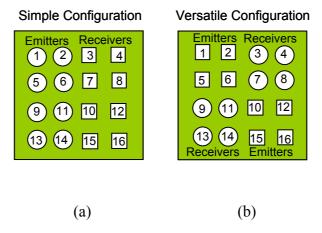

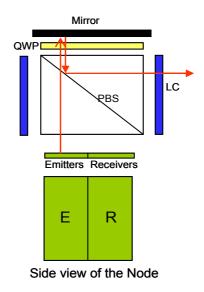

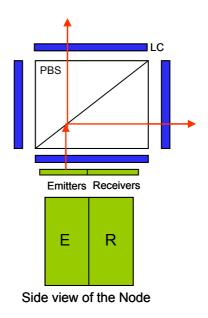

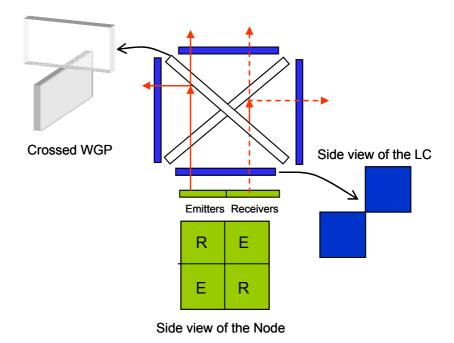

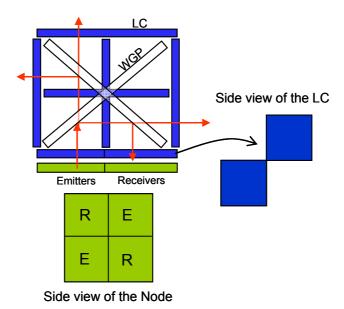

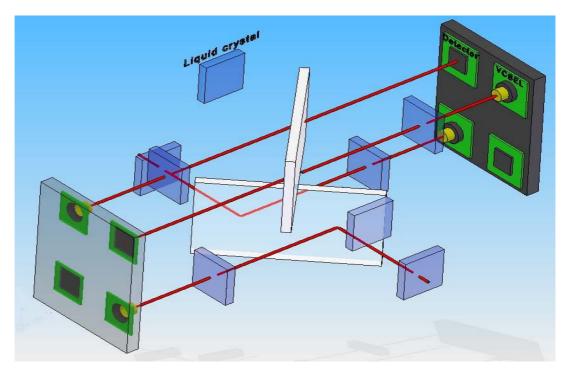

| 5.2 Design of a Node of the Optical Highway                                   | 105 |  |  |

| 5.2.1 Optical Requirements                                                    | 106 |  |  |

| 5.2.2 Design Requirements                                                     | 108 |  |  |

| 5.2.3 Mapping Emitters and Receivers on the Node                              | 109 |  |  |

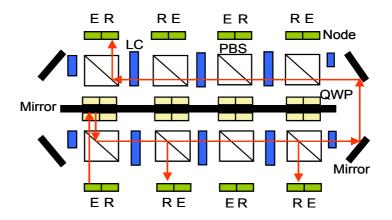

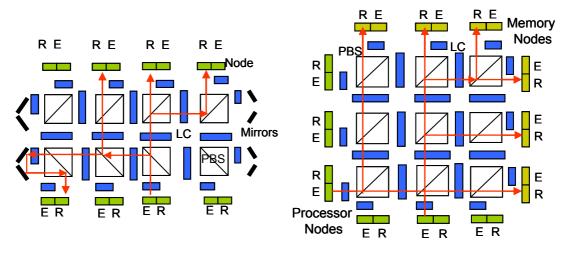

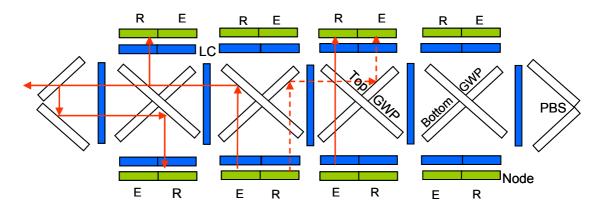

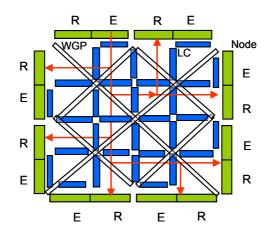

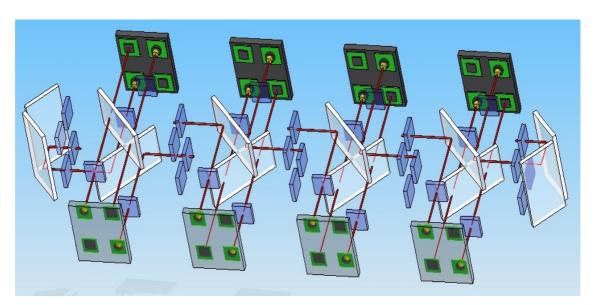

| 5.3 Design of Optical stage and Optical Highway Architectures                 | 111 |  |  |

| 5.3.1 Design Requirements                                                     | 111 |  |  |

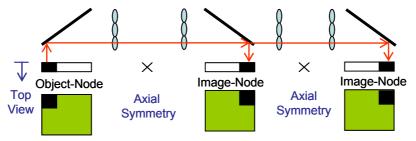

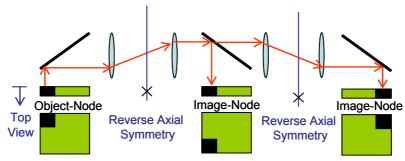

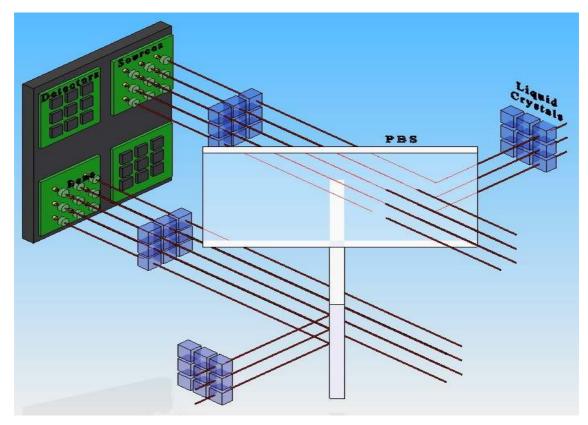

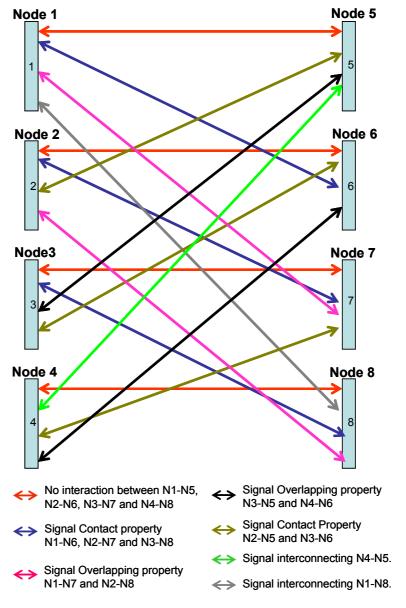

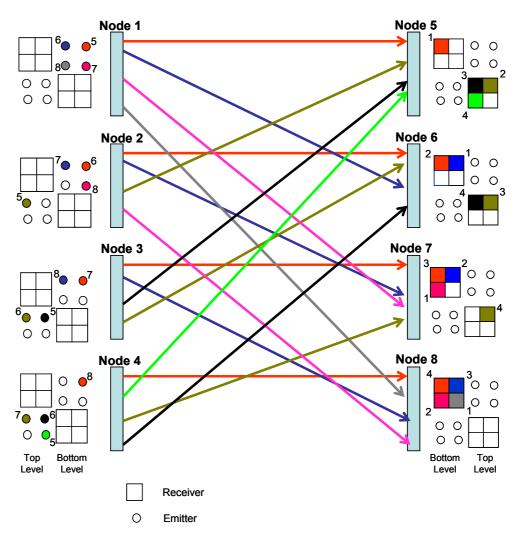

| 5.3.2 Design of the Optical Stage and Optical Highway Architectures           |     |  |  |

| 5.3.3 Performance of the Optical Highway Architectures                        | 119 |  |  |

| 5.4 Conclusion                                                                | 121 |  |  |

| References                                                                    | 122 |  |  |

| Chapter 6 – Experimental Implementation of an Optical Highway Architecture  | 123 |

|-----------------------------------------------------------------------------|-----|

| 6.1 Introduction                                                            | 123 |

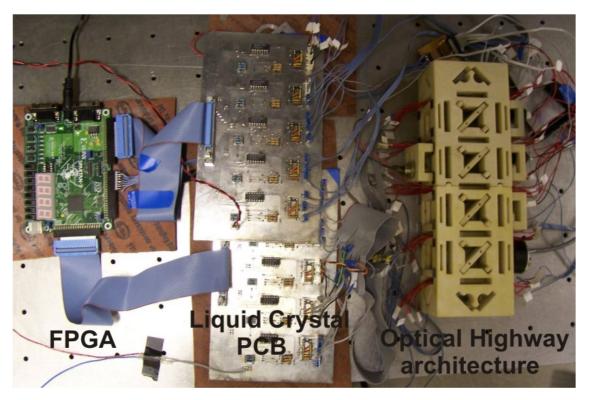

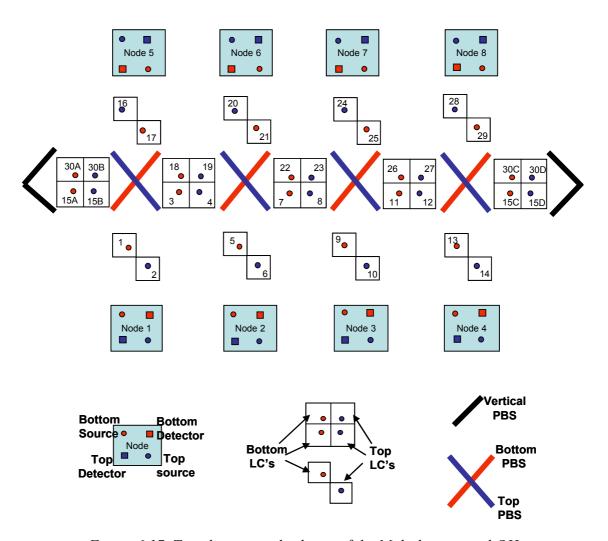

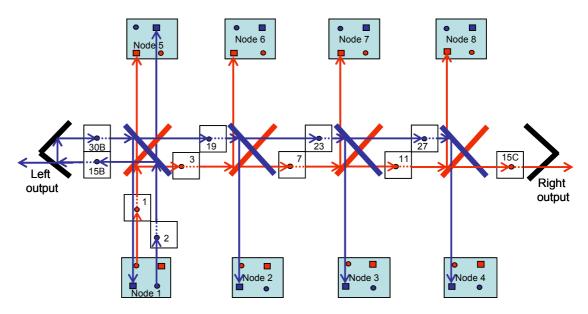

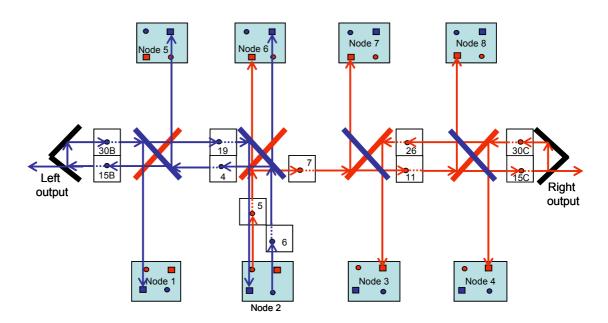

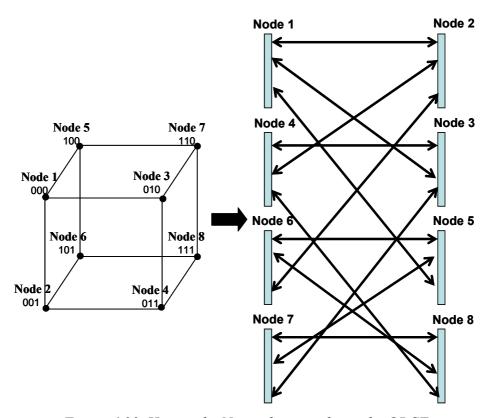

| 6.2 System Overview                                                         | 123 |

| 6.3 Optimised Cut-Through Ring Architecture                                 | 125 |

| 6.4 Optical Components                                                      | 129 |

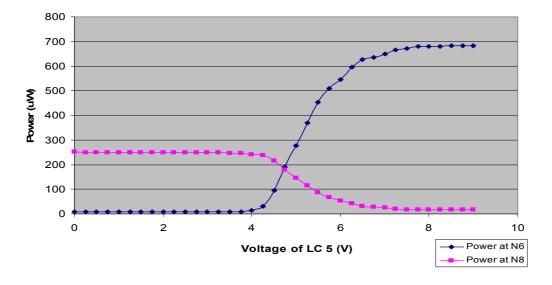

| 6.4.1 Liquid Crystal Characterisation                                       | 129 |

| 6.5 Design of the OCTR Architecture using Rapid Prototyping Technology      | 131 |

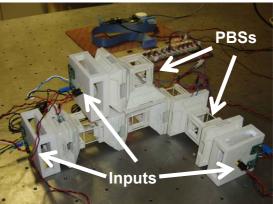

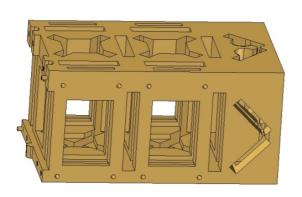

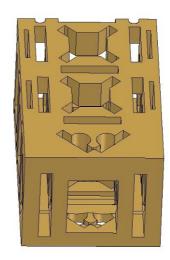

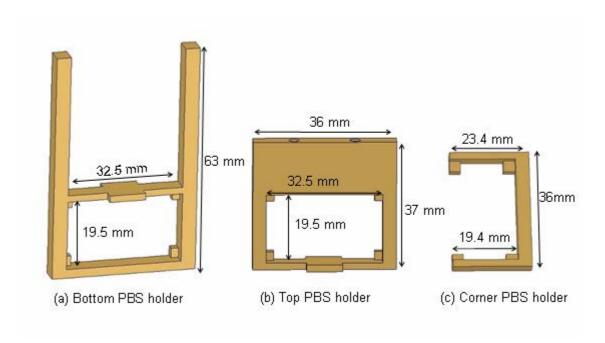

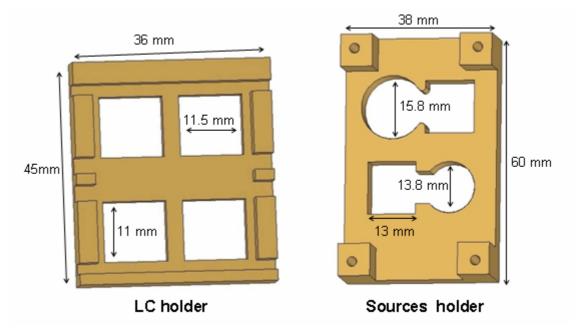

| 6.5.1 Design and Implementation of the Structures                           | 131 |

| 6.5.2 Assembling the Optomechanical System                                  | 135 |

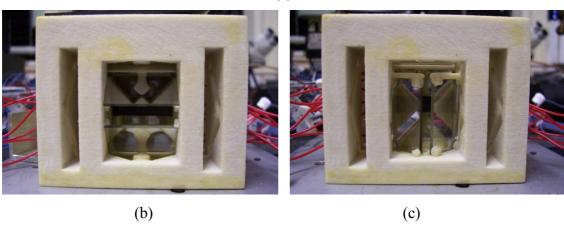

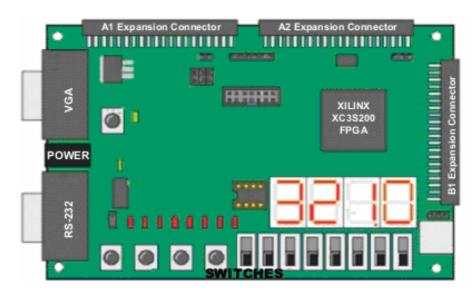

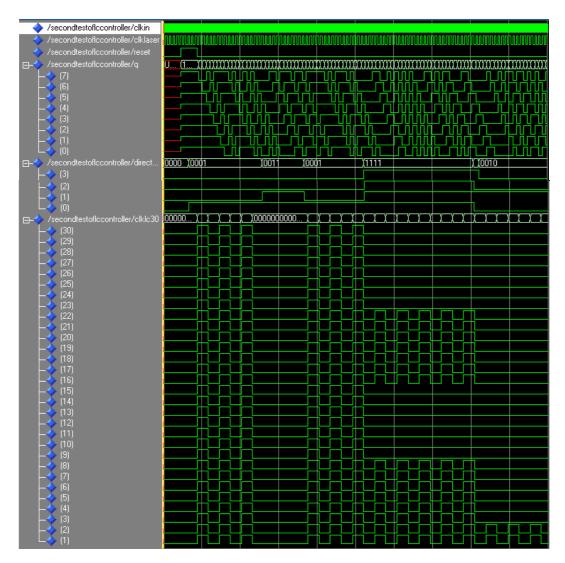

| 6.6 Programming the Field Programmable Gate Array Module                    | 137 |

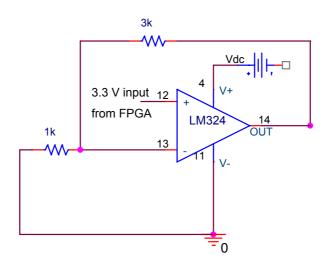

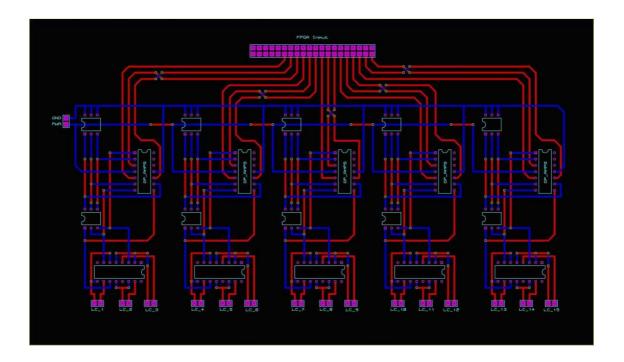

| 6.6.1 PCB Design                                                            | 139 |

| 6.7 Results                                                                 | 141 |

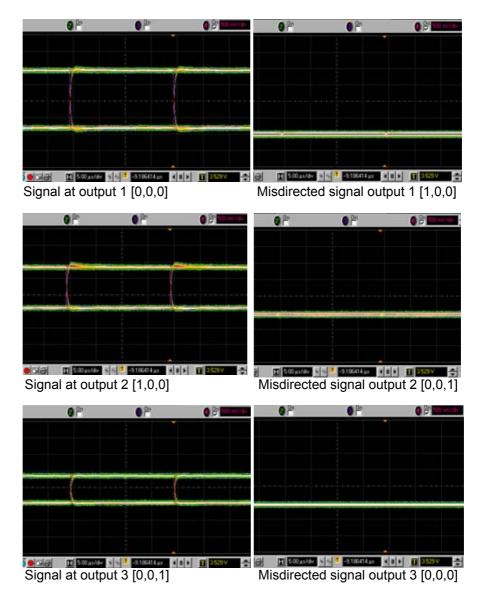

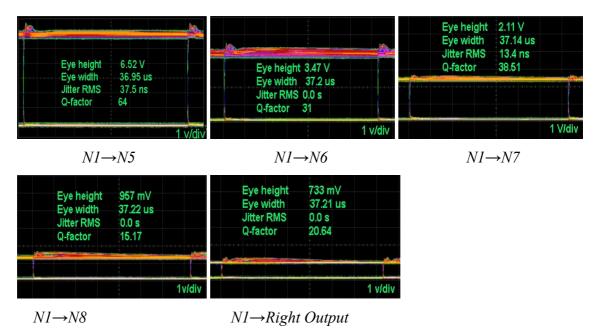

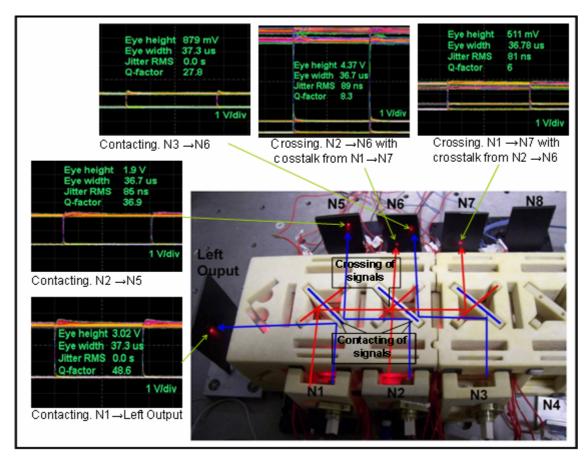

| 6.7.1 Experiment 1 – Connectivity of Node 1                                 | 144 |

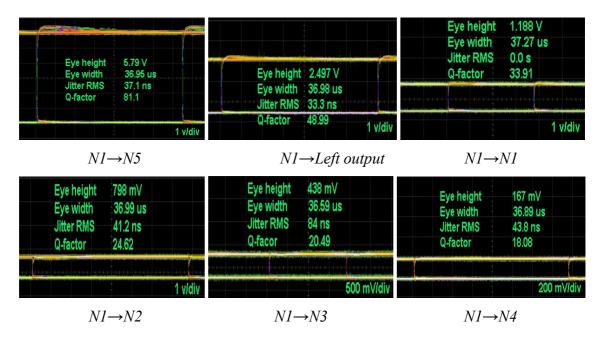

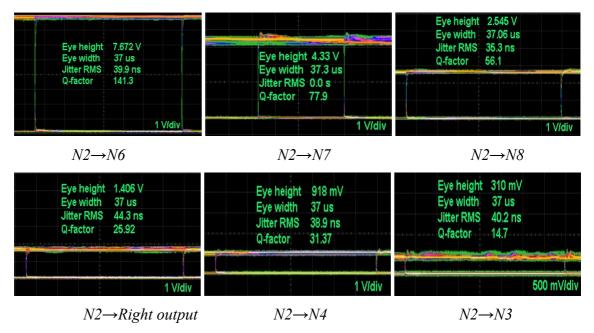

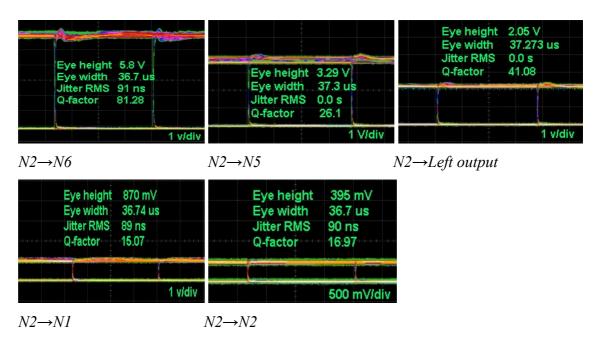

| 6.7.2 Experiment 2 – Connectivity of Node 2                                 | 148 |

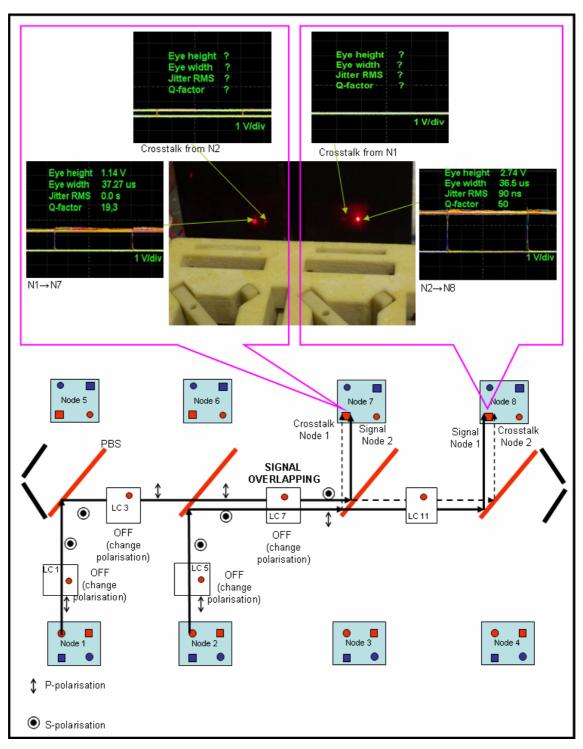

| 6.7.3 Experiment 3 – Optical Channels Efficiency and Properties of the OCTR |     |

| Architecture                                                                | 152 |

| 6.8 Applications of the ORCT Architecture                                   | 158 |

| 6.9 Conclusion                                                              | 162 |

| References                                                                  | 163 |

| Chapter 7 – Conclusions and Future Work                                     | 164 |

| 7.1 Summary                                                                 | 164 |

| 7.2 Conclusions                                                             | 165 |

| 7.3 Future Work                                                             | 166 |

| References                                                                  | 167 |

#### PUBLICATIONS AND PRESENTATIONS

- R. Gil-Otero, T. Lim, and J. F. Snowdon, "Characterization of a Reconfigurable Free-Space Optical Channel for Embedded Computer Applications with Experimental Validation Using Rapid Prototyping Technology", *EURASIP Journal on Embedded Systems*, Vol. 2007, Article ID 67603, 2007. doi:10.1155/2007/67603, January 2007.

- 2. C. J. Moir, R. Gil-Otero, G. Russel and J. F. Snowdon, "Architecture and Tolerancing for Matrix Operations on the Optical Highway", *Optical Engineering*, 45(9), 095401, September 2006.

- 3. R. Gil-Otero, Craig J. Moir, Gordon Russell, T. Lim, and John F. Snowdon, "Free-Space Optical Interconnected Topologies for Parallel Computer Application and Experimental Implementation using Rapid Prototyping Techniques", *Optical Engineering*, 45(8), 085402, August 2006.

- 4. R. Gil-Otero, J. Snowdon, "Characterization of a reconfigurable Free-space optical channel", Poster presentation at the Scottish Universities Alliance, SUPA Photonics in Strathclyde University, Glasgow, UK, July 2006.

- R. Gil-Otero, C.J Moir, T.Lim, G A Russell, J F Snowdon, "Rapid Prototyping for Free-Space optical interconnects", Poster presentation at ECOC Conference in Scottish Exhibition Conference Centre, Glasgow, UK, September 2005.

- S Kumpatla, R. Gil-Otero, G A Russell, J J Casswell, C J Moir, J F Snowdon, "Optically Interconnected Computing (OIC) Group", Poster presentation at the Scottish Universities Alliance, SUPA Conference in Strathclyde University ,Glasgow, UK, May 2005.

- 7. Rafael Gil-Otero, G. A. Russell, T.Lim, K. J. Symington, J. Snowdon, "Design of a 3 dimensional optical interconnect architecture based on free space", Oral presentation in PREP Conference, Lancaster, UK, March 2005.

## **Chapter 1**

## Introduction

#### 1.1 Introduction and Thesis Outline

The world's Information Technology industry is moving a step closer towards incorporating photonics with the aim of overcoming bandwidth bottlenecks. The recent development of the first electrically driven Hybrid Silicon Laser for Intel at the University of Santa Barbara [1] is a good example of technological advancements toward standard high-volume, low-cost silicon manufacture techniques available for integrating silicon photonic chips.

For communication technology, fiber-based optical interconnects have already proven their advantages over electrical interconnects over long distances. However, for the new era of parallel computing applications where high bandwidth is required over relatively short distances (<1m), the utilisation of fiber becomes difficult and costly.

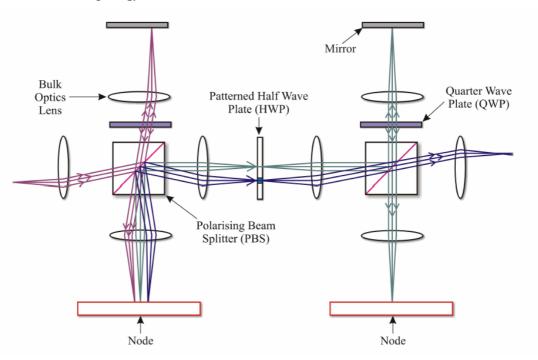

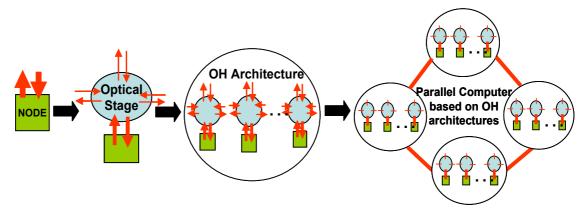

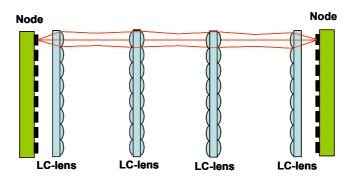

Free-Space Optical Interconnection (FSOI) networks are particularly attractive for connecting many nodes in a complex topology, where a node may be a board or a chip. Potential applications occur both in multiprocessor computing systems and switching systems. Several architectures exploiting this technology have been designed. These systems are generally based on an optical system, often referred to as an optical bus which comprises several image relay stages in a linear (or ring) topology [2], [3], [4].

This thesis is focused on the study of a particular FSOI system called Optical Highway (OH) [2],[5]. OH is a polarised beam routing system which provides a very high spatial and temporal bandwidth to which a large number of nodes (processors with associated memory) can be connected. The objective of the research is to analyse and characterise devices and technologies that can be useful for implementing the OH. A diverse number of OH architectures is proposed and different properties of the OH such as reconfigurability, scalability, tolerance to misalignment and polarisation losses will also be under research.

This first chapter, will present a general overview of the limitations of current electrical interconnects and computer technologies. It will also analyse the influence of these limitations on new computer architectures based on parallel processing that are being employed to fulfil the requirements for present and future computers. The last part of the chapter will present the advantages of optoelectronic systems over electronics for solving communication problems.

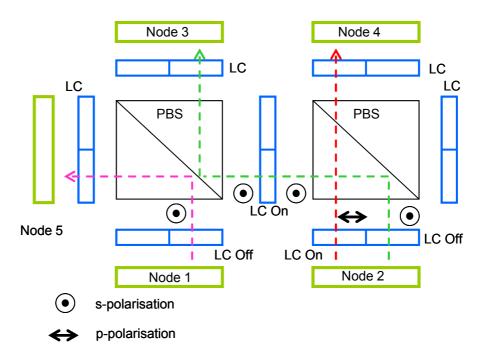

Chapter 2 will show the advantages of FSOI systems over other optical communication systems. The state-of-the-art in FSOI technology will also be analysed and the OH will be presented as the FSOI system under study in this thesis. The last part of this chapter will propose a novel design of the OH that exploits the properties of FSOIs such as reconfigurability, which is achieved by using Liquid Crystals (LC).

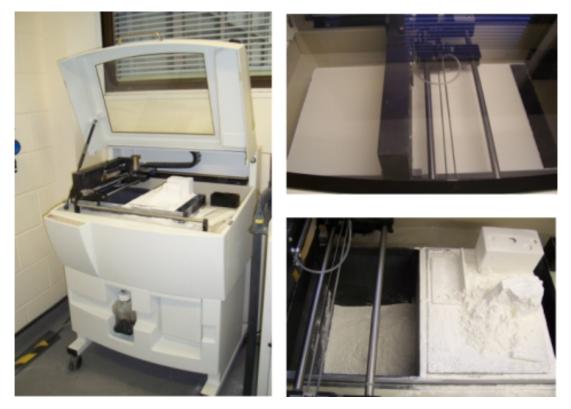

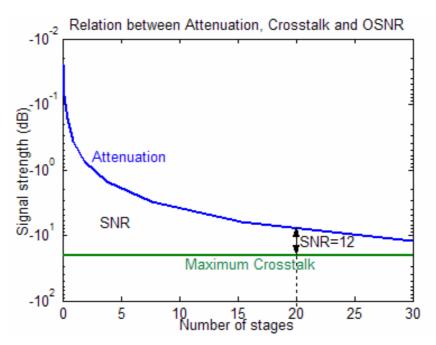

In Chapter 3, new 'off-the-shelf' optical components will be proposed and tested for using as optical stages of the OH. A technology known as Rapid Prototyping (RP) will also be employed for the first time in order to implement optomechanical structures at low cost and low production times. Then, the optomechanical system will be used to undertake a first estimation of the scalability of the system, which will be compared theoretically.

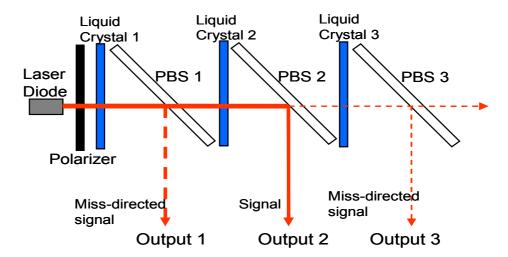

Chapter 4 will characterise a more suitable set of optical components including 90° Twisted Nematic Liquid Crystals (TNLC) which will allow us to achieve more optimum results. Then, the reconfigurable properties of one channel of the OH will be tested using Eye Diagrams (ED) as an analysing technique. The chapter will conclude with the analysis of a second method used to estimate the scalability of the system.

Chapter 5 will analyse the requirements for designing efficient OH architectures. Different designs of the OH at different levels will also be presented and characteristics such as performance, cost, efficiency and redundancy will be taken into account.

Chapter 6 will focus on the construction, assembly and proof-of-work of a particular architecture, the Optimised Cut-Through Ring (OCTR) architecture, proposed in Chapter 5. This architecture will be used to interconnect 8 nodes and different properties of free space optical signals in general and the OH in particular will be tested.

Finally, Chapter 7 concludes this dissertation and outlines some potential areas of future research

#### 1.2 Motivation

The motivation for this research comes from the need to find a solution to the limitations of the use of electrical interconnects for short, high-bandwidth links such as input/output (I/O) buses and memory buses links. We will show how electrical interconnects slow down the performance of computer system components such as processors, memories and I/Os and increase the gap in performance between them.

This thesis is also motivated by the bigger role that computer manufacturers are giving to parallel processing as the main solution for maintaining Moore's law. One of the major challenges of multiprocessor systems is the communication data between processors, symmetric multiprocessors (SMP) or system buses where, currently very high bandwidth and low latency are required.

#### 1.2.1 Electrical Interconnect Limitations.

Current technology in CMOS electronics operates chip speeds in multi-GHz clock rates and transistor gates down to 90 nm. Thus Moore's Law does not seem to be slowing down in the near future according to the 2003 ITRS Roadmap [6]. Yet, electrical interconnects do not seem poised to keep up. Metal wires are currently being used to connect chips to boards (links ~10-cm long), boards to boards (~50 cm), router linecards to each other (~3 m) and so on. Unfortunately, at frequencies above 5 GHz, a copper wire along an internet router backplane fails to act as a simple electrical signal channel [7]. The many imperfections of the metallic interconnect such as frequency-dependent loss, impedance mismatching and skin depth, complicate the transmitter circuitry. To some extent, these problems can be overcome at a cost of electrical power consumption. However, since the heat extraction from CMOS chips has recently become a serious problem ([6], [8]) reducing electrical power consumption has developed into a high-priority design issue.

In the following sections, we take a closer look at each of the major issues with electrical interconnects.

#### **Frequency-Dependent Loss**

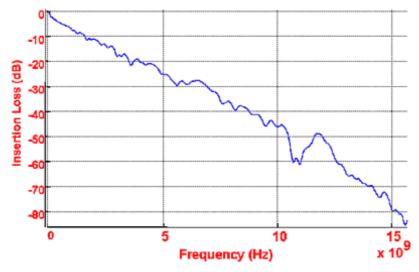

Mohammed et al. at Intel [9] simulated a 20-inch electrical interconnect on a standard printed circuit board using parameters for the material FR4. Their results, shown in their Figure 1.1, indicate that there is an insertion loss of about -25 dB at 5 GHz and about -45 dB at 10 GHz. At higher signal frequencies, the losses in the electrical interconnect gets even worse. In absolute terms, this amount of loss is severe, and the variation in loss with respect to frequency causes signal distortion.

Figure 1.1. Simulation of 20" channel transmitter [9].

A process called equalization can compensate for this aspect of the channel by amplifying frequency components that are more strongly attenuated during the transmission. Equalization, however, requires previous knowledge of the data transfer rate and of the channel characteristics (or at least some active method of determining the characteristics) and consumes valuable chip area and electrical power [9]. As the bit rates increase, the loss of the electrical channel gets worse and equalization schemes will only become less practical.

A second consequence of the frequency-dependent loss of the electrical channel is the so-called "aspect-ratio limit" of electrical lines [10], [11]. The capacity of an electrical interconnect system,  $B_{MAX}$ , is essentially limited by the total cross-section, A, and the length, L:

$$B_{MAX} = B_0 \times \frac{A}{L^2}$$

Equation 1.1

The constant  $B_0$  is related to the resistivity of the interconnect and is only weakly dependent on the fabrication technique. For copper, it is about  $10^{14}$ bits<sup>-1</sup> in a co-axial cable,  $10^{15}$ bits<sup>-1</sup> in a multi-chip module (MCM) and  $10^{16}$ bits<sup>-1</sup> in cross-chip lines.

Since the distance that must be traveled by the signal and the size of the chips are usually fixed in a system, the maximum aspect-ratio can be calculated and thus, the maximum aggregate data rate is known. In other words, it does not matter what specific architecture is implemented (many small wires or a few large wires) as filling a particular volume with information-carrying wires will result in the ability to transmit only a certain amount of data per second. Advanced techniques such as multilevel coding and repeatering can be used to extend this limit, but these techniques consume additional power [7].

#### **Impedance Mismatching**

Another major problem is to construct electronic transmission lines (board-to-board interconnects) with uniform characteristic impedance.

In a practical computer or router system, the electronic boards are plugged into a backplane which connects the many boards to each other. A signal generated on one board, for example, must pass through the ball grid array on the transmitter chip onto the printed circuit board, travel along a metal trace on the board, cross over to the backplane through a connector, along the backplane, through another connector, along another board, and through another ball grid array in order to arrive at the receiver circuit. At each interface, two traces come together in a way that is likely to contain some discontinuities in the size and shape of the joint between them. Electrical signals passing through such discontinuities generate reflections due to the impedance mismatch at the interface [7], [12]. It is essential to minimised these reflections because they can cause intersymbol interference (ISI). ISI means the information in one bit is corrupted by the energy or information in some other bit(s) in the data stream. ISI, in this case, is essentially an 'echo' – the first part of a signal tries to pass these interfaces but some of the energy is reflected, and when it comes back in the same direction a split second later this 'echo' gets superimposed with the signal that is currently trying to pass the interface for the first time. Note that reflections are not the only cause of ISI. Other channel imperfections such as dispersion can lead to ISI as the energy from one bit corrupts the adjacent bits in time.

#### Crosstalk

As the highest frequency in an electrical signal approaches 5-10 GHz, a wire with an oscillating electric field at that frequency will be emitting radiation that will affect the nearby wires. Thus, a signal that is supposed to be confined to one wire will actually be contributing to the energy or signal carried on another. This "crosstalk" is obviously noise on the receiving signal that degrades the ability of the receiver circuit to properly distinguish the digital levels. The large amount of data that must pass through a chip's I/O, requires a dense array of interconnects. If an electrical interconnect scheme is utilised, each line must be well protected in order to avoid any possibility of crosstalk

#### **Power**

A major problem with electronic interconnects is the power dissipated in terminating resistors, especially in conventional complimentary metal oxide semiconductor (CMOS) signalling. Complex architectures such as rack and blade systems are crowded with copper lines which drain power, generate heat, and force system designers into placing the hottest components right next to each other. The result is that some blade servers can not be fully populated with the latest processors and workloads may have to be offloaded to cooler systems to avoid overheating.

Reducing electrical power consumption has developed into a high-priority design issue. Thus, the growth in power consumption must be stopped whilst still gaining performance. Voltage scaling techniques will help spread out the thermal management problem. However, electrical noise will become an issue limiting voltage scaling and also device performance since at very low VCC voltages, reduced signal to noise ratios will lead to increases in bit errors and thus frequent transient processor failure.

#### **Pin Density**

The exponential growth in transistor densities, as predicted by Moore in 1965, has lead to smaller faster chips. However, the number of I/O pins connecting the chips to the outside world is not improving at the same rate as transistor performance.

Higher clock speeds have increased the amount of data required to keep the chips 'fed' with data. To avoid increasing the frequency of the I/O pins operation, increasingly more pins are required. At the same time the chips are reducing in size and, because of the planar nature of electronic design, the space available around the chip for

connections is shrinking. The size of the I/O pins cannot be reduced much further because of bandwidth limitation imposed by reducing the cross-sectional area and by increasing difficulties in working with very fine metal wire. According to the 2004 ITRS roadmap [13], the number of pins available per chip will increase at a rate of approximately 11% per year over the next fifteen years. This is a much lower rate than the predicted rate of increase in the number of transistors per chip, which is projected at 26% per year in the same period.

Even though pins are expected to run at a higher frequency thus increasing the effective bandwidth, the on-chip frequency will increase at the same rate [13], which will offset the increase in pin frequency. In addition, the cost per pin is predicted to decrease at a lower rate (~5%) than that of the increase in the number of pins [13]. This means that the overall cost of packaging will increase at a rate of approximately 5% a year. If no effort is made to reduce the cost further (or reduce the rate of increase in the number of pins), the total packaging cost will double in the next fifteen years, a trend that is opposite to other design cost trends.

#### 1.2.2 Influence of Electrical Interconnects on Memory Performance.

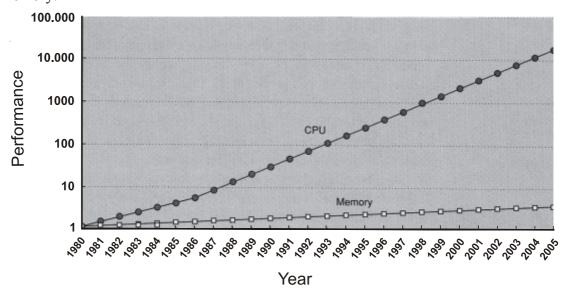

Over the past few decades, transistor performance has been improving at a much faster rate compared to memory performance. Figure 1.2 plots the evolution of CPU performance against the historical performance improvement in time to access main memory.

Figure 1.2. Evolution of Memory and CPU Performance [14].

DRAM is the memory technology that is used almost exclusively for direct communication with the CPU. Therefore, it is a key technology to the overall performance of electronic computing systems because memory deployed in its current form is significantly slower that the microprocessor. For example, while leading edge processors are now operating at 4 GHz, present generation memory is only capable of a 400 MHz performance. This disparity results in a condition generally referred to as the 'memory wall'. In such conditions, the CPU must remain in a wait state until the memory data is written or retrieved.

The 2004 ITRS Roadmap [13] predicts that transistor speed will continue to improve at a much faster annual rate (21%) over the next fifteen years compared to the rate of improvement in DRAM latency (10%). Thus, even though each is improving exponentially, the exponent for the microprocessor is substantially larger than that for the DRAMs. The difference between diverging exponentials also grows exponentially, so although the disparity between processor and memory speed is already an issue, it will become a much bigger one. Therefore, computer designers are faced with an increasing processor - memory performance gap, which now is the primary obstacle to improve computer system performance. Part of this disparity is due to the limits of current interconnection design, the memory bus, which often results, particularly at higher frequencies, in disturbances that contribute to signal distortion.

In addition, because of the growing memory access latencies (measured in processor cycles), any request that misses in the caches may eventually take hundred of cycles to satisfy. Thus, system speed will now be dominated by memory performance. This problem can be solved by reducing the average memory access time, which depend on three factors; Hit time, Miss penalty and Miss rate. In reference [14] different latency tolerances (or reduction) techniques are presented. However, these techniques increase the processor's memory bandwidth needs by causing the processor to request the same stream of operands in less time or by causing the processor to request more data from memory. Thus, the two factors of memory latency and memory bandwidth are closely related. Improvement in memory bandwidth is critically necessary to support novel memory latency techniques. There are a wide range of techniques to improve effective memory bandwidth. One of the most important includes the use of wider and faster connection to memory [15].

Traditional approaches to improving the memory bandwidth include the speeding up of the memory clock (this is to reduce the access latencies), increasing the bus width, or both. For conventional DRAMs, these approaches are reaching their practical limits. While clock rate scaling causes tight system timing requirements, which dictate precise component and PCB modelling, the increase of bus width comes at the expense of increasing the pin count, increasing I/O power, and creating multitude of mechanical and PCB layout problems.

## 1.2.3 Influence of Electrical Interconnects on Processor Performance and the New Era of Parallel Processing.

When compared with the original bus interface on the Intel 8088 processor used by IBM in the first IBM PC, we find that available bus performance has increased significantly. The original 8088 processor had an 8 bit wide data bus operating at 4.77 MHz. The peak data bandwidth, product of the bus frequency and the data bus width, was therefore 419 Mbit/s or 4.77 Mbyte/s. When compared with this bus, the current highest performance general purpose peripheral bus available (the PCI-Express) has widened by a factor of 8 and its signaling speed has increased by a factor of 28 for an overall improvement in peak bandwidth of approximately 2000% [14]. Owing to improvements in bus utilization the improvement of actual bandwidth over the last 20 years has been even more dramatic than this, as has the improvement in actual processor performance. While the growth in bus performance over the last several years has been impressive there are many indications that a new approach must be taken for it to continue.

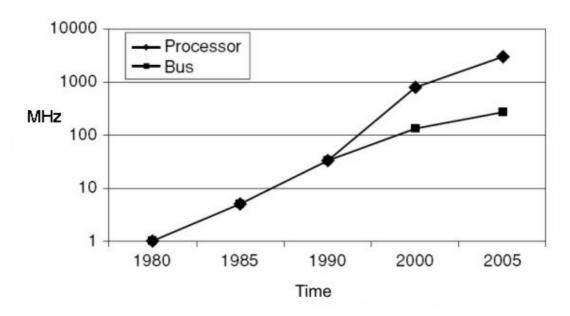

Figure 1.3, [16], shows the exponential growth of processor performance over the last 30 years compared to the slower growth of processor bus frequency over that same period of time. The MHz scale of the chart is logarithmic and the difference between the core CPU performance, represented by the clock frequency, and the available bandwidth to the CPU, represented by the bus frequency, continues to grow.

*Figure 1.3. Frequency and bandwidth growth [16].*

The connections between processors and peripherals have been traditionally, shared buses and often a hierarchy of buses. Devices are placed at the appropriate level in the hierarchy according to the performance level they require. Low-performance devices are placed on lower-performance buses, which are bridged to the higher-performance buses so they do not overload the higher-performance devices.

Traditional external buses used on more complex semiconductor processing devices such as microprocessors are made up of three sets of pins, which are soldered to wire traces on printed circuit boards. These three categories of pins or traces are address, data and control. The address pins provide unique context information that identifies the data. The data is the information that is being transferred and the control pins are used to manage the transfer of data across the bus. For a very typical bus on a mainstream processor there will be 64 pins dedicated to data, with an additional eight pins for parity protection on the data pins. There will be 32–40 pins dedicated to address with 4 or 5 pins of parity protection on the address pins and there will be approximately another 30 pins for control signaling between the various devices sharing the bus. This will bring the pin count for a typical bus interface to approximately 150. Due to of the way that semiconductor devices are built; there will also be a large complement of additional power and ground pins associated with the bus. These additional pins might add another 50 pins to the bus interface pin requirement, raising the total pin count attributed to the bus alone to 200. This 200 pin interface might add several dollars to the packaging and

testing cost of a semiconductor device. The 200 wires traces that would be required on the circuit board would add cost and complexity as well. If the bus is needed to cross a backplane to another board, connectors would need to be found that would bridge the signals between two boards without introducing unwanted noise, signal degradation and cost. Then, if it is assumed that the system will require the connection of 20 devices to achieve the desired functionality, we begin to understand the role that the bus can play in limiting the functionality and feasibility of complex embedded systems.

The use of cache memory and more advanced processor microarchitectures has helped to reduce the growing gap between CPU performance and available bus bandwidth. Increasingly, processors are being developed with large integrated cache memories and directly integrated memory controllers. However, multiple levels of on- and off-chip cache memory and directly integrated memory controllers, while useful for reducing the gap between a processor's data demands and the ability of its buses to provide the data, does little to support the connection of the processor to external peripheral devices or the connection of multiple processors together in multiprocessing (MP) systems.

In addition to the increasing performance of processors, the need for higher levels of bus performance is also driven by two other key factors: First, the need for higher raw data bandwidth to support higher peripheral device performance requirements. Second the need for more system concurrency. The overall system bandwidth requirements have also increased because of the increasing use of Direct Memory Access (DMA) smart processor-based peripherals and multiprocessing in systems.

#### **Parallel Processing**

Multiprocessing is increasingly seen as a viable approach to adding more processing capability to a system. Historically, multiprocessing was used only in the very highest end computing systems and typically at great cost. However, the continuing advance of semiconductor process technology has made multi-processing a more dominant technology and its use can offer advantages beyond higher processing performance. It is believed that parallel processors will definitely have a bigger role in the future. This view is driven by three observations [14]. First, there appears to be slow but steady progress in one of the major obstacles to widespread use of parallel processors, software. This progress is probably faster in server and embedded applications, which exhibit natural parallelism and currently can be exploited without the trouble of rewriting a gigantic software base. Second, it is unclear whether architectural innovation

that has been based for more than 15 years on increased exploitation of instruction-level parallelism (ILP) can be sustained indefinitely. Modern multiple-issue processors have become incredibly complex, and the performance achieved through increasing complexity, silicon technology and power seem to be decreasing. Third, since microprocessors are likely to remain the dominant uniprocessor technology, the logical way to improve performance beyond a single processor is by connecting multiple microprocessors together. This combination is likely to be more cost-effective than designing a custom processor. The use of multiprocessing may also reduce the total system power dissipation at a given performance point. This occurs because it is often possible to operate a processor at a reduced frequency and achieve greatly reduced power dissipation.

While many obstacles to multiprocessing have been reduced or removed, the processor interconnect has increasingly become the main limiting factor in the development of multiprocessing systems. Existing multiprocessor bus technologies restrict the shared bandwidth for a group of processors. For example, in existing multiprocessors systems, communication of data between processors may cost anywhere from 100 clock cycles to over 1000 clock cycles, depending on the communication mechanism, the type of interconnect, and the scale of the multiprocessor. For multiprocessing to be effective, the processors in a system must be able to communicate with each other at high bandwidth and low latency.

## 1.3 Using Optics in Computers

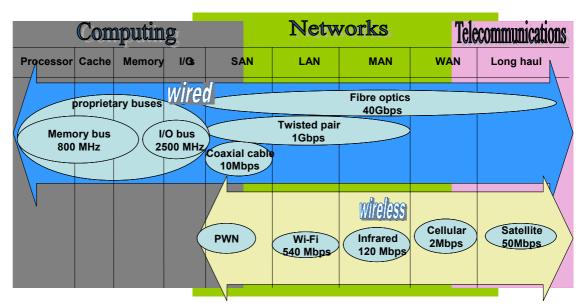

The use of optical interconnects is often cited as having potentially great advantages over the use of electronic technology. In fact, optical communication has already transformed the telecommunications industry, Figure 1.4. Today, Wide Area Networks (WANs) based on fiber-optics have permeated every aspect of terrestrial communication. The success of fiber-optic insertion in telephone systems and the promise of economies of scale from a larger component market resulted in adoption of optics for Metropolitan Area Networks (MAN) and Local Area Network (LAN) connectivity where low-cost is a dominant factor. The Gigabit Ethernet standard (IEE 802.3z) of 1998 and the 10 Gigabit Ethernet standard (IEEE 802.3ae) in progress since 2001 are representative of the adoption of fiber-optics for the LAN environment.

Recently, optics has been used to solve a different class of problems in Store Area Networks. In these networks the link distance is less than 300m, so the advantage of optics for long-distance transmission is not important. However, electrical interconnections simply can not provide the needed bandwidth density and this is where optics has another distinct advantage.

The use of optics in computers is oriented to tackle the electronics and architectural problems presented in the previous section. However, before considering new computer architectures based in optics we should be sure that it must be nearly impossible to build an equivalent system with pure electronics within a prolonged future. Therefore, it is important to know the advantages and a disadvantage of optics over electronics for interconnects.

Figue 1.4 Nowadays, optics is used for both wired and wireless communications in the networks and telecommunications world. Because of the low attenuation and less need for repeaters than twisted pair and coaxial cables, fibre is the most economic choice for telecommunication and WAN's. For smaller networks fibre optics is employed when high bandwidth is required, and for wireless communications, optics (infrared) is a commercial solution for low cost and quick installation MAN's. The many advantages of optics can also be used in the near future for solving the interconnect problems of the computing world.

#### 1.3.1 Optical Interconnects

The difference between electronics and optics is essentially the difference between the electron and the photon. Since electrons carry mass and charge they interact very strongly with each other making them ideally suited for switching. Photons, on the other hand, do not carry mass or charge and are therefore non-interacting in free-space. This makes them ideally suited for interconnection since, as we will see optics can avoid complex problems of electrical interconnect bus design such as signal and clock distortion, high-frequency attenuation, temperature dependence, wave reflection and impedance matching phenomena. In addition, the optics itself does not need to be redesigned, in contrast to electrical bus, as the clock rate on the bus is increased.

#### **Frequency-Dependent Loss**

The information channel in the case of optical interconnects is either free space (air or glass) or optical fiber (glass). The frequency-dependent distortion for an optical signal in either material does not have any comparable limit with that of an electrical signal because it does not have the resistive loss physics. Optics does not rely on wires with their associated resistance and capacitance. Therefore, it can avoid problems such as signal and clock distortion and high-frequency attenuation. Moreover, at the relevant frequencies, neither material absorbs or scatters much of the energy over a large range of frequencies. The attenuation of optical fiber is around 0.2dB/km at the optimum wavelength of 1550 nm. Thus, almost all the energy sent into the fiber reaches the receiver. For free space optical communication the attenuation highly depends on weather conditions. However, for the distances dealt with in this thesis (generally indoor and <1m) weather conditions are not taken into account and attenuation of 0.43 dB/km (in clear air conditions for infrared wavelength) can be considered. This implies that a short-distance optical system would have little or no need for equalisation or repeaters, saving power and reducing the thermal load.

#### **Impedance Mismatching**

Impedance matching in optical systems is achieved simply by utilising antireflection coatings [11]. Because the refractive index of the materials remain relatively constant over the optical frequency range of interest, an impedance matching layer is sufficient for all signals. The simplest anti-reflection coating between media with refractive

indices  $n_1$  and  $n_2$  is a single layer of material with a properly chosen thickness (t =  $\lambda/(2n)$ ) and index of refraction (n =  $\sqrt{(n_1n_2)}$ ).

#### Crosstalk

Reduced crosstalk due to electromagnetic interference is another significant advantage of optical systems [11]. The short wavelength of optical waves ( $\sim 1 \mu m$ ) allows the energy in the beam to be focused down to a small spot at the detector. Thousands of individual beams can be imaged simultaneously using a single lens without significant cross-talk.

#### **Pin Density**

Optics can provide a potential solution to this problem. It is quite easy to manufacture arrays of optoelectronic devices with their optical I/Os normal to the chip. It is also feasible to have the I/O connected across the whole area of the chip by placing electronic I/O pads across the chip on top [17]. This has the advantage of allowing the surface area and not the edges of the chip to be used for I/O. In this case, the solder links between the electronic chip and the optoelectronic chip would be very short so the bandwidth can remain very high.

#### **Other Factors**

Optical technologies have also other advantages over electronics for interconnections. These are as follows:

- Larger number of fan-ins and fan-outs

- As a single beam of light can be sent to many detectors, by using a DOE for example, (fan-out) and many beams can reach one detector (fan-in). The power losses and lack of I/Os limit the electronics fan-ins and fan-outs.

- Lower signal and clock skew

- The narrow band nature of light, compared with the broad band nature of an electronic signal, means lower dispersion when the signal travels through an interconnection media and, therefore, less spreading of signals.

- Potential for reconfigurable interconnect

- Optical interconnects can make use of the greater number of available degrees of freedom optically available (such as polarisation and wavelength) to create multiple paths, which can be taken dependent on a controllable property of the carrier beam.

Table 1.1 summarises the most significant difference between electronic and optics for interconnect applications.

|                          | Electronic                                                                                                                                                                                                            | Optics                                                                                                                                                                                                                                                     |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transmission             | Wires                                                                                                                                                                                                                 | ■ Fiber, Free Space and Guide Wave                                                                                                                                                                                                                         |  |  |

| Attributes of<br>Signal  | <ul> <li>Amplitude-phase</li> <li>Signal spectrum</li> <li>Modulation</li> <li>Pulse width/spectrum</li> <li>Power</li> </ul>                                                                                         | <ul> <li>Amplitude-phase</li> <li>Signal spectrum</li> <li>Modulation</li> <li>Pulse width/spectrum</li> <li>Power</li> <li>Coherence</li> <li>Light spectrum</li> <li>Polarisation</li> <li>Spatial distribution</li> <li>Spatial mode content</li> </ul> |  |  |

| Density                  | <ul> <li>Overlapping or crossing of lines not allowed</li> <li>Size of the signal limited by the wire</li> <li>Planar technology</li> </ul>                                                                           | <ul> <li>Overlapping and crossing allowed (free-space)</li> <li>Size of the beam limited by diffraction</li> <li>3D allowed. Ideal for parallel computer</li> </ul>                                                                                        |  |  |

| Delay                    | <ul> <li>Max. signal propagation speed ~ 0.1mm/ps</li> <li>Signal propagation speed ~1/C' ~ interconnection density</li> </ul>                                                                                        | <ul> <li>Max. signal propagation speed ~         <ul> <li>0.3mm/ps</li> </ul> </li> <li>The signal propagation speed does not depend on the interconnection density</li> </ul>                                                                             |  |  |

| Bandwidth                | <ul> <li>The density of electrical interconnections is affected by the bandwidth carried by each connection (because of parasitic C' and L' effects)</li> <li>Max bandwidth limit of any electrical system</li> </ul> | <ul> <li>The density of optical interconnections is not affected by the bandwidth carried by each connection.</li> <li>The bandwidth depends primarily on thermal and real state considerations.</li> </ul>                                                |  |  |

| Power                    | Matching impedance needed at the end of the line to avoid reflections => large power expenditure                                                                                                                      | Power requirements mainly limited<br>by the sensitivity of the<br>photodectors, the efficiency of the<br>conversions and the transmission<br>efficiencies                                                                                                  |  |  |

| Noise                    | ■ High noise features                                                                                                                                                                                                 | Low noise features                                                                                                                                                                                                                                         |  |  |

| Technology<br>& Material | Easy (CMOS), low cost. All Si possible                                                                                                                                                                                | Complicated (III-V materials, hybrid integration). High cost.                                                                                                                                                                                              |  |  |

| heat                     | <ul><li>Electrical wires generate<br/>heat</li></ul>                                                                                                                                                                  | <ul> <li>Optical interconnects do not<br/>generate heat</li> </ul>                                                                                                                                                                                         |  |  |

| Alignment                | Low sensitivity to misalignment                                                                                                                                                                                       | Extremely sensitive to misalignment                                                                                                                                                                                                                        |  |  |

Table 1.1 Electronics versus Optics for interconnect applications.

From Table 1.1, it is clear that optics has potential advantages over electronics for interconnection. However, it also outlines the main problem for the implementation of optics over short distances, which is the cost.

The primary barrier to extensive use of optics at short ranges is the cost of conversion from electrical to optical and back again. Silicon photonics holds the potential to create low-cost, highly integrated optical components using the same CMOS-based manufacturing techniques that have revolutionised the electronics industry over the past 40 years. Unfortunately, silicon's indirect bandgap makes light emission in the bulk material highly inefficient. Thus, it is extremely difficult to fabricate any kind of light emitter with this material. A high effort has been made to overcome this problem. However, to date, an electrically pumped pure silicon laser has not been demonstrated. Until an electrically pumped silicon laser is demonstrated, III-V semiconductor materials will continue to be necessary to produce communication lasers. The question then is to determine how these optical sources can be integrated cost-effectively onto a silicon photonic chip.

As mentioned at the beginning of the chapter, a breakthrough has been made by Intel at the University of Santa Barbara [1] with the recent development of the first electrically driven Hybrid Silicon Laser which has overcome many problems inherent in the previous integration by employing a volume-manufacturable wafer-bonding process which allows the fabrication of multiple hybrid lasers without the need for alignment, which is a critical costly step.

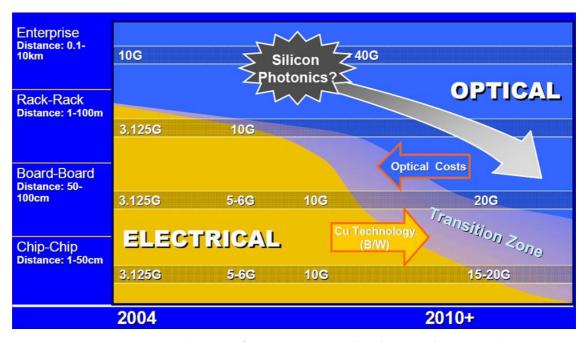

This is an example of how the world's Information Technology industry is moving a step closer towards incorporating photonics, and Figure 1.5 shows the prediction made by Intel where the transition period for changing from electronic to optics depend on how long Cu technology can hold with the high demand of bandwidth and when optical interconnect will be costly effective.

Figure 1.5. Prediction of interconnect technology evolution [18].

For the distances dealt with in this thesis (on card and multi-chip-level <1m) a cost effective solution will not be available in the near future. However, sometime after 2015 the interconnect industry based on electronic technology does not have any known solution for feeding the terabits of information needed for future multiprocessors architectures [19]. Therefore, it is believed that between 2015 and 2020, optics can start to be employed at this level [18].

#### 1.4 Conclusion

This introductory chapter has analysed the physical limitations of electrical interconnects and their effects on memory and processor performance. The interconnect requirements for the new era of parallel processing and how the advantages of optics over electronics can fulfil these requirements have also been analysed. Although, cost is currently the main factor that impedes a wide acceptance of optics, we believe that faster increase of optics over electronics technology will lead in the future to the use of optics for short distances.

#### References

- [1] M. Paniccia, V. Krutul, R. Jones and J. Bowers, "A Hybrid Silicon Laser: Silicon Photonics Technology for Future Tera-Scale Computing", *Technology@Intel Magazine*, 2006.

- [2] J. A. B. Dines, J F. Snowdon, M. P. Y. Desmullinez, D. B. Barsky, A. V. Shafarenko and C. R. Jesshope, "Optical Interconnectivity in a Scalable Data-Parllel System", *Parallel and Distributed Computing*, Vol. 41, pp. 120-130, 1997.

- [3] G. Kirk, D. V. Plant, T. H. Szymanski, Z. G. Vranesic, F. A. P. Tooley, D. R. Rolston, M. H. Ayliffe, F. K. Lacroix, B. Robertson, E. Bernier, and D. F.-Brosseau, "Design and Implementation of a Modulator-Based Free-Space Optical Backplane for Multiprocessor Applications", *Applied Optics*, 42, 2465-2481, 2003.

- [4] G. Kim, H. Xuliang, R.T. Chen, "An 8-Gb/s optical backplane bus based on microchannel interconnects: design, fabrication, and performance measurements", *Lightwave Technology*, Vol. 18, Issue 11, 1477-1486, 2000.

- [5] G. A. Russell, J. F. Snowdon, T. Lim, J. Casswell, P.Dew and I. Gourlay, "The Analysis of Multiple Buses in a Highly Connected Optical Interconnect", *Technical Digest of Quantum Electronics and Photonics 15, IoP Publishing Glasgow*, pp. 75, 2001.

- [6] Semiconductor Industry Association, "International Technology Roadmap for Semiconductors", http://public.itrs.net/Files/2003ITRS/Home.htm, 2003.

- [7] A. Emami-Neyestanak, "Design of CMOS Receivers for Parallel Optical Interconnects", Ph.D. Dissertation in Department of Electrical Engineering, Stanford University, Stanford, CA, pp. 142, 2004.

- [8] E. N. Wang, L. Zhang, L. N. Jiang, J. M. Koo, J. G. Maveety, E. A. Sanchez, K. E. Goodson, and T. W. Kenny", Micromachined jets for liquid impingement cooling of VLSI chips," *Journal of Microelectromechanical Systems*, Vol. 13, pp. 833-42, 2004.

- [9] E. A. Mohammed, A.; Thomas, T.; Braunisch, H.; Lu, D.; Heck, J.; Liu, A.; Young, I.; Barnett, B.; Vandentop, G.; Mooney, R., "Optical Interconnect System Integration for Ultra-Short-Reach Applications", vol. 2004, *Intel Technology Journal ed*: Intel Corporation, 2004.

- [10] D. A. B. Miller and H. M. Ozaktas, "Limit to the bit-rate capacity of electrical interconnects from the aspect ratio of the system architecture", *Journal of Parallel* and Distributed Computing, Vol. 41, pp. 42-52, 1997.

- [11] D. A. B. Miller, "Physical reasons for optical interconnection", *International Journal of Optoelectronics*, Vol. 11, pp. 155-68, 1997.

- [12] D. A. B. Miller, "Rationale and challenges for optical interconnects to electronic chips", *Proceedings of the IEEE*, Vol. 88, pp. 728-49, 2000.

- [13] International Technology Roadmap for Semiconductors. ITRS 2004 Update. Semiconductor Industry Association, http://www.itrs.net/Common/2004Update/2004Update.htm, 2004.

- [14] John L Hennessy and David A Patterson, "Computer Architecture: A Quantitative Approach", Morgan Kaufman, CA, Third edition, 2003.

- [15] D. Burger, J.R. Goodman, and A. Kagi. "Memory Bandwidth Limitations of Future Microprocessors", *Proc. 23rd Ann. Int'l Symp*. Computer Architecture, Assoc. of Computing Machinery, pp. 79-90, Aug. 1996.

- [16] S. Fuller. "RapidIO, The Embedded System Interconnect", John Wiley & Sons, Ltd ISBN: 0-470-09291-2, 2005.

- [17] M. W. Haney and M. P. Christensen, "Fundamental Geometric Advantages of Free-Space Optical Interconnects", *Proceedings of the Third International Conference on Massively Parallel Processing Using Optical Interconnections*, pp. 16-23, 1996.

- [18] MIT Microphotonics Center Industry Consortium Communication, "2005 communication technology roadmap Microphotonics", http://mphroadmap.mit.edu/aboutctr/report2005 /1 ctr2005 overview.pdf, 2005.

- [19] Semiconductor Industry Association, "International Technology Roadmap for Semiconductors", http://www.itrs.net/Links/2006Update/FinalToPost/09\_Interconnect2006Update.pdf, 2006.

### **Chapter 2**

# Free Space Optical Interconnects for Parallel Computer Applications

#### 2.1 Introduction

The previous chapter demonstrated the problems of electronic interconnects and the potential of optics, especially for communication technology where fiber-based optical interconnects have already proven its advantage over electrical interconnects over long distances.

This chapter introduces FSOI technology for short distance communications. The advantages of FSOIs over other interconnect technologies and the current state-of-theart in this field will be analysed. A particular FSOI system known as Optical Highway (OH) will also be examined. This system, proposed by the OIC group at Heriot-Watt University, provides a very high spatial and temporal bandwidth to which a large number of nodes can be connected in an arbitrary topology. This section will propose for first time new concepts and ways of improve the OH.

## 2.2 Free Space Optical Interconnect Networks and Current State-of-the-Art

Optics has been discussed as a future technology in computers in many articles which describe a wide variation of non-pure electronic systems [1],[2],[3],[4]. Despite this, optics has still not reached its full impact. As it was said in the previous chapter, cost is a major drawback that impedes the wide acceptance of optics. However, there are other factors such as misalignment, losses and crosstalk that also contribute to the slow development of this field. In any case, it seems clear that the key to success will not just consist of replacing electrical wires since many properties of optics will be wasted using that strategy. Instead, new computer architectures based on the best characteristics of both optics and electronics should be developed. If solutions could be found that utilise properties of optics such as transmission in all spatial dimension (an extra dimension compared to two dimensional electrical planes), light coherence, high bandwidth,

multiple wavelengths, immunity to electro-magnetic interference [1], together with the complementary characteristics of electronics, then we could also build new competitive systems.

This thesis focuses on parallel computer systems rather than processor design. Parallel computer systems have to deal with extreme bandwidths. Therefore it is natural to replace the information highways with optoelectronic interconnects, and thus utilise optical properties.

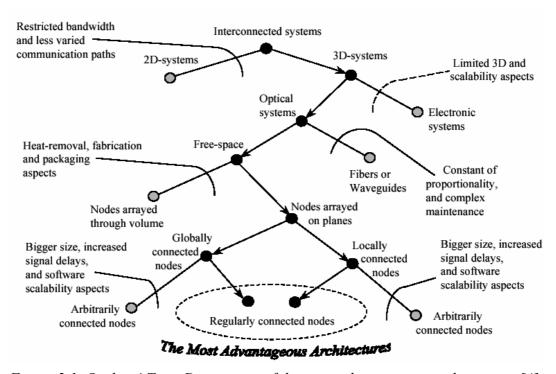

In Figure 2.1 we describe the ideas of Ozaktas' Tree [2],[3] where a systematic method (an architecture tree) is used to find the most promising parallel computer architecture by weighing the pros and cons of many design possibilities and removing the idea that is considered to be inferior to another.

Figure 2.1. Ozaktas' Tree. Description of the most advantageous architectures [4].

Note that the result of the architecture tree seems to favour regular, globally or locally interconnected 3D-systems using free space communication between nodes arrayed through planes. Ozaktas' Tree differs from Figure 2.1, however, since all locally connected systems are also pruned in favour of globally connected systems. He argues that these systems will use fewer time steps to complete a certain operation, and that the system growth rate will not increase compared to locally connected systems due to the requirement to have large distances between nodes to remove the heat. On the other

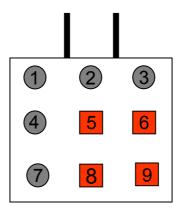

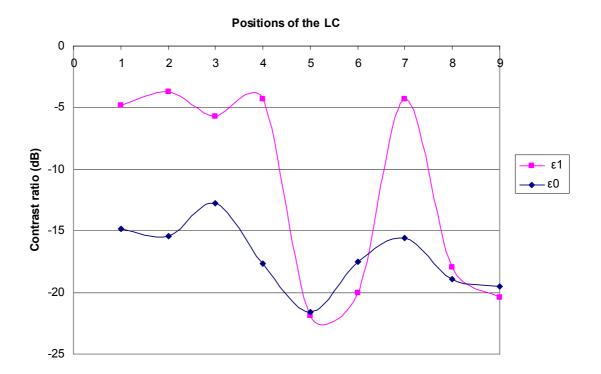

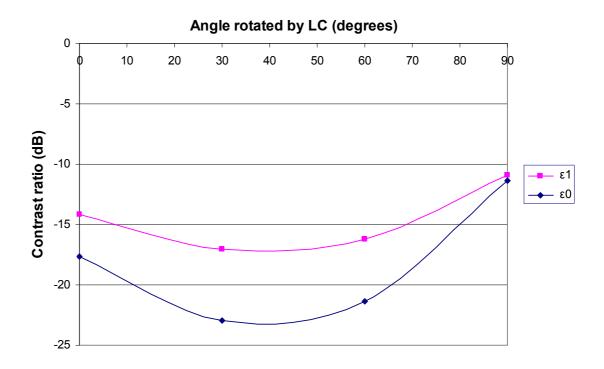

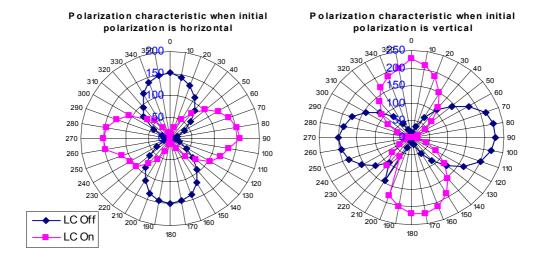

hand, H. Forsberg [4] argues that complex global architectures also suggest that we should use micro-optical systems and this could be a problem in reference to bisection bandwidth because of diffraction effects. Thus, he decides to keep the locally connected systems branch in order to allow the possibility of using macro-optic systems.