# Title A novel parallel algorithm for surface editing and its fpga implementation

Name Yukun Liu

This is a digitised version of a dissertation submitted to the University of Bedfordshire.

It is available to view only.

This item is subject to copyright.

## A NOVEL PARALLEL ALGORITHM FOR SURFACE EDITING AND ITS FPGA IMPLEMENTATION

YUKUN LIU

Ph.D.

September 2013

UNIVERSITY OF BEDFORDSHIRE

## A NOVEL PARALLEL ALGORITHM FOR SURFACE EDITING AND ITS FPGA IMPLEMENTATION

by

## YUKUN LIU

Ph.D.

Institute for Research in Applicable Computing

A thesis submitted to the University of Bedfordshire in partial fulfilment of the requirements for the degree of Doctor of Philosophy

September 2013

#### ABSTRACT

Surface modelling and editing is one of important subjects in computer graphics. Decades of research in computer graphics has been carried out on both low-level, hardware-related algorithms and high-level, abstract software. Success of computer graphics has been seen in many application areas, such as multimedia, visualisation, virtual reality and the Internet. However, the hardware realisation of OpenGL architecture based on FPGA (field programmable gate array) is beyond the scope of most of computer graphics researches. It is an uncultivated research area where the OpenGL pipeline, from hardware through the whole embedded system (ES) up to applications, is implemented in an FPGA chip.

This research proposes a hybrid approach to investigating both software and hardware methods. It aims at bridging the gap between methods of software and hardware, and enhancing the overall performance for computer graphics. It consists of four parts, the construction of an FPGA-based ES, Mesa-OpenGL implementation for FPGA-based ESs, parallel processing, and a novel algorithm for surface modelling and editing.

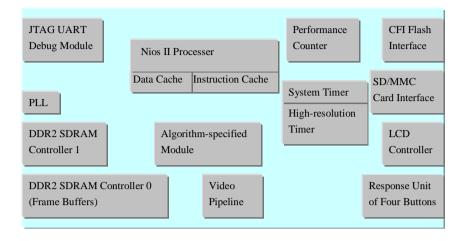

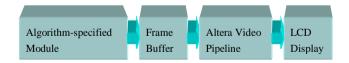

The FPGA-based ES is built up. In addition to the Nios II soft processor and DDR SDRAM memory, it consists of the LCD display device, frame buffers, video pipeline, and algorithm-specified module to support the graphics processing.

Since there is no implementation of OpenGL ES available for FPGA-based ESs, a specific OpenGL implementation based on Mesa is carried out. Because of the limited FPGA resources, the implementation adopts the fixed-point arithmetic, which can offer faster computing and lower storage than the floating point arithmetic, and the accuracy satisfying the needs of 3D rendering. Moreover, the implementation includes Bézier-spline curve and surface algorithms to support surface modelling and editing.

The pipelined parallelism and co-processors are used to accelerate graphics processing in this research. These two parallelism methods extend the traditional computation parallelism in fine-grained parallel tasks in the FPGA-base ESs.

The novel algorithm for surface modelling and editing, called Progressive and Mixing Algorithm (PAMA), is proposed and implemented on FPGA-based ES's. Compared with two main surface editing methods, subdivision and deformation, the PAMA can eliminate the large storage requirement and computing cost of intermediated processes. With four independent shape parameters, the PAMA can be used to model and edit freely the shape of an open or closed surface that keeps globally the zero-order geometric continuity. The PAMA can be applied independently not only FPGA-based ESs but also other platforms.

With the parallel processing, small size, and low costs of computing, storage and power, the FPGA-based ES provides an effective hybrid solution to surface modelling and editing.

## DECLARATION

I declare that this thesis is my own unaided work. It is being submitted for the degree of Doctor of Philosophy at the University of Bedfordshire.

It has not been submitted before for any degree or examination in any other university.

Name of candidate:

Signature:

Date:

## DEDICATION

To my parents To my husband, Jie Geng To my son, Hao Geng

To all who gave me a hand to reach this achievement, I will always say: Thank you.

### ACKNOWLEDGEMENTS

Issac Newton said, "If you say that I see far, it is because I am standing on the shoulders of giants".

This PhD research would have been a huge, unachievable piece of work if there had not been the facilities available in the surroundings, which come from different companies and organisations, and, of course, without the Internet. Thanks for all the open or commercial resources. With them, the research has been accomplished at the foundation built from the facilities and sources. Most of them have been quoted as references at the end of the thesis. It is just like "standing on the shoulders of giants".

It is a trial-and-error process. It is a dark tunnel always with a definite light in front of me, far or near. It is a lonely journey full of joys and sadness. It is my PhD journey. It is just a scientific exploration, I think. Thanks for all the help from different places and my deep heart to support me.

I would like to express my thanks to my team of supervisors, Prof. Yong Yue, Prof. Carsten Maple, and Prof. Jiaomin Liu, for their encouragement, criticism, guidance, suggestions, and support during the research.

I would like to thank Mrs. Carol Connett and her family for their help and good time along with them during my stay in the UK.

I would like to thank Qixiang Wang for his suggestions and advice in my research.

I would like to thank my colleagues in my working university, Hebei University of Science and Technology, Prof. Liwei Guo, Chunru Huang, Guojiang Gao, and Shiquan Qiao, for their help in my work during my PhD research.

Thanks to Prof. M. James C. Crabbe, Dr. Dayou Li, Dr. Jon Hitchcock, Dr. Herbert Daly, Dr. Xiaohua Feng, Shijuan Pan, Hui Wei, Shuang Gu, Beisheng Liu, Tao Cao, and others, for providing help when I needed.

Finally, my very special thanks are due to my beloved family, parents, husband and son, whose encouragement has been invaluable.

## TABLE OF CONTENTS

| ABSTRACT I               |

|--------------------------|

| DECLARATION II           |

| DEDICATION               |

| ACKNOWLEDGEMENTS······IV |

| TABLE OF CONTENTS V      |

| LIST OF TABLESXI         |

| LIST OF FIGURESXII       |

| LIST OF ABBREVIATIONS    |

| LIST OF NOTATIONS XXI    |

| Chapter 1: | Introd                                                           | uction1                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1        | Backgr                                                           | ound1                                                                                                                                                                                                                                                                                                              |

|            | 1.1.1                                                            | Software and Hardware in Computer Graphics1                                                                                                                                                                                                                                                                        |

|            | 1.1.2                                                            | Hardware Solution in Computer Graphics2                                                                                                                                                                                                                                                                            |

|            | 1.1.3                                                            | Parallelism in Computer Graphics4                                                                                                                                                                                                                                                                                  |

| 1.2        | Resear                                                           | rch Motivation ······4                                                                                                                                                                                                                                                                                             |

| 1.3        | Resear                                                           | ch Aims and Objectives5                                                                                                                                                                                                                                                                                            |

| 1.4        |                                                                  | rch Methodology 6                                                                                                                                                                                                                                                                                                  |

| 1.5        | Thesis                                                           | Organisation 7                                                                                                                                                                                                                                                                                                     |

| Chapter 2: |                                                                  | ture Reviews                                                                                                                                                                                                                                                                                                       |

| 2.1        |                                                                  | e Studies of ESs ······9                                                                                                                                                                                                                                                                                           |

| 2.2        | Investi                                                          |                                                                                                                                                                                                                                                                                                                    |

|            |                                                                  | gation of Hardware Graphics Applications 11                                                                                                                                                                                                                                                                        |

|            | 2.2.1                                                            | GPU Applications 11                                                                                                                                                                                                                                                                                                |

|            | 2.2.1<br>2.2.2                                                   | GPU Applications 11<br>FPGA Applications 12                                                                                                                                                                                                                                                                        |

|            | 2.2.1<br>2.2.2<br>2.2.3                                          | GPU Applications11FPGA Applications12FPGAs vs. GPUs13                                                                                                                                                                                                                                                              |

|            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                                 | GPU Applications11FPGA Applications12FPGAs vs. GPUs13FPGAs vs. CPUs14                                                                                                                                                                                                                                              |

| 2.3        | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Introdu                      | GPU Applications11FPGA Applications12FPGAs vs. GPUs13FPGAs vs. CPUs14ction of OpenGL, OpenGL ES and their Implementations15                                                                                                                                                                                        |

| 2.3<br>2.4 | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Introdu                      | GPU Applications11FPGA Applications12FPGAs vs. GPUs13FPGAs vs. CPUs14ction of OpenGL, OpenGL ES and their Implementations15gation of Traditional Computation Parallelism16                                                                                                                                         |

|            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Introdu                      | GPU Applications       11         FPGA Applications       12         FPGAs vs. GPUs       13         FPGAs vs. CPUs       14         ction of OpenGL, OpenGL ES and their Implementations       15         gation of Traditional Computation Parallelism       16         Data Parallelism: SIMD and MIMD       17 |

|            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Introdu                      | GPU Applications11FPGA Applications12FPGAs vs. GPUs13FPGAs vs. CPUs14ction of OpenGL, OpenGL ES and their Implementations15gation of Traditional Computation Parallelism16Data Parallelism: SIMD and MIMD17Operator Parallelism18                                                                                  |

|            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Introdu<br>Investig<br>2.4.1 | GPU Applications       11         FPGA Applications       12         FPGAs vs. GPUs       13         FPGAs vs. CPUs       14         ction of OpenGL, OpenGL ES and their Implementations       15         gation of Traditional Computation Parallelism       16         Data Parallelism: SIMD and MIMD       17 |

|         | 2.4.5             | Promotion for New Concept Introduction to Parallelism 20    |

|---------|-------------------|-------------------------------------------------------------|

| 2.5     | 5 Related         | Studies in Surface Modelling and Editing 20                 |

| 2.6     | 6 Chapte          | r Summary 25                                                |

|         |                   |                                                             |

| Chapter | <u>3:</u> An Inte | egrated Hybrid Embedded System 26                           |

|         |                   |                                                             |

| 3.1     | I Feature         | es and Principles of ES Design 26                           |

|         | 3.1.1             | Physical Requirements for ESs                               |

|         | 3.1.2             | Analysis for ES Design 28                                   |

|         | 3.1.3             | Challenges for ES Design 34                                 |

|         | 3.1.4             | Prospective Principles for ES Design 36                     |

| 3.2     | 2 Reasor          | s for Choosing an ES as this Project Platform               |

| 3.3     | B Environ         | ment Structure of this Research 42                          |

|         | 3.3.1             | Embedded Hardware System······ 43                           |

|         | 3.3.2             | Device Driver Functions 44                                  |

|         | 3.3.3             | Hardware Abstraction Level 46                               |

|         | 3.3.4             | ANSI C Library and HAL API 47                               |

|         | 3.3.5             | Operating System 51                                         |

|         | 3.3.6             | Applications 51                                             |

| 3.4     | 4 Chapte          | r Summary 51                                                |

|         |                   |                                                             |

| Chapter | <u>4:</u> FPGA    | based Embedded Hardware System for Graphics Applications 53 |

|         |                   |                                                             |

| 4.1     | I Traditio        | nal ES Development 53                                       |

| 4.2     | 2 FPGA            | Device Evolution and Applications 55                        |

|         | 4.2.1             | FPGA Evolution History 55                                   |

|         | 4.2.2             | FPGA Features and Reprogrammable Technologies 55            |

|         | 4.2.3             | Architecture Diversity in FPGA-based Systems 58             |

| 4.3     | B FPGA-           | based ES Development 59                                     |

| 4.4     | FPGA [            | Device for this Research                                    |

|         | 4.4.1             | LABs and LEs ······ 61                                      |

|         | 4.4.2             | M9K Memory Blocks                                           |

|         | 4.4.3             | Multiplier Blocks and DSPs 61                               |

|         | 4.4.4             | PLLs and Global Clock Networks 62                           |

|         | 4.4.5             | I/O Banks 62                                                |

|         | 4.4.6             | Embedded Processors 62                                      |

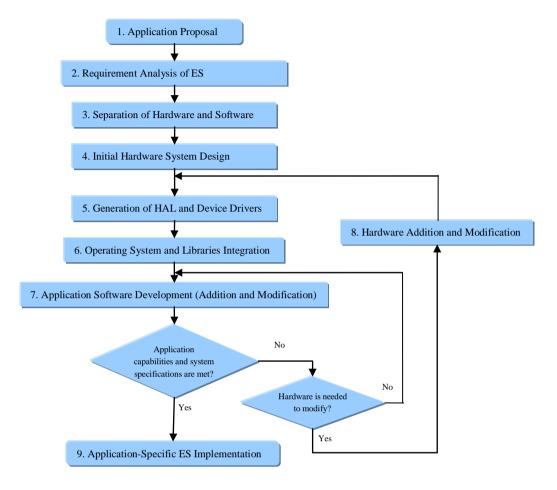

| 4.5     | 5 FPGA-l          | based ES Design Flow                                        |

|         | 4.5.1             | Application Proposal                                        |

|         | 4.5.2             | Requirement Analysis of ES 63                               |

|            | 4.5.3    | Separation of Hardware and Software                      | ·· 64 |

|------------|----------|----------------------------------------------------------|-------|

|            | 4.5.4    | Initial Hardware System Design                           | ·· 64 |

|            | 4.5.5    | Generation of HAL and Device Drivers                     | ·· 64 |

|            | 4.5.6    | Operating System and Libraries Integration               | ·· 64 |

|            | 4.5.7    | Application Software Development                         | 64    |

|            | 4.5.8    | Hardware Addition and Modification                       | 65    |

|            | 4.5.9    | Application-Specific ES Implementation                   | 65    |

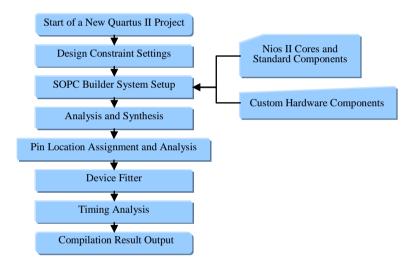

| 4.6        | FPGA-    | based ES Design with Altera Facilities                   | 65    |

|            | 4.6.1    | Start of a Quartus II Project and Design Constraints     | 66    |

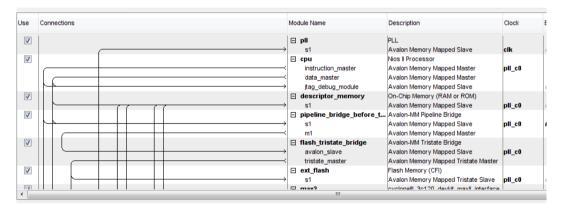

|            | 4.6.2    | SOPC Builder System Setup                                | 67    |

|            | 4.6.3    | Analysis and Synthesis                                   | 67    |

|            | 4.6.4    | Pin Location Assignment and Analysis                     | 68    |

|            | 4.6.5    | Device Fitter                                            | 69    |

|            | 4.6.6    | Timing Analysis ·····                                    | 70    |

|            | 4.6.7    | Compilation Result Output                                | 70    |

|            | 4.6.8    | About Go-Back ·····                                      | 71    |

| 4.7        | Setup    | of FPGA-based Embedded Hardware System for Graphics      |       |

|            | Applic   | ations                                                   | 71    |

|            | 4.7.1    | Nios II Processer Settings                               | 71    |

|            | 4.7.2    | System Clock Settings                                    | 72    |

|            | 4.7.3    | DDR2 SDRAM Memory Controller Settings                    | 73    |

|            | 4.7.4    | CFI Flash Memory Controller Settings                     | 73    |

|            | 4.7.5    | JTAG UART Settings                                       | 74    |

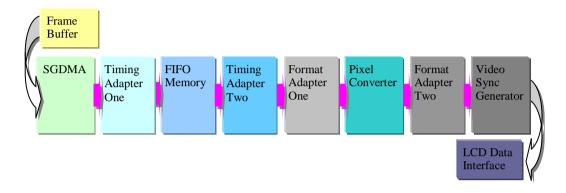

|            | 4.7.6    | Settings for LCD Controller Interface and Video Pipeline | 74    |

| 4.8        | Challen  | nges and Features of the FPGA-based ES                   | 76    |

| 4.9        | Chapte   | r Summary                                                | 76    |

|            |          |                                                          |       |

| Chapter 5: | Integra  | ating Mesa-OpenGL into FPGA-based ES                     | 78    |

|            |          |                                                          |       |

| 5.1        | OpenG    | L                                                        | 79    |

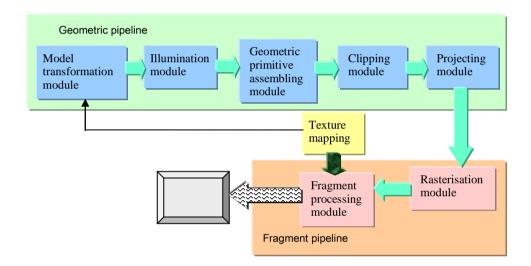

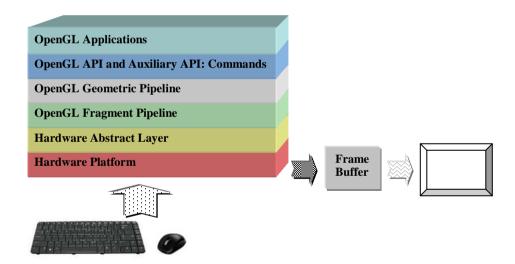

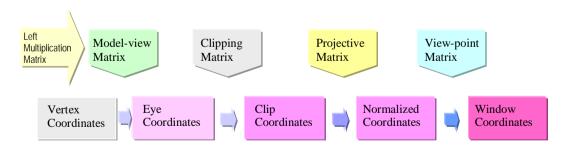

|            | 5.1.1    | Geometric Pipeline                                       | 79    |

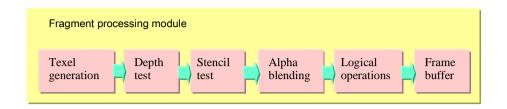

|            | 5.1.2    | Fragment Pipeline                                        | 81    |

|            | 5.1.3    | Rendering Flow of an OpenGL Interactive Application      | 84    |

| 5.2        | OpenG    | L ES                                                     | 85    |

|            | 5.2.1    | Versions and Profiles of OpenGL ES ·····                 | 85    |

|            | 5.2.2    | OpenGL ES Implementations                                | 87    |

| 5.3        | Differer | nt Roles in OpenGL ES                                    | . 87  |

|            | 5.3.1    | OpenGL ES Standard Setter Role                           | 88    |

|            | 5.3.2    | OpenGL ES Implementer Role ·····                         | 93    |

|            |          |                                                          |       |

|                | 5.3.3            | OpenGL ES Application Developer Role 93                          |

|----------------|------------------|------------------------------------------------------------------|

| 5.4            | 1 Mesa-          | OpenGL····· 95                                                   |

|                | 5.4.1            | Introduction of Mesa OpenGL 96                                   |

|                | 5.4.2            | General OpenGL Implementation                                    |

| 5.5            | 5 Implen         | nentation of Mesa-OpenGL on FPGA-based ES107                     |

|                | 5.5.1            | Bézier Curves and Surfaces ·····107                              |

|                | 5.5.2            | Window System Interface 110                                      |

|                | 5.5.3            | Fixed Point Arithmetic111                                        |

| 5.6            | 6 Chapte         | er Summary ······112                                             |

|                |                  |                                                                  |

| Chapter        | <u>6:</u> Parall | elism Implementation in FPGA-based ES114                         |

| 6.1            | l Classif        | ication of Traditional Parallelism114                            |

| 6.2            | 2 Analys         | is on Processing Features in Parallelism115                      |

|                | 6.2.1            | Two Perspectives: Application's View and Hardware's View115      |

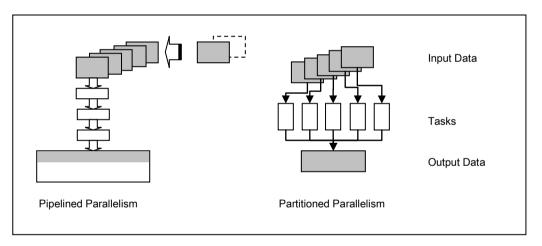

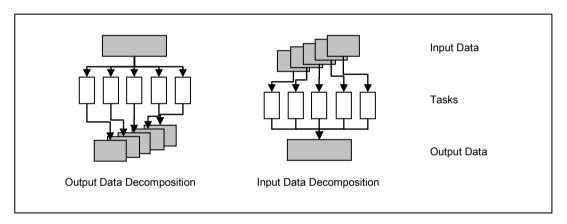

|                | 6.2.2            | Two Styles: Pipelined Parallelism and Partitioned Parallelism117 |

| 6.3            | B Metho          | dologies of Processing in Parallel118                            |

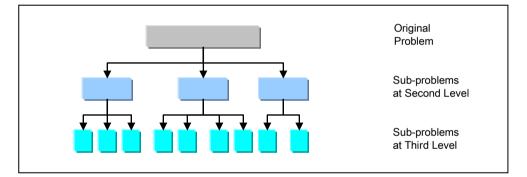

|                | 6.3.1            | Computation Decomposition at High Level118                       |

|                | 6.3.2            | Parallelism Mapping at High Level······123                       |

|                | 6.3.3            | Expansion on Parallelism Decomposition126                        |

| 6.4            | 1 Paralle        | lism in the Graphics Processing in this Research128              |

|                | 6.4.1            | Pipeline Effect129                                               |

|                | 6.4.2            | Timing and Data Format Matching in Pipelining130                 |

|                | 6.4.3            | Co-processor in FPGA-based ES132                                 |

| 6.5            | 5 Chapte         | er Summary ······134                                             |

| <u>Chapter</u> | <u>7:</u> Novel  | Algorithm for Surface Modelling and Editing, PAMA135             |

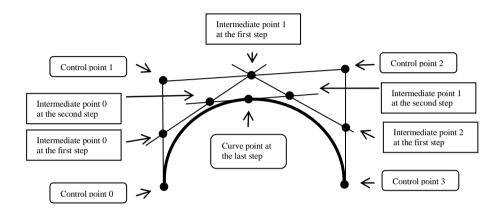

| 7.1            | l Prelim         | nary 136                                                         |

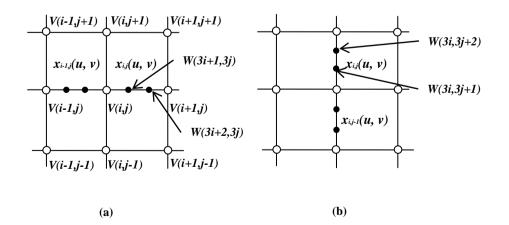

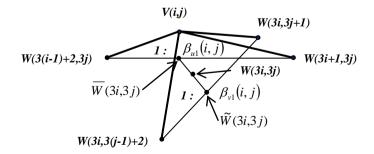

| 7.2            | 2 Progre         | ssive and Mixing Algorithm, PAMA137                              |

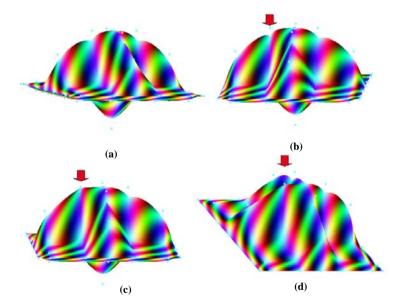

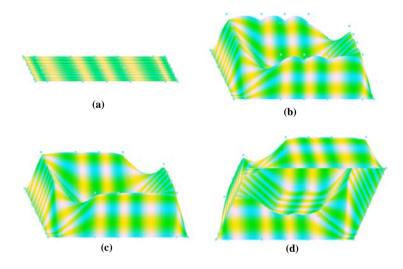

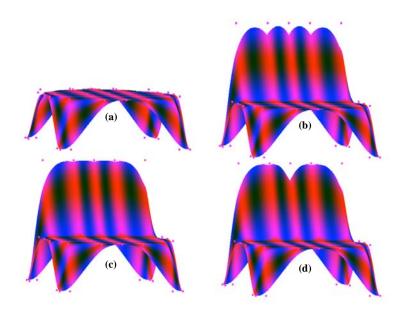

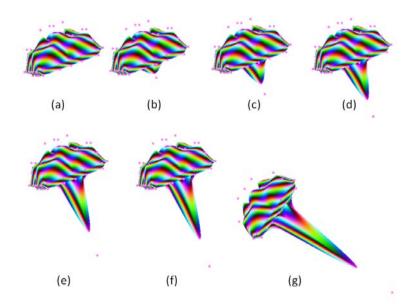

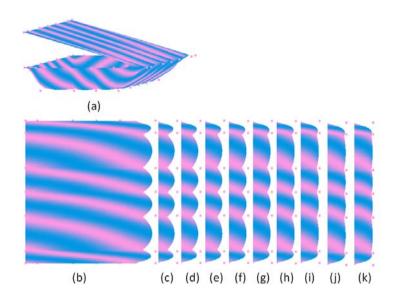

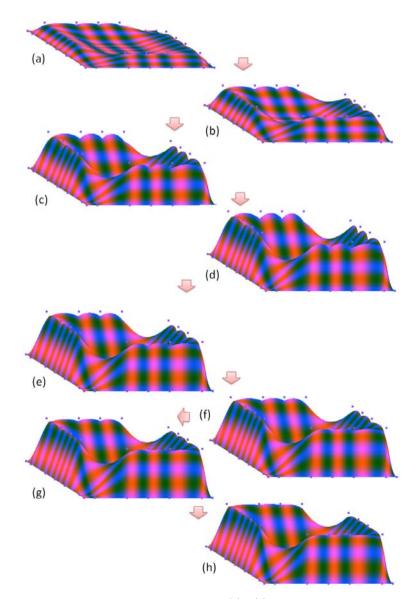

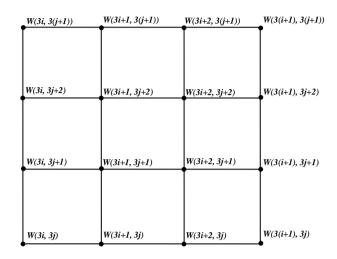

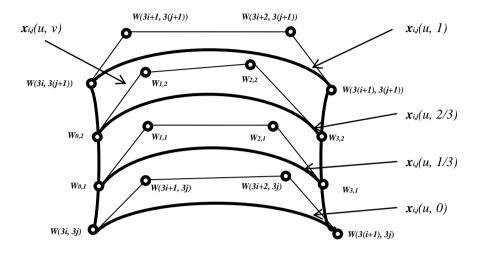

| 7.3            | 3 Surfac         | e Modelling and Editing with PAMA·····142                        |

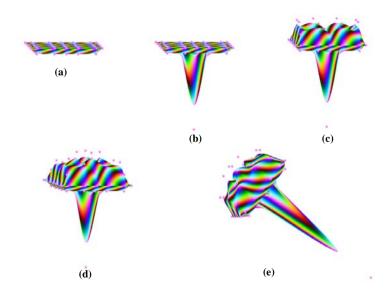

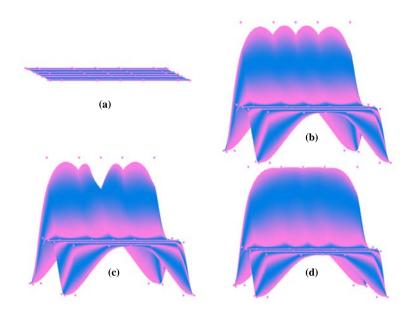

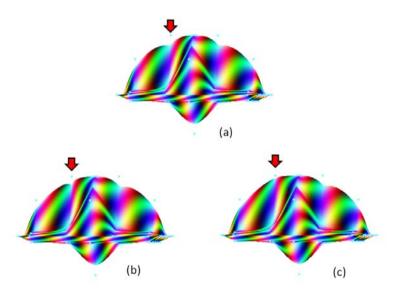

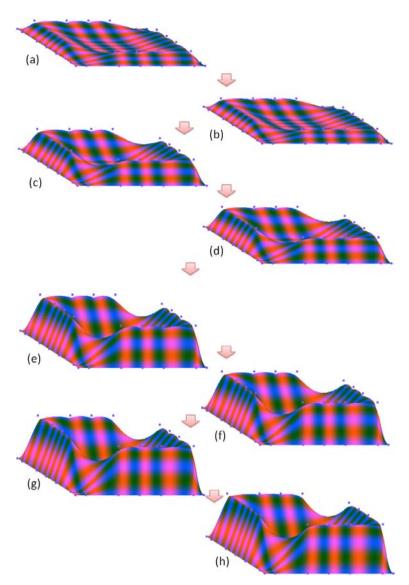

| 7.4            | 1 Differe        | nt Effects of Shape Parameters148                                |

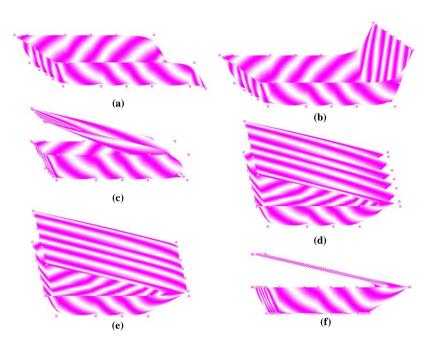

|                | 7.4.1            | Skewing in u or v Directions148                                  |

|                | 7.4.2            | Tenseness in u or v Directions ······149                         |

|                | 7.4.3            | Skewing in Both u and v Directions149                            |

|                | 7.4.4            | Tenseness in Both u and v Directions150                          |

| 7.5            | 5 Novel          | Features of PAMA152                                              |

| 7.6            | 6 Chapte         | er Summary ······155                                             |

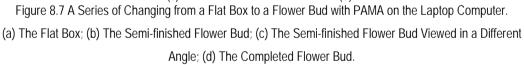

| Chapt        | er 8:        | Results of Surface Modelling and Editing with PAMA on FPGA-based     |

|--------------|--------------|----------------------------------------------------------------------|

|              | ES…          |                                                                      |

|              |              |                                                                      |

|              | 8.1          | Verification Methodology157                                          |

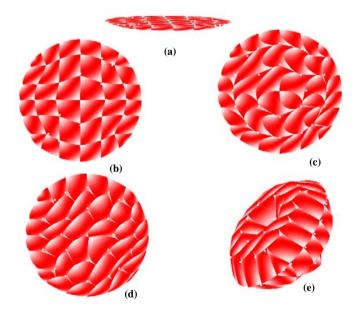

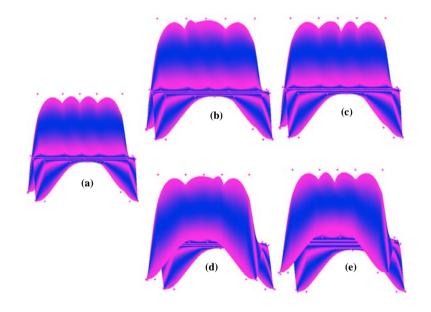

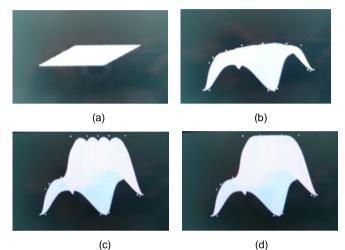

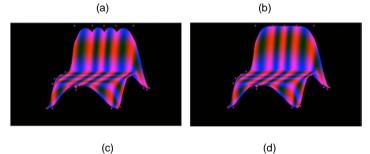

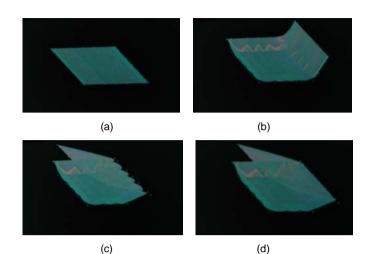

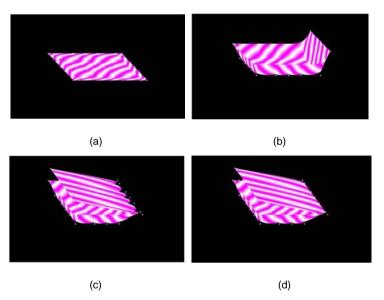

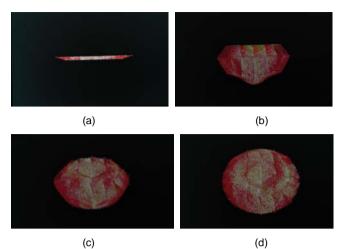

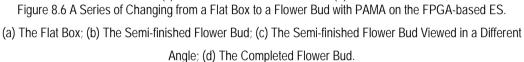

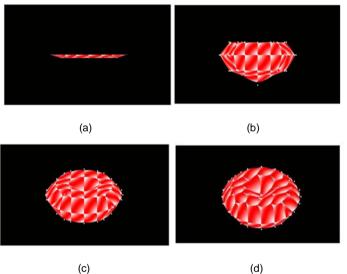

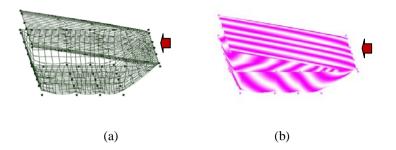

|              | 8.2          | Results of PAMA Applications in the FPGA-based ES158                 |

|              | 8.3          | Discussions of Graphics Applications on FPGA-base ES161              |

|              |              | 8.3.1 Distinction between Two Hardware Systems162                    |

|              |              | 8.3.2 Difference between Two OpenGL Implementations163               |

|              |              | 8.3.3 Storage and Computing Costs of PAMA164                         |

|              | 8.4          | Chapter Summary                                                      |

| <u>Chapt</u> | <u>er 9:</u> | Future Work ······167                                                |

|              | 9.1          | Future Work for Methodology of Hybrid Design of Application-specific |

|              |              | ESs with Software and Hardware Components167                         |

|              | 9.2          | Future Work for FPGA-based ESs ·····168                              |

|              | 9.3          | Future Work for OpenGL Implementations168                            |

|              | 9.4          | Future Work for Parallel Processing169                               |

|              | 9.5          | Future Work for PAMA169                                              |

| <u>Chapt</u> | <u>er 10</u> | Conclusions 170                                                      |

|              | 10.1         | Conclusions of Methodology for Hybrid Design and Implementation of   |

|              |              | ESs 170                                                              |

|              | 10.2         | Conclusions of FPGA-based ES171                                      |

|              | 10.3         | Conclusions of Mesa-OpenGL Implementation171                         |

|              | 10.4         | Conclusions of Parallel Processing172                                |

|              | 10.5         | Conclusions of PAMA172                                               |

| <u>Apper</u> | <u>ndix:</u> | Continuities of PAMA173                                              |

|              | A.1          | Parametric Continuities and Geometric Continuities                   |

|              | A.2          | Geometric Properties of Bézier Curves176                             |

|              | A.3          | Composite Bézier Surfaces                                            |

|              | A.4          | First-order Geometric Continuity of Composite Bézier Surfaces        |

|              | A.5          | Tangent Planes of a Bézier Surface187                                |

|              | A.6          | Analysis of First Order Geometric Continuities                       |

|              | A.7          | Construction of Control Points on Common Boundaries with PAMA193     |

|              | A.8          | Twists and Constructions for Corner Points with PAMA196              |

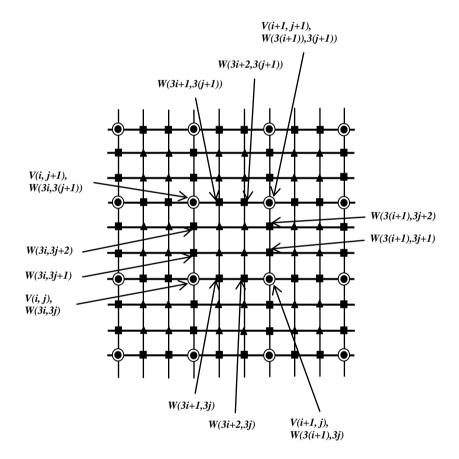

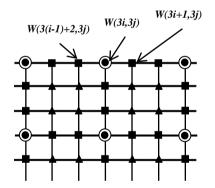

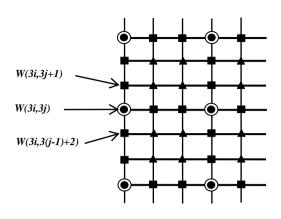

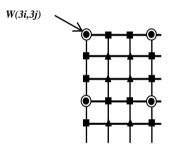

| A.9 Constructions of Inside Points with PAMA199 |

|-------------------------------------------------|

| A.10 Summarising PAMA's Continuities200         |

| A.10.1 For G <sup>0</sup>                       |

| A.10.2 For G <sup>1</sup>                       |

| A.10.3 For G <sup>2</sup>                       |

| A.10.4 For C <sup>1</sup> 201                   |

| References ······203                            |

| List of Publications (2009 to 2013)······212    |

| <u>Table 2.1:</u> | Comparisons be | tween FPC  | GAs and CPUs   | ••••  |         |             | ••••• | • 14  |

|-------------------|----------------|------------|----------------|-------|---------|-------------|-------|-------|

| <u>Table 2.2:</u> | Comparisons an | nong Three | e Surface Mode | lling | and Edi | ting Method | s     | ·· 23 |

| Table 8.1:        | Comparisons    | between    | Environments   | of    | Laptop  | Computer    | and   |       |

| FPG               | A-based ES     |            |                |       |         |             |       | 162   |

## LIST OF FIGURES

| Figure 1.1:                                                                                                                                                                                                                                           | Structure of the Project8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

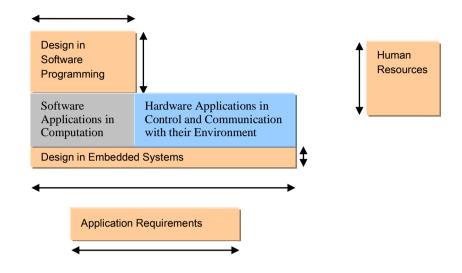

| Figure 3.1:                                                                                                                                                                                                                                           | Comparisons of Application Requirements and Human Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| betwe                                                                                                                                                                                                                                                 | een ES and Software Programming Designs. Horizontal Widths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Represent Application Requirements; Vertical Heights Represent Human                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Reso                                                                                                                                                                                                                                                  | urces for Research and Development. The Wider Width of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                                                                                                                                                                                       | angle of Design in ESs Shows the Wider Application Diversity of ESs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                                                                                                                                                                                                                       | Thinner Height of the Rectangle of Design in ESs Shows the Smaller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Sepa<br><u>Figure 3.2:</u>                                                                                                                                                                                                                            | rate Human Resources in ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

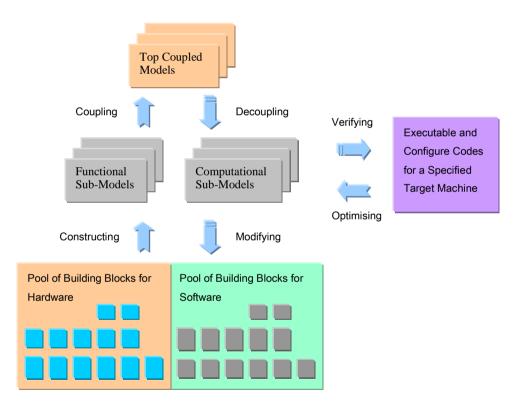

| Figure 3.3:                                                                                                                                                                                                                                           | Hierarchy of Design Process for ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

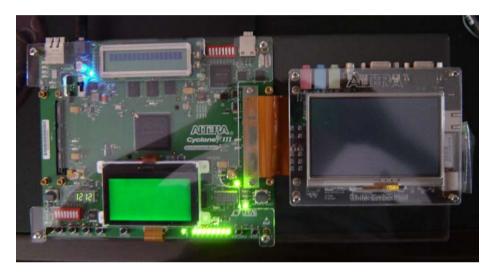

| Figure 3.4:                                                                                                                                                                                                                                           | Altera Cyclone III ESs Development Board 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

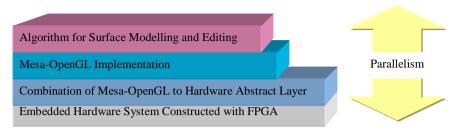

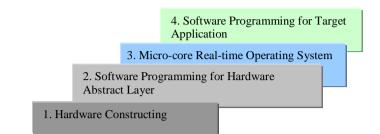

| Figure 3.5:                                                                                                                                                                                                                                           | Environment Structure of the Research and its Expansion 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Figure 3.6:                                                                                                                                                                                                                                           | Block Diagram of the ES Customised for the Research 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Figure 3.7:                                                                                                                                                                                                                                           | Graphics Pipeline in FPGA-based ES 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                       | Four User-Defined Buttons on Altera Cyclone III ESs Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                                                       | 50<br>50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

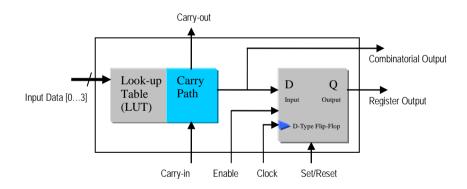

|                                                                                                                                                                                                                                                       | LE's Composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                                                                                                       | Programmable Interconnect Network ····· 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

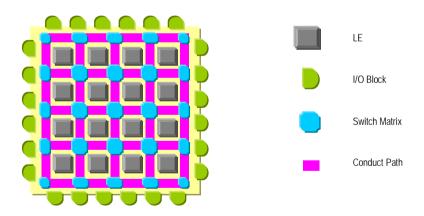

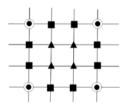

| Figure 4.3:                                                                                                                                                                                                                                           | Generic Structure of an FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Figure 4.4:                                                                                                                                                                                                                                           | Development Flow of Combining Hardware and Software for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Figure 4.4:                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| <u>Figure 4.4:</u><br>Applie                                                                                                                                                                                                                          | Development Flow of Combining Hardware and Software for cation-specific ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Figure 4.4:<br>Applic<br>Figure 4.5:                                                                                                                                                                                                                  | Development Flow of Combining Hardware and Software for<br>cation-specific ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Figure 4.4:<br>Applie<br>Figure 4.5:<br>Figure 4.6:                                                                                                                                                                                                   | Development Flow of Combining Hardware and Software for<br>cation-specific ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

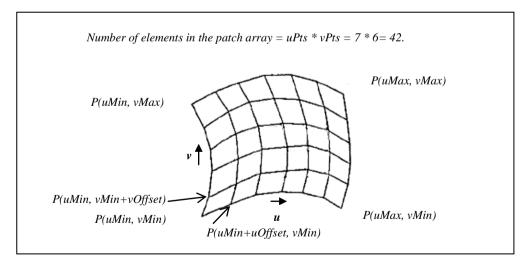

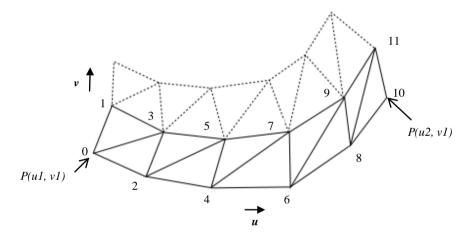

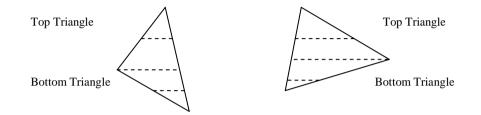

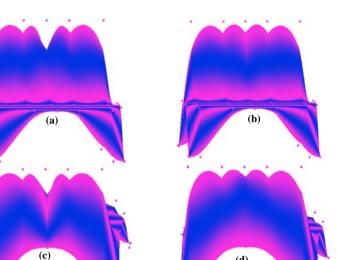

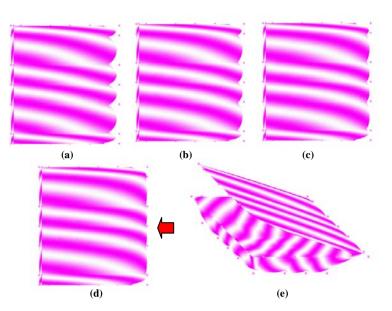

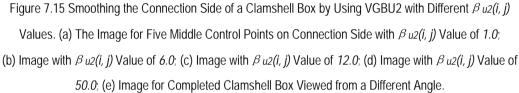

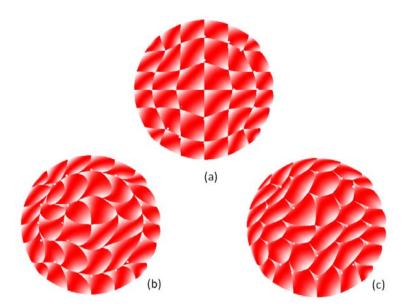

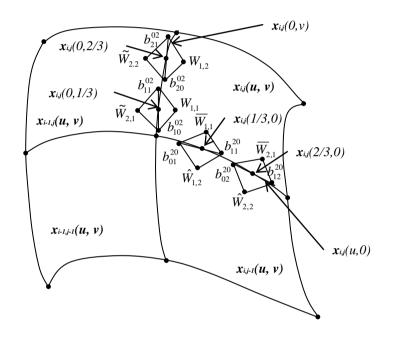

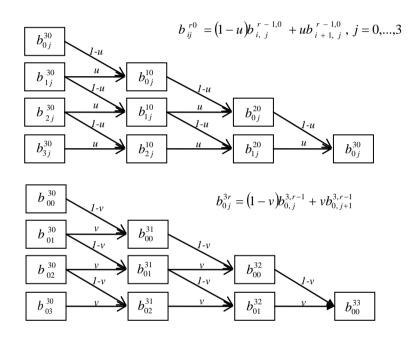

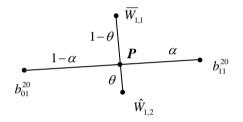

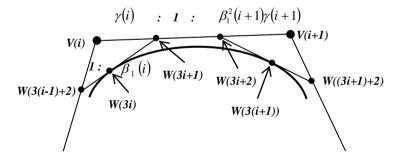

| Figure 4.4:<br>Applie<br>Figure 4.5:<br>Figure 4.6:<br>Figure 4.7:                                                                                                                                                                                    | Development Flow of Combining Hardware and Software for<br>cation-specific ESs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |