# Volume 1

# RAPID CLOCK RECOVERY ALGORITHMS FOR DIGITAL MAGNETIC RECORDING AND DATA COMMUNICATIONS

by

# PAUL MICHAEL SMITHSON

A thesis submitted to the University of Plymouth in partial fulfilment for the degree of

# DOCTOR OF PHILOSOPHY

School of Electronic, Communication and Electrical Engineering

Faculty of Technology

February 1999

# LIBRARY STORE

REFERENCE ONLY

| UNIV       | REITY OF PLYMOUTH |

|------------|-------------------|

| itom No.   | 900 60            |

| Date       | 1 1 AUG 1999 T    |

| Class No.  | T621.3822 SMI     |

| Contl. No. | X703911465X       |

| L          | BRARY SERVICES    |

# Author's declaration

At no time during the registration for the degree of Doctor of Philosophy has the author been registered for any other University award.

Several IEE and IEEE colloquia's and international conferences have been attended.

Seven refereed papers have been published and presented at international conferences, relevant publications of which are reproduced in Appendix 11.

In addition this research has been included, and the author referenced, within the text of two published technical textbooks [1] and [2].

Signed

Date .

iv

# **Table of Contents**

# Volume 1

| Copyright Declaration                          | i    |

|------------------------------------------------|------|

| Abstract                                       | ii   |

| Acknowledgement                                | iii  |

| Author's Declaration                           | iv   |

| Table of Contents                              | v    |

| List of Figures for Volume 1                   | X    |

| List of Tables for Volume 1                    | xvi  |

| Glossary of Abbreviations                      | xvii |

| Introduction                                   | 1    |

| 1. Background to the investigation             | 9    |

| 1.1. Clock recovery architectures              | 10   |

| 1.1.1. High-Q passive resonator clock recovery | 12   |

| 1.1.2. PLL clock recovery                      | 15   |

| 1.1.3. Quadricorrelator                        | 21   |

| 1.1.4. Gated oscillator clock recovery         | 24   |

| 1.1.5. Maximum Likelihood                      | 26   |

| 1.1.6. Early-late synchroniser                 | 30   |

# TABLE OF CONTENTS

| 1.1.7. 541                                                                                                                                                    | mmary of clock recovery architectures                                                                               |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------|

| 1.2. Channel                                                                                                                                                  | coding                                                                                                              | 37           |

| 1.2.1. Scr                                                                                                                                                    | ambled NRZ                                                                                                          | 39           |

| 1.2.2. Red                                                                                                                                                    | cording codes                                                                                                       | 42           |

| 1.2.2.1.                                                                                                                                                      | NRZI coding                                                                                                         | 46           |

| 1.2.2.2.                                                                                                                                                      | Manchester code                                                                                                     | 48           |

| 1.2.2.3.                                                                                                                                                      | Miller code                                                                                                         | 49           |

| 1.2.2.4.                                                                                                                                                      | Miller <sup>2</sup> code                                                                                            | 50           |

| 1.2.2.5.                                                                                                                                                      | RLL 2,7 code                                                                                                        | 52           |

| 1.2.2.6.                                                                                                                                                      | Summary of recording codes                                                                                          | 53           |

|                                                                                                                                                               | CVI a see A see 2                                                                                                   |              |

|                                                                                                                                                               | Chapter 2                                                                                                           |              |

| 2. DSP-based                                                                                                                                                  | Cnapter 2                                                                                                           | 56           |

|                                                                                                                                                               | -                                                                                                                   |              |

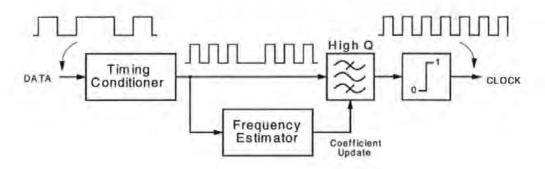

| 2.1. System of                                                                                                                                                | d clock recovery                                                                                                    | 59           |

| 2.1. System of 2.1.1. Tin                                                                                                                                     | d clock recoverydescription                                                                                         | 60           |

| 2.1. System of 2.1.1. Tin 2.2. Clock re                                                                                                                       | d clock recoverydescription                                                                                         | 60<br>63     |

| 2.1. System of 2.1.1. Tin 2.2. Clock re 2.3. Simulati                                                                                                         | d clock recoverydescriptionning conditionerecovery filter theory                                                    |              |

| <ul><li>2.1. System 6</li><li>2.1.1. Tin</li><li>2.2. Clock re</li><li>2.3. Simulati</li><li>2.3.1. Sin</li></ul>                                             | d clock recovery                                                                                                    |              |

| <ul><li>2.1. System 6</li><li>2.1.1. Tin</li><li>2.2. Clock re</li><li>2.3. Simulati</li><li>2.3.1. Sin</li></ul>                                             | description  ning conditioner  ecovery filter theory  nulation model  nulation results                              |              |

| <ul> <li>2.1. System 6</li> <li>2.1.1. Tin</li> <li>2.2. Clock re</li> <li>2.3. Simulati</li> <li>2.3.1. Sin</li> <li>2.3.2. Sin</li> </ul>                   | description  ming conditioner  ecovery filter theory  nulation model  nulation results  Acquisition performance     |              |

| <ul> <li>2.1. System 6</li> <li>2.1.1. Tin</li> <li>2.2. Clock re</li> <li>2.3. Simulati</li> <li>2.3.1. Sin</li> <li>2.3.2. Sin</li> <li>2.3.2.1.</li> </ul> | description  ming conditioner  ecovery filter theory  mulation model  Acquisition performance  Flywheel performance | 596063707171 |

# TABLE OF CONTENTS

| 2.5. FPGA Implementation               | 87  |

|----------------------------------------|-----|

| 2.5.1. Quantization                    | 90  |

| 2.5.2. Application                     | 94  |

| Chapter 3                              |     |

| 3. Adaptive clock recovery             | 96  |

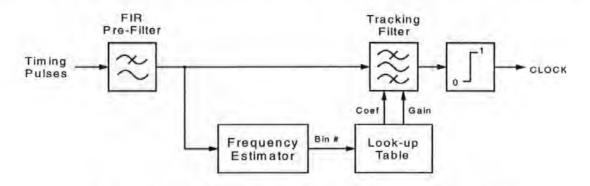

| 3.1. System description                | 99  |

| 3.1.1. Tracking filter gain            | 101 |

| 3.1.2. Detection filter symmetry       | 103 |

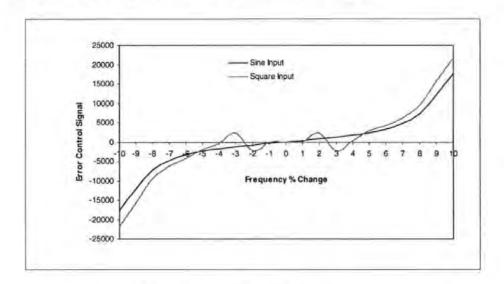

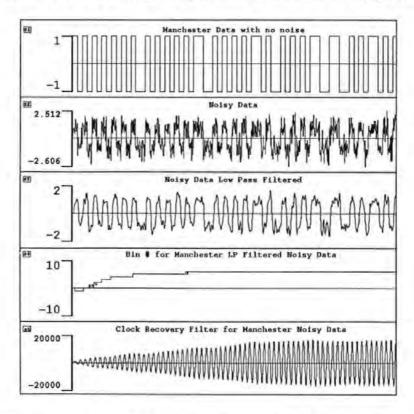

| 3.1.3. Tracking control - Sine Input   | 110 |

| 3.1.3.1. Test simulations – Sine Input | 116 |

| 3.1.4. Tracking control – Data input   | 119 |

| 3.2. Simulations                       | 126 |

| 3.2.1. Simulation model                | 127 |

| 3.2.2. Simulation results              |     |

| 3.2.2.1. Acquisition performance       | 130 |

| 3.2.2.2. Flywheel performance          | 135 |

| 3.2.2.3. Tracking performance          | 139 |

| Chapter 4                              |     |

| 4. OFFT-based clock recovery           | 143 |

| 4.1. The OFFT algorithm                | 145 |

| 4.2. Simulations                       | 151 |

# TABLE OF CONTENTS

| 4.3. Test apparatus                              | 154 |

|--------------------------------------------------|-----|

| 4.3.1. DSP software implementation               | 158 |

| 4.3.2. Real-time testing                         | 163 |

| Chapter 5                                        |     |

| 5. Discussion of results                         | 165 |

| 5.1. Background summary                          | 165 |

| 5.2. DSP-based clock recovery                    | 169 |

| 5.2.1. Fixed frequency clock recovery system     | 170 |

| 5.2.2. Adaptive tracking clock recovery system   | 171 |

| 5.2.3. Adaptive OFFT-based clock recovery system | 173 |

| 5.2.4. FPGA implementation                       | 175 |

| 5.3. Applications                                | 177 |

| 5.4. Further work                                | 182 |

| Chapter 6                                        |     |

| 6. Conclusions                                   | 183 |

| References                                       | 186 |

| Bibliography                                     | 196 |

# Volume 2

# Appendices

| Table of Contents for Appendices                                | Vol.2. A-i   |

|-----------------------------------------------------------------|--------------|

| List of Figures for Appendices                                  | Vol.2. A-v   |

| List of Tables for Appendices                                   | Vol.2. A-xii |

| Appendix 1: PLL theory                                          | Vol 2 A1     |

| Appendix 2: PLL results                                         |              |

| Appendix 3: Recording codes                                     | Vol.2. A3    |

| Appendix 4: Fixed frequency clock recovery                      | Vol.2. A4    |

| Appendix 5: Fixed frequency clock recovery - Schematic diagrams | Vol.2. A5    |

| Appendix 6: Fixed frequency clock recovery - Real-time DSP      | Vol.2. A6    |

| Appendix 7: Adaptive tracking clock recovery                    | Vol.2. A7    |

| Appendix 8: FFT Derivation                                      | Vol.2. A8    |

| Appendix 9: OFFT-based clock recovery                           | Vol.2. A9    |

| Appendix 10: Dual-processor DSP board                           | Vol.2. A10   |

| Appendix 11: Author's published papers                          | Vol.2. A11   |

# **List of Figures**

| Figure 1 Clock recovery used for synchronous re-timing of data | 3  |

|----------------------------------------------------------------|----|

| Figure 1-1 Clock recovery system                               | 10 |

| Figure 1-2 Optimum re-sampling                                 | 11 |

| Figure 1-3 High-Q passive resonator clock recovery             | 12 |

| Figure 1-4 PLL clock recovery circuit                          | 15 |

| Figure 1-5 Lead-lag digital PLL                                | 17 |

| Figure 1-6 DPLL with DLL phase selection                       | 19 |

| Figure 1-7 Quadricorrelator                                    | 21 |

| Figure 1-8 Gated oscillator clock recovery                     | 24 |

| Figure 1-9 Open-loop MAP-Estimate clock synchroniser           | 27 |

| Figure 1-10 Closed-loop MAP-estimate clock synchroniser        | 28 |

| Figure 1-11 Early-late gate synchroniser                       | 30 |

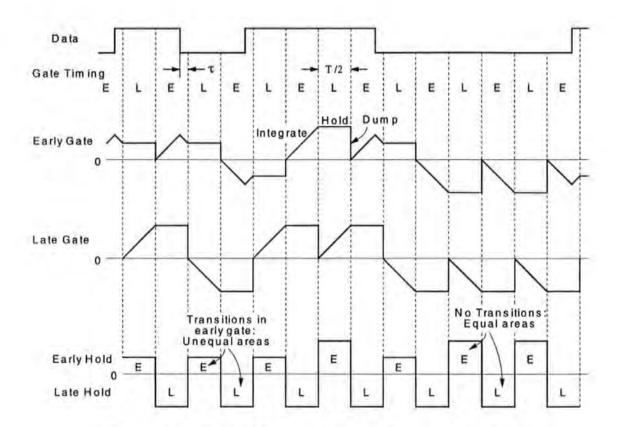

| Figure 1-12 Timing diagram for early-late synchroniser         | 31 |

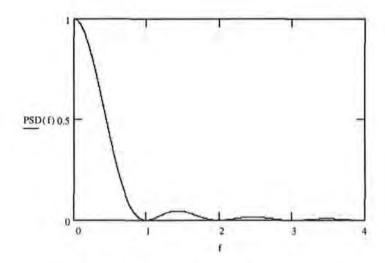

| Figure 1-13 PSD of NRZ data                                    | 38 |

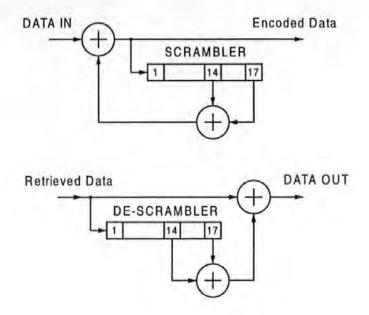

| Figure 1-14 Data scrambler/de-scrambler                        | 40 |

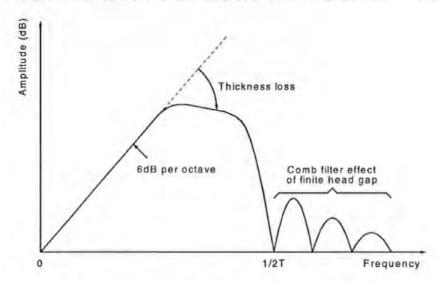

| Figure 1-15 Frequency response of a recording channel          | 43 |

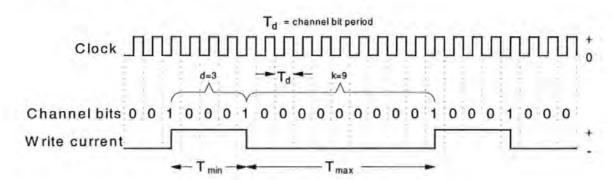

| Figure 1-16 Channel bit convention                             | 44 |

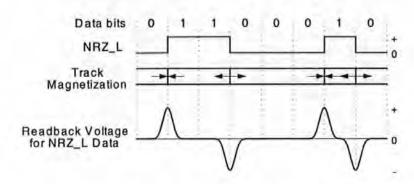

| Figure 1-17 Saturated magnetic recording                       | 46 |

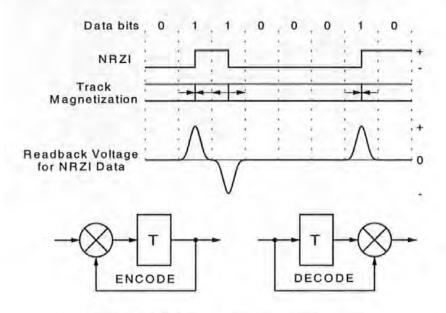

| Figure 1-18 NRZI or differential coding                        | 47 |

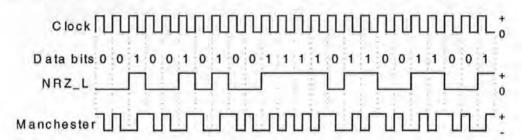

| Figure 1-19 Manchester coding                                  | 18 |

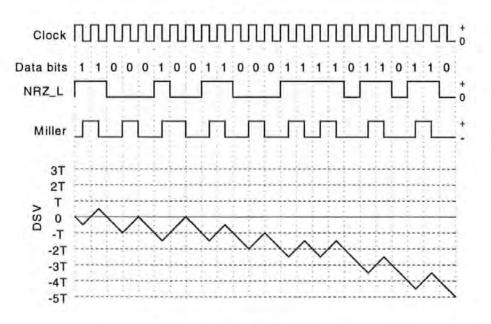

| Figure 1-20 Miller coding                                     | 49 |

|---------------------------------------------------------------|----|

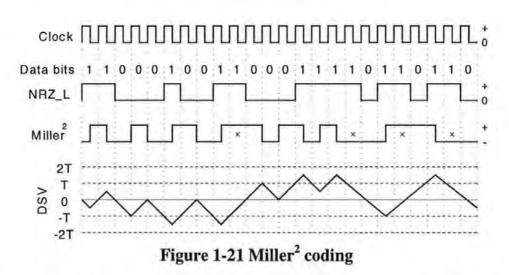

| Figure 1-21 Miller <sup>2</sup> coding                        | 50 |

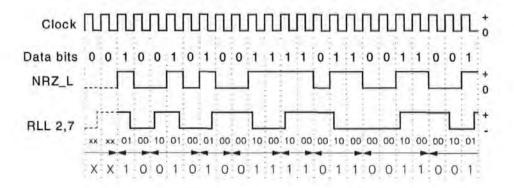

| Figure 1-22 RLL 2,7 coding                                    | 52 |

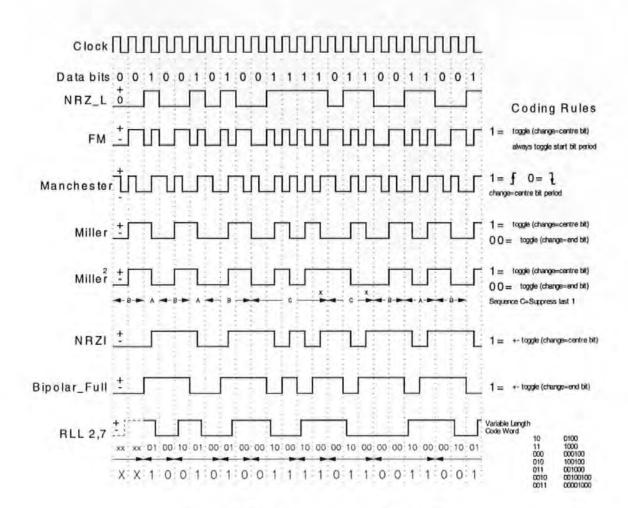

| Figure 1-23 Common recording codes                            | 54 |

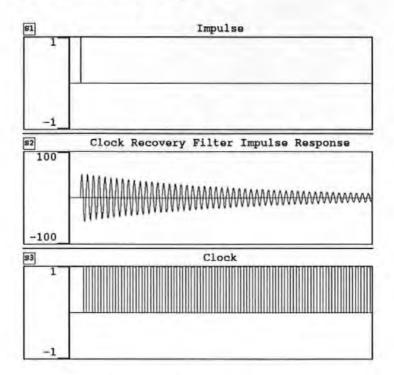

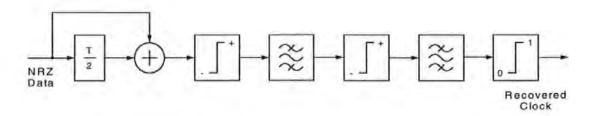

| Figure 2-1 Feed-forward clock recovery system.                | 57 |

| Figure 2-2 IIR filter impulse response                        | 58 |

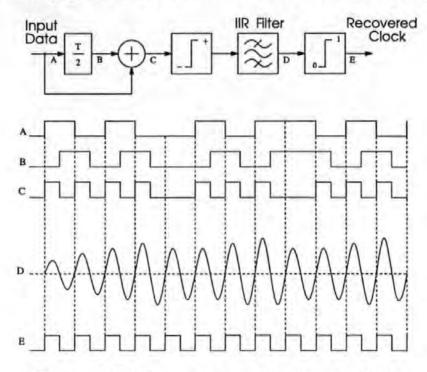

| Figure 2-3 Clock recovery system with waveforms               | 59 |

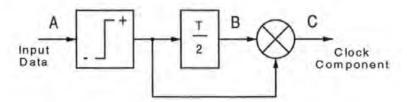

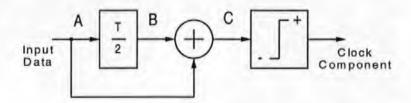

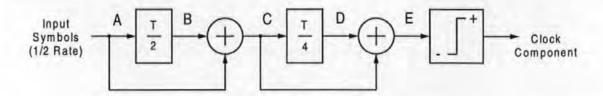

| Figure 2-4 Delay and Multiply conditioner                     | 60 |

| Figure 2-5 Delay and Add conditioner                          | 61 |

| Figure 2-6 Delay and Add Timing                               | 61 |

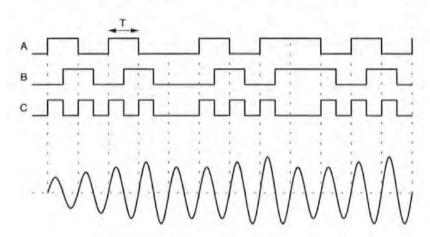

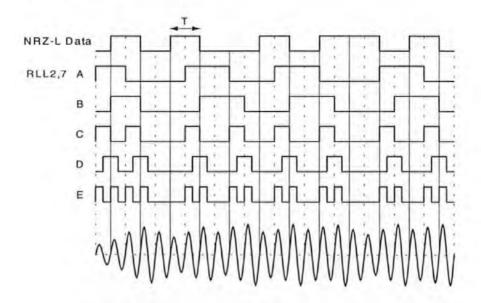

| Figure 2-7 Two stage Delay and Add conditioner                | 62 |

| Figure 2-8 Timing diagram for 1/2 rate codes                  | 62 |

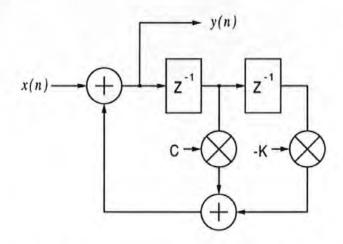

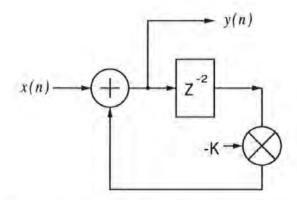

| Figure 2-9 Architecture of clock recovery IIR filter          | 63 |

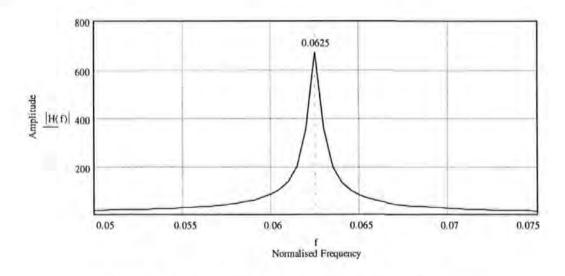

| Figure 2-10 Frequency response of the IIR filter              | 64 |

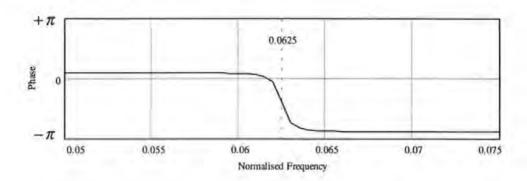

| Figure 2-11 Phase response of the IIR filter                  | 65 |

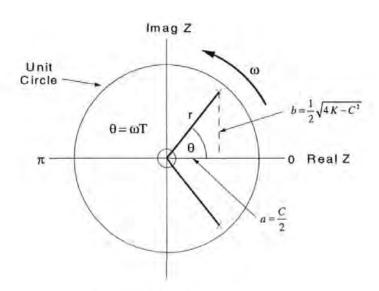

| Figure 2-12 Z-Plane diagram                                   | 66 |

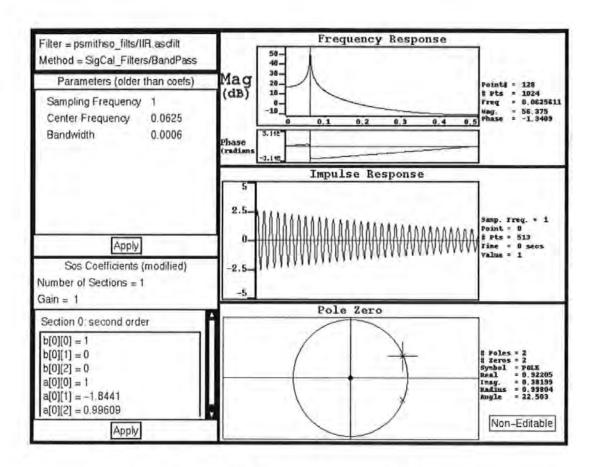

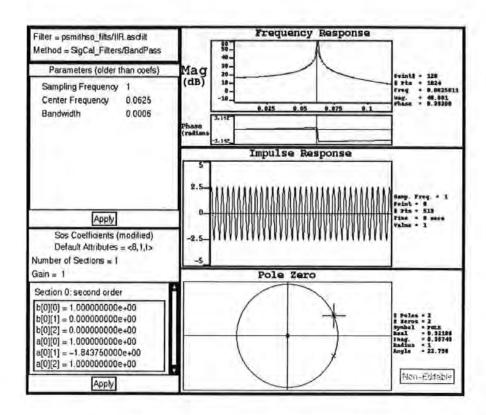

| Figure 2-13 Filter design analysis                            | 68 |

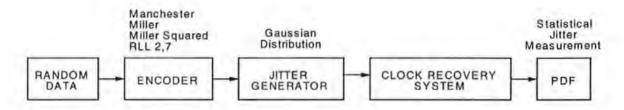

| Figure 2-14 Overview of simulation model                      | 70 |

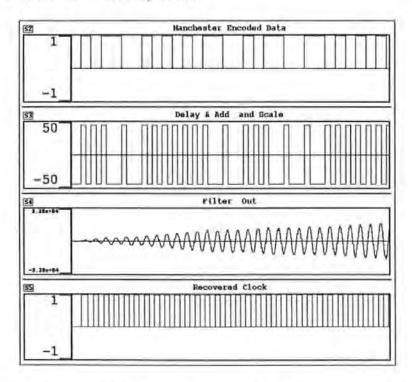

| Figure 2-15 Acquisition performance - Manchester encoded data | 71 |

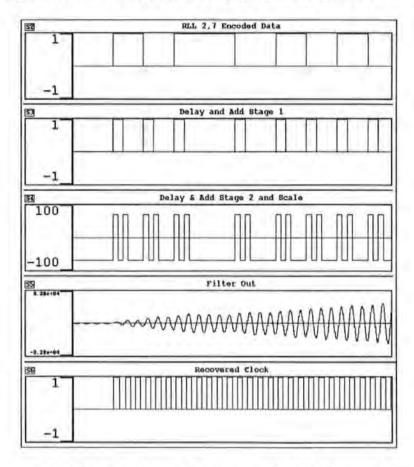

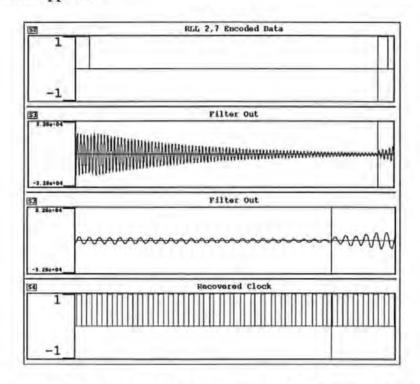

| Figure 2-16 Acquisition performance - RLL 2,7 encoded data    | 72 |

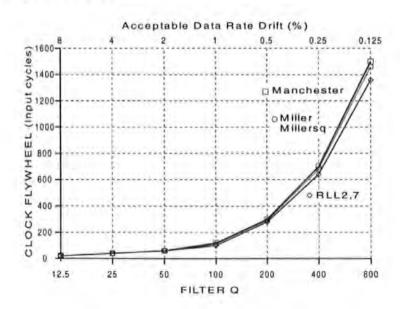

| Figure 2-17 Filter-O versus flywheel                          | 73 |

| Figure 2-18 Flywheel performance - Manchester encoded data     | 74 |

|----------------------------------------------------------------|----|

| Figure 2-19 Flywheel performance - RLL2,7 encoded data         | 75 |

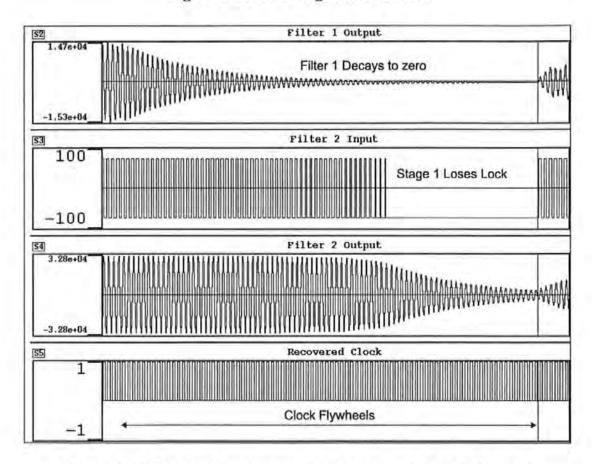

| Figure 2-20 Two-stage filter section                           | 76 |

| Figure 2-21 Flywheel performance - Two stage filter (NRZ data) | 76 |

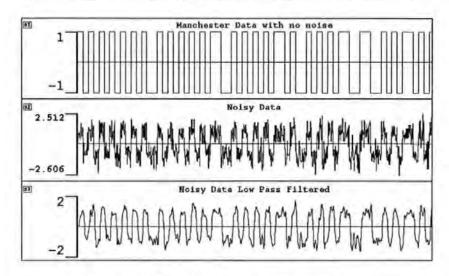

| Figure 2-22 Data with additive noise                           | 77 |

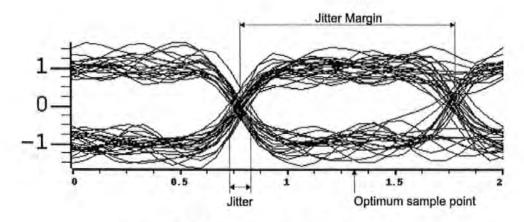

| Figure 2-23 Eye diagram of noisy data                          | 77 |

| Figure 2-24 Acquisition with applied jitter                    | 78 |

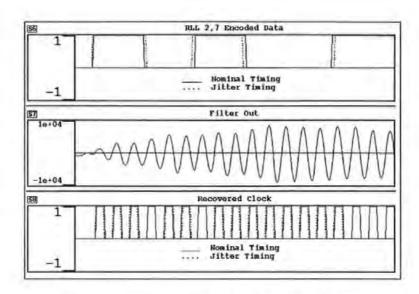

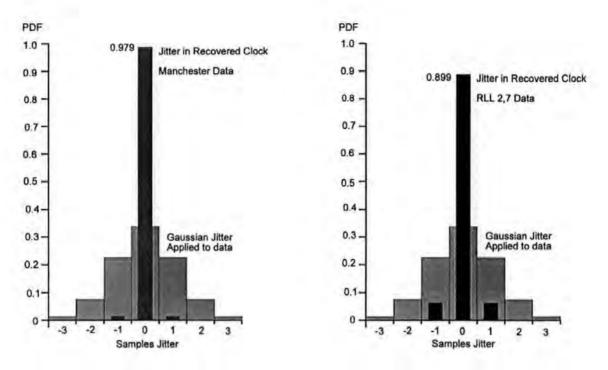

| Figure 2-25 PDF of jitter in the recovered clock               | 79 |

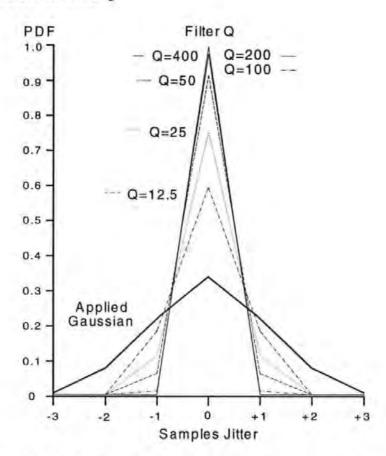

| Figure 2-26 PDF of jitter versus Filter Q - Manchester data    | 80 |

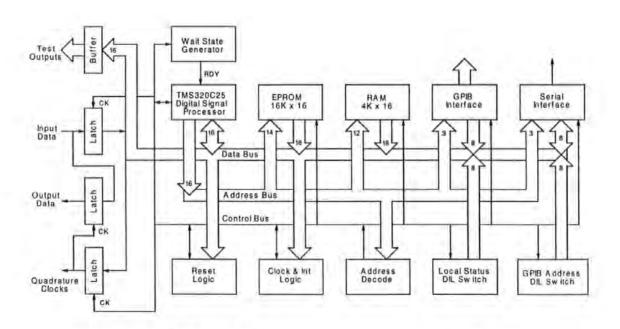

| Figure 2-27 DSP-based clock recovery hardware - Block diagram  | 81 |

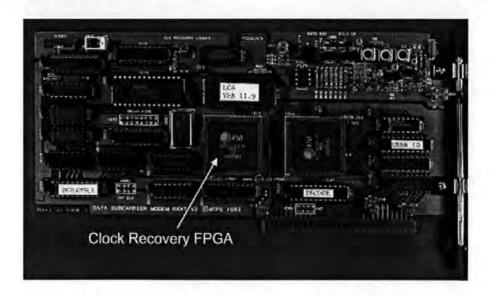

| Figure 2-28 DSP-based clock recovery board                     | 82 |

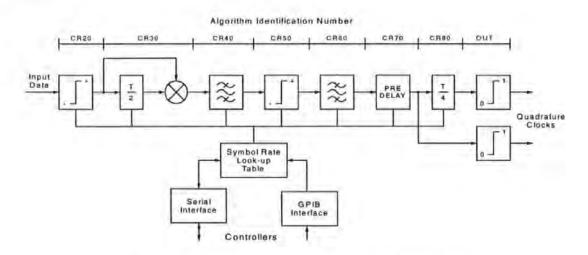

| Figure 2-29 DSP Software algorithm overview                    | 83 |

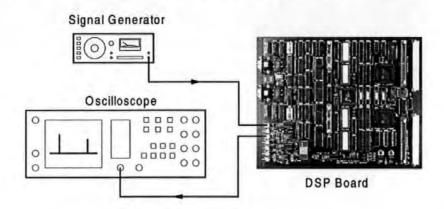

| Figure 2-30 Clock recovery test system                         | 85 |

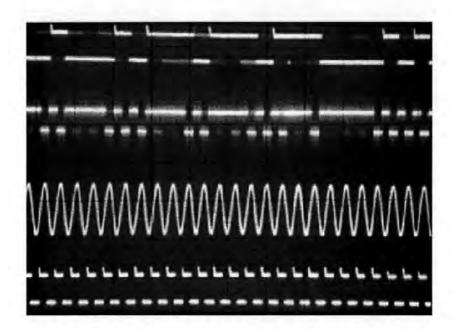

| Figure 2-31 Oscilloscope display of clock recovery signals     | 86 |

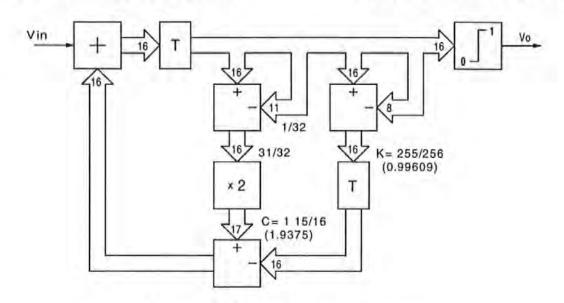

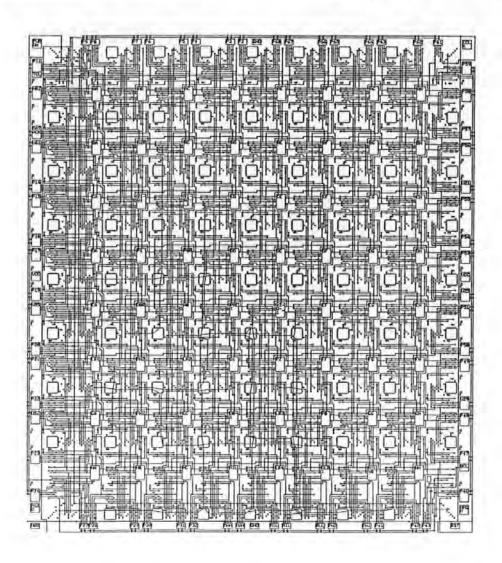

| Figure 2-32 FPGA Filter architecture                           | 88 |

| Figure 2-33 Routed FPGA die                                    | 89 |

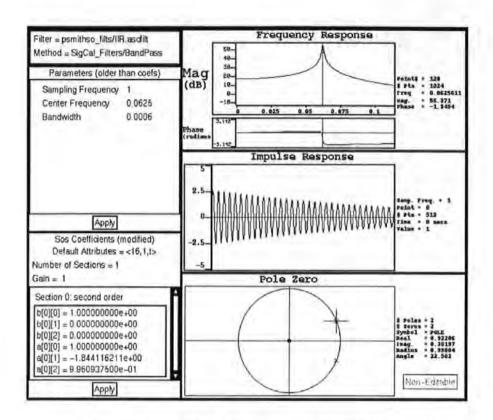

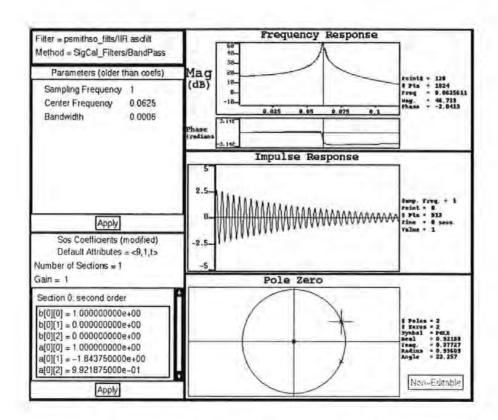

| Figure 2-34 IIR Filter quantized to 16-bits                    | 91 |

| Figure 2-35 IIR Filter quantized to 9-bits                     | 92 |

| Figure 2-36 IIR Filter quantized to 8-bits                     | 93 |

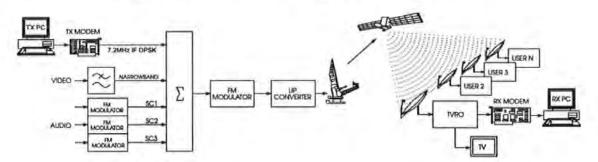

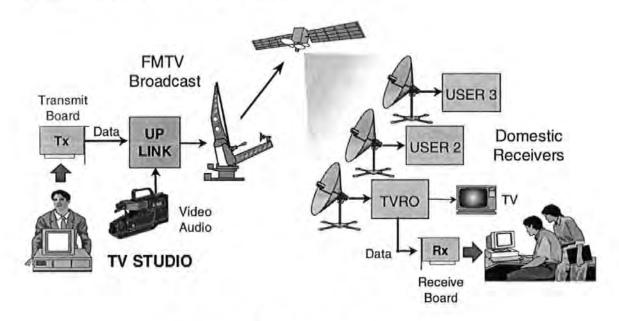

| Figure 2-37 Satellite data broadcasting system                 | 94 |

| Figure 2-38 Sub-carrier receive modem                          | 95 |

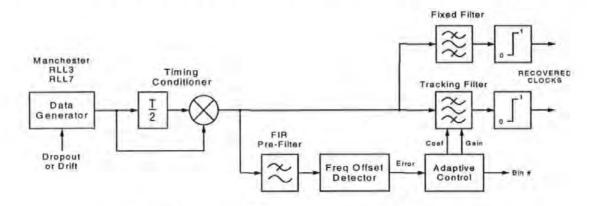

| Figure 3-1 Concept of adaptive clock recovery               | 97  |

|-------------------------------------------------------------|-----|

| Figure 3-2 Adaptive clock recovery system                   | 99  |

| Figure 3-3 Tracking filter with no amplitude compensation   | 101 |

| Figure 3-4 Tracking filter with amplitude compensation      | 102 |

| Figure 3-5 Response of non-symmetrical detection filters    | 103 |

| Figure 3-6 Ideal mirrored detection filters                 | 104 |

| Figure 3-7 Cosine function of filter coefficient            | 105 |

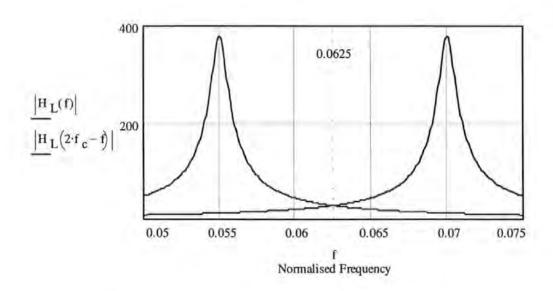

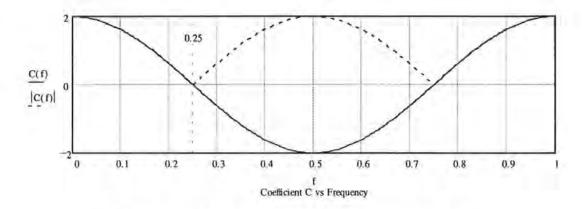

| Figure 3-8 Symmetrical detection filters                    | 106 |

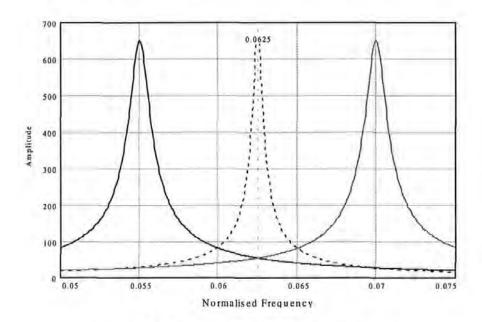

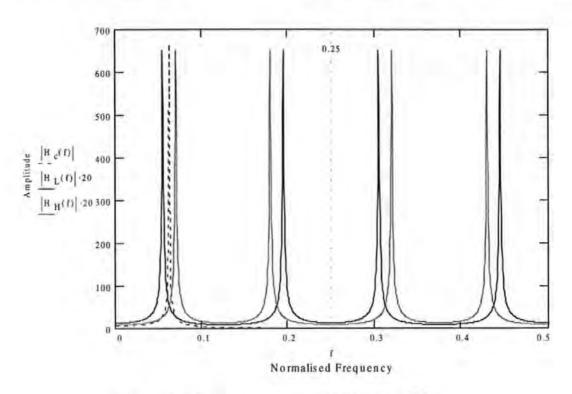

| Figure 3-9 Repeat spectrum of detection filters             | 108 |

| Figure 3-10 Simplified filter architecture                  | 109 |

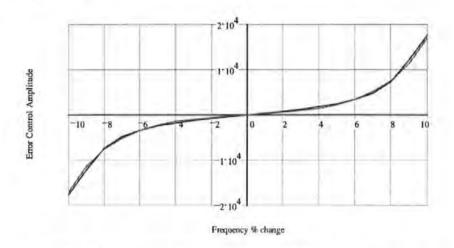

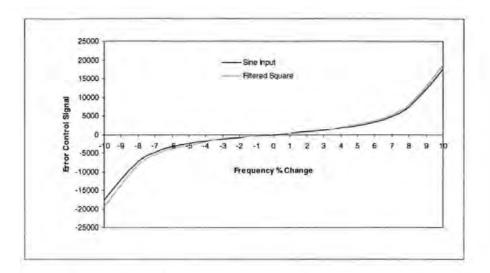

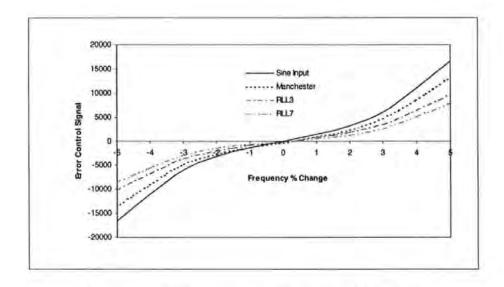

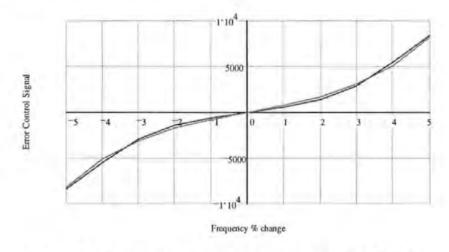

| Figure 3-11 Error calibration over ±10% frequency offset    | 111 |

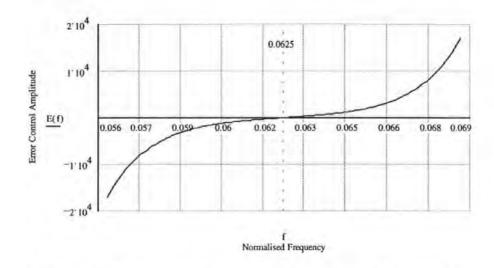

| Figure 3-12 Error calibration as a function of frequency    | 112 |

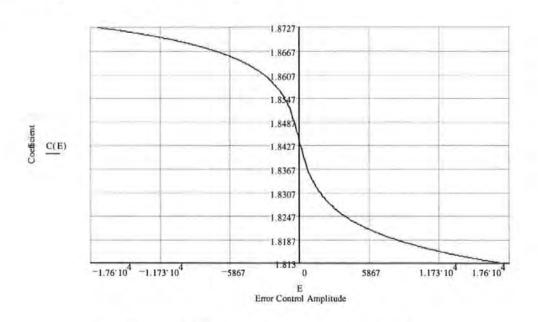

| Figure 3-13 Coefficient vs. Error signal                    | 113 |

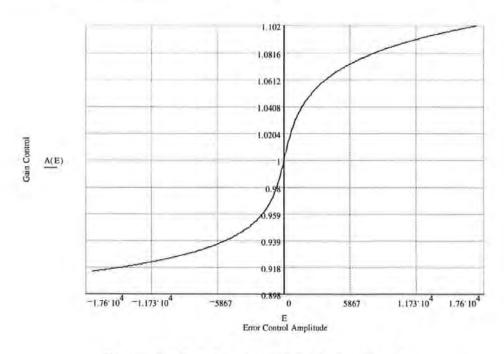

| Figure 3-14 Gain control vs. Error signal                   | 114 |

| Figure 3-15 Overview of adaptive filter test model          | 116 |

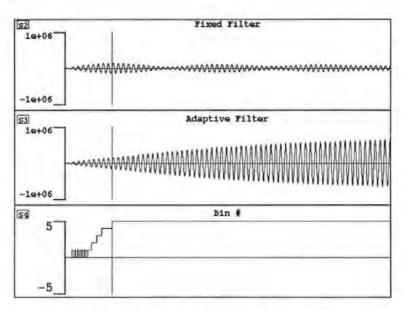

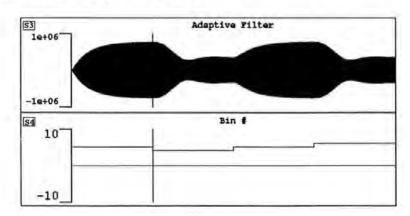

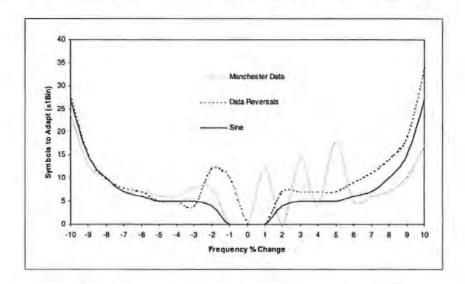

| Figure 3-16 Tracking filter simulation - sinusoidal input   | 117 |

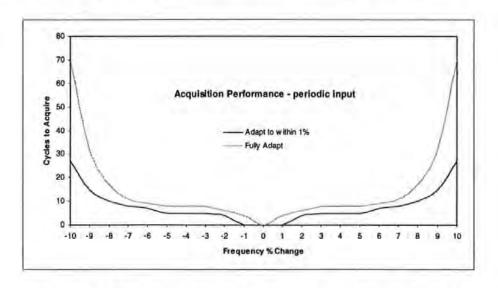

| Figure 3-17 Acquisition performance for a periodic input    | 118 |

| Figure 3-18 Tolerance to ±1% frequency offset               | 118 |

| Figure 3-19 Error control for a signal generator input      | 119 |

| Figure 3-20 Adaptive filter for use with rectangular pulses | 120 |

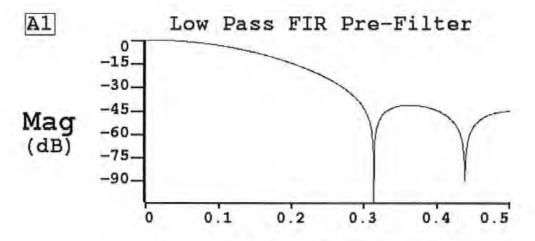

| Figure 3-21 Pre-filter frequency response                   | 120 |

| Figure 3-22 Error control signal with a pre-filter          | 121 |

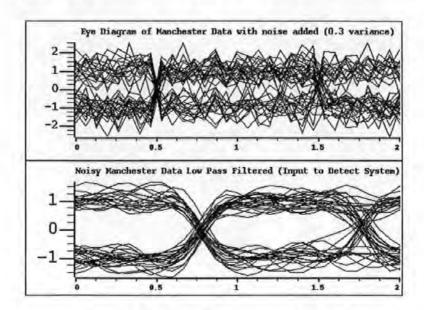

| Figure 3-23 Eye diagram pre-filtered                                     | 122 |

|--------------------------------------------------------------------------|-----|

| Figure 3-24 Acquisition performance with additive noise                  | 122 |

| Figure 3-25 Reduction in detection filter spacing                        | 123 |

| Figure 3-26 Error control signal for ±5% offset                          | 124 |

| Figure 3-27 Error calibration function for RLL7 data                     | 125 |

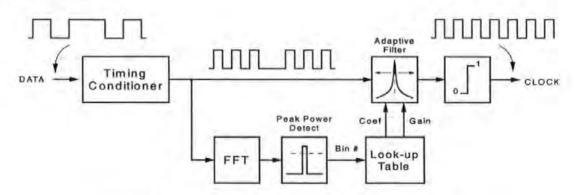

| Figure 3-28 Overview of adaptive simulation model                        | 127 |

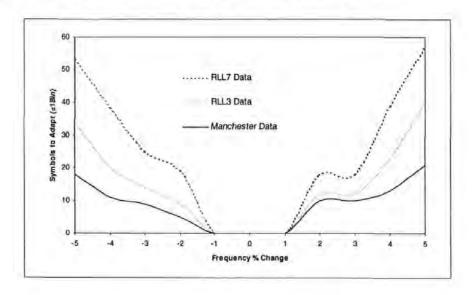

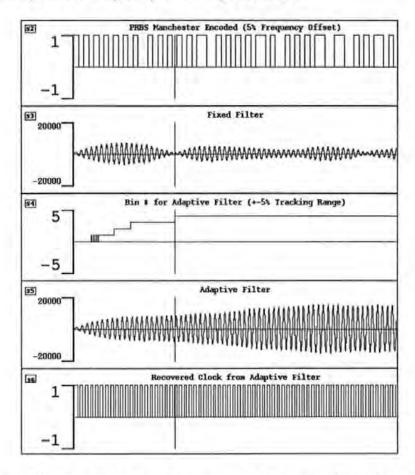

| Figure 3-29 Acquisition performance - ±5% tracking range                 | 130 |

| Figure 3-30 Acquisition performance ±5% range - Manchester data          | 131 |

| Figure 3-31 Acquisition performance ±5% range - RLL7 data with preamble. | 132 |

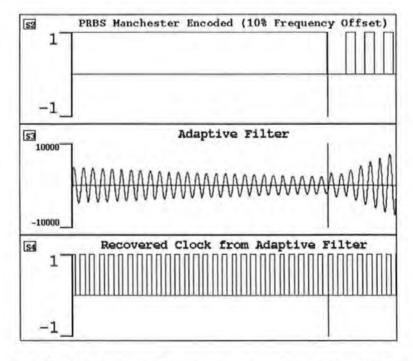

| Figure 3-32 Acquisition performance - ±10% tracking range                | 133 |

| Figure 3-33 Acquisition performance ±10% range - Manchester data         | 134 |

| Figure 3-34 Flywheel performance +10% offset - Manchester data           | 136 |

| Figure 3-35 Flywheel performance zoomed in - Manchester data             | 136 |

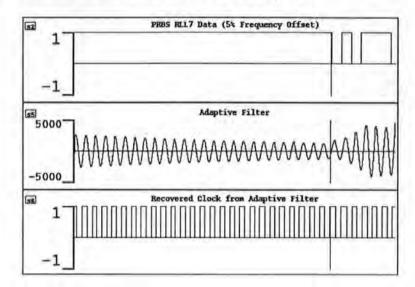

| Figure 3-36 Flywheel performance +5% offset - RLL7 data                  | 137 |

| Figure 3-37 Flywheel performance zoomed in - RLL7 data                   | 138 |

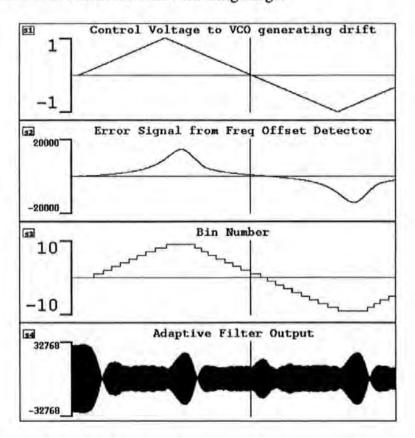

| Figure 3-38 Tracking performance ±10% range - Sine input                 | 139 |

| Figure 3-39 Abrupt change in tracking direction - Sine input             | 141 |

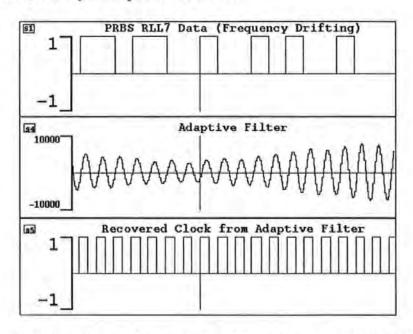

| Figure 3-40 Tracking performance ±5% range – RLL7 data                   | 141 |

| Figure 3-41 Abrupt change in tracking direction - RLL7 data              | 142 |

|                                                                          |     |

| Figure 4-1 Concept of FFT-based adaptive clock recovery                  | 143 |

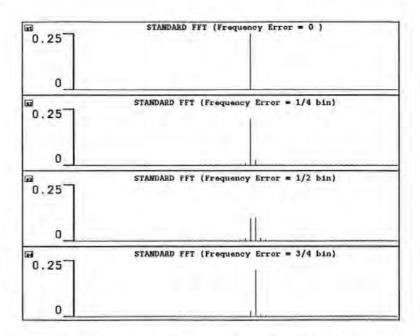

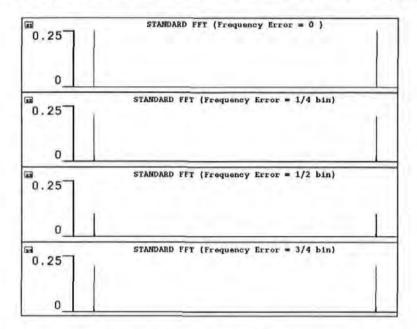

| Figure 4-2 Power spectrum for standard FFT                               | 144 |

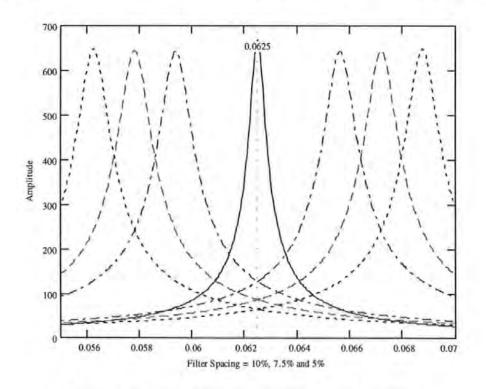

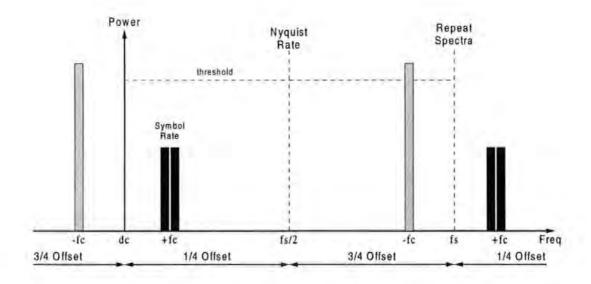

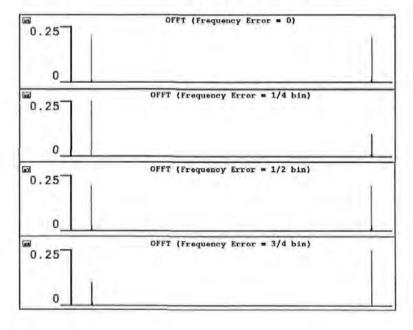

| Figure 4-3 Spectrum of the OFFT                              | 146 |

|--------------------------------------------------------------|-----|

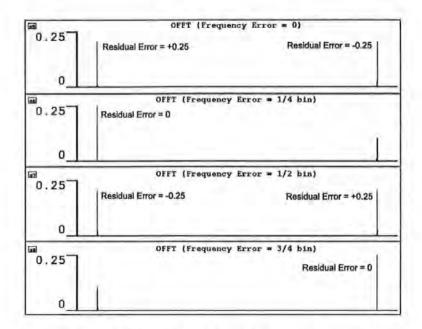

| Figure 4-4 Simulation of FFT with frequency offsets          | 147 |

| Figure 4-5 Simulation of OFFT with frequency offsets         | 147 |

| Figure 4-6 OFFT residual frequency errors                    | 149 |

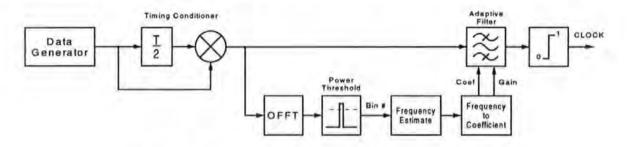

| Figure 4-7 Overview of OFFT simulation model                 | 151 |

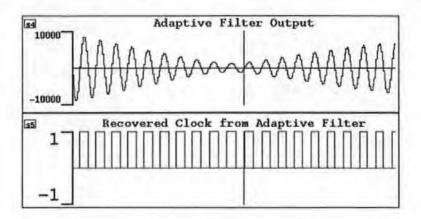

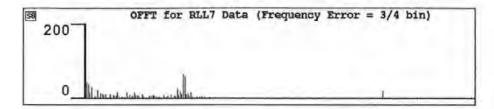

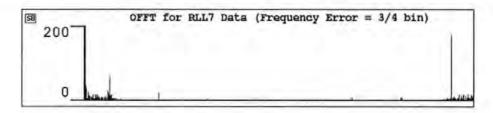

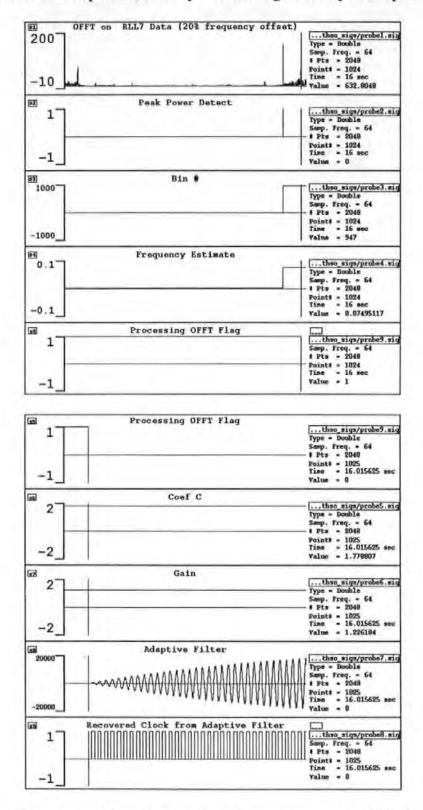

| Figure 4-8 Simulation of OFFT with RLL7 data - zoomed in     | 152 |

| Figure 4-9 Simulation of 1024-point OFFT with RLL7 data      | 152 |

| Figure 4-10 Simulation of clock recovery using OFFT          | 153 |

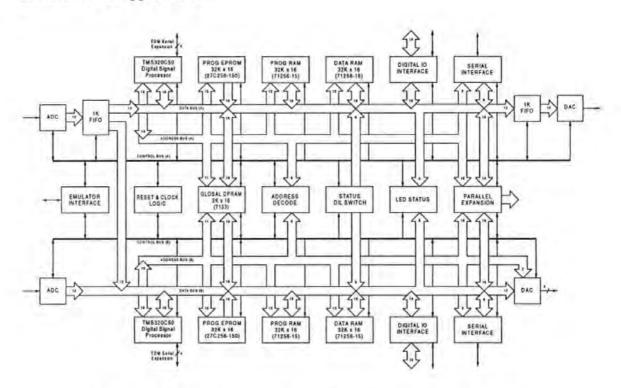

| Figure 4.11 Dual-processor DSP hardware - Block diagram      | 154 |

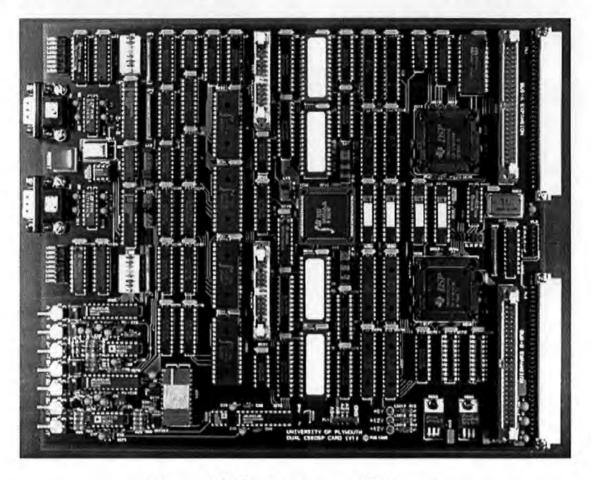

| Figure 4-12 Dual-processor DSP board                         | 155 |

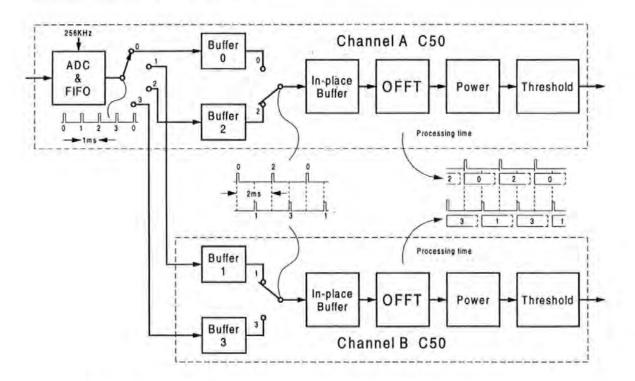

| Figure 4-13 OFFT implementation using flip-flop dual buffers | 158 |

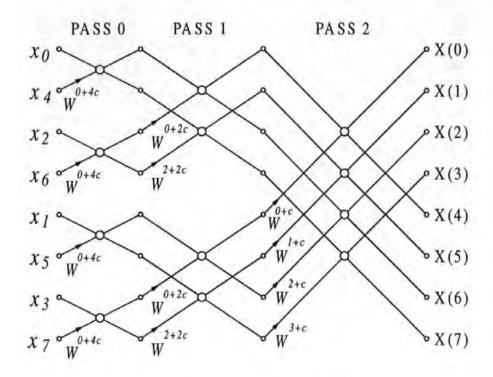

| Figure 4-14 Flow diagram for an 8-point OFFT                 | 160 |

| Figure 4-15 The OFFT test arrangement                        | 163 |

| Figure 4-16 Real-time OFFT test system                       | 163 |

| Figure 4-17 Real-time OFFT power spectrum output             | 164 |

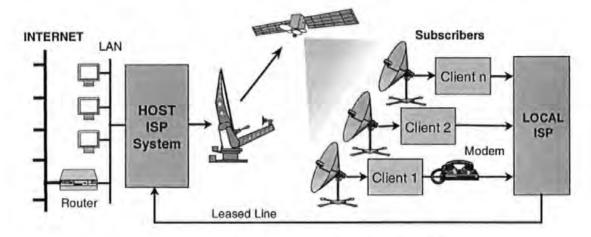

| Figure 5-1 Distance learning system                          | 177 |

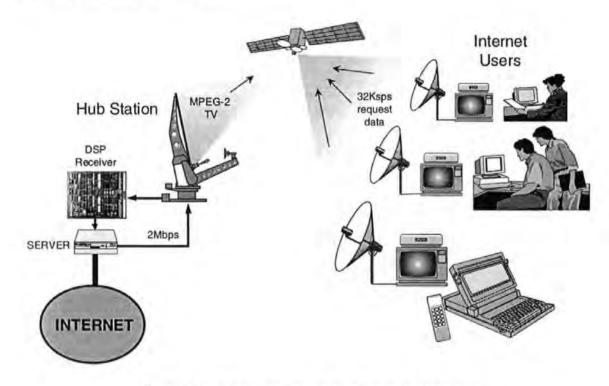

| Figure 5-2 Satellite Internet Service Provision              | 178 |

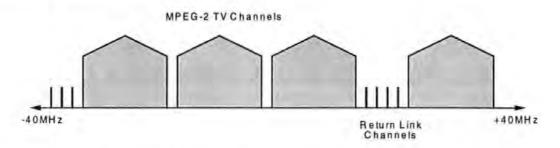

| Figure 5-3 Two-way satellite internet system                 | 179 |

| Figure 5-4 Satellite transponder frequency plan              | 180 |

# **List of Tables**

| Table 1-1 Summary of clock recovery algorithms                                         | 33  |

|----------------------------------------------------------------------------------------|-----|

| Гаble 1-2 Sequence of irreducible polynomials         Гаble 1-3 Code table for RLL 2,7 | 41  |

|                                                                                        | 52  |

| Table 1-4 Summary of popular recording codes                                           | 55  |

|                                                                                        |     |

| Table 3-1 Simulation data look-up table                                                | 129 |

# **Glossary of Abbreviations**

ADC Analogue-to-Digital Converter

AGC Automatic Gain Control

AM Amplitude Modulation

APLL Analogue Phase Locked Loop

ASCII American Standard Code for Information Interchange

ASIC Application Specific Integrated Circuit

**BER** Bit Error Rate

BIOS Basic Input and Output System

BNSC British National Space Centre

**BPF** Band Pass Filter

**BPSK** Binary Phase Shift Keying

CAD Computer Aided Design

CCIR-601 Recommendations for digitising video signalsCCIR-656 Recommendations for interfacing CCIR 601 signals

**CCITT** Consultative Committee for International Telegraph & Telecommunication

CD Compact Disk

CLB Configurable Logic Block

CMOS Complementary Metal Oxide Semiconductor

**COFF** Common Object File Format

CR Clock Recovery

CRC Cyclic Redundancy Check

CRSYNC Clock Recovery Synchroniser

**D1** Professional digital video recording format in composite form. (CCIR-656)

**D2** Professional digital video recording format in composite form.

(NTSC, PAL, SECAM)

DAB Digital Audio BroadcastingDAC Digital-to-Analogue ConverterDASH Digital Audio Stationary Head

**DBPSK** Differential Binary Phase Shift Keying

**DBS** Direct Broadcast Satellite

**DC** Direct Current

DCRSi Digital Cassette Recorder System Incremental

DDS Direct Digital Synthesiser

DFT Discrete Fourier Transform

**DIL** Dual in Line

**DIT** Decimation in Time

### GLOSSARY OF ABBREVIATIONS

DLL Delay Locked Loop

DM Delay Modulation

DMA Direct Memory Access

DOS Disk Operating System

DPLL Digital Phase Locked Loop

**DSP** Digital Signal Processing or Digital Signal Processor

**DSV** Digital Sum Variation

**DTH** Direct to Home

**DTTL** Digital Data Transition Tracking Loop

DVB Digital Video BroadcastingDVC Digital Video Cassette

EBN European Business News

EBU European Broadcasting Union

ECPD Edge Controlled Phase Detector

**EPROM** Erasable Programmable Read Only Memory

**ESA** European Space Centre

FDD Frequency Difference Detector

FDS Filter Design System

FEC Forward Error Correction

FFT Fast Fourier Transform

FIFO First-In-First-Out memory

FIR Finite Impulse Response (filter)

FM Frequency Modulation FPD Frequency Phase Detector

**FPGA** Field Programmable Gate Array

FSK Frequency Shift Keying

**GPIB** General Purpose Interface Bus (IEEE488 standard)

GOPS Giga Operations per Second

HC High speed CMOS

**HCT** High speed CMOS (TTL compatible)

**HD** Hard (rigid disk) Drive

HEX Hexadecimal HPF High Pass Filter

IEE Institute of Electrical Engineers

**IEEE** Institute of Electrical and Electronic Engineers

IF Intermediate Frequency

IIR Infinite Impulse Response (filter)

#### GLOSSARY OF ABBREVIATIONS

IO Input and Output

ISA Industry Standard Architecture

ISI Inter-Symbol Interference

ISO International Standards Organisation

**ISP** Internet Service Provider

ITU International Telecommunications Union

JTAG Joint Test Action Group

LAN Local Area Network

LC Inductor and Capacitor

LED Light Emitting Diode

LMS Least Mean Squared

LPF Low Pass Filter

LSB Least Significant Bit

MAP Maximum a posterori

MFM Modified Frequency Modulation

MIPS Million Instructions per Second

ML Maximum Likelihood

MPEG Motion Pictures Expert Group

MSB Most Significant Bit

MSK Multiple Shift Keying

MUX Multiplexer

NRZ Non Return to Zero

NRZI Non Return to Zero Inverse

NRZ-L Non Return to Zero Level

NRZ-M Non Return to Zero Mark

NTSC National Television Standard Committee

**OFFT** Offset Fast Fourier Transform

PAL Phase Alternate Line

PC Personal Computer

PD Phase Detector

PDF Probability Density Function

PFD Phase Frequency Detector

PISO Parallel-In-Serial-Out

PLD Programmable Logic Device

PLL Phase Locked Loop

**PRBS** Pseudo Random Binary Sequence

### **GLOSSARY OF ABBREVIATIONS**

PSD Power Spectra Density

PSK Phase Shift Keying

PSU Power Supply Unit

QPSK Quadrature Phase Shift Keying

RAM Random Access Memory

RDAT Rotary-head Digital Audio Tape recorder

RDS Radio Data System

RLL Run Length Limited

RLL3 Maximum run length limited to 3 (PRBS)

RLL7 Maximum run length limited to 7 (PRBS)

**ROM** Read Only Memory

RS232 Standard asynchronous serial communication interface

**RS422** Standard differential interface (twisted pair)

RZ Return to Zero

SAW Surface Acoustic Wave (filter)

SCPC Single Carrier per Channel

SISP Satellite Internet Service Provision

**SMPTE** Society of Motion Pictures and TV Engineers

SNG Satellite News Gathering SNR Signal to Noise Ratio

SPW Signal Processing Worksystem SWDS SoftWare Development System

TDM Time Division Multiplexing

TDMA Time Division Multiple Access

TTL Transistor-Transistor-Logic

TV TeleVision

**TVRO** TeleVision Receive Only

**UART** Universal Asynchronous Receiver Transmitter

UW Unique Word

VCO Voltage Controlled Oscillator VSAT Very Small Aperture Terminal

WAN Wide Area Network

WWW World-Wide-Web

# Introduction

The 1990's may well be considered as the era of information technology, with the prevalence of computers, digital communications and hence the need for data storage. Diverse data storage media have been introduced, such as silicon (flash memory) [3] and the CD (Compact Disk) [4], however improvements in magnetic recording has resulted in magnetic media as the prominent leader in mass storage technology. With improvements to the storage medium, the read/write heads and the channel electronics, the capacity of magnetic rigid disks has approximately doubled every 3 years (period 1960-90) [5]. These improvements to the channel, coupled with fast data-access times, has resulted in the magnetic disk drive remaining the dominant data storage device in computer technology.

As storage densities increased, digital audio became viable and, driven by the enormous consumer market, products such as the audio CD [6] and RDAT (Rotary Head Digital Audio Tape) [7] have taken over from their analogue counterparts, as state of the art digital recording.

Data communications is another huge growth area, with satellite data communications providing exciting new applications such as MPEG-2 (Motion Pictures Expert Group) compressed digital TV [8], Internet access [9] and personal communications [10].

These new applications have been made possible largely due to the advances in digital electronics. DSP (Digital Signal Processing) processors now offer more than 2 GOPS (Giga 10<sup>9</sup> Operations per Second) [11] while semi-custom devices such as FPGA's (Field Programmable Gate Array), provide more than 130,000 gates with toggle rates in excess of 150MHz [12]. The cost of the more modest DSP devices have reduced considerably and such devices with on-chip memory can provide a dual role of signal processing and control, replacing the more common microprocessor.

Digital solutions are often preferred over their analogue equivalents since designs are usually more repeatable, reliable and robust. As DSP devices become faster and more powerful, the work that the processor can perform may be increased to encompass such areas as clock recovery, channel filtering, demodulation, error correction and control. DSP allows the use of re-configurable hardware, resulting in a flexible and cost-effective product. Low data rate systems are already emerging [13], and it is likely that the DSP-based algorithms developed today will be adopted by higher speed systems, as faster and more powerful devices become available.

This thesis restricts attention to the topic of clock recovery, which is a vital processing part of digital magnetic recording and communications. Despite much work in this field, few novel advances have been made in this important area of data recovery (see Section 1.1 Clock recovery architectures), which is surprising when

one considers that potential improvements can be achieved, both in terms of storage capacity, bandwidth and BER (Bit Error Rate).

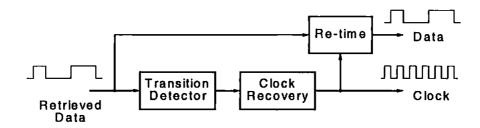

Figure 1 Clock recovery used for synchronous re-timing of data

In data recording systems and data modem receivers, it is necessary to generate a time-base, which is synchronised to the retrieved data. The recovered clock is normally extracted from timing information contained within the data-bearing signal. Figure 1 illustrates a clock synchroniser, where the recovered clock is used to re-time the retrieved data, and for subsequent synchronous post-processing. The channel-coding scheme used to store or transmit the data is in part chosen to provide a strong spectral component at the clock rate and such codes are termed "self clocking" [14].

The principle of locking a local oscillator within the receiver, to the frequency and phase of the retrieved data, is typically used to derive a synchronised time-base. The most common technique for this purpose is the basic PLL (Phased-Locked Loop)

[15]. In order to ensure that the PLL is in a locked condition before data are retrieved, a preamble containing a synchronising sequence must be applied before data can be accurately clocked.

In magnetic recording, the synchronising preamble must be stored on the recording medium. This occupies capacity that could otherwise be used for data. Each data block recorded is preceded by a preamble of transitions whose main purpose is to provide a timing reference for synchronising the PLL. Often, in tape recording systems, a post-amble is also applied to allow a block to be read in the reverse direction and to prevent a transient, when the heads are turned off, from corrupting the last bits written [16]. Latest hard-disk drives [17] [18] devote approximately 6% of the total storage capacity to the purpose of clock synchronisation.

A clock recovery system with improved acquisition would release some of this capacity for the storage of useful data as well as increasing data-access time.

Also, loss of lock and synchronisation can occur if the data synchronising the PLL "drops out" for a period of time, due to defects on the magnetic medium, and problems can occur in regaining lock if the data signal is poor. The "dropout", together with prolonged re-acquisition time, results in corrupted data.

Similarly, in burst-mode communication systems, a preamble is transmitted to allow the receiver to achieve synchronisation before message data can be decoded for subsequent processing. For certain applications the message data can be very short, for example a network "ping" packet [19]. In such cases the synchronising preamble may be longer than the message itself, clearly an undesirable arrangement.

Furthermore, once synchronisation has been achieved and the packet successfully received, a guard band must be applied before the next packet can be transmitted.

This is to allow the synchroniser to drop out of lock, thereby allowing a new acquisition cycle to begin [20]. This is in direct conflict to the essential flywheel feature necessary to maintain synchronisation over periods of lost data. Terrestrial and satellite communication systems also suffer from temporary loss of data when the signal fades. This is typically due to adverse weather conditions, such as heavy rain or multi-path reflections producing signal cancellation.

While magnetic recording and communication systems appear to be widely different technologies, they do in fact share a common objective; namely the retrieval of burst data. The investigation of clock synchronisation described in this thesis is therefore relevant to both technologies and the algorithms investigated will be helpful in solving many of the problems identified.

Clock recovery systems derive their timing information from the retrieved data transitions. Hence, the channel-coding scheme employed influences the performance of the clock recovery system. One area that is distinctly different between magnetic recording and communication systems, is the method of increasing the channel efficiency. Broadband communication systems use multilevel signals and hence the channel capacity can be improved by employing complex modulation schemes. These include amplitude, frequency and phase modulation or a combination of all three [21].

In general, digital magnetic recording operates with just two levels ±1. This is because the magnetic particles of the medium are saturated in one of two directions. The channel capacity may, however, be increased by the use of RLL (Run Length Limited) coding [22]. If data are encoded to contain fewer transitions, then these transitions can be recorded closer together for a given packing density, resulting in increased storage capacity. However this can affect the self-clocking properties of the coded data, which could adversely affect clock synchronisation.

Throughout this research, computer simulations have been performed to simulate and analyse system performance [23] [24]. SPW (Signal Processing Worksystem) is a powerful integrated software suite, which has been extensively employed for system design and analysis [25]. Full simulation models and results are located in the appendices, key extracts of which are included in the relevant chapters.

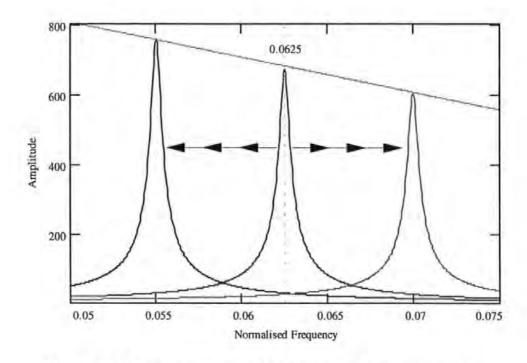

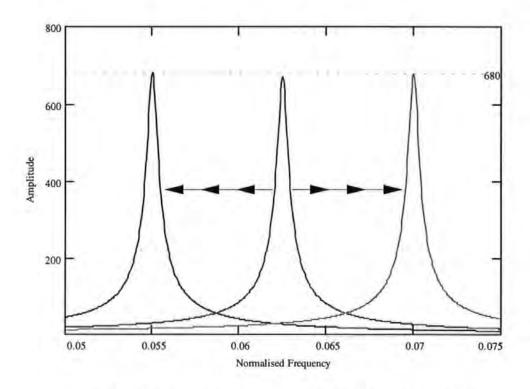

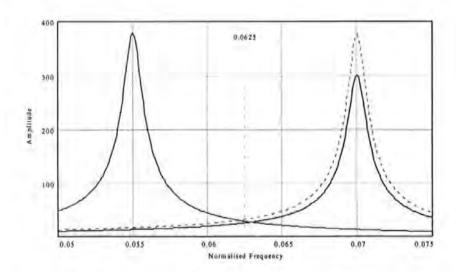

Computer simulations have been standardised with the use of normalised frequencies. The sample rate has been normalised to 1Hz and the nominal symbol rate normalised to 16 samples/symbol = 0.0625Hz. The advantage of using normalised frequencies is that the system can easily be scaled to any absolute frequency. For example, at 16 samples/symbol a sample rate of 1MHz results in a symbol rate of 1MHz/16 = 62.5KHz.

Chapter 1 provides a background to the investigation. Current clock recovery algorithms are reviewed together with a summary of their limitations for burst data

applications. The channel-coding scheme employed is fundamental to clock recovery performance. Hence, channel coding is reviewed and five codes are selected as bench marks for subsequent analysis of clock recovery performance. These codes are described and have been selected to represent a typical cross-section of available codes. A summary of popular recording codes is provided to demonstrate the various trade-offs.

Three new DSP-based algorithms have been investigated:

- . ♦ A fixed frequency clock recovery system.

- ♦ An adaptive (tracking) clock recovery system.

- ♦ An OFFT (Offset Fast Fourier Transform) based clock recovery system.

These algorithms together with results, are presented in Chapters 2, 3 and 4, respectively.

Chapter 2 describes a novel DSP-based clock recovery scheme utilising a high-Q IIR filter that demonstrates superior performance over that of a PLL, particularly in terms of clock acquisition. Long flywheel periods can be tolerated, maintaining clock synchronisation over severe data dropouts or fades. Simulation results are analysed for the new clock recovery scheme to determine clock acquisition, flywheel performance and clock jitter in the presence of noise. Performance using several magnetic recording codes is investigated. Hardware and software implementation of the new algorithm is described. The simulation results are

verified in real-time using a fixed-point digital signal processor [26]. The IIR filter algorithm has also been implemented in an FPGA, using fast coefficient multipliers [Appendix 11{3}]. This device has been successfully incorporated into a commercial satellite modem for reception of computer data, utilising a sub-carrier on an analogue FM satellite TV broadcast [Appendix 11{4}].

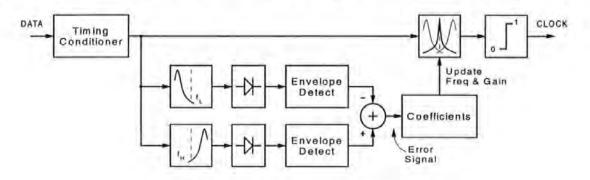

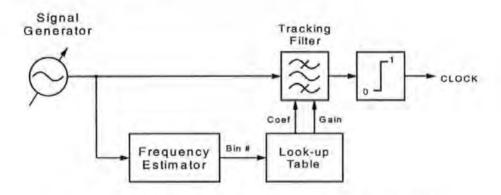

Chapter 3 describes the investigation of an adaptive tracking system, based upon two detection filters. These detection filters have a wider bandwidth than the tracking filter and are placed symmetrically around the nominal input (symbol rate) frequency. The output of the detection filters are envelope-detected and subtracted to generate a dc error-control signal which is used to move the tracking filter to the correct symbol rate.

Chapter 4 describes an OFFT [27] that is used to estimate the frequency of the retrieved symbols. The frequency estimate is used to determine the correct coefficients necessary to move the centre frequency of the clock recovery filter to the correct symbol rate. The OFFT has been implemented, and results verified in real-time, using a specially designed dual DSP board based around two fixed-point DSP processors [28].

Finally, Chapter 5 summarises the investigation with conclusions, a discussion of the results, applications and recommendations.

# Chapter 1

# 1. Background to the investigation

Current clock recovery algorithms, which are represented by basic architectures, are reviewed. These architectures are described and their individual performance noted. A summary of their relative performance is provided, with particular reference to acquisition of burst data.

The channel-coding scheme employed is fundamental to clock recovery performance. Hence, the principles of channel coding are reviewed and five codes are selected as bench marks for subsequent analysis of clock recovery performance. These codes are Scrambled NRZ (Non Return to Zero) [29], Manchester [30], Miller [31], Miller<sup>2</sup> (Miller Squared) [32] and RLL2,7 [33]. These codes are described and have been selected to represent a typical cross-section of available codes, from high clock-content codes through to the more efficient block codes. In practice recording codes are pre-coded with NRZI (Non Return to Zero Inverse) [34] encoding to eliminate phase ambiguity and error propagation. The NRZI code is also described. A summary of popular recording codes is provided to demonstrate the various trade-offs.

### 1.1. Clock recovery architectures

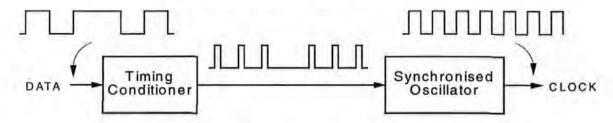

Figure 1-1 illustrates the concept of a clock recovery system, where a local oscillator is synchronised to the input transitions, which oscillates freely in their absence. The oscillator must be capable of fly wheeling over periods of missing data transitions, with negligible drift.

Figure 1-1 Clock recovery system

A clock recovery system in its simplest form can be represented by two basic building blocks; a timing conditioner and an oscillator that generates a periodic output synchronised to the input symbol rate.

The timing conditioner is required to extract, from the data-bearing signal, a strong spectral component at the symbol rate. This can be achieved by means of auto-correlation of the retrieved data, and this technique is described in Section 2.1.1. In its simplest form the timing conditioner can be implemented by means of a transition detector, where the data are delayed by the propagation delay of a few logic gates and then "Exclusive-Or" gated with the non-delayed version. Alternatively, a differentiator can be used, followed by a squaring circuit to invert the negative impulses.

Synchronisation of the oscillator to the input transitions is typically achieved by means of a feedback loop, employing phase error detection. The method of phase detection often governs the type of timing conditioner employed. Many detectors are level sensitive and require a rectangular pulse shape [35]. Whereas the use of a transition detector necessitates the use of an ECPD (Edge Controlled Phase Detector) [36], where the phase error is derived from the time difference between the input signal and the local clock, setting and resetting a flip-flop.

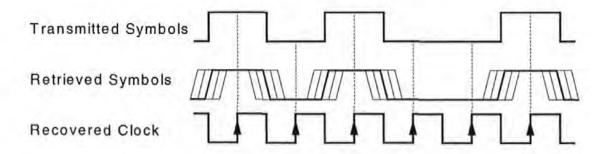

The retrieved symbols usually contain timing jitter due to channel noise [37]. It is necessary for the clock recovery system to reject jitter in the recovered clock and resample the retrieved symbols at the centre of the symbol period, thereby avoiding data errors, as illustrated in Figure 1-2.

Figure 1-2 Optimum re-sampling

The frequency of the local oscillator is usually controlled by means of an error signal in a closed loop configuration. It is also possible to implement a burst oscillator in an open loop configuration by means of a high-Q self-synchronising ringing filter, and it is this concept that forms the basis of a DSP approach discussed in later chapters.

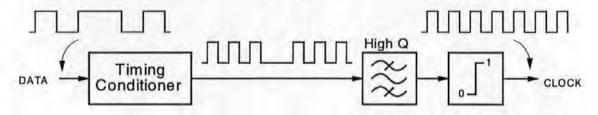

### 1.1.1. High-Q passive resonator clock recovery

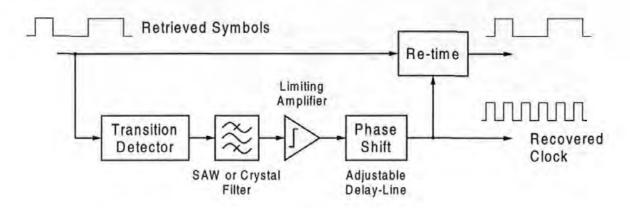

In concept, the simplest clock recovery system, is one employing a high-Q passive resonating filter [38], as illustrated in Figure 1-3.

Figure 1-3 High-Q passive resonator clock recovery

A transition detector provides pulses at the symbol rate, which excites a high-Q bandpass filter, pre-tuned to the symbol frequency. The filter "rings" at the symbol rate and continues to oscillate for a period of time, even in the absence of input transitions. The filter output is provided with gain and hard limited to produce a recovered clock, which is then delayed to align the clock to the centre of the symbol period, for optimum re-sampling.

This simple approach, in several respects, provides an ideal clock recovery system.

The recovered clock is rapidly acquired and flywheels over long symbol runlengths. Also, the filter's high-Q, and hence, narrow bandwidth provides high noise immunity, virtually eliminating jitter in the recovered clock.

### BACKGROUND 1.1.1 HIGH-Q PASSIVE RESONATOR CLOCK RECOVERY

Hence, this system is often used as a benchmark, against which, clock recovery performance of other systems is compared. However, certain restrictive assumptions are made. Firstly, the symbol rate must be accurate and stable. This is usually the case in communications systems, where the symbol rate is derived from a crystal-controlled oscillator in the transmitter [39]. Unfortunately, this is rarely the case for tape recording systems, which suffer from mechanical limitations and tape stretch [40]. A second assumption is that the high-Q filter, is and remains, accurately aligned to the frequency and phase of the input symbols. Hence, the design of such circuits requires careful alignment of the clock, relative to the data, with consideration given to temperature, power supply, component ageing and process variations.

A passive tuned LC (inductors and capacitors) "tank" filter may be used to implement the high-Q filter, but the parameters of these components suffer from variations due to temperature change and ageing. To combat these variations, the high-Q filter is often implemented by means of a SAW (Surface Acoustic Wave) [41] or crystal filter [42]. These expensive devices are manufactured to a fixed frequency, centred at the symbol rate.

Clock recovery employing SAW and crystal filters are generally used at data rates above 200Mb/s [43], and are therefore unsuitable for use at low data rates. These devices exhibit a large insertion loss (-20dB is typical for a SAW filter) and hence, a high-gain limiting amplifier is required to generate a suitable logic-level clock, for

re-timing the data. A problem with these non-linear devices is that they exhibit an unknown group delay, due to manufacturing variations. The resulting phase variation must be compensated, with a manually adjusted delay-line, to achieve optimum timing for re-sampling the symbols.

It is not practical to integrate a SAW or crystal resonator into an integrated circuit and therefore, clock recovery schemes of this type are implemented using discrete components. While a clock recovery system employing a high-Q filter is attractive in concept, it is these practical considerations, which make a realisable system expensive and unpopular.

It is however, possible to implement a high-Q filter using DSP, thereby eliminating undesirable variations and the need for manual tuning. Hence, a repeatable, reliable and robust clock recovery system can be produced, which may be re-configured "on-the-fly" to accommodate a wide range of different symbol rates. It is this new approach to an old problem that forms the basis of the novel DSP algorithms, discussed in later chapters.

Example publications of clock recovery systems employing SAW or crystal filters are referenced in [44] and [45] respectively.

### 1.1.2. PLL clock recovery

The PLL is popular for clock recovery and forms the basis of most other types of closed-loop clock recovery systems. Appendices 1 and 2 supplement this section, analysing the performance of the basic PLL. Appendix 1 provides a glossary of commonly used PLL terminology, together with detailed analysis and loop equations. Appendix 2 contains PLL simulation models and results, which are used for comparison with the new DSP approach, discussed in later chapters.

A survey of APLLs (Analogue PLL) by Gupta [46] provides over 40 publications, while Lindsey and Chie [47] have carried out analysis and a survey of DPLLs (Digital PLL). More recently, monolithic PLLs have become popular, and Razavi [48] provides a collection of 47 publications, 15 of which are specific to clock recovery.

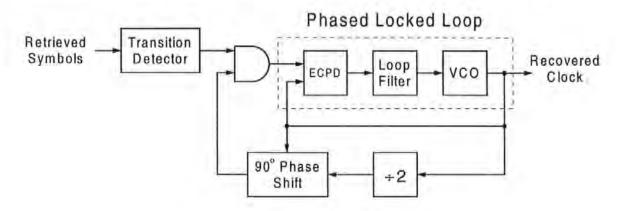

Figure 1-4 shows how a hybrid (digital and analogue) PLL can be used with a transition detector to perform clock recovery, from Manchester encoded data.

Figure 1-4 PLL clock recovery circuit

Retrieved symbols are applied to a transition detector producing pulses, which are gated with a 90° phase-shifted version of the divided output clock. This provides periodic pulses at half the symbol rate for input to the PLL. These pulses are applied to an ECPD, producing a phase error signal proportional to the phase difference between the input and feedback transitions. The output from the ECPD is low-pass filtered, producing a dc control voltage to the VCO (Voltage Controlled Oscillator), so as to sustain or correct the output frequency. The negative edges of the output are used to clock the phase shifter, thereby providing the 90° phase-shift.

Many PLL integrated circuits [49] contain a choice of PDs (Phase Detector). A multiplier or "Exclusive-Or" PD is level sensitive and requires rectangular pulses confined to the symbol period. A PFD (Phase Frequency Detector) can be edge controlled and is often employed to aid clock acquisition.

The simplest form of PFD has a 3-state output [50] for driving the loop filter, the average of which controls the VCO. If a phase error exist, then the PFD output attempts to drive the VCO control voltage to either its positive or negative extreme (depending upon the direction of the phase error) for the duration of the phase difference, and at a high impedance state for the remainder of the time. This produces a "sample-and-hold" effect providing a "charge-pump" to the capacitor at the loop (low-pass) filter. Hence the LPF (Low Pass Filter) achieves its final control voltage more rapidly than that of a simple PD, thereby aiding acquisition.

Simple flip-flop PFDs of this type rely on a periodic input, but unfortunately provide an incorrect output in the absence of input transitions. During missing data transitions, these simple detectors interpret the VCO output to be higher than the input frequency, driving the control voltage in such a direction so as to correct the apparent difference. The "Exclusive Or" PD on the other hand, drives the VCO to its nominal frequency in the absence of transitions. Therefore the choice of phase and frequency detectors, for random or burst data, requires careful consideration in the absence of missing data transitions.

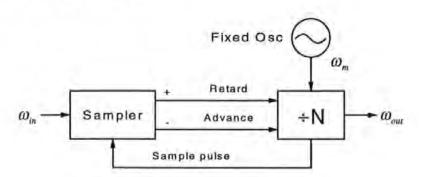

Figure 1-5 illustrates an example of a DPLL, first described by Levy and Cessna [51], consisting of a sampler, a divide by N counter and a fixed rate clock oscillator. The operation is similar to an earlier design by Natali [52] employing a DCO (Digitally Controlled Oscillator).

Figure 1-5 Lead-lag digital PLL

In the absence of feedback, the loop is designed for  $\omega_m/N \cong \omega_i$ . The  $\div N$  counter counts down the oscillator frequency and generates a sample pulse each time it passes through a zero count. The sampler detects changes of input polarity and when the loop is phase-locked, the sampler is clocked synchronous to the input.

The counter is arranged so that its count is advanced by one increment if the sample is positive and decremented if it is negative. If the output is identical to the input frequency then the sampler detects an equal number of positive and negative polarities, resulting in cancellation of the advance and retard signals.

If however, the input frequency is increased, then the advance signal reduces the division by one count and the phase at the counter output increases by I/N cycles.

Over successive cycles the change in phase at the counter output moves, so as to reduce the output frequency to that of the input.

This simplified DPLL is similar to a non-linear first order APLL, that is a loop with no filter. Unlike its analogue equivalent, the output phase has now been quantized creating a source of phase jitter in the recovered clock. This can be minimised with a high-frequency fixed oscillator and hence, a large  $\pm N$  counter.

With this type of DPLL, there is no VCO and this makes them far less sensitive to voltage or temperature variations. A useful feature of a DPLL is that the centre frequency and control bandwidth can be made programmable and adjusted by means of a microprocessor, hence these parameters can be dynamically adjusted.

The DLL (Delay Locked Loop) [53] is a close relative of the PLL and provides a means of replacing the VCO of an APLL with a voltage controlled delay-line.

When in lock, the DLL delays its periodic input by an integer number of input periods (usually one), such that the relative phase shift at the PD can be considered

zero. For clock synchronisation a tapped delay-line can be employed, and the optimum timing selected for re-sampling the retrieved symbols. However, unlike the PLL the DLL does not contain an oscillator and therefore does not generate its own clock. Hence, the DLL is only suitable for generating an output at the same frequency as its periodic input.

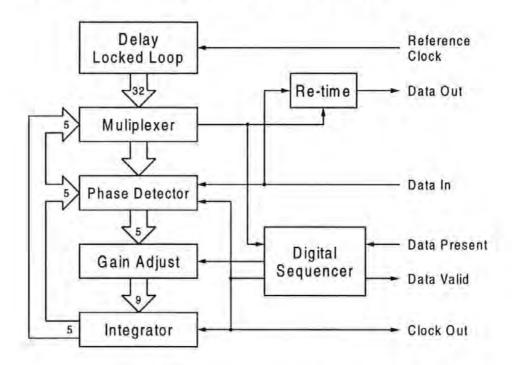

Sonntag and Leonowich [54] have presented a DPLL for burst-mode re-timing of Manchester data, incorporating a DLL, as shown in Figure 1-6.

Figure 1-6 DPLL with DLL phase selection

A stable fixed-frequency reference clock is input to a DLL containing a digital delay-line, providing 32 equally spaced clock phases. The "Phase Detector", "Gain Adjust" and "Integrator" blocks, form a DPLL. When the DPLL is locked, a multiplexer selects 1 of 32 phases for optimum re-timing of the data. The selected

phase is also input to a PD, which produces a 5-bit data word, representing the phase difference between the selected local clock and the input data. The resulting error signal is provided with gain and integrated, producing an address to the multiplexer to select the appropriate clock phase.

Upon detection of burst data, an acquisition cycle is initiated and a digital sequencer applies a pseudo-clock, based upon the retrieved data transitions. The pseudo-clock drives the DPLL until a suitable DLL clock phase is found. When the loop is locked, the pseudo-clock is replaced with the DLL clock for the duration of the burst. The referenced publication [54] quotes a preamble of just 3 transitions, required to align the phase of the local DLL clock to the optimum timing.

A problem with this algorithm is that when acquisition is complete, the pseudo clock is replaced with the locally generated DLL clock. The DLL clock is derived from a reference frequency, which is not locked to the retrieved data. Hence, this algorithm assumes that the frequency of the locally generated DLL clock matches closely the symbol rate frequency, and that the data burst is short. Otherwise, drift between the locally generated clock with respect to the retrieved data symbols, would eventually produce cycle slips, resulting in data errors. The output clock also suffers from quantization jitter, resulting from the discrete DLL phases.

Examples of clock recovery algorithms used on magnetic recording systems, employing combinations of PLLs and DLLs are referenced in [55] [56].

# 1.1.3. Quadricorrelator

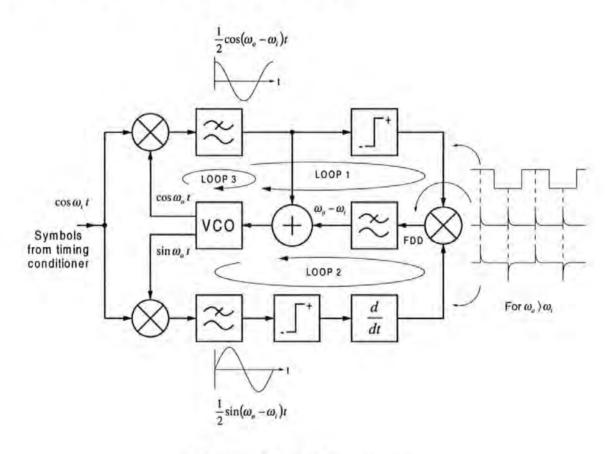

A clock recovery architecture that has been implemented in both analogue and digital domains is the "Quadricorrelator". The Quadricorrelator was first presented by Shaeffer [57], given its name by Richman [58] and modified by Belliso [59]. Shown in Figure 1-7 is a block diagram of the Quadricorrelator, which contains a combination of three loops sharing the same VCO.

Figure 1-7 Quadricorrelator

Loops 1 and 2 perform frequency detection and form a FDD (Frequency Difference Detector), while Loop 3 provides a simple PLL. The input from a timing conditioner contains a strong symbol timing frequency component  $\omega_i$ , while the VCO oscillates at  $\omega_a$ .

When the loop is out of lock, the quadrature phase detectors (multipliers) generate beat signals with a 90° phase difference, one proportional to the cosine of the frequency difference, and the other the sine. One will lead the other by 90° if the VCO frequency is too high. The reverse is the case, if the VCO frequency is too low. This reversal in the phase relationship is detected by a third detector (FDD), and is used to produce either a positive or negative signal, depending upon the direction of the phase error. This signal is then low-pass filtered to produce a dc control voltage to adjust the VCO, so as to reduce the frequency error.

The differentiator in Loop 2 produces a positive and negative pulse each time a cycle is slipped (i.e. one cycle of the beat signal). These pulses are then multiplied by the quantized output of Loop 1, producing unipolar pulses, whose polarity is indicative of the sign of the frequency difference. Two pulses are produced for each cycle slip, and the dc output from the LPF is proportional to the frequency difference,  $\omega_o$ - $\omega_i$ .

As the magnitude of  $\omega_o$ - $\omega_l$  drops, Loop 3 (a simple PLL) begins to assist the lock process. When the VCO frequency approaches the output frequency, the dc feedback from the FDD approaches zero relinquishing control, and Loop 3 dominates locking the VCO output to the input signal.

When lock is achieved, the beat cycles disappear (due to no cycle slips), and the output from the differentiator is zero. Hence, the output from the FDD multiplier is also zero, and therefore does not detract from the PLL performance.

The use of frequency detection in the Quadricorrelator makes the capture range independent of the locked loop bandwidth, allowing a narrow PLL bandwidth in the LPF of Loop 3. In such applications it is more desirable to replace the filter in Loop 3 with two LPFs, one with a wide bandwidth for Loop 1 (frequency detection), and another with a narrow bandwidth in Loop 3 (phase detection and tracking). This will then provide good jitter rejection and memory (to flywheel over symbol run lengths or dropouts), once phase lock has been achieved. Because the frequency detection circuits can respond to noise and spurious components due to their wide bandwidths, it is also preferable to disable Loops 1 and 2, once phase lock has been attained.

A drawback of the Quadricorrelator in discrete form is the requirement for a VCO with quadrature outputs. This can be achieved by passing the VCO output through a delay line to shift the phase by 90°. However, dependence of the delay upon frequency, temperature and component tolerance make a stable design difficult.

Theoretical analysis of the Quadricorrelator is referenced in [59] and [60]. Publications of clock recovery systems employing the Quadricorrelator are referenced in [61]-[63].

# 1.1.4. Gated oscillator clock recovery

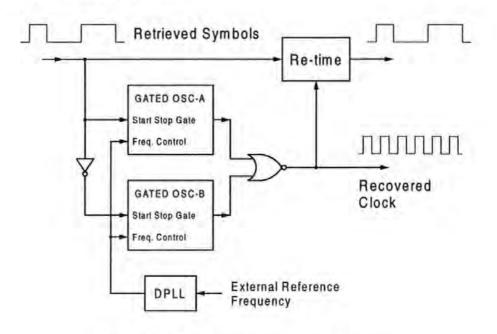

Banu and Dunlop [64] have presented an open-loop burst-mode clock recovery system, with instantaneous locking to the first retrieved transition. The block diagram is shown in Figure 1-8.

Figure 1-8 Gated oscillator clock recovery

A DPLL is locked to an external local reference oscillator, providing a stable frequency to the gated oscillators. Two matched, gated square-wave oscillators are started and stopped alternately, by the symbol transitions. The recovered clock is obtained by combining their outputs, by means of a logic gate. In a closed-loop system, accumulated phase errors between the retrieved symbols and the local oscillator are re-circulated around the loop. Whereas, this open-loop implementation discards timing errors every time the oscillators are stopped. The phase of the recovered clock is therefore reset to that of the retrieved symbols, upon every symbol transition.

The problem with this algorithm is that there is no noise immunity, whatsoever.

The action of resetting the phase of the gated oscillators, to each symbol transition, causes the recovered clock to inherit all of the symbol jitter.

This renders the recovered clock unsuitable for synchronous post processing, necessitating the use of a flexible memory interface, such as a FIFO (First-In-First-Out) buffer [65]. Also, during the data burst, it is necessary to ensure that the FIFO buffer neither becomes empty nor full, otherwise data errors will occur. This may be achieved by the use of asynchronous handshakes, normally made available within FIFO memory devices.

Although this gated oscillator algorithm provides instantaneous clock acquisition, it is only suitable for asynchronous communications (unless the retrieved symbols are free from timing jitter, which is rarely the case).

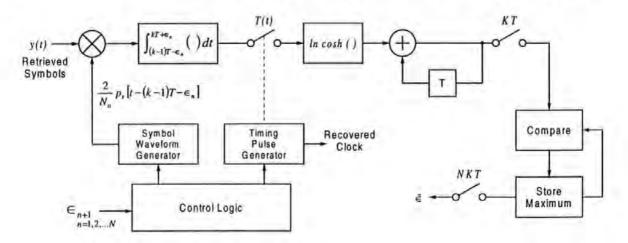

## 1.1.5. Maximum Likelihood

The theory of estimating epoch, of a received signal plus noise, can be approached using the theory of maximum *a posteriori* estimation of an unknown signal in Gaussian noise [66] [67]. In the context of clock recovery, there is optimum clock timing, known as the ML (Maximum Likelihood) estimate or MAP (maximum *a posteriori*) estimate [68].

The theory assumes that the baseband pulse shape is known and is confined to the bit period (T), thereby allowing a stored replica to be generated at the receiver. The history of the received signal is observed over a finite number of symbols (K), during which, the timing misalignment between the retrieved symbols and the locally generated clock is assumed constant, but unknown. Based upon this information, an estimate of the unknown optimum timing can be found.

Theoretical analysis of MAP-estimation is referenced in [68].

The MAP estimate,  $\hat{\epsilon}$ , of the random epoch  $\epsilon$ , is the value that maximises:

$$\Lambda(y, \epsilon) = \ln f(y, \epsilon) = \sum_{k=0}^{K} \ln \cosh \left[ \frac{2}{N_o} \int_{T_k(\epsilon)} y(t) p_s [t - (k-1)T - \epsilon] dt \right] \qquad \dots \dots (1-1)$$

An interpretation of equation (1-1) in the time domain, is to cross-correlate the received signal (y(t)), with a stored replica  $(p_s(t))$ , in each sub-interval (k), take the log hyperbolic cosine of this result, and accumulate these values over all sub-intervals (K). The epoch value  $(\in)$  that yields the largest accumulated value, is then

declared the best timing estimate ( $\hat{\epsilon}$ ). A parallel approach to the MAP-estimator is not practical, due to the large number of "integrate-and-dump" circuits, required for each iteration of k (where k is large to minimise phase quantization). Figure 1-9 shows a serial realisation, where a single "integrate—and-dump" circuit is employed.

Figure 1-9 Open-loop MAP-Estimate clock synchroniser

During each successive interval, a different local symbol-timing phase is selected, and the corresponding epoch estimated. The current sub-interval epoch is compared with the largest past epoch (within the interval *NKT*), and the greater of the two is stored, together with its timing phase information. After all sub-intervals have been processed, the currently stored epoch is declared the MAP-estimate, and the corresponding timing phase is used as the reference for the recovered clock. Compared to a parallel approach, this serial implementation increases clock acquisition time by a factor of *N*, since all sub-intervals must be processed to arrive at the MAP-estimate. Also, the block processing involved renders this open loop approach unsuitable for tracking short-term symbol rate drift.

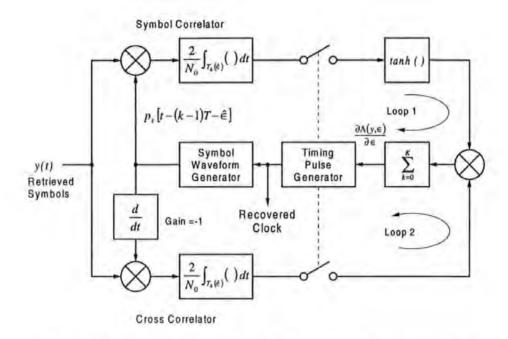

Stiffler [69] and Mengali [70] have devised a closed loop tracking synchroniser, that converges towards the MAP-estimate. Megali's tracker is shown in Figure 1-10

Figure 1-10 Closed-loop MAP-estimate clock synchroniser

An alternative interpretation of equation (1-1), is achieved by differentiating with respect to ∈ and equating to zero, yielding:

$$\frac{\partial \Lambda(y, \epsilon)}{\partial \epsilon} \Big|_{\epsilon = \hat{\epsilon}} = \sum_{k=0}^{K} \left[ \frac{2}{N_o} \left\{ \int_{T_k(\hat{\epsilon})} y(t) \frac{\partial p_s[t - (k-1)T - \hat{\epsilon}]}{\partial \hat{\epsilon}} dt \right. \\

+ y(kT + \hat{\epsilon}) p_s(T) - y[(k-1)T + \hat{\epsilon}] p_s(0) \right\} \right] \\

\times \tanh \left\{ \frac{2}{N_o} \int_{T_k(\hat{\epsilon})} y(t) p_s[t - (k-1)T - \hat{\epsilon}] dt \right\} \\

= 0 \tag{1-2}$$

For an estimate of  $\in$  other than the MAP-estimate, the function  $\partial \Lambda(y, \in)/\partial \in$  will be either positive or negative, depending on whether  $(\in < \hat{\in})$  or  $(\in > \hat{\in})$ . Hence,  $\partial \Lambda(y, \in)/\partial \in$  can be used to indicate the search direction.

The phase of the timing pulse generator, which controls the "integrate-and-dump" circuits, is incremented every symbol period, by an amount proportional to the magnitude of  $\partial \Lambda(y, \in)/\partial \in$ , and in a direction based upon the sign of  $\partial \Lambda(y, \in)/\partial \in$ , as computed from the previous KT interval.

The closed loop dynamics produce an estimation of the frequency error, which is used to control the VCO. This is different from the open loop approach shown in Figure 1-9, which estimates the optimum timing (not the error).

By definition, MAP-estimators operate upon historical information, with little regard given to the problem of rapid acquisition. Synchronisers based upon MAP-estimation operate at low signal to noise ratios and are often used in coherent modems for deep space exploration [71].

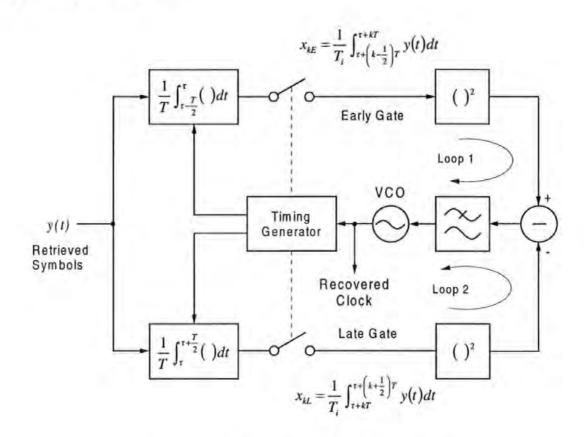

## 1.1.6. Early-late synchroniser

An Early-Late gate synchroniser, as shown in Figure 1-11, is popular for rectangular pulses. The index k is a sequence of symbol pulses, of period T, while  $\tau$  represents the timing error.

Figure 1-11 Early-late gate synchroniser

The circuit consists of a pair of gated integrators, each performing its integration over a time interval of T/2. Integration by the early gate occurs in the T/2 interval preceding the nominal location of data transitions, while the late gate integrates during the T/2 interval following the transition. Gate intervals adjoin but do not overlap. If the timing error is zero, then the data transitions fall exactly on the boundary between early and late gates, as shown in Figure 1-12.

If the timing error is not zero, a transition falls not on the boundary but within one or the other of the gates. Since signal polarity changes within the gate containing a transition, the associated integration reaches a lesser magnitude than when the transition is external to the gate. Comparison of the magnitudes of the two integrators therefore gives an indication of the timing error.

Figure 1-12 Timing diagram for early-late synchroniser

Useful gate output is the integration value that has been accumulated after T/2 sec; so at this point the magnitudes are compared and dumped and the cycle repeats. The resulting error voltage controls the frequency of the VCO, which in turn adjust the sampling point at the gates, so as to minimise the phase error.

In the absence of transitions, no timing information is present and the voltage from both loops are zero. If there is a long run of data without transitions, no error information is supplied to the loop and the phase of the VCO slowly drifts, eventually resulting in cycle slips of the recovered clock.

In a practical system, the held samples are compared sequentially (as seen from the waveforms in Figure 1-12), not simultaneously, which results in simplified circuitry. A more detailed analysis of the Early-Late gate synchroniser can be found in [72] [73].

The Early-Late gates acts to place the boundary between the two gates exactly at the transition instant and departure from this timing generates the loop error. It is also possible to produce an error signal by using a single gate system that straddles the transition. Lindsey and Tausworthe [74] have invented such a scheme, known as the "Digital Data-Transition Tracking Loop" (DTTL). If the transition is exactly centred within this mid-phase gate, integration over the gate interval is zero. If however the transition is not centred, then the integration produces either a positive or negative error output. Sense of the error is determined according to the direction of the transition. In the absence of transitions, no information is presented and the integrator output is ignored.

As for the MAP-Estimator, the early-late synchroniser operates at low signal-tonoise ratios and has been used for deep space exploration [75].

## 1.1.7. Summary of clock recovery architectures

Clock recovery algorithms can be classified into open or closed loop and wide or narrow bandwidth. Table 1-1 summarises the described algorithms and compares their relative performance.

|                                        | CI                      | ass                                                       |          | Performance            |                     |      |          |

|----------------------------------------|-------------------------|-----------------------------------------------------------|----------|------------------------|---------------------|------|----------|

| System                                 | Open/<br>Closed<br>Loop | Band- Tracking Jitter Clock width Range Reject Acqisition | Acqis-   | Clock<br>Fly-<br>Wheel | Imple-<br>mentation |      |          |

| High-Q Resonator                       | Open                    | Narrow                                                    | Poor     | Good                   | Good                | Good | Simple   |

| PLL<br>(wide loop filter)              | Closed                  | Wide                                                      | Good     | Poor                   | Moderate            | Poor | Moderate |

| PLL<br>(narrow loop filter)            | Closed                  | Narrow                                                    | Poor     | Good                   | Poor                | Good | Complex  |

| PLL<br>(frequency detection)           | Closed                  | Narrow                                                    | Moderate | Good                   | Moderate            | Good | Complex  |

| PLL<br>(DLL phase selection)           | Open &<br>Closed        | Narrow                                                    | Poor     | Good                   | Good                | Good | Complex  |

| Quadricorrelator                       | Closed                  | Wide &<br>Narrow                                          | Good     | Good                   | Moderate            | Good | Complex  |

| Gated Oscillator                       | Open                    | Wide                                                      | Good     | None                   | Good                | Good | Simple   |

| MAP-Estimator                          | Open                    | Wide                                                      | Moderate | Good                   | Poor                | Poor | Complex  |

| MAP-Estimator<br>Tracking Synchroniser | Closed                  | Wide                                                      | Moderate | Good                   | Poor                | Poor | Complex  |

| Early-Late Gate<br>Synchroniser        | Closed                  | Wide                                                      | Moderate | Good                   | Poor                | Poor | Complex  |

Table 1-1 Summary of clock recovery algorithms

In general, open-loop algorithms demonstrate rapid clock acquisition and long clock flywheel periods. The exception to this case is the MAP-estimator, which by definition, operates upon historical information (i.e. previously received symbols). Open-loop algorithms also have the advantage that jitters due to noise, are flushed-out of the system and are not regenerated around a closed loop.

For systems that exhibit an accurate and stable symbol frequency, the high-Q resonator provides good overall performance, producing rapid clock acquisition, long flywheel periods and good jitter rejection. Unfortunately, practical considerations make these systems expensive to implement.

The open-loop gated oscillator is simple to implement, provides instantaneous acquisition and exhibits good flywheel performance. However, this algorithm must be rejected for synchronous operation, because the recovered clock inherits all of the symbol jitter. This is unacceptable for a synchronous system, since clock jitter causes the symbols to be incorrectly sampled, resulting in data errors.

A closed-loop algorithm is usually employed, for systems that exhibit symbol rate drift. In order that phase and frequency variations may be tracked, many closed-loop algorithms are based upon the basic PLL.

Appendix 2 concludes with a summary of PLL characteristics, and points out some of the difficulties and undesirable features. These include: instability of a feedback system, conflicting loop parameters, phase variations of the recovered clock relative to the symbols, variable start-up conditions and the need for a long synchronising pre-amble. Techniques such as zero phase start and variable loop time constants may be employed to aid acquisition [55], but these parameters render the loop complex to design and implement.

A PLL with a narrow-loop filter seriously limits the capture range, which is usually less than 10 times its closed-loop bandwidth [62]. For similar noise rejection performance to that of a high-Q resonator, a loop bandwidth of 0.1% is required, which provides a capture range of less than  $\pm 1\%$ . Also, a training sequence of several hundred symbols are required, in order to achieve lock.

Hence, the basic PLL is often modified with frequency detection to extend the capture range and improve acquisition. The most successful of these algorithms is the Quadricorrelator, which employs a wide bandwidth FDD to aid acquisition and a narrow bandwidth PLL once phase-lock is achieved. This improves the capture range to  $\pm 5\%$  and reduces the training sequence to approximately 30 phase-reversal symbols. However, the Quadricorrelator requires the use of an expensive quadrature VCO, and stable designs are difficult to implement.

Other PLL clock synchronisers use a combination of open and closed loops. A DLL is used to provide a selection of clock phases, the optimum of which is chosen to retime the symbols. The DLL can only accept a periodic input and therefore cannot be locked to the input transitions. Hence, the DLL is locked to a local reference frequency. A wide-band PLL takes a snapshot of the symbol timing, which is used to select the optimum clock phase from the DLL. The recovered clock is then taken from the DLL, which operates in an open-loop configuration, relative to the retrieved symbols. The wide-band PLL achieves rapid clock acquisition and the

changeover to an open-loop configuration provides good noise immunity and clock flywheel performance. However, if the data burst is long, drift between the local reference clock and the retrieved symbols, eventually results in cycle slips.

The closed-loop tracking MAP-estimator and the Early-Late gate synchroniser, operate at low signal to noise ratios, providing optimum clock timing for resampling the data. However, these synchronisers are intended for use in coherent communications modems and do not address the problem of rapid acquisition. Hence, clock acquisition is poor, requiring several hundred symbols in order to achieve lock. Also, the MAP-estimator is constrained to a strictly confined pulse shape and is therefore unsuitable for rectangular pulses.

The summary of clock recovery architectures, tabulated in Table 1-1, demonstrates the various performance trade-offs. There is no single algorithm, which satisfies all the requirements of an ideal clock recovery system. The high-Q passive resonator provides good overall performance, with the exception of tracking symbol rate drift. It is possible to implement a high-Q "ringing" filter using DSP techniques, which eliminates many of the practical problems associated with the implementation of a passive resonator. The use of DSP also allows system parameters to be reconfigured "on-the-fly", and this may be exploited to provide an adaptive high-Q tracking filter. Hence, it is the use of DSP to implement a high-Q "ringing" filter, which forms the basis of the new algorithms described in subsequent chapters.

# 1.2. Channel coding

In communications systems the channel code is usually called the transmission or line code, while in magnetic recording it is more commonly known as the modulation or recording code. The time interval between signal transitions significantly affects the ability of a clock recovery system to achieve and maintain synchronisation. Therefore, a channel-coding scheme is in part chosen to provide frequent transitions, so as to aid clock recovery. However, this is often achieved at the expense of channel bandwidth efficiency [76].