# Channel Coding Techniques for a Multiple Track Digital Magnetic Recording System.

## Paul James Davey

A thesis submitted to the University of Plymouth

in partial fulfilment for the degree of

DOCTOR OF PHILOSOPHY

Sponsoring Establishment:

School of Electronic, Communication and Electrical Engineering

Faculty of Technology

Collaborating Establishment:

Hewlett Packard, Computer Peripherals Division (Bristol)

October, 1994

14. NOV. 1994

## UNIVERSITY OF PLYMOUTH LIBRARY SERVICES

Item

No. Class No.

Contl. No.

900 2009991

X702947414

1-621.3804

13 DAV

90 0206999 1

REFERENCE ONLY

# Channel Coding Techniques for a Multiple Track Digital Magnetic Recording System

#### by Paul James Davey

#### **Abstract**

In magnetic recording greater areal bit packing densities are achieved through increasing track density by reducing space between and width of the recording tracks, and/or reducing the wavelength of the recorded information. This leads to the requirement of higher precision tape transport mechanisms and dedicated coding circuitry.

A TMS32010 digital signal processor is applied to a standard low-cost, low precision, multiple-track, compact cassette tape recording system. Advanced signal processing and coding techniques are employed to maximise recording density and to compensate for the mechanical deficiencies of this system. Parallel software encoding/decoding algorithms have been developed for several Run-Length Limited modulation codes. The results for a peak detection system show that Bi-Phase L code can be reliably employed up to a data rate of 5kbits/second/track. Development of a second system employing a TMS32025 and sampling detection permitted the utilisation of adaptive equalisation to slim the readback pulse. Application of conventional read equalisation techniques, that oppose inter-symbol interference, resulted in a 30% increase in performance.

Further investigation shows that greater linear recording densities can be achieved by employing Partial Response signalling and Maximum Likelihood Detection. Partial response signalling schemes use controlled inter-symbol interference to increase recording density at the expense of a multi-level readback waveform which results in an increased noise penalty. Maximum Likelihood Sequence detection employs soft decisions on the readback waveform to recover this loss. The associated modulation coding techniques required for optimised operation of such a system are discussed.

Two-dimensional run-length-limited  $(d, k_y)$  modulation codes provide a further means of increasing storage capacity in multi-track recording systems. For example the code rate of a single track run length-limited code with constraints (1, 3), such as Miller code, can be increased by over 25% when using a 4-track two-dimensional code with the same d constraint and with the k constraint satisfied across a number of parallel channels. The k constraint along an individual track,  $k_x$ , can be increased without loss of clock synchronisation since the clocking information derived by frequent signal transitions can be sub-divided across a number of, y, parallel tracks in terms of a  $k_y$  constraint. This permits more code words to be generated for a given (d, k) constraint in two dimensions than is possible in one dimension. This coding technique is furthered by development of a reverse enumeration scheme based on the trellis description of the  $(d, k_y)$  constraints. The application of a two-dimensional code to a high linear density system employing extended class IV partial response signalling and maximum likelihood detection is proposed. Finally, additional coding constraints to improve spectral response and error performance are discussed.

# **Table of Contents**

| ABSTRACT                                      | ii  |

|-----------------------------------------------|-----|

| TABLE OF CONTENTS                             | ii  |

| LIST OF FIGURES                               | \   |

| ACKNOWLEDGMENT                                | vi  |

| DECLARATION                                   | vii |

| DEDICATION                                    | i   |

| 1. INTRODUCTION                               | 1   |

| 2. BACKGROUND TO THE INVESTIGATION            |     |

| 2.1 MAGNETIC RECORDING OF DIGITAL INFORMATION |     |

| 2.1.1 Digital Recording Theory                | (   |

| 2.1.2 Practical Limitations                   |     |

| 2.2 CHANNEL EQUALISATION                      | 20  |

| 2.2.1 Write Equalisation                      | 2   |

| 2.2.2 Read Equalisation                       |     |

| 2.3 SIGNAL DETECTION                          |     |

| 2.4 MODULATION CODING                         | 27  |

| 2.4.1 Run-Length Limited (RLL) Codes          |     |

| 2.4.2 Charge Constrained (D.CFree) Codes      |     |

| 2.5 CODING SCHEMES.                           |     |

| 2.5.1 Scrambled NRZ (S-NRZ)                   |     |

| 2.5.2 Block Codes                             | 40  |

| 2.5.3 Variable Length RLL Coding              |     |

| 2.5.4 Look-Ahead RLL Codes                    |     |

| 2.5.5 Charge Constrained Codes                |     |

| 2.5.6 Convolutional Codes                     |     |

| 2.6 COMBINED ERROR CORRECTING AND RLL CODING  |     |

| 2.7 MULTI-LEVEL SIGNALLING                    | 55  |

| 2.8 SUMMARY                                   |     |

| 2.9 REFERENCES                                |     |

| 3. EXPERIMENTAL DEVELOPMENT                   |     |

| 3.1 Introduction                              |     |

| 3.2 GATED PEAK DETECTION SYSTEM               |     |

| 3.2.1 Apparatus                               |     |

| 3.2.2 Software                                |     |

| 3.2.3 Experimental Procedure                  |     |

| 3.2.4 Results for System Characterisation     |     |

| 3.2.5 Peak Detection Performance              |     |

| 3.3 SAMPLING DETECTION SYSTEM                 |     |

| 3.3.1 Apparatus                               |     |

| 3.3.2 Read Equalisation                       |     |

| 3.3.3 Adaptive Equalisation                   |     |

| 3.3.4 Results for Pulse Slimming              |     |

| 3.4 DISCUSSION                                |     |

| 3.5 REFERENCES                                | 114 |

|                | D RECORDING DENSITY USING ONE DIMENSIONAL CODIN                                                 | _         |

|----------------|-------------------------------------------------------------------------------------------------|-----------|

|                | S                                                                                               |           |

|                | 10N                                                                                             |           |

|                | LIKELIHOOD SEQUENCE DETECTION                                                                   |           |

|                | i Algorithm                                                                                     |           |

|                | nce Detection                                                                                   |           |

|                | SPONSE SIGNALLING (CORRELATIVE LEVEL CODING)                                                    |           |

|                | ation to Magnetic Recording                                                                     |           |

|                | )NG                                                                                             |           |

|                | ling                                                                                            |           |

|                | misalion                                                                                        |           |

| • • •          | Codes                                                                                           |           |

|                | Codes                                                                                           |           |

|                | ed Spectral Null Codeg for EPR4 Channels                                                        |           |

|                | /-                                                                                              |           |

|                |                                                                                                 |           |

| 4.6 KEFERENCE  | S                                                                                               | 162       |

| 5. TWO DIME    | ENSIONAL CODING                                                                                 | 169       |

| 5.1 INTRODUCT  | ION                                                                                             | 169       |

|                | 3N                                                                                              |           |

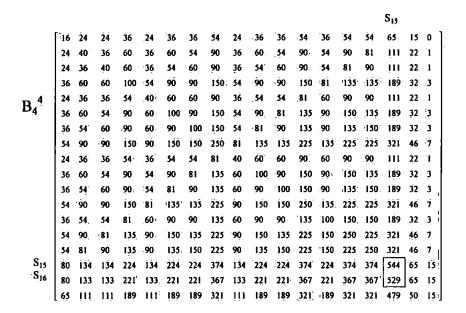

| 5.2.1 Capaci   | ity of Two Dimensional Codes                                                                    | 173       |

|                | Clock Recovery                                                                                  |           |

| 5.3 Two DIMEN  | SIONAL CODING ALGORITHMS                                                                        | 182       |

|                | Coding Technique                                                                                |           |

| 5.3.2 Sliding  | Block Technique                                                                                 | 184       |

| 5.3.3 Enume    | ration                                                                                          | 184       |

|                | e Enumeration                                                                                   |           |

| 5.4 Two DIMEN  | SIONAL CODING FOR EPRML CHANNELS                                                                | 192       |

|                | imensional rate 1/2 (1,8,2;3) code without DC null                                              |           |

| 5.5 COMBINED I | Error Correction & Modulation                                                                   | 196       |

| 5.6 DISCUSSION |                                                                                                 | 199       |

| 5.7 REFERENCE  | S                                                                                               | 201       |

| 6 CONCLUSI     | ONS & FURTHER WORK                                                                              | 203       |

|                | NS                                                                                              |           |

|                | ORK                                                                                             |           |

| APPENDIX A     | PUBLISHED PAPERS.                                                                               | ·         |

| APPENDIX B     | SOFTWARE, WRITTEN IN PASCAL, FOR THE IBM PC COMHOST COMPUTER.                                   | 1PATABLE  |

| APPENDIX C     | SOFTWARE, WRITTEN IN TMS320C25 ASSEMBLY LANGUA<br>DIGITAL COMPACT CASSETTE TAPE RECORDING SYSTE |           |

| APPENDIX D     | DESCRIPTION OF FINITE STATE TRANSITION MATRIX AT                                                | ND FINITE |

# **List of Figures**

| Figure 2.1 Basic Blocks in a Digital Magnetic Recording Channel                                          |      |

|----------------------------------------------------------------------------------------------------------|------|

| Figure 2.2 Record Head Geometry                                                                          |      |

| Figure 2.3 Inter-Symbol Interference induced Peak Shift                                                  |      |

| Figure 2.4 Inter-Symbol Interference induced Droop                                                       |      |

| Figure 2.5 Azimuth Variation as Tape passes Read Head                                                    |      |

| Figure 2.6 Jitter results in amplitude error due to timing uncertainty                                   |      |

| Figure 2.7 Write Precompensation used to equalise a readback signal                                      | 22   |

| Figure 2.8 NRZ & NRZI coding schemes                                                                     | 28   |

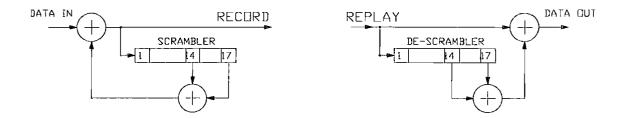

| Figure 2.9 Scrambled NRZ                                                                                 |      |

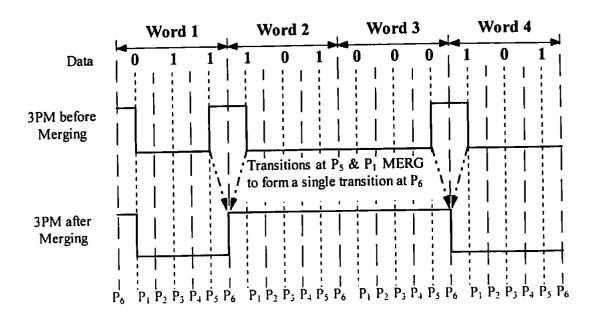

| Figure 2.10 Example 3PM code showing Merging                                                             |      |

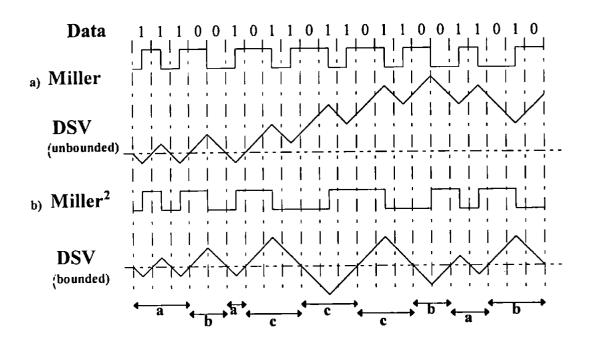

| Figure 2.11 Miller Squared Encoding Sequences                                                            |      |

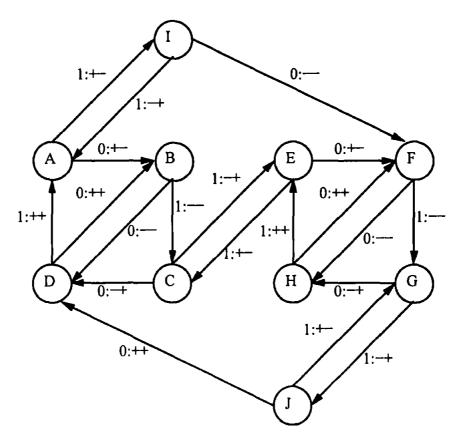

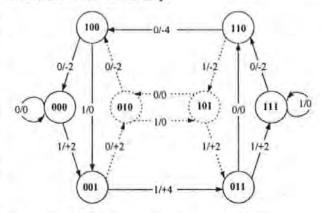

| Figure 2.12 Miller Squared Finite State Transition Diagram                                               | , 50 |

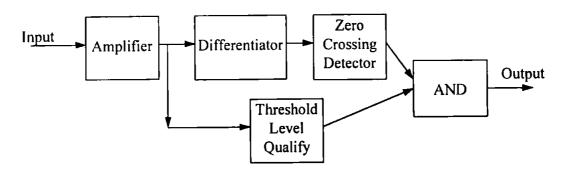

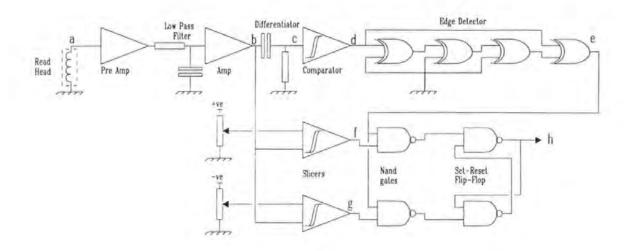

| Figure 3.1 Block Diagram of Gated Peak Detector                                                          |      |

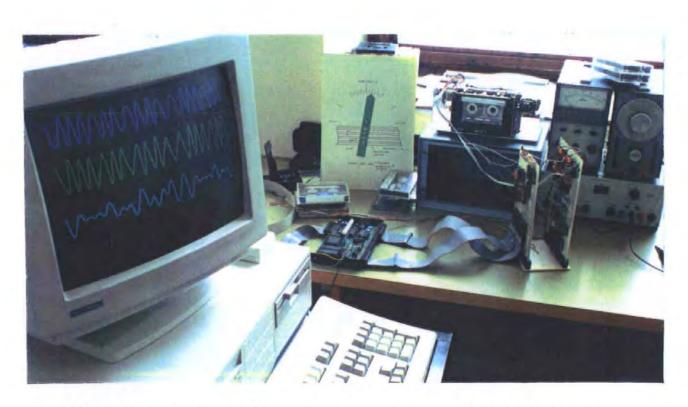

| Figure 3.2 Photograph of Experimental Apparatus                                                          |      |

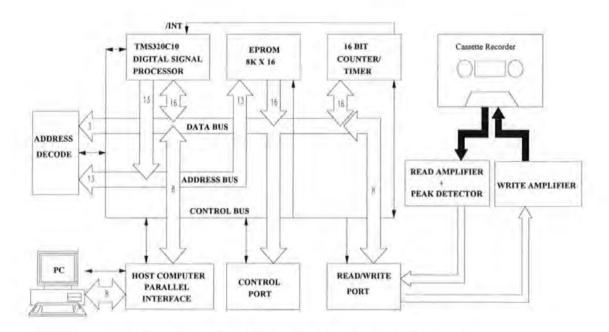

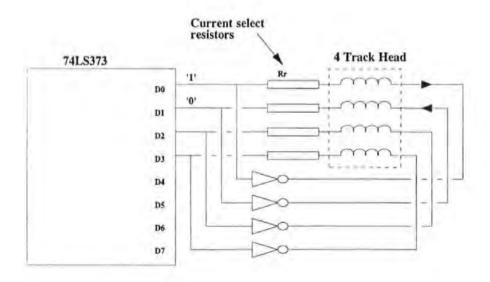

| Figure 3.3 Basic Elements of Recording System 1                                                          |      |

| Figure 3.4 Simple Write Amplifier Circuit                                                                |      |

| Figure 3.5 Read Amplifier including Gated Peak Detector                                                  |      |

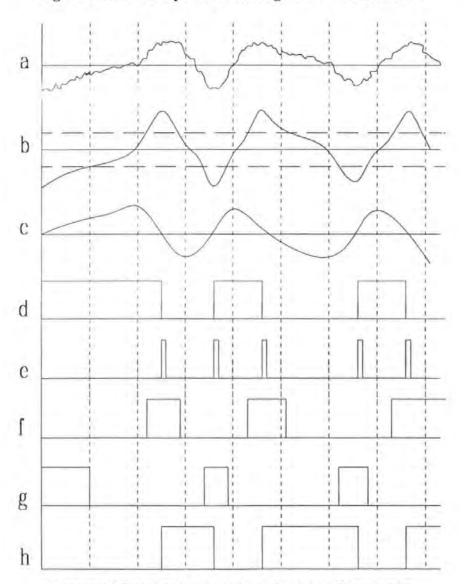

| Figure 3.6 Read Amplifier / Peak Detector Waveforms                                                      |      |

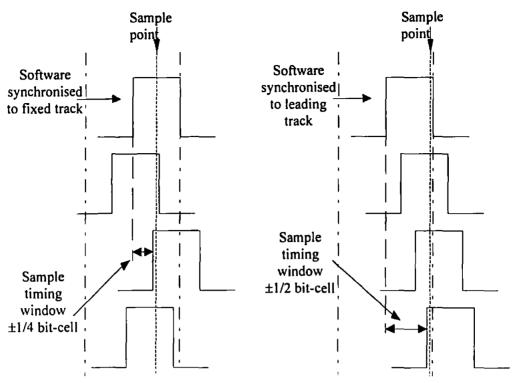

| Figure 3.7 Comparison of (a) fixed track synchronisation (b) leading track synchronisation               |      |

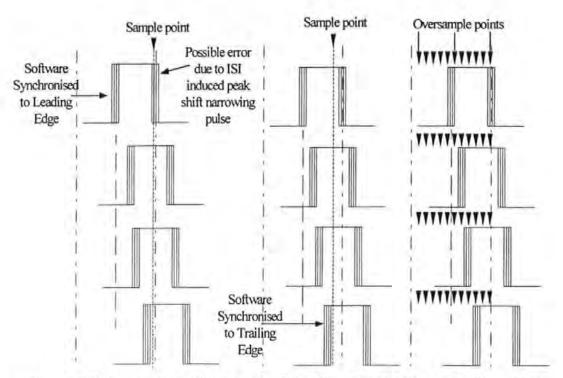

| Figure 3.8 Comparison of a) Leading Edge Synchronisation, b) Tailing Edge Synchronisation and c          |      |

| Oversampled Read                                                                                         |      |

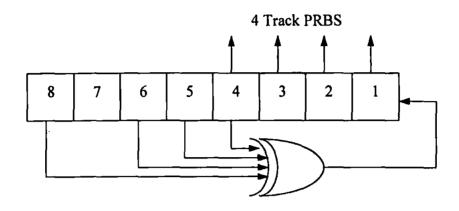

| Figure 3.9 PRBS generator                                                                                |      |

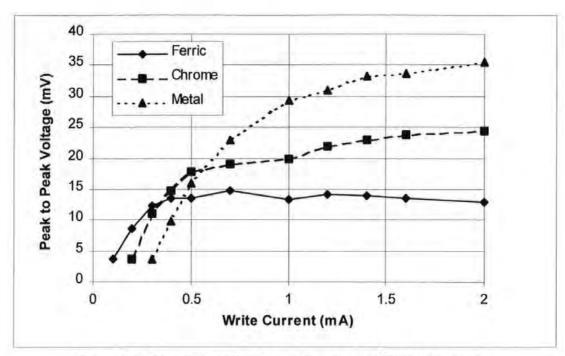

| Figure 3.10 Signal Amplitude as a function of Write Current                                              |      |

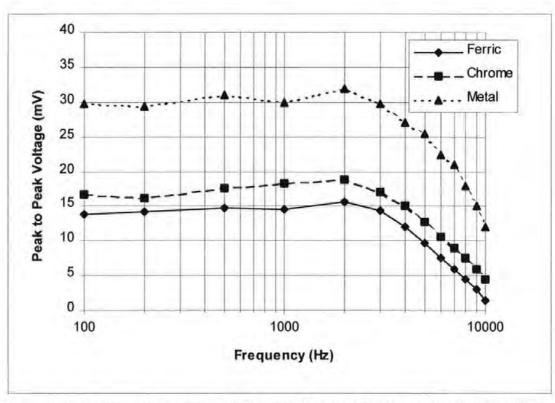

| Figure 3.11 Frequency Response of Compact Cassette System with various tapes                             |      |

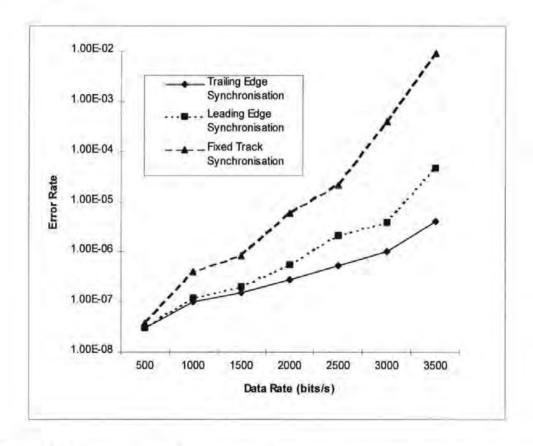

| Figure 3.12 Comparison of Error Rate Performance for various Synchronisation techniques                  | 93   |

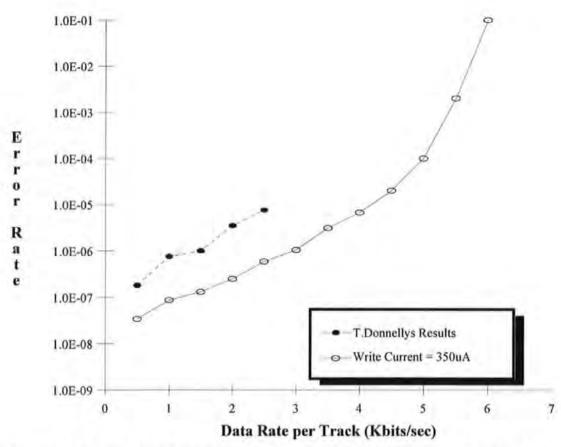

| Figure 3.13 Error Rate Performance for a 4 track Digital Compact Cassette Tape Storage System            |      |

| Employing Bi-Phase-L Code                                                                                |      |

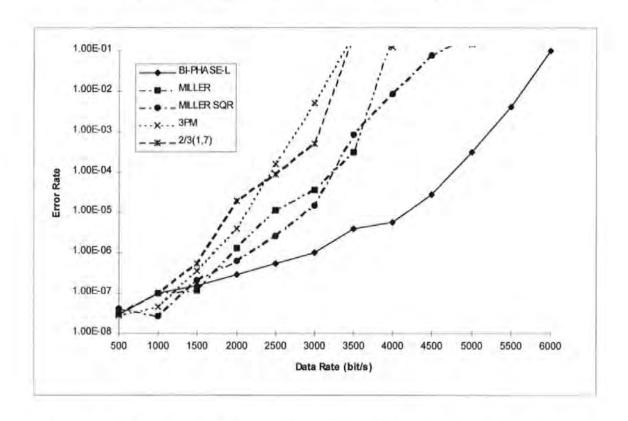

| Figure 3.14 Comparison of Error Rate performance for various Coding schemes                              |      |

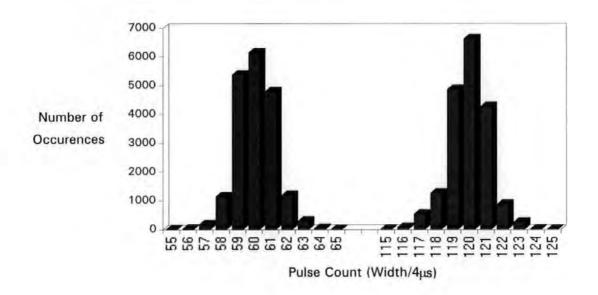

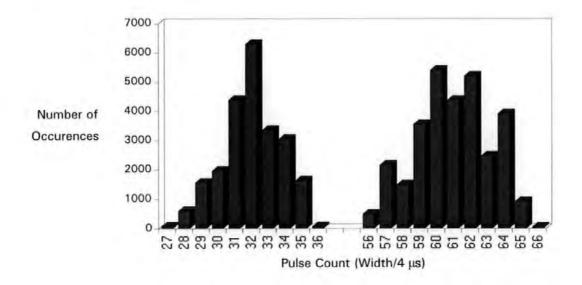

| Figure 3.15 Distribution of Pulse Count (Width) for Bi-Phase-L code at: a) Low Data Rate, b) High        |      |

| Data Rate                                                                                                |      |

| Figure 3.16 Photograph of Recording System employing Sampling Detection                                  |      |

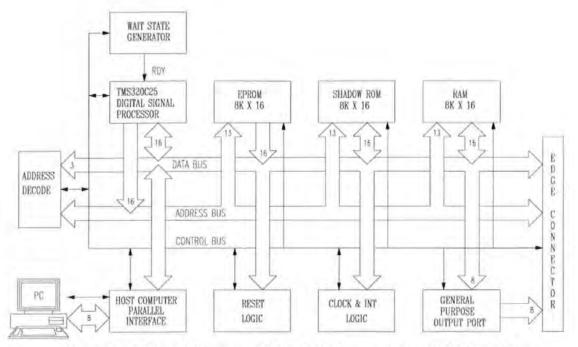

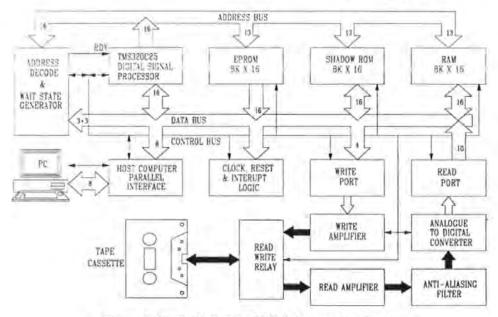

| Figure 3.17 Block Diagram of Digital PCB containing TMS 320C25                                           |      |

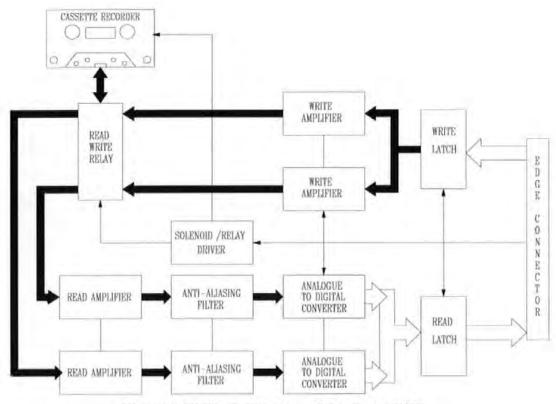

| Figure 3.18 Block Diagram of Analogue PCB                                                                |      |

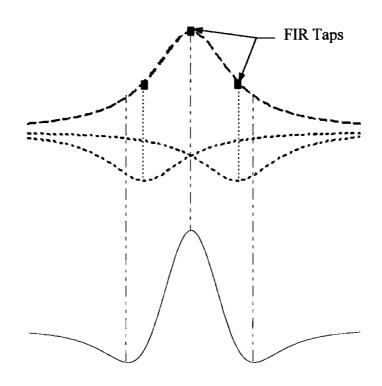

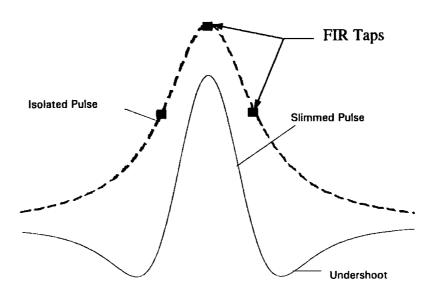

| Figure 3.20 Slimmed Pulse as a result of filter waveforms                                                |      |

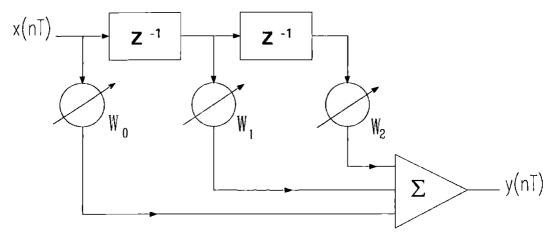

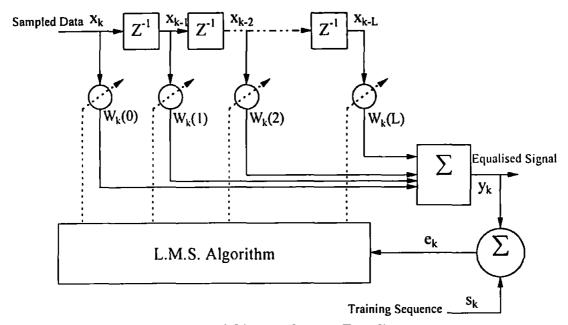

| Figure 3.21 An Adaptive Equaliser                                                                        |      |

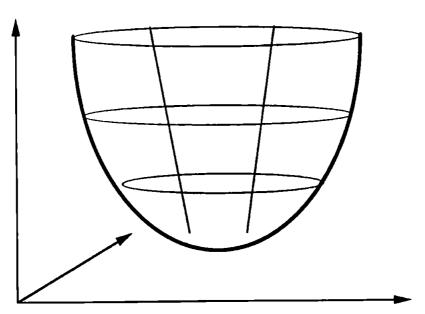

| Figure 3.22 Error performance surface for an Adaptive Equaliser                                          |      |

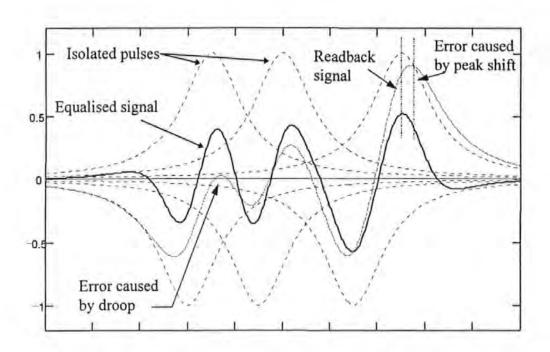

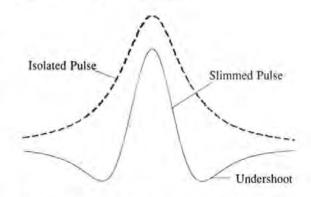

| Figure 3.23 Isolated Lorentzian Pulse Slimmed with a 3-tap Transversal Filter                            |      |

|                                                                                                          | 109  |

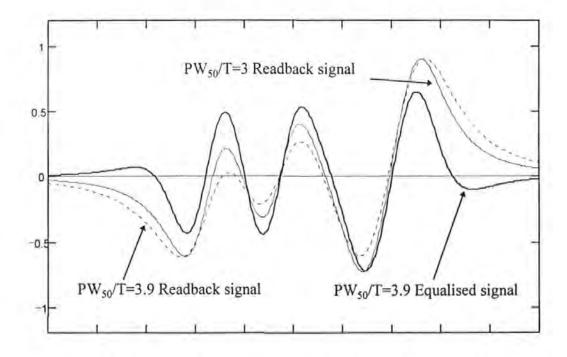

| Figure 3.24 Modelled Equalisation of a Lorentzian Readback Signal at High Recording Density (PW50/T=3.9) | 111  |

| Figure 3.25 Comparison of Unequalised and Equalised Lorenzian Signal of Density PW50/T=3.9 a             |      |

| Unequalisaed Lorentzian Signal of Density PW50/T=3                                                       |      |

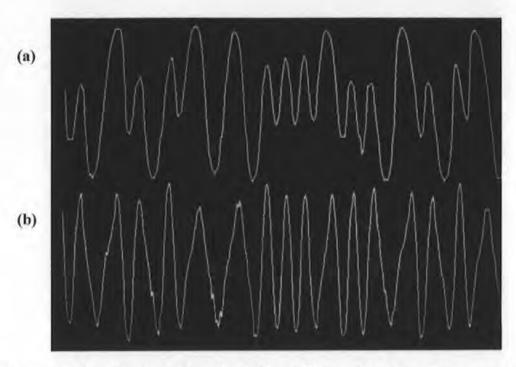

| Figure 3.26 Equalisation of Readback Signal Slimmed via 5-tap Transversal Filter (a) Read signal fi      |      |

| head (b) Read signal after pulse slimming                                                                |      |

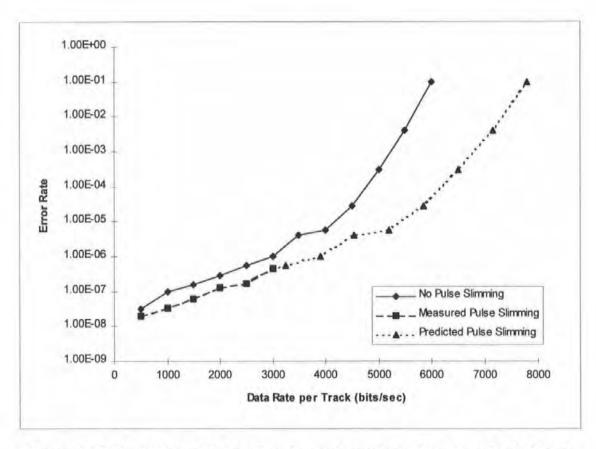

| Figure 3.27 The Effects of Pulse Slimming on Error/Data Rate for a Multi-Track Tape System               |      |

|                                                                                                          |      |

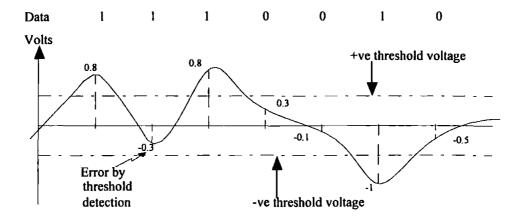

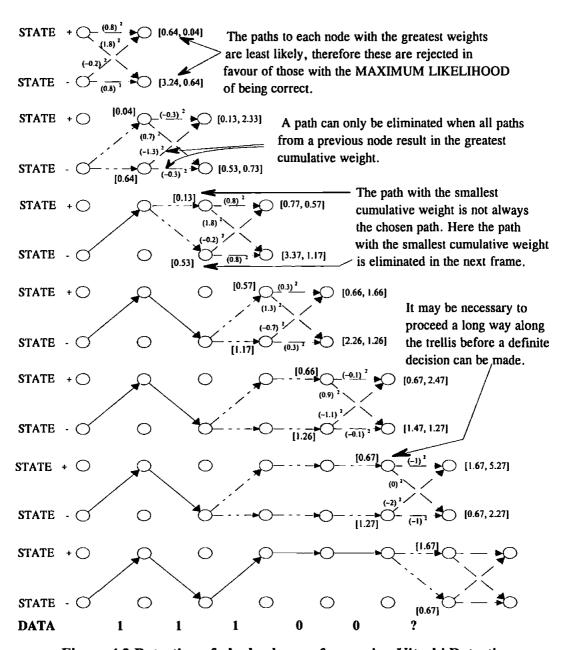

| Figure 4.2 Detection of playback waveform using Viterbi Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 4.1 Equalised Playback waveform                                          | 119 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|

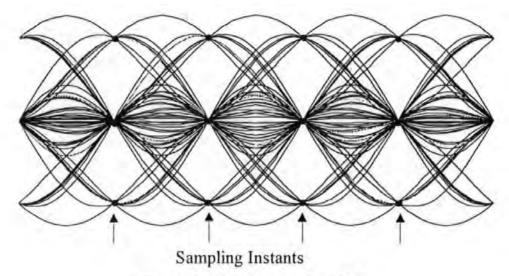

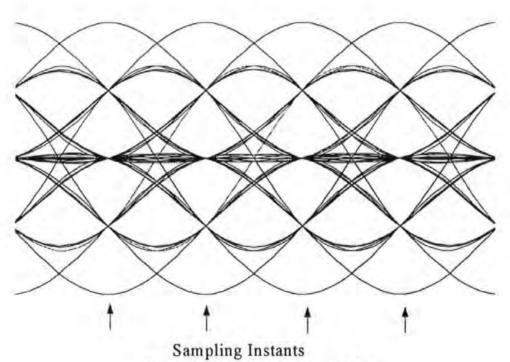

| Figure 4.4 Eye Diagram for EPR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 4.2 Detection of playback waveform using Viterbi Detection               | 119 |

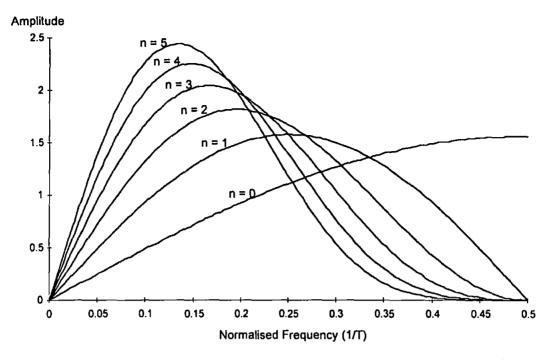

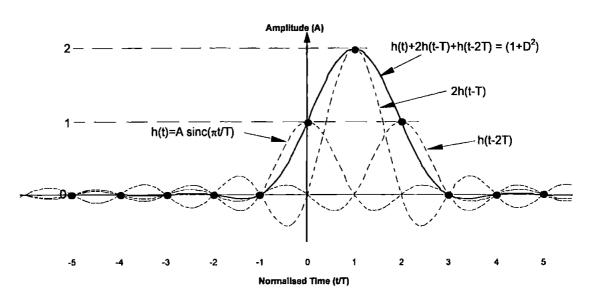

| Figure 4.5 Signal Spectrum for Partial Response Schemes (1-D)(1+D) <sup>n</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |     |

| Figure 4.6 PR4 Step Response $(1+D)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                 |     |

| Figure 4.7 EPR4 Step Response $(1+D)^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 4.5 Signal Spectrum for Partial Response Schemes (1-D)(1+D) <sup>n</sup> | 129 |

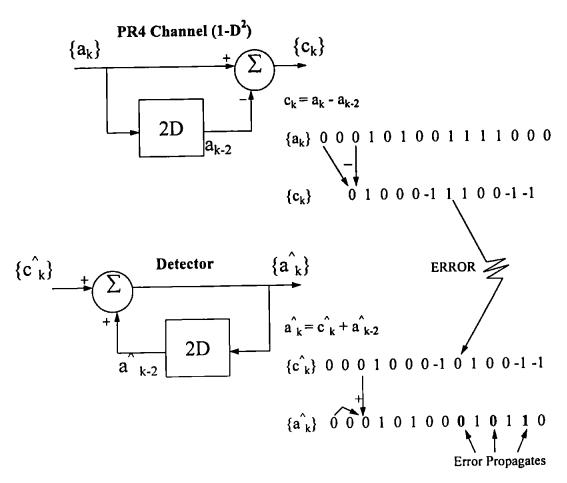

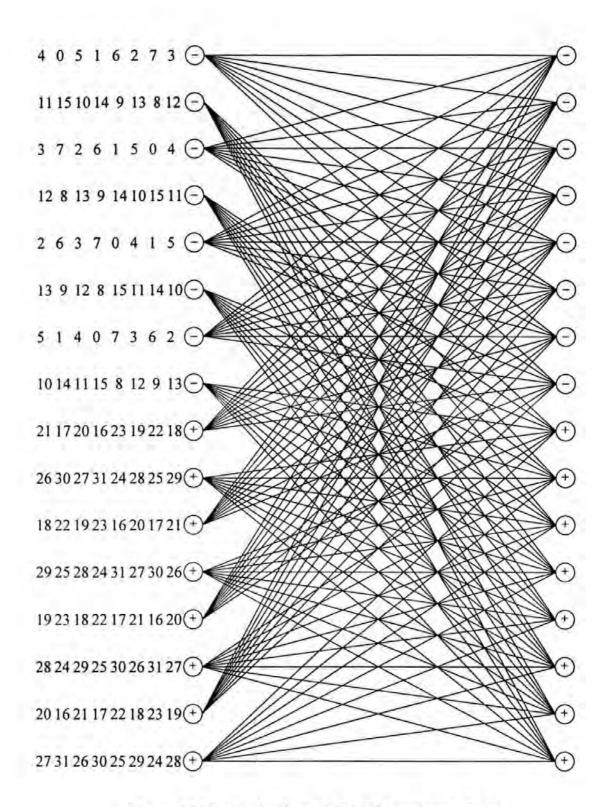

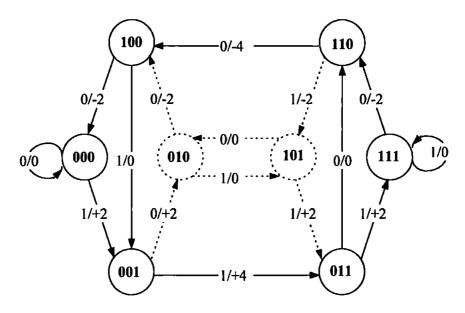

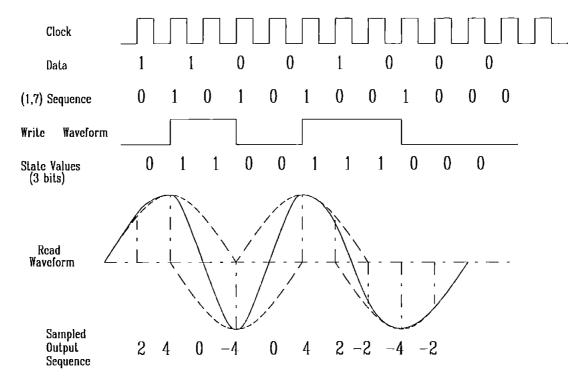

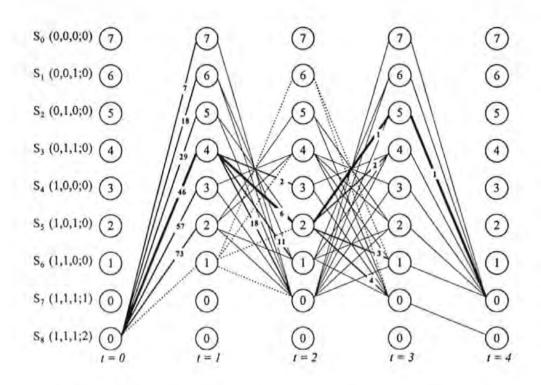

| Figure 4.8 Propagation of Errors in PR4 channel133Figure 4.9 Use of Precoder to prevent Error Propagation133Figure 4.10 Lattice of States for (0, 3/3) code143Figure 4.11 Trellis for Rate 4/5 Wolf-Ungerboeck Code147Figure 4.12 State Diagram for sequences with DSV ≤ 6150Figure 4.13 Trellis Diagram of rate 8/10 MSN code151Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel156Figure 4.15 State Diagram for (1,7) EPRML code157Figure 4.16 (1,7) EPR4 Sequence Detection157Figure 5.2 Construction of Two-Dimensional finite state transition matrix177Figure 5.3 Block Diagram of a Gobal Clock Recovery system181Figure 5.4 Global Clock Recovery waveforms181Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code183Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;188                               | Figure 4.6 PR4 Step Response (1+D)                                              | 130 |

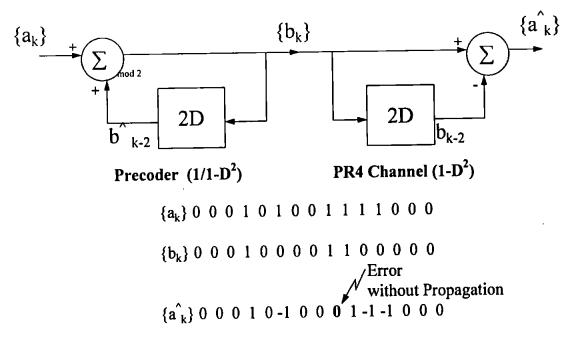

| Figure 4.9 Use of Precoder to prevent Error Propagation.133Figure 4.10 Lattice of States for (0, 3/3) code.143Figure 4.11 Trellis for Rate 4/5 Wolf-Ungerboeck Code.147Figure 4.12 State Diagram for sequences with DSV ≤ 6.150Figure 4.13 Trellis Diagram of rate 8/10 MSN code.151Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel.156Figure 4.15 State Diagram for (1,7) EPRML code.157Figure 4.16 (1,7) EPR4 Sequence Detection.157Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence.176Figure 5.3 Block Diagram of a Gobal Clock Recovery system.181Figure 5.4 Global Clock Recovery waveforms.181Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code.183Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;188                                                                             | Figure 4.7 EPR4 Step Response (1+D) <sup>2</sup>                                | 130 |

| Figure 4.10 Lattice of States for (0, 3/3) code143Figure 4.11 Trellis for Rate 4/5 Wolf-Ungerboeck Code147Figure 4.12 State Diagram for sequences with DSV ≤ 6150Figure 4.13 Trellis Diagram of rate 8/10 MSN code151Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel156Figure 4.15 State Diagram for (1,7) EPRML code157Figure 4.16 (1,7) EPR4 Sequence Detection157Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence176Figure 5.2 Construction of Two-Dimensional finite state transition matrix177Figure 5.3 Block Diagram of a Gobal Clock Recovery system181Figure 5.4 Global Clock Recovery waveforms181Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code183Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;188                                                                       | Figure 4.8 Propagation of Errors in PR4 channel                                 | 133 |

| Figure 4.11 Trellis for Rate 4/5 Wolf-Ungerboeck Code       147         Figure 4.12 State Diagram for sequences with DSV ≤ 6       150         Figure 4.13 Trellis Diagram of rate 8/10 MSN code       151         Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel       156         Figure 4.15 State Diagram for (1,7) EPRML code       157         Figure 4.16 (1,7) EPR4 Sequence Detection       157         Figure 5.2 Construction of Two-Dimensional finite state transition matrix       177         Figure 5.3 Block Diagram of a Gobal Clock Recovery system       181         Figure 5.4 Global Clock Recovery waveforms       181         Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code       183         Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;       188                      | Figure 4.9 Use of Precoder to prevent Error Propagation                         | 133 |

| Figure 4.12 State Diagram for sequences with DSV ≤ 6       150         Figure 4.13 Trellis Diagram of rate 8/10 MSN code.       151         Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel.       156         Figure 4.15 State Diagram for (1,7) EPRML code.       157         Figure 4.16 (1,7) EPR4 Sequence Detection.       157         Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence.       176         Figure 5.2 Construction of Two-Dimensional finite state transition matrix.       177         Figure 5.3 Block Diagram of a Gobal Clock Recovery system.       181         Figure 5.4 Global Clock Recovery waveforms.       181         Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code.       183         Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;       188 | Figure 4.10 Lattice of States for (0, 3/3) code                                 | 143 |

| Figure 4.13 Trellis Diagram of rate 8/10 MSN code151Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel156Figure 4.15 State Diagram for (1,7) EPRML code157Figure 4.16 (1,7) EPR4 Sequence Detection157Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence176Figure 5.2 Construction of Two-Dimensional finite state transition matrix177Figure 5.3 Block Diagram of a Gobal Clock Recovery system181Figure 5.4 Global Clock Recovery waveforms181Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code183Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;188                                                                                                                                                                                                                                        | Figure 4.11 Trellis for Rate 4/5 Wolf-Ungerboeck Code                           | 147 |

| Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel       156         Figure 4.15 State Diagram for (1,7) EPRML code       157         Figure 4.16 (1,7) EPR4 Sequence Detection       157         Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence       176         Figure 5.2 Construction of Two-Dimensional finite state transition matrix       177         Figure 5.3 Block Diagram of a Gobal Clock Recovery system       181         Figure 5.4 Global Clock Recovery waveforms       181         Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code       183         Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;       188                                                                                                                                                     | Figure 4.12 State Diagram for sequences with DSV ≤ 6                            | 150 |

| Figure 4.15 State Diagram for (1,7) EPRML code       157         Figure 4.16 (1,7) EPR4 Sequence Detection       157         Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence       176         Figure 5.2 Construction of Two-Dimensional finite state transition matrix       177         Figure 5.3 Block Diagram of a Gobal Clock Recovery system       181         Figure 5.4 Global Clock Recovery waveforms       181         Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code       183         Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;       188                                                                                                                                                                                                                                                       | Figure 4.13 Trellis Diagram of rate 8/10 MSN code.                              | 151 |

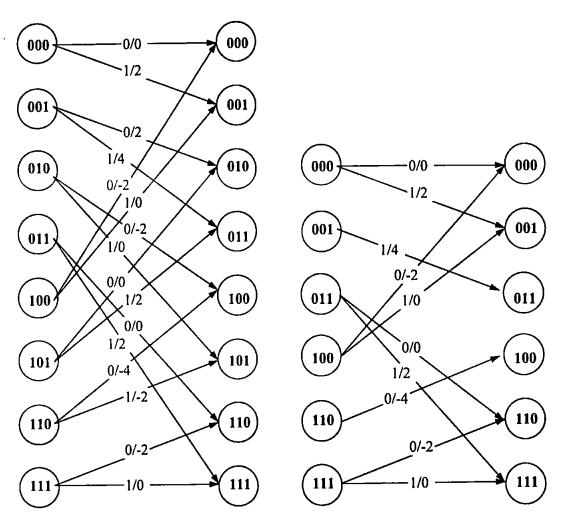

| Figure 4.16 (1,7) EPR4 Sequence Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 4.14 Trellis diagram for a) EPR4 channel b) d=1 constrained EPR4 channel | 156 |

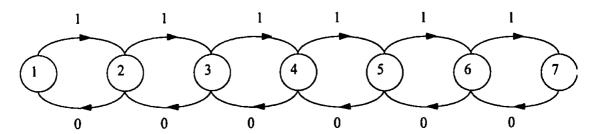

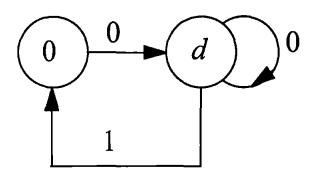

| Figure 5.1 Finite State Transition Diagram for (1,∞) RLL sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 4.15 State Diagram for (1,7) EPRML code                                  | 157 |

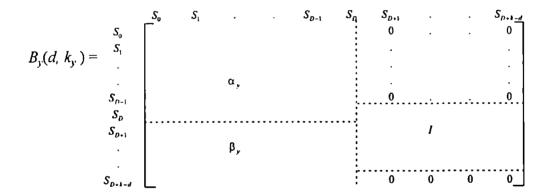

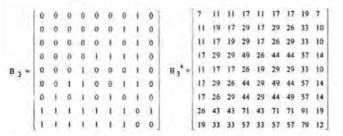

| Figure 5.2 Construction of Two-Dimensional finite state transition matrix 177  Figure 5.3 Block Diagram of a Gobal Clock Recovery system 181  Figure 5.4 Global Clock Recovery waveforms 181  Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code 183  Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM; 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 4.16 (1,7) EPR4 Sequence Detection                                       | 157 |

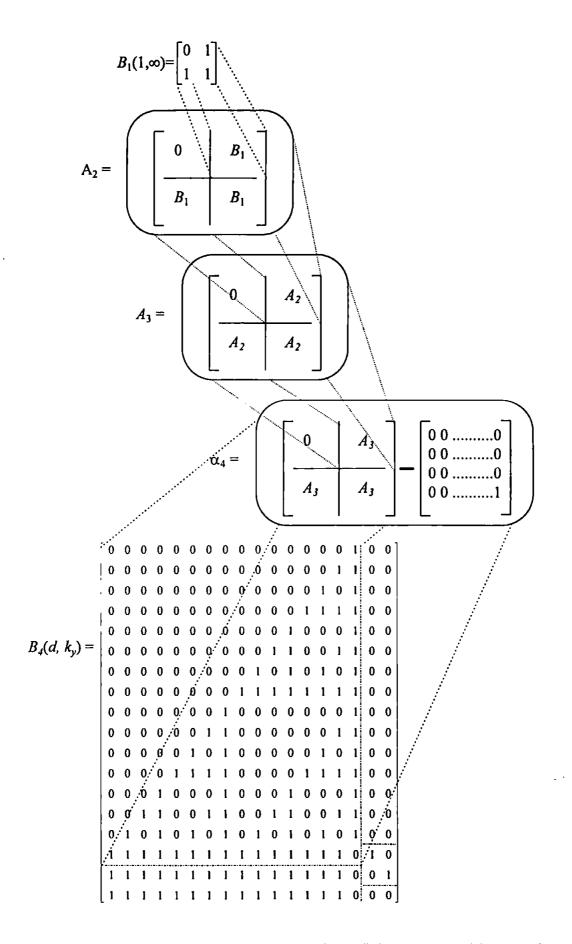

| Figure 5.2 Construction of Two-Dimensional finite state transition matrix 177  Figure 5.3 Block Diagram of a Gobal Clock Recovery system 181  Figure 5.4 Global Clock Recovery waveforms 181  Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code 183  Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM; 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 5.1 Finite State Transition Diagram for (1.∞) RLL sequence               | 176 |

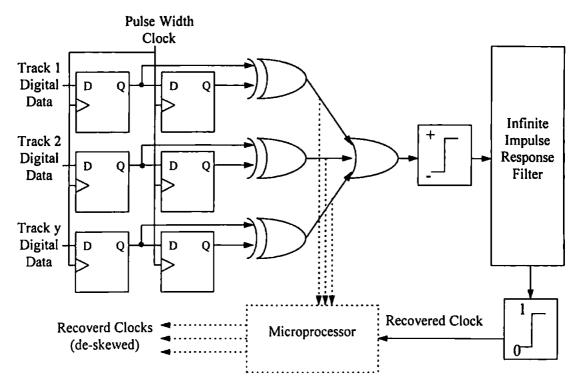

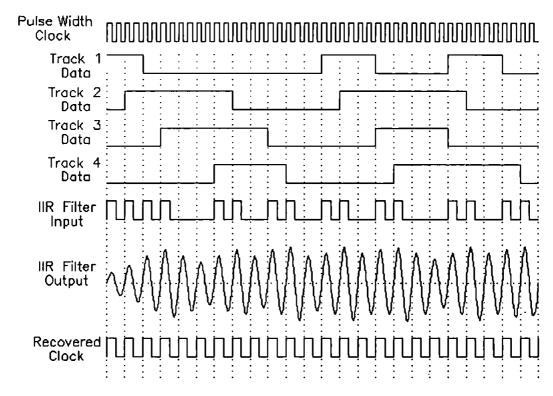

| Figure 5.3 Block Diagram of a Gobal Clock Recovery system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                 |     |

| Figure 5.4 Global Clock Recovery waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                 |     |

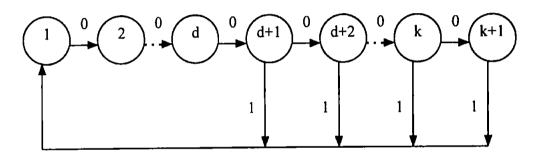

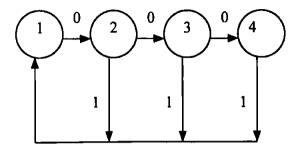

| Figure 5.5 4th Order FSTM for a 4-track (1,3) Two-dimensional code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                 |     |

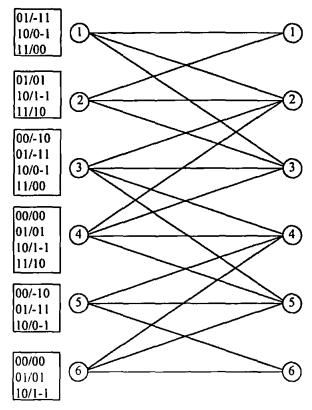

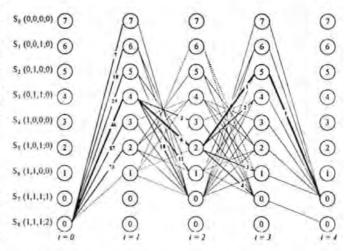

| Figure 5.6 a) Single-Step FSTM; b) Fourth order FSTM;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |     |

# Acknowledgement

I would like to express my gratitude to all those people and organisations who have been associated with this project, in particular:

My supervisors Dr. T. Donnelly (Director of Studies) and Professor D. J. Mapps of the School of Electronic, Communication and Electrical Engineering, for their constant support, encouragement, guidance and friendship throughout the project.

Dr Neil Darragh of the C.R.I.S.T. research group, who, through many interesting and lively discussions has significantly clarified and broadened my knowledge in this area.

Mr. Paul Smithson of the School of Electronic, Communication and Electrical Engineering for his help on clock recovery and interfacing to the TMS320C25 digital signal processor.

My friends and colleagues at the University of Plymouth whose comradeship and encouragement together with innumerable discussions have aided my work immeasurably.

All the technical staff within the School of Electronic, Communication and Electrical Engineering for their practical help.

And, not least of all, to my Parents and my wife Moira, without whose unlimited support, patience, love and understanding this work would not have been possible.

# **Declaration**

I declare that this thesis is the result of my own investigation, and is not submitted in candidature for the award of any other degree. At no time during the registration for the degree of Doctor of Philosophy has the author been registered for any other University award.

During the research programme I undertook a course of advanced studies. These included the extensive reading of literature relevant to the research project, and attendance of international conferences and seminars on signal processing, coding and magnetic recording.

Papers were presented at the Euromicro'92 Conference, Paris, France, 1992 and at the IEEE International Magnetics Conference (Intermag '94), Albuquerque, New Mexico 1994.

Paul James Davey

Date 27/10/94

I dedicate this thesis to my children

Christine and Michael Davey

and to the memory of my grandparents.

Rose & Jim Phillips

#### **CHAPTER 1**

# Introduction

The advent of the *information age* brings an enormous demand for storage of digital data, along with the demands for processing and transmission of such data. For each of the past three decades the capacity of magnetic storage devices has risen by an order of magnitude. Most of this increased storage density has resulted from improvements in the part of the system we call "the channel", which includes the storage medium itself, the read/write heads with associated electronics, and the positioning of these heads.

If we restrict attention to linear density gains, the progress due to advances in signal processing and coding technology has also made a significant improvement to the linear density achievable with a typical set of recording components. However, instead of utilising modern modulation and coding methods that would yield performance closer to the channel capacity, the design engineers for storage systems have taken the alternative approach of increasing the channel capacity itself. This development has resulted in the utilised channel capacity being well below that which is theoretically possible.

Magnetic recording is by far the most popular technique for storing information, in particular magnetic tape has become the predominant means for mass storage of both digital and analogue data. The principal advantage of magnetic tape as a data storage medium is it can store large amounts of information in a relatively small amount of space, and at low cost per bit. In spite of the great progress in optical and electronic

technology, it seems that no viable substitution for magnetic memory, tape or disk, for mass storage will become available in the near future. Therefore, the future trend will be to improve the capacity of current recording techniques through the application of advanced signal processing.

Modern communication theory has played a major role in increasing the efficiency and reliability of communication systems. The aim of this research is to achieve analogous increase in reliability for the storage and retrieval of digital data in magnetic recording systems. More specifically, here the aim is to increase the capacity or packing density of a digital magnetic storage system by increasing the amount of data that can be stored in a unit area of magnetic media. This can be achieved by increasing linear density and/or by increasing the track density. All of this must be accomplished without sacrificing the reliability of the retrieved data.

Recent work at the University of Plymouth has demonstrated the effectiveness of employing a programmable device in the data channel of a recording system. By harnessing the flexibility of a microprocessor in an adaptive manner excellent error/data rate performance has been achieved using a standard cassette mechanism.

It is therefore proposed to extend this work and examine, in part, the application of advanced digital signal processing and, in particular, channel coding schemes to a digital magnetic tape recording system as a means of continuing the increase in density. Techniques are investigated that can more efficiently utilise the available spatial bandwidth of the magnetic recording channel, leading to the desired density increases. A further aim is also to offset the mechanical vagaries of a low-cost tape transport and tape, such as the compact-cassette format, by intelligent software algorithms. The

problem of low signal to noise ratios and high error rates can be alleviated by employing more sophisticated coding schemes that will exploit the multiple-track capabilities of such a system.

Chapter 2 describes the basic elements of a digital magnetic recording channel. The chapter proceeds to describe the sources of error present in the recording channel and some channel coding and equalisation techniques that have been applied to overcome them. Important properties of modulation codes are discussed, in particular run-length limited, and charge constrained modulation codes and their application to the magnetic recording channel. A systematic review is presented of an assortment of various codes that have been adopted in practical storage systems, some of which were also implemented by the author in the peak detect system. The chapter concludes with a description of some alternative modulation coding techniques that include error correction capabilities and multi-level recording.

Chapter 3 describes the initial hardware and software employed in the first stage of the investigation. This system is categorised by the type of detection that was implemented, namely peak detection. The experimental procedure and results pertaining to this system are also given. The chapter continues to discuss the application of a second digital magnetic recording system designed and constructed by the author. This recording system differs from the previous design in that it incorporates a sampling detection system that periodically samples the amplitude of the readback signal and converts the result from the analogue to digital domain, after suitable amplification and filtering.

Finally an equalisation technique employing a digital filter to pulse-slim the readback signal and increase the data rate for a given error rate is also described.

Chapter 4 discusses the application of advanced signal processing techniques, such as Partial Response Signalling and Maximum Likelihood Sequence Detection as a means to further increase linear recording density. The code constraints and several coding techniques, including trellis codes and Matched Spectral Null codes, pertaining to such a system are described in some detail.

Chapter 5 describes a new class of modulation codes that exploits the two-dimensional properties of multi-track digital magnetic recording systems to provide increased areal storage density. Techniques for constructing multi-track codes are discussed and a new technique for implementing a two-dimensional code is presented. The chapter ends by discussing the application of a new two-dimensional code to a multi-track system employing extended class IV partial response and maximum likelihood detection.

Finally the author's conclusions are presented in Chapter 6, together with areas of further work.

#### **CHAPTER 2**

# **Background to the Investigation**

#### 2.1 Magnetic Recording of Digital Information

The magnetic recording process is based on the interaction between the magnetic storage medium and the magnetic head; usually the two are moving with respect to each other. In the recording process the head magnetises the medium, whilst during replay the head generates an induced voltage reflecting the rate of change of magnetisation recorded on the surface.

The magnetic recording channel can be viewed as a communication channel that has a band-pass frequency response which suffers from both amplitude and timing instability and is non-linear due to the hysteresis exhibited by the magnetic medium. Transmission of d.c. is prevented since the read head output voltage is proportional to the derivative of the head flux. The low frequency limit is directly related to the overall physical dimensions of the read head, whereas the high frequency response is limited by the read head gap null, the inductance of the read head and the existence of spacing losses. At

<sup>&</sup>lt;sup>1</sup> This discussion assumes an inductive head. Magneto-Resistive heads produce a signal proportional to the flux rather than the rate of change of flux.

low and medium frequency a recording channel may be rendered linear by the use of a.c. bias.

#### 2.1.1 Digital Recording Theory

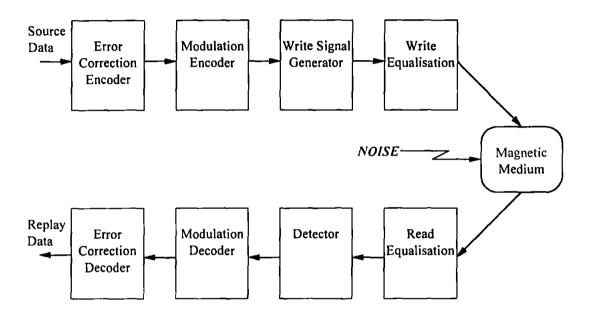

A general block diagram of a digital magnetic recording system is shown in Figure 2.1.

Figure 2.1 Basic Blocks in a Digital Magnetic Recording Channel

Binary source data are first encoded with an error correction code (ECC), then modulation encoded<sup>2</sup>. The modulation encoded data are then sent to a write driver which produces a two level waveform that is written onto the magnetic medium. The magnetisation on the medium is then read back and this *readback* waveform is assumed to have been corrupted by noise. The readback waveform is passed through an equaliser which shapes the spectrum to match a desired target response. Next, the equalised

6

<sup>&</sup>lt;sup>2</sup> A considerable amount of work has been done on combining the ECC and the modulation codes discussed later, however, most current recording systems keep the two processes separate.

waveform is sent to the detector which produces an estimate of the channel data. The estimate is then decoded by the modulation decoder and finally an error correction decoder is employed to recover any errors.

A multiple-track recording system consists of two or more basic systems in parallel, each track usually working independently of the others. However, the multi-track recording system used throughout this thesis employs the operation of several tracks simultaneously. It will be discussed later in this dissertation how parallel channels offer distinct advantages, in terms of recording density and clock recovery, over conventional serial operation.

#### Channel Capacity

Shannon [1] proved that the channel capacity C, could be calculated such that if the maximum information rate R, at which information can be transmitted is less than C, data can be sent error free through a noisy channel. Channel capacity C is defined as

$$C ext{ (bits/second)} = B \log_2 (1 + SNR)$$

eqn{1}

where

B =channel Bandwidth (Hz),

SNR = Signal to Noise Ratio = Signal power (watts) / Noise power (watts).

This classic law assumes Additive White Gaussian Noise (AWGN), i.e. the noise is additive, covers all frequencies and has a Gaussian distribution.

This shows that the bandwidth of a channel and the signal to noise ratio (SNR) may be traded off against each other in achieving the desired capacity.

Mallinson [2] shows that the SNR for a tape of width W may be approximated as

$$SNR = W.N_{pr}(\lambda_{min})^2/2.\pi$$

eqn{2}

where

$\lambda_{min}$  = minimum recorded wavelength,

$N_p$  = number of magnetic particles per unit volume.

Therefore if the width of the tape is divided into y tracks (ignoring guard-bands) the SNR of each track is reduced by 1/y, giving a total channel capacity of

$$C_v = y.B.\log_2(1+SNR/y).$$

eqn{3}

Therefore, from equation {3}the capacity will increase linearly with the number of tracks as will the areal packing density. However, this is at the expense of reduced SNR. In addition, equation {2} shows that doubling the number of tracks reduces the SNR by 3dB, whilst halving the minimum recorded frequency reduces the SNR by 6dB. Hence, it seems beneficial to have a multi-track system operating at a reduced data rate. However, as track widths narrow substantially other sources of noise such as crosstalk and dropouts become more relevant.

Systems that approach the Shannon bound usually incorporate error correction coding, where enough redundancy has been added to the transmitted signal to allow the decoder to detect and correct any errors that might occur.

One of the problems which makes research in signal processing for magnetic channels difficult is that entirely satisfactory models have not been found. The mathematical models which are used today range from finite difference methods requiring supercomputers to linear systems approaches running on personal computers. The models

which accurately capture the essence of a magnetic recording system tend to be far too complex for signal processing applications, whilst the models that are simple enough for use in signal-processing algorithms generally have extreme restrictions on the operating conditions in which they are valid. In addition the noise which one must deal with is non-stationary and not very well characterised and in some cases, such as thin -film media, is data dependent.

Therefore, in this research we have tried to limit channel modelling to a minimum, using real or sampled signals whenever possible. However, this is not always convenient for predicting results.

#### Pulse Superposition

Linear pulse superposition [3] applied to magnetic recording states that the voltage waveform produced by a series of flux reversals is the algebraic sum of a series of isolated pulses, centred on the flux reversals.

Expressed mathematically, the combination of a number x, of isolated pulses p(t), separated by T/2 is

$$e(t) = \sum_{x} (-1)^{x} \cdot p(t + x \cdot \frac{T}{2})$$

eqn {4}

where T = 1/data rate.

Once the shape of the isolated pulse p(t), has been determined, the voltage of the replay signal can be generated by combining pulses with the appropriate spacing for any recorded data sequence at any desired packing density.

#### Non-linear Distortion

The principle of linear superposition is very accurate for systems operating at low densities and at low data rates. However, it has been well documented that the linear superposition model begins to break down as the spatial separation between recorded transitions becomes smaller [4,5]. The most common form of non-linear distortion is non-linear bit shift or non-linear inter-symbol interference. Non-linear bit shift is due to the magnetic field interaction between adjacent recorded transitions and the head field as they are being recorded. The non-linear interaction depends upon the previously written data and as such can usually be precomputed and compensated on the write side with write-precompensation (discussed later).

As the spatial density of the recording system is further increased other non-linear distortions can occur such as partial erasure [6]. These non-linearities are beyond the scope of this investigation and as such are neglected.

#### Lorentzian Model

The accuracy of modelling the channel using pulse superposition is dependent on the shape and width of the isolated pulse used. A simple and frequently used expression to represent the replay signal is given by the Lorentzian pulse described in Equation {5}

$$p(t) = \frac{1}{1 + (\frac{t}{PW_{so}})^2}$$

eqn(5)

where

$PW_{50}$  is the pulse width at half (50%) height.

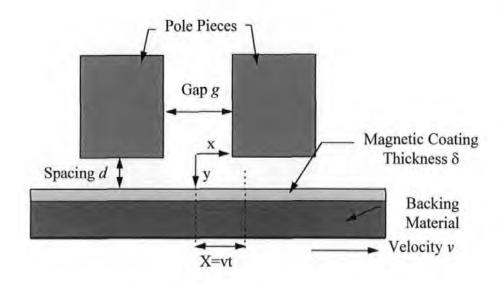

From the work of Karlquist, for distance y > g/2, the head field components, illustrated in Figure 2.2, are:

$$H_{x} = \frac{H_{g}}{\pi} \left[ \tan^{-1} \left( \frac{g/2 + x}{y} \right) + \tan^{-1} \left( \frac{g/2 - x}{y} \right) \right]$$

eqn{6}

$$H_y = -\frac{H_g}{2\pi} \ln \frac{(g/2 + x)^2 + y^2}{(g/2 - x)^2 + y^2}$$

eqn{7}

Figure 2.2 Record Head geometry

A purely longitudinal field results in a symmetrical pulse and a purely perpendicular field produces a dipulse. The resultant response to the current transition is a combination of the two fluxes from the longitudinal and perpendicular component.

Further analysis and development of models for the read/write process is beyond the scope of this research.

#### 2.1.2 Practical Limitations

The recording channel differs from most communication systems in a number of respects. Reliability requirements are usually much higher for magnetic recording systems. For instance, an error rate of 10<sup>-12</sup> or less is not uncommon, also signal power is limited and can not be increased with respect to noise. It is therefore essential to completely define and understand all the error causing mechanisms.

#### Noise

Many communications' systems have only a single type of noise, whereas in magnetic recording channels there are several major sources of error:

- a) media noise,

- b) electronics noise,

- c) read/write noise.

Despite limited amounts of available quantitative data, the behaviour of the noise can be roughly described as follows.

Media noise is due to the manufacturing irregularities and to weak recorded tracking information. Media noise may contain a spike component, due to impurities, which results in such a large noise level that no data bits can be written at those geographic locations on the magnetic surface. The noise also contains a continuous component, which may be due to the non-uniformity of the ferromagnetic material.

All components with resistance generate noise according to their temperature, the electronics and more importantly the read/write head are no exception. Over the normal

operational temperature range this noise is more or less constant. The reading and writing noise contain an electrical component of uncertain spectrum, possibly white, and a mechanical component of coloured spectrum, resulting from the variations in distance between the head, the medium and neighbouring head/medium signals. In general, for a given recording on tape, a better signal to noise ratio will be obtained by moving the tape relative to the head at a higher speed, since the head noise is constant and the signal induced is proportional to speed. This is one advantage that rotary head recorders have over stationary head recorders.

#### Inter-Symbol Interference

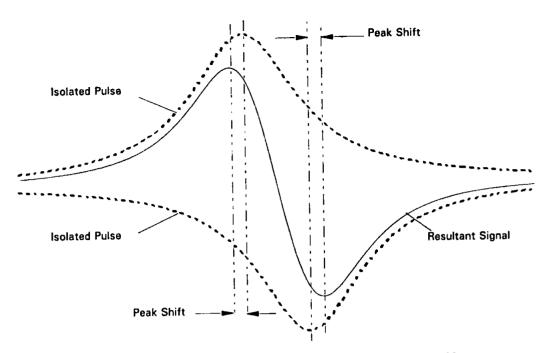

Due to the finite gap of the replay head, increasing the density of recorded data stored on the magnetic medium causes closely spaced magnetic transitions to interfere with one another. This phenomenon, known as Inter-Symbol Interference (ISI) results in peak shift distortion, also known as pulse crowding, and reduction in signal amplitude causing timing and detection errors.

The recording density effectively specifies a length of track or time interval in which each flux reversal is contained. This is termed the bit-cell or bit interval. In digital recording, a large number of output pulse patterns arise. At low densities each pulse is individually resolved. With higher densities the dispersivity of the channel causes each flux reversal to spill over from its cell into the cells of its neighbours. In this way the flux reversals or symbols interact in such a way as to cause distortion.

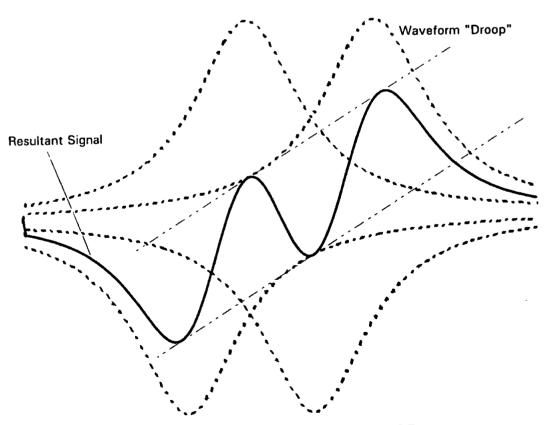

The adverse effects of ISI are manifested in two ways:-

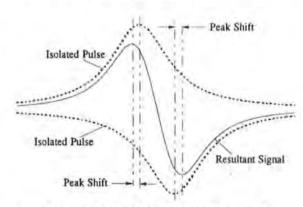

a) Firstly the ISI causes the position of the replay pulse peaks to be shifted, known as 'peak shift'. This causes the signal to be less resilient to the addition of noise and gives rise to a discrepancy in pulse location timing with respect to the original clock time period on writing. Figure 2.3 illustrates the output signal when there is an isolated pair of magnetisation changes separated by a distance t appreciably less than PW<sub>10</sub> (Pulse Width at 10% of its height). The individual signal from each saturation reversal is shown as well as the resultant voltage, obtained by the superposition of the individual pulses.

ð

b) Secondly since the replay pulses alternate in polarity they interfere destructively resulting in a reduction of signal amplitude. This causes the SNR to be reduced and hence causes the probability of error to increase. When a stream of four successive saturation reversals are recorded, the inner pulses are surrounded by two adjacent pulses of opposite polarity and therefore are reduced in peak amplitude to a greater degree than the pulses on the waveforms' extremities. The net effect is to give the waveform the appearance of a 'droop' as shown in Figure 2.4. It is clear that there is also a baseline shift, down for the first half of the waveform and up for the second. Droop is a major disadvantage in peak and threshold detection techniques because at a critical packing density the peaks will no longer cross the zero threshold and as such can no longer be detected.

Figure 2.3 Inter-Symbol Interference induced Peak Shift

Figure 2.4 Inter-Symbol Interference induced Droop

#### Azimuth Variation (Skew)

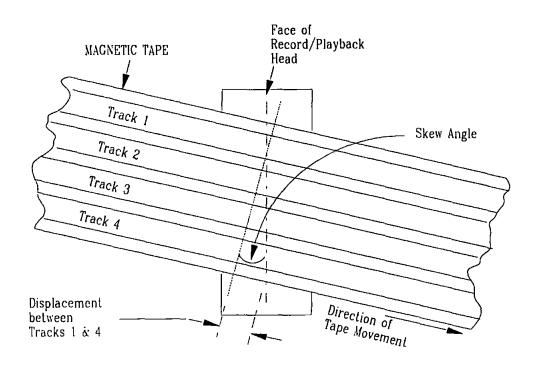

The initial task of the channel decoding process is to detect transitions in the data stream and from this decide at what point the data should be sampled. If all tracks are sampled simultaneously, tape-azimuth variations, also known as skew, need to be taken into account. Ideally, the tape should pass perpendicularly to the head, in a straight line. However, in practice, due to the limited tape guidance system and imperfect slit edges, the tape weaves across the head producing a constantly varying skew angle, illustrated in Figure 2.5.

At low linear packing densities this is not a significant problem as the magnitude of skew is insufficient to cause the sample point to drift into the next bit cell. However, as the linear packing density increases, the magnitude of the data-skew (measured in bits) between tracks increases up to a point where it can become the most significant cause of errors.

Several attempts [7-10] to compensate for the azimuth variation have been reported which involve dynamically rotating the read head to correspond with the maximum amplitude of the readback signal. However, this method is mechanically expensive and generally outweighs the cost of a better tape guidance system. An alternative software solution employed by Donnelly [11] involves initially sampling the readback signals, computing the degree of skew and then re-aligning them digitally. Although more computationally intensive, the electronics to perform this technique are relatively inexpensive but are limited by speed of operation. Since azimuth variations change slowly with respect to the data rate this does not pose a major problem.

Figure 2.5 Azimuth Variation as Tape passes Read Head

#### Jitter

In analogue audio equipment timing instability of the readback waveform gives rise to wow and flutter: in digital recording this term is referred to as *jitter*. In the main jitter is largely due to head-tape velocity variation. Magnetic tape transports are designed to provide a linear motion of the tape with as little variation as possible. However, in practice the combination of mechanical and electrical tolerances for the tape drive in conjunction with environmental factors such as vibration, etc., result in velocity variations exceeding the specified tolerance [12].

Static friction (stiction) between the in-contact head and slow moving tape can cause micro velocity changes which are excited by the flexibility and surface irregularities of the tape. Together these are also responsible for the most significant amount of jitter.

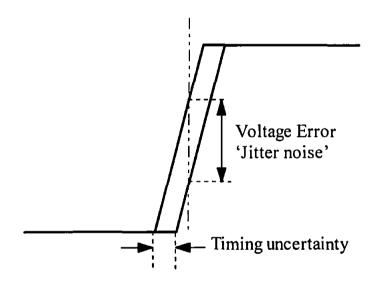

Figure 2.6 illustrates how jitter causes uncertainty about the signal voltage relative to a stable time reference for a signal with a finite rate of change of voltage; this has the same effect as noise. Since jitter is directly proportional to the rate of change of voltage in the readback signal the degree to which it affects the error rate increases with frequency. This introduces an important channel code parameter, the *jitter margin*  $T_{w}$  also termed window margin or phase margin, that determines the tolerance in locating a transition in a bit cell. It is defined as the permitted range of time over which a transition can still be received correctly, divided by the data bit cell period T. In general the larger the value of  $T_{w}$  the better since it has the effect of reducing peak shift distortion.

Figure 2.6 Jitter results in amplitude error due to timing uncertainty.

In a sampling system, a finite amount of variation in the sampling clock can lead to timing jitter. This has to be carefully controlled since this has the potential to cause more catastrophic errors than in the previous type of jitter. Since the theory underlying the correct operation of most digital signal processing techniques, such as filtering etc., relies on samples at regular intervals.

#### **Dropouts**

Many shallow drops in the envelope of the readback signal can be observed in high density digital magnetic recording. Asperities and discontinuities in the recording medium cause hard dropouts which have a drastic effect on the recorded signal, however these are minimised by modern medium manufacturing techniques. More common are losses in level caused mainly by instantaneous increases in the separation between the tape and the head due to surface roughness of the tape and debris such as dust and oxidised particles. These are termed soft dropouts. Increase in separation causes not only a drop in the envelope but also a loss of amplitude in the higher frequencies of the readback signal. Perry et al. [13] have demonstrated how a microprocessor based system can be used to characterise the effect of dropouts for a high density digital magnetic tape system. Meeks [14] further describes how an appropriate error correction strategy can be selected once the dropout characteristics are determined.

#### Crosstalk

To increase track density care must be taken that the tracks are not so closely spaced that serious pickup leakage interference arises from adjacent recorded tracks. Since the amount of leakage increases with the wavelength of the recorded signal, (similar to the separation loss), the leakage can become pronounced potentially resulting in problems at low frequencies. This type of noise is termed crosstalk and can be considered as similar to the influence of Gaussian noise, since the leakage power is restricted to lie within the low frequency range and the random data signals recorded on the tracks are presumed to have no correlation with each other. Hence channel codes that have little or no low frequency response are less prone to crosstalk induced errors.

#### 2.2 Channel Equalisation

To enhance the performance of the magnetic recording channel at high packing densities appropriate equalisation techniques must be applied to match the frequency and phase response of the recording channel to that of the recorded signal. Equalisation is the process that modifies the transfer function of the analogue channel to provide more reliable data detection by compensating for the channel distortions such as ISI and peak shift. However, the improvement in the channel transfer function is usually accompanied by a degradation in signal to noise ratio, resulting from boosting the high frequencies where there is little signal and much noise. Therefore, although any degree of equalisation can be theoretically applied, the equaliser design will usually be a compromise between the required transfer function and the resultant loss in SNR due to equalisation.

The choice of equalisation depends upon the following:

- a) the amount of inter-symbol interference to be compensated,

- b) the modulation code,

- c) the detection technique used,

- d) the signal to noise ratio,

- e) the noise spectrum shape.

Channel equalisation may be implemented either prior to the recording process, in which case it is referred to as write equalisation or write precompensation, or during the replay process where it is termed read or post equalisation or simply just equalisation.

#### 2.2.1 Write Equalisation

Write equalisation attempts to modify the spectral components of the signal to be recorded or written to match the frequency response of the channel. The principle benefit of write equalisation is that all the signal conditioning is performed before noise is introduced into the system, hence reducing noise in the readback signal relative to post-equalisation.

However, in practice it is difficult to provide correct equalisation using a write equaliser alone since the channel response is constantly varying due to tape surface asperities, substrate irregularities and the intimacy of the head contact and wear. These variations attenuate the high frequencies much more than the low frequencies which undermines any predicted or fixed equalisation scheme.

Write equalisation can be sub-divided into three different techniques:

#### Amplitude write equalisation

This method varies the amplitude and/or shape of the write current so that it is no longer a binary signal. Jacoby [15] suggested a cosine equaliser, which is sometimes used for read equalisation, to shape the write current. This technique is not popular due to the need for complex write-side electronics.

#### Precompensation

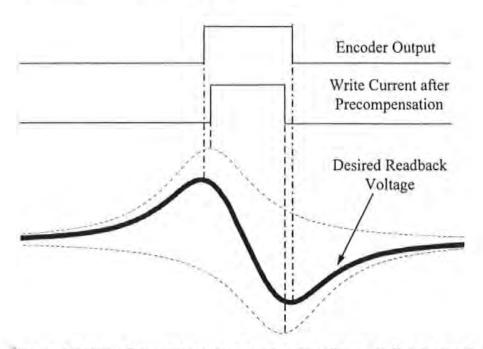

Precompensation is the favoured technique for write equalisation in the magnetic recording channel since it is data dependent and maintains a binary write signal and is therefore relatively easy to implement. Equalisation is achieved by repositioning the write transitions to offset peak shift in the readback signal [16]. For example, consider the binary signal 0110, as shown in Figure 2.7. The first transition could be written slightly later than its normal clock time and the transition of the second bit slightly earlier in time. This precompensation effectively uses a controlled amount of intersymbol interference to improve the overall readback performance by reducing peak shift of the two pulse peak relative to the clock window centres. Since the data to be recorded is known, a set of precompensation rules can be implemented to deal with the data patterns that create the worst-case performance.

Other methods include the use of redundant magnetic transition pairs at strategic locations on the write waveform [17,18].

Figure 2.7 Write Precompensation used to equalise a readback signal

#### Precoding

Both Tomlinson [19] and Harashima and Miyakawa [20] independently proposed precoding as a means of equalisation over twenty years ago. This technique employs a feedback transversal filter whose impulse response is the inverse of the channel and which can also maintain a binary write signal through the use of modulo-two arithmetic. This technique although not yet fully utilised in magnetic recording has been used, in conjunction with Trellis Coded Modulation, with great success for achieving increased data rates in telephone-line modems [21].

#### 2.2.2 Read Equalisation

This method refers to the use of a linear filter at the output which changes the overall impulse response of the system before the peak detector.

Since read equalisers operate on the signal after noise has been added by the channel the noise spectrum is modified as well as the signal. Therefore an improvement in distortion is usually accompanied by a degradation in signal to noise ratio.

The equaliser increases the bandwidth of the signal by compensating for the loss in high frequencies produced by the recording channel. The increase in bandwidth results in a narrower pulse in the time domain, which has the effect of reducing pulse interaction and hence reduces ISI induced peak shift. However, the amplification of the higher frequency components of the signal spectrum extends the noise power spectral density causing an increase in average noise power. Hence, noise induced peak shift is increased. This trade off between ISI and noise-induced peak shift is the basis of equaliser design.

#### Pulse Slimming

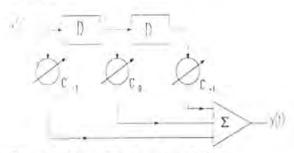

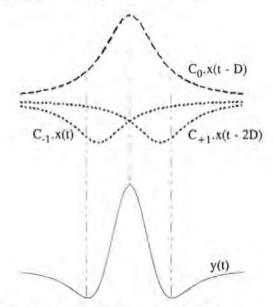

Pulse slimming is a time domain approach to read equalisation, its purpose being to create a channel whose isolated transition response is a thinner pulse than that produced by the unequalised channel. Many different types of pulse-slimming filters have been used to reduce adjacent pulse interference [22-28].

Jacoby [23] describes one of the more classic equaliser circuits, achieved by a resistor, inductor, capacitance network which controls signal amplitude and phase separately.

Kameyama [25] described a cosine equaliser, that slimmed an isolated pulse by approximately 30% when the SNR at the input is 35dB. The basic circuit is composed of a delay line, an amplitude divider and a differential amplifier. The delay line is terminated with a matching impedance at the input and is open ended at the output so that the signal is completely reflected. This causes the incoming and reflected pulse to add constructively and therefore double in amplitude. For an input signal of  $f_i(t+\tau)$  the output of the equaliser  $f_o(t)$  is expressed as

$$f_0(t) = 2f_i(t) - K(f_i(t+\tau) + f_i(t-\tau))$$

eqn {8}

where  $\tau$  is the delay and K is the ratio of the amplitude divider.

The resultant transfer function of this equaliser described in the frequency domain is

$$F(\omega) = 1 - K \cos(\omega \tau) \qquad eqn\{9\}$$

hence the name cosine equaliser.

#### 2.3 Signal Detection

Whereas there have been significant technology developments in read/write heads, magnetic media and servo systems, the analogue *Peak Detection* [29] method of data recovery has remained largely unchanged for over 25 years.

Data detection in the conventional peak detection magnetic recording channel is achieved by first differentiating the analogue signal and then processing the differentiated signal with a zero crossing detector to determine the presence or absence of a zero crossing event within the detection window. In the absence of noise or other imperfections the zero crossing of the derivative signal in peak detection occur only at times corresponding to the clock times at which a transition was written. Enhancements such as precompensation, Run-Length-Limited codes and more sophisticated detectors have extended the performance of peak detection systems.

The peak detector has the advantage of being both robust and extremely simple to implement. However, by its very nature it performs best at low linear densities. The underlying technique used in all peak detection systems is termed a *hard limited* process. The output is determined to be either above or below a decision threshold and performs *hard decisions* on each bit (symbol-by-symbol) coming out of the channel. In doing so this method of detection looses information about how close the signal is to the threshold and as such how *good* the decision was. If the data bits passing through a channel are independent of one another the performance of the detector is optimum. However, modulation coding introduces correlation among the bits in a sequence and therefore a hard-decision detection is not optimum.

An optimum detection process for correlated data uses a *soft decision* algorithm that decides the result based on past, present and future decisions being above or below a decision threshold and then gives a measure of "goodness" or confidence that determines how close the result was to the threshold level.

Therefore, whilst the peak detector has been acceptable in the past in terms of simplicity, low cost and speed, it has become increasingly apparent that to make more efficient use of available bandwidth a more sophisticated detection method is required. Recent attention has focused on sampling detection and an entirely new type of modulation coding and signal processing, a revolutionary rather than evolutionary approach. These techniques are described further in chapter 4.

A prime requirement in a digital communication channel employing soft decision detection is that the amplitude of the readback signal is periodically sampled. Historically this has prevented the graduation to digital signal processing due to the high speed requirements of many storage systems and the high cost of fast silicon. Hence, only recently, with the introduction of high speed compact mixed digital and analogue signal processors, such techniques have been made feasible. Conversion from the analogue to digital domain also permits other advanced DSP techniques to be performed on the signal such as adaptive equalisation and clock recovery.

### 2.4 Modulation Coding

In coding for a magnetic recording channel using saturation recording, engineers are presented with overcoming an array of potential problems, some of which are not clearly understood. As opposed to most communication systems:

- (a) timing recovery must be obtained from the modulated data,

- (b) the noise is non-white and may have a (pattern dependent) multiplicative nature,

- (c) most detection systems are sub-optimal,

- (d) uncertainty in channel characteristics must be tolerated,

- (e) inter-symbol interference dominates at high recording densities.

Due to the differentiating nature of the read head, only polarity changes in the magnetic-medium saturation produce significant energy at the output of the read electronics. As such, the magnetic channel is often modelled as the linear superposition of these step responses. Since timing recovery must be obtained from the channel response to the modulation code all modulation codes require relatively frequent changes in magnetic saturation.

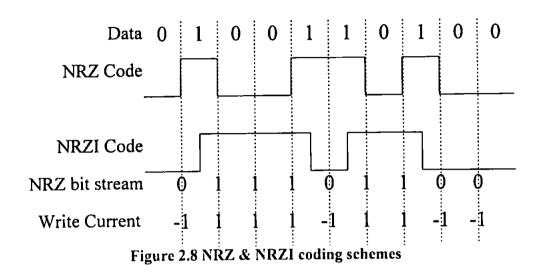

Two common notations used to designate magnetic modulation codes are *Non-Return* to *Zero* (NRZ) and *Non-Return to Zero Increment* (NRZI). Actual recording bits consist of saturation in one direction (+1) or in the other (-1). In NRZ notation a charge in one direction of saturation is referred to as a '1', whilst a charge in the opposing direction is referred to as a '0'. In NRZI notation a change in direction of saturation is referred to as a '1' and no change i.e. constant state of saturation is referred to as '0'. In

NRZI coding, the modulation code first undergoes a precoding operation to convert to a NRZ bit stream. The NRZ bit stream is level shifted and amplified to produce the actual recorded bits (write current), illustrated in Figure 2.8.