# THE APPLICATION OF REAL-TIME SOFTWARE IN THE IMPLEMENTATION OF LOW-COST SATELLITE RETURN LINKS

by

#### JAMES TOM SLADER

A Thesis submitted to the University of Plymouth in partial fulfilment for the Degree of

#### DOCTOR OF PHILOSOPHY

Satellite Research Centre

Department of Communication and Electronic Engineering

Faculty of Technology

October 2001

| UNIVERSITY OF PLYMOUTH |                    |  |

|------------------------|--------------------|--|

| Item No.               | 9004983271         |  |

| Date                   | - 8 NOV 2001 T     |  |

| 1 38 No.               | THESIS 621.382 SLA |  |

| Julia No.              |                    |  |

|                        | PLYMOL             |  |

REFERENCE ONLY

LIBRARY STORE

## THE APPLICATION OF REAL-TIME SOFTWARE IN THE IMPLEMENTATION OF LOW-COST SATELLITE RETURN LINKS

#### by James Tom Slader

#### Abstract

Digital Signal Processors (DSPs) have evolved to a level where it is feasible for digital modems with relatively low data rates to be implemented entirely with software algorithms. With current technology it is still necessary for analogue processing between the RF input and a low frequency IF but, as DSP technology advances, it will become possible to shift the interface between analogue and digital domains ever closer towards the RF input. The software radio concept is a long-term goal which aims to realise software-based digital modems which are completely flexible in terms of operating frequency, bandwidth, modulation format and source coding. The ideal software radio cannot be realised until DSP, Analogue to Digital (A/D) and Digital to Analogue (D/A) technology has advanced sufficiently. Until these advances have been made, it is often necessary to sacrifice optimum performance in order to achieve real-time operation. This Thesis investigates practical real-time algorithms for carrier frequency synchronisation, symbol timing synchronisation, modulation, demodulation and FEC. Included in this work are novel software-based transceivers for continuous-mode transmission, burst-mode transmission, frequency modulation, phase modulation and orthogonal frequency division multiplexing (OFDM).

Ideal applications for this work combine the requirement for flexible baseband signal processing and a relatively low data rate. Suitable applications for this work were identified in low-cost satellite return links, and specifically in asymmetric satellite Internet delivery systems. These systems employ a high-speed (>>2Mbps) DVB channel from service provider to customer and a low-cost, low-speed (32-128 kbps) return channel. This Thesis also discusses asymmetric satellite Internet delivery systems, practical considerations for their implementation and the techniques that are required to map TCP/IP traffic to low-cost satellite return links.

### Contents

| I. Introdu | ction                                                                |

|------------|----------------------------------------------------------------------|

| 1.1 Int    | roduction and Background to Digital Modems & Software Radio          |

| 1.1.1      | Outline Baseband I/Q and Digital Low IF Modulators                   |

| 1.1.2      | Outline Baseband I/Q and Low IF Demodulator Structures               |

| 1.1.3      | Software Radio                                                       |

| 1.2 Ar     | oplication of Software-Based Signal Processing in Low-Cost Satellite |

| Return Lin | nks                                                                  |

| 1.2.1      | Introduction to Low-Cost Satellite Return Links                      |

| 1.2.2      | Signal Processing Requirements in Low-Cost Satellite Return Links    |

| 1.2.3      | Satellite Internet Delivery Systems                                  |

| 1.3 Or     | ganisation of Thesis                                                 |

| 2. A Dopp  | oler Tracking Modem for LEO Microsatellites                          |

| 2.1 Fr     | equency Synchronisation and Doppler Tracking13                       |

| 2.1.1      | Coarse Frequency Synchronisation14                                   |

| 2.1.2      | Fine Doppler Tracking18                                              |

| 2.2 M      | ethods Employed to Minimise Processing Overheads22                   |

| 2.2.1      | Frequency Modulation and Frequency Correction22                      |

| 2.2.2      | Root 40% Raised Cosine Filtering                                     |

| 2.2.3      | Frequency Discrimination30                                           |

| 2.2.4      | Block Processing and Sub-Sampling33                                  |

| 2.3 Sin    | mulation Performance30                                               |

| 2.3.1      | Coarse Doppler Tracking Performance                                  |

| 2.3.2      | Fine Doppler Tracking Performance39                                  |

| 2.3.3      | Coarse + Fine Doppler Tracking Performance                           |

| 2.4 Su     | immary and Conclusions4                                              |

| 3. A Burs  | t Demodulator for a Satellite Data Return Link4                      |

| 3.1 Bu     | urst Demodulator Overview4                                           |

| 3.1.1      | Frame Structure for Transmitted Burst4                               |

| 3.2 Ca     | arrier Frequency Acquisition4                                        |

| 3.2.1      | FFT Carrier Frequency Acquisition4                                   |

| 3.2.2      | Offset-FFT Carrier Frequency Acquisition5                            |

| 3.2.3      | Carrier Frequency Acquisition with Phase Reversing Preamble5         |

| 3.2.4   | Carrier Frequency Acquisition DSP Implementation          | 54  |

|---------|-----------------------------------------------------------|-----|

| 3.2.4.  | 1 A General Offset-FFT Algorithm                          | 54  |

| 3.2.4.  | 2 Fixed-Point DSP Considerations                          | 56  |

| 3.2,4.  | 3 Real-time DSP Implementation                            | 57  |

| 3.2.5   | Carrier Frequency Acquisition Performance                 | 60  |

| 3.2.5.  | 1 OFFT & FFT Acquisition Performance                      | 62  |

| 3.2.5.  | 2 Sensitivity to Carrier Frequency Offset                 | 63  |

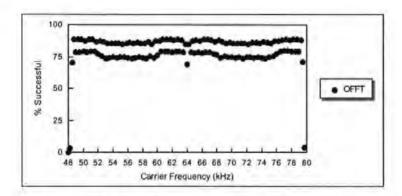

| 3.2.5.  | 3 OFFT Carrier Frequency Acquisition Range                | 64  |

| 3.3 Syr | mbol Clock Recovery                                       | 66  |

| 3.3.1   | Symbol Clock Recovery IIR Filter                          | 67  |

| 3.3.2   | Symbol Clock Recovery DSP Implementation                  | 71  |

| 3.3.3   | Symbol Clock Recovery Performance                         | 75  |

| 3.4 For | rward Error Correction Algorithms                         | 76  |

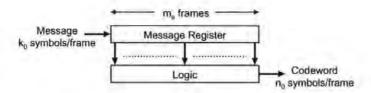

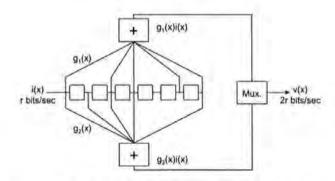

| 3.4.1   | Review of Convolutional Coding Theory                     | 77  |

| 3.4.2   | Viterbi Decoder Algorithm Software Implementation         | 79  |

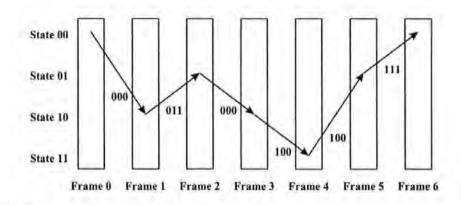

| 3.4.2.  | Decoder Trellis Representation                            | 80  |

| 3.4.2,  | 2 Calculating 'Metric Updates'                            | 82  |

| 3.4     | .2.2.1 'Previous States' Look-up Table                    | 83  |

| 3.4     | .2,2.2 'Metric Update' Look-up Table                      | 84  |

| 3.4     | .2.2.3 'Encoder Output' Look-up Table                     | 85  |

| 3.4.2.  | 3 Re-tracing Through the Decoder Trellis                  | 87  |

| 3.4.3   | Modified Viterbi Algorithms                               | 87  |

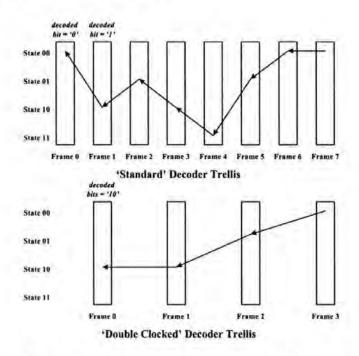

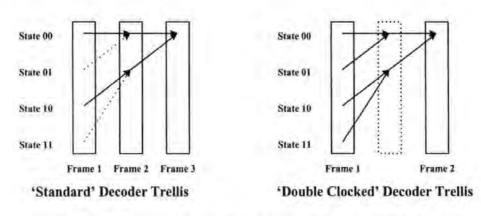

| 3.4.3.  | 1 'Double Clocked' Viterbi Decoder Algorithm              | 87  |

| 3.4.4   | Optimised Viterbi Decoder Algorithm for the TMS320C50     | 90  |

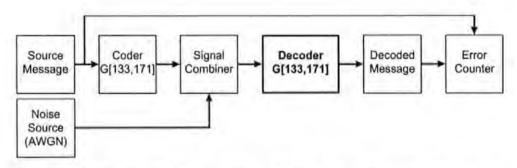

| 3.4.5   | Performance Analysis                                      | 92  |

| 3.5 Bu  | rst Demodulator Performance                               | 94  |

| 3.5.1   | Simulated Test Rig                                        | 94  |

| 3.5.2   | Sensitivity to Input Signal Level                         | 95  |

| 3.5.3   | BER Performance                                           | 96  |

| 3.5.4   | Error-Free Packet Performance.                            | 97  |

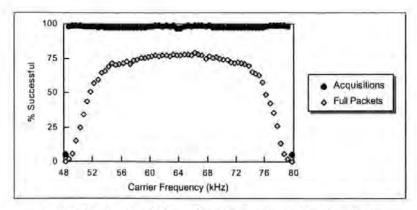

| 3.5.5   | Sensitivity to Carrier Frequency Offset                   | 98  |

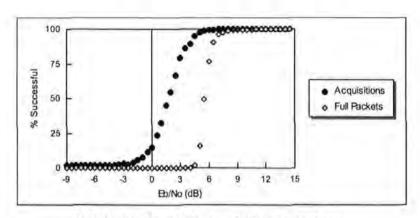

| 3.5.6   | Satellite Trials                                          | 100 |

| 3.6 Sun | mmary and Conclusions                                     | 102 |

| Synchro | onisation of OFDM Demodulators for Satellite Applications | 103 |

| 4.1   | Introduction                                                             |

|-------|--------------------------------------------------------------------------|

| 4.2   | OFDM System Models105                                                    |

| 4.3   | Carrier Frequency Synchronisation                                        |

| 4.3.  | 1 Effects of Frequency Error110                                          |

| 4.3   | 2 Combined Coarse and Fine Frequency Synchronisation112                  |

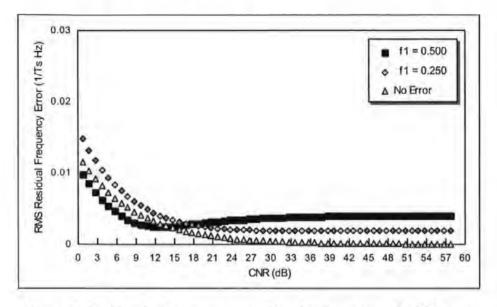

| 4.3   | 3 Simulated Carrier Frequency Synchronisation Performance                |

| 4.4   | OFDM Symbol Timing Synchronisation                                       |

| 4.4   | 1 Analysis of Symbol Timing Error119                                     |

| 4.4   | 2 Coarse Symbol Timing Synchronisation                                   |

| 4.4   | 3 Fine Symbol Timing Synchronisation                                     |

| 4.4   | 4 Simulated Symbol Timing Synchronisation Performance128                 |

| 4.5   | Conclusions131                                                           |

| 5. Ap | plications in Highly Asymmetric Satellite Internet Delivery Systems 132  |

| 5.1   | Definition of Symmetrical and Asymmetric Internet Delivery Systems 133   |

| 5.2   | Novel Asymmetric Satellite Internet Delivery Systems                     |

| 5.2   | An Improved Asymmetric Satellite Internet Delivery System 135            |

| 5.3   | Network Device Driver Software for IP Transmission Over a Satellite Data |

| Reply | Link                                                                     |

| 5.3   | .1 Network Device Driver Overview                                        |

| 5.3   | .2 Ethernet Emulation over the Satellite Data Reply Link                 |

| 25    | 5.3.2.1 Ethernet Emulation for Uni-Directional Links                     |

| 5.3   | .3 Packet Filtering and Prioritising140                                  |

| 5.3   | .4 User Authorisation and Distribution of System Parameters              |

| 5.4   | Improving Throughput in Satellite Internet Delivery Systems141           |

| 5.4   | .1 The Effect of Satellite Delay on TCP/IP Throughput142                 |

| 5.4   | .2 Enhancing Throughput With Standard TCP/IP Mechanisms                  |

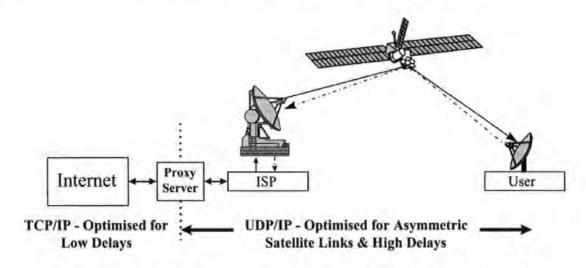

| 5.4   | .3 Enhancing Throughput with UDP/IP146                                   |

| 5.5   | System Performance                                                       |

| 5.5   | .1 Collision Reduction with Frequency Hopping Algorithms                 |

| 5.5   | .2 Time Division Multiple Access (TDMA)                                  |

| 5.6   | Conclusion                                                               |

| 6. Co | nclusions154                                                             |

| 6.1   | Contributions to Knowledge                                               |

| 6.2   | Conclusions and Future Work157                                           |

| A. DS  | P Hardware                                                       | 160   |

|--------|------------------------------------------------------------------|-------|

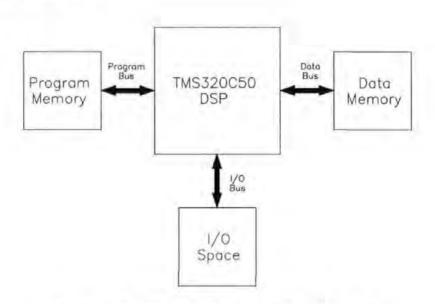

| A.1    | TMS320C50 Fixed-Point Digital Signal Processor                   | 160   |

| A.1    | .1 A Generic TMS320C50 DSP System                                | , 163 |

| A.2    | Dual-C50 DSP System                                              | 163   |

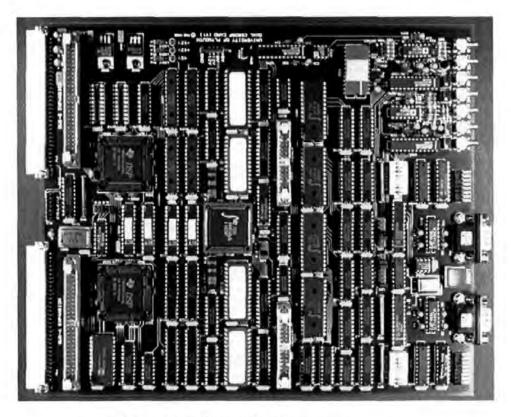

| A.2    | .1 Dual-C50 System Board                                         | 165   |

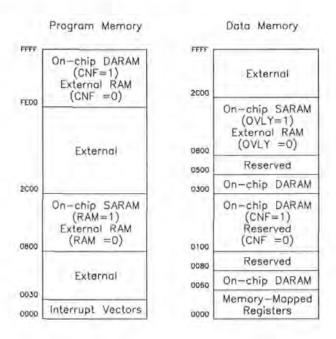

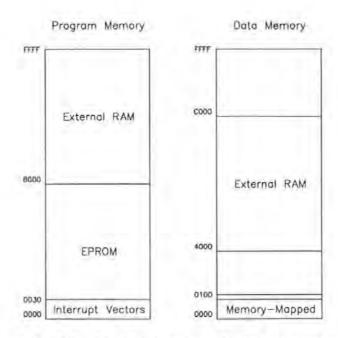

| A.2    | 2 Dual-C50 DSP System Board Memory Maps                          | ,167  |

| A.3    | C50 DSP Software                                                 | 170   |

| A.3    | .1 C50 Assembly Code Program Structure                           | 170   |

| A.3    | .2 C50 Assembly Code Program Example                             | 172   |

| A.3    | .3 Strategy for Developing Real-Time DSP Code                    | 176   |

| B. Des | cription of Doppler Tracking Modem and Oscilloscope Signal Plots | 178   |

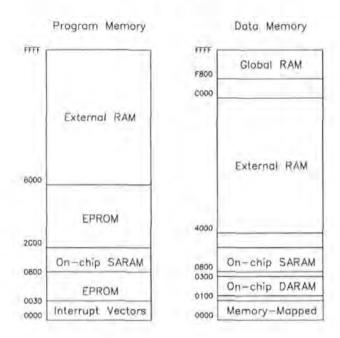

| B.1    | Description of 9.6kbps FM Modulator                              | 178   |

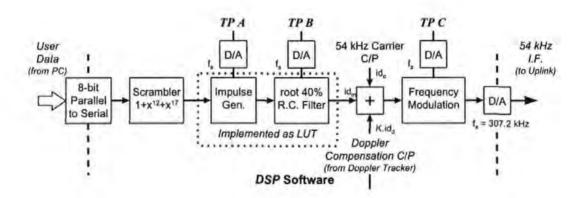

| B.1    | 1 9.6kbps FM Modulator Signal Plots                              | 180   |

| B.2    | Description of 9.6kbps FM Demodulator                            | 181   |

| B.2    | 1 9.6kbps FM Demodulator Signal Plots                            | 184   |

| C. Off | set-FFT Derivation                                               | 188   |

| C.1    | 8-point OFFT Pass 2, Group 0 (Final Pass)                        | 188   |

| C,2    | 8-point OFFT Pass 1, Group 0                                     | 191   |

| C.3    | 8-point OFFT Pass 1, Group 1                                     | 192   |

| C.4    | 8-point OFFT - Pass 0, Group 0                                   | 193   |

| C.5    | 8-point OFFT - Pass 0, Group 1                                   | 194   |

| C.6    | 8-point OFFT - Pass 0, Group 2                                   |       |

| C.7    | 8-point OFFT - Pass 0, Group 3                                   | 196   |

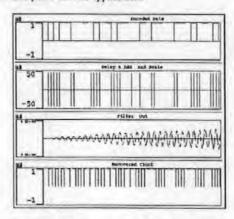

| D. Sup | plemental Burst Demodulator Information                          | 197   |

| D.1    | Burst Demodulator Summary                                        | 198   |

| D.1    | .1 Signal Plots for BPSK Demodulation                            | 199   |

| D.1    | .2 Signal Plots for QPSK Demodulation                            | 203   |

| D.2    | Frequency Correction                                             | 207   |

| D.2    | .1 Mathematical Analysis                                         | 207   |

| D.2    | .2 DSP Implementation                                            | 208   |

| D.3    | Matched Filtering                                                | 210   |

| D.3    | .1 Mathematical Analysis                                         | 210   |

| D.3    | .2 DSP Implementation                                            | 212   |

| D.4    | Differential Demodulation                                        | 213   |

| D.4.1      | Mathematical Analysis                                   | 214 |

|------------|---------------------------------------------------------|-----|

| D.4.2      | DSP Implementation                                      | 215 |

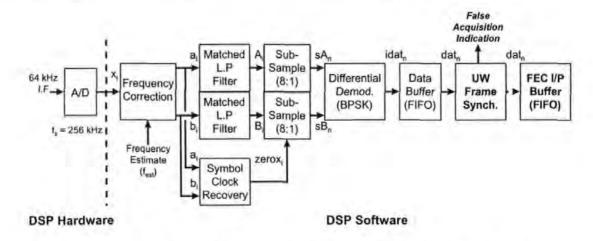

| D.5 Ur     | ique Word Frame Synchronisation                         | 216 |

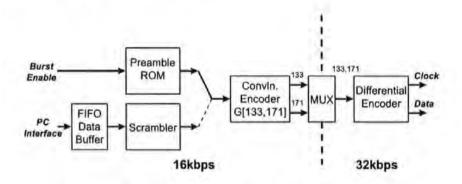

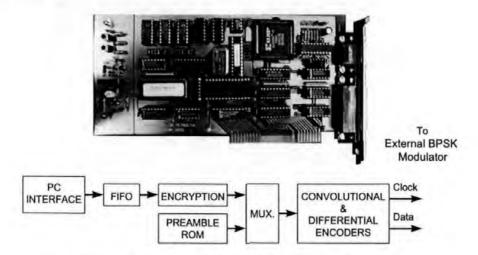

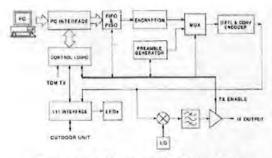

| D.5.1      | Digital Transmitter Hardware                            | 217 |

| D.5.2      | Unique Word Selection                                   | 218 |

| D.5.3      | DSP Implementation                                      | 219 |

| D.6 So     | ftware FIFO Buffers & Inter-Processor Communication     | 221 |

| D.6.1      | Burst Demodulator Applications for Software FIFO Buffer | 222 |

| D.6.2      | Software FIFO Buffer DSP Implementation                 | 223 |

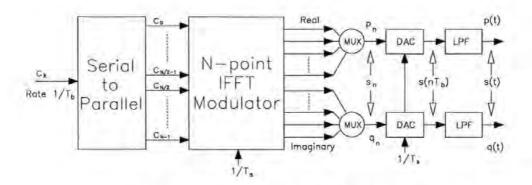

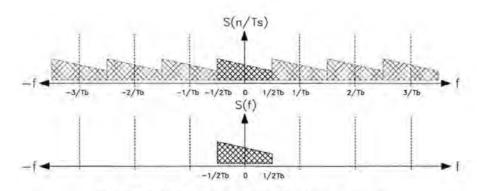

| E. OFDM    | Modulator and Demodulator Models                        | 226 |

| E.1 OF     | DM System Models                                        | 226 |

| E.1.1      | The Complex Sampling OFDM Modulator Model               | 226 |

| E.1.2      | The Real Sampling OFDM Modulator Model                  | 230 |

| E.1.3      | The Complex Sampling Demodulator Model                  | 233 |

| E.1.4      | The Real Sampling Demodulator Model                     | 236 |

| E.2 Co     | mparison of Theoretical OFDM Models                     | 238 |

| E.2.1      | Digital Hardware Requirements                           | 240 |

| E.2.2      | Analogue Hardware Requirements                          | 240 |

| E.2.3      | Analogue Filter Requirements                            | 240 |

| F. The Int | ernet Protocol Suite                                    | 241 |

| F.1 Ur     | derlying Network Technology                             | 243 |

| F.2 Int    | ernet Addressing Scheme                                 | 244 |

| F.2.1      | Free Addresses                                          | 246 |

| F.2.2      | Routing                                                 | 247 |

| F.2.3      | Subnetting                                              | 248 |

| F.2.4      | Internet Addressing Summary                             | 251 |

| F.3 Th     | e Internet Protocol                                     | 251 |

| F.4 Th     | e Transmission Control Protocol                         | 253 |

| F.4.1      | TCP Reliability and Flow Control                        |     |

| F.4.2      | TCP Segment Format                                      |     |

| F.5 Th     | e User Datagram Protocol                                |     |

|            | Internet Delivery Systems - Supplemental Information    |     |

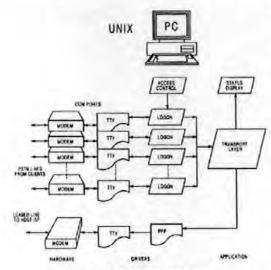

|            | Hybrid Terrestrial/Satellite Internet Delivery System   |     |

| G.1.1      | Novel Network Software and Hardware                     |     |

| C   | G.2 An Asymmetric Satellite Internet Delivery System              | 264              |

|-----|-------------------------------------------------------------------|------------------|

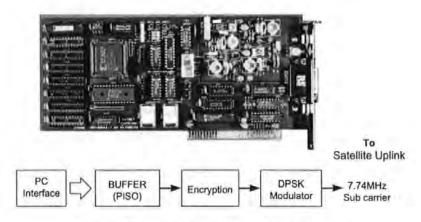

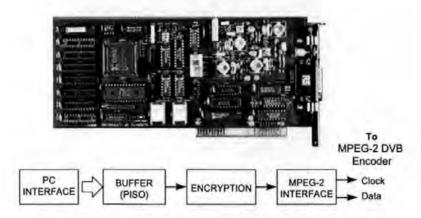

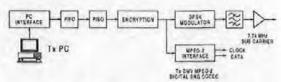

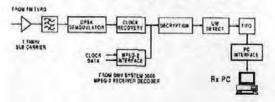

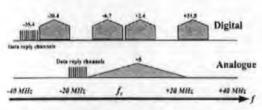

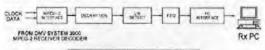

|     | G.2.1 Data Broadcast Hardware                                     | 266              |

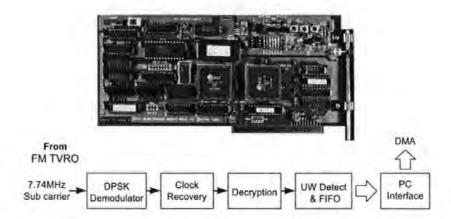

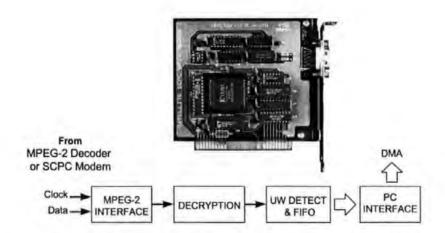

|     | G.2.2 User Return Link Hardware                                   | 267              |

| H.  | Paper I - "A Data Reply Link System for Satellite TV Applicatio   | ns"269           |

| I.  | Paper 2 - "Development of an Operational Satellite Internet Servi | ce"274           |

| J.  | Paper 3 - "A Novel Internet Delivery System Using Asym            | metric Satellite |

| Cha | nnels".                                                           | 279              |

| K.  | References                                                        | 288              |

| L.  | Bibliography                                                      | 293              |

#### List of Abbreviations

ADC Analogue to Digital Converter

ADSL Asymmetrical Digital Subscriber Line

ARP Address Resolution Protocol

ASIC Application Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BPS Bits per Second

BPSK Binary Phase Shift Keying

CNR Carrier To Noise Ratio

DA-TDMA Demand Assigned TDMA

DAC Digital to Analogue Converter

DBPSK Differential Binary Phase Shift Keying

DFT Discrete Fourier Transform

DIT Decimation in Time

DNS Domain Naming System

DOPSK Differential Quadrature Phase Shift Keying

DSL Digital Subscriber Line

DSP Digital Signal Processor/Processing

DVB Digital Video Broadcasting

EPROM Erasable Programmable Read Only Memory

FEC Forward Error Correction

FFT Fast Fourier Transform

FIFO First In First Out (Memory)

FIR Finite Impulse Response (Filter)

FM Frequency Modulation

FPGA Field-Programmable Gate Array

FSK Frequency Shift Keying

FTP File Transfer Protocol

GEO Geosynchronous Earth Orbit

HTTP Hyper-Text Transfer Protocol

ICI Inter-Channel Interference

IF Intermediate Frequency

IFFT Inverse Fast Fourier Transform

IIR Infinite Impulse Response (Filter)

IP Internet Protocol

ISI Inter-Symbol Interference

ISP Internet Service provider

LAN Local Area Network

LEO Low Earth Orbit

LSB Lest Significant Bit

LUT Look-Up Table

MAC Medium Access Controller

MEO Medium Earth Orbit

MTU Maximum Transmission Unit

NIC Network Interface Controller

Tretwork Interface Controller

OFDM Orthogonal Frequency Division Multiplexing

PC Personal Computer

PLL Phase-Locked Loop

PSTN Public Switched Telephone Network

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

RAM Random Access Memory

ROM Read Only Memory

SNR Signal to Noise Ratio

SPS Symbols Per Second

TCP Transmission Control Protocol

TDMA Time Division Multiple Access

UDP User Datagram Protocol

UW Unique Work

VSAT Very Small Aperture Terminal

#### List of Illustrations

| Figure 1-1. Digital communication system overview                                    |

|--------------------------------------------------------------------------------------|

| Figure 1-2. Basic I/Q modulator structures                                           |

| Figure 1-3. Basic I/Q demodulator structures4                                        |

| Figure 1-4. Ideal 'Software Radio' receiver6                                         |

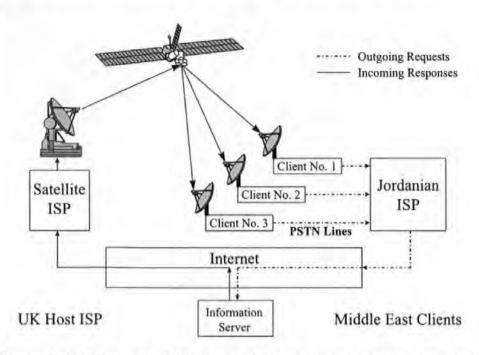

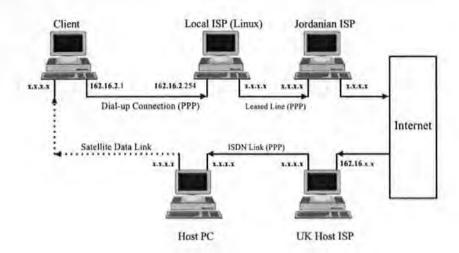

| Figure 1-5. Interactive satellite DVB system with satellite return channel8          |

| Figure 1-6. Outline Ku-band satellite data reply link system                         |

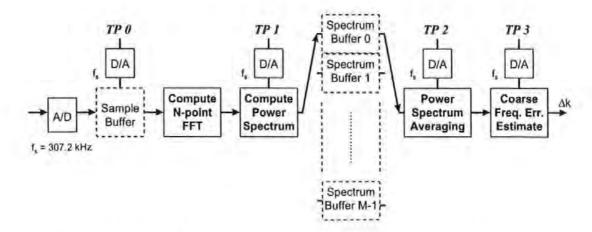

| Figure 2-1. Coarse frequency synchronisation sub-system (N=256, M=64)15              |

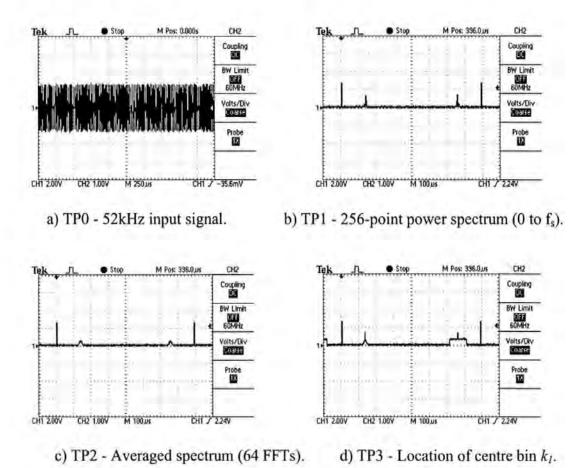

| Figure 2-2. Coarse frequency synchronisation signals ( $N = 256$ , $M = 64$ )        |

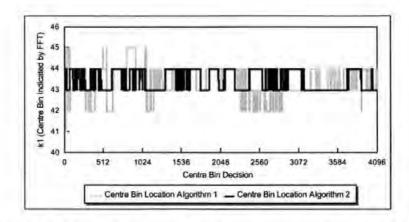

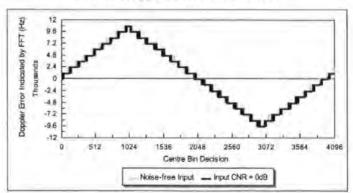

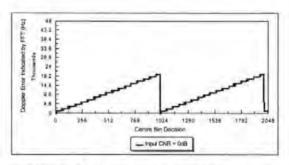

| Figure 2-3. Coarse frequency synchronisation performance with ideal noise-free input |

| signal - $k_1 = 43$ , $N = 256 \& M = 128$                                           |

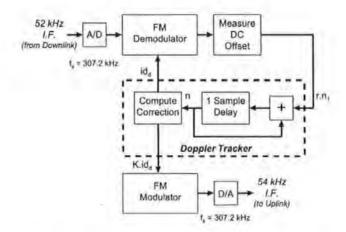

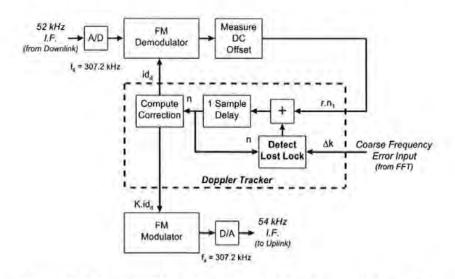

| Figure 2-4. Fine Doppler tracking for modulator & demodulator                        |

| Figure 2-5. Practical fine Doppler tracking for modulator and demodulator with       |

| automatic (re)initialisation from coarse frequency synchronisation FFT sub-          |

| system                                                                               |

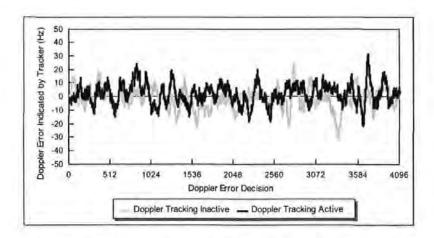

| Figure 2-6. Doppler error indicated at tracker input for ideal noise-free & Doppler- |

| free input signal21                                                                  |

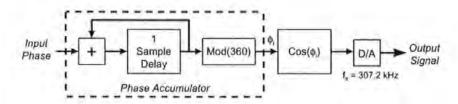

| Figure 2-7. General 'Phase Accumulator' for frequency synthesis                      |

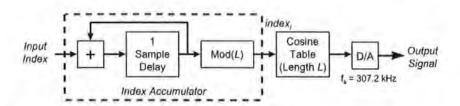

| Figure 2-8. Practical 'Index Accumulator' for frequency synthesis                    |

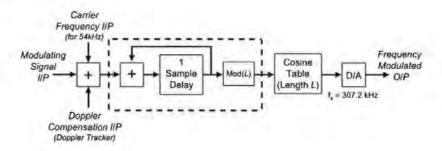

| Figure 2-9. 'Index Accumulator' for frequency modulation - FM modulator23            |

| Figure 2-10. 'Index Accumulator' for frequency correction - FM demodulator24         |

| Figure 2-11. FM modulator DSP assembly code for frequency modulation - 'Index        |

| Accumulator' instructions highlighted                                                |

| Figure 2-12. FM demodulator DSP assembly code for frequency correction - 'Index      |

| Accumulator' instructions highlighted25                                              |

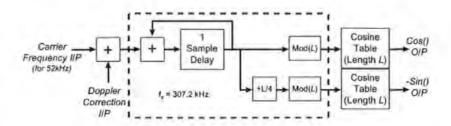

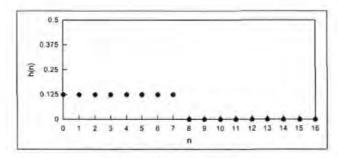

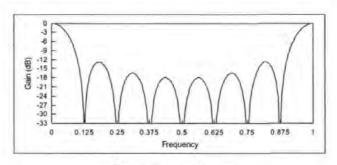

| Figure 2-13. Root 40% raised Cosine filter responses                                 |

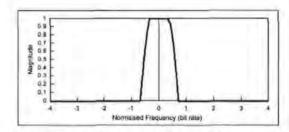

| Figure 2-14. Impulse responses for practical root 40% raised Cosine filters28        |

| Figure 2-15. Impulse responses for practical 40% raised Cosine filters28             |

| Figure 2-16. DSP assembly code required to produce one output sample for 'FIR        |

| Filter', 'Look-up Table' & 'IIR Filter Approximation' implementations of a root      |

| 40% raised Cosine filter                                                             |

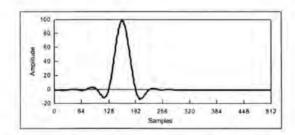

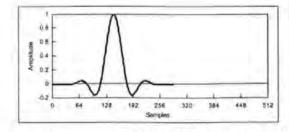

| Figure 2-17. Demodulator root 40% raised Cosine filtered output - data = 0xf536      |

| Figure 2-18. Demodulator root 40% raised Cosine filtered output - random data 37     |

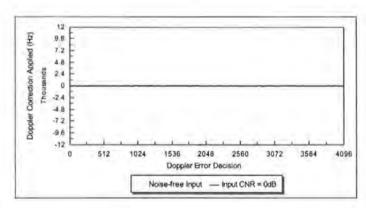

| 9,600bps)                                                                                    |

|----------------------------------------------------------------------------------------------|

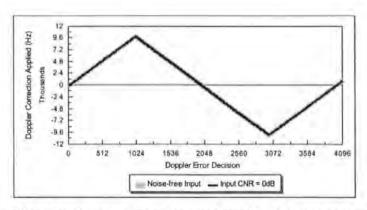

| Figure 2-20. Fine tracking over 4096 decision cycles (3.64 minutes at 9,600bps)39            |

| Figure 2-21. Coarse & fine Doppler tracking over 2048 decision cycles (1.82 minutes          |

| at 9,600bps) - linearly changing Doppler error of 375 Hz per second40                        |

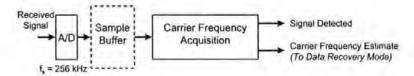

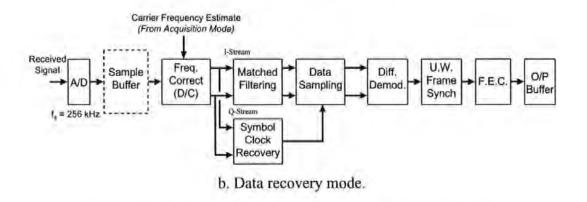

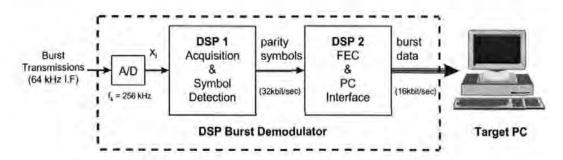

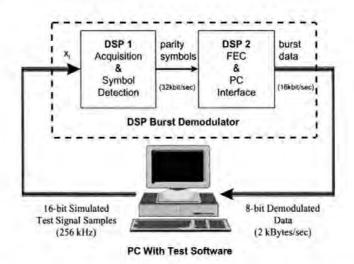

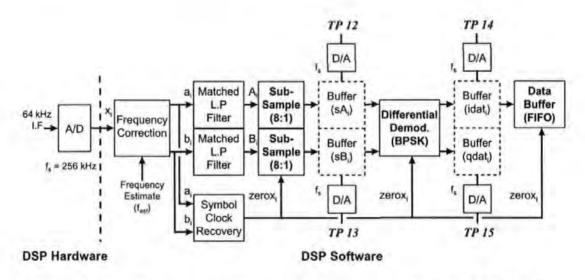

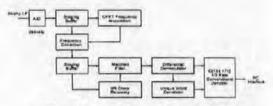

| Figure 3-1. General digital burst demodulator block diagram44                                |

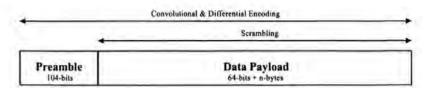

| Figure 3-2. Transmitted burst format (frame structure)                                       |

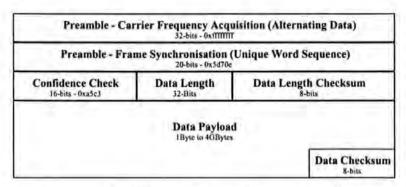

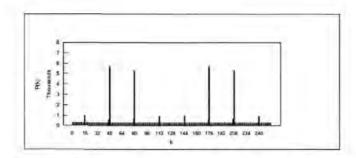

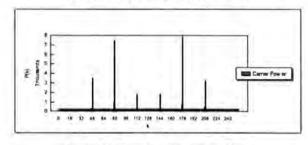

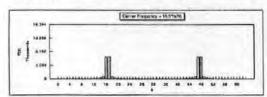

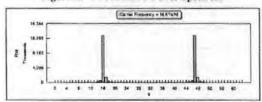

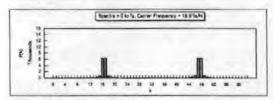

| Figure 3-3. 256-point FFT power spectra                                                      |

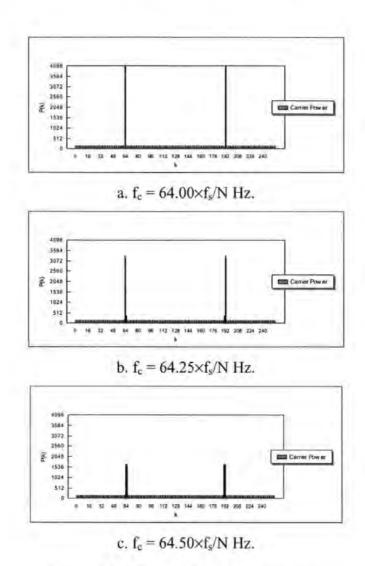

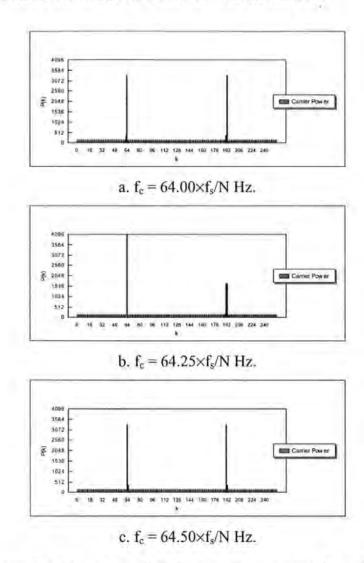

| Figure 3-4. 256-point Offset-FFT power spectra (offset=0.25)                                 |

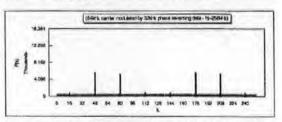

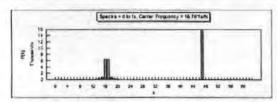

| Figure 3-5. Offset-FFT power spectrum for 32ksps phase reversing preamble                    |

| (f <sub>s</sub> =256kHz, f <sub>c</sub> =64kHz, N=256, offset=0.25)54                        |

| Figure 3-6. In-place FFT 'Butterfly' routine for the TMS320C50 DSP57                         |

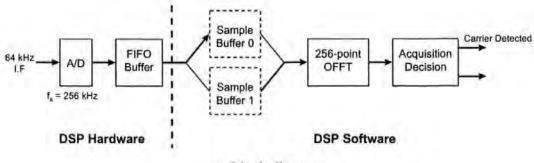

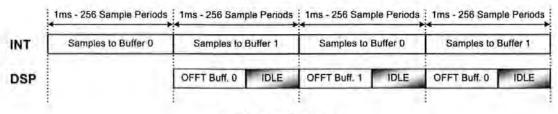

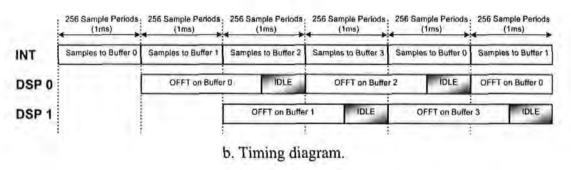

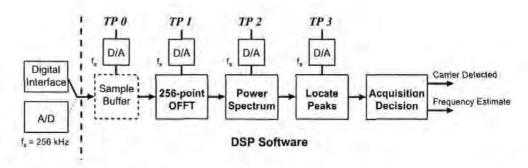

| Figure 3-7. Real-time OFFT carrier frequency acquisition (single 80MHz DSP)59                |

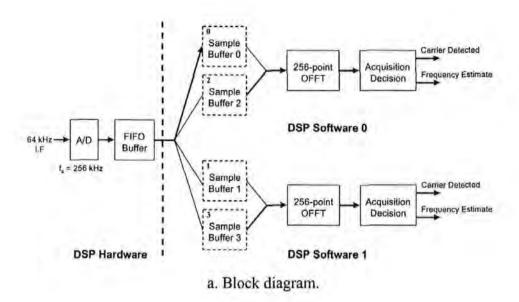

| Figure 3-8. Real-time OFFT carrier frequency acquisition (dual 40MHz DSP)60                  |

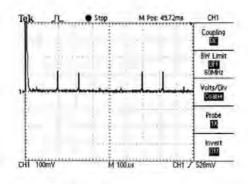

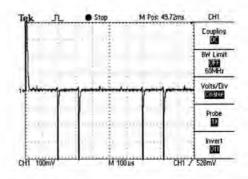

| Figure 3-9. Burst demodulator implementation - carrier frequency acquisition61               |

| Figure 3-10. Carrier frequency acquisition test outputs (optimum conditions)62               |

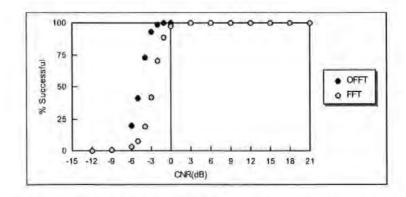

| Figure 3-11. FFT verses OFFT acquisition performance (f <sub>c</sub> =64.375kHz, maximum     |

| signal level)62                                                                              |

| Figure 3-12. FFT verses OFFT carrier frequency acquisition performance (maximum              |

| signal level, CNR = -3dB)                                                                    |

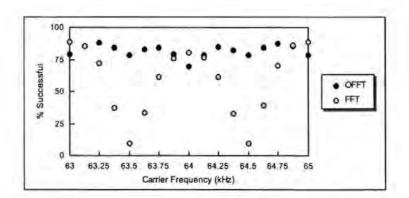

| Figure 3-13. OFFT carrier frequency acquisition performance (maximum signal level,           |

| CNR = -3dB)64                                                                                |

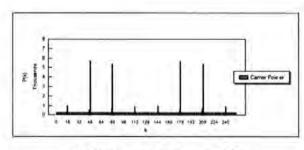

| Figure 3-14. OFFT power spectrum for 32ksps phase reversing preamble (f <sub>s</sub> =256kHz |

| N=256, c=0.25, f <sub>c</sub> =64kHz)                                                        |

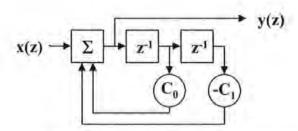

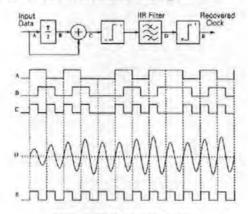

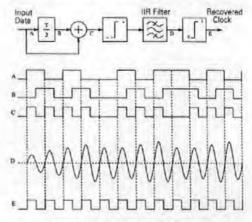

| Figure 3-15. Clock recovery IIR filter structure                                             |

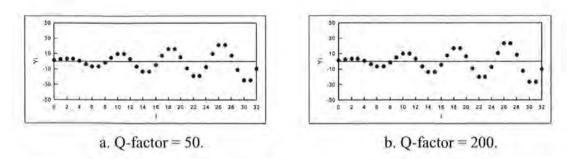

| Figure 3-16. Clock recovery filter acquisition performance - optimum stimulus 70             |

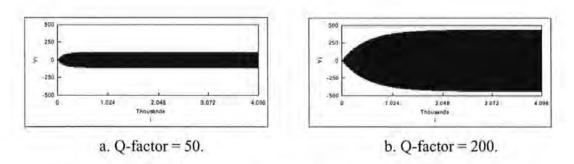

| Figure 3-17. Clock recovery filter output growth - optimum stimulus                          |

| Figure 3-18. Clock recovery filter flywheel performance - stimulus removed71                 |

| Figure 3-19. Clock recovery filter TMS320C50 assembly code                                   |

| Figure 3-20. DSP burst demodulator implementation - symbol clock recovery 74                 |

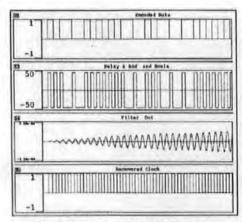

| Figure 3-21. Clock recovery signal samples (8 symbol periods shown)                          |

| Figure 3-22. Clock recovery filter sensitivity to carrier frequency offset                   |

| Figure 3-23. DSP burst demodulator external system interfaces                                |

| Figure 3-24. Convolutional encoder structure                                                 |

| Figure 3-25. G[133,171] convolutional encoder                                                        |

|------------------------------------------------------------------------------------------------------|

| Figure 3-26. G[5,7,7] convolutional code encoding illustration - trellis diagram 79                  |

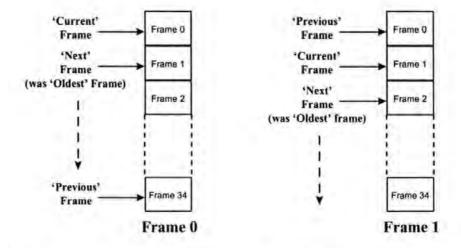

| Figure 3-27. Viterbi decoder algorithm trellis - memory organisation                                 |

| Figure 3-28. Viterbi decoder algorithm trellis - circular memory addressing81                        |

| Figure 3-29. Comparison of decoder trellis and decoded bit decisions for 'Standard'                  |

| and 'Double Clocked' Viterbi decoder algorithms - (K=3 code)88                                       |

| Figure 3-30. Comparison of path elimination for 'Standard' and 'Double Clocked'                      |

| Viterbi decoder algorithms - (K=3 code)                                                              |

| Figure 3-31. Block diagram of DSP Viterbi decoder test software92                                    |

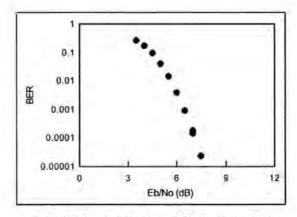

| Figure 3-32. Experimental & theoretical BER curves - G[133,171] code93                               |

| Figure 3-33. Simulated test-rig for DSP burst demodulator94                                          |

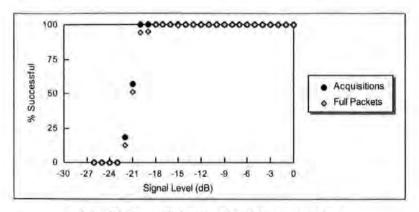

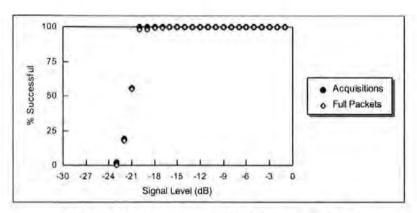

| Figure 3-34. Burst demodulator sensitivity to input signal level (noise free)96                      |

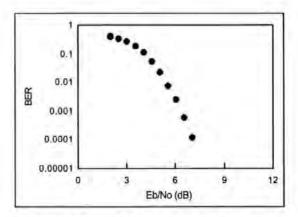

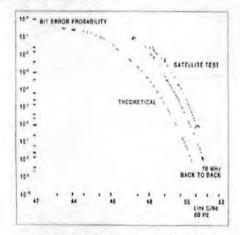

| Figure 3-35. Burst demodulator BER performance                                                       |

| Figure 3-36. Burst demodulator error-free packet performance                                         |

| Figure 3-37. Burst demodulator sensitivity to carrier frequency offset99                             |

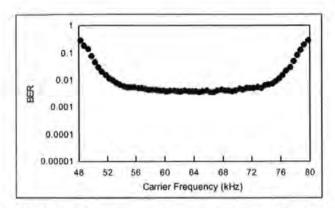

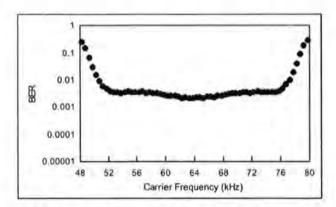

| Figure 3-38. Burst demodulator BER sensitivity to carrier frequency offset100                        |

| Figure 3-39. Burst demodulator BER performance                                                       |

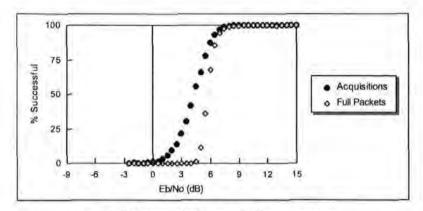

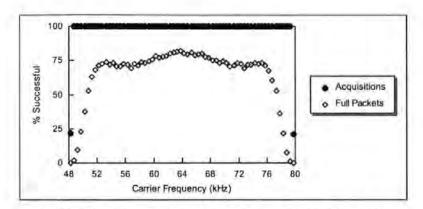

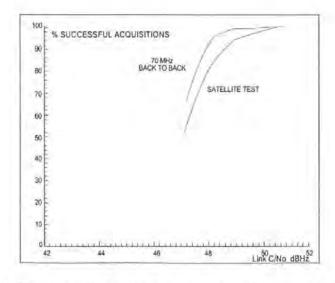

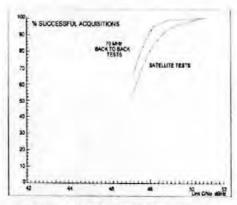

| Figure 3-40. Burst demodulator packet acquisition performance                                        |

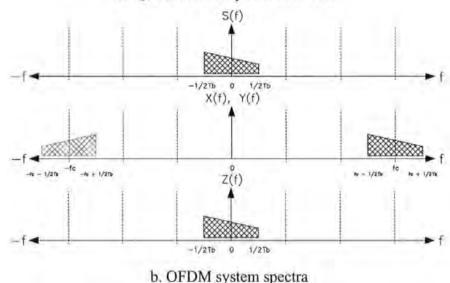

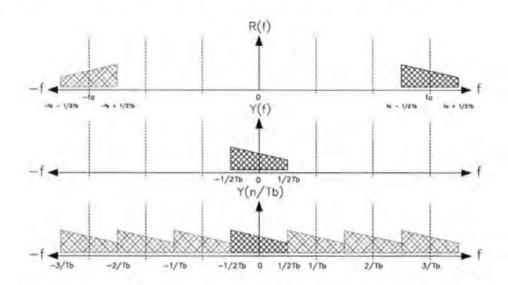

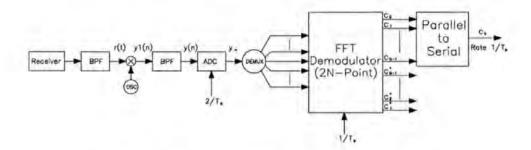

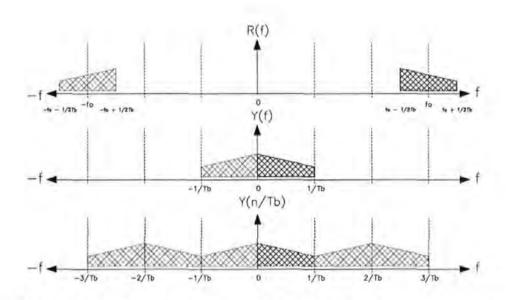

| Figure 4-1. Baseband QPSK-OFDM modulator and spectra                                                 |

| Figure 4-2. QPSK-OFDM system overview and spectra                                                    |

| Figure 4-3. Baseband QPSK-OFDM demodulator and spectra                                               |

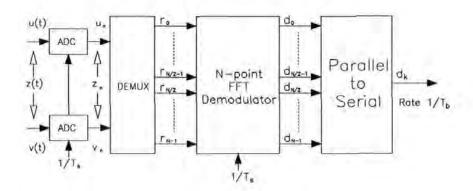

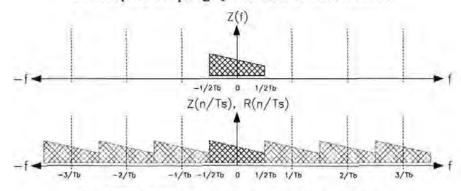

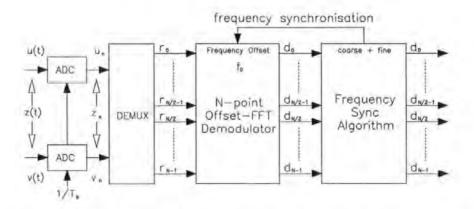

| Figure 4-4. QPSK-OFDM demodulator with carrier frequency synchronisation109                          |

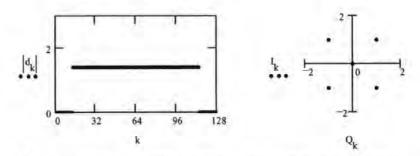

| Figure 4-5. The effect of coarse and fine frequency error on demodulator outputs, $d_k$              |

| $I_k+jQ_k$ , in terms of magnitude and phase (N=128)111                                              |

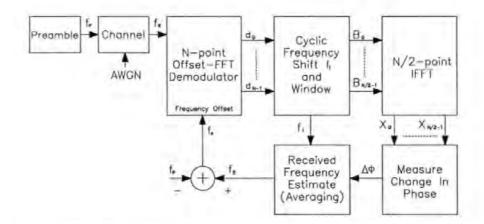

| Figure 4-6. Combined carrier frequency error estimation algorithm (residual error f <sub>R</sub> -   |

| f <sub>2</sub> )112                                                                                  |

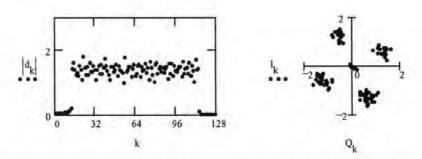

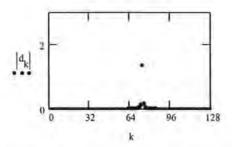

| Figure 4-7. Effect of frequency error $\Delta f_e = 10.125/T_s$ Hz on demodulator outputs $d_k$ in   |

| terms of magnitude (N=128, $f_P = 64/T_s$ Hz)                                                        |

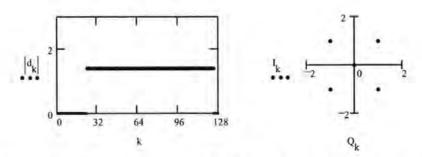

| Figure 4-8. Demodulator outputs Bk in terms of magnitude after -f1 Hz cyclic shift to                |

| eliminate coarse frequency error component (N = 128, $\Delta f_1 = 0.125/T_s$ Hz)   13               |

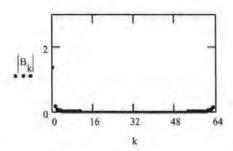

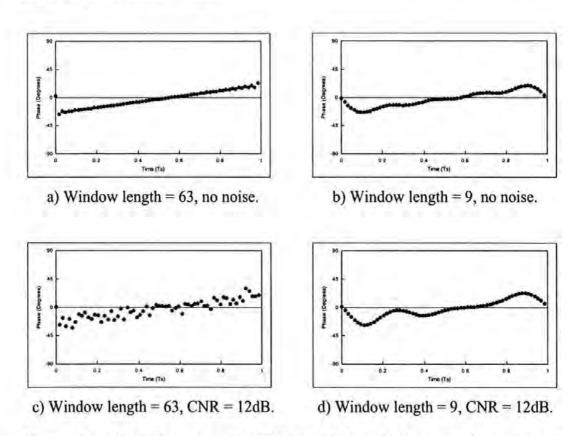

| Figure 4-9. Signal phase φ <sub>n</sub> over OFDM symbol period T <sub>s</sub> arising from residual |

| frequency error $\Delta f_1 = -0.125/T_s$ Hz (IFFT length = N/2, CNR measured at                     |

| demodulator input)                                                                                   |

|                                                                                                      |

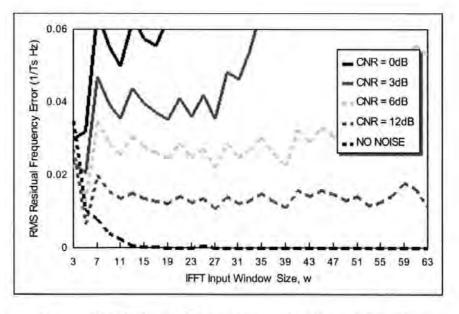

| Figure 4-10. Effect of IFFT window size ( $\Delta f_1 = 0.5/T_s$ Hz)116                          |

|--------------------------------------------------------------------------------------------------|

| Figure 4-11. Carrier frequency synchronisation error (N=128, w=5, f <sub>2</sub> averaged over 8 |

| iterations)                                                                                      |

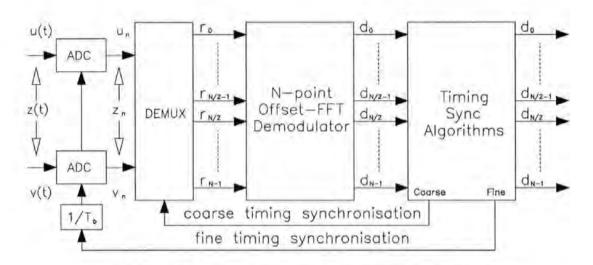

| Figure 4-12. OFDM demodulator with symbol timing synchronisation                                 |

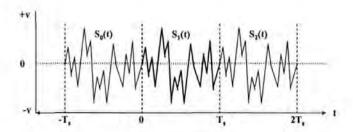

| Figure 4-13. Continuous time signal for three consecutive OFDM symbols                           |

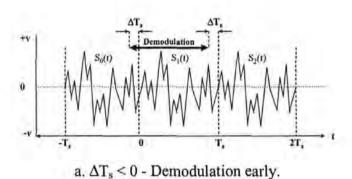

| Figure 4-14. Demodulator symbol timing error with respect to transmitted OFDM                    |

| signal120                                                                                        |

| Figure 4-15. Phase error in demodulated QPSK symbols $d_k = I_k + jQ_k$ resulting from           |

| symbol timing error $ \Delta T_s  = T_b/8$ (N = 128)                                             |

| Figure 4-16. $ d_k $ as a function of $\Delta T_s$ during coarse timing synchronisation preamble |

| (T <sub>s</sub> =1, k=N/4 and N=32)124                                                           |

| Figure 4-17. Phase error in demodulated and normalised QPSK symbols $d_k = I_k + jQ_k$           |

| resulting from symbol timing error $\Delta T_s = T_b/8$ (N = 128)126                             |

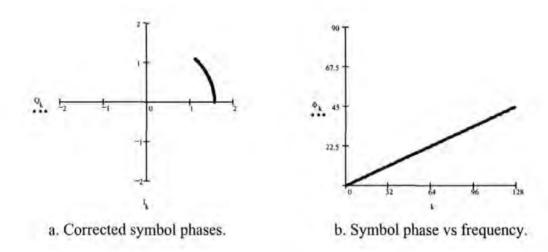

| Figure 4-18. Phase error in corrected QPSK symbols $d_k = I_k + jQ_k$ resulting from             |

| symbol timing error $\Delta T_s = T_b/8$ (N = 128)                                               |

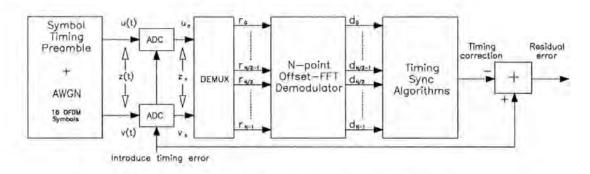

| Figure 4-19. Simulated OFDM symbol timing synchronisation system                                 |

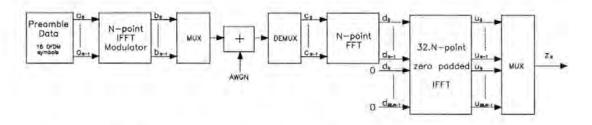

| Figure 4-20. Generation of over-sampled OFDM symbol timing test signal                           |

| Figure 4-21. Simulated timing synchronisation performance after coarse                           |

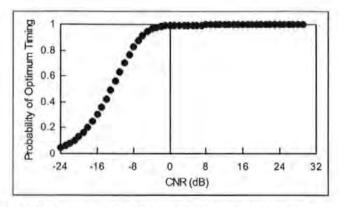

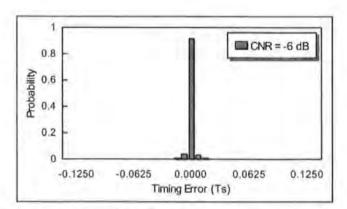

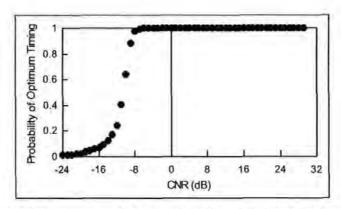

| synchronisation algorithm (N=128)129                                                             |

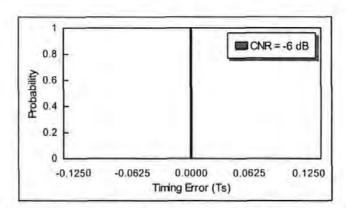

| Figure 4-22. Simulated timing synchronisation performance after both coarse and fine             |

| synchronisation algorithms (N=128)                                                               |

| Figure 5-1. Symmetrical Internet delivery system133                                              |

| Figure 5-2. Asymmetric Internet delivery system                                                  |

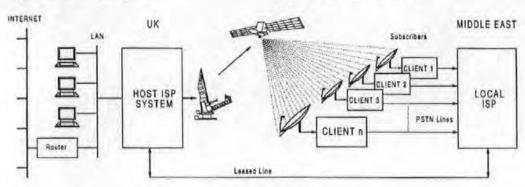

| Figure 5-3. Improved asymmetric satellite Internet delivery system - overview 136                |

| Figure 5-4. Improved asymmetric satellite Internet delivery system - network                     |

| diagram                                                                                          |

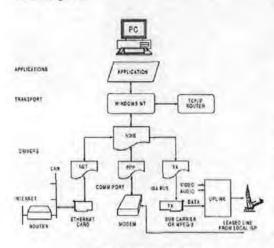

| Figure 5-5. Network device driver software                                                       |

| Figure 5-6. Encapsulation of Ethernet Frames within Satellite Return Link Packets.               |

| 139                                                                                              |

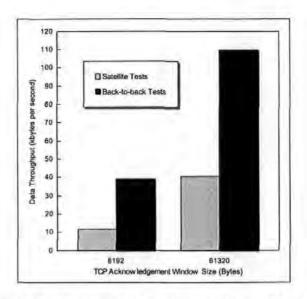

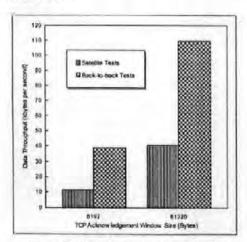

| Figure 5-7. Effect of satellite delays (600ms RTT) & TCP acknowledgement window                  |

| size on TCP/IP throughput performance                                                            |

| Figure 5-8. An optimised asymmetric satellite Internet delivery system146                        |

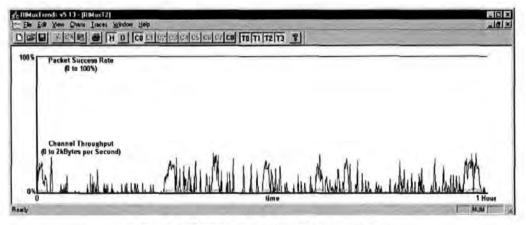

| Figure 5-9. Request channel performance for a single user - 1 hour interval147                   |

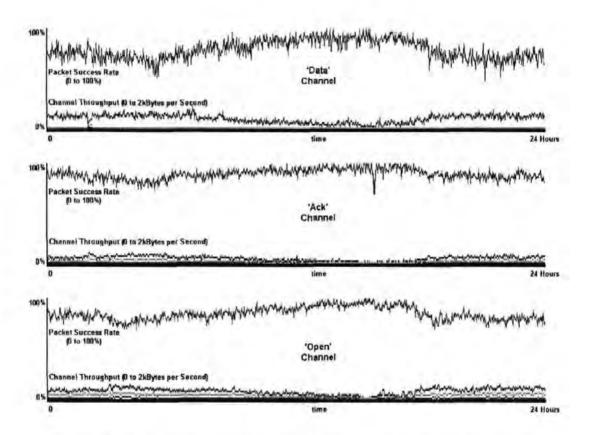

| Figure 5-10. Request channel performance for "Data", "Ack" and "Open" Traffic -              |

|----------------------------------------------------------------------------------------------|

| multiple users over 24 hour interval (12:00 to 12:00)                                        |

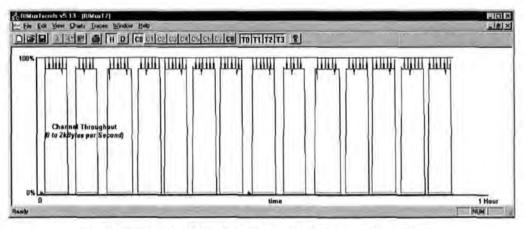

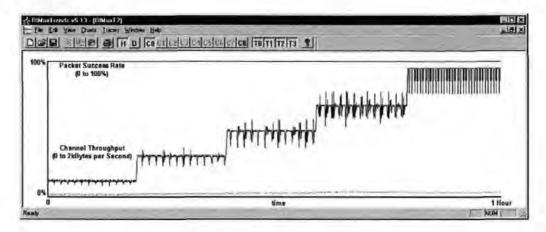

| Figure 5-11. TDMA request channel performance - single user over 1 hour interval,            |

| FTP upload with dynamic bandwidth allocation                                                 |

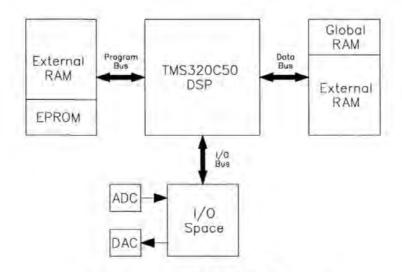

| Figure A-1. TMS320C50 'Harvard' architecture                                                 |

| Figure A-2. C50 memory maps                                                                  |

| Figure A-3. Generic C50 DSP system                                                           |

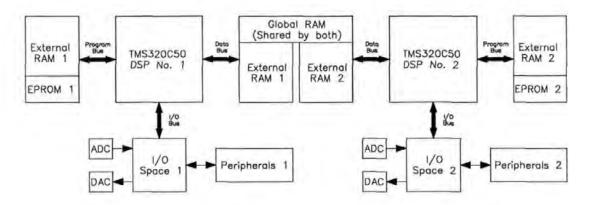

| Figure A-4. Dual-C50 DSP system overview                                                     |

| Figure A-5. Dual-C50 DSP system board                                                        |

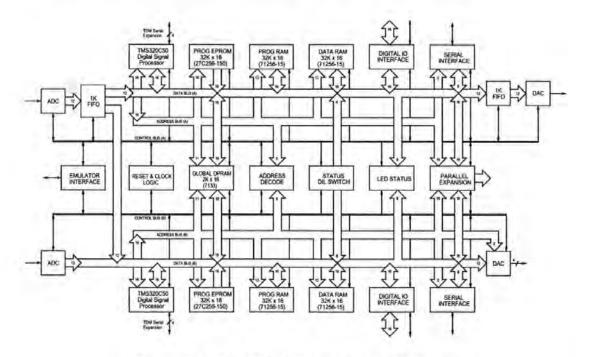

| Figure A-6. Dual-C50 DSP system block diagram                                                |

| Figure A-7. Dual-C50 DSP system default memory maps                                          |

| Figure A-8. Dual-C50 DSP system optimised memory maps                                        |

| Figure A-9. Dual-C50 DSP system I/O memory map                                               |

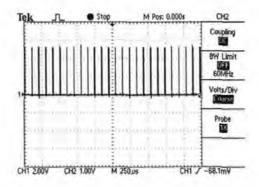

| Figure B-1. 9.6kbps FM modulator (single DSP)178                                             |

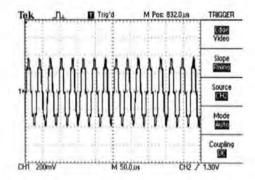

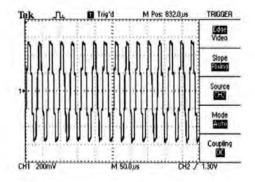

| Figure B-2. FM modulator TP A - Notional mapped ±1 data at 9.6kbps input to root             |

| 40% raised Cosine filter (25 symbol periods)                                                 |

| Figure B-3. FM modulator TP B - Root 40% raised cosine filtered data obtained from           |

| a look-up table (25 symbol periods)                                                          |

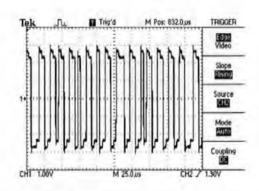

| Figure B-4. FM modulator TP C - FM output at nominal 54kHz centre frequency (25              |

| symbol periods)                                                                              |

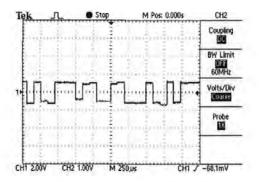

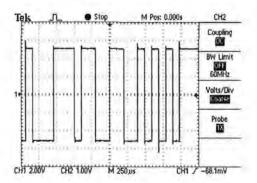

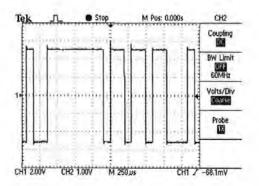

| Figure B-5. 9.6kbps FM demodulator DSP 1 - FM demodulation & Doppler tracking.               |

|                                                                                              |

| Figure B-6. 9.6kbps FM demodulator DSP 2 - Symbol timing synchronisation 182                 |

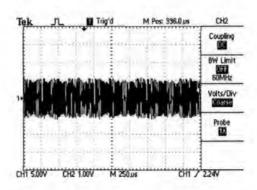

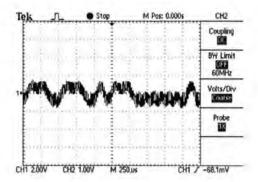

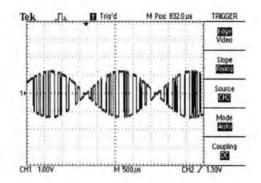

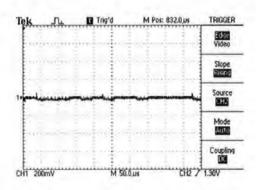

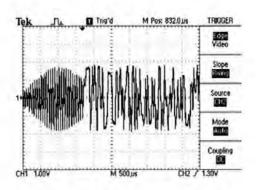

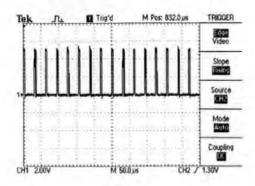

| Figure B-7. FM demodulator TP A - 9.6kbps FM signal received from ADC (25                    |

| symbol periods)184                                                                           |

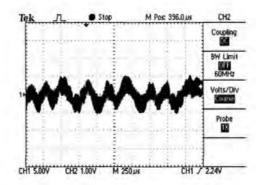

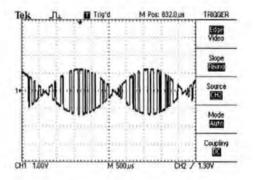

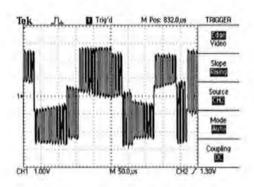

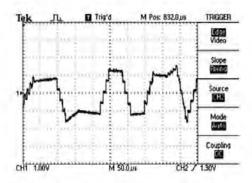

| Figure B-8. FM demodulator TP B - Down converted in-phase stream prior to                    |

| filtering (25 symbol periods)                                                                |

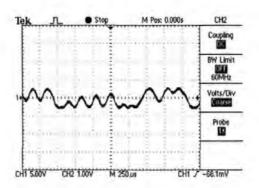

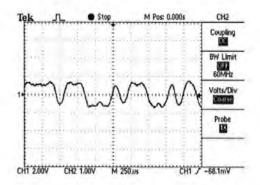

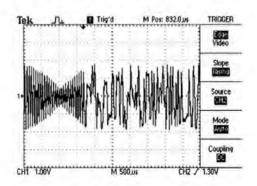

| Figure B-9. FM demodulator TP C - Down converted in-phase stream after low pass              |

| filtering (25 symbol periods)                                                                |

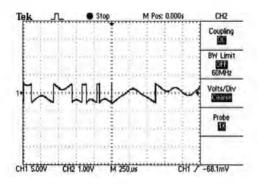

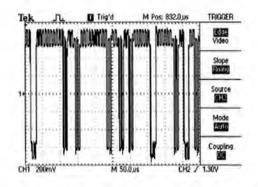

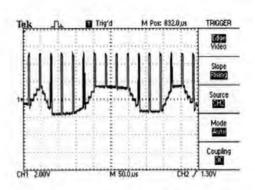

| Figure B-10. FM demodulator TP D - Output from extended Tan <sup>-1</sup> phase detector (25 |

| symbol periods)185                                                                           |

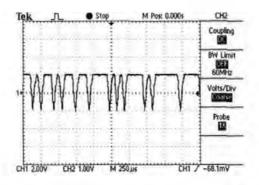

| Figure B-11. FM demodulator TP E - Differential phase detector output prior to               |

| matched filtering (25 symbol periods)                                                        |

| Figure B-12. FM demodulator TP F - Differential phase detector output after root                          |

|-----------------------------------------------------------------------------------------------------------|

| 40% raised Cosine matched filter (25 symbol periods)185                                                   |

| Figure B-13. FM demodulator TP G - Full wave rectified data signal stimulus for IIR                       |

| clock recovery filter (25 symbol periods)186                                                              |

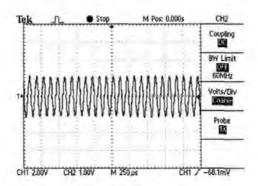

| Figure B-14. FM demodulator TP H - Output from IIR clock recovery filter (25                              |

| symbol periods)                                                                                           |

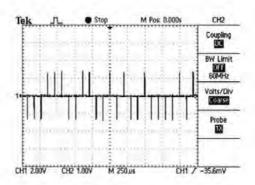

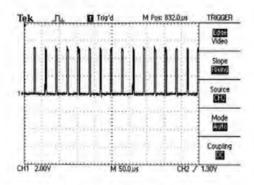

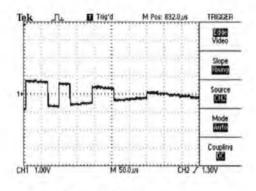

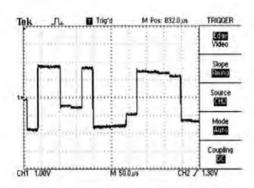

| Figure B-15. FM demodulator TP I - Symbol clock positive going zero crossing                              |

| detector output (25 symbol periods)                                                                       |

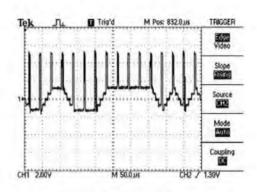

| Figure B-16. FM demodulator TP J - Sampled data output prior to data decision                             |

| threshold (25 symbol periods)                                                                             |

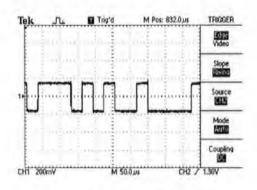

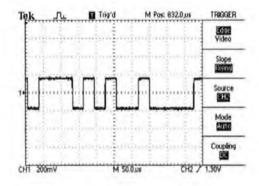

| Figure B-17. FM demodulator TP K - Detected synchronous (clocked) data after                              |

| decision threshold (25 symbol periods)                                                                    |

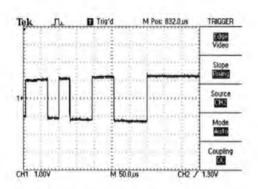

| Figure B-18. FM demodulator TP L - De-scrambled data applied to output buffer (25                         |

| symbol periods)187                                                                                        |

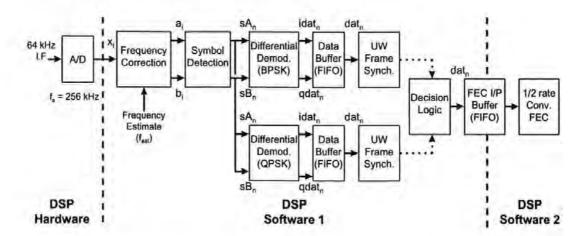

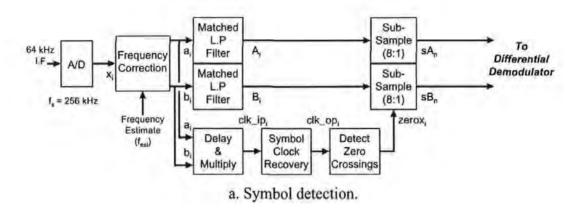

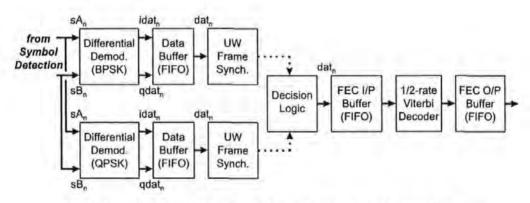

| Figure D-1. BPSK/QPSK software-based DSP burst demodulator - overview 197                                 |

| Figure D-2. BPSK/QPSK software-based DSP burst demodulator - detailed overview.                           |

| 198                                                                                                       |

| Figure D-3. Demodulator input sample stream x <sub>i</sub> (32ksps BPSK signal, f <sub>c</sub> =64kHz, 16 |

| symbol periods shown)                                                                                     |

| Figure D-4. Frequency corrected sample streams a <sub>i</sub> +jb <sub>i</sub> (250Hz residual frequency  |

| error, 16 & 160 symbol periods shown)                                                                     |

| Figure D-5. Matched filtered frequency corrected sample streams A <sub>i</sub> +jB <sub>i</sub> (250Hz    |

| residual frequency error, 16 & 160 symbol periods shown)200                                               |

| Figure D-6. Symbol clock recovery filter signal samples clk_ipi and clk_opi (250Hz                        |

| residual frequency error, 16 symbol periods shown)200                                                     |

| Figure D-7. Location of +ve zero crossings in recovered symbol clock zerox; (16                           |

| symbol periods shown)                                                                                     |

| Figure D-8. Detected symbols sA <sub>n</sub> +j sB <sub>n</sub> (250Hz residual frequency error, 16 & 160 |

| symbol periods shown)201                                                                                  |

| Figure D-9. BPSK differential demodulator output idat <sub>n</sub> +jqdat <sub>n</sub> (BPSK signal       |

| transmitted, 250Hz residual frequency error, 16 symbol periods shown) 202                                 |

| Figure D-10. QPSK differential demodulator output idatn+jqdatn (BPSK signal                               |

| transmitted, 250Hz residual frequency error, 16 symbol periods shown) 202                                 |

| Figure D-11. Demodulator input sample stream x <sub>1</sub>                                               |

| Figure D-12. Frequency corrected sample streams $a_i + j b_i$ (250Hz residual frequency                 |

|---------------------------------------------------------------------------------------------------------|

| error, 16 & 160 symbol periods shown)203                                                                |

| Figure D-13. Matched filtered frequency corrected sample streams A <sub>i</sub> +jB <sub>i</sub> (250Hz |

| residual frequency error, 16 & 160 symbol periods shown)                                                |

| Figure D-14. Symbol clock recovery filter signal samples clk_ipi and clk_opi (250Hz                     |

| residual frequency error, 16 symbol periods shown)204                                                   |

| Figure D-15. Location of +ve zero crossings in recovered symbol clock zerox <sub>i</sub> (250Hz         |

| residual frequency error, 16 symbol periods shown)205                                                   |

| Figure D-16. Detected symbols sAn+j sBn (250Hz residual frequency error, 16 & 160                       |

| symbol periods shown)                                                                                   |

| Figure D-17. BPSK differential demodulator output idat <sub>n</sub> +jqdat <sub>n</sub> (QPSK signal    |

| transmitted, 250Hz residual frequency error, 32 symbol periods shown) 206                               |

| Figure D-18. QPSK differential demodulator output idat <sub>n</sub> +jqdat <sub>n</sub> (QPSK signal    |

| transmitted, 250Hz residual frequency error, 32 symbol periods shown)206                                |

| Figure D-19. Frequency correction TMS320C50 assembly code209                                            |

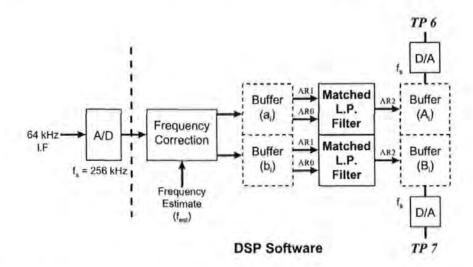

| Figure D-20. DSP burst demodulator implementation - frequency correction210                             |

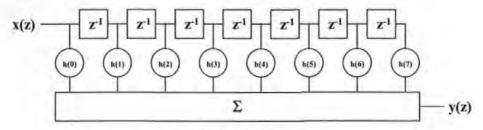

| Figure D-21. Matched data filter (integrator)                                                           |

| Figure D-22. Matched filter TMS320C50 assembly code212                                                  |

| Figure D-23. DSP burst demodulator implementation - matched filtering213                                |

| Figure D-24. DSP burst demodulator implementation - differential detection216                           |

| Figure D-25. Burst transmitter digital hardware                                                         |

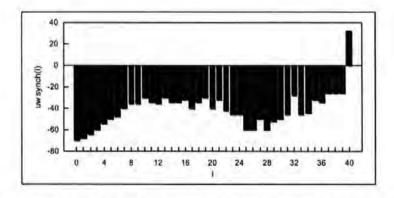

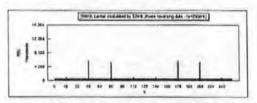

| Figure D-26. Optimum 40-bit Unique Word search result - sequence 0x5d70e219                             |

| Figure D-27. DSP burst demodulator implementation - UW frame synch220                                   |

| Figure D-28. TMS320C50 assembly code - write to I/P FIFO buffer (DSP 1)225                              |

| Figure D-29. TMS320C50 assembly code - read from I/P FIFO buffer (DSP 2)225                             |

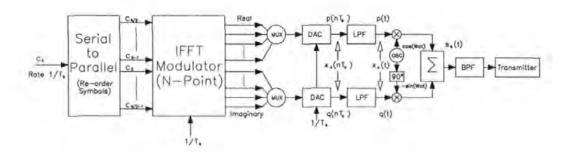

| Figure E-1 Complex sampling OFDM modulator                                                              |

| Figure E-2. OFDM spectra - a. sampled baseband OFDM signal $x_c(nT_b)$ , b. baseband                    |

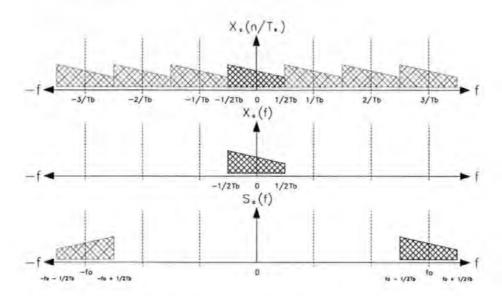

| OFDM signal $x_c(t)$ , c. transmitted OFDM signal $s_c(t)$                                              |

| Figure E-3 Real sampling OFDM modulator                                                                 |

| Figure E-4. OFDM spectra - a. sampled baseband OFDM signal $x_r(nT_b/2)$ , b.                           |

| baseband OFDM signal $x_r(t)$ , c. mixer output $s_I(t)$ , d. transmitted signal $s_r(t)$ 232           |

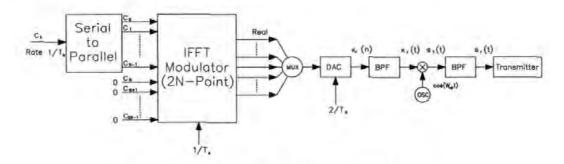

| Figure E-5 Complex sampling OFDM demodulator                                                            |

| Figure E-6. OFDM spectra - a. received OFDM signal $r(t)$ , b. baseband OFDM signal                     |

| $y(t)$ , c. sampled baseband OFDM signal $y(nT_b)$ 235                                                  |

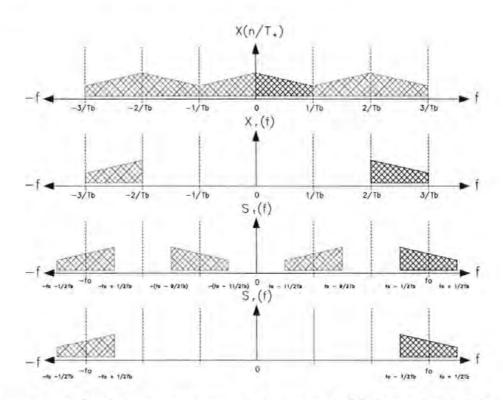

| Figure E-7 Real sampling OFDM demodulator                                           |  |

|-------------------------------------------------------------------------------------|--|

| Figure E-8. OFDM spectra - a. received OFDM signal $r(t)$ , b. baseband OFDM signal |  |

| $y(t)$ , c. sampled baseband OFDM signal $y(nT_b)$ 238                              |  |

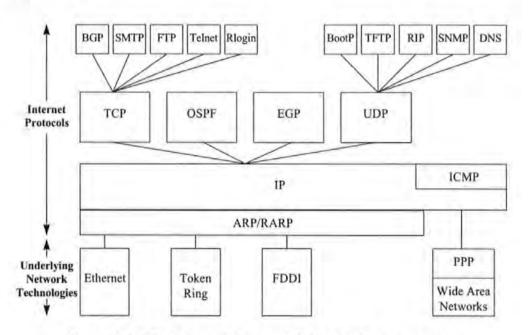

| Figure F-1. The Internet Protocol Suite (Major Protocols)241                        |  |

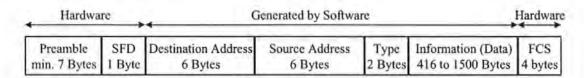

| Figure F-2. Ethernet Frame structure                                                |  |

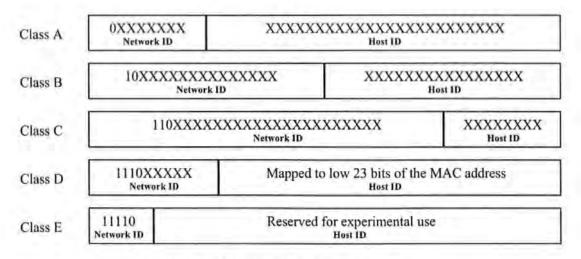

| Figure F-3 Internet address classes                                                 |  |

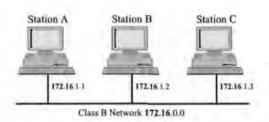

| Figure F-4 Network on which direct routing may be used247                           |  |

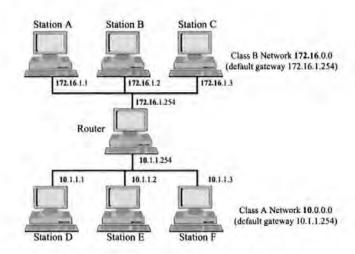

| Figure F-5 Two Networks linked by a Router                                          |  |

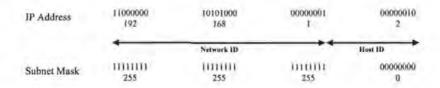

| Figure F-6 Using a Subnet Mask to define Network and Host ID249                     |  |

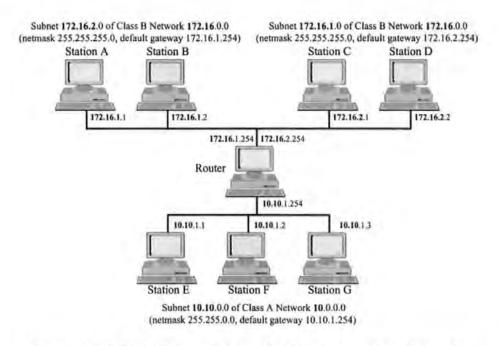

| Figure F-7 A Multi-homed Router linking three logical Networks250                   |  |

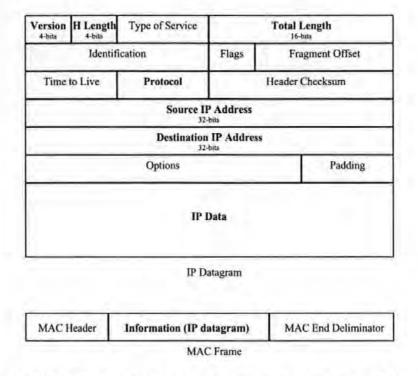

| Figure F-8. IP Datagram format and encapsulation within a MAC Frame252              |  |

| Figure F-9. TCP and the four-layer model                                            |  |

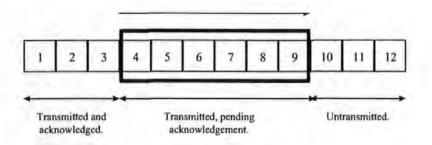

| Figure F-10. Sliding Window principle                                               |  |

| Figure F-11. Sliding Window example                                                 |  |

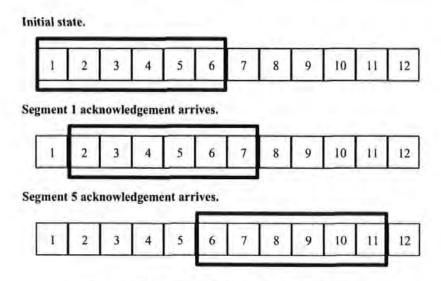

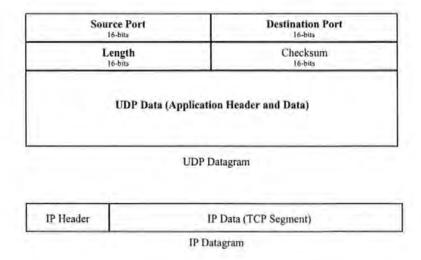

| Figure F-12. TCP Segment format and encapsulation within an IP Datagram257          |  |

| Figure F-13. UDP and the four-layer model                                           |  |

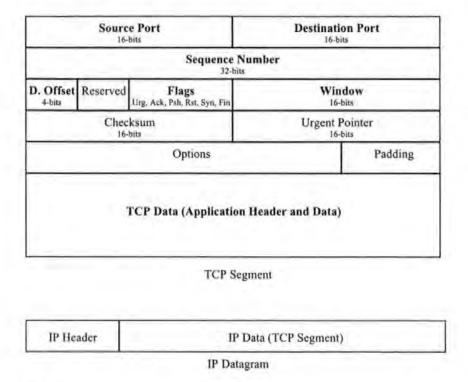

| Figure F-14. UDP Datagram format and encapsulation within an IP Datagram258         |  |

| Figure G-1. Hybrid satellite Internet delivery system - system overview260          |  |

| Figure G-2. Hybrid satellite Internet delivery system - network diagram261          |  |

| Figure G-3. Data broadcast PC interface                                             |  |

| Figure G-4. Data broadcast receive interface card                                   |  |

| Figure G-5. Asymmetric satellite Internet delivery system - system overview265      |  |

| Figure G-6. Asymmetric Internet delivery system - network diagram266                |  |

| Figure G-7. Host PC data broadcast PC interface card                                |  |

| Figure G-8. User MPEG-2 receive PC interface card                                   |  |

| Figure G-9. User Return Link PC interface card                                      |  |

| Figure G-10. User 14GHz outdoor equipment 268                                       |  |

| List of Tables                                                                         |

|----------------------------------------------------------------------------------------|

| Table 2-1. A 'Tan-1 Look-Up Table' with unacceptable output precision in the range     |

| 0° - 80°3                                                                              |

| Table 2-2. A practical 'Tan-1 Look-Up Table'                                           |

| Table 2-3. Illustration of improvements to FM demodulator software efficiency wit      |

| the use of block processing and sub-sampling3                                          |

| Table 3-1. FFT carrier frequency acquisition performance                               |

| Table 3-2. Offset-FFT carrier frequency acquisition performance5                       |

| Table 3-3. Optimum FFT coefficient memory utilisation                                  |

| Table 3-4. General FFT coefficient memory utilisation.                                 |

| Table 3-5. Odd harmonic bin locations for phase reversing preamble (fc=64kHz)6         |

| Table 3-6. Clock recovery IIR filter parameters for Q-factors from 50 to 3200 - target |

| f <sub>0</sub> = 0.125, f <sub>8</sub> =16                                             |

| Table 3-7. G[5,7,7] convolutional code encoding example                                |

| Table 3-8. 'Previous States' look-up table                                             |

| Table 3-9. 'Metric Update' look-up table                                               |

| Table 3-10. 'Encoder Output' look-up table                                             |

| Table 3-11. Optimised 'Encoder Output' look-up table                                   |

| Table 3-12. Comparison of metric computation overhead in 'Standard' & 'Double          |

| Clocked' Viterbi decoder algorithms9                                                   |

| Table 3-13. Comparison of metric computation overhead in 'Standard' & 'Triple          |

| Clocked' Viterbi decoder algorithms9                                                   |

| Table 3-14. Experimental BER test results - G[133,171] code9                           |

| Table 4-1. Typical preamble data structure for OFDM carrier frequency and symbol       |

| timing synchronisation10                                                               |

| Table 5-1. Modifications for enhancing TCP over satellite channels [57]14              |

| Table 5-2. General characteristics of ACK, OPEN and DATA traffic14                     |

| Table A-1 Applications for the TMS320C5x DSPs (Source - Texas Instruments)16           |

| Table C-1. Butterfly computations for Pass 2 of an 8-point Offset-FFT19                |

| Table C-2. Butterfly computations for Pass 1, Group 0 of an 8-point Offset-FFT 19      |

| Table C-3. Butterfly computations for Pass 1, Group 1 of an 8-point Offset-FFT 19      |

| Table C-4. Butterfly computation for Pass 0, Group 0 of an 8-point Offset-FFT 19       |

| Table C-5. Butterfly computations for Pass 0. Group 1 of an 8-point Offset-FFT19       |

| Table C-6. Butterfly computations for Pass 0, Group 2 of an 8-point Offset-Fl  | FT 195 |

|--------------------------------------------------------------------------------|--------|

| Table C-7. Butterfly computations for Pass 0, Group 3 of an 8-point Offset-Fl  | FT196  |

| Table D-1. Effect of linear phase error on differentially detected BPSK symbol | ols215 |

| Table D-2. Memory organisation for FIFO buffer (depth = 5 locations)           | 224    |

| Table E-1 Summary of OFDM modulator model requirements                         | 239    |

| Table E-2 Summary of OFDM demodulator model requirements                       | 239    |

| Table F-1. Common Ethernet 'type' codes                                        | 244    |

| Table F-2. Common IP protocol codes.                                           | 253    |

#### Acknowledgements

I'd like to thank my supervisors Prof. Martin Tomlinson and Dr. Graham Wade for their wisdom and guidance.

I would also like to thank my colleagues Paul Smithson, Peter van Eetvelt and Adrian Ambroze for their advice, encouragement and friendship throughout.

This work is dedicated to Jenny, Wendy & John Slader, and could not have been completed without their continuing love and support.

#### Author's Declaration

At no time during the registration for the Degree of Doctor of Philosophy has the author been registered for any other University award.

This study was financed by a University of Plymouth studentship.

Relevant scientific seminars and conferences were regularly attended and work was presented at major International conferences. Three papers were prepared for publication and published (Slader et al., 1996; Smithson et al., 1996; Slader et al., 1998).

Signed Janes T Steh

Date 28/10/2001

#### 1. Introduction

This Thesis is concerned with digital software-based modems for low-cost satellite links using both Low Earth Orbiting (LEO) and Geosynchronous Earth Orbiting (GEO) satellites. The work considers carrier frequency synchronisation, filtering, symbol timing synchronisation, burst demodulation and forward error correction. The main aims are to investigate the tradeoffs in performance which are required to realise the signal processing algorithms in real-time. The work investigates low-complexity, software-based signal processing algorithms for satellite modulator/demodulators and their real-time implementation on signal processing hardware based upon the Texas Instruments TMS320C50 fixed-point DSP, see Appendix A. The work divides into three strands and considers the carrier frequency and symbol timing synchronisation requirements for satellite data communication using frequency modulation (FM), differential phase modulation (D-BPSK, D-QPSK) and orthogonal frequency division modulation (OFDM). Much of this work is embodied in a satellite system which is now operational and is discussed later in the Thesis. This work also includes transport protocols for mapping TCP/IP applications to low-cost satellite return links and channel access protocols for fair and efficient utilisation of shared return channels.

#### 1.1 Introduction and Background to Digital Modems & Software Radio

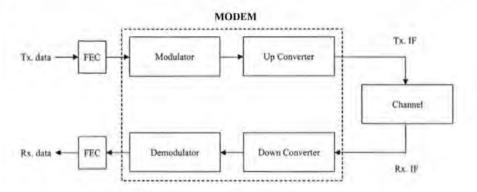

The following is an introductory background to digital modems and software radio. Figure 1-1 shows a block diagram of a typical digital communication system.

Figure 1-1. Digital communication system overview.

Data for transmission is encoded for forward error correction (FEC), to protect against channel errors, and is applied to the input of the modem where the modulator processes the data depending upon the choice of modulation and coding schemes. The modulation scheme depends upon whether power efficiency or spectral efficiency is of greater importance. Spectral efficiency of 2bits/sec/Hz is achieved practically with high order modulation schemes such as 8-phase shift keying (8-PSK) and 16-Quadrature amplitude modulation (16-QAM). The output from the modulator is a bandpass signal centred on an intermediate frequency (IF), and the upconverter performs translation of the signal to the desired transmit IF. In satellite communication it is common for the upconverter to provide a 70MHz transmit IF interface for satellite Earth Station applications. The channel adds noise to the signal and, depending upon the application, the signal can also be distorted in a number of ways. Satellite links are particularly susceptible to signal attenuation due to climatic effects such as rain. The downconverter operates in reverse to the upconverter, mixing the signal back down from the receive IF to a second (lower frequency) IF for the demodulator. The demodulator is responsible for receive filtering and sampling the wanted signal. Once the signal is sampled it can be processed digitally to compensate for carrier frequency and symbol timing errors allowing the received bits to be extracted. Occasional demodulated bit errors may be tolerated because of the FEC scheme, and the original transmitted data stream is reproduced at the output of the modem.

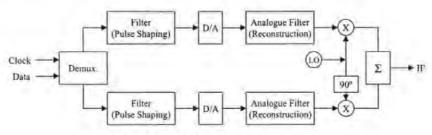

#### 1.1.1 Outline Baseband I/Q and Digital Low IF Modulators

Figure 1-2a shows a baseband I/Q modulator structure. The demultiplexer generates odd and even bit sequences and each is oversampled and shaped by a digital filter to eliminate intersymbol interference (ISI) between successive symbols. After digital to analogue conversion (D/A) the signals are passed through analogue reconstruction filters and mixed up to an IF by a quadrature analogue modulator. Problems associated with this structure are mainly due to the accuracy of the analogue modulator, where any amplitude and phase imbalance result in a degradation to system performance. The characteristics of the D/A pair are also critical and must be matched in terms of output range and conversion times. These factors become even more significant as the order of the modulation scheme increases.

a. Baseband I/Q analogue modulator.

b. Digital low IF modulator.

Figure 1-2. Basic I/Q modulator structures.

The problems associated with the baseband I/Q analogue modulator may be overcome by shifting the signal from baseband digitally and reconstructing the bandpass signal on a low frequency IF, Figure 1-2b. With upconversion performed in the digital domain the problems associated with the analogue modulator are avoided, only one D/A converter is required and several analogue components are eliminated. Since the low IF modulator structure is digital, functions may be reordered and novel architectures developed; such refinements are presented later in the Thesis.

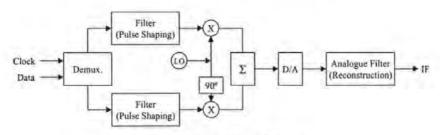

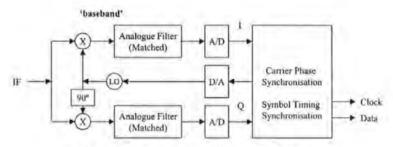

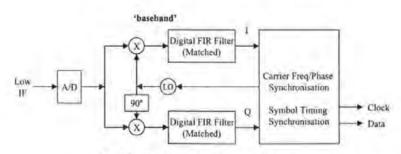

#### 1.1.2 Outline Baseband I/Q and Low IF Demodulator Structures

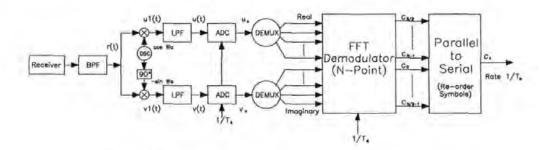

Figure 1-3a shows the front end of a baseband I/Q demodulator with analogue quadrature demodulator. The signal is shifted down to 'nominal' baseband by an analogue quadrature down converter and is subject to the same potential for amplitude and phase imbalance as the modulator equivalent. The signal plus noise is filtered using analogue filters which are matched to those pulse shaping filters in the modulator. After filtering, the I and Q components are sampled and their digital outputs processed to remove symbol timing and carrier phase offsets. Feedback from the digital section to the analogue downconverter is subject to additional digital to analogue conversion.

a. Baseband analogue I/Q demodulator.

b. Digital low IF demodulator.

Figure 1-3. Basic I/Q demodulator structures.

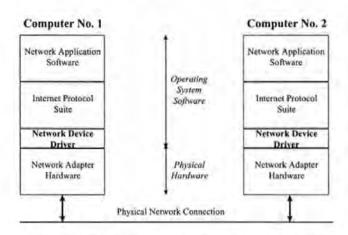

The front end of a digital low IF demodulator is shown in Figure 1-3b. The downconversion process is similar to the baseband I/Q structure, but the difference is in their implementation. Instead of mixing down to baseband in the analogue domain, the signal is mixed down to a low frequency IF and mixed to baseband in the digital domain. The A/D must therefore have sufficient bandwidth and signal to noise ratio to sample the wideband signal so that performance is not degraded over the frequency range of operation. Another difference is that receive filtering is conducted in the

digital domain and can therefore be perfectly matched with the transmit filters. In a noiseless environment no ISI will occur between adjacent symbols, and digital filters provide the additional advantage of constant group delay. As with the modulator, the low frequency IF demodulator eliminates many analogue components making performance more predictable and repeatable. In terms of digital components, only one A/D is required but with somewhat greater performance requirements. Digital downconversion may be realised efficiently using look-up tables (LUTs) and the digital filters with finite impulse response (FIR) digital filter structures, carrier frequency and phase synchronisation can be conducted completely in the digital domain. As with the modulator, the low IF demodulator structure is also completely digital giving potential for functions to be reordered and novel architectures to be developed. Novel architectures and refinements to downconversion, filtering, carrier frequency synchronisation, symbol timing synchronisation and many other areas are discussed throughout the Thesis.

#### 1.1.3 Software Radio

The low IF digital modem structures described previously are commonly implemented with discrete digital hardware but recent advances in Digital Signal Processor (DSP) technology are now beginning to offer a software-based alternative. The main advantage of software-based modems over custom hardware and application specific integrated circuits (ASICs) is that of flexibility and upgradeability. A software implementation also allows generic hardware to be developed which can be tailored to specific applications. This software can be replaced at any time when improvements are made or if changes are required, and such updates can even be applied automatically over-the-air.

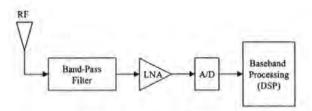

Building on the above, the software radio concept is summarised in <sup>[1]</sup> as follows; "Software radio in an emerging technology to build flexible radio systems which are multi-service, multi-standard, multi-band, reconfigurable and reprogrammable by software". Current modems employ an analogue RF front end and digital processing only in the latter stages, the 'ideal' software radio moves the boundary between analogue and digital to the RF input and performs <u>all</u> processing with software in the digital domain, Figure 1-4.

Figure 1-4. Ideal 'Software Radio' receiver.

The 'ideal' software radio transceiver is unrealisable with today's technology [2] and Figure 1-4 is considered as a long term target. The main limitations are associated with A/D and digital signal processor technologies. In the former case jitter performance is currently unacceptable at high sample rates and input resolution must be sacrificed as speed increases, ie. 6-bit to 8-bit resolution at Gsamples/second, 10-bit resolution for Msamples/second and 16-bit resolution for ksamples/second. In the latter case today's signal processors have relatively long instruction cycle times and cannot yet achieve real-time operation at the highest sample rates.

From the literature [1]-[20] it is clear that the 'ideal' software radio is not expected by many researchers in the field for another decade, when it is predicted that technology will have advanced sufficiently. The first step is to employ flexible analogue front-ends where the selection of operating frequency, channel and bandwidth can be made under software control, and with software-based signal processing between baseband frequencies and a low IF. Numerous researchers are working on enabling technologies including D/A, filtering and receiver architectures [13]-[18] so that, as technology improves, the boundary between analogue and digital can gradually shift towards the RF input. Other researchers are striving to define standards for the implementation of software modules so that a consistent and flexible interface is employed throughout [3]. Part of this research includes protocols for software download which will allow over-the-air updates to be conducted either ondemand or automatically as required [5]. Other topics of research include mobility management, security and user applications. The author's main interests are in novel real-time software architectures for combined modulation, demodulation, frequency synchronisation, timing synchronisation and FEC based upon the low IF structures described previously. The work in this Thesis also explores compromises to optimum theoretical performance which are required to achieve real-time operation with today's DSP technology and identifies suitable applications.

#### 1.2 Application of Software-Based Signal Processing in Low-Cost Satellite Return Links

Where high data rates (>>1Mbps) are concerned, ASICs and (or) custom digital hardware is required to achieve real-time execution of complex signal processing algorithms. At lower data rates (<1Mbps) Digital Signal Processors and software-based algorithms can also achieve real-time execution and offer increased flexibility. Applications for software-based modems must therefore combine a requirement for complex signal processing with a relatively low data throughput. The following provides a brief introductory background to one such application in low-cost satellite return links.

#### 1.2.1 Introduction to Low-Cost Satellite Return Links

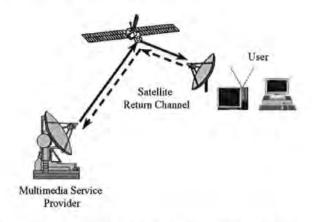

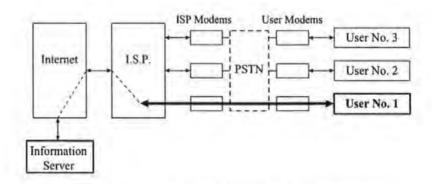

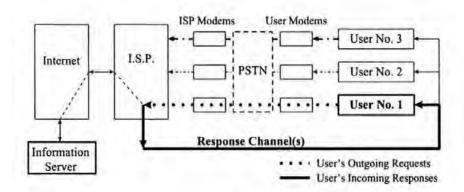

The use of MPEG-2 compressed digital TV provides increased channel capacity in comparison to conventional analogue satellite broadcasting and allows a greater range of services to be provided. These new services can include video on demand, home shopping, distance learning, delivery of Internet data and a wealth of other interactive multimedia applications. These services are typically asymmetric with large amounts of data sent from the service provider to the user but with little, or nothing, sent from the user in return. To provide a fully interactive service, and to allow true user interaction, a return channel from the user to the service provider is required. A return channel can be provided terrestrially by the public switched telephone network (PSTN), the integrated services digital network (ISDN), cable modem, dedicated terrestrial circuit or by radio link. All terrestrial return channels have the requirement for an existing communications infrastructure, which may not be available due to local investment or geographic location.

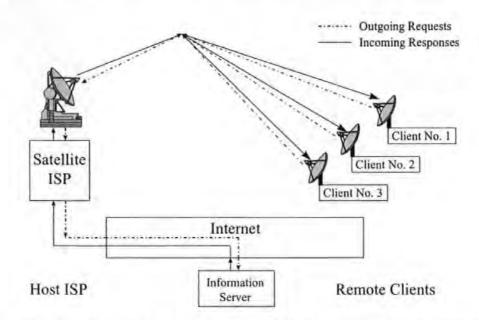

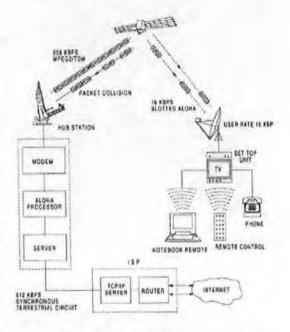

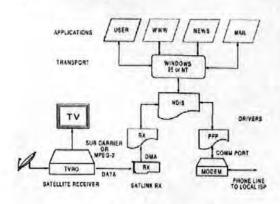

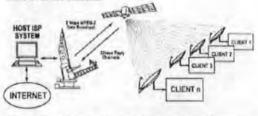

Another solution, which has none of the limitations associated with terrestrial return channels, is to provide a satellite data return channel, Figure 1-5. A satellite return channel can be provided anywhere within a satellite's footprint and has no requirement for an existing local communications infrastructure.

Figure 1-5. Interactive satellite DVB system with satellite return channel.

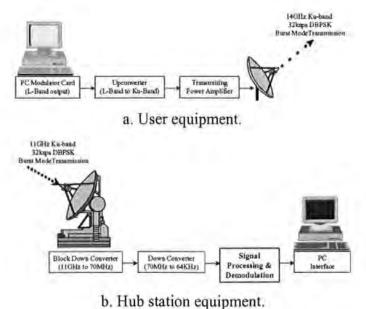

#### 1.2.2 Signal Processing Requirements in Low-Cost Satellite Return Links

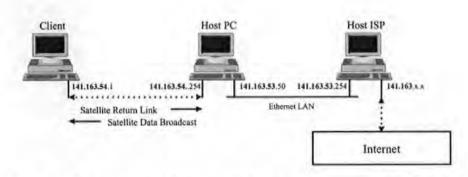

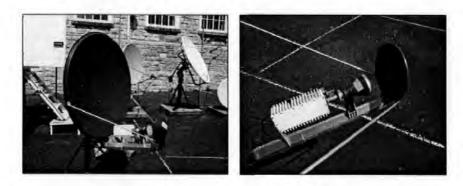

The cost of conventional Very Small Aperture Terminal (VSAT) technology is currently prohibitive and part of the work in this Thesis was driven by the desire to provide low cost satellite data reply links using a conventional Television Receive Only (TVRO) antenna equipped with a small transmitting power amplifier, Figure 1-6a. The frequency stability of this equipment is typically not very good and, as a consequence, signal processing algorithms are required at the Hub Station to compensate, Figure 1-6b. Other low-cost satellite links can be provided using Low or Medium Earth Orbiting (LEO or MEO) satellites where the requirements for signal processing differ.

Figure 1-6. Outline Ku-band satellite data reply link system.

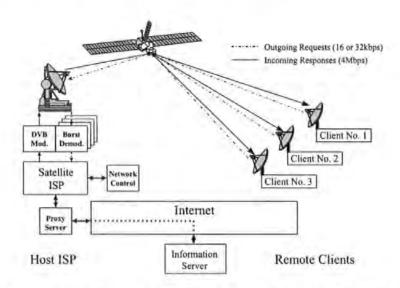

#### 1.2.3 Satellite Internet Delivery Systems

A great deal of interest is currently being shown towards high-speed delivery of Internet data by satellite. Benefits of such systems include higher download speeds, alleviation of congestion on terrestrial network segments and the ability to simultaneously reach large and widely separated user groups. Some are adopting the multicast approach where the most popular Web pages are broadcast to all terminals and stored (cached) locally for faster access. In these systems the user may be required to form a temporary PSTN connection in order to request information that has not been cached. Other systems, including investigations involving the author <sup>[53]</sup>, employ a low-cost satellite return link to provide a 'permanently connected' return channel. In these systems the author's main interests are with channel access protocols, to allow request channels to be shared efficiently by multiple users, and transport protocols for mapping TCP/IP traffic to low-cost satellite links. Novel systems and protocols are discussed in detail later in the Thesis.

#### 1.3 Organisation of Thesis

Chapter 2 is concerned with frequency synchronisation in modems for use with LEO (Low Earth Orbiting) microsatellites. These investigations were funded by I.S.T. (Instituto Superior Technico) of Lisbon, Portugal in relation to the PoSAT-1 microsatellite [33]. The main focus for these investigations was tracking the Doppler frequency error experienced at the demodulator input, providing correction within the demodulator and also providing pre-correction for the uplink at the modulator output. Algorithms are presented in this Chapter which satisfy these aims and are suitable for real-time implementation on TMS320C50 fixed-point DSPs. To allow the synchronisation algorithms to be evaluated both modulator and demodulator algorithms were also investigated. Many optimisations and compromises are required to achieve real-time execution, hence the Chapter is also concerned with efficient algorithms for frequency correction, frequency modulation, frequency discrimination and data shaping filters. The algorithms were verified in back-to-back simulations and the results are discussed at the end of the Chapter. A Doppler tracking modem was implemented using four DSPs and is described in Appendix B.

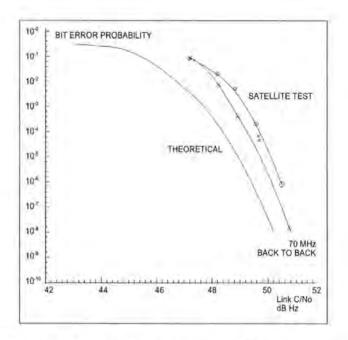

Chapter 3 is concerned with DSP software-based burst demodulator algorithms, and in particular with rapid carrier frequency acquisition and symbol timing synchronisation. In contrast to Chapter 2 these investigations were conducted with respect to Geostationary satellites and employ differential phase modulation. These investigations were funded in part by BNSC (The British National Space Council) and ESA (The European Space Agency) and satellite trials were conducted with collaboration from Eutelsat. Algorithms for a burst demodulator are discussed in Chapter 3 which satisfy the aims of the investigation and are evaluated in both backto-back and satellite trials towards the end of the Chapter. Carrier frequency acquisition and symbol timing synchronisation is achieved after 32 symbols have been received with the use of a modified FFT algorithm, known as the Offset-FFT [36], and a 'delay and multiply' symbol clock recovery technique based upon an IIR resonator filter [42]. For operation at low SNR it is necessary to employ FEC over the satellite channel, but it was found that a Viterbi decoder algorithm for a standard constraint length 7 1/2-rate convolutional code represented a significant computation overhead. A modification to the standard Viterbi decoder algorithm is also discussed which reduces computation overhead to acceptable levels. Part of the work from this Chapter was published in (Slader et al., 1996), Appendix H, and the complete burst demodulator is described in Appendix D.

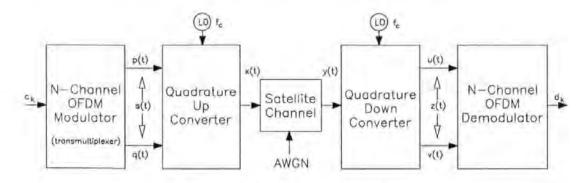

Chapter 4 is concerned with OFDM (Orthogonal Frequency Division Multiplexing) as a means to achieve higher data throughput for the equivalent DSP computation capacity. These investigations were funded by EPSRC (Engineering and Physical Sciences Research Council). The aims for these investigations were to identify suitable synchronisation algorithms to form the basis of a coherent software-based OFDM modem for use in satellite applications. The Chapter begins with an overview of OFDM modems, and a mathematical comparison between real-sampling and complex-sampling configurations is made in Appendix E. Carrier frequency and symbol timing synchronisation are critical with OFDM and the effects of frequency error and symbol timing error are explored analytically within the Chapter. The Offset-FFT [36] is identified as a means to achieve simultaneous demodulation and frequency correction which allows synchronisation algorithms to operate on the demodulated data directly. Low complexity synchronisation algorithms are derived which, in conjunction with an optimised preamble sequence, are suitable for DSP

software implementation. These algorithms are evaluated by simulation and results are presented at the end of the Chapter.

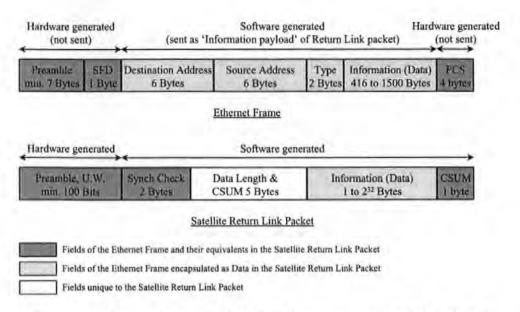

To confirm the relevance of the work in this Thesis Chapter 5 is concerned with a practical application for DSP software-based modems in asymmetric satellite Internet delivery systems. The author has contributed to investigations into asymmetric satellite Internet delivery systems employing both terrestrial and satellite data reply channels. In the latter case, techniques from Chapter 3 were successfully utilised. The Chapter begins with a generic overview of Internet delivery systems and defines symmetrical and asymmetric system configurations. This introduction is complemented by a review of the Internet Protocol Suite and IP networking concepts in Appendix F. A novel asymmetric satellite Internet delivery system is described along with the software techniques employed to allow IP transmission over a satellite data reply channel. The delays of each satellite link impose a fundamental limitation on the average transfer rate which can be achieved in satellite based TCP/IP networks. These limitations are discussed and modifications to overcome these limitations are reviewed. The most important components of the system are the low-speed satellite return channels which must be shared efficiently by the users without contention (collision). The final section of Chapter 5 identifies characteristics of the return channel transmission and evaluates the effectiveness of frequency-hopping and demand-assigned TDMA channel access mechanisms. Two publications resulting from this work, (Smithson et. al., 1996) and (Slader et. al., 1998), can be found in Appendix I and Appendix J respectively.

In Chapter 6 the work in this Thesis is summarised, conclusions are drawn and topics for further investigations identified.

#### 2. A Doppler Tracking Modem for LEO Microsatellites

The PoSAT-1 satellite [33] is one of a series of Polar orbiting LEO (Low Earth Orbiting) microsatellites manufactured by the University of Surrey. These typically contain a store and forward processing payload which allows messages to be transmitted to the satellite as it passes overhead and downloaded on request by a receiver in another part of the world. The data rate to and from the satellite is 9.6kbps and employs frequency modulation. As a result of the Doppler frequency shift experienced by the receiver, due to the satellite's orbital velocity, the centre frequency of the signal received from the satellite may be shifted by ±10kHz. This is a significant amount relative to the bandwidth of the signal and must be corrected prior to demodulation. Similarly, transmissions to the satellite must be pre-corrected (tuned in the opposite direction) so that the centre frequency is correct when received by the satellite. Both Doppler tracking and modulator/demodulator functions are suitable for implementation with DSP software due to the increased flexibility offered. Funding from I.S.T. (Instituto Superior Technico) Lisbon, Portugal was provided to investigate DSP algorithms for a Doppler-tracking modulator and demodulator for use with PoSAT-I and similar LEO microsatellites [32]. This research was concerned specifically with frequency synchronisation and Doppler tracking, and a two-stage frequency synchronisation process was devised involving FFT-based algorithms for coarse frequency synchronisation and feedback within the demodulator to achieve fine frequency synchronisation (Doppler tracking); sections 2.1.1 and 2.1.2 respectively.

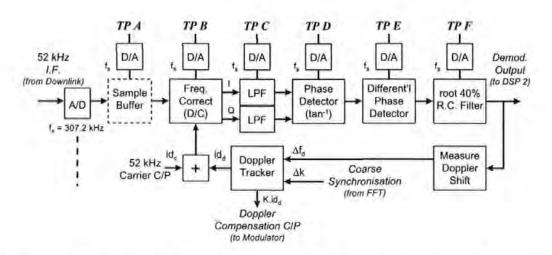

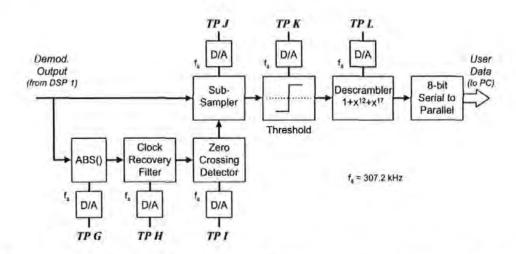

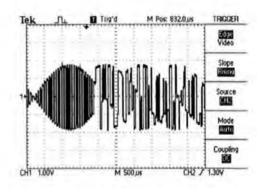

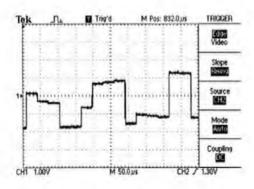

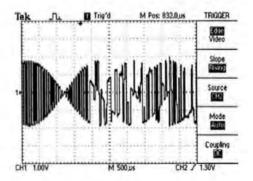

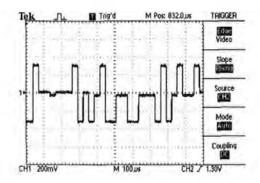

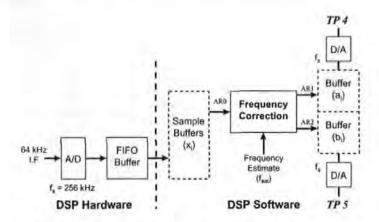

For evaluation of the frequency synchronisation algorithms it was necessary to implement both 9.6kbps FM modulator and demodulator [34]. The FM modulator was implemented with software on a single DSP while the FM demodulator was implemented with software on dual-DSP hardware; due to the intensive nature of the demodulator algorithms. Descriptions of the modulator and demodulator and signal plots from each stage of the software are presented in Appendix B. In order to achieve real-time execution, processing overheads were minimised with a combination of optimised software routines and by making carefully selected compromises to theoretical performance, the main techniques employed are discussed in section 2.2. Pre-Doppler compensation is introduced within the modulator and Doppler correction

is applied to the demodulator using a synthesised local oscillator. In section 2.2.1, the manner in which the local oscillator is implemented is shown as a means to reduce processing overhead. The system employs matched root 40% raised cosine filtering, which would generally require a FIR filter with many (hundreds of) coefficients. To reduce processing overhead this was implemented with a pre-computed LUT in the modulator and with an IIR filter approximation in the demodulator, section 2.2.2. The most intensive portion of the FM demodulator was frequency discrimination, and a phase detector implemented with a LUT is discussed in section 2.2.3. Finally, in section 2.2.4, the use of block sample processing and selective sub-sampling is shown as an effective means of dramatically reducing processing overhead. Results and conclusions are presented in sections 2.3 and 2.4 respectively.

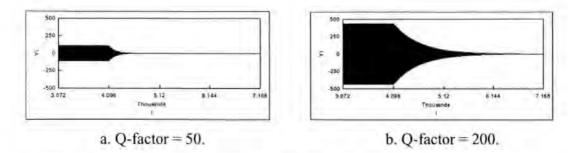

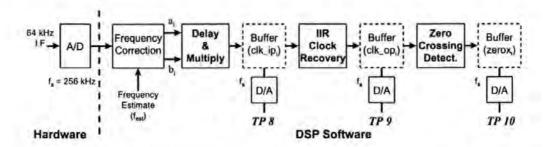

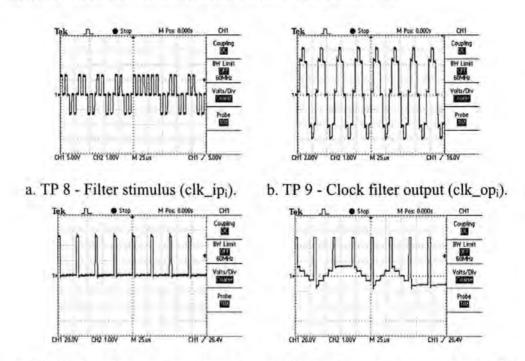

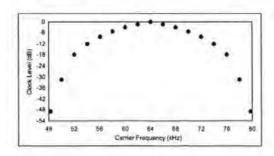

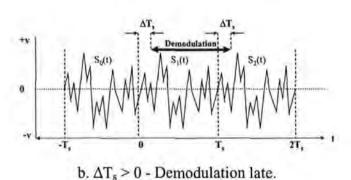

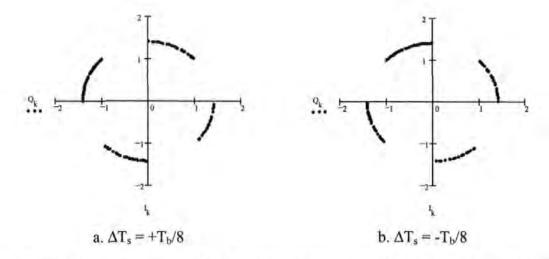

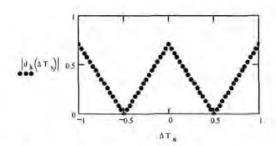

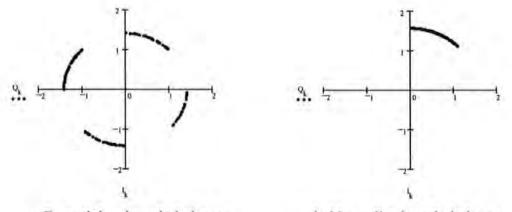

#### 2.1 Frequency Synchronisation and Doppler Tracking