# A KNOWLEDGE BASED SUPPORT TOOL FOR THE EARLY STAGES OF ELECTRONIC ENGINEERING DESIGN

DEAN GRANT CURTIS SCOTHERN

A thesis submitted in partial fulfilment of the requirements for the Council for National Academic Awards for the degree of Doctor of Philosophy

September 1991

Polytechnic South West

IN COLLABORATION WITH THE UNIVERSITY OF READING. and PLESSEY SEMI-CONDUCTORS, ROBOROUGH, PLYMOUTH.

いまたい

· water ~

いいいないとなったりと

# 90 010 3899 8 TELEPEN

X-X-X-X

4

in the second

# REFERENCE ONLY

|              | SITY OF PLYMOUTH<br>BARY D. BV DECS |

|--------------|-------------------------------------|

| ltem<br>No.  | 900 103899-8                        |

| Class<br>No. | T-006.33 Sco                        |

| Contl<br>No. | X702588244                          |

LIBRARY STORE

## Acknowledgements

I would like to thank both my supervisors Professor Keith Baker and Phil Culverhouse for their sterling support and encouragement during the period of research and patience throughout the long write up.

Thanks also to all the members of the PEDA project team including Professor J.St.B.T Evans, Ian Dennis, Pat Pearce, Peter Jagodzinski, Linden Ball and the late Gill Venner. The continued advice and stimulation of these colleagues proved invaluable in creating a rich and friendly research environment.

I would also like to acknowledge the financial support given by the National Advisory Body, without whom the present programme of research would not have been possible.

Finally I would like to thank the staff of the Computing Dept of R.N.E.C Manadon for the use of a computer during this write up, and my friends the Robs, Rich and Ian, for the long suffering I have subjected them to.

#### **Declarations**

1) Whilst registered for this degree, I have not been a registered candidate for another award of the CNAA or other University.

2) The present research project was funded by a National Advisory grant originally awarded to Professor K.D.Baker and Dr G. Sullivan in 1986. On their departure to Reading University at the end of that year, the grant was taken over by Mr P.F. Culverhouse, Professor J.St.B.T. Evans, and Dr P.D. Pearce. The funding awarded to the present researcher extended over the period from 1st September 1986 to 30th December 1989.

3) The research project was one of three associated projects funded under the N.A.B grant. Whilst the three projects were motivated by the common desire to develop a software system to aid engineers in the early stages of design, each researcher's work was undertaken as a distinct and separable programme of work. The author of this thesis was concerned with the underlying functionality of the design aid. The other two were: (a) concerned with the nature of the cognitive processes in engineering design with the aim of directing the development of the design aid; and (b) the interface to the system.

4) A course of advanced study has been completed in partial fulfilment of the requirements for the degree consisting of: (a) attendance at selected lecture and seminar series run under the M.Sc. Intelligent Systems course at Polytechnic South West; and (b) attendance at a number of relevant professional conferences and workshops.

Early Stages

of Electronic Engineering Design.

Author:

Dean Grant Curtis Scothern

Abstract:

A desire to produce a design support system for the early stages of electronic engineering design, has led to the conception of the Plymouth Engineer's Design Assistant (PEDA), pulling together experience from the three fields of computing, psychology and electronic engineering. The basic emphasis of this tool has been to use psychological techniques to analyze the cognitive aspects of designers in action and then make recommendations for design tool improvement.

The results of the complementary psychological research, and other relevant literature are examined and potential avenues to realizing an improving design explored. A new idealized abstract representation of early electronic engineering is proposed, which is more in line with the cognitive needs of designers, thus enabling the production of more capable design tools. The main points of the representation are discussed, and comparisons with other approaches and tools drawn. The abstract representation is then taken and used to form a specific implementation as the core to the PEDA tool. An overview of the PEDA tool is given, followed by a discussion regarding the important aspects of the implementation. Important issues and problems raised during the course of the research are discussed, together with suggestions for future work.

Title:

# **Table of Contents**

| 1. Introduction                                                    | . 8 |

|--------------------------------------------------------------------|-----|

| 1.1. Overall Structure of this Chapter                             | . 8 |

| 1.2. Underlying Concerns, Aims and Goals                           | . 8 |

| 1.3. General Introduction                                          | . 9 |

| 1.3.1. The Field of Electronic Engineering                         | . 9 |

| 1.3.2. Design Activity                                             | . 9 |

| 1.3.3. The Need for Design Support Environments in                 |     |

| Electronic Engineering                                             | 10  |

| 1.3.4. Design Support Environments                                 | 11  |

| 1.4. Aims of the Research                                          | 13  |

| 1.5. Thesis Outline                                                | 13  |

| 2. Requirements for Early Electronic Engineering Design: The       |     |

| Psychological Basis of the PEDA project.                           | 18  |

| 2.1. Overall Structure of this Chapter                             | 18  |

| 2.2. Justification for Psychological Basis of the PEDA project.    | 18  |

| 2.3. Results of the Related Psychological research                 | 19  |

| 2.4. Requirements for a Design Support System                      | 28  |

| 2.5. Other Relevant Work                                           | 29  |

| 2.6. Relevance To Design Support Systems in Electronic Engineering |     |

|                                                                    | 31  |

| 3. An Idealised Representation for the Early Stages of             |     |

| Electronic Engineering Design                                      | 38  |

| 3.1. Overall Structure of this Chapter                             | 38  |

| 3.2. Rationale for a New Representation                            | 38  |

| 3.2.1. An Examination of Requirements                              | 39  |

| 3.2.1.1. The First Requirement:                                    | 39  |

| 3.2.1.2. The Second Requirement:                                   | 41  |

| 3.2.1.3. The Third Requirement:                                    | 45  |

| 3.2.1.4. The Fourth Requirement:                                     | 48 |

|----------------------------------------------------------------------|----|

| 3.2.1.5. The Fifth Requirement:                                      | 49 |

| 3.2.2. Representational Issues Common to all the                     |    |

| Requirements                                                         | 50 |

| 3.2.2.1. Explicit and Implicit Models of the User.                   | 50 |

| 3.2.2.2. Providing Functionality                                     | 51 |

| 3.2.2.3. The Level of Representation                                 | 51 |

| 3.2.2.4. Efficiency and Implementation Concerns                      | 52 |

| 3.2.3. The Case for a New Representation                             | 52 |

| 3.3. An Idealised Representation for the Early Stages of Engineering |    |

| Design                                                               | 54 |

| 3.3.1. Block Diagram and Alternative Design                          |    |

| Representation                                                       | 55 |

| 3.3.2. Block Diagram and Alternative Management                      | 58 |

| 3.3.3. Constraint Comparison System                                  | 59 |

| 3.3.4. The Equation Based Simulator                                  | 60 |

| 3.3.5. Decision Point System                                         | 63 |

| 3.3.6. Error Detection                                               | 63 |

| 3.4. Comparison with Existing Systems or Methods                     | 65 |

| 3.4.1. Representing Each Design and Design Alternatives              | 65 |

| 3.4.2. Constraints and Constraint Comparison                         | 68 |

| 3.4.3. Simulation                                                    | 69 |

| 3.4.4. History and Decision Record                                   | 70 |

| 3.4.5. Errors and Inconsistencies                                    | 71 |

| 3.4.6. Comparison with Combined Approaches                           | 71 |

| 3.4.6.1. "A Conceptual Framework for ASIC Design                     |    |

| (Leung, Lisher and Shanblatt, 1988)                                  | 71 |

| 3.4.6.2. "An object based representation for the                     |    |

| evolution of VLSI designs" (Gabbe and                                |    |

| Subrahmanyam, 1987)                                                  | 73 |

| 3.4.6.3. Walker and Thomas: the System Architect's                   |    |

| Workbench.                                                           | 74 |

| 3.4.6.4. Knapp and Parker Advanced Design                            |    |

| AutoMation project (ADAM)                                    | 75  |

|--------------------------------------------------------------|-----|

| 3.5. Summary                                                 | 75  |

| 4. The PEDA Representation for Early Electronic Engineering  |     |

| Design                                                       | 86  |

| 4.1. Overall Structure of this Chapter                       | 86  |

| 4.2. The Plymouth Engineering Design Assistant : An Overview | 86  |

| 4.2.1. The PEDA User Interface: Overview                     | 87  |

| 4.2.2. PEDA Internal Design Representation: Overview         | 88  |

| 4.3. The Representation of Designs Within the PEDA System    |     |

| 4.3.1. The Representation of Individual Designs Within the   |     |

| PEDA System                                                  | 89  |

| 4.3.1.1. Functional Blocks                                   | 91  |

| 4.3.1.2. PEDA Block Representation                           | 93  |

| 4.3.1.3. Block Templates                                     | 96  |

| 4.3.1.4. Links to the User Interface                         | 97  |

| 4.3.2. Alternative Designs Within PEDA                       | 98  |

| 4.3.2.1. Alternative Designs                                 | 98  |

| 4.3.3. The PEDA Representation of Alternatives               | 98  |

| 4.4. The Management of Alternatives, and History Tracing     | 102 |

| 4.4.1. The Management of Alternatives in PEDA                | 102 |

| 4.4.2. History Tracing                                       | 103 |

| 4.5. Links to User Interface                                 | 105 |

| 4.6. The PEDA Constraint System                              | 105 |

| 4.6.1. Introduction                                          | 105 |

| 4.6.2. Constraint System Implementation                      | 107 |

| 4.6.2.1. What Constraints are in PEDA                        | 107 |

| 4.6.2.2. How Constraints are used in PEDA                    | 108 |

| 4.6.3. Links to the User Interface                           | 114 |

| 4.7. Simulation of Designs                                   | 114 |

| 4.7.1. The PEDA Simulator                                    | 116 |

| 4.7.2. PEDA Simulator Operation                              | 116 |

| 4.7.3. PEDA Simulator Implementation                         | 117 |

-

| 4.7.3.1. Packets                                             | 118 |

|--------------------------------------------------------------|-----|

| 4.7.3.2. Packet Movement                                     | 118 |

| 4.7.3.3. Packet Maintenance                                  | 119 |

| 4.7.3.4. Data Driven Operation of Blocks                     | 119 |

| 4.7.3.5. Data Evaluation                                     | 120 |

| 4.7.4. Links to User Interface                               | 121 |

| 4.7.5. PEDA Simulation Example                               | 121 |

| 4.7.6. Feedback and the Alternative(Alt) Block.              | 124 |

| 4.8. Integration in the PEDA Representation: An Example      | 125 |

| <b>4.9. Summary</b>                                          | 127 |

|                                                              |     |

| 5. Contributions, Final Discussion And Further Work          | 133 |

| 5.1. Overall Structure of This Chapter                       |     |

| 5.2. Contributions                                           | 133 |

| 5.3. Final Discussion                                        | 134 |

| 5.3.1. The Overall Approach to Applying Knowledge Based      |     |

| Techniques to Design Tools                                   | 134 |

| 5.3.2. The Target Domain of Knowledge Based Systems          | 136 |

| 5.3.3. The Complexity Inherent in Design Systems             | 136 |

| 5.3.4. The Target Level of Representations                   | 137 |

| 5.3.5. How Target Languages Shape Representations            | 138 |

| 5.3.6. The Use of the Separation of Concerns in              |     |

| Representations                                              | 138 |

| 5.3.7. The Similarity Between the Representation of Software |     |

| and Engineering Designs                                      | 139 |

| 5.4. Problems Encountered                                    | 139 |

| 5.4.1. The Ambiguity of Terminology (Design Process)         | 139 |

| 5.4.2. Limitations of Target Languages                       | 140 |

| 5.5. Further Work                                            | 140 |

| 5.5.1. Representation of Designs and Design Alternatives     | 141 |

| 5.5.2. Management of Designs and Design Alternatives         | 141 |

| 5.5.3. The Constraint Comparison System                      | 142 |

| 5.5.4. The Simulator                                         | 142 |

| 5.5.5. The Decision Point System              | 142 |

|-----------------------------------------------|-----|

| 5.5.6. The Detection and Correction of Errors | 143 |

| 5.5.7. Implementations in Other Languages or  |     |

| Environments                                  | 143 |

| 5.6. Concluding Remarks                       | 144 |

| A. PEDA in Use                                |     |

| C. PEDA Core Implementation Program Code      |     |

|                                               | C-1 |

**Chapter 1: Introduction**

| 1. Introduction                                    | 8  |

|----------------------------------------------------|----|

| 1.1. Overall Structure of this Chapter             | 8  |

| 1.2. Underlying Concerns, Aims and Goals           | 8  |

| 1.3. General Introduction                          | 9  |

| 1.3.1. The Field of Electronic Engineering         | 9  |

| 1.3.2. Design Activity                             | 9  |

| 1.3.3. The Need for Design Support Environments in |    |

| Electronic Engineering                             | 10 |

| 1.3.4. Design Support Environments                 | 1  |

| 1.4. Aims of the Research 1                        | 13 |

| 1.5. Thesis Outline 1                              | 13 |

## **1. Introduction**

#### 1.1. Overall Structure of this Chapter

This introduction provides an overview of the research discussed in the rest of this dissertation. The research has been concerned with the means of producing a design tool for the early stages of electronic engineering design, which would offer improved support for the designer by addressing those parts of that activity which were shown to be important as a result of related psychological work. This process has been split into two parts. The first involves the generation of an abstract representation that captures these important aspects. The second is an implementation of this representation as a software based design support environment known as the Plymouth Engineering Design Assistant (PEDA).

The chapter begins with an outline of the main themes behind the research. This is followed by a general introduction, providing background information to the subject of electronic engineering and its support. It ends with the aims of the research, and a brief outline of the form and content of the remaining chapters.

#### 1.2. Underlying Concerns, Aims and Goals

There are a number of concerns, aims and goals that have had a crucial effect on the work discussed in this dissertation. They are briefly mentioned now to give an insight to the intended overall context of the work.

The first concern was that a design support system should help the designer through a cooperative approach, and that the representation used at the core of such a tool should be explicitly designed with this in mind. The second, intended that cooperative support would be improved through a clearer knowledge of the needs of designers. And thirdly, these needs would in part be cognitive in nature and therefore would be best addressed through psychological analysis of designers in action. These concerns in turn promoted the view that satisfying these concerns would produce tools which were more useful and less complex than the results of many other approaches, by providing functionality which was tailored to the actual psychological needs of designers. The logical result of these considerations was the initialization of work on the PEDA project overall, and in this case on deriving the abstract representation and its implementation (discussed in chapters 3 and 4), based on requirements derived in part from psychological studies (Ball, 1990).

#### **<u>1.3.</u>** General Introduction

This section provides a short summary of design in electronic engineering and its progression from a purely manual, towards an increasingly automated task. This development is shown to be the result of escalating design complexity over the years, and has resulted in a large number of support tools which are simply classified into two divisions. Overall trends in this area are discussed and are followed by a lead into the basis of the PEDA project.

A more detailed discussion of the various aspects of these tools is not reviewed here. This information regarding the specific background details of requirements, representations, models and implementation particulars, has been moved to the applicable sections of chapters 2, 3 and 4 which concentrate on these aspects individually.

#### **1.3.1. The Field of Electronic Engineering**

The field of electronic engineering is a wide and diverse domain, covering many areas, from the large to the small, and affecting much of our modern lives. In an engineering sense it has traditionally been divided into two large subdomains, known as digital and analogue electronics. These have been exemplified to the public by personal computers on the digital side, and television & audio products in the analogue field. In addition this separation has been made more marked by correspondingly specialised analogue and digital design engineers.

#### 1.3.2. Design Activity

The process of design is a highly complex activity, that has largely resisted attempts to categorise it effectively. This is shown somewhat by the plethora of different approaches in existence in many domains (There are for example, quite a few software design methodologies). It can be described however reasonably well in abstract terms as: "largely a process of integrating constraints imposed by the problem, the medium, and the designer" (Mostow, 1985),

For description purposes this design activity is commonly divided into a number of stages. Unfortunately the exact description and positioning of those stages is somewhat open to debate and is often a source of confusion. However a simplistic view adequate for this text, and avoiding any exact definition of any particular design activity or process, would state that a design proceeds from specification to artifact with various hierarchical levels in between, going from abstract to reality in a logical manner. Obviously the real activity is much more complicated than this, but the above description does give the references to the early stages of design mentioned later somewhat more meaning in the overall context.

#### 1.3.3. The Need for Design Support Environments in Electronic Engineering

Design support systems have over the years been introduced to make the task of producing electronic designs easier, quicker and less error prone. In the 1980s tools were used which provided such facilities as schematic capture and logic simulation, offering assistance to design entry and validation stages of design. As designs have become more and more complex there has been a natural tendency for design tools to further aid the designer by incorporating more and more of the design process. This has been shown to be most apparent in the VLSI arena, where the improvements in lithographic techniques have made possible very complex designs involving millions of transistors. Purely manual design of such complex designs, would be very difficult and as a result design tools have been very successful in this area. Further, in the computer design industry the process seems to be accelerating, with the technology directly providing the more powerful computing platforms, which the increasingly more sophisticated design software needs to run on, and in turn the designers using the latest software to achieve reasonable design times of the next generation hardware. The net result is that there has been a rapid growth in electronic design support systems, with the newer systems covering increasingly more aspects of the design cycle, and a gradual movement towards the higher and more abstracted levels of design. The rationale behind this tactic has been the placing of design resources where their impact on design

is greatest (Bunza, Hoffman & Thompson, 1990), promoting creativity, and finding design errors early on, where the cost of correcting them is relatively low. As a result new and improved design tools have been introduced to aid the designer, as the complexity of their designs has increased. This increase in complexity and a desire to minimize the product design time has created the need for more and more sophisticated design aids.

#### 1.3.4. Design Support Environments

A very simple but useful classification of computer based design support environments splits them into two main types (Culverhouse 1988).

The first broad category comprises the conventional toolkit, which is often the combination of low level circuit design systems including schematic capture, together with a number of functional subsystems, for example logic simulation. A large number of these tools exist covering a multitude of areas, for example logical, behavioural and mathematical simulation for both the analogue and digital domains of electronic circuit design. At other levels, support may be provided for the layout of VLSI designs as well as printed circuit board manufacture. An example of this type of tool would be the early Mentor Graphics IDEA 1000 system, commercially available in the middle 1980s.

The second class of tool makes use of Artificial Intelligence based techniques (Winston, 1984, & Harmon and King, 1985) and often incorporates embedded specific expert knowledge to assist the designer in a selected area. These systems take an active role in certain parts of design activity and in those areas can greatly improve an engineer's productivity. In recent times a great deal of effort has been centred on such tools especially in the design automation arena and prototype systems such as the "Design Automation Assistant" (Kowalski and Thomas, 1985) and "VEXED" (Mitchell et. al., 1985) have been described. Good progress has been made, and is likely that these tools will eventually automate a great deal of design activity, perhaps even from the earliest specification stage downwards.

An examination of the literature has indicated that although current examples of both types of system offer much to the engineer they seemed lacking in a number of areas:

Firstly, many of the conventional toolkits tend to be passive user directed

systems, containing little embedded knowledge about the design or the designer. As a result they can do little to automate the repetitive aspects of design, or help the designer be more creative.

Secondly the expert knowledge embedded within the second class of systems tends to be very specific in its content and has dealt with particular design problems in comparatively narrow domains, and not with the more general issues applicable to a wider range of problems. Though this may be due to the difficultly of eliciting this type of abstract knowledge from designers (Evans, 1986).

Another aspect seen often in design tools, has been the tendency to focus on the later stages of design concerning with the validation of a design through simulation or timing analysis, as opposed to the earlier and higher levels of the design process (the "what if" stages). This trend has begun to change with the development of more sophisticated tools, though developments in this area have been tentative. In this respect the knowledge based workbenches tend to cover the widest range of the design process, in an albeit narrow domain, going from behavioural, functional and physical specifications for a VLSI design, to a completed chip floor plan.

In a similar vein, there has been a drift towards completely automating whole portions of the design activity, basically adopting a replacement strategy and stepping away from a cooperative approach to design in which the best aspects of both machine and operator are effectively utilized.

However the most important consideration from the point of view of this work is that the basis of these tools appears to be formed from the desired end problem, for example a CAD based verification tool would be based on the requirements of design verification. In a similar way an automated design tool covering behavioural specification to integrated circuit floor plan, would be based on the engineering requirements of these areas. A more interesting and potentially more rewarding approach towards producing a more effective design tool, would be to derive engineers needs, from a rigorous analysis of designers at work. Such a tool should be more centred towards their needs, than those whose target is a design goal. This analysis has been performed by (Ball, 1990) a co researcher on the PEDA project, and has been used to help derive a useful representation for early design and a pilot implementation in the PEDA system.

#### 1.4. Aims of the Research

As mentioned before, the main aim of the PEDA project was to produce a tool, based upon sound psychological principles and research, that offered support to the designer in the early stages of design, by attending to their cognitive as well as engineering needs. This would be done in part by paying close attention to the results of psychological work due to Ball, (1990) a co-researcher on the PEDA project, and discussed in chapter 2. High level requirements for a cooperative system, from that work would be used as the basis for the internal representation of early design within the PEDA environment. The primary goal of this research was therefore to formulate a representation that was a consistent and logical framework for representing important aspects of early engineering design within PEDA, directed by these requirements.

#### 1.5. Thesis Outline

This chapter has given an outline of the basic motivation and aims of the research, and a short introductory overview of electronic engineering design. The contents of the remaining chapters are now described briefly.

Chapter 2: This chapter discusses the psychological basis of the PEDA project, and shows how the requirements for the abstract representation in chapter 3 were obtained and justified.

Chapter 3: This chapter discusses the theoretical aspects of representing the important aspects of the above design process within a tool. It is divided into a series of sections each concerned with a particular aspect of design activity, forming a link between the requirements and how they might be achieved.

Chapter 4: This chapter examines the PEDA tool and the implementation of the abstract representation discussed in chapter 3 at its core.

Chapter 5: This chapter pools together the work described in the previous chapters and provides a summary and conclusions regarding the work. A section

is devoted to possible further work on PEDA.

The appendices contain an example of the PEDA tool in use, an overview of the various tools and programming languages used in the realization of the PEDA system, and the program code relevant to the main text.

#### References for Chapter 1

Ball, L., "Cognitive Processes in Engineering Design," PhD Thesis, Department of Psychology, Polytechnic South West, Devon, UK, 1990.

Bunza, G., Hofman, G.and Thompson, E., "Design automation goes concurrent in the 1990s," Electronic Product Design, April 1990.

Culverhouse, P., "Design Tools for Engineers," Polytechnic South West NAB group internal report, 1986.

Evans, J. St. B. T., "Knowledge Elicitation in the Training and Assessment of High Level Cognitive Skills," Report Prepared for the Army Personnel Research Establishment, 1986.

Harmon, P. and King, D., "Expert Systems," John Wiley & Sons, 1985.

Kowalski, T. J. and Thomas D. J., "The VLSI Design Automation Assistant: What's in a Knowledge Base," <u>Proceedings of the 22nd ACM/IEEE Design Automation</u> <u>Conference</u>, 1985.

Mitchell, T., Steinberg, Louis, I., and Shulman, J. S., "A Knowledge-Based Approach to Design," <u>IEEE Transactions on Pattern Analysis and Machine Intelligence</u>, vol. 7, no. 5, 1985.

Mostow, J., "Towards Better Models of the Design Process," <u>The AI magazine</u>, pp.44-57, 1985.

Winston, P. H., "Artificial Intelligence 2nd Ed," Addison-Wesley, 1984.

Chapter 2: Requirements for Early Electronic Engineering Design: The Psychological Basis of the PEDA Project

| 2. Requirements for Early Electronic Engineering Design: The       |    |

|--------------------------------------------------------------------|----|

| Psychological Basis of the PEDA project.                           | 18 |

| 2.1. Overall Structure of this Chapter                             | 18 |

| 2.2. Justification for Psychological Basis of the PEDA project.    | 18 |

| 2.3. Results of the Related Psychological research                 | 19 |

| 2.4. Requirements for a Design Support System                      | 28 |

| 2.5. Other Relevant Work                                           | 29 |

| 2.6. Relevance To Design Support Systems in Electronic Engineering |    |

|                                                                    | 31 |

# 2. Requirements for Early Electronic Engineering Design: The Psychological Basis of the PEDA project.

#### 2.1. Overall Structure of this Chapter

The aim of this chapter is to show how the set of requirements for the representation discussed in chapter 3 were obtained. The main emphasis of the discussion is on the justification for the psychological basis of the PEDA project, and some of the results of the work conducted by Ball (1990), the psychological researcher on that project, which are directly relevant to the work on the representation of early electronic engineering design discussed in chapter 3. The psychological work involving studies on the cognitive processes involved in engineering design, is outlined and then a link is formed to the work on realizing design support and the early design abstract representation discussed here in later chapters. Only those areas that are thought to be directly relevant to this dissertation are examined, as a complete account is given in Ball's thesis (Ball 1990). These areas cover a discussion on the cognitive needs of engineers and a set of requirements for a cooperative system that would begin to address them.

The chapter ends with a discussion of other work in the literature which has been found to be applicable, and the overall relevance of the final requirements towards systems which purport to assist the early stages of electronic engineering design.

#### 2.2. Justification for Psychological Basis of the PEDA project.

The PEDA system was initially conceived as a cooperative engineering design support tool that would offer assistance to the engineer designer during the early stages of design. A brief survey by Culverhouse, (1986) had indicated that contemporary design tools offered little assistance to these earlier stages, involving the testing of ideas, comparison and selection of alternatives. Very little was known by the research group on the PEDA project on exactly how such assistance should be afforded. Unfortunately it appeared that the design of computer aided support systems was traditionally an introspective and intuitive method done by the tool creators, who were often the domain experts, ie a "designed by engineers for engineers" philosophy. This

was not viewed satisfactory, as a sound and solid basis was required on which to base the development of the tool. Without this basis the tool might hinder the designer by not taking into account some important and unthought of aspect of design activity. It was logical to reason that this would be best achieved by first understanding the way in which engineers design, a task which lends itself to psychological study. In the literature there appeared to be very little prior work on the underlying processes of design in the field of electronic engineering, but there has been some research on software design processes (eg. Jeffries et al, 1981), though the majority of human factors research has been concerned with the Human Machine Interaction aspects of computers (eg Myers, 1986 or Hutchins, 1985). As a consequence the research by Ball into the cognitive processes involved in engineering design was instigated. One especially exciting aspect of this work, was that a study of engineers solving real world problems, might provide valuable information regarding the engineering design process, and indicate the particular strengths and weaknesses in their designing. This information could then be used in the formation of a design tool, which would be targetted at these cognitive needs, providing the correct type of support that engineers need. This type of support would have the added benefit of being comparatively general in scope, covering a wider range of end problems, than systems whose intelligence was aimed at one or two narrow domains.

#### 2.3. Results of the Related Psychological research

The related research produced a number of findings about the way in which engineers design which have important implications for design tools that address the early stages of design.

The first finding deals with the way in which the engineers initially addressed their designs. Ball found that the engineers tended to adopt a problem reduction strategy in the development of their work. Initially this would involve splitting the main problem into a set of smaller, more manageable subproblems that could be dealt with separately and with the minimum of cross interaction. Each subproblem would then be focused upon in turn, and in the case of the less experienced designers, developed in an essentially depth first manner, completing each subproblem before moving on to the next. The more experienced engineers would tend to adopt a more breadth first

approach to solving the design problems, and would only complete a subproblem to a particular level, before moving on to the next one. Only when all subproblems had been addressed in this way, did these engineers move down to the next level, splitting up the design as mentioned above.

In this aspect the results of the psychological research are in agreement with, the majority of computer based engineering tool approaches. There are a multitude of commercial CAD based tools available, that cater for the hierarchical decomposition of designs into functional modules, aligning very well with the problem reducing strategies adopted. However there is little evidence for the use of a sound psychological basis in the development of such tools, except in software engineering (Jeffries et al 1981), and the similarity between results appears to be due to a fortuitous agreement between intuitive techniques and the psychological work.

The apparent differences between experienced and novice designers, has in the instance of software development tools, been responsible for the appearance of tools which enforce a particular stratagem on the user, one that would hopefully improve the performance of novices, by adopting an idealized approach, for instance the use of breadth first, top down strategies (Jeffries et al 1981). A problem with this type of tactic is that such techniques may hinder rather than aid the designer, in that there may be additional aspects of the design activity, hidden to casual analysis, that are not faced by the particular approach chosen. The psychological findings suggest that a design assistant should encourage, but not enforce a particular design strategy. This tactic is supported by the tentative observation that even expert designers do not always adopt a rigid regime and may for example expand parts of a design in at least partially depth first manner. In fact this overall theme appears throughout the findings, indicating that the design process is governed by trends. It therefore seems unlikely that user centred design support will be effectively achieved through the use of rigid methodologies, when the underlying activities are at present seen to be so changeable.

The second important finding was primarily concerned with the way in which designers pursue alternatives. Ball found that the electronic engineers studied spent very little of their design time in a search for different solutions to the problems, but instead concentrated on one high level solution. This was found to be true over widely differing levels of expertise, from expert to novice and so appeared to indicate a general aspect of the subjects studied. He attributed the result to the use of a "satisficing" principle by

the designers, in which possible solutions are accepted on the grounds that they are good enough or "satisfactory", instead of using a more rigorous or exhaustive search for the "best" design.

This trend is in stark contrast to our preconceived views as engineers of the way in which we design. Good design practice dictates, that designers initially examine a number of alternative ideas, before selecting a few to pursue further. Ball does admit that the engineers studied may have been performing some form of rapid and hidden comparison, or that the time constraints imposed on the designers during his studies may have influenced their design activities, away from the common engineering conception of an idealized route. This is countered by the observation that if extensive comparisons were being made, then it would be expected that this would be expressed in their verbal or "think aloud" protocols and little evidence was found for this in the early and more abstract stages of design. In the later stages of their design activity however, he did observe a trend by the more expert engineers to produce slightly improved versions upon the main design theme, though this activity was comparatively minor to that expected. (Note: Verbal protocols are a successful psychological tool used to gain access to the thoughts of subjects, by making them verbalize their thoughts whilst solving the problem.)

Ball suggests that designers may suffer from a form of cognitive overload affecting their searching strategies at the higher levels of design where changes have far reaching consequences, but cope quite well at the lower levels, with small changes or "tweaking", where the effects of change are generally far more manageable to the unaided designer. For example: a decision to use an analogue, digital or mixed technologies approach in the initial stages of design will affect all aspects of the design from then on, whilst a small change involving a gain control resistor in the final design will have comparatively little effect on the rest of the design.

The effects of time and other environmental constraints are harder to account for, although a number of different studies made by Ball (1990) with quite different environments produced similar results. The first study involved the use of undergraduate electronic engineering students making a current design log of their final year project, together with video and sound recordings of their activity reports. A second set of studies involved video and sound protocol studies of electronic engineers solving a particular set design problem, and employed a time pressing environment, as this was

the only way of reasonably collecting the verbal protocols during design. Unfortunately if the study had taken place over the normal time scales of a product, then the resulting data would have taken many man years to collate and analyze. Ball suggests that the results are still applicable though, as a time pressured environment is probably more indicative of real life design problems on projects that are working to deadlines, and incidentally where a design support tool would be used to most effect.

He follows on and states that the issue of the pursuing of alternatives is further clouded, by the problems involved in determining the relative optimality of a design, and it is quite possible, that some of the engineers could have produced the "best" design, from their "satisficing" approaches. Unfortunately whilst designs can be judged on "satisficing" grounds in that they do or do not meet the design criteria, the determination of the "best" design is somewhat subjective and based to some degree on the expert designers opinions, with the attendant biases which that might entail. Fortunately these problems were somewhat avoided, by the observation in this case, that the majority of solutions provided in the second study were quite different, and so although one design could be the most optimal, it is unlikely that all the others were as well. This suggests that the methods employed by the engineers were not geared to producing the "best" design, but rather a satisfactory one.

From a design standpoint, the lack of explicit alternative solution generation may be very important, considering the very high demands set on designers today, although it must be added that the "satisficing" approach may be the reason why designers can produce effective and reliable designs within a reasonable time scale, considering the complexity of even small problems. Ball indicates that some of probable causes of the "satisficing" tactic might be the cognitive limitations associated with the finite size of human working memory, in that we tend to have problems keeping track of a great deal of information at once, and it seems reasonable that the "satisficing" route might reduce the number of variables that the designer had to consider at any one time to a manageable level. This can be taken as a very good case for some form of computerized assistance regarding the management of alternatives, as a means of overcoming these working memory limitations. In addition the fact that engineers already possess some form of rudimentary selection system, indicates that a system that superintends this activity, by perhaps making it more explicit and accessible, may improve the performance in this important area. It can also be seen that some form of

automated comparison scheme is desirable to help compare different solutions in an unbiased and consistent manner.

The selection of alternatives is an area that contemporary design support tools do not seem to address, and whilst there are many schemes for the representing of alternative solutions or versions (Chou & Kim, 1986), (Gabbe & Subrahmanyam, 1987) and (Katz, Anwarrudin & Chang, 1986), there appears to be little effort centred on the selection of alternatives within the framework of electronic engineering based design tools. Constraint based systems exist (Chan & Paulson, 1987), but the emphasis tends to be towards design and not comparison processes. This may again be due to the way in which tool requirements have been traditionally gathered, by the use of such techniques as retrospective and intuitive analysis of the problem domain or questioning of target users. Ball draws attention to research that indicates that such methods may give unreliable results and suggests that systematic psychological techniques (eg. protocol analysis) are more scientific (Nisbett & Wilson, 1977 and Evans 1986).

Another outcome of the studies is the suggestion by Ball that there is some evidence to support the view that the subject engineers were creating and then using mental models (Johnson-Laird, 1983), to simulate the behaviour of different aspects of the designs as they evolved. For example, what would happen at the outputs if a certain set of inputs were applied to a design? Interestingly, the same type of modelling could be potentially used to evaluate the usefulness of alternative designs for a particular problem. Ball suggests a tentative theoretical model for the processes in engineering design that involves the use of a generalized high level "design schema", an entity which contains knowledge which is applicable to a wide range of similar problems. The "design schema" controls the partitioning and decomposition of the problem into subproblems, together with the use and evaluation of possible solutions at each level, and is in effect the coordinator of the designing activity. He then proposes that the basis of the "design schema" is in fact the problem reduction strategy mentioned earlier. If this is superintended with the means of efficiently providing domain specific technical knowledge, then the core of a fairly sophisticated entity, that can be used to provide reasonably expert solutions to a wide range of design problems, is produced.

This model may have some important ramifications for the generation of design aids. Firstly, if it were possible to implement the model within an aid, it could then be used to provide the basis of the assistance. It's internal state would be indicative of the

user's state and therefore could be used to provide contextually based assistance relevant to the user's need at the time. This model could also be used as part of a training system that "taught" novice engineers how to design more effectively, by comparing their design activity to its internal representation, and offering advice on what they should be doing next or possibly intervening in some subtle, but calculated manner, with the aim of altering their "design schema".

Secondly, if the user were substituted for the problem reduction strategy aspect of the model, then reasonably expert solutions could be produced, by correctly linking the required domain specific knowledge to the user, in effect producing a cooperative system where the best aspects of both machine and operator are effectively utilized. This is a desirable approach as most designers are quite capable of applying such a strategy, whereas it would be difficult and unnecessary to encode efficiently in an automated form at present. As a result engineers might be able to produce more optimal designs in an area away from their specialities. In addition the availability of a general purpose model applicable to other design situations, involving different problem domains should theoretically speed the development of design assistants in those areas, or more ideally, allow the creation of a general purpose design assistant.

A fourth major outcome of the psychological research relevant to the generation of a computer based model of design, is related to the inconsistencies, omissions and errors made by the engineers in their design activities. Errors can occur when the designer is trying to form some understanding of the problem.

An example of this may be seen where some of the engineers studied inadvertently created new incorrect relationships between mathematical parameters. Normally trigonometric functions like sine are associated with angles, but in this problem this was not the case. Unfortunately the designer was given other cues that tended to reinforce the angle association, and one of these involved the use of the irrational number pi in the equation definition for the variable that would be used in the sine function. The error that occurred, happened when the designer was deriving some other equations that involved the use of other trigonometric functions which did involve angles. An erroneous substitution was then made using one these angles in the given equation.

For example:

A possible explanation for this was that the engineer had failed to build up a complete representation of the equations. This was supported by the fact the engineers involved who displayed this tendency, spent the least time in initially understanding the requirements of the design problem, and also spent the least time referring back to the specifications as the design progressed.

Errors also occurred subsequent to this representational or encoding phase, when applying design knowledge to generate, combine or even evaluate possible solutions. One example involved a designer who was performing an expansion of a partial solution, and failed to include parts of the original partial solution in the expanded version. Additionally inconsistency problems arose, with mathematical notation in a number of design solutions, where the same variable name was used in two equations at different points in the design work. This caused problems later when the wrong equation was substituted in another equation.

For example:

```

Now initially:

theta = arcsine(l/a)

a angle usually called theta

is the inverse sine of the

Opposite divided by the hypotenuse and later:

theta = arccosine(j/l)

another angle,

which will be called theta as well

And finally:

a = tan (theta)

Now substitute for the wrong theta,

therefore:

a = tan (arccosine (j/l)),

instead of:

a = tan (arcsine (l/a))

```

Ball attributes these types of errors to a number of causes: working memory limitations are blamed, when the designer is concentrating on several items of information, and errors occur, for example the equations; and a lack of vividness of the problem information may have caused the problems regarding incomplete formation of an internal representation of the specification.

This is an aspect of design which apparently has yet to be tackled to any great extent by design support environments. This may be due to the fact that most design tools tend to address the later stages of design, where any equations have already been formulated and checked for correctness. Simple mistakes, dependent on where they happen in the design, may cause problems when discovered, causing delays due to redesigns and may even invalidate the whole design solution, a result which would not be acceptable in the fiercely competitive design market of today. Additionally there are problems to do with the safety of critical systems, that occur when an ok, but mathematically incorrect design, is a key element in a complex system, for example an aircraft control system, where the reliability of such systems is an very important issue. It seems, therefore, that there is a great need for some form of assistance to address this type of cognitive problem, especially in the earlier stages of design, where mathematical manipulation and equation generation is generally carried out. The benefits would hopefully involve reduced design time and greater throughput, due to the elimination of simple mistakes early on in the design history.

In conclusion, the psychological research, although tentative, has produced a set of findings regarding the design strategies and cognitive limitations of designers which were generalisable over very different tasks, time scales and skill of the designers. This work is in general agreement with recent research in mechanical engineering by Ullman, Dietterich and Stauffer, (1988), who have produced a similar set of findings regarding the activities of mechanical engineering designers. These encouraging results have enabled Ball to produce a set of very general requirements for a design support system that would be targetted at the cognitive needs of designers. The requirements, shown overleaf, are quite general, but provide valuable pointers to the creation of such a system.

#### 2.4. Requirements for a Design Support System

The five general requirements are itemized below, together with an individual description relating their relevance to design support.

A design support system should:

(1) "Encourage the designer to consider an increased number of initial highlevel solution concepts and enable the efficient formulation of alternative versions of each solution concept through levels of increasing design detail."

(2) "Assist with the choice of competing design solutions, for example, enabling evaluations of solutions to be made on the basis of comparative functional simulations."

(3) "Superintend the designer's exploratory activity, for example, helping the designer to backtrack if a path proves unpromising (i.e. by providing a record of paths taken together with the current point of exploration) or suggesting worthwhile paths of investigation (i.e. by suggesting design alternatives)."

(4) "Ensure the designer's awareness of design conflicts (e.g. if crucially important constraint requirements have been overlooked when the designer is focusing on a narrow aspect of the overall design solution)."

(5) "Ensure the designer's awareness of inconsistencies in the notation that is being used (e.g. if two different design parameters have been given the same symbolic label)."

The requirement (1) arose from the observation mentioned in the previous section, that designers tend to use a "satisficing" principle in which they focussed their

efforts on a single satisfactory high level solution path. It was therefore thought that encouraging a more explicit approach, in which options are more thoroughly investigated, could lead to improved design performance.

Requirement (2) arose from the same observations as (1), but the emphasis is on making the selection between alternatives easier, by allowing the user to apply a set of selection criteria to a whole set of alternatives. This activity would be a difficult and error prone process if done by the user unaided, and whilst it would be wrong to say that, making such a scheme available, will make the user pursue alternatives to a greater extent, it can however, make the proposition more attractive by reducing the cognitive burden in this area. In addition the problem of implicit biases affecting the choice of alternatives is somewhat alleviated with the introduction of an explicit checking scheme. The designer can now be made aware of which constraints are being applied. Similarly less time should be wasted on pursuing "dead end" designs, by making sure that all the relevant constraints are applied in a consistent manner to the selected alternatives, at an early stage of the design activity.

Requirement (3) is also designed to help with the pursuing of alternatives, by reducing the amount of information that the designer has to keep in working memory. The information held would hopefully allow the designer to retrace his or her steps, up from an unsatisfactory solution, regaining the information that was valid previously, before the unsatisfactory alternative was examined.

Both requirements (4) and (5) are associated with the mistakes that designers can make during their designs. A designer can loose consistency with various parts of a design, when concentrating upon a particular aspect, and so needs to be alerted to the fact. The designer also needs to be alerted to inconsistencies in the notation of the solution, be it mathematical or otherwise.

#### 2.5. Other Relevant Work

The aim of this section is to outline other work which has significantly influenced the selection of the requirements stated earlier, as being suitable for the formation of the abstract representation and implementation discussed in chapters 3 and 4.

Most design systems are built to satisfy a set of explicitly or implicitly specified

requirements and so the number of potentially influential sources is quite high. However there are comparatively few which are applicable to cooperative early engineering design.

In the area of Co-operative interface management M. Smyth, (1988) outlines a set of requirements for a cooperative system, which are quite similar to Ball's in electronic engineering:

(1) Increase the number of initial design solutions.

(2) Reduce the time and cost of the design process.

- (3) Increase the number of design iterations where necessary.

- (4) Increase the designers awareness of potential design conflicts in the proposed solution.

- (5) Move the solution range closer to the theoretical optimal solution.

A similar view is taken in the Mechanical domain by Ullman et. al. (1988) who makes a number of recommendations to improve CAD systems:

The first is that we should raise the abstraction level at which computer based tools can provide external memory aids for the designer.

Secondly, tools might also be extended by providing some means of constraint management assistance.

Thirdly, there is a general need for CAD to support the human designer's cognitive limitations.

A very useful and often cited paper by Mostow (1985) suggests the areas that a comprehensive model of design should address. In short these are:

1) The State of the design.

2) The goal structure of the design process.

- 3) Design Decisions.

- 4) Rationales for design decisions.

- 5) Control of the design process.

- 6) The role of learning in design.

It can be seen that there is a degree of commonality between the sets of requirements. Both Ball and Smyth are in broad agreement, and Ullman makes overall suggestions that the other two detail. The last set of suggestions due to Mostow, appear to differ, but in fact are pitched at a different level, being concerned more with the structure of the internal model than the tool. The overall concern of all these approaches has been to produce better systems by taking into account more of the human design process than just the state of design.

#### 2.6. Relevance To Design Support Systems in Electronic Engineering

Very little psychological work has previously been carried out on design in electronic engineering, and it appears that introspective and intuitive techniques have been used to formulate the specifications for many design tools in this area. Unfortunately, psychological evidence has indicated that these techniques can be ineffective (Nisbett & Wilson, 1977 and Evans 1986), and so there has arisen a real need to determine accurately the needs of designers. The research done by Ball has been successful so far in that it has produced a set of requirements, that should address some of these needs. Some aspects of design activity have also been addressed by contemporary tools. These aspects will be covered in the next chapter where the requirements are linked to the derivation of an abstract representation for the early stages of electronic engineering design, but in brief they can be roughly divided into two areas. Firstly, non intelligent tools which tend to be reasonably general, but normally support the later stages of design, for example from circuit design solution to printed circuit board manufacture. Secondly, intelligent tools based on expert system approaches, which cover more of the design activity, but tend towards tackling a specific design problem domain, such as a digital filter, VLSI chip or mechanical linkage design, for example The VLSI Design Automation Assistant by Kowalski et al ,1985, in which the intelligence is aimed at the automatic decomposition of functional and behavioural specifications in VLSI designs. One result of this directed effort, is that the intelligence has been aimed at the target problem, instead of the cognitive problems of the designer. It was with this in mind that the PEDA system was conceived, and by basing its design on sound psychological research on the cognitive processes in design, it was hoped that it would be more able to address the general needs of designers, rather than specific problem domains.

#### **References for Chapter 2**

Ball, L., "Cognitive Processes in Engineering Design," PhD Thesis, Department of Psychology, Polytechnic South West, Devon, UK, 1990.

Chan, W. T. And Paulson Jr, B. C., "Exploratory Design Using Constraints," AI EDAM, pp 59-71, 1987.

Chou, H. and Kim, W., "A Unifying Framework for Version Control in a CAD Environment," <u>Proceedings of the Twelfth International Conference on Very large</u> <u>Databases</u>, pp. 336-344, 1986.

Culverhouse, P., "Design Tools for Engineers," Polytechnic South West NAB group internal report, 1986.

Evans, J. St. B. T., "Knowledge Elicitation in the Training and Assessment of High Level Cognitive Skills," Report Prepared for the Army Personnel Research Establishment, 1986.

Gabbe, J. D. and Subrahmanyam, P. A., "An Object-Based Representation for the Evolution of VLSI Designs," <u>Artificial Intelligence in Engineering</u>, vol. 2, no. 4, 1987.

Hutchings, E. L., Hollan, J. D. & Norman, D. A., "Direct Manipulation Interfaces," <u>Human Computer Interaction</u>, Vol. 1, pp. 311-338, 1985

Johnson-Laird, P. N., "Mental Models," Cambridge: Cambridge University Press, 1983.

Jeffries, R., Turner, A. A, Polson P. G., and Atwood, M. G., "The Processes Involved in Designing Software," <u>in Cognitive Skills and their acquisition</u>, ed J. R. Anderson, Hillsdale, NJ.: Lawrence Erlbaum associates.

Katz, R. H., Anwarrudin, M., Chang, E., "A Version server for Computer-Aided Design

Data," Proceedings of the 23rd ACM/IEEE Design Automation Conference, 1986.

Mostow, J., "Towards Better Models of the Design Process," <u>The AI magazine</u>, pp.44-57, 1985.

Myers, B. A., "Visual Programming, Programming by Example, and Program Visualisation: A Taxonomy," Proceedings of ACM/SIGCHI, pp.59-66, 1986.

Nisbett, R. E., & Wilson, T. D. "Telling more than we can know: Verbal reports on mental processes," <u>Psychological Review</u>, Vol. 84, pp. 231-295, 1977.

Smyth, M., "Articulating the Designer's Mental Codes," LUTCHI Research Centre internal paper (draft) ref: HCC/L/24, 11th May 1988.

Ullman, D. G., Dietterich, T. G., and Stauffer, L. A., "A Model of the Mechanical design process Based on Empirical Data," <u>AI EDAM</u>, vol. 2, no. 1, pp. 33-52, 1988.

Chapter 3: An Idealised Representation for the Early Stages of Electronic Engineering

| 3. | An Idealised Representation for the Early Stages of                  |    |

|----|----------------------------------------------------------------------|----|

|    | Electronic Engineering Design                                        | 38 |

|    | 3.1. Overall Structure of this Chapter                               | 38 |

|    | 3.2. Rationale for a New Representation                              | 38 |

|    | 3.2.1. An Examination of Requirements                                | 39 |

|    | 3.2.1.1. The First Requirement:                                      | 39 |

|    | 3.2.1.2. The Second Requirement:                                     | 41 |

|    | 3.2.1.3. The Third Requirement:                                      | 45 |

|    | 3.2.1.4. The Fourth Requirement:                                     | 48 |

|    | 3.2.1.5. The Fifth Requirement:                                      | 49 |

|    | 3.2.2. Representational Issues Common to all the                     |    |

|    | Requirements                                                         | 50 |

|    | 3.2.2.1. Explicit and Implicit Models of the User.                   | 50 |

|    | 3.2.2.2. Providing Functionality                                     | 51 |

|    | 3.2.2.3. The Level of Representation                                 | 51 |

|    | 3.2.2.4. Efficiency and Implementation Concerns                      | 52 |

|    | 3.2.3. The Case for a New Representation                             | 52 |

|    | 3.3. An Idealised Representation for the Early Stages of Engineering |    |

|    | Design                                                               | 54 |

|    | 3.3.1. Block Diagram and Alternative Design                          |    |

|    | Representation                                                       | 55 |

|    | 3.3.2. Block Diagram and Alternative Management                      | 58 |

|    | 3.3.3. Constraint Comparison System                                  | 59 |

|    | 3.3.4. The Equation Based Simulator                                  | 60 |

|    | 3.3.5. Decision Point System                                         | 63 |

|    | 3.3.6. Error Detection                                               | 63 |

|    | 3.4. Comparison with Existing Systems or Methods                     | 65 |

|    | 3.4.1. Representing Each Design and Design Alternatives              | 65 |

|    | 3.4.2. Constraints and Constraint Comparison                         | 68 |

|    | 3.4.3. Simulation                                                    | 69 |

|    | 3.4.4. History and Decision Record                                   | 70 |

|    | 3.4.5. Errors and Inconsistencies                                    | 71 |

|    | 3.4.6. Comparison with Combined Approaches                           | 71 |

| 3.4.6.1. "A Conceptual Framework for ASIC Design   |    |

|----------------------------------------------------|----|

| (Leung, Lisher and Shanblatt, 1988)                | 71 |

| 3.4.6.2. "An object based representation for the   |    |

| evolution of VLSI designs" (Gabbe and              |    |

| Subrahmanyam, 1987)                                | 73 |

| 3.4.6.3. Walker and Thomas: the System Architect's |    |

| Workbench.                                         | 74 |

| 3.4.6.4. Knapp and Parker Advanced Design          |    |

| AutoMation project (ADAM)                          | 75 |

| 3.5. Summary                                       | 75 |

# 3. An Idealised Representation for the Early Stages of Electronic Engineering Design

# 3.1. Overall Structure of this Chapter

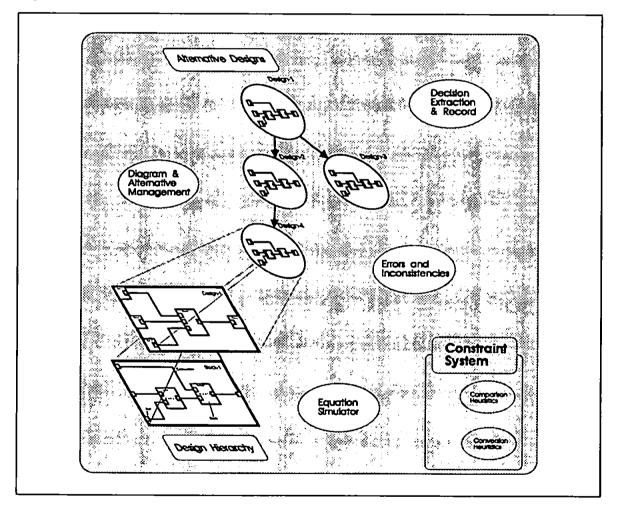

The aim of this chapter is to present an idealised abstracted representation for the early stages of electronic engineering design, that has been devised during the development of the Plymouth Engineer's Design Assistant (PEDA), a tool designed to aid and complement the designer in the early formative stages of design activity. The chapter begins with the rationale and arguments for the creation of the representation, and then leads on to a full description. The various parts of the representation are outlined and developed into a characteristically simple structure of alternative designs and constraining information. A critique then follows, comparing the high level idealised representation with other methods, models, approaches and environments in electronic engineering and related domains. The chapter concludes with an outline of the salient aspects of the representation in preparation for the next chapter, which describes a partial implementation as the core within the PEDA environment.

#### 3.2. Rationale for a New Representation

The objective of this section is to provide the rationale and arguments for the creation of a new representation for the early stages of electronic engineering design, discussed in section 3.3.

This is done primarily through an examination of the psychologically derived requirements in chapter 2. These requirements are individually scrutinised generating a number of issues that need to be addressed if the requirements are to be dealt with adequately. Methods of achieving these aims are discussed, and where they exist examples from the electronic engineering design domain are taken and are shown to be generally unsuitable. Overall representational issues that affect the choice of a representation in this area of the domain are also outlined. All these points are then combined with the arguments behind the PEDA project, to state the claim for a new representation in section 3.2.3.

#### 3.2.1. An Examination of Requirements

Each requirement from chapter 2 can now be examined in turn, to see how they can be met, and to indicate the unsuitability of some common solutions in the literature.

#### 3.2.1.1. The First Requirement:

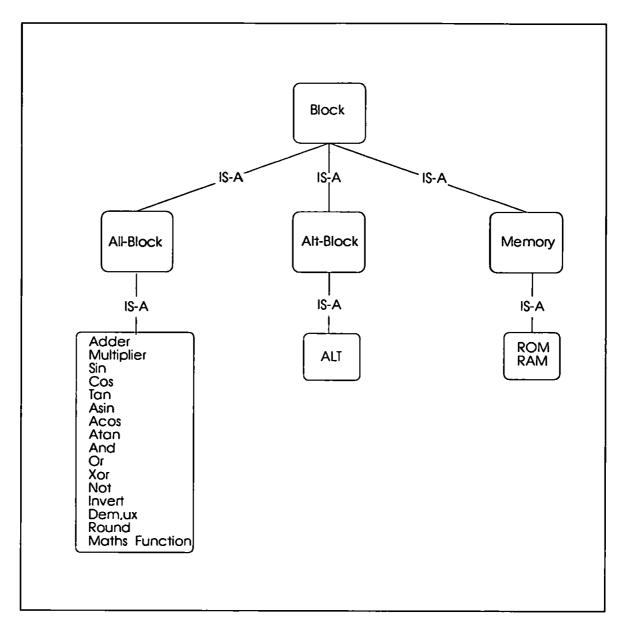

The first general requirement for a design tool, taken from chapter 2, is as follows:

"Encourage the designer to consider an increased number of initial high-level solution concepts and enable the efficient formulation of alternative versions of each solution concept through levels of increasing design detail."

There are a number of issues that need to be addressed here before the above requirement can be realized. The first and most basic one is that a representation for a design needs to be found. Initially this may seem a comparatively easy operation as it is not specified within the requirements and as a result there is considerable freedom on how it may be realised. The literature abounds with design representations and so there should be little difficulty in selecting a suitable candidate. Unfortunately it is in this area that a number of problems arise, which stem from the basic conceptual emphasis of trying to meet these requirements in a simple but elegant manner. Ideally a representation of design is needed which is uniform in its structure. This is not only desirable from a aesthetic point of view, but more importantly is in line with the results of the psychological studies (Ball, 1990) in which designers tended not to separate the domains of description (unlike the proposals by Stefic et al, 1981), but merged them in the early stages of electronic engineering design. Sadly this reduces significantly the number of candidate representations from the design automation arena. Another meaningful problem was that representations are generally discussed in either low level terms, using a language such as LISP (for example Davis & Shrobe, 1983), or in very abstract terms (for example Sinclair et al, 1989), and cause problems regarding the level of design detail. This is an important issue covering the whole of the representation and is discussed briefly in section 3.2.4 and in section 3.4 when comparing the representation with other approaches.

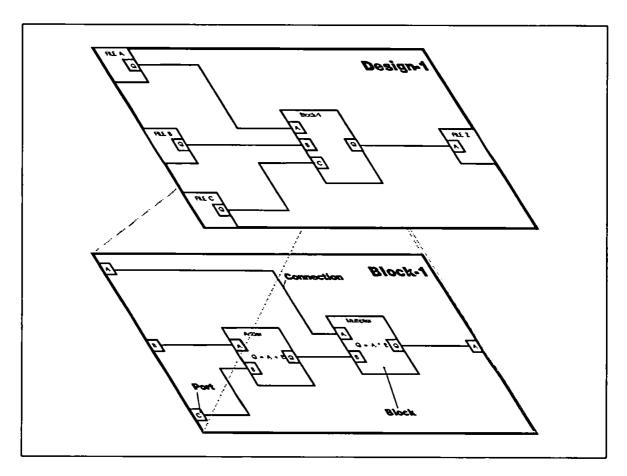

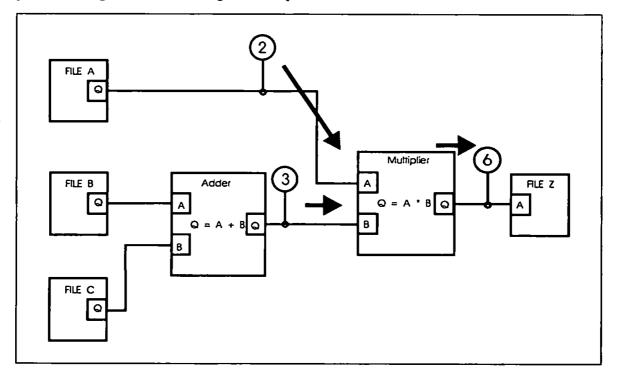

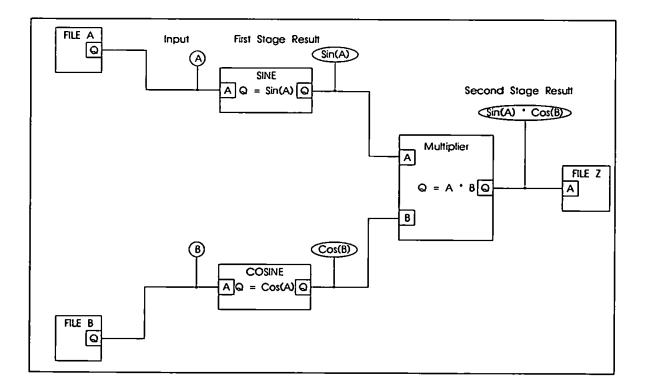

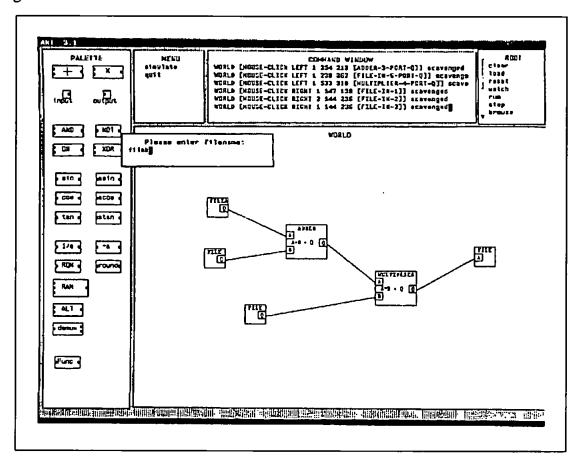

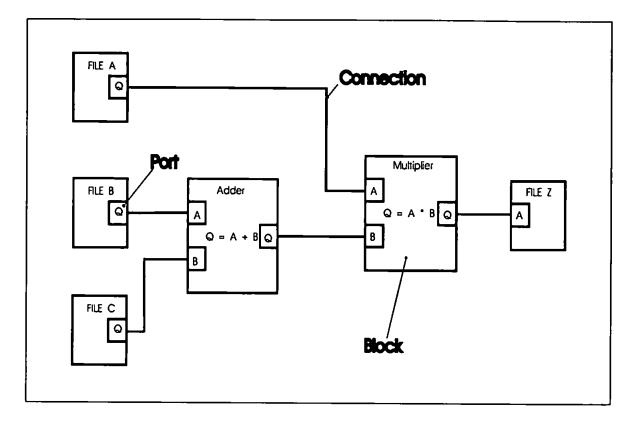

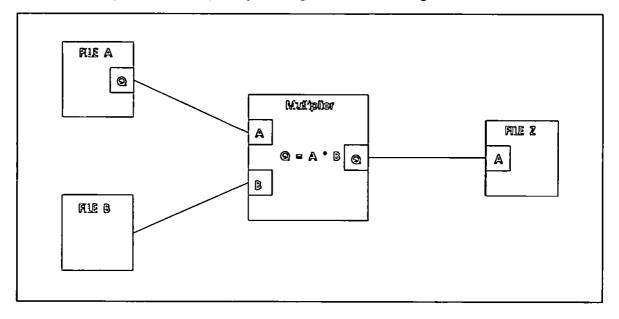

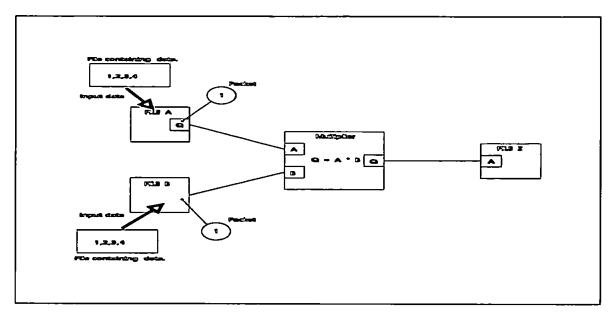

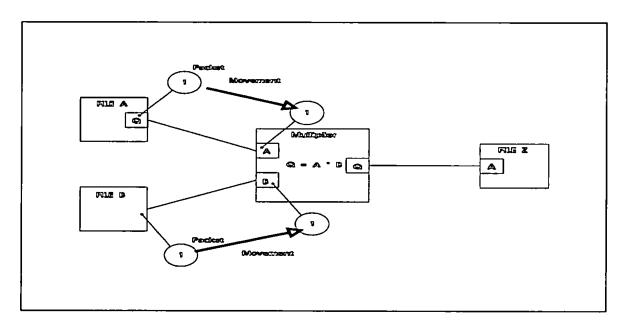

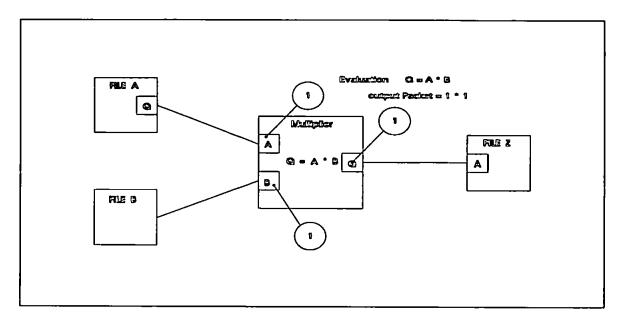

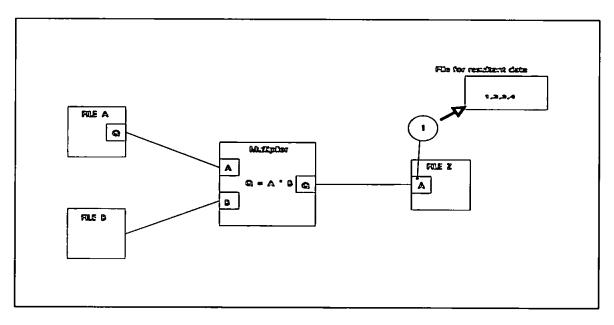

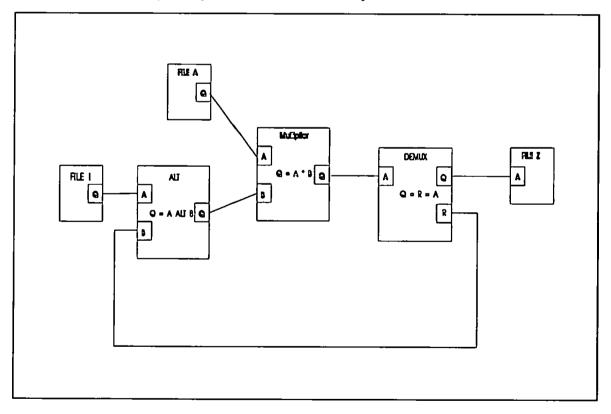

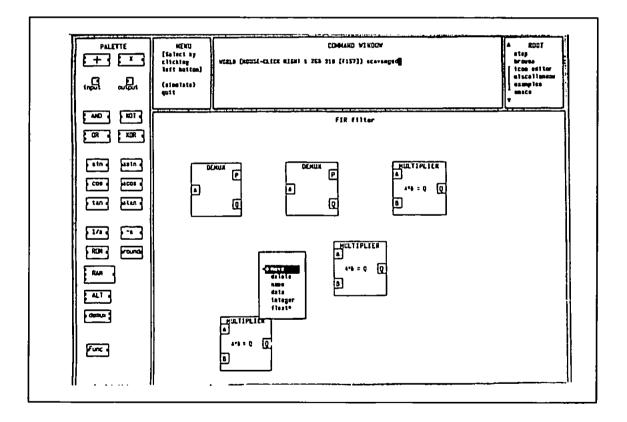

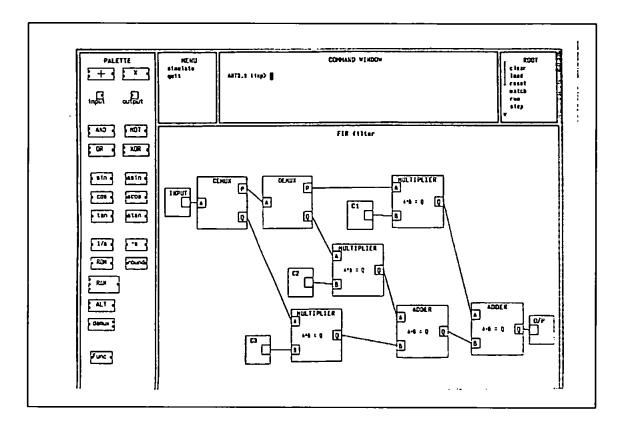

In essence, what is actually required, is a simple representation for the design that captures the important aspects of the design in the early stages. A hierarchical structure is desirable as this neatly captures the normal design representation by designers in their work (Ball, 1990). One credible solution would involve the structure being made up from a collection of blocks that would together form a block diagram, very similar to the visual representation on paper. These blocks would be connected in the horizontal plane by connections allowing the desired mathematical functionality to be built up and along which information or data would be seen pass by the user during simulation. The blocks themselves would contain all the information, necessary to describe what they are, and their relationships to other blocks including information would be relevant to the requirements of the design.

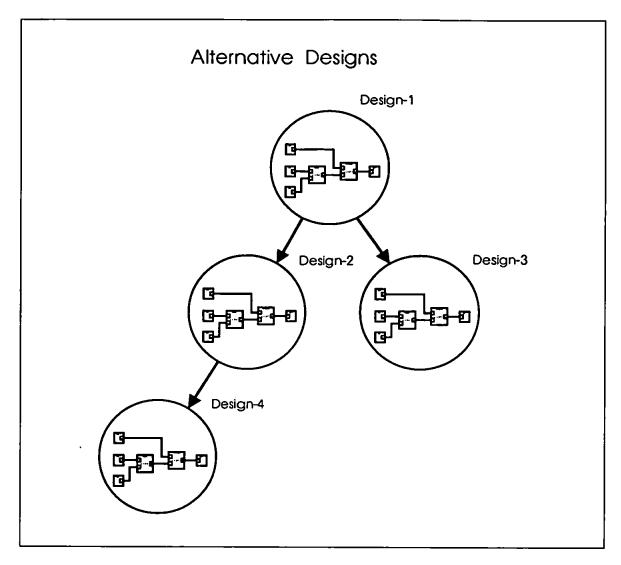

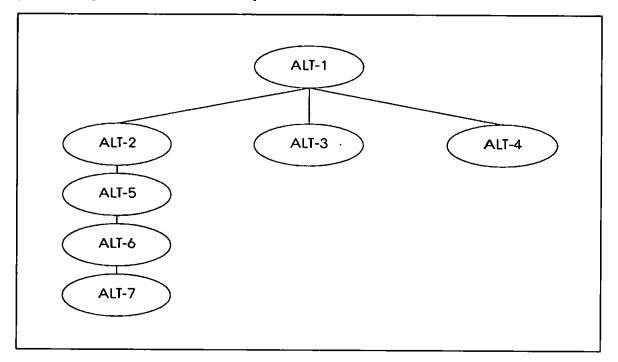

The second important issue raised by the first requirement deals with the representation of design alternatives. Again this appears to be a greatly addressed area, but unfortunately the effort tends to concentrate on aspects such as "version serving". As a result the facilities offered by these approaches are not particularly relevant to the needs of the designer regarding alternatives in the early stages of design. For example approaches may offer means of keeping track of the most up to date parts of design in different representations between the members of a design group (Katz et al, 1986 and Gabbe & Subrahmanyam, 1987), but do not aid the designer in exploring new designs. In addition the overall trend with these approaches is to rigidly support the separation of domains theme and so it would be difficult to reconcile them with the representation of designs mentioned earlier.

Actually alternatives can be addressed in a very simple manner by treating different alternatives as separate block diagrams. Additional information can then be added to describe the relationship between diagrams in the same way as between different blocks. This method of treating blocks, block diagrams and alternatives in a homogeneous manner is very attractive as it allows mechanisms developed for one aspect of the representation to be used on the others. This will be seen to be extremely useful when constraints are discussed later. Also having only one scheme greatly simplifies the representation, because then there is no need for transformations between the various design domains. These transformations are generally needed (Walker, 1988), because of the differences (non isomorphism) between the domains in the later stages

of design. This non isomorphism makes the different domain views of the same design topologically different, and thus to maintain interdomain consistency, the transformations are required.

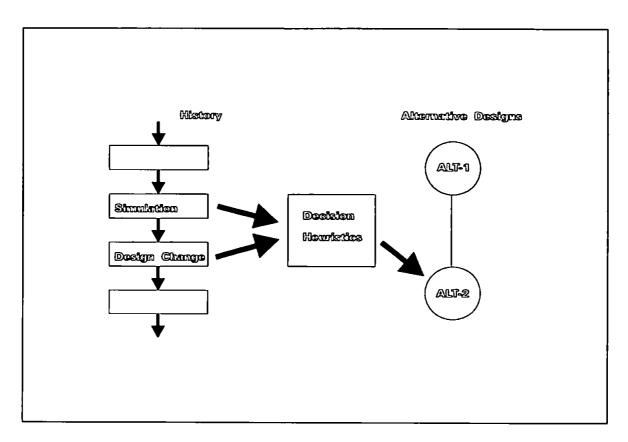

The two aspects, designs and design alternatives mentioned above, go some way towards addressing the second statement of the first requirement, leaving the first. In examining this it is reasonable to assume that actively encouraging designers to pursue design alternatives is primarily a user interface function, however the representation has an important task also, by providing a simple and clear means of portraying alternative designs. In which case, any system that makes the representation of alternatives easy and, or automatic could be viewed as encouraging the user to use them when compared with systems which do not provide any high level support of alternatives. This line of reasoning could be extended to consider an alternative management system which analyses the user machine interaction to determine if the designer is working on a different approach to a problem, and then handles the creation of new alternatives accordingly. Such an approach would go some way towards encouraging the user to explore new design concepts, whereas a "version server" which maintains historic consistency between the different parts of a design would not.

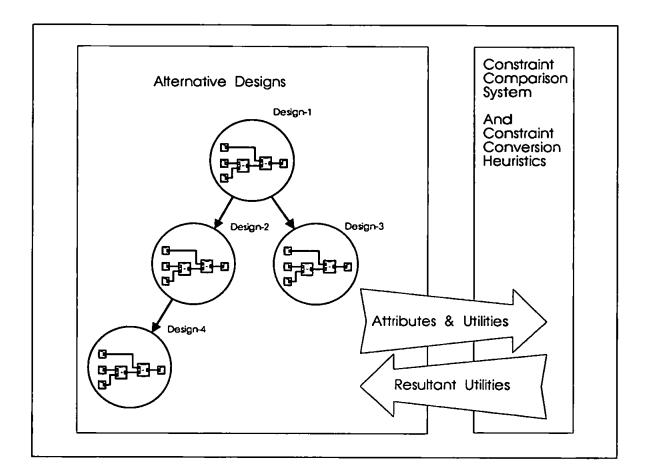

# 3.2.1.2. The Second Requirement:

The second requirement taken from chapter 2 states:

"Assist with the choice of competing design solutions, for example, enabling evaluations of solutions to be made on the basis of comparative functional simulations."

Two important questions that need to be answered before this requirement can be successively tackled are: What means can be used to distinguish between different designs; and what methods can be used to compare them?

There are many ways of differentiating between designs, limited only by the types of information used. This may be in the functionality of the designs themselves, in that an adder is different from a multiplier, or in other ways, for example this design was produced in 6 weeks and that one in 6 months. The only real limits to this general statement are the relevance of the information to the task and the difficulty in generating that information. In this way any design or designs could be conceivably be

compared on the basis of any information which was instrumental to their existence. This is a difficult requirement for any system, and can only be reasonably achieved through reducing the information required to a manageable level.

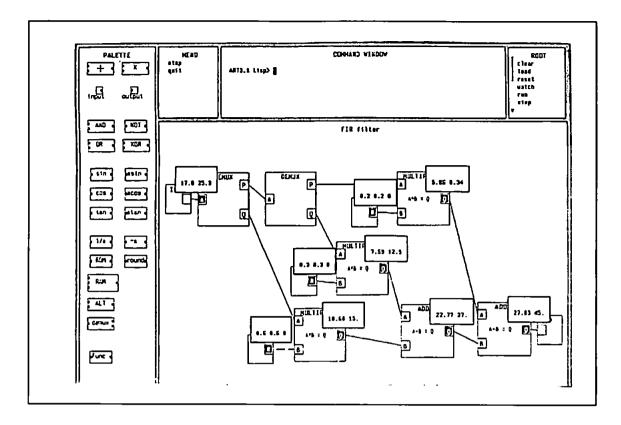

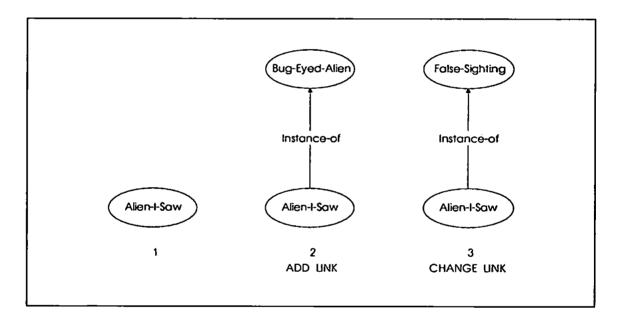

Each piece of information can be viewed as a constraint, though not totally in the sense of constraint satisfaction, for example where unknown elements in an equation are derived from known values (Tong, 1987), or where designs are synthesised that meet constraints (Chan et al, 1987), but in a more general vein. With this approach any information contained in a design is regarded as a constraint in that it tends to make the design more specific, and therefore constrains it in some way. For instance if there are no requirements other than: "Make something" then the design can be any object, whereas if the design is already an adder then it is not going to factorise easily. Constraints can be classified into many different areas, the following paragraphs outline a few of them relevant to the requirements.