# SystemC Through the Looking Glass:

# Non-Intrusive Analysis of Electronic System Level Designs in SystemC

by

Jannis Stoppe

Supervisor:

Prof. Dr. Rolf Drechsler

Second referee:

Prof. Dr. Stefan Edelkamp

# CONTENTS

| _ |                 |                                                       |  |  |  |  |

|---|-----------------|-------------------------------------------------------|--|--|--|--|

| 1 | INT             | RODUCTION AND MOTIVATION 1                            |  |  |  |  |

| 2 | PRELIMINARIES 7 |                                                       |  |  |  |  |

|   | 2.1             | Hardware Design Approaches 8                          |  |  |  |  |

|   | 2.2             | SystemC 13                                            |  |  |  |  |

| 3 | EXT             | RACTION OF SYSTEMC META DATA 19                       |  |  |  |  |

|   | 3.1             | State of the Art 20                                   |  |  |  |  |

|   | -               | Debug Symbol Parsing 27                               |  |  |  |  |

|   |                 | Extraction of Static Information via Debug Symbols 28 |  |  |  |  |

|   |                 | Extraction of Dynamic Information 31                  |  |  |  |  |

|   | 3.5             | Conclusion 39                                         |  |  |  |  |

| 4 | EXT             | RACTION OF SYSTEMC BEHAVIOUR 41                       |  |  |  |  |

|   | 4.1             | Software-Based Approaches 42                          |  |  |  |  |

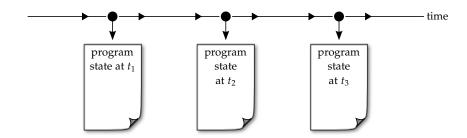

|   |                 | Consecutive Snapshot Extraction 46                    |  |  |  |  |

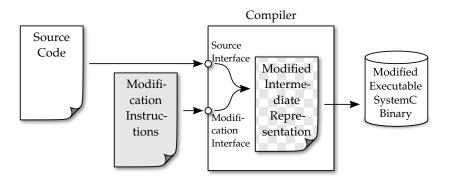

|   |                 | Compiler-based Behaviour Modification 48              |  |  |  |  |

|   |                 | Aspect-Oriented Analysis Insertion 50                 |  |  |  |  |

|   | 4.5             | Conclusion 62                                         |  |  |  |  |

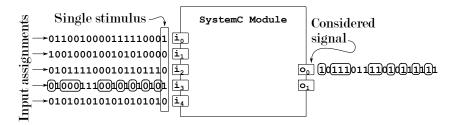

| 5 | FIL             | ling the gaps with machine learning 65                |  |  |  |  |

|   | 5.1             | Reverse-Engineering Module Logic 69                   |  |  |  |  |

|   | 5.2             | ESL-specific Additions 73                             |  |  |  |  |

|   |                 | 5.2.1 SystemC's modularity 74                         |  |  |  |  |

|   |                 | 5.2.2 Time of extraction 75                           |  |  |  |  |

|   |                 | 5.2.3 Time delays 77                                  |  |  |  |  |

|   |                 | 5.2.4 Internal states 78                              |  |  |  |  |

|   |                 | 5.2.5 User-defined datatypes 79                       |  |  |  |  |

|   |                 | 5.2.6 Circles 80                                      |  |  |  |  |

|   |                 | 5.2.7 Summary 80                                      |  |  |  |  |

|   | 5.3             | Conclusion 82                                         |  |  |  |  |

| 6 | APF             | elication 83                                          |  |  |  |  |

|   | 6.1             | Visualization 84                                      |  |  |  |  |

|   |                 | 6.1.1 Previous Work 85                                |  |  |  |  |

|   |                 | 6.1.2 Realization 87                                  |  |  |  |  |

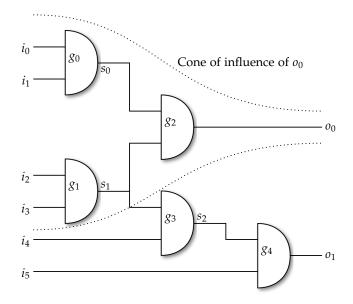

|   | 6.2             | Cone of Influence Extraction 91                       |  |  |  |  |

|   | 6.3             | Feature Localization 94                               |  |  |  |  |

|   |                 | 6.3.1 Previous Work 95                                |  |  |  |  |

|   |                 | 6.3.2 Realization 98                                  |  |  |  |  |

|   | 6.4             | 1                                                     |  |  |  |  |

|   | 6.5             | Stimuli Generation via Machine Learning 102           |  |  |  |  |

# Contents

6.5.1 Previous Work 1036.5.2 Applying Machine Learning for CDSG 1046.6 Conclusion 106

7 CONCLUSION 107

## DISCLAIMER

# I hereby declare that

- this dissertation is my own original work,

- it has been completed without claiming any illegitimate assistance and

- I have acknowledged all sources used (both, verbatim and regarding their content).

Jannis Stoppe, February 27, 2017

I would like to thank Robert Wille for the assistance he offered whenever I needed it and the time he put into me

and Rolf Drechsler for enabling me to present my ideas to the world and giving me the opportunity to work in a beautiful environment.

Your support has been invaluable.

I would also like to thank my wife and children for being a patient, loving support during stressful times.

You give meaning and make me endure, which is more than I ever could have hoped for.

We can only see a short distance ahead, but we can see plenty there that needs to be done.

Alan Turing [113]

The complexity of digital systems is increasing.

Ever since Gordon E. Moore projected that the amount of components in integrated circuits would double every year in 1965 [75] (and later revised that to every two years in 1975 [76]), his prediction would hold. This exponential growth not only leads to faster and more complex systems, it also results in serious issues concerning their design: A current 18-core Intel Haswell Xeon chip consists of more than 5 billion transistors [79] – nearly twice as many as there are base pairs in the human DNA [115].

Being able to manufacture such large systems, while being an impressive achievement by itself, still requires them to be designed in the first place. This simple aspect is a serious problem for the development of modern chips as the design tools must enable the designers to handle such large systems: if these large systems cannot be designed, they cannot be manufactured.

Classic Hardware Description Languages (HDLs) that have been designed to model hardware are – by definition – close to the hardware they describe. This also means that systems that are written using these HDLs cannot easily be run and/or tested if the description is still incomplete. Thus, the development process becomes a bottom-up approach, requiring designers to first build the system as a whole and then start testing it. Issues with the overall architecture can therefore only be found once the system has been fully implemented, making decisions that need to revise architectural properties expensive and thus large systems tough to be designed.

Traditional HDLs hence struggle with the complexity of modern hardware. In order to keep up with the manufacturing advances, the designs are following a modular approach and the distinct parts are re-used. Especially in conjunction with well-scaling parts such as memory (which can simply be "made larger" in order to gain the according benefits), these larger designs can still be achieved – at least to a certain degree. Still, complexity remains a key issue, especially for designs that cannot be scaled easily or do not benefit from such a scaling. HDLs are therefore increasingly facing the issue of the *design gap* [35], i.e. the problem

that systems cannot be designed in accordance to the available manufacturing capabilities due to their complexity.

In order to handle this complexity, more abstract description languages have been introduced. These so-called system level descriptions are used to model the coarse structure using established features (such as modules and signals) but use an underlying high-level programming language (such as C++) to describe the detailed behaviour of these parts. This means that a system can be prototyped more quickly and the system as a whole may be tested before the actual hardware (or software) parts have been implemented.

The current de-facto standard for system level design is SystemC [7]. Implemented as a C++ library and specified in an open standard [81], it combines the benefits of an established high-level programming language (such as tool chains, libraries, Integrated Development Environments (IDEs) etc.) with the ability to describe hardware designs on an abstract level and simulate them despite being implemented in this abstract way.

Although these system level languages strive to reduce the amount of complexity needed to create a prototypical system design, the designs still are considerably complex. To appropriately model all parts of a system and their interactions, the design usually becomes quite large, even when working on higher levels of abstraction. The sheer size of a design may make it difficult for new designers to join a project. Acquiring knowledge about a design, either to introduce new members into a team or to keep other people working on the project up to date with recent changes, is therefore a critical part of the design process.

This *Design Understanding* can be approached in a variety of ways, depending on the available sources of information. Reading the source code of the design is usually inefficient and not an appropriate way of starting to understand a design, especially for larger designs. While a proper (manually created) documentation is usually the best way to introduce designers to certain parts of the work, the creation and especially maintenance of a manual is a time-consuming (and therefore expensive) process with no immediate benefit for a project, making it sometimes infeasible to keep the documentation in an appropriate condition.

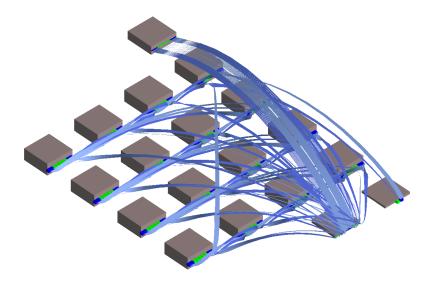

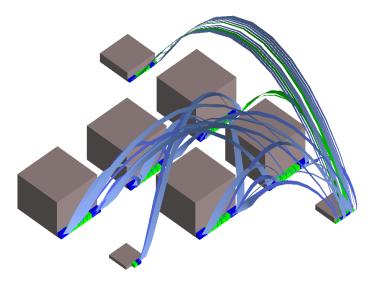

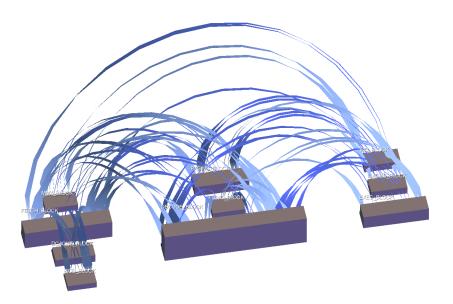

Methods to automatically generate or retrieve more abstract representations of hardware designs to allow designers to quickly grasp important structures are one way to approach the problem of imperfect, manually created meta documents. The automatic generation of e.g. visual representations of system designs is a common way to quickly allow designers to take a glance at a system's general structure. While this approach of course needs to address issues such as the complexity of the resulting images [45] or the performance of the visualisation [58, 128],

deriving the structure to be displayed from the source code has been a straightforward procedure for classic HDLs.

System level descriptions in general and SystemC implementations in particular level descriptions are, however, harder to analyse. The hardware structures are not described statically as in classic HDLs but instead are *created dynamically at run-time*, making a static analysis approach to extract the structure more difficult or even impossible. Additionally, C++ is an older language with lots of different dialects available that is not even considered context-free. This means that writing a single parser that could serve as a front end to analyse a design is an equally futile task. Lastly, compilers are used to translate the system descriptions into an executable form – in case of C++ binary code which can directly be executed on a given computer. This means that once the program has been processed to be executable, it is even harder or downright impossible to analyse.

This work proposes new methods and approaches to analyse SystemC designs despite these issues and without shifting the burden to the designer (by e.g. requiring the source code to adhere to certain standards). More precisely, the research question of this thesis is

How can the desired information from a given SystemC design be extracted without assuming restricted language means and without modifying the existing infrastructure like parsers or compilers?

This means that there are two core requirements to any solution. The first is that the source code should be considered untouchable. If the solution to the analysis problem is anything that requires major source code alterations, the designers may as well simply add the required tracing functionality to their code without utilizing another solution. As the time required to use a solution can be directly translated to the money that an engineer needs to be paid, the solution must be easily added in order to prevent large costs for something like an analysis tool. The second requirement is that the resulting method should be compatible to at least all major C++ compilers (i.e. gcc, clang and Microsoft Visual C++ Compiler (MSVC++)). As SystemC adheres strictly to the C++ standard, it can be used in any type of project, regardless of the code elements being used in them. This means that a SystemC project may use any C++ dialect to describe the system. Therefore, while an analysis tool may not support each and every exotic framework available, any method to analyse SystemC should at least be able to handle the source code used on the major platforms.

These points are summarized as the trait of *non-intrusiveness*, describing that an existing project (encompassing both, infrastructure such as compilers being used and the source code of the design itself) should not

be altered by any analysis approach. It is an important issue concerning the methods that can be used to analyse a system description and thus represents a cornerstone of design decisions throughout this thesis.

The remainder of this thesis first gives an overview of existing HDLs in general and SystemC in particular in Chapter 2. Afterwards, there are four Chapters that provide the core contributions of this work.

- Chapter 3 illustrates how a static model describing the design can be extracted from a SystemC description.

- Chapter 4 then shows how these techniques can be further refined to be applied to running designs, allowing their behaviour to be traced as well.

- Chapter 5 explains how information that was not retrieved using the previous steps can be learned using approaches from the machine learning domain.

- Chapter 6 finally illustrates how these approaches can be applied and shows the according use-cases.

Chapter 7 contains a brief summary of the thesis. It proposes several research questions for potential future work as well.

The approaches that are proposed in this thesis have been previously published on various occasions:

- Martin Ring, Jannis Stoppe, Christoph Lüth, and Rolf Drechsler. Change impact analysis for hardware designs. In Forum on specification & Design Languages (FDL), 2016

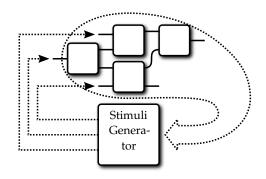

- Jannis Stoppe, Arved Friedemann, and Rolf Drechsler. SystemCDG AI based coverage driven stimuli generation for SystemC. In *International Workshop on Logic & Synthesis (IWLS)*, 2016

- Martin Ring, Jannis Stoppe, Christoph Lüth, and Rolf Drechsler. Change management for hardware designers. In Workshop on Design Automation for Understanding Hardware Designs (DUHDe). IEEE, 2016

- Rolf Drechsler and Jannis Stoppe. Hardware/software co-visualization on the electronic system level using SystemC. In *International Conference* on VLSI Design (VLSID), pages 44–49, 2016

- Jannis Stoppe and Rolf Drechsler. Analyzing SystemC designs: SystemC analysis approaches for varying applications. Sensors, 15(5):10399 10421, 2015

- Nils Przigoda, Jannis Stoppe, Julia Seiter, Robert Wille, and Rolf Drechsler. Verification-driven design across abstraction levels: A case study. In *Euromicro Conference on Digital System Design (DSD)*, pages 375 382. IEEE, 2015

- Jannis Stoppe, Robert Wille, and Rolf Drechsler. Automated feature localization for dynamically generated SystemC designs. In *Design*, *Automation & Test in Europe Conference & Exhibition (DATE)*, pages 277 280. EDA Consortium, 2015

- Jannis Stoppe and Rolf Drechsler. Ecore model generation from System-C/C++ implementations. In *Workshop on Design Automation for Understanding Hardware Designs (DUHDe)*. IEEE, 2015

- Jannis Stoppe and Rolf Drechsler. KI-Unterstützung im Systementwurf.

Industrie Management Zeitschrift für industrielle Geschäftsprozesse (IM),

1:21 24, 2015

- Jannis Stoppe, Robert Wille, and Rolf Drechsler. Validating SystemC implementations against their formal specifications. In *Symposium on Integrated Circuits and Systems Design (SBCCI)*. ACM, 2014

- Jannis Stoppe, Marc Michael, Mathias Soeken, Robert Wille, and Rolf Drechsler. Towards a multi-dimensional and dynamic visualization for ESL designs. In Workshop on Design Automation for Understanding Hardware Designs (DUHDe). IEEE, 2014

- Jannis Stoppe, Robert Wille, and Rolf Drechsler. Cone of influence analysis at the Electronic System Level using machine learning. In *Euromicro Conference on Digital System Design (DSD)*, pages 582 587. IEEE, 2013

- Jannis Stoppe, Robert Wille, and Rolf Drechsler. Data extraction from SystemC designs using debug symbols and the SystemC API. In *IEEE* Computer Society Annual Symposium on VLSI (ISVLSI), pages 26 – 31. IEEE, 2013

## INTRODUCTION AND MOTIVATION

Additionally, further papers were published after the editorial deadline. While these are directly or indirectly related to the work presented here, they are not covered in this thesis.

- Rolf Drechsler and Jannis Stoppe. Hardware/software co-visualization: The lost world. In *International Workshop on Boolean Problems (IWSBP)*, 2016

- Mehran Goli, Jannis Stoppe, and Rolf Drechsler. AIBA: an automated intra-cycle behavioral analysis for SystemC-based design exploration. In *International Conference on Computer Design (ICCD)*, 2016

- Mehran Goli, Jannis Stoppe, and Rolf Drechsler. Automatic equivalence checking for SystemC-TLM 2.0 models against their formal specifications. In *Design, Automation and Test in Europe (DATE)*, 2017

- Kevin Leonard Schneider, Oliver Keszöcze, Jannis Stoppe, and Rolf Drechsler. Effects of cell shapes on the routability of digital microfluidic biochips. In *Design*, *Automation and Test in Europe (DATE)*, 2017

Simplicity does not precede complexity, but follows it.

Alan Jay Perlis [86]

The physical elements that constitute a computer system are its Hardware – as opposed to the Software, which is made up of the programs and data which are executed and stored on a given hardware.

While the term hardware encompasses all physical parts of a computer system [21] (i.e. including parts such as cases, keyboards, mounts etc.), this work focuses on aspects of the design of Integrated Circuits (ICs) (also referred to as microchips). These ICs are of electronic circuits on a small plate of semiconductor material onto which the required parts are applied [75].

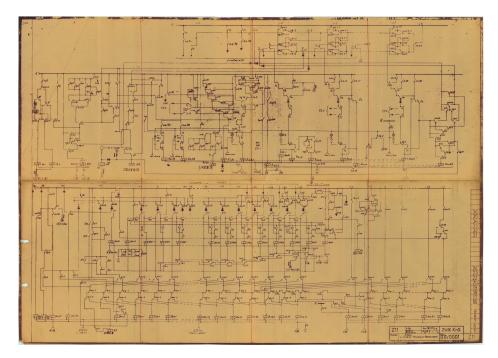

Just like software (or any other system), hardware needs to be designed. For small systems (as they were common during the early days of computer systems), the hardware can be designed manually. In this case, the elements and parts that are available in hardware (i.e. transistors and connections) are set up and laid out until the system is ready to be built. Figure 1 illustrates how this classic design on paper looks like: parts of the design were simply drawn and described. While the approach of doing this using pen and paper worked well for early, small designs, modern ones consist of billions of transistors, each merely a few nanometres in size.

Obviously, designing such systems manually, i.e. by simply laying out hardware parts, is infeasible. To be able to handle designs of such scales, several different hardware description languages were developed, each with its own features and issues. The most distinct differences, however, can be seen regarding different abstraction layers. Hardware can be described using various means. The available components that are the obvious choice, leading to a fine-grained description of a hardware design that can easily be manufactured. Another way is to use formulas that can be mapped to these components, allowing designers to use mathematical constructs to describe a design. Various other abstraction levels are also available, up to natural language: specifications written in English are still hardware descriptions, albeit they may be inaccurate or incomplete. This variety of description means allows designers to work on systems using different granularities, depending on the precision, speed and features being required for the process.

Figure 1: The plan of a part of the Arithmetic and Logical Unit (ALU) of Conrad Zuse's Z11 [130].

This chapter gives an overview on hardware design paradigms, outlining different approaches to hardware design in Section 2.1. As this work specifically focuses on aspects of designing hardware on the Electronic System Level (ESL) using SystemC, Section 2.2 then focuses on this level of abstraction and the SystemC library in particular.

## HARDWARE DESIGN APPROACHES

Today's approach to hardware design is layered, going from abstract towards more detailed system descriptions. Each of these layers serves a particular purpose, allowing designers to handle the respective design tasks at the abstraction level that fits best a given goal.

Different abstraction levels to describe hardware

TRANSISTORS are the fundamental elements of current ICs. A transistor can be used to amplify or switch an electronic current. Combined with the ability to manufacture them on small scales using modern photolithography (i.e. "printing" them onto semiconducting material), the transistor has become *the* basic building block for all parts in an IC. The *Transistor Level* is describing how these parts need to be connected for a given circuit design, making it the lowest abstraction level.

When designing hardware systems, working on this lowest of all abstraction levels leads to large descriptions as even mundane systems tend to require a large amount of transistors. Figure 1 illustrates the complexity of these layouts. With even early computing machines suf-

Figure 2: AND gate built from transistors

Figure 3: Visualization of a hardware design at the gate level.

fering from the complexity of descriptions that relied on transistors as their primary means of specification, it is obvious that designing systems on this level is not a sustainable approach to hardware design. Instead, while the translation to transistors (and their layout) is required for a system to be built, this is usually done automatically in order to let designers work on more abstract descriptions that allow them to handle a given system's complexity more easily.

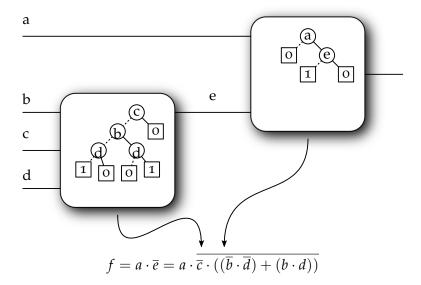

THE GATE LEVEL is the first abstraction to the description of the transistors and their connections. As transistors can be used to model certain boolean functions, systems can be described using these and then be directly mapped to their respective transistor counterparts. Figure 2 illustrates this relation, showing how an exemplary boolean AND can be modelled using transistors. Figure 3 shows a visualization of a hardware design at the gate level.

The advantage of this abstraction level is that there exists a direct correspondence from a mathematical set of tools to a hardware design. Thus, not only can formulas that are used to describe a system be translated into a hardware description but the methods developed in the field of boolean algebra can directly be applied to improve a given design.

One approach to this abstraction level is the description of a combinatorial circuit using a truth table or Binary Decision Diagram (BDD), both of which can easily be translated to a boolean function. Once this is done, methods such as e.g. the Quine-McCluskey algorithm [67] can be used to minimize this function. The resulting function is minimal,

which means it uses fewer boolean operators and variables in order to describe the same result. With boolean operations being implemented as gates that can directly be translated to transistor descriptions, this also means that the resulting circuit will use fewer transistors and thus require less space (and thus be cheaper to produce). This illustrates how the abstraction of using gates to describe a circuit can improve the design process.

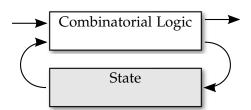

No registers in boolean logic

Unfortunately though, using boolean functions to describe circuits not only provides a rather small step concerning the abstraction of the description (and thus still results in large descriptions), it also practically disregards the notion of persistent states. ICs can be divided into the combinatorial logic (which can easily be described as a boolean function) and its registers that retain their state until specifically being set to a new state. In order to make this defining feature of computer hardware a core feature of the description as well (and thus be able to efficiently design circuits that actually use it), another, even more abstract layer was introduced.

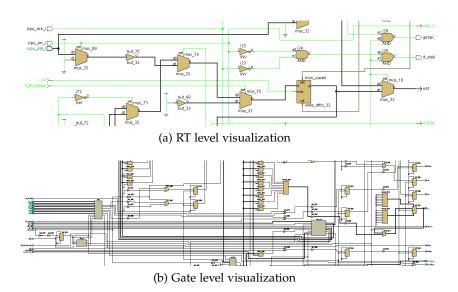

THE REGISTER TRANSFER LEVEL (RTL) focuses on the description of registers and the logic that interconnects them (i.e. that transfers information between registers – hence the name). This core idea of hardware design on the Register Transfer Level (RTL) is therefore already close to traditional (software) programming paradigms that rely on data and operations. However, due to their intended usage as HDLs, languages that describe hardware on the RTL have very distinct features that separate them from modern high-level software programming languages. The most prominent of these is their inherent parallelism. As hardware describes a set of transistors and intermediate wires, elements described in these HDLs are not evaluated sequentially (as it is the case for software) but instead represent a system where assignments happen in parallel.

Verilog and VHDL

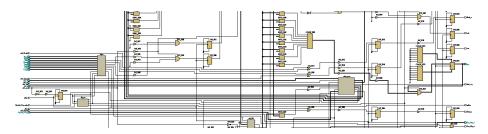

The most famous examples of RTL HDLs are the VHSIC Hardware Description Language (VHDL) [80] and Verilog [112]. Both of these were regarded as "breakthroughs" [20] concerning the development of digital circuits after they were introduced as they finally enabled designers to abstract from gate level designs. They both have been standardized by the Institute of Electrical and Electronics Engineers (IEEE) [41, 42]. Figure 4 shows the visualization of an RTL hardware description.

Notice that these two languages have been extended over the years and also include non-synthesizeable language constructs that allow designers to more rapidly describe a circuit's behaviour but require this description to be altered or rewritten before it can actually translated into hardware. While this seems to contradict the idea of RTL descriptions being *hardware* descriptions, it illustrates the issue that hardware design on the RTL faces: the level of abstraction no longer suffices to describe hardware on the current level of complexity. However, larger

Figure 4: Visualization of a hardware design at the RTL.

abstractions necessarily result in descriptions that may be executable but not snythesizeable. Even simple means such as a loop that *may* be unbounded (i.e. has no well-defined upper bound concerning how often it is executed) or a second wait statement in a process that lets a given description wait for another signal in two different "locations" of its description are easy to execute but cannot be synthesized. This means that the HDLs being used today offer designers the choice of (temporarily) adding more abstract elements that limit the description to a simulation for the sake of more quickly having a working prototype of a given system.

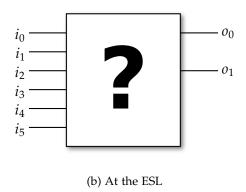

THE ELECTRONIC SYSTEM LEVEL (ESL) basically inverts this line of thought. Instead of enriching RTL HDLs with abstract features, ESL descriptions use already-abstract high-level programming languages and add hardware-description capabilities to these.

This results in a much more "top-down" approach. As a system description can use all high-level constructs that are offered by its underlying programming language, a first prototype is usually established quickly on the ESL. Especially the abundance of libraries for modern software programming language helps speeding up this process: instead of e.g. having to implement an image processing algorithm in a language that is synthesizeable (or close to it), any existing library (such as e.g. OpenCV [10] for an image processing problem) can be used to add this functionality to a given ESL description. A "module", i.e. a block of the hardware design, is thus regarded as a black box – its internal workings remain hidden to the surrounding framework (and maybe even the designer).

While certain parameters (such as the time that is required to calculate a result in the final system) may need to be guessed or ignored for the time being, this approach results in the ability to very rapidly see if the architecture of a design works as intended. The detailed hardware implementation is thus no longer part of the hardware description. Instead, ESL designs give designers the ability to see if the anticipated behaviour of the given parts of the design works as intended – and from that point, gradually decrease the abstraction of the description until it can be synthesized again. Generally, the ESL can thus be regarded as an

ESL descriptions are executable specifications

executable specification: while it (mostly) cannot be synthesized, it can simulate the desired behaviour and thus specifies in detail the interfaces the final implementation needs to comply with.

THE FORMAL SPECIFICATION LEVEL (FSL) adds another layer of abstraction to even more rapidly design the cornerstones of a system. Instead of providing an ESL-like executable specification, the Formal Specification Level (FSL) focuses on the specifications of the system itself, sacrificing the executability to gain more abstraction and thus allow designers to work more rapidly.

The Unified Modeling Language (UML) [9, 117] is the most prominent example of a formal specification language. Focused on software development, it allows designers to plan the structure of their application, describe the desired behaviour or constrain the input and output of functions using Object Constraint Language (OCL) constraints.

An adaption of the UML that instead focuses on the development of hardware designs is the Systems Modeling Language (SysML). The software-centric view of the UML is replaced with description means for hardware designs, allowing designers to formally describe a system before starting with an implementation on the ESL.

While these cannot be executed (and thus clearly offer fewer details than the ESL designs), they enable designers to quickly develop unambiguous schematics for a given design. These can be used to e.g. communicate the design to other people who are part of the development process (such as other designers, customers, management etc.) in an understandable fashion or even (due to their formal nature) locate errors (such as deadlocks or oxymorons).

THE INFORMAL SPECIFICATION LEVEL (ISL) finally is the most abstract way to describe a system. Using natural language and without any further restrictions, the Informal Specification Level (ISL) is used to draft out a system description as a first step.

While there are approaches to automatically analyse and process these natural language specification [43], these approaches are neither complete nor flawless and can in general only be considered an effort to assist a manual translation to a less abstract description. Instead, any natural language description on the ISL should be seen as a way to communicate between people, describing the system in the level of detail that is required to achieve whatever aim the description serves.

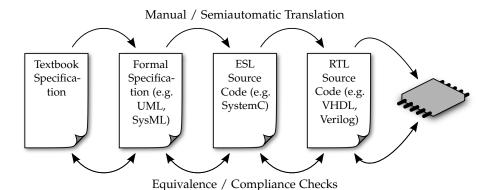

The description means for hardware thus form a hierarchy from the most abstract description to the least abstract one. Starting with the ISL that has virtually no restrictions over the FSL that provides a formal specification and the ESL that provides an executable specification, the design is usually finalized on the RTL that provides a synthesizeable description and can thus be automatically translated into hardware

Figure 5: Today's hardware design flow

schematics. Figure 5 illustrates these connections between the different layers of hardware design approaches.

## SYSTEMC

SystemC is a C++ library for modelling and simulating system designs on the ESL. Like other ESL modelling frameworks, it provides means to model hardware structures and a simulation kernel that provides the needed logic to simulate the parallel behaviour that is inherent to hardware designs. By providing descriptions means for both, hardware concepts (like modules, signals, ports, etc.) and software concepts (like class instantiations, function calls, memory allocation, etc.), it allows to model and to execute hardware and software systems on various levels of abstraction. While modules and their connections (both representing parts of a hardware system) are instantiated, the logic behind those can be both, made up of simulated hardware elements down to gate level or just a software simulation of the behavior that is supposed to be realized in hardware or software later on.

While a variety of ESL description libraries exist that extend most major high-level languages with hardware description means (such as Esys.net for developing in .net/mono [51, 52], Hardware Join Java for developing in Java [46], Chisel for developing in Scala [2], and more), SystemC has emerged as the "top of the pack". By now, SystemC is considered an "industry standard" [96], has been standardized [81] and is widely used to prototype the structure of hardware/software systems as well as their behaviour in both, academia and industry.

**Example 1** Figure 6 shows a SystemC program that realizes a simple carry-ripple adder. The bit-width of the adder is not statically defined, but will be provided by the user when executing the program. This is realized by iteratively instantiating new one-bit full adders.

When writing hardware designs in SystemC, designers have the full spectrum of the underlying language at their disposal. Modules are class

```

#include <systemc.h>

SC_MODULE(fullAdder) {

sc_in<bool> a, b, carryIn;

sc_out<bool> result, carryOut;

void calculate() {

carryOut.write((a && carryIn) || (b && carryIn) || (a && b));

result.write((a \ \&\& \ !b \ \&\& \ !carryIn) \ \mid \mid \ (!a \ \&\& \ b \ \&\& \ !carryIn) \ \mid \mid

(!a && !b && carryIn) || (a && b && carryIn));

SC\_CTOR(fullAdder)\colon \ a("a")\ ,\ b("b")\ ,\ result("result")\ ,\ carryOut("

carryOut") {

SC_METHOD(calculate);

sensitive << a << b;

};

int sc_main (int argc , char *argv[]) {

int bits = 2;

if (argc > 1)

bits = max(o, min(16, atoi(argv[1])));

fullAdder* previous;

for (int i = 0; i < bits; i++) {

fullAdder* fa = new fullAdder("fullAdder");

if (i > 0) {

sc_signal <bool>* sig = new sc_signal <bool>("carrySignal");

previous->carryIn(*sig);

fa->carryOut(*sig);

previous = fa;

return o;

```

Figure 6: SystemC program

instances, their internal states (registers, flip-flops etc.) can be modelled using field variables and the internal logic is written using arbitrary C++ code.

This leads to a design paradigm that detaches the behaviour from its implementation. Where RTL languages such as VHDL provide designers with the ability to specify *several* implementations to choose from, SystemC abstracts further from this concept and does not require anything as long as the behaviour has been described properly. In VHDL, designers e.g. need to decide which kind of adder should be used if two numbers should be added – e.g. whether or not a carry lookahead should be used and which one. SystemC on the other hand is focused on the efficient simulation of these systems, leaving the question of implementation details for later in the design process: adding two numbers is done, and while the designer may specify how much time the final implementation supposedly will take, this is not necessary.

The designer does not even need to decide whether a given functionality should be implemented in software or hardware. Instead, the behaviour that is specified may later be translated to hardware, software or a mixture of both. This principle is called <code>Hardware/Software Co-Design</code> [18] and allows designers to use SystemC to quickly develop working prototypes of hardware/software systems without being required to implement all the details that would be needed in order to have a working e.g. VHDL design.

This term reflects how the design process encompasses the development of both, software and hardware parts, that later interact closely. The SystemC design process may start with an arbitrary, abstract C++ implementation which is then iteratively translated into a combination of RTL desriptions (which may be embedded into the SystemC simulation) and C programs that are executed on the RTL parts until the whole system becomes a set of synthesizeable parts and can thus be translated into a single hardware / software implementation.

Beyond the classes that represent hardware structures, SystemC offers a simulation kernel that manages the execution of the methods that represent a module's internal logic . Two concepts of the simulation kernel are of special interest for this work:

- The simulation kernel splits the execution of a SystemC program into two phases, the *elaboration phase* and the *simulation phase*. The former is meant to create the system that is to be simulated, i.e. all (virtual) hardware parts such as modules and signals are initialized. The latter then simulates this system and actively *prohibits* the creation of further SystemC objects.

- The simulation kernel manages an *event queue* that contains all processes and threads that need to be executed at a later point in simulation time. This means that the SystemC kernel runs an event

Hardware / Software Co-Design

SystemC simulation kernel

driven simulation, waking up those parts of the design that need to be updated and letting all other elements of the design lay dormant, thus saving computational power. This way, the simulation kernel simulates the parallelism that is inherent to the hardware parts that are modelled by SystemC. Note that the kernel, while it simulates the parallelism of the simulated system, is not itself running in parallel but is instead a strictly sequential, single-threaded software, thus avoiding issues that may arise from parallel execution such as race conditions at the cost of decreased performance.

Its design allows SystemC to separate the functionality (that needs to be built in order to end up with an executable system) from the implementation. In this case, the latter means either the hardware that implements the desired behaviour or the combination of the hardware platform and the software that is executed on it in order to end up with a module that implements the given behaviour. The C++ implementation that describes the behaviour for SystemC designs should be considered an executable specification instead of an implementation though. As the given source code that describes a thread's behaviour can neither be translated into software nor hardware automatically, it does not qualify for being an implementation in the sense of embedded systems. However, while it is much more abstract than a hardware implementation or the combination of an IC and the embedded software running on it (and may ignore several other traits of an implementation such as timing), it is of course still a C++ implementation that is executed to emulate the module's behaviour.

While these concepts are already focusing on shorter design cycles by letting designers create executable prototypes as early as possible, the concept of arbitrary C++ code includes libraries, which results in even faster prototyping of certain modules. As there is a vast amount of C++ libraries available, they may all be used to quickly develop solutions for a given problem. This means that development cycles are much shorter, allowing for designers to quickly iterate design prototypes with customers, start to write tests early on and validate design concepts at a lower cost than using the traditional hardware design approach.

SystemC performance

While this approach results in shorter development processes by allowing designers to quickly build working (i.e. executable) prototypes, it also has advantages when running the simulation itself. As the module logic is implemented in arbitrary C++ code, no simulation kernel call is required to calculate the result of an operation. Instead, after the kernel wakes up e.g. a given method, the results are calculated at once and the designer may instruct the simulation kernel to wait for a given time frame in order to emulate how the module would require some time to finish the given calculations. For the simulation, this means that much less overhead is required in order to perform calculations as the simulation kernel needs to be invoked less often.

TLM

Transaction Level Modeling (TLM) is the next step in this manner, altering the way modules communicate in order to increase performance by reducing the kernel activity associated with these operations. While TLM had started as an optional extension to SystemC, it is now part of the standard and serves the purpose of further increasing simulation performance and unifying transactions between modules. It does so by introducing two core concepts to the existing foundation of the SystemC library:

- 1. Temporal Decoupling is the idea of letting different parts of the SystemC model advance at different speeds. The traditional, event-driven model relies on a single simulation time value that is advanced for all components. If anything is supposed to take time in the simulation, the processes need to be stopped and the required events to wake them up again communicated to the kernel. These are then added to the event queue (and later have the kernel invoke them again). This process, if done repeatedly, takes time and thus slows down the simulation speed.

- TLM instead give designers the possibility to use functions as interfaces that model a transaction and simply store the time that is supposed to pass in a thread-specific variable. That means that instead of invoking the scheduler that manages the consecutive execution of SystemC threads, functions in different modules call each other and invoke the required actions, each time annotating that simulation time should have passed (but did not yet) and at some point wait for the simulation kernel to "catch up". This results in an even better performance, although certain concepts (such as pipelining) cannot be translated into these transactions.

- 2. The Generic Payload is a generic transaction class that serves as a common foundation to transfer information. Instead of having different types for each port (such as boolean or integer), the tlm\_generic\_payload class enables designers to use a single type for various transactions, storing both data and meta information for a given transaction. This results in better interoperability, allowing modules to be interconnected easier thus eliminating the need for wrapper modules in a lot of cases and again speeding up both, development and simulation time.

The advantages of the design approach on the ESL and the features of SystemC in particular have turned SystemC into a "de-facto standard" [7]. SystemC is by now widely used, with the reference implementation being available under an open source license. While other ESL solutions are available as well, the adaptation of SystemC is far ahead of any contenders. This is the main reason for the focus of this work: in order to ensure a scientific (and maybe industrial) relevance, this work focuses on SystemC. While other solutions for design on the

## PRELIMINARIES

ESL may not share the same set of issues that need to be solved, the degree of usage of SystemC justifies solving these using the given platform.

Names and attributes must be accommodated to the essence of things, and not the essence to the names, since things come first and names afterwards.

Galileo Galilei

SystemC is implemented as a C++ library. This means that a design implementation may use any C++ statements to describe both, the system's structure and behaviour. Any C++ libraries can be used to add functionality to a design, vastly simplifying the design process especially for complex tasks that have been implemented in software before. However, relying purely on C++ comes at a price as well: High level software languages such as Java or C# include frameworks for introspection and reflection of running programs. The former allows the designer to write code that inspects the structures that were created by the running program, the latter allows the designer to write code that modifies those structures. E.g. in Java, retrieving an object's type, getting a list of its field variables and invoking one of its methods can be achieved using a few lines of code that utilize the reflection framework. In C++, this behaviour is not supported.

When compiling a C++ program, the compiler translates the program into machine code, stripping it of all unnecessary information (such as information about an object's fields' names and types), thereby making it impossible to simply retrieve any information about the structures that are present in a running program. However, as SystemC relies on C++ to create the simulated system in the first place, this run-time retrieval would be needed for e.g. a generic visualization tool.

Simply put, the lack of native reflection/introspection in C++ renders the extraction of any meta information about a SystemC design a far-from-trivial problem. This chapter focuses on approaches to bypass this shortcoming, presenting an approach to gather as much data as possible to enable design understanding techniques for SystemC.

The remainder of this chapter gives an overview of existing approaches to the extraction of SystemC features in Section 3.1, introduces a novel and unintrusive approach in Section 3.2 and gives details about its implementation in Sections 3.3 and 3.4 before concluding in Section 3.5.

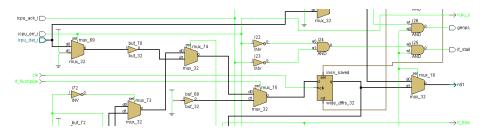

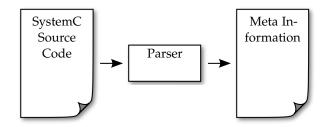

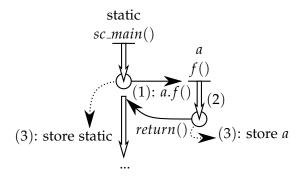

Figure 7: Parsing SystemC

## STATE OF THE ART

Due to the lack of native support for reflection and introspection, researchers developed several approaches concerning the extraction of information from a given SystemC design.

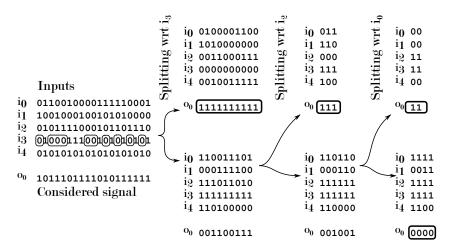

A common approach to the extraction issue was to parse the given SystemC source code in order to extract the needed information. Figure 7 illustrates the corresponding procedure: As the source code does not have to be executed, the analysis builds a model from reading the source code alone. Several dedicated SystemC parsers have been implemented, most of them being open and available for usage.

Approaches using parsers to extract SystemC design information

- ParSyC [31] is a SystemC parser based on the Purdue Compiler Construction Tool Set (PCCTS) [85], the predecessor to ANother Tool for Language Recognition (ANTLR) [84]. ParSyC has been developed at the University of Bremen, the source code has not been released publicly yet. ParSyC translates the SystemC description into an Abstract Syntax Tree (AST), builds an intermediate representation from this AST which can be checked for semantic consistency and finally synthesizes this intermediate result to a netlist. This last step limits the parser to a synthesizeable subset of C++/SystemC, limiting the available code elements to the intersection of the C++ constructs the parser can understand and those that can be synthesized.

- The Karlsruhe SystemC Parser Suite (KaSCPar) [48] is another SystemC parser, created using the Java Compiler Compiler (JavaCC) and the according preprocessor *JJTree*. As being a user-created parser for SystemC/C++, it has the same problems as ParSyC concerning portability: KaSCPar does not support the whole C++ standard, so compiler-specific additions to the standard library are usually unsupported. The same is true for libraries or anything else that does not have its source code embedded into the project. This renders several patterns for SystemC development unavailable.

- SystemC to Verilog Synthesizable Subset Translator (sc2v) [14] is a tool that does not primarily analyse a SystemC design but focuses

on the translation from SystemC to Verilog, but as a detailed SystemC analysis is a prerequisite to properly translate a given design to Verilog, it fits well into this list. As the primary purpose of this tool is the translation into Verilog, it limits itself to the analysis of a synthesizeable subset of SystemC. While this is a reasonable decision for a translation tool, it is limiting the analysis capabilities.

- SystemCXML [4] uses doxygen [114] as a foundation for its code analysis. Using an existing solution instead of writing a custom C++ parser certainly helps this approach in the analysis process as C++ constructs are not as limited as a custom solution (that may be incomplete). However, SystemCXML is limited to extracting the behavioural properties of the code from the generated doxygen files, basically limiting it to e.g. a list of module instanciations. The interpretation of conditional statements such as loops only results in an according syntax tree. SystemCXML does not generate the according structures, limiting its application to e.g. visualizing the source code instead of the system itself.

- SystemPerl [98] is a collection of Perl scripts that parse SystemC using regular expressions. In order to properly parse the given source code, SystemPerl requires the designer "to provide hints in the program for the preprocessor to identify the constructs to be expanded" [63], meaning that the original source code needs to be modified and prepared for the tool to be able to properly interpret it.

- Another (unnamed) parser, based on using Flex/Bison for lexical and syntactical analysis was introduced in [11]. This tool relies on processing the code with a C parser after its analysis though, which will make it difficult to adopt it to handling the full C++ language.

- Scoot [8] focuses on generating a formal model from SystemC designs. Just like the other parsers, it relies on a purely static analysis of a given design. In order to make the parsing process more feasible, scoot requires the usage of a customized collection of SystemC header files, which "declare only relevant aspects of the API" [8]. Scoot also uses a modified scheduler which performs better than the standard scheduler that comes with the SystemC kernel. Interestingly, it also provides a way to translate the analysed design back into a C++ project that does not depend on the SystemC library anymore, resulting (together with the scheduler modifications) in a better simulation performance. However, as scoot has certain limitations concerning the available language constructs and even modifies the SystemC kernel, utilizing it for an existing

project may require some heavy refactoring of the given source code, which might not always be possible.

All these parsers have in common that, by definition, they parse the source code and use this result to extract the system that was described in there.

Advantages of parsers

The advantage of this approach is that the whole analysis process remains in the hand of a single tool. Also, the static approach keeps the architecture simple as no further execution of a given design is needed in order to extract a synthesizeable description.

Limitations of parsers.

However, while the static parsing approach works well for designs that describe one single, static system, this approach has some serious drawbacks when it comes to more dynamic structures. Parsers, by definition, do not execute a given system. This quickly becomes a problem when taking SystemC's notion of design setup into account where the design itself is created by executing the according C++ code during the elaboration phase. Structures may be created by simply lining up calls to module constructors which can easily be parsed. However, elaborate designs can be realized by creating structures in loops or recursions, creating lots of instances with just a few lines of code. Creation can also be nested, with submodules being created within other modules, maybe even hidden within macros or other code elements that may or may not be active depending on how the compiler's preprocessor modifies the code. A design may even be created using e.g. user-defined input values, letting the designer specify e.g. the number of cores of a simulated CPU or the amount of cache available to a system before running the previously compiled executable file. Naturally, parsers are unable to retrieve the correct design in this case.

Overall, parsers have serious issues when it comes to analysing complex designs. At least the elaboration phase needs to be executed in order to extract a particular system design from a SystemC implementation.

Hybrid approaches

Hybrid approaches expand the parsing approach to extract a SystemC design from its source code. First, just like the parsers discussed above, they apply a static analysis of the source code to extract e.g. the structure of a given module. Second, however, they solve the problem of analysing the system's elaboration phase by executing the program at least until the start of the simulation.

However, while the general idea of this approach seems straightforward, extracting information about the structures inside a running C++ program is not easy. Compilers usually discard all the information that is not needed to execute a given program. This includes information about the created objects and their structure – in order to execute a C++ program, the program itself does not need the information that an object contains a field called m\_internal\_state, it just needs to know that

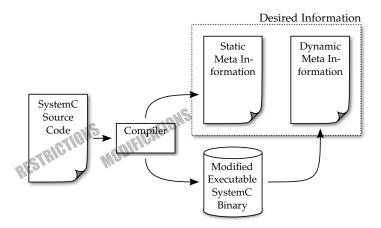

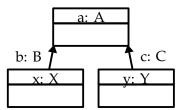

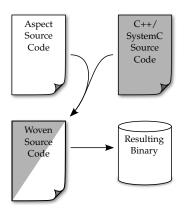

Figure 8: Hybrid approaches

a value at address n needs to be changed, even disregarding the value's type.

As the compiler removes the unnecessary information during compilation, it is the one element in the workflow that has access to the information in the first place. Hybrid approaches use this fact to extract the needed data before it is discarded by the compiler by modifying the compilation workflow in a way that lets them extract the information or prevent it from being removed in the first place. Basically, the idea is simple: If the compiler gets rid of the information that is needed, it needs to be modified not to do this anymore.

The compiler needs to analyse the program's static structure anyway in order to compile it. This means that any structural information about the source code is present in the compiler and just needs to be extracted. Any constructs that are usually hard to parse (such as preprocessor directives) have been properly processed by the time the compiler has analysed the program structure. Problems therefore either do not arise from the language constructs being used or would also lead to compilation problems when trying to compile the program in order to simulate the system.

The dynamic information (e.g. what modules have been created in the elaboration phase) cannot be extracted at compile-time as the elaboration phase needs to be executed for this information to be present at all. However, as the compiler is the one that translates the program into an executable binary, it can just as well modify this binary to track and later store the information about the system being set up.

Figure 8 shows how this static analysis of the program's source code combined with the ability to track the dynamic creation of objects at runtime by modifying the resulting binary file results in a detailed model of the given design. First, the SystemC source code is processed by the compiler. Usually, this compiler would just translate the code into an

Separation of static and dynamic information extraction executable file that could then be run. However, the compiler may be configured or altered to emit and store intermediate results of processing the code. The results of this static code analysis (i.e. the static meta information) are the first part of the information needed to retrieve the information present in a SystemC design. Second, the executable file the compiler builds is modified in order to emit and store information that is crucial for retrieving the structures from the running application that cannot be retrieved statically. These two sets of retrieved information represent a model of the design, which is the information that was desired in the first place. There are a few implementations that follow this idea:

Hybrid extraction approaches

- Pinapa [77] relies on the GNU Compiler Collection (gcc) to analyse SystemC designs. The main advantage of the approach taken is that the limitations of traditional parsers using their own C++ grammar are overcome by utilizing an off-the-shelf front end instead. This idea, combined with the approach of executing the compiled elaboration phase to retrieve the dynamic instances that describe the actual system, makes Pinapa a much more robust tool than the parsing approaches outlined above. However, in order to extract the data, it uses a "slightly modified version of SystemC" and requires "a patch to the GNU C++ compiler" [78]. As both, the SystemC kernel and the compiler need to be modified for Pinapa to work, this solution is not portable: projects either need to use the given compiler or are simply unsupported. The SystemC kernel modifications restrict projects to the SystemC reference implementation and even then problems may arise if the given project needed some modifications to the given SystemC kernel by itself, requiring the two SystemC kernels to be merged. Also, as SystemC itself may be updated, this approach requires a constant maintenance to keep up with the changes of the underlying SystemC library.

- A development that improves the approach taken by ParSyC with a dynamic execution of the elaboration phase was also suggested [36]. While this approach solves the parser's problem of not being able to fully extract the elaboration phase's result, the issue of relying on custom parsers for the code interpretation is still present in this approach. Unlike the other dynamic approaches, it does not use an off-the-shelf front end for C++, thus limiting the available language features which in turn might result in the need for serious re-writing of the code.

- PinaVM [62] is the successor of Pinapa. Instead of using a patched gcc, PinaVM relies on using the LLVM compiler framework via its Application Programming Interface (API). Instead of using e.g. a modified version of gcc (like Pinapa), PinaVM relies on using

LLVM like a library to handle the given code base. While this has the advantage of being more compatible with version changes ("Although its API is not fully stable, it is clean, and the migration from a version of LLVM to another is a painless task" [62]), it comes at the price of being dependent on what this API offers. As a result of working on LLVM, PinaVM heavily relies on handling the intermediate representation LLVM builds from the source code, the so-called bitcode. This assembler-like language is much less abstract than the original C++ code, resulting in each original statement usually being translated into several new statements, which makes the mapping from the used representation to the original source code a non-trivial task. Also, PinaVM, just like Pinapa and SHaBE (see below) relies on one single front end. As the method itself cannot be transferred to other front ends, this makes this a powerful but restricted solution: projects that use code that are incompatible to LLVM are not supported by PinaVM either.

- SystemC Hierarchy and Behavior Extractor (SHaBE) [12] uses a different approach that relies on a debugger instead. While both, Pinapa and PinaVM are modifying the compilation process itself, SHaBE instead uses a combination of the gcc and the corresponding GNU Debugger (gdb), utilizing the latter to stop the execution of a running SystemC program and extract the dynamic information from the debugger. Using a predefined set of breakpoints, SHaBE tracks e.g. the creation of SystemC modules by stopping the execution in the constructor of the sc\_module class and inspecting the call stack to get the inheritance hierarchy. At this point, an object's fields can also be retrieved, allowing SHaBE to also extract an object's static features. To retrieve information about the system's behaviour, SHaBE goes a way similar to Pinapa. It hooks into the compiler to retrieve the program's abstract syntax tree, which contains detailed information about the system's functions and their interaction. Instead of modifying the gcc, a plugin is used though, allowing SHaBE to be more robust concerning changes of the underlying compiler, assuming that the plugin API does not change frequently. Just like Pinapa and PinaVM, this ties this approach to one specific compiler though. Not only is the plugin written for gcc but other compilers simply do not offer a corresponding architecture. Thus, this approach is not portable and relies heavily on the project being interoperable with the chosen architecture. This even excludes projects that rely on workflows based on older versions of the gcc, with the plugin API being a rather recent addition to the project.

- Another approach that uses a debugger is presented in [93]. Although the focus of this approach lies on the actual debugging of

the system, it still handles the same issues to inspect the system in the first place (i.e. the extraction of the given system's properties). Like SHaBE, this approach uses gdb to extract the data from the running program and therefore suffers the same lock-in issues as the former. While this tool comes with its own visualization to control the debugging environment, it is using a proprietary engine by Concept Engineering (a company based in Freiburg) to do so, thus limiting the availability of the system.

While these approaches differ slightly, they share the same features of a dynamic extraction.

Basically, the idea that a compiler has access to all structures and can be used to modify the output in any way is sound. A design that is handled using either of these tools can be analysed well: both, static and dynamic structures are accessible to the tool and may be extracted, so the output of these methods is thorough.

However, this information retrieval approach does still come with a trade-off. The solutions are tightly intertwined with the compiler that they are based on. Either because the compiler itself is modified (as in Pinapa [77]) or because a plugin specific to that compiler needs to be used during compilation (as in SHaBE [12]). This implies that no other setup may be used in order for the respective implementation to be applied.

The impact of this fact differs depending on the code base. Projects that strictly stick to the C++ standard [81] should be portable enough. As the build process differs from compiler to compiler, setting up the build environment for a new compiler is usually a cumbersome but still manageable task.

However, C++ comes with dialects and libraries that are not standardized and which jeopardize the application of this approach in other build environments. Different environments have access to different libraries and tools. Microsoft e.g. offers several extensions to the standard C++ library that cannot simply be ported to other build environments [73]. The problem of dialects even exists within the same environment: updating a compiler may break the compilation for some source constructs.

This is a problem for this approach, as the number of available compilers is currently limited to those that can be modified through plug-ins or source modifications, with closed-source compilers probably remaining unsupported due to the missing ability to add features at will. The solution to port an existing project to a supported build environment implies that a potentially large part of the code base needs to be rewritten. This is a time-consuming and therefore expensive task that should be avoided if possible, especially considering that data extraction methods are usually supposed to assist the designer instead of causing him even more work.

Hybrid approaches are tightly linked to a specific compiler

> Language dialects therefore are an issue

The hybrid approach therefore comes with the most promising, yet also quite limiting notion of either supporting a given SystemC project and being able to export the full design down to the abstract syntax tree or not supporting it at all.

Overall, existing approaches either suffer from

- being focused on static aspects only,

- the need to use a customized adaption of SystemC and, therefore, an inapplicability e.g. for future releases of SystemC and/or combination with other methods that modify SystemC as well, or

- a dependency on customized compilers and/or parsers which limits the usable language constructs.

## DEBUG SYMBOL PARSING

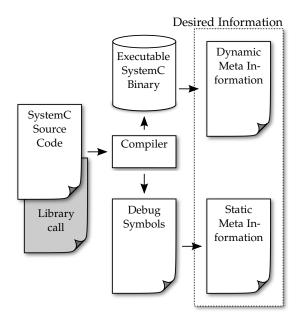

In order to address the research question, the data and interfaces that are available in SystemC/C++ designs are exerted as much as possible. In particular,

- debug symbols (that are generated by practically all compilers, albeit using differing standards) from which relevant (static) information of the considered design can be obtained and

- the SystemC API that allows for an extraction e.g. of values from data-structures during the execution of a program

## are being used.

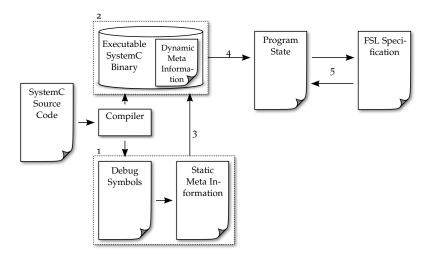

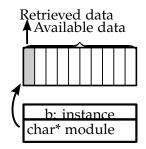

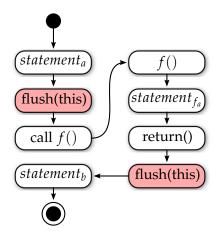

In this Section, an approach is proposed which exploits these existing interfaces for a generic and flexible information extraction of SystemC designs. More precisely, the debug symbols that are generated during compilation anyway are used to extract the static meta information of SystemC programs. Following this approach, modifying a compiler (e.g. to dump the accumulated information) can be avoided as the desired information can also be extracted from these symbols. Figure 9 illustrates the proposed workflow.

Dynamic information can obviously be retrieved only during the execution of a program as some values might not be known at compile-time. But instead of trying to retrieve this information by modifying the given design (e.g. to dump values currently assigned to signals) or by deduction from the static information, the existing infrastructure is used. In fact, the SystemC API is exploited to extract the desired information during run-time, making the solution for dynamic extraction independent from the platform or the compiler being used.

Instead of modifying the compiler and working with a binary extended by additional information needed for data extraction only, the

Figure 9: The SystemC build process.

existing data structures and interfaces are exploited (namely the debug symbols and the SystemC API). By relying on this existing infrastructure, the proposed solution is flexible, quite independent from compiler versions, and fully supports the whole range of SystemC.

In the next section, the proposed approach is described in detail. Two different modules implement the ideas proposed above: The first module reads the compiler-generated debug symbols and extracts static information of the design from it. The second module is a C++ library which can be called during run-time to export SystemC objects that are currently residing in memory. This allows for an extraction of the dynamic information. Afterwards, the extracted dynamic information is matched with its static counterpart.

## EXTRACTION OF STATIC INFORMATION VIA DEBUG SYMBOLS

Existing approaches for the extraction of static information rely on parsing the code using a custom program or interpreting the intermediate language of a given compiler. In the proposed solution, debug symbols of the compiled program are exploited instead. Such debug symbols are created by almost every modern compiler and contain meta information of the code. This data is usually used to aid the designer in developing and debugging his/her implementation. For this purpose, the compilers collect and build extensive data about the program which, after the compilation, is written to the disk so that the debugger can use

```

.stabs "fullAdder: Tt(0,4872)=s5332!1,020,(0,1927);a:(0,1979),736,448;b

:(0,1979),1184,448;carryIn:(0,1979),1632,448;result:(0,3933),2080,480;carryOut:(0,3933),2560,480; ...

```

Figure 10: Debug symbols in the STABS format

them. However, in a similar fashion, the desired static information can be extracted from these symbols.

**Example 2** Figure 10 shows some debug symbols in the STABS format as they have been generated by the GNU compiler using the example program introduced in Figure 6. As can been seen, relevant static information of the design (e.g. the fullAdder class and its fields) can be recognized. This kind of information is available to a very deep level, including access modifiers of fields, a function's lines in the source code, function parameter types, base class information, size of types, etc. Furthermore, many debug symbols are arranged in a hierarchical manner, i.e. a debug symbol may be composed of several subsymbols.

The information available through these debug symbols can be exploited to extract the desired static information of a given system.

Two tools have been developed to illustrate how the debug symbols can serve as a source of information:

The first tool uses the Microsoft VC++ compiler and the *Program Database*-files (PDB-files) generated by it [72]. Although the format itself is proprietary, using the *Debug Interface Access* (DIA) SDK [71], the debug symbols that are collected in those files can be accessed.

The second tool is based on the DWARF debug symbols [27] and the libdwarf/dwarfdump tools to read them. These open tools provide a more streamlined access to the DWARF debug symbols that can be generated by both, gcc [101] and clang [53]. More specifically, the output generated by dwarfdump is passed on to the tool that translates the structures into the needed format.

Using these tools, the data from debug symbols can be obtained on all platforms and all major compilers. To the best of my knowledge, there is no compiler that does not generate the needed information in the form of debug symbols and stores them for later usage, making this approach unversally applicable.

Figure 11 shows the procedure of the extraction for the Microsoft data. Given a PDB-file created by the VC++ compiler from a SystemC design, all topmost debug symbols are loaded first (line 2). Afterwards, each symbol is separately considered and analyzed (lines 3-5). The desired information is thereby dumped into an XML-data structure representing the static information of the system. Since the debug symbols are hierarchically structured, the analysis is recursively conducted through the function *analyzeSymbol* (line 8). Here, all the desired information of the

Reading debug data files

```

function analyzeDebugData(filename) begin

symbolTable = loadDataFromDebugFile(filename)

2

for each symbol in symbolTable

3

analyzeSymbol(symbol)

4

end for

end function

6

7

8

function analyzeSymbol(currentSymbol) begin

dumpAllData(currentSymbol)

9

if currentSymbol has typeInformation then

10

analyzeSymbol(typeInformation)

11

end if

12

if currentSymbol has subSymbols AND

13

14

currentSymbol is NOT baseClass AND

currentSymbol is NOT typedef then

15

16

for each subsymbol in subsymbols

17

analyzeSymbol(subsymbol)

18

19

end if

end function

20

```

Figure 11: Pseudo code of debug information extraction

currently considered debug symbol are dumped to the XML-data structure first (line 9). Afterwards, it is checked whether further hierarchical information is available (lines 10-19). If this is the case, the corresponding sub-symbols are analyzed by recursively calling *analyzeSymbol* for them. To avoid redundancies, lines 14 and 15 stop the recursion if types are found that are also part of the *symbolTable* and would otherwise be extracted several times.

**Example 3** Consider again the SystemC code from Figure 6 to be analyzed. Using the PDB-file generated by the VC++ compiler, the analysis of the first debug symbol (line 8) results in an XML-tag like

```

<userDefinedType name="fullAdder" addressOffset="o"

addressSection="o" constType="o" length="428">

```

stating that the considered system contains the class fullAdder (an instance of which occupies 428 bytes in memory). More information about this class can be gained by the analysis of the corresponding sub-symbols through the recursive calls (line 10-18). One of the fullAdder class's sub-symbols contains e.g. information about its field "a" (i.e. the full adder's first input bit):

```

<data name="a" [...] >

<type>

<userDefinedType name="sc_core::sc_in\&lt;bool\&gt;"}[...] >

```

Note the field's name ("a") and the field's type (sc\_core::sc\_in<bool> with "<" being replaced by "&lt;" and ">" by "&gt;" respectively to keep the XML structure valid) in the description. This information is contained in its own debug symbol that is part of the former symbol. The hierarchy is encompassed by the recursion. More information could be gained by searching for the description of the given type itself. Other sub-symbols provide information e.g. on inheritance, functions, their parameters, etc.

The DWARF format, on the other hand, does not need the recursion step that is required for the PDB file analysis (and shown in Figure 11). Where the interface to read the PDB data is handing out references to a given sub-symbol, the DWARF data is rather flat, with links between symbols being stored in the form of unique identifiers that can just be ported either as such or in the form of target names.

Using any of these procedures allows for an exploitation of debug symbols, which are generated anyway, for the purpose of static information extraction. Compared to previously proposed solutions with their respective constraints and requirements, this results in a near-to-none setup as all the information is retrieved from existing compilers and tools. The whole extraction step can be embedded transparently into the compilation workflow and does not require any human interaction after its initial setup.

While the advantages of this method (being applicable to any setup, being portable to any platform and being usable, as it doesn't require any interaction beyond the initial setup) are clear, it is limited to the information that is stored by the compiler in the debug symbols. This means that usually, the static information does not contain the full abstract syntax tree. In most cases, the information is structural only, meaning that e.g. the information that a certain class has a function is stored but not the contents of said function.

This means that the advantages come with a price tag and the retrieved information, while being vast, is not complete. In the end, this is a tradeoff that the designer needs to consider when chosing a method to analyse SystemC code.

Especially for the use case of Design Understanding, the advantages of the proposed approach far outweigh the information that cannot be retrieved though. As this use case does not require complete information but has its focus on the quick and simple retrieval of more abstract information present in a design, this new approach suits this aim well by being simple and unversal to apply. Basically, the usability is the point the given approach excels in, as the required steps to use it are kept to a minimum, making it suitable for a quick glance into a given system on a more abstract level than the source code could provide.

## EXTRACTION OF DYNAMIC INFORMATION

The SystemC library comes with an API that provides not only means of virtually creating and simulating systems, but also allows for accessing and inspecting the created instances of a system during run-time. That is, SystemC itself is, in principle, able to deliver an overview of the dynamic information of the instantiated system. Existing approaches exploiting this API for the extraction of dynamic information still rely on

**Applicability**

Limited to the information the compiler stores

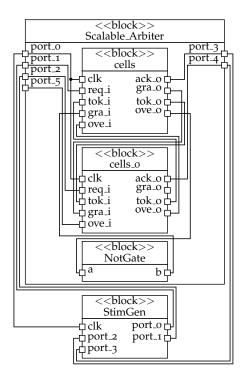

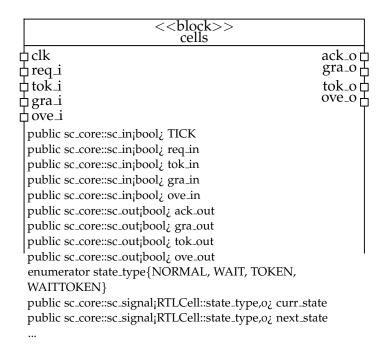

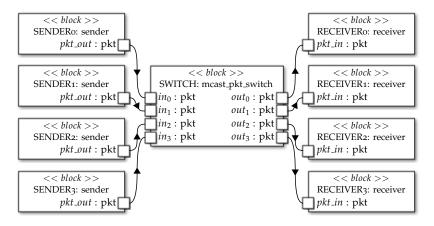

Figure 12: Diagram extracted using the SystemC API from the arbiter example [23].

modifying the SystemC library [40] and, hence, only provide a limited and restricted solution.

The proposed solution requires as few changes as possible to the existing setups by performing the following steps each time dynamic information should be retrieved:

ACCESSING THE INSTANTIATED **OBJECTS** The SystemC API provides a function to get access to the simulation context (via sc\_get\_curr\_simcontext()) through which an object\_manager instance can be retrieved (via context->get\_object\_manager()). The object\_manager in turn provides access to all instantiated SystemC-objects that are being used in the current run of the SystemC program. This means that objects that do not implement the sc\_object class (and are thus not managed by the SystemC simulation kernel) cannot be retrieved via this method, but all objects that are functioning as stand-ins e.g. for a hardware module or a signal can be. Extracting the objects that are available using this method returns the information illustrated in Figure 12: Instanciated modules, their ports and signals are all retrieved.

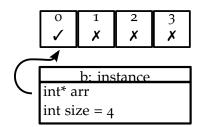

NAMING THE RETRIEVED OBJECTS To name the retrieved objects, [40] named the instances based on the fields' names. That is, an object created by the SystemC line fullAdder faField("faName")

would be named *faField*. While this approach seems obvious at first sight, this leads to serious problems as

- field names may be used more than once (at different locations in the program) and

- a single instance may be assigned to several fields and, hence, a single instance might be referred to by several different field names.