#### UNIVERSIDADE ESTADUAL DE CAMPINAS

#### FACULDADE DE ENGENHARIA MECÂNICA

**Augusto Yoshio Horita**

# Automation Approaches for Embedded Systems Design Flows Based on Formal Models of Computation

Estratégias de Automação para Desenvolvimento de Projetos de Sistemas Embarcados Baseados em Modelos Formais de Computação

#### Augusto Yoshio Horita

# Automation Approaches for Embedded Systems Design Flows Based on Formal Models of Computation

# Estratégias de Automação para Desenvolvimento de Projetos de Sistemas Embarcados Baseados em Modelos Formais de Computação

Dissertation presented to the School of Mechanical Engineering of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Mechanical Engineering, in the area of Mechatronics.

Dissertação apresentada à Faculdade de Engenharia Mecânica da Universidade Estadual de Campinas como parte dos requisitos exigidos para obtenção do título de Mestre em Engenharia Mecânica, na Área de Mecatrônica.

Orientador: Prof. Dr. Denis Silva Loubach

ESTE EXEMPLAR CORRESPONDE À VERSÃO FINAL DA DISSERTAÇÃO DEFENDIDA PELO ALUNO AUGUSTO YOSHIO HORITA, E ORIENTADA PELO PROF. DR. DENIS SILVA LOUBACH.

#### Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Rose Meire da Silva - CRB 8/5974

Horita, Augusto Yoshio, 1987-

H782a

Automation approaches for embedded systems design flows based on formal models of computation / Augusto Yoshio Horita. - Campinas, SP: [s.n.], 2019.

Orientador: Denis SIIva Loubach.

Dissertação (mestrado) – Universidade Estadual de Campinas, Faculdade de Engenharia Mecânica.

1. Sistemas embarcados (Computadores). 2. Computabilidade e modelos de computação. I. Loubach, Denis Silva, 1982-. II. Universidade Estadual de Campinas. Faculdade de Engenharia Mecânica. III. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: Estratégias de automação para desenvolvimento de projetos de sistemas embarcados baseados em modelos formais de computação

#### Palavras-chave em inglês:

Embedded systems (Computers)

Computability and models of computation

Área de concentração: Mecatrônica

Titulação: Mestre em Engenharia Mecânica

Banca examinadora: Denis Silva Loubach

Eurípedes Guilherme de Oliveira Nóbrega

Romis Ribeiro de Faissol Attux Data de defesa: 17-10-2019

Programa de Pós-Graduação: Engenharia Mecânica

Identificação e informações acadêmicas do(a) aluno(a)

- ORCID do autor: https://orcid.org/0000-0003-2805-8530

Currículo Lattes do autor: http://lattes.cnpq.br/1738569966447609

# UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA DEPARTAMENTO DE MECÂNICA COMPUTACIONAL

### DISSERTAÇÃO DE MESTRADO ACADÊMICO

# Automation Approaches for Embedded Systems Design Flows Based on Formal Models of Computation

# Estratégias de Automação para Desenvolvimento de Projetos de Sistemas Embarcados Baseados em Modelos Formais de Computação

Autor: Augusto Yoshio Horita

Orientador: Prof. Dr. Denis Silva Loubach

A banca examinadora composta pelos membros abaixo aprovou esta dissertação:

Prof. Dr. Denis Silva Loubach, Presidente Departamento de Sistemas de Computação/ITA

Prof. Dr. Eurípedes Guilherme de Oliveira Nóbrega FEM/Unicamp

Prof. Dr. Romis Ribeiro de Faissol Attux FEEC/Unicamp

A Ata da defesa com as respectivas assinaturas dos membros encontra-se no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

This work is dedicated to my wife and kids, who have inspired and supported me.

#### Acknowledgements

First, I thank God for all the blessings I have got, including wonderful people around me, besides the opportunities and virtues I was given to which made this work possible.

I thank Prof. Dr. Denis Silva Loubach, who has always been attentive and patient with my difficulties, giving me all the support and sharing his expertise that led me to finish this work. Besides, I thank Ricardo Bonna for promptly sharing his knowledge whenever I needed.

I thank Unicamp for affording me the opportunity to complete my MSc. study here. I thank my parents, brother and sister, who are part of my being, teaching me how to be better and never give up.

I deeply thank my wife, for always giving me the necessary support and being by my side. I thank my children for giving me the inspiration to be a better person.

I humbly extend my thanks to all my friends and persons who co-operated in any manner with me in this work.

#### Resumo

Sistemas embarcados de alta performance estão presentes em cada vez mais áreas de aplicação. Com o aumento da complexidade, se torna mais difícil atender ao requisito de se projetar o sistema mais otimizado utilizando menos recursos. Nesse contexto, os métodos de projeto de sistemas embarcados baseados em modelos formais têm sido estudados para tornar esse processo mais robusto e escalável. O uso de modelos de computação (MoC), que consistem na modelagem de uma aplicação utilizando um alto nível de abstração com base formal, possibilita uma análise sistemática do sistema antes de sua implementação. Ferramentas e frameworks têm sido desenvolvidos para a modelagem baseada em MoCs. Algumas dessas ferramentas suportam a simulação dos modelos, possibilitando a verificação das funcionalidades do sistema antes das próximas fases do projeto. O aumento do nível de abstração, proporcionado pelo uso dos MoCs, dificulta a fase de implementação pela falta de detalhes nos modelos de alto nível de abstração. Nesse sentido, esta pesquisa tem como objetivo identificar possíveis estratégias de automação para o desenvolvimento de sistemas embarcados baseado em modelos formais de computação.

*Palavras-chave*: Sistemas embarcados, Modelos de computação, Projeto baseado em modelos formais, Modelagem, Simulação, Programação funcional.

#### **Abstract**

Sophisticated and high performance embedded systems are present in an increasing number of application domains. As the complexity grows, it gets harder to satisfy the requirement of getting the most optimized system using less development resources. In this context, formal-based design methods have been studied to make the development process robust and scalable, using the correct-by-construction approach. Models of computation (MoC), which consists on modeling an application at a high abstraction level by using a formal base, enables a system-atic application analysis before its implementation. Different tools and frameworks have been developed supporting MoCs. Some of them can simulate the models and also verify its functionality and feasibility before the next design steps. As MoC elevates the abstraction level, the implementation steps get more complex, creating an abstraction gap. In view of this, the present research aims to identify possible automation approaches for embedded systems design flows.

*Keywords*: Embedded systems, Models of computation, Formal-based design flow, Modeling, Simulation, Functional programming.

# **List of Figures**

| 1.1  | Synthesis process from specification model to system implementation (Sander,                                                                                                                                                                                                                                           |    |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|      | 2003)                                                                                                                                                                                                                                                                                                                  | 17 |  |

| 2.1  | A possible CPS structure (Lee, 2010)                                                                                                                                                                                                                                                                                   | 21 |  |

| 2.2  | SY process representation, adapted from (Jantsch, 2003)                                                                                                                                                                                                                                                                | 23 |  |

| 2.3  | SDF example, adapted from (Lee and Messerschmitt, 1987)                                                                                                                                                                                                                                                                | 24 |  |

| 2.4  | Modal model example                                                                                                                                                                                                                                                                                                    | 25 |  |

| 2.5  | $\rm H.263$ encoder graph generated and visualized with $\rm SDF^3$ (Stuijk, 2018)                                                                                                                                                                                                                                     | 26 |  |

| 2.6  | ForSyDe Design Process (Sander, 2003)                                                                                                                                                                                                                                                                                  | 28 |  |

| 2.7  | PtolemyII architecture based on (Ptolemaeus, 2014)                                                                                                                                                                                                                                                                     | 28 |  |

| 2.8  | Process built by a Process Constructor (Sander et al., 2016)                                                                                                                                                                                                                                                           | 30 |  |

| 2.9  | ForSyDe models of computation                                                                                                                                                                                                                                                                                          | 31 |  |

| 2.10 | MoCs Chart, according to (University of California, Berkeley-online, 2018)                                                                                                                                                                                                                                             | 32 |  |

| 2.11 | Compiler architecture based on (Bourke et al., 2015)                                                                                                                                                                                                                                                                   | 36 |  |

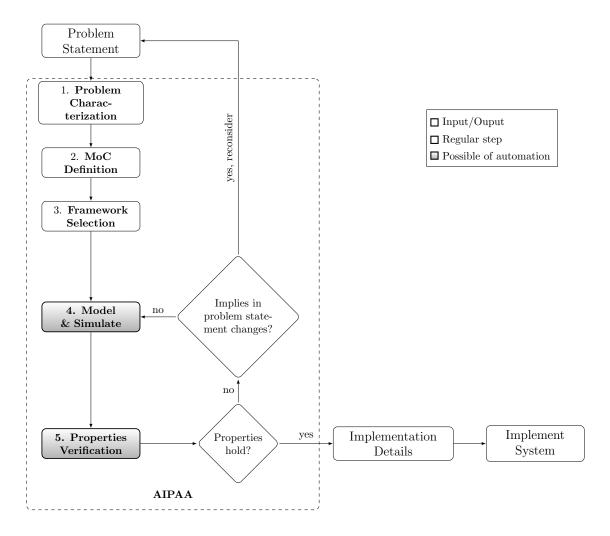

| 3.1  | Analysis and identification of possible automation approaches (AIPAA) applicable to embedded systems design flow. AIPAA needs the "problem statement" as a given input, and aids to produce a model, which is verified and executable, as output. This output can be used as entry point in the implementation domain, |    |  |

|      | e.g., "implementation details" and "implement system"                                                                                                                                                                                                                                                                  | 40 |  |

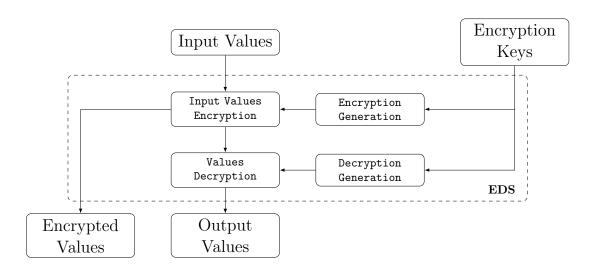

| 3.2  | EDS system flow chart                                                                                                                                                                                                                                                                                                  | 51 |  |

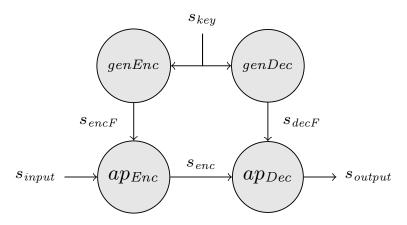

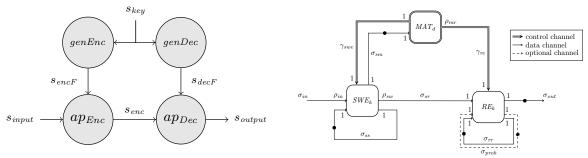

| 3.3  | Encoder-decoder system SY graph                                                                                                                                                                                                                                                                                        | 53 |  |

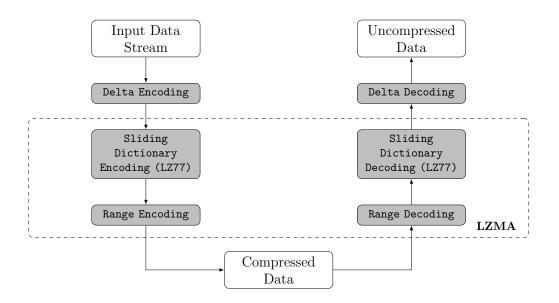

| 4.1  | LZMA compression and decompression schemes, based on (Leavline, 2013)                                                                                                                                                                                                                                                  | 59 |  |

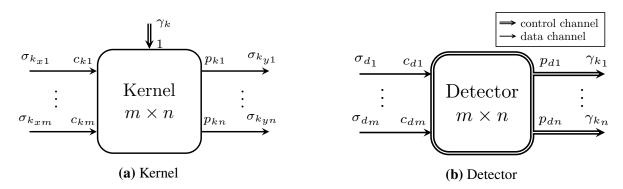

| 4.2  | SADF actor types, both with m inputs and n outputs (Bonna et al., 2019)                                                                                                                                                                                                                                                | 62 |  |

| 4.3  | LZMA high level modeling dataflow graph based on SADF MoC. Initial tokens                                                                                                                                                                                                                                              |    |  |

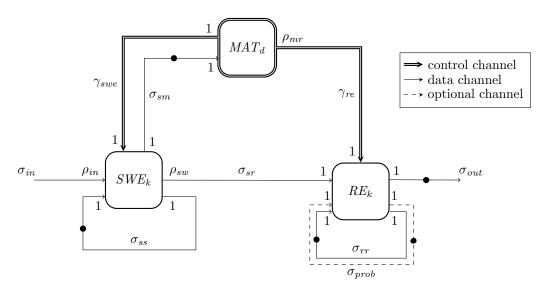

|      | are represented by •                                                                                                                                                                                                                                                                                                   | 64 |  |

| 5 1  | Formal-based models dataflow graphs                                                                                                                                                                                                                                                                                    | 70 |  |

# **List of Tables**

| 2.1 | Functional and Imperative Paradigms Comparison (Moraes and Loubach, 2017). |    |

|-----|----------------------------------------------------------------------------|----|

|     |                                                                            | 35 |

| 4.1 | Sliding Window Encoding Output Packages, based on source code (Pavlov,     |    |

|     | 2019). The symbol $\oplus$ represents concatenation of binary values       | 61 |

| 4.2 | $\sigma_{sr}$ possible token formats                                       | 66 |

| 4.3 | <i>l</i> variable possible sizes                                           | 66 |

| 4.4 | $SWE_k$ Scenarios and token rates discrimination                           | 66 |

| 4.5 | $MAT_d$ output control channels token rates and scenarios discrimination   | 66 |

| 4.6 | Feasible LZMA system static scheduling                                     | 75 |

# List of Symbols and Abbreviations

**AIPAA** Analysis and Identification of Possible Automation Approaches

ALU Arithmetic Logic Unit

**ARM** Advanced RISC Machine

**CPS** Cyber-Physical Systems

**CSDF** Cycle-Static Dataflow

**CSP** Communicationg Sequential Processes

**CT** Continuous Time

**DSL** Domain Specific Language

**EDS** Encoder-Decoder System

**EDSL** Embedded DSL

ForSyDe Formal System Design

**FPGA** Field Programmable Gate Array

**FPU** Floating Point Unit

**FSM** Finite State Machine

**GHC** Glasgow Haskell Compiler

**GHCi** GHC interactive environment

**GPU** Graphics Processing Unit

**GUI** Graphical User Interface

**HDL** Hardware Description Language

iCyPhy Industrial Cyber-Physical Center

**IEEE** Institute of Electrical and Electronics Engineers

**MoC** Model of Computation

MoML Modeling Markup Language

NASA National Aeronautics and Space Administration

**OSMC** Open Source Modelica Consortium

**PASS** Periodic Admissible Sequential Schedule

**R2D2C** Requirements to Design Code

**RISC** Reduced Instruction Set Computer

**SADF** Scenario-Aware Dataflow

**SDK** Software Development Kit

**SDF** Synchronous Dataflow

**SDF3** Synchronous Dataflow For Free

**SOL** Sequential Object Language

**SR** Synchronout Reactive

SY Synchronous

**TSM** Tagged Signal Model

**XML** eXtensible Markup Language

# **Contents**

| 1 | Intro | duction                               | 1                                                                   | 16 |  |

|---|-------|---------------------------------------|---------------------------------------------------------------------|----|--|

|   | 1.1   | Researc                               | ch Objective                                                        | 17 |  |

|   | 1.2   | Researc                               | ch Scope                                                            | 17 |  |

|   | 1.3   | Researc                               | ch Requirements                                                     | 18 |  |

|   | 1.4   | Expecto                               | ed Results                                                          | 18 |  |

|   | 1.5   | Docum                                 | ent Structure                                                       | 19 |  |

| 2 | Back  | ground                                |                                                                     | 20 |  |

|   | 2.1   | 1 Embedded and Cyber-Physical Systems |                                                                     |    |  |

|   | 2.2   | Models                                | of Computation (MoC)                                                | 21 |  |

|   |       | 2.2.1                                 | Tagged Signal Model (TSM)                                           | 21 |  |

|   |       | 2.2.2                                 | Timed Models of Computation                                         | 22 |  |

|   |       | 2.2.3                                 | Untimed Models of Computation                                       | 23 |  |

|   |       | 2.2.4                                 | Hybrid Models                                                       | 25 |  |

|   | 2.3   | Framev                                | vorks supporting formal MoCs                                        | 25 |  |

|   |       | 2.3.1                                 | Formal System Design (ForSyDe)                                      | 27 |  |

|   |       | 2.3.2                                 | PtolemyII                                                           | 27 |  |

|   | 2.4   | MoCs I                                | Perspective under PtolemyII and ForSyDe                             | 29 |  |

|   |       | 2.4.1                                 | ForSyDe Overview                                                    | 29 |  |

|   |       | 2.4.2                                 | PtolemyII Overview                                                  | 31 |  |

|   | 2.5   | Function                              | onal Programming Paradigm                                           | 33 |  |

|   |       | 2.5.1                                 | Haskell Programming Language                                        | 33 |  |

|   | 2.6   | Impera                                | tive Programming Paradigm                                           | 34 |  |

|   |       | 2.6.1                                 | Java Language                                                       | 34 |  |

|   | 2.7   | Straigh                               | tforward Paradigms Comparison                                       | 35 |  |

|   | 2.8   | Propert                               | ies Verification                                                    | 35 |  |

|   | 2.9   |                                       | atic Code Generation                                                | 36 |  |

|   | 2.10  | Main R                                | elated Works                                                        | 37 |  |

|   | 2.11  |                                       | ury                                                                 | 38 |  |

| 3 | A M   | ethod fo                              | or Possible Automation Exposure                                     | 39 |  |

|   | 3.1   |                                       | is and Identification of Possible Automation Approaches - The AIPAA |    |  |

|   |       | •                                     | 1                                                                   | 39 |  |

|   |     | 3.1.1 Problem Characterization                                       | 40 |

|---|-----|----------------------------------------------------------------------|----|

|   |     | 3.1.2 MoC Definition                                                 | 41 |

|   |     | 3.1.3 Framework Selection                                            | 42 |

|   |     | 3.1.4 Modeling and Simulation                                        | 43 |

|   |     | 3.1.5 Properties Verification                                        | 44 |

|   |     | 3.1.6 Directions to Implementation Details and System Implementation | 47 |

|   | 3.2 | Analysis of Possible Automation Approaches                           | 48 |

|   |     | 3.2.1 Proposed Automation to Properties Verification                 | 48 |

|   |     | 3.2.2 Automatic Code Generation                                      | 50 |

|   | 3.3 | Illustrative Example                                                 | 50 |

|   |     | 3.3.1 Problem Characterization                                       | 51 |

|   |     | 3.3.2 MoC Definition                                                 | 52 |

|   |     | 3.3.3 Framework Selection                                            | 52 |

|   |     | 3.3.4 Modeling and Simulation                                        | 52 |

|   |     | 3.3.5 Properties Verification                                        | 56 |

|   |     | 3.3.6 Implementation Details and Implement System                    | 56 |

|   | 3.4 | Summary                                                              | 57 |

| 4 | AIP | AA Method Application                                                | 58 |

|   | 4.1 | LZMA - The Problem Statement                                         | 58 |

|   | 4.2 | Problem Characterization                                             | 59 |

|   |     | 4.2.1 Sliding Window Encoding                                        | 59 |

|   |     | 4.2.2 Range Encoding                                                 | 60 |

|   | 4.3 | MoC Definition                                                       | 61 |

|   |     | 4.3.1 Scenario-Aware Dataflow (SADF) MoC                             | 62 |

|   | 4.4 | Framework Selection                                                  | 63 |

|   | 4.5 | Modeling and Simulation                                              | 63 |

|   |     | 4.5.1 SADF LZMA Model Description                                    | 64 |

|   |     | 4.5.2 LZMA Modeling with ForSyDe SADF MoC                            | 66 |

|   |     | 4.5.3 Model Simulation                                               | 71 |

|   | 4.6 | Properties Verification                                              | 73 |

|   |     | 4.6.1 SADF MoC Properties and Verification Methods                   | 73 |

|   |     | 4.6.2 LZMA Model Properties Verification                             | 74 |

|   | 4.7 | Implementation Details and Implement System                          | 75 |

|   | 4.8 | Summary                                                              | 76 |

| 5 | Res | ılts, Analysis and Discussion                                        | 77 |

|   | 5.1 | Literature Review                                                    | 77 |

|   | 5.2 | Case Studies Specification                                           | 77 |

|   | 5.3 | Framework Selection Criteria                                         | 78 |

|   | 5.4 | Case Study Modeling Based on Formal Methods     | 78 |

|---|-----|-------------------------------------------------|----|

|   | 5.5 | Analysis Identifying Steps to be Automated      | 79 |

|   |     | 5.5.1 Properties Verification with "Quickcheck" | 79 |

|   |     | 5.5.2 Automatic Code Generation                 | 80 |

|   | 5.6 | Scientific Publications                         | 80 |

|   | 5.7 | Summary                                         | 81 |

| 6 | Con | clusion                                         | 82 |

|   | 6.1 | Specific Conclusions                            | 82 |

|   |     | 6.1.1 Work Requirements Traceability            | 83 |

|   | 6.2 | Main Contributions                              | 83 |

|   | 6.3 | General Conclusions                             | 84 |

|   | 64  | Recommendations and Future Works                | 84 |

#### 1 INTRODUCTION

Embedded systems are present in a growing number of different application areas, which includes a wide complexity range, from simple wearable gadgets to aerospace and biomedical. Power consumption, performance, and cost usually figure as key constraints to these systems. *Real-time embedded systems*, specifically, have as a critical requirement predictable and deterministic response time. A design error in these cases can cost whole projects or even lives (Buttazzo, 2011).

Besides the growing number of embedded systems applications, their integration and connectivity, aiming to improve control and monitoring methods, have created the concept of *cyber-physical systems* (CPS), which represents the integration of computation and physical processes controlled by embedded computers and its networks, generally, by using feedback loops. Therefore, computation and physical systems affect one another (Lee, 2010).

As embedded systems and CPS complexities grow, it gets harder and harder to specify, model and simulate them, therefore making the system implementation phase more complex. In this sense, *formal-based design methods* have been developed to make this process reliable, robust and scalable together with *design space exploration* (DSE).

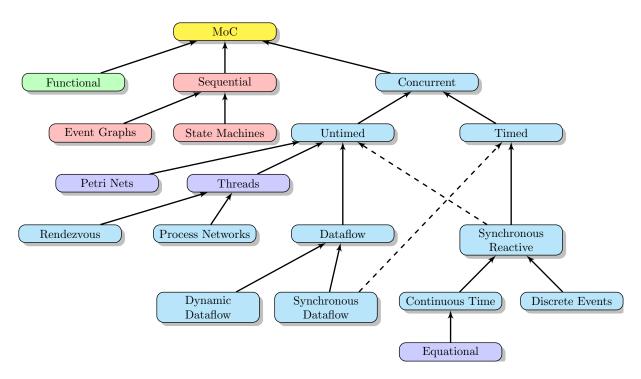

Towards the *correct-by-construction* development, optimizing the available resources, Edwards et al. (1997) argue that systems should be implemented at a high abstraction level, using formal models. This implementation consists on an executable model which makes no references to implementation code or platforms. In this context, *models of computation* (MoC) are presented as a key approach to formal-based system modeling and simulation. There is a range of existing MoCs, some illustrated in Fig. 2.10, where each one represents and captures different aspects and semantics of system's functionalities. Therefore, one should carefully choose the MoC to use based on the type of application being modeled, besides the modeling and simulation methods (Jantsch and Sander, 2005).

Considering the design phase, a range of frameworks were developed aiming to aid the modeling and simulation of systems on a formal base. Examples are Ptolemy II (Ptolemaeus, 2014), ForSyDe (Sander et al., 2016), SDF3 (Stuijk et al., 2006), and Simulink (MathWorks, 2019a). Each framework focuses on different design methodologies aspects and has its own profits and drawbacks when compared to the others.

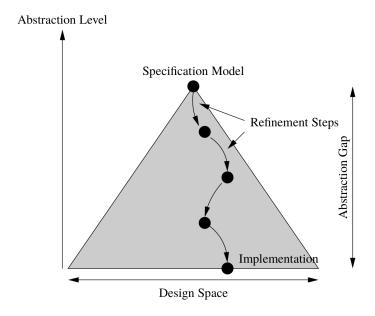

Although formal models with a high abstraction level have advantages, making possible the early detection of inconsistencies and ambiguities in the specification model step, they have a counter-part known as *abstraction gap*, caused by its absence of implementation details. This

leads to a wider *design space* possibilities, defined as the range of implementations options related to the initial model. Fig. 1.1 illustrates the synthesis process and that abstraction gap (Sander, 2003).

**Figure 1.1.** Synthesis process from specification model to system implementation (Sander, 2003).

Research works are continuously presenting methods to optimize and overcome the abstraction gap, composing the *design space exploration* concept (Sinaei and Fatemi, 2016; Li et al., 2017).

# 1.1 Research Objective

This research work objective is to **identify possible automation approaches for design flows based on formal models of computation**, aiming to assist in a *future implementation* of automatic code generation and also a trustable, robust and scalable embedded systems design flow.

# 1.2 Research Scope

The present research considers both the *design* and the *high level implementation*, *i.e.*, in the specification domain, of an embedded system case study, following formal design methods to model and simulate the system.

Basically, two types of MoCs with different timing abstraction, as discussed in (Horita et al., 2019a), are used here. One is the *synchronous* (SY) MoC, representing the timed classification of MoCs, and the other is the *synchronous dataflow* (SDF), representing the untimed. A third MoC, named *scenario-aware dataflow* (SADF) is also addressed in the present work. SADF is a generalization of SDF to model dynamic systems.

Based on the defined high level abstraction models and their simulation and high level implementations, it should be possible to identify which are the main intermediate steps candidate to be automated.

# 1.3 Research Requirements

This research work addresses the following requirements:

- $R_0$  Literature review with respect to the main concepts and theory on MoC and high level modeling;

- $R_1$  Complete specification of embedded systems case studies;

- $R_2$  A formal-based modeling framework selection criteria and list of candidates tools;

- R<sub>3</sub> Embedded system case study modeling and high level implementation, based on formal design methods; and

- $R_4$  An analysis identifying implementation steps to be automated.

# 1.4 Expected Results

The expected results are the formal-based modeling, simulation and high level implementation of case studies. Besides that, this research aims to present an analysis of refinement steps taken during the design space exploration, pointing out possible automation approaches in the design flow, that can be implemented as a future works.

The validation of this research will be based on the verification of the correct manual system implementation, following the selected MoC semantics.

#### 1.5 Document Structure

The remainder of this document is organized as follows. Chapter 2 presents a background on the main concepts used in this work. In Chapter 3, it is described a proposed method for possible automation identification together with an illustrative example. Next, Chapter 4 shows the implementation of a case study based on the introduced method, demonstrating its potential and applicability. Chapter 5 introduces a discussion regarding the case study development and results. Finally, Chapter 6 summarizes the research conclusions, contributions and possible future works.

#### 2 BACKGROUND

This chapter presents the main concepts involved in this research, including embedded and cyber-physical systems, models of computation, functional programming paradigm and automatic code generation, together with related works.

# 2.1 Embedded and Cyber-Physical Systems

Embedded systems can be defined as computing systems designed to perform a dedicated function, in which hardware and software are tightly coupled (Li and Yao, 2003). One of the main components of these systems is the processing unit, *i.e.*, microcontrollers or microprocessors, in which application instructions are executed. As the technology advances, different processor's architectures are developed, optimizing their performance by increasing their capabilities, *e.g.*, runtime reconfiguration, or resources, *e.g.*, multiple processing cores.

Despite those performance improvements, a range of complex applications requires embedded system's networks to monitor and control physical variables or processes based on logical computational algorithms, usually using feedback loops. This intersection of cyber and physical components is named *cyber-physical systems* (CPS). It combines engineering models and methods from mechanical, electrical, and chemical engineering with models and methods from computer science (Lee, 2015). CPS applications include modern transportation systems, security systems, and distributed robotics, for instance.

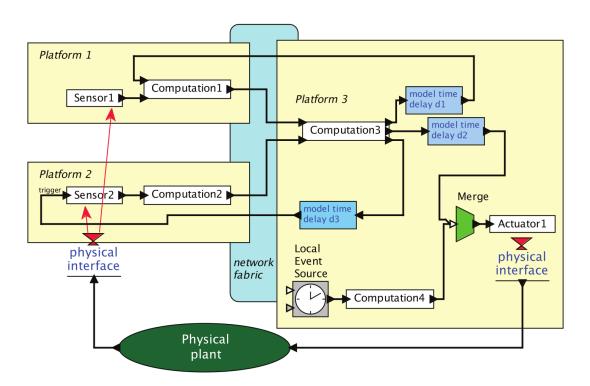

A possible CPS structure is illustrated in Fig. 2.1, representing a network of three platforms composed by actuators, sensors and embedded computers, as *computation* blocks. As an example, (Lee, 2010) describes it as an automation application, in which controllers for high-speed printing presses are modeled as the actuators and sensors represent disruptions detection. The control algorithms, modeled as computation blocks, handle rapid shutdown modes to prevent damage to the equipment in case of paper jams.

As the applications complexity grows, the number of components included in the CPS network and the computational algorithms can exponentially increase. In a scalable perspective, the greater and more complex the CPS gets, the harder it is to specify, simulate and implement these systems. In view of this, formal-based design methodologies are adopted aiming the correct-by-construction development.

Figure 2.1. A possible CPS structure (Lee, 2010).

# **2.2** Models of Computation (MoC)

According to Jantsch (2003), a *model* is a simplification of another entity, which can be a physical entity or even another model. It describes only the characteristics that are relevant for a given task.

In the present research context, formal models of computation (MoCs) are used to model embedded systems. These MoCs elevate the abstraction level of the modeled systems, making no reference to implementation platforms or implementation languages, but capturing functional behaviors regarding communication, synchronization and processes interactions (Fernández, 2009; Jantsch, 2005). Essentially, MoCs are collections of *abstract rules* that dictate the semantics of execution and concurrency in heterogeneous computational systems.

# 2.2.1 Tagged Signal Model (TSM)

As MoCs abstract the system functionality, which are relevant for a specific task, a range of different models have been developed. As a consequence, the selection of a MoC is not a trivial design step. For that reason, many researches have presented different comparison methods and MoC's classification (University of California, Berkeley-online, 2018; Lee and Sangiovanni-

Vincentelli, 1998; Paul and Thomas, 2005).

In this sense, Lee and Sangiovanni-Vincentelli (1998) presented a meta-model/framework named *tagged signal model* (TSM) for reasoning about MoCs definitions and properties. A range of MoCs, studies and frameworks share the main concepts contained in that research work (University of California, Berkeley-online, 2018; Sander, 2002; Jantsch, 2003). Within TSM, systems are regarded as a collection of processes. A process communicates through signals, composed by events, having the following definitions.

**Definition 1 (Event)** An event e, is an elementary unit of information composed by a tag  $t_i \in T$  and a value  $v_i \in V$ .

**Definition 2 (Signal)** A signal s, belonging to the set of signals S, is a set of events  $e_i = (t_i, v_i)$ , responsible for processes communication.

**Definition 3 (Process)** A process P is a set of possible behaviors, and can be viewed as relations between input signals  $S^I$  and output signals  $S^0$ . The set of output signals is given by the intersection between the input signals and the process  $S^0 = S^I \cap P$ . A process is functional when there is a single value mapping  $f: S^I \to S^0$  which describes it. Therefore, a functional process has either one behavior or no behavior at all.

TSM classifies the MoCs within two categories, *timed* and *untimed*, which are described as follows.

### 2.2.2 Timed Models of Computation

In a *timed* MoC, the set of tags *T* is *totally ordered*. For that reason, the tags are also considered the *timestamp* of each event. As a consequence, it is possible to order every event in every signal of the MoC based on its tag. As examples of timed MoCs, TSM presents continuous time, discrete-event, synchronous and sequential systems (Jantsch, 2003).

The synchronous MoC was one of the first to be defined and also is a widely used timed MoC. For those reasons, it is object of study in the present research.

#### Synchronous (SY) MoC

The synchronous MoC is based on the *perfect synchrony hypothesis*, which states that neither computation nor communication takes time. The time is abstracted by dividing its axis into slots. Everything that happens inside a specific slot occurs synchronized by a global time clock

(Jantsch, 2003). For a system to attend the perfect synchrony hypothesis, the time slot must be selected in a manner that all the model's process are able to respond *fast enough*, *i.e.*, inside the same time slot.

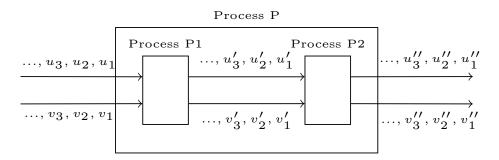

Fig. 2.2 represents a SY process, composed by two sub-process. The signals are composed by the events  $u_x$  and  $v_x$ , where x is the tag of these events, which in turn are inputs to the Process P. The Process P1 sub-process consumes  $u_x$  and  $v_x$ , producing the intermediate signals composed by  $u_x'$  and  $v_x'$ . The last are consumed by Process P2, generating the Process P output signals composed by the events  $u_x''$  and  $v_x''$ . According to synchrony hypothesis,  $v_1'$  and  $v_1''$  are outputted at the same instant, *i.e.*, the first time slot or first execution cycle of the system. The next events of each signal also follow the same behavior.

**Figure 2.2.** SY process representation, adapted from (Jantsch, 2003).

A wide range of systems can be modeled using synchronous MoC due to its behavior, in which the processes read inputs, compute outputs and communicate with other processes, *e.g.*, reactive systems and CPS composed by sensors and actuators (Lee and Sangiovanni-Vincentelli, 1998).

## 2.2.3 Untimed Models of Computation

In an *untimed* MoC, the set of tags *T* are *partially ordered*, denoting causality or synchronization, as a consequence, only local groups of events can be ordered based on their tags, rather than all set *T*. Some examples of untimed MoCs are Kahn process networks (KPN), dataflows and Petri Nets (Lee and Sangiovanni-Vincentelli, 1998).

The dataflows can be divided into a range of MoCs. They are represented by directed graphs, where each *node* represents a process and the *arcs* represent the communication paths. A process can only execute, *i.e.*, fire, if it has the necessary events, *i.e.*, *tokens*, available in all of its input ports.

One special case of dataflow is the synchronous dataflow (SDF). It was first presented in 1987 (Lee and Messerschmitt, 1987) and is widely used due to its performance characteristics, as the inputs and outputs rates are defined at compile time, and its modeling simplicity compared

to others MoCs from the dataflows family.

#### Synchronous Dataflow (SDF) MoC

SDF MoC was first presented as dataflows graphs composed by synchronous nodes (Lee and Messerschmitt, 1987). A node is defined as *synchronous* if the number of tokens consumed by the input ports and produced by the output ports are constant and possible to be defined at compile time.

The SDF graph must be non-terminating, which means that the model must be able to run without any deadlock. To check if a model is consistent, it is possible to perform a formal analysis based on the *periodic admissible sequential schedule* (PASS).

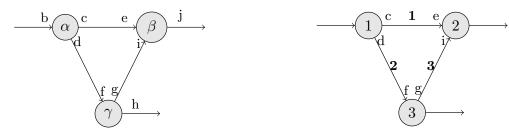

Fig. 2.3a illustrates how a system may be modeled using the SDF MoC graph. To prove the existence of the system PASS, it is necessary to assemble its topology matrix, in which the (x,y) entry represents the amount of data produced by the node y on the arc x. Fig. 2.3b identifies the arcs and nodes of the example system and the Eq. (2.1) represents its topology matrix.

- (a) Regular representation of SDF graph.

- **(b)** SDF with identified nodes and paths.

**Figure 2.3.** SDF example, adapted from (Lee and Messerschmitt, 1987).

$$\Gamma = \begin{bmatrix} c & -e & 0 \\ d & 0 & -f \\ 0 & i & -g \end{bmatrix}$$

(2.1)

A set of lemmas and equations (Lee and Messerschmitt, 1987) demonstrates a necessary condition for a system model containing *s* nodes to hold the PASS:

$$rank(\Gamma) = s - 1 \tag{2.2}$$

The SDF MoC is suitable to model streaming processing due to the possibility to previously define the periodic processing cycle and the token rate of the input and output processes ports.

#### 2.2.4 Hybrid Models

As the CPS complexity grows, it comprehends more processes and variables that do not follow the same semantics when compared to each other, composing the concept of heterogeneous systems. As a consequence, it is not possible to model the whole system using only one MoC, as each MoC represents only one aspect of the entire system (Eker et al., 2003). In this sense, frameworks and modeling domain specific language (DSL) included tools to model these systems by enabling the use of multiple MoCs in one single model, generating the *hybrid models* concept.

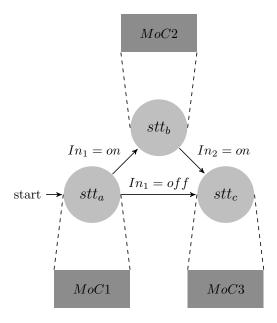

A typical example of hybrid models application is the *modal model*, in which the top level represents a finite state machine (FSM) and each state is refined into models that can be driven by different MoCs. An example is illustrated in Fig. 2.4, in which the states are represented by *stt* nodes, the sub-models by *MoC* nodes, and environment inputs by *In*. This type of model can be used with systems that dynamically changes it behavior depending on user or environment inputs, such as sensor data (Lee and Tripakis, 2010).

Figure 2.4. Modal model example.

# 2.3 Frameworks supporting formal MoCs

There is a wide range of formal-based development frameworks that differs on a series of aspects, such as available MoCs, user interface, functionality, underlying programming paradigm

and language, and license styles.

Simulink is considered one of the most powerful and complete available framework, being a block diagram environment for simulation and model-based design that is integrated to Matlab (MathWorks, 2019a). Simulink includes tools for modeling, simulating and automatic code generation, among other features. It also checks the model compatibility with industry standards such as DO-178C, DO-331 and ISO 26262. Its main disadvantage, if one can point that, is the commercial license style, besides being a proprietary code framework.

Regarding open source frameworks, *Modelica* is presented as a modeling language alternative targeting CPS, which was formalized in 1997, and is supported by a global and non-profit association (Association, 2019). It also provides a modeling and simulation environment, the *OpenModelica*, also maintained by a non-profit association, the OSMC (Open Source Modelica Consortium (OSMC), 2019).

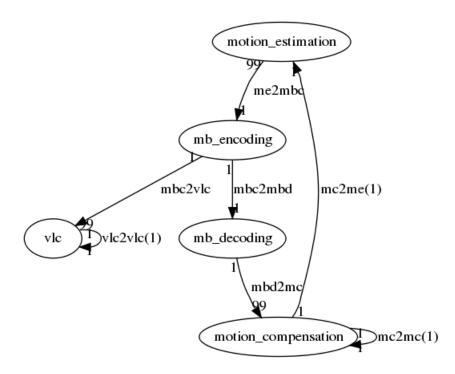

SDF<sup>3</sup> (Stuijk et al., 2006), read as "SDF For Free", is presented as a tool that aims the generation, analysis and visualization of SDF graphs, as illustrated in Fig. 2.5. Its analysis computes parameters of the SDFG, such as the *repetition vector*, which represents the number of times each actor should be fired to bring the system back to beginning state. In this context, an actor is the representation of an SDF node. The source code of this framework is accessible under the SDF<sup>3</sup> proprietary license conditions. One disadvantage of this framework is the lack of a system simulation tool.

Figure 2.5. H.263 encoder graph generated and visualized with SDF<sup>3</sup> (Stuijk, 2018).

A variety of other frameworks can be found in the literature, *e.g.*, EWD framework (Mathaikutty et al., 2008) and the SystemC modeling framework presented in (Herrera and Villar, 2007).

To reduce the multitude of frameworks and select a couple to work with, the next criteria were proposed and followed in the present work. A framework must support both modeling and simulation of embedded systems, besides the open source code license style (Horita et al., 2019a). Based on this, the framework used in this research case study were ForSyDe and PtolemyII, which are presented in Sections 2.3.1 and 2.3.2.

#### 2.3.1 Formal System Design (ForSyDe)

Aiming the elevation of model abstraction level, and still based on formal design methods, formal systems design (ForSyDe) was first presented in 1999 (Sander and Jantsch, 1999) as a methodology based on a purely functional language, *Haskell*, and on the perfect synchrony hypothesis, thus supporting only synchronous MoC at first. Its main modeling and simulation tool is the ForSyDe-Shallow, implemented as a Haskell embedded domain specific language (EDSL). Nowadays, ForSyDe methodology framework has evolved, including new MoCs, such as continuous time, SDF, and scenario-aware dataflow (SADF) (Bonna et al., 2019), besides other branches and frameworks, *e.g.*, ForSyDe-SystemC, a modeling framework based on the IEEE standard language SystemC (Sander et al., 2016).

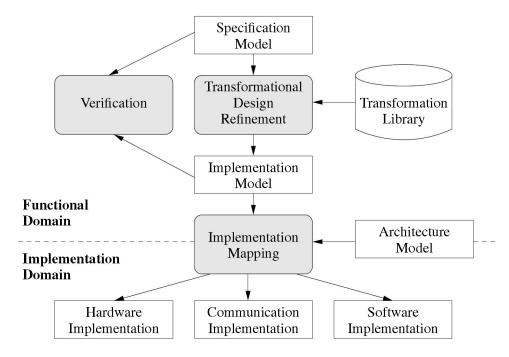

The ForSyDe methodology is illustrated in Fig. 2.6. Its synthesis process is divided into two phases: the *refinement* of the high abstraction level specification model into the implementation model, and the *mapping* of the implementation model into a system architecture.

The refinement phase is performed in the functional domain through the application of formal-based design transformations. As a consequence, the model semantics is prevailed and, the formal verification and validation methods applied to these models can be the same.

The mapping phase is allocated in the implementation domain, in which the model processes are mapped to allocation of resources, platform partitioning and code generation.

The main purpose of the refinement phase is to refine the high abstraction specification model, including implementation information, in order to optimize the mapping phase.

The ForSyDe formal based modeling representation and classification is presented in Section 2.4.1.

## 2.3.2 PtolemyII

The PtolemyII framework is part of the Ptolemy Project, that has been developed at the University of California at Berkeley, starting in the 80's. It aims the formal modeling and simulation of heterogeneous cyber-physical systems and is based on the imperative paradigm and object-

Figure 2.6. For SyDe Design Process (Sander, 2003).

oriented design, using Java as base language. This provides multi-threading and graphical user interface (Ptolemaeus, 2014).

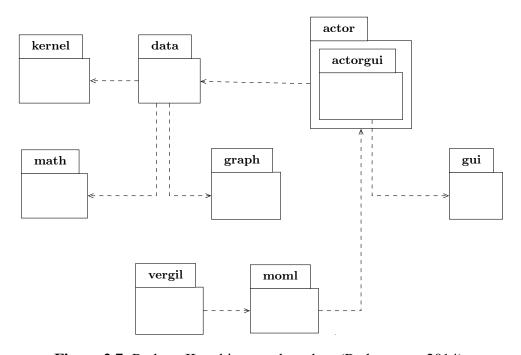

Since PtolemyII is based on a strongly typed and objected-oriented language, *i.e.*, Java, its architecture has a well-defined package structure and packages functionality, as illustrated in Fig. 2.7.

Figure 2.7. PtolemyII architecture based on (Ptolemaeus, 2014).

PtolemyII architecture:

- The kernel package defines the structure of MoCs and the relationship among components and domains, besides their hierarchy;

- Data package includes classes responsible for data transfer among models. The main class in this package is the Token, which represents the base for all units of data exchanged among components;

- Math package treats operations with matrices and vectors;

- Graph package provides support to plot, analyze and manipulate mathematical graphs;

- The actor package implements I/O ports and actors, which are executable entities that exchange data through ports. This package contains the Director class, which are customized to drive the model semantics, *i.e.*, it is the MoC representation inside the application;

- Graphical user interface GUI package offers user interface methods to parameterize and customize the model components. It also provides user interface sub-packages, *i.e.*, vergil package which implements Vergil, the GUI for PtolemyII; and

- moml package provides a parser for modeling markup language (MoML) files, which is the XML schema used to store models.

Nowadays, Ptolemy project has grown and includes different branches based on PtolemyII, some sponsored by commercial partners, having as main purpose the application of formal based design methodologies. This set of branches composes the *Industrial Cyber-Physical Systems Center* (iCyPhy) (University of California, 2018).

# 2.4 MoCs Perspective under PtolemyII and ForSyDe

As the MoCs variety and complexity grows, some concepts and implementation methods can slightly differ from one framework to another, each one having its benefits and drawbacks. This section presents how PtolemyII and ForSyDe classify models of computation and how the MoCs are represented in their system model.

# 2.4.1 ForSyDe Overview

For SyDe implements its models of computation based on the TSM. The signals are modeled as *list of events*, where the tags can either be implicitly given by the event position in the list

or explicitly specified by a list of tuples, depending on which MoC is used. Two events from different signals with the same tag do not necessarily happen at the same time, their tags only represent the order of events in their specific signal.

In ForSyDe, *infinite signals* can be modeled thanks to Haskell *lazy evaluation* mechanism, as shown in Listing 2.1. That evaluates the necessary number of events by using the takeS function applied to the signal  $\{5,5,5\}$  (Sander et al., 2016).

**Listing 2.1.** Haskell Lazy Evaluation.

```

1 constS x = x :- constS x

2 takeS 3 (constS 5)

```

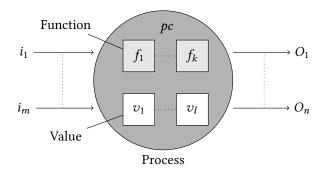

The ForSyDe processes modeling methodology is mainly based on the concept of process constructors, illustrated in Fig. 2.8. This are basically *higher-order functions* that take side effect-free functions and values as arguments to create processes. Each MoC implemented in ForSyDe is essentially a collection of process constructors that enforce the semantics of that specific MoC.

Process constructors are classified as follows.

- 1. combinational process that has no state;

- 2. delay process delays input; and

- 3. sequential process that has an internal state and contains a delay process.

The implementation of heterogeneous systems can be done by using process constructors from different MoC libraries.

**Figure 2.8.** Process built by a Process Constructor (Sander et al., 2016).

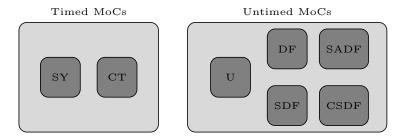

ForSyDe MoCs classification is derived from the TSM framework, which means they can be divided into timed and untimed MoCs, as shown in Fig. 2.9.

ForSyDe defines the untimed MoCs by sets of process constructors and combinators, characterized by the way its processes communicate and synchronize with each other, and in particular, by the absence of timing information available to and used by processes. It operates on the

**Figure 2.9.** For SyDe models of computation.

causality abstraction of time. Only the order of events and cause and effect of events are relevant (Jantsch, 2003). ForSyDe includes the following MoCs in this category: dataflow (DF); synchronous dataflow (SDF); cycle-static dataflow (CSDF); scenario-aware dataflow (SADF); and the untimed MoC (U) (ForSyDe Group, 2019).

In the timed MoCs, on the other hand, timing information is conveyed on the signals by *absent events* transmitted in regular time intervals, allowing the processes to know when a particular event has occurred and when no event has occurred. The sole sources of processes information are input signals, without the need of access to a global state variable. ForSyDe includes two timed MoCs, the synchronous (SY) and the continuous time (CT) (ForSyDe Group, 2019).

### 2.4.2 PtolemyII Overview

The main way to model and simulate systems using PtolemyII is using its GUI, called *Vergil*. The models are represented as a set of actors, that communicates through interconnected ports. The model semantics are driven by an special actor called Director, which is the graphical representation of the selected MoC.

The actors represent the system processes and can be classified into two groups: opaque and transparent. The opaque actor has its intern logic invisible to the outside model, *i.e.*, the sub-model inside it can be driven by a different Director, composing a hierarchical and heterogeneous system model. The transparent actor semantics are driven by the Director included in the model they belong to. All the actors have its source code available and are customizable.

PtolemyII includes a wider set of MoCs when compared to ForSyDe. Fig. 2.10 illustrates the most commonly used and their relationship, considering their behavior and heritage, according to (University of California, Berkeley-online, 2018).

In PtolemyII, synchronous-reactive (SR) MoCs execution follows ticks of a global clock. At each tick, each variable, represented visually in Vergil by the wires that connect the actors, may or may not have a value. Its value, or absence of value, is given by an actor output port connected to the wire. The actor maps the values at its input ports to the values at its output

**Figure 2.10.** MoCs Chart, according to (University of California, Berkeley-online, 2018).

ports, using a given function. The function can vary from tick to tick.

The PtolemyII SR MoC is by default untimed, but it can optionally be configured as timed, in case there is a fixed time interval between ticks.

In PtolemyII dataflow MoCs, the execution of an actor consists of a sequence of firings, where each firing occurs as a reaction to the availability of input data. A firing is a computation that consumes the input data and produces output data.

Considering the SDF domain, when an actor is executed, it consumes a fixed amount of data from each input port, and produces a fixed amount of data to each output port. As a consequence, the potential for deadlock and boundedness can be statically checked, and its schedules can be statically computed. PtolemyII SDF MoC can be timed or untimed, though it is usually untimed.

An example of non-concurrent MoC included in PtolemyII is the FSM, which is considered as a sequential MoC. In that case, the graphical components are not actors, but states, and their relationships represent transitions between those states. Transitions have guards that determine when state transitions can occur.

An FSM can be used to define the behavior of an actor used in other domains. When that actor executes, the FSM reads the inputs, evaluates the guards to determine which transition to take, and produces outputs as specified on the selected transition.

FSM is also used to create a class of hierarchical models, the modal models. In this case, the states of an FSM contain submodels that process inputs and produce outputs. Each state of the FSM represents a mode of execution, that can be driven by different MoCs. When a submodel is not active, its local time does not advance.

## 2.5 Functional Programming Paradigm

Considering that systems should be first modeled at a high abstraction level during the specification phase of a project (Edwards et al., 1997), the present work focus is on functional programming paradigm-based framework, *i.e.*, ForSyDe.

The reason is that functional paradigm features elevate the model abstraction level. It is possible to list higher-order and side-effect free functions, data abstraction, lazy evaluation and pattern-matching as useful features.

Functional programming base was first introduced in 1936, when Alonzo Church *et al.* presented the main concepts of *Lambda Calculus* (Turner, 2013). In that paradigm, all the computation functions of a program are mathematical expressions to be evaluated.

Some languages were then created based on that paradigm, including Lisp, Miranda, Scheme and *Haskell*. ForSyDe has as its main programming language Haskell.

#### 2.5.1 Haskell Programming Language

Haskell had its first official report issued in 1990, having an update in 1998, named *Haskell 98 Report* (Hudak et al., 2007). During the first years of existence, Haskell was mainly used in the academic area. During the 2000's, with the advents of multi-core processors and logical parallelism needs, it gained visibility and developers began to contribute with several libraries, having a full language revision in 2010.

Haskell is a pure functional language, which means it is exclusively based on the concepts of this paradigm. Its main characteristics can be briefly described as follows.

- *Laziness*: all the function and variables evaluation are done only when needed. As a consequence, it is possible to declare infinite lists in Haskell, taking the necessary values only when they require to be used;

- Statically Typed: all variables and functions types are known at compile time. Besides, types can also be inferred by the compiler. If it cannot infer or identify a variable or function type, an error is raised at compile time;

- Referential transparency: functions always return the same value considering they have the same inputs. As a consequence, all functions can be replaced by their returning value;

- *Immutable state*: functions do not implicitly modify variables or states, and cannot affect other functions, *i.e.*, they are side-effects free;

• *High level*: complex algorithms can be implemented through simpler syntax when compared to other paradigms, *e.g.*, imperative or object-oriented.

As Haskell becomes more popular, more tools and packages are developed. Its main compiler is the *Glasgow Haskell Compiler* (GHC), commonly used with its interactive environment, the *GHCi*, which supports different operational systems and platforms. Besides, the environment has an useful system used for building and packages libraries called *cabal*. It builds the applications in a portable way. The main tools can be found in the Haskell home page (Haskell, 2018).

# 2.6 Imperative Programming Paradigm

Although the imperative programming paradigm has not the same abstraction level as the functional one, it has characteristics that can contribute in model-based design, *e.g.*, concurrency programming or classes inheritance. The imperative paradigm representation is directly derived from the way digital hardware works, by signals changing state over time. The machine code works in an imperative way, without abstractions. This paradigm can be explained as a sequential execution of commands over time, producing a program that behaves as a state function of time (Scott, 2009). Some widely used pure imperative languages are C, Pascal, Basic and Fortran.

Imperative programming paradigm can be divided into some subsets, depending on the research, this classification can differ. Scott (2009) includes into these subsets the *von Neumann*, *scripting* and *object-oriented* paradigms.

## 2.6.1 Java Language

*Java*, the PtolemyII base language, is classified as an object-oriented programming language. The main feature of this paradigm is the modularity and encapsulation, improving the scalability when compared to other languages, like C.

The Java attributes allows the modeling of concurrent or parallel process of a system, using threads. This facilitates the creation of new classes, due to its inheritance feature, and allows the development of graphical user interfaces.

## 2.7 Straightforward Paradigms Comparison

Although imperative paradigm has its advantages, allowing a low level software tuning, the functional paradigm enforces safer programming and higher abstraction level, attending one of the model-based development methodology targets. Moraes and Loubach (2017) briefly lists benefits and drawbacks of these paradigms when programming real-time systems, as shown in Table 2.1.

**Table 2.1.** Functional and Imperative Paradigms Comparison (Moraes and Loubach, 2017).

|                   | Imperative                                                                                                                                                                        | Functional                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Management | Allocation and deallocation are done as the developer implements.                                                                                                                 | Functional languages are interpreted/-compiled and high-level, the compiler itself implements garbage collection.                                                  |

| Determinism       | To ensure determinism, all state mutations must be covered, which is complex in imperative programs.                                                                              | Functional programs have referential transparency and force explicit notation on code that mutates state, making validation on functional determinism much easier. |

| Time Measure      | Due to their proximity with machine language, imperative languages are straightforward regarding time measuring.                                                                  | Due to garbage collection's non determinism, it can be hard to measure time for specific functions.                                                                |

| Concurrency       | Concurrency adds yet another level of complexity regarding state mutations, since the number of possible interactions between threads is exponential on the number of processors. | Immutable state allows for concurrent independent computation without affecting the functional determinism.                                                        |

# 2.8 Properties Verification

Working with formal-based models and targeting the correct-by-construction design requires the model to be simulated and tested in different procedure steps. One of these steps consists on the verification whether the model holds all the required system properties it should, or not.

The exhaustive test of each property, comprehending all the possible errors, is a hard and labor intensive task, costing a considerable portion of the software development. In this sense, a range of tools have been presented towards the automatic generation of test cases for model properties verification (Claessen and Hughes, 2000; Naylor and Runciman, 2007; Runciman et al., 2008; Castagna and Gordon, 2017).

Quickcheck (Claessen and Hughes, 2000) was first presented in 2001 as a DSL, implemented in Haskell, targeting the test of program properties and was used as base for other similar tools having the same purpose, *e.g.*, SmallCheck (Runciman et al., 2008), Reach (Fowler and Huttom, 2016), and Luck (Castagna and Gordon, 2017). Besides, it has also been emulated in many other programming languages, including Scala, F# and Google Go (Horváth et al., 2010).

To accomplish the properties verification, Quickcheck uses pre-defined checkable formal system specifications, called *properties*, as inputs and automatically generates random values test cases for each one, indicating if the model holds the desired property or not.

#### 2.9 Automatic Code Generation

With the elevation of the model abstraction level, aiming the verification and simulation of the system functionality, there is a lack of implementation details. Towards a more robust, scalable and formal-based design, researches have been presenting alternatives for automatic code generation based on formal models of computation.

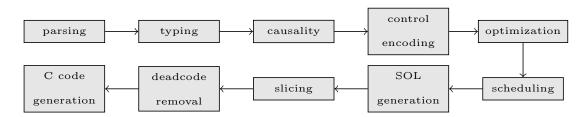

A synchronous-based code generator for explicit hybrid systems languages, which includes discrete and continuous time semantics, was presented by Bourke et al. (2015). A compiler was created to generate statically scheduled sequential code having as inputs a formal model based on Scade 6 synchronous languages using ordinary differential equations. Fig. 2.11 illustrates the presented compiler flowchart. It passes through some consistency analysis and optimization. The code is then translated into a sequential object language (SOL), having its output sliced into functions and again optimized by removing dead-code from the source. Finally, the SOL is translated into C language.

**Figure 2.11.** Compiler architecture based on (Bourke et al., 2015).

Another automatic code generation tool was presented by Grabmüeller and Kleeblatt (2007), called Harpy. It is a domain-specific language for runtime code generation targeting x86 architectures. Its main base language is Haskell, taking advantage of the its features for needed abstractions and language extensions, *e.g.*, meta-programming. Harpy was added to the Haskell community's central package archive, which is called Hackage (Community, 2019).

### 2.10 Main Related Works

In the context of higher abstraction level models and abstraction gap, frameworks and methodologies have been developed towards possible automation approaches for formal model-based design flows. Those tools differ in aspects such as input modeling language, output implementation language and target design step.

Simulink is one of the most powerful and commercially used tools for model-based design of systems. One of its design flow automation tool is the Embedded Coder, which generates C and C++ code for embedded processors in mass production. The generated code is intended to be portable and can be configured to attend standards such as MISRA C, DO-178, IEC 61508 and ISO 26262 (MathWorks, 2019b). Studies have used that tool to test and implement code into customized applications.

The work presented in (Krizan et al., 2014) discusses Simulink usage for automatic generation of C code in critical applications, according to DO-178C and DO-331 standards. They also discussed the possibility of automatic code generation of a whole application or of separate parts, or tasks.

The main difficulties when working with Simulink tools are related to its license costs and proprietary implementation source code, commonly making it impracticable for researchers and developers to perform a deeper analysis of its capabilities and algorithms.

The present research advocates to open source frameworks and tools, making it possible to take advantage of researches collaborative environment and deeper code analysis.

Related to open source software, Copilot is presented as a DSL, based on Haskell, targeting runtime verification (RV) programs for real-time, distributed and reactive embedded systems (Pike et al., 2013). Runtime verification programs are applications which runs in parallel with the systems application, monitoring its correctness ans consistency at the runtime. Copilot is implemented throughout a range of packages, including automatic generations of C code: *copilot-c99*, based on Atom Haskell package, and *copilot-sbv*, based on SBV Haskell package. Although Copilot is a powerful tool for safe C code generation, even for critical systems, it mainly targets a specific application type, the RVs. The present work aims to address a wider range of application and cyber-physical systems.

Requirements to Design Code (R2D2C) project was first presented by NASA aiming full formal development, from requirements capture to automatic generation of provable correct code (Rash et al., 2006). Its approach takes the specifications defined as scenarios using DSLs, or UML cases, infers a corresponding process-based specification expressed in communicating sequential processes (CSP), and finally transforms this design to Java programming language. That tool also makes it possible to apply reverse engineering, extracting models from programming language codes. The present research aims to analyze possible automation strategies for

embedded systems design flows having as inputs formal MoCs implemented through a framework or an EDSL

Some challenges, advances and opportunities of embedded systems design automation were presented in (Seshia et al., 2017). According to that research, some CPS characteristics were listed as obstacles for this automation, including: heterogeneity, dynamic and distributed systems, large-scale and existence of human-in-the-loop. They argued that, for design automation tools, a series of features would be necessary, *e.g.*, cross-domain, learning-based, time-awareness, trust-aware and human-centric. One of the possible presented approaches was the combination of model-based design (MBD), contributing with formal mathematical models, and data-driven learning, which inputs data resulted from extensive field testing.

The present work represents an effort on contributions to the embedded design automation based on MBD research. A case study is designed, modeled, simulated, verified and implemented in high level, targeting the identification of automation approaches to help overcoming the listed difficulties.

# 2.11 Summary

This chapter presented the main concepts used along with the research, starting with embedded and cyber-physical systems, followed by models of computation and the programming paradigms. In addition, it presented examples of frameworks that support formal CPS modeling. Automatic code generation tools and methodologies were also considered in this chapter.

Finally, the main related works targeting formal embedded systems design automation were presented, highlighting the main differences to this research.

Next chapter describes the methodology and analysis introduced in the present research, representing its contribution proposal.

### 3 A METHOD FOR POSSIBLE AUTOMATION EXPOSURE

This chapter presents the proposed method for *analysis and identification of possible automation approaches* (AIPAA) applicable to embedded systems design flow supported by formal models of computation.

Towards the automation approaches identification, the introduced method uses a design methodology, separated into well-defined steps, as described in Section 3.1. Next, the design steps are analyzed, resulting in a set of possible automation approaches, presented in Section 3.2. An illustrative example representing the methodology application is presented in Section 3.3.

# 3.1 Analysis and Identification of Possible Automation Approaches

## - The AIPAA Method

One of the first steps when designing an embedded system is the system description in the form of *problem statement*. This includes functionalities, behaviors, capabilities and constraints of the system. An accurate and detailed problem statement leads to an effective, robust and optimized design flow.

Elaborating the embedded system detailed problem statement is not a trivial task. The present research work considers a design flow methodology assuming the problem statement is already described. The problem statement is considered to be an *input* for the system design flow under use.

The AIPAA method takes into account only the *system specification* domain. The implementation domain comprehends a variety of concepts and tools other than this research scope. However, the present work presents straightforward guidelines on how the implementation domain can take advantage of the AIPAA outputs.

Fig. 3.1 illustrates the proposed method, *i.e.*, AIPAA. Each one of the five steps are detailed in the next subsections.

**Figure 3.1.** Analysis and identification of possible automation approaches (AIPAA) applicable to embedded systems design flow. AIPAA needs the "problem statement" as a given input, and aids to produce a model, which is verified and executable, as output. This output can be used as entry point in the implementation domain, *e.g.*, "implementation details" and "implement system".

### 3.1.1 Problem Characterization

This first step, *problem characterization*, aims to conduct an initial analysis on the "problem statement" input aiming the identification of its relevant behaviors and characteristics towards the design of the system.

To facilitate the identification of problem semantics, both the problem procedures and processing must be separated into *functions*, also defining how they should execute and communicate to each other.

These definitions allow for the problem analysis and characterization, which will aid in the

further MoC definition. When applying the method, the following questions must be answered.

- $Q_1$  Does the problem have concurrent or only sequential processes?

- $Q_2$  Are the problem communication paths totally or partially ordered?

- $Q_3$  Is the problem a dataflow problem?

- $Q_4$  Are the inputs and processing cyclic?

- $Q_5$  Can a single clock be used to synchronize all the involved processes?

### **Step Required Inputs**

This step requires the following inputs:

1. Problem statement describing the problem functionalities, behaviors, inputs and desired outputs.

### **Step Expected Output**

After the application of this step considering the required inputs, the expected outputs are:

- 1. Problem separation into functions and their relationship definition; and

- 2. A list of well-defined problem characteristics according to the previously stated questions.

### 3.1.2 MoC Definition

As stated in Section 2.2, models of computation describe only the characteristics that are relevant for a given task. In this sense, it is needed to *analyze the problem characterization step* results aiming the identification of relevant behaviors and functionality that permits its semantics classification into one or more MoCs.

A range of complex applications comprehends behaviors that may not be possible to be modeled using just a single MoC. As a consequence, the model semantics must be split into more than one MoC, generating the concept of heterogeneous systems modeling. In that case, a second phase should be included into this step, defined as MoC division, which classifies each problem characteristic into a MoC that better fits it.

The present research work only addresses the study of a single MoC at a time within a system, *i.e.*, using either SY or SDF MoCs. For this limitation, an analysis on the available MoCs was performed and just two MoCs were selected, based on the criteria that they had to be representative, widely used and should differ on timing abstractions.

As stated in Section 2.2.2, SY is a timed MoC, i.e., its signals are totally ordered, and it is based on the perfect synchrony hypothesis. The SDF, on the other hand, is an untimed MoC, i.e., its signals are partially ordered, composed by nodes with fixed token rates and it is non-terminating, as described in Section 2.2.3.

### **Step Required Inputs**

This step requires the following input:

1. List of problem characteristics.

### **Step Expected Output**

After the application of this step, the expected outputs is:

1. The definition of a MoC to be used in the system design flow.

### 3.1.3 Framework Selection

A support framework is an important tool that aids in the system *modeling* and *simulation* step of the design flow. There is a number of facts to be considered when selecting a formal-based framework. The proposed AIPAA method considers the following.

- **License style**: The framework license style must comply with the project requirements. It can vary from open source or freeware to a proprietary and paid license style;

- **Included MoCs**: The set of available MoCs can drastically differ when comparing frameworks. *e.g.*, SDF<sup>3</sup> only supports SDF, SADF and CSDF, on the other hand, Simulink, ForSyDe or PtolemyII supports a range of MoCs, as illustrated in Fig. 2.10. The selected MoC, in Section 3.1.2, must be part in the framework supported MoC list;

- Capabilities: The frameworks varies on its capabilities, including system simulation and heterogeneous system modeling. In this sense, model simulation figure as an interesting feature for a framework to have;

- **Interfaces**: Frameworks differ on its modeling and simulation interfaces. It ranges from a script environment to a GUI. The simulation input and output interfaces varies from files, predefined or user inputted and must also be considered;

- Scalability: Towards scalable models, some frameworks are implemented based on programming languages and have interfaces that facilitates the modeling of large or distributed systems;

• **Programming language paradigm**: Frameworks are based on a wide range of programming languages, leading to a variation on its programming paradigm, *e.g.*, imperative or functional. Each paradigm has its own benefits. Functional can lead to a better model scalability and higher abstraction level, on the other hand, imperative paradigm facilitates new MoCs modeling due to inheritance capability.