UNIVERSIDADE ESTADUAL DE CAMPINAS Faculdade de Engenharia Elétrica e de Computação

Pattam Gyanesh Kumar Patra

# MACSAD: Multi-Architecture Compiler System for Abstract Dataplanes

### MACSAD: Sistema de Compilador Multi-Arquitetura para Planos de Dados Abstratos

Campinas

2019

Pattam Gyanesh Kumar Patra

## MACSAD: Multi-Architecture Compiler System for Abstract Dataplanes

## MACSAD: Sistema de Compilador Multi-Arquitetura para Planos de Dados Abstratos

Thesis presented to the Faculty of Electrical and Computer Engineering of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor, in the area of Computer Engineering.

Tese apresentada à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas como parte dos requisitos exigidos para a obtenção do título de Doutor em Engenharia Elétrica, na Área de Engenharia de Computação.

Supervisor: Prof. Dr. Christian Rodolfo Esteve Rothenberg

Este exemplar corresponde à versão final da tese defendida pelo aluno Pattam Gyanesh Kumar Patra, e orientada pelo Prof. Dr. Christian Rodolfo Esteve Rothenberg

> Campinas 2019

Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Rose Meire da Silva - CRB 8/5974

Patra, Pattam Gyanesh Kumar, 1986-MACSAD: Multi-Architecture Compiler System for Abstract Dataplanes / Pattam Gyanesh Kumar Patra. – Campinas, SP : [s.n.], 2019.

Orientador: Christian Rodolfo Esteve Rothenberg. Tese (doutorado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Redes definidas por software (Tecnologia de rede de computador). 2. Comutação de pacotes (Transmissão de dados). 3. Software - Desempenho. 4. Aprendizagem supervisionada (Aprendizado do computador). 1. Esteve Rothenberg, Christian Rodolfo, 1982-. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: MACSAD: Sistema de Compilador Multi-Arquitetura para Planos de Dados Abstratos Palavras-chave em inglês: Software-defined networking (Computer network technology) Packet Switching (Data transmission) Network performance Supervised learning (Machine learning) Área de concentração: Engenharia de Computação Titulação: Doutor em Engenharia Elétrica Banca examinadora: Christian Rodolfo Esteve Rothenberg [Orientador] Rodolfo Jardim de Azevedo Leonardo de Souza Mendes Rodolfo da Silva Villaca Fernando Manuel Valente Ramos Data de defesa: 21-05-2019 Programa de Pós-Graduação: Engenharia Elétrica

Identificação e informações acadêmicas do(a) aluno(a)

<sup>-</sup> ORCID do autor: https://orcid.org/0000-0001-5106-4336 - Currículo Lattes do autor: http://lattes.cnpq.br/8044336523774815

#### COMISSÃO JULGADORA – TESE DE DOUTORADO

Candidato: Pattam Gyanesh Kumar Patra RA: 153806

Data da Defesa: 21 de Maio de 2019

**Título da Tese:** "MACSAD: Multi-Architecture Compiler System for Abstract Dataplanes".

Prof. Dr. Christian Rodolfo Esteve Rothenberg

Prof. Dr. Rodolfo Jardim de Azevedo

Prof. Dr. Leonardo de Souza Mendes

Prof. Dr. Rodolfo da Silva Villaca

Prof. Dr. Fernando Manuel Valente Ramos

A ata de defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no SIGA (Sistema de Fluxo de Dissertação/Tese) e na Secretaria de PósGraduação da Faculdade de Engenharia Elétrica e de Computação.

#### **Dedicated** To

My family who gave me reason to smile, to cry, to get angry, who challenge me to reach beyond myself. My friend circle, JWALKERS, for being with me for the last 15 years, offered their shoulders to lean on, opened their arms to offer solace, stood by me to protect, and gave me a sense of existence, importance and aliveness everyday. A friend whom i met accidentally here in Brazil after 8 long years turning out to be a great thing as he continue to provide critical advises in every important juncture of my personal life & became the magic glue to keep both my personal and professional life sane. The amazing new friends i made in INTRIG who welcomed me to their hearts and to their home out of curiosity, love and respect, whom i now carry with me for life. Gergely Pongrácz for showing faith, for listening and for offering the valuable guidance i needed. Specially, to the stranger i put my complete faith on even before coming to Brazil, who became much more than a friend or an advisor, my YODA, Christian Rothenberg.

# Acknowledgements

This work was supported by the Innovation Center, Ericsson Telecomunicações S.A., Brazil under grant agreement UNI.61 through Funcamp/Unicamp intermediation.

Cognizance of newth & vicissitude is all i long, for it To live until I live. (speaking for myself)

## Abstract

Software-Defined Networking (SDN) strives for programmable data plane, yet flexible and scalable control and application planes. Despite having received less attention compared to control and application aspects of SDN, data planes are a critical piece of the SDN puzzle. We envision a flexible data plane showing characteristics, namely, *Programmability*, Portability, Performance, and Scalability (3PS) as different aspects of flexibility. While Programmability & Portability aspects focus on the architecture and design of the data plane, Performance & Scalability appears during the evaluation of it. We extend the focus of data plane evolution from Programmability from SDN school of thought to include Portability aspect of flexibility. Programmable data plane confirms to protocol-independent nature, whereas Portability addresses multi-architecture requirements of data plane design. P4 language, a new entrant, being a protocol-independent and target-independent high-level programming language is capable to take data plane evolution to the next level by unlocking the desired facets of data plane flexibility. To bring this required level of flexibility to a data plane, a multi-architecture compiler system is necessary which can compile a P4 program conforming to protocol & target independence nature of P4; However, such a unified compiler system solution is what we lack of. The main contribution of this thesis, the Multi-Architecture Compiler System for Abstract Dataplanes (MACSAD) proposal, is an effort to fill the gap by extending the Top-Down approach of P4 towards programmability with Bottom-Up approach of OpenDataPlane (ODP) towards target-independence with its low-level but cross-platform (HW & SW) APIs. We strengthen the contributions of this thesis by including *Performance*, and *Scalability* aspects of flexibility too as part of our evaluation of MACSAD in multiple realistic scenarios.

**Keywords**: MACSAD; P4; OpenDataPlane; Software-Defined Networking; Programmable Dataplane; Performance analysis.

### RESUMO

Redes Definidas por Software (Software-Defined Networking - SDN) almejam um plano de dados programável, além de planos de controle e aplicação flexíveis e escaláveis. Apesar de ter recebido menor atenção quando comparado aos aspectos dos planos de controle e aplicação, o plano de dados concerne uma peça chave nos enigmas de SDN. Nós contemplamos um plano de dados flexível apresentando as características, nomeadas, Programabilidade, Portabilidade, Desempenho e Escalabilidade (Programmability, Portability, Performance, and Scalability - 3PS) como diferentes aspectos de flexibilidade. Enquanto os aspectos de Programabilidade e Portabilidade focam na arquitetura e projeto do plano de dados, Desempenho e Escalabilidade aparecem durante a avaliação do mesmo. Estendemos o foco da evolução do plano de dados de Programabilidade da escola de pensamento SDN para incluir Portabilidade como aspecto de flexibilidade. O plano de dados programável confirma a natureza independente do protocolo, enquanto a Portabilidade atende aos requisitos de arquitetura múltipla do projeto do plano de dados. A linguagem P4, uma nova entrante, sendo uma linguagem de programação de alto nível independente do protocolo e independente do alvo, é capaz de levar a evolução do plano de dados ao próximo nível, desbloqueando as facetas desejadas da flexibilidade do plano de dados. Para trazer esse nível necessário de flexibilidade para um plano de dados, é necessário um sistema de compilador com várias arquiteturas que possa compilar um programa P4 em conformidade com o protocolo e a natureza de independência de destino de P4; No entanto, essa solução de sistema de compilador unificado é o que nos falta. A principal contribuição desta tese, a proposta do Sistema de Compiladores de Arquitetura Múltipla para Planos de Dados (Multi-Architecture Compiler System for Abstract Dataplanes - MACSAD), é um esforco para preencher a lacuna estendendo a abordagem Top-Down de P4 em direção à programabilidade com a abordagem Bottom-Up do OpenDataPlane (ODP) em direção à independência de destino com suas APIs de baixo nível, mas de plataforma cruzada (HW & SW). Reforçamos as contribuições desta tese incluindo aspectos de Desempenho e Escalabilidade da flexibilidade também como parte de nossa avaliação do MACSAD em múltiplos cenários realistas.

**Palavras-chaves**: MACSAD; P4; OpenDataPlane; Redes Definidas por Software; Plano de Dados Programável; Análise de Desempenho.

# List of Figures

| Figure 1 –  | Supported Features envisioned by MACSAD                                | 26 |

|-------------|------------------------------------------------------------------------|----|

| Figure 2 –  | Where ODP is situated?                                                 | 35 |

| Figure 3 –  | PISA Architecture. Based on: (MCKEOWN, 2015)                           | 38 |

| Figure 4 –  | P4 Abstract Forwarding Model                                           | 40 |

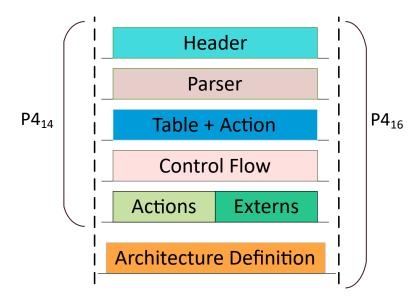

| Figure 5 –  | Components of a P4 Program                                             | 40 |

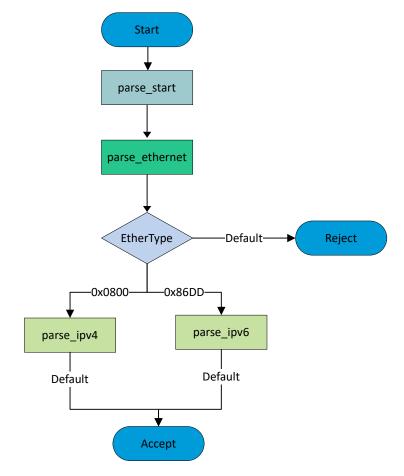

| Figure 6 –  | P4 Parser Graph Example                                                | 43 |

| Figure 7 –  | P4Runtime Reference Architecture                                       | 47 |

| Figure 8 –  | High-level Reference Architecture & Use Case Workflow                  | 52 |

| Figure 9 –  | Three Step Compilation Process.                                        | 55 |

| Figure 10 – | Code-autogeneration Flow Diagram.                                      | 61 |

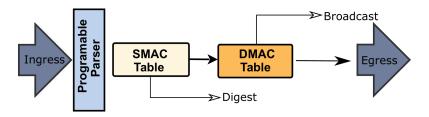

| Figure 11 – | L2FWD Use Case Pipeline.                                               | 78 |

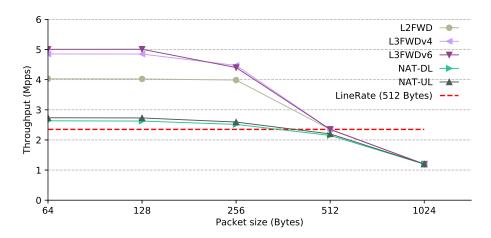

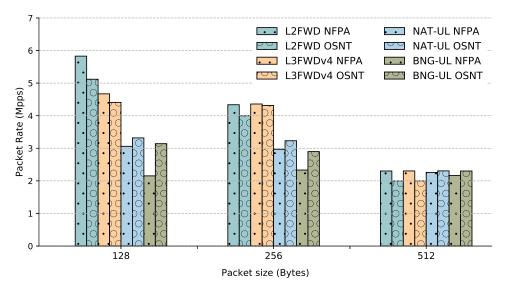

| Figure 12 – | L2FWD Performance Evaluation (1 core, 100 Table entries) on Testbed    |    |

|             | A                                                                      | 79 |

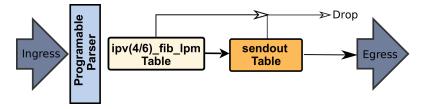

| Figure 13 – | L3FWDv $(4/6)$ Use Case Pipeline                                       | 80 |

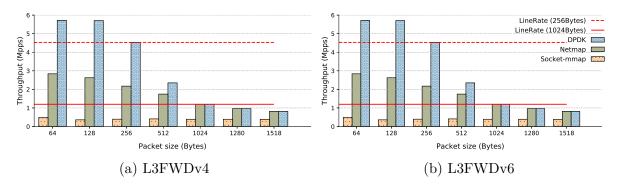

| Figure 14 – | L3FWD (IPv4 & IPv6) Performance Evaluation (1 core, 100 Table          |    |

|             | entries) on Testbed A                                                  | 81 |

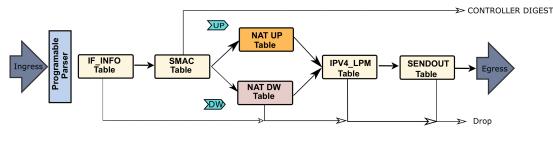

| Figure 15 – | NAT Use Case Pipeline                                                  | 82 |

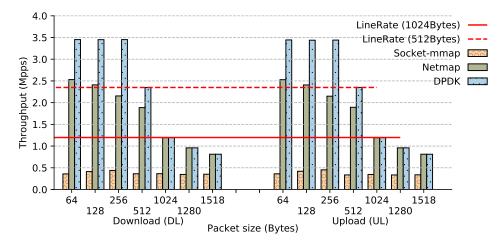

| Figure 16 – | NAT (UL & DL) Performance Evaluation (1 core, 100 Table entries)       |    |

|             | on Testbed A                                                           | 83 |

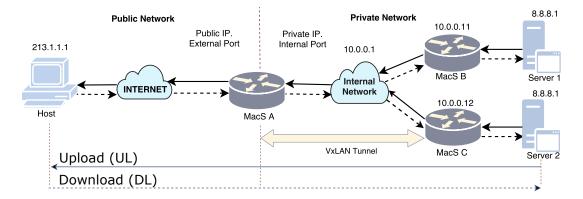

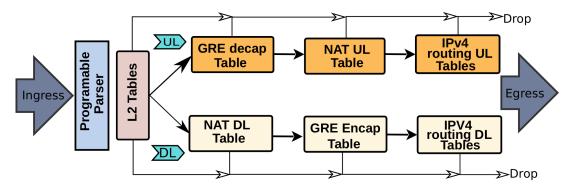

| Figure 17 – | Data Center Gateway (DCG) use case scenario.                           | 84 |

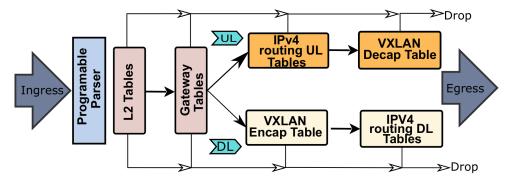

| Figure 18 – | DCG pipeline featuring the UL and DL table details                     | 85 |

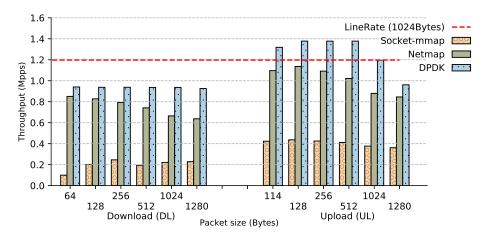

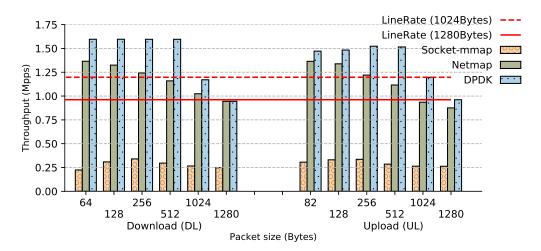

| Figure 19 – | DCG (UL & DL) Performance Evaluation (1 core, 100 Table entries)       |    |

|             | on Testbed A                                                           | 86 |

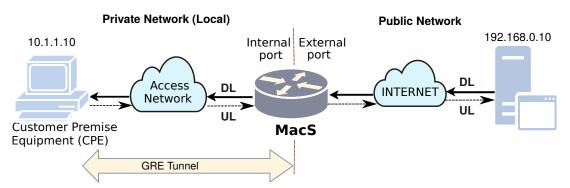

| Figure 20 – | BNG use case illustrating a subscriber and an external public service  | 88 |

| Figure 21 – | Implemented BNG pipeline featuring the main UL and DL tables           | 89 |

| Figure 22 – | BNG (UL & DL) Performance Evaluation (1 core, 100 Table entries)       |    |

|             | on Testbed A                                                           | 90 |

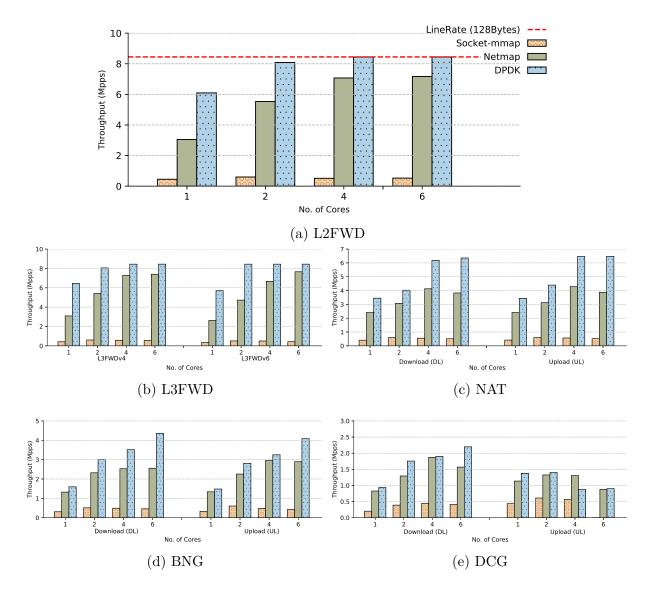

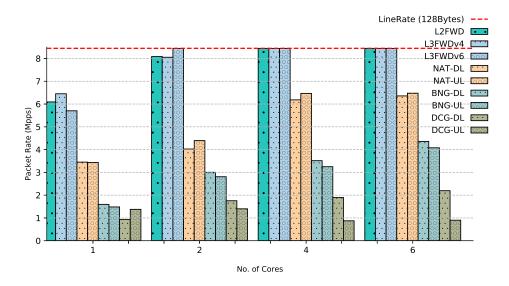

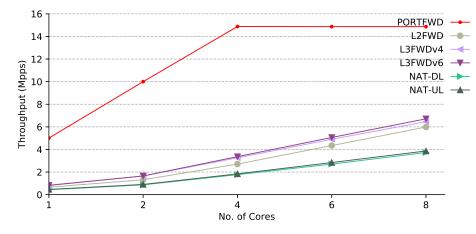

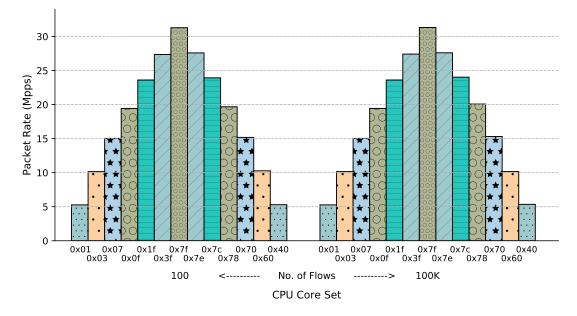

| Figure 23 – | Packet Rate for all Use Cases with different CPU Cores (128 Bytes,     |    |

|             | 100 Table entries) on Testbed A.                                       | 92 |

| Figure 24 – | Packet Rate for Different Use Cases and CPU cores (128 Bytes) on       |    |

|             | Testbed A                                                              | 93 |

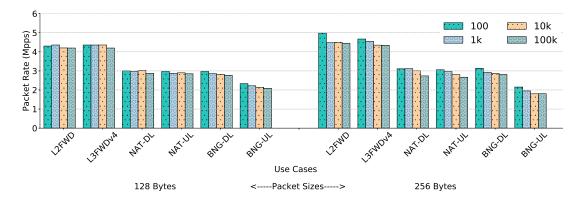

| Figure 25 – | Packet Rate of different Use Cases & packet sizes. (100 Entries, 4 CPU |    |

|             | Cores) on Testbed D                                                    | 94 |

| Figure 26 – | Packet rate for different Use Cases & CPU Cores. (64 Bytes, 100 En-    |    |

|             | tries) on Testbed D                                                    | 95 |

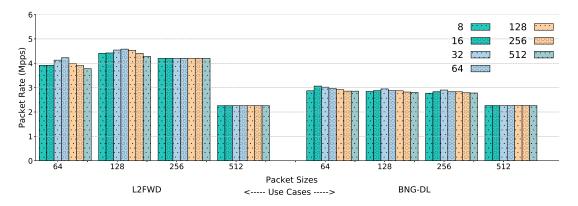

| Figure 27 – Packet rate for different Use Cases, FIB sizes. (2 core, DPDK) on                       |       |

|-----------------------------------------------------------------------------------------------------|-------|

| Testbed E $\ldots$ | 96    |

| Figure 28 – Packet Rate for different Use Cases, burst sizes. (100 Entries, 2 CPU                   |       |

| cores, DPDK) on Testbed E $\ldots$                                                                  | 97    |

| Figure 29 – Forwarding performance of different Use Cases, Pkt sizes, TG. (100                      |       |

| Entries, 2 Cores) on Testbed E                                                                      | 98    |

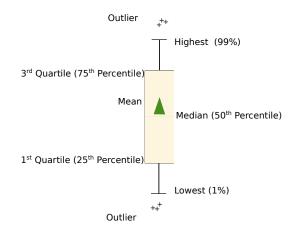

| Figure 30 – Understanding Boxplot for Latency Measurements                                          | 100   |

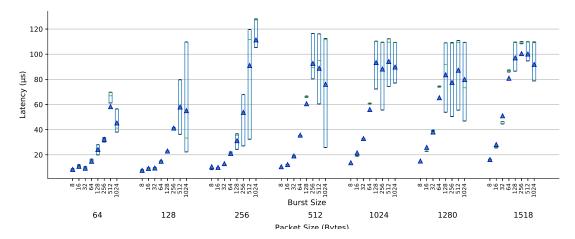

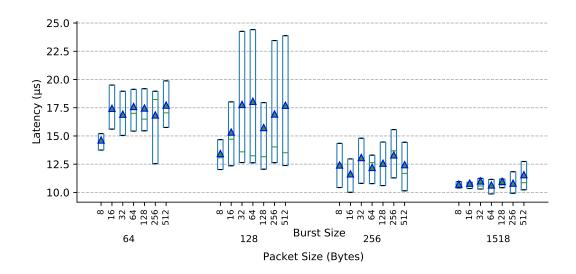

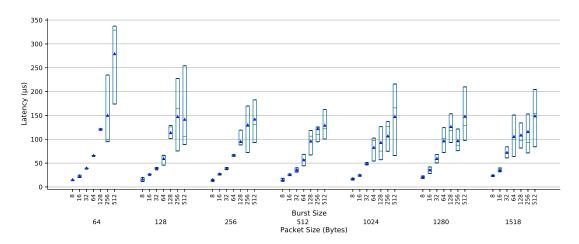

| Figure 31 – Latency of L2FWD DPDK Example for different packet sizes & burst                        |       |

| sizes. (2 CPU, 99% line rate) on Testbed E                                                          | 101   |

| Figure 32 – Latency of L2FWD Use Case for different packet sizes & burst size.                      |       |

| (100 Entries, DPDK, 2 CPU, 99% line rate) on Testbed E $\ldots \ldots$                              | 102   |

| Figure 33 $-$ Latency of L2FWD Use Case (TX part re-implemented similar to DPDK                     |       |

| example) for different packet sizes & burst size. (100 Entries, DPDK,                               |       |

| $2 \text{ CPU}, 99\%$ line rate) on Testbed E $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$    | 103   |

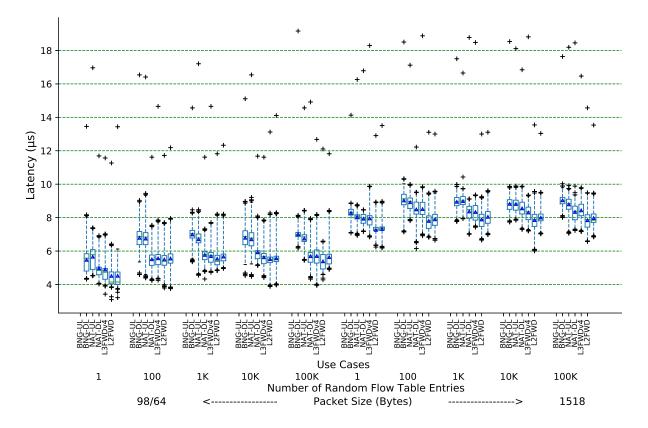

| Figure 34 – Latency of different Use Cases, packet sizes, Fib Sizes. (64 Bytes and                  |       |

| 1580 Bytes, 100 Entries, DPDK, 10% line rate) on Testbed E $\ldots$ .                               | 104   |

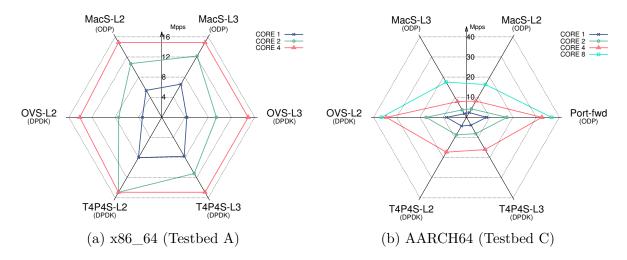

| Figure $35$ – Packet Rate comparison of different platforms and switches for selected               |       |

| use cases (100 FIB size) and varying CPU cores                                                      | 105   |

| Figure 36 – Packet Rate for L2FWD (100 entries, 64 Bytes) on Testbed B                              |       |

| Figure 37 – Packet Rate for L3FWDv4 (100 entries, 64 Bytes) on Testbed B                            | 107   |

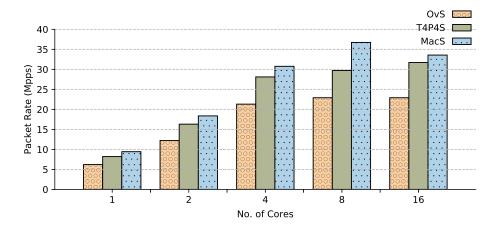

| Figure 38 – Forwarding performance for different MacS (VNF) Use Cases with dif-                     |       |

| ferent CPU Cores (64B, Testbed A).                                                                  | 109   |

| Figure 39 – IPv4 and IPv6 forwarding performance of different I/O drivers, FIB                      |       |

| size, VNFs (4 CPU cores)                                                                            | 109   |

| Figure 40 – Performance (Mpps) when dynamically (30s intervals) changing the                        |       |

| sets of CPU cores allocated to packet processing for different FIB sizes                            |       |

| on Testbed A                                                                                        | 111   |

| Figure 41 – Performance (Mpps) when dynamically (30s intervals) changing the                        |       |

| sets of CPU cores allocated to packet processing for different FIB sizes                            |       |

| on Testbed B                                                                                        |       |

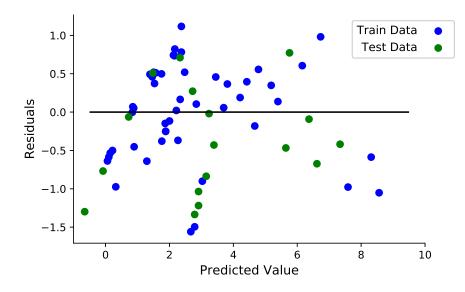

| Figure 42 – Residual Plot for Linear Regression                                                     |       |

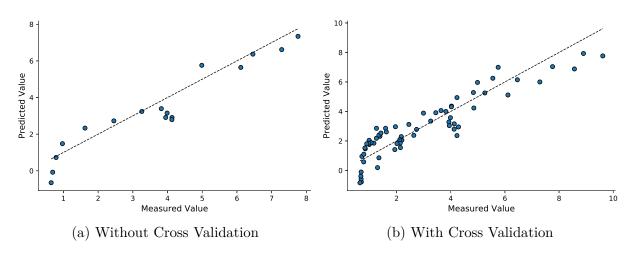

| Figure 43 – Packet Rate (Predicted Value vs Measured Value)                                         |       |

| Figure 44 – Abstract Packet Processing Pipeline                                                     | 132   |

| Figure 45 – Packet Rate comparison for all Use Cases with batch optimization for                    | 104   |

| different CPU Cores (64 Bytes, 100 Table entries) on Testbed A                                      | 134   |

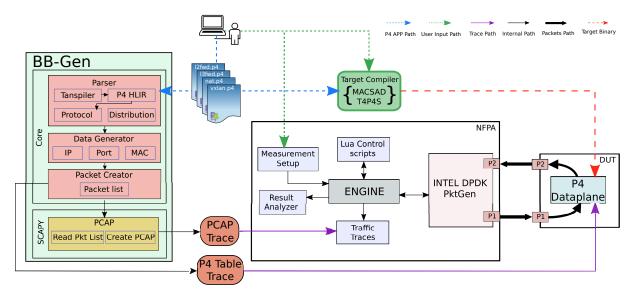

| Figure 46 – BB-Gen Architecture and Integration with NFPA and MACSAD &                              | 1 4 1 |

| T4P4S                                                                                               |       |

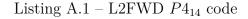

| Figure 47 – L2FWD Dependency Graphs                                                                 |       |

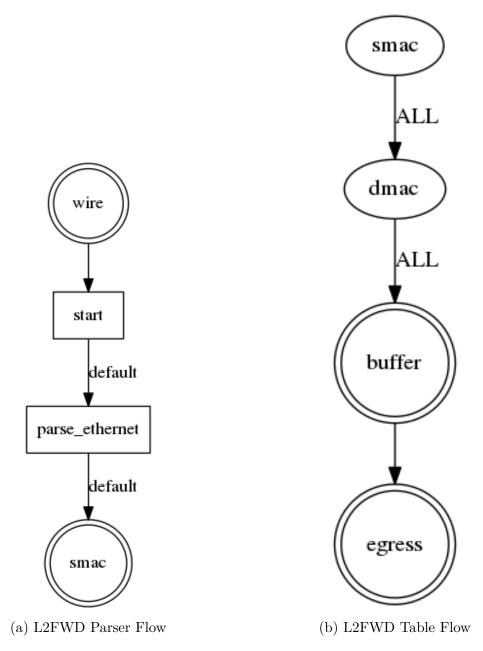

| Figure 48 – L3FWDv4 Dependency Graphs                                                               | 167   |

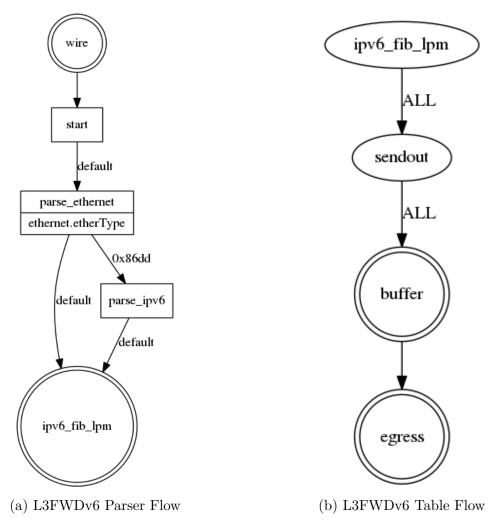

| Figure 49 – L3FWDv6 Dependency Graphs   | 168 |

|-----------------------------------------|-----|

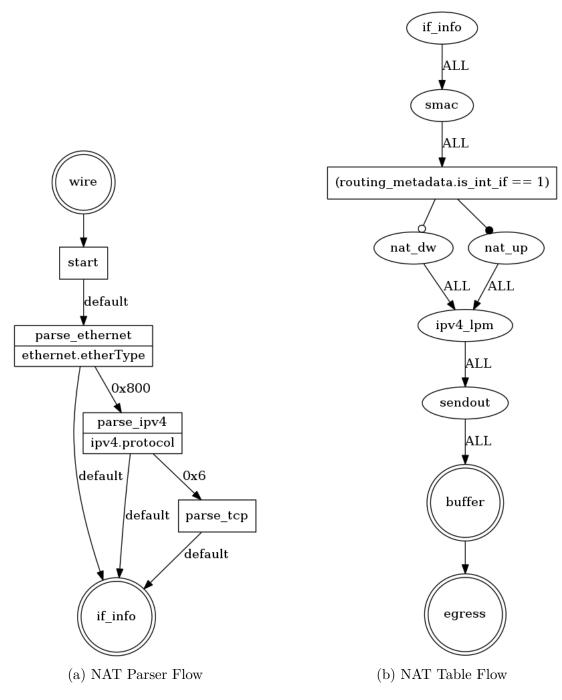

| Figure 50 – NAT Dependency Graphs       | 174 |

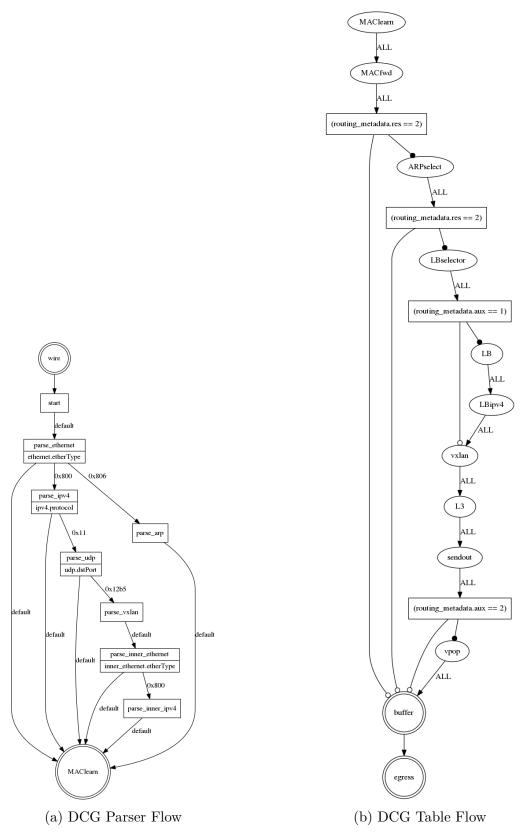

| Figure 51 – DCG Dependency Graphs       | 185 |

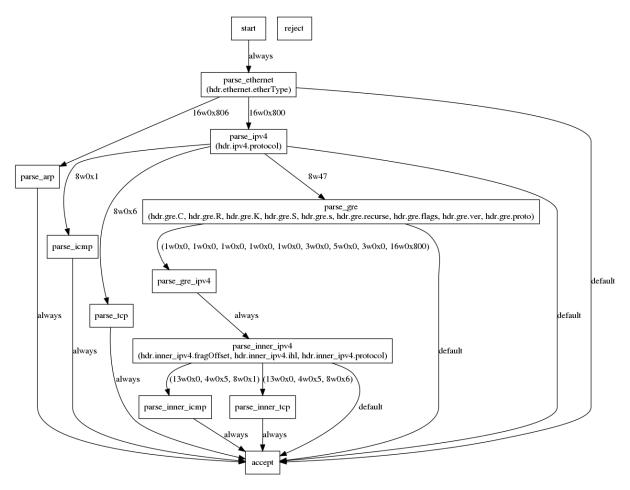

| Figure 52 – BNG Parser Dependency Graph | 197 |

| Figure 53 – BNG Table Dependency Graph  | 198 |

# List of Tables

| Table 1 –  | Research Directions                                                                                                                                                                 | 24  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2 –  | ODP supported platforms                                                                                                                                                             | 36  |

| Table 3 –  | Year-on-Year Evolution of OpenFlow                                                                                                                                                  | 45  |

| Table 4 –  | Scope, Approach, and Feature Comparison List of different Programmable                                                                                                              |     |

|            | Switch Projects                                                                                                                                                                     | 49  |

| Table 5 –  | Packet Processing Functions                                                                                                                                                         | 53  |

| Table 6 –  | P4 Object List in HLIR                                                                                                                                                              | 57  |

| Table 7 –  | Backend APIs Categorical Examples                                                                                                                                                   | 59  |

| Table 8 –  | Transformation of P4 Constructs to 'C' Language                                                                                                                                     | 61  |

| Table 9 –  | Auto-generated Code for Header Instances                                                                                                                                            | 63  |

| Table 10 – | Auto-generated Code for Header Field Instances                                                                                                                                      | 63  |

| Table 11 – | Auto-generated Table APIs for Control Plane                                                                                                                                         | 73  |

| Table 12 – | Testbed Summary                                                                                                                                                                     | 78  |

| Table 13 – | Packet Rate Behavior for Different FIB Sizes                                                                                                                                        | 96  |

| Table 14 – | Processing Time for a Single Network Packet                                                                                                                                         | 98  |

| Table 15 – | Latency of BNG-UL use case for different FIB sizes & packet sizes in                                                                                                                |     |

|            | Testbed E $\ldots \ldots $                                          | .04 |

| Table 16 – | P4 Use Case Complexity Details                                                                                                                                                      | 17  |

| Table 17 – | MACSAD Switch (MACS) Dataset Sample                                                                                                                                                 | 19  |

| Table 18 – | Coefficient Vector of Linear Regression Model                                                                                                                                       | 26  |

| Table 19 – | Ridge Regression Model $\mathbb{R}^2$ Scores $\ldots \ldots \ldots$ | 28  |

| Table 20 – | Regularized Model with $\alpha$ value as 0.001 $\ldots \ldots \ldots$                                         | .28 |

| Table 21 – | Performance Measures of Different Regression Models                                                                                                                                 | .29 |

| Table 22 – | Use Case Performance Results (64 Bytes, 100 Table Entries, DPDK,                                                                                                                    |     |

|            | Testbed A)                                                                                                                                                                          | 35  |

## Acronyms

- **AAA** Authentication, Authorization and Accounting.

- **API** Application Programming Interface.

- **ARM** Advanced RISC Machine.

- BNG Broadband Network Gateway.

- ${\bf BRAS}\,$  Broadband Remote Access Server.

- **CISC** Complex Instruction Set Computing.

- **CPE** Customer Premise Equipment.

- DCG Data Center Gateway.

- **DL** Download.

- $\mathbf{DPDK}\,$  Data Plane Development Kit.

- ${\bf dRMT}$  disaggregated Reconfigurable Match-Action Table.

- ${\bf DSL}\,$  Domain Specific Language.

- **EO** Elementary Operation.

- **FIB** Forwarding Information Base.

- GCC GNU Compiler Collection.

- **GRE** Generic Routing Encapsulation.

- HLIR High Level Intermediate Representation.

- **IR** Intermediate Representation.

- **ISP** Internet Service Provider.

- ${\bf JSON}\,$  JavaScript Object Notation.

- ${\bf LLVM}\,$  Low Level Virtual Machine.

- ${\bf LPM}\,$  Longest Prefix Match.

MacS MACSAD Switch.

MACSAD Multi-Architecture Compiler System for Abstract Dataplanes.

**NAT** Network Address Translation.

${\bf NF}\,$  Network Function.

**NFPA** Network Function Performance Analyzer.

${\bf NFV}\,$  Network Function Virtualization.

**NOS** Network Operating System.

NUMA Non-Uniform Memory Access.

**ODP** OpenDataPlane.

OF OpenFlow.

$\mathbf{OPX}$  OpenSwitch.

**OvS** OpenvSwitch.

P4 Programming Protocol-Independent Packet Processors.

**PI** Protocol Independence.

**PISA** Protocol Independent Switch Architecture.

**POF** Protocol-oblivious Forwarding.

**PRT** P4Runtime.

**RISC** Reduced instruction set computing.

**RMT** Reconfigurable Match Tables.

**RSS** Receive Side Scaling.

**SAI** Switch Abstraction Interface.

**SDK** Software Development Kit.

**SDN** Software-Defined Networking.

**SONIC** Software for Open Networking in the Cloud.

${\bf T4P4S}$  Translator for P4 Switches.

$\mathbf{U}\mathbf{L}$  Upload.

**VM** Virtual Machine.

**VNF** Virtual Network Function.

**VTEP** Virtual Tunnel End Point.

**VXLAN** Virtual eXtensible Local Area Network.

# Contents

| 1 | Intr | oductio | on                                                                                   | 21 |

|---|------|---------|--------------------------------------------------------------------------------------|----|

|   | 1.1  | Backg   | ground and Motivation                                                                | 21 |

|   | 1.2  | Resear  | rch Hypothesis                                                                       | 24 |

|   | 1.3  | Thesis  | s Approach & Contributions                                                           | 24 |

|   |      | 1.3.1   | Multi-Architecture Compiler System for Abstract Dataplanes                           | 26 |

|   |      | 1.3.2   | Multidimensional Evaluation                                                          | 27 |

|   |      | 1.3.3   | Use Case Complexity Analysis                                                         | 28 |

|   |      | 1.3.4   | Compiler Optimization                                                                | 28 |

|   |      | 1.3.5   | Additional Open-source Artifacts                                                     | 28 |

|   |      | 1.3.6   | Noted Contributions                                                                  | 29 |

|   | 1.4  | Outlin  | ne                                                                                   | 31 |

| 2 | Lite | rature  | Review                                                                               | 32 |

|   | 2.1  | Relate  | ed Technologies                                                                      | 33 |

|   |      | 2.1.1   | Packet IOs                                                                           | 33 |

|   |      |         | 2.1.1.1 FD.io (Fast data – Input/Output) $\ldots \ldots \ldots \ldots$               | 34 |

|   |      |         | 2.1.1.2 Netmap $\ldots$                                                              | 34 |

|   |      |         | 2.1.1.3 Data Plane Development Kit (DPDK)                                            | 34 |

|   |      |         | 2.1.1.4 OpenDataPlane (ODP)                                                          | 35 |

|   |      | 2.1.2   | Packet Switch Pipeline Architectures                                                 | 36 |

|   |      |         | 2.1.2.1 Reconfigurable Match-Action Table (RMT)                                      | 36 |

|   |      |         | 2.1.2.2 disaggregated Reconfigurable Match-Action Table (dRMT)                       | 37 |

|   |      |         | 2.1.2.3 Protocol Independent Switch Architecture (PISA)                              | 37 |

|   |      | 2.1.3   | High Level Domain Specific Languages                                                 | 38 |

|   |      |         | 2.1.3.1 Pyretic                                                                      | 38 |

|   |      |         | 2.1.3.2 Protocol-Oblivious Forwarding (POF)                                          | 38 |

|   |      |         | 2.1.3.3 Network Assembly Language (NetASM)                                           | 39 |

|   |      |         | 2.1.3.4 Programming Protocol-Independent Packet Processors (P4)                      |    |

|   |      | 2.1.4   | Control Plane API Abstractions                                                       |    |

|   |      |         | 2.1.4.1 OpenFlow (OF) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 44 |

|   |      |         | 2.1.4.2 Switch Abstraction Interface (SAI)                                           | 45 |

|   |      |         | 2.1.4.3 Ethernet Switch Device Driver Model (switchdev)                              | 46 |

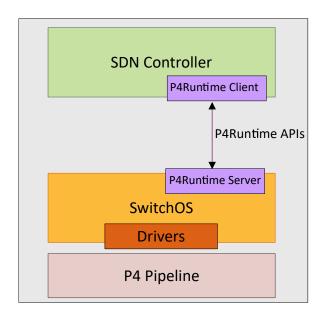

|   |      |         | 2.1.4.4 P4Runtime (PRT) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        | 46 |

|   | 2.2  |         | ed Work                                                                              |    |

|   | 2.3  |         | uding Remarks                                                                        |    |

| 3 | Mul  |         | nitecture Compiler System for Abstract Dataplanes                                    |    |

|   | 3.1  | Archit  | tecture                                                                              | 51 |

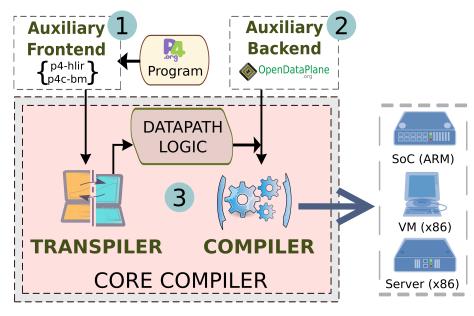

|   |     | 3.1.1  | Auxiliary Frontend                                                                                                                                                     |

|---|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.1.2  | Auxiliary Backend                                                                                                                                                      |

|   |     | 3.1.3  | Core Compiler                                                                                                                                                          |

|   |     |        | 3.1.3.1 Transpiler                                                                                                                                                     |

|   |     |        | 3.1.3.2 Compiler                                                                                                                                                       |

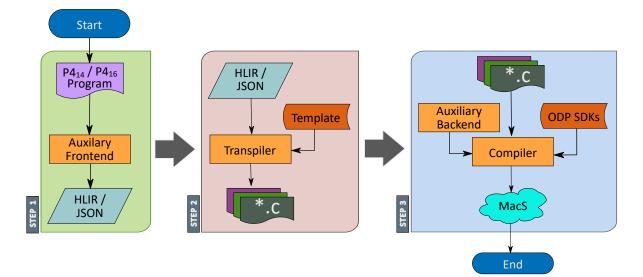

|   | 3.2 | Comp   | ilation Process $\ldots \ldots 55$                                                 |

|   | 3.3 | P4 to  | IR Code Generation $\ldots \ldots 56$                                              |

|   | 3.4 | Intern | al & Helper APIs                                                                                                                                                       |

|   | 3.5 | Source | e to Source Code Transformation $\ldots \ldots \ldots$ |

|   |     | 3.5.1  | Transforming Language Abstractions                                                                                                                                     |

|   |     | 3.5.2  | Auto-generating Data Path Logic                                                                                                                                        |

|   | 3.6 | Featur | res of Architecture                                                                                                                                                    |

|   |     | 3.6.1  | Programmability                                                                                                                                                        |

|   |     |        | 3.6.1.1 Protocol Independent Parser                                                                                                                                    |

|   |     |        | 3.6.1.2 Protocol Independent Dataplane                                                                                                                                 |

|   |     | 3.6.2  | Portability                                                                                                                                                            |

|   |     | 3.6.3  | Contoller Support                                                                                                                                                      |

|   | 3.7 | Conclu | uding Remarks                                                                                                                                                          |

| 4 | Ехр | erimen | tal Evaluation                                                                                                                                                         |

|   | 4.1 | Testbe | ed Details $\ldots \ldots 75$                                                      |

|   | 4.2 | Use C  | ase Descriptions                                                                                                                                                       |

|   |     | 4.2.1  | Port Forwarding (PortFWD)                                                                                                                                              |

|   |     | 4.2.2  | Layer-2 Forwarding (L2FWD)                                                                                                                                             |

|   |     | 4.2.3  | Layer-3 Forwarding (L3FWDv4/v6) $\ldots \ldots \ldots$ |

|   |     | 4.2.4  | Network Address Translation (NAT)                                                                                                                                      |

|   |     | 4.2.5  | Data Center Gateway (DCG) with VXLAN                                                                                                                                   |

|   |     |        | $4.2.5.1  \text{Download (DL)}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  84$                                                                            |

|   |     |        | 4.2.5.2 Upload (UL) $\dots \dots \dots$                                |

|   |     | 4.2.6  | Broadband Network Gateway (BNG)                                                                                                                                        |

|   |     |        | 4.2.6.1 Upload (UL) $\dots \dots \dots$                                |

|   |     |        | 4.2.6.2 Download (DL)                                                                                                                                                  |

|   | 4.3 | MacS   | Evaluation & Analysis                                                                                                                                                  |

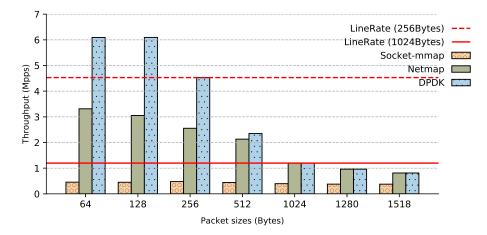

|   |     | 4.3.1  | Packet Rate Analysis                                                                                                                                                   |

|   |     |        | 4.3.1.1 Impact of FIB Sizes                                                                                                                                            |

|   |     |        | 4.3.1.2 Impact of Burst Sizes                                                                                                                                          |

|   |     |        | 4.3.1.3 Impact of Traffic Generators                                                                                                                                   |

|   |     | 4.3.2  | Latency Analysis                                                                                                                                                       |

|   |     | 4.3.3  | Performance Comparison Against Related Works                                                                                                                           |

|   | 4.4 | Perfor | mance Evaluation of MacS as Network Function                                                                                                                           |

|    | 4.5   | Adaptive Scalability by Dynamic CPU Core Allocation | . 110 |

|----|-------|-----------------------------------------------------|-------|

|    |       | 4.5.1 Results Analysis                              | . 110 |

|    |       | 4.5.2 Discussion                                    | . 112 |

|    | 4.6   | Concluding Remarks                                  | . 113 |

| 5  | Con   | nplexity Analysis                                   | 114   |

|    | 5.1   | Use Case Complexity                                 | . 114 |

|    | 5.2   | Machine Learning (Regression) Analysis              | . 117 |

|    |       | 5.2.1 Data Processing                               | . 119 |

|    |       | 5.2.2 Regression Models                             | . 121 |

|    |       | 5.2.3 Regression Analysis                           | . 125 |

|    | 5.3   | Concluding Remarks                                  | . 129 |

| 6  | Opt   | imization                                           | 131   |

|    | 6.1   | MACSAD Packet Processing Optimization               | . 131 |

|    | 6.2   | Evaluation and Analysis                             | . 134 |

|    | 6.3   | Concluding Remarks                                  | . 137 |

| 7  | Оре   | n Source Artifacts                                  | 139   |

|    | 7.1   | BB-Gen Tool                                         | . 139 |

|    | 7.2   | OpenDataPlane (ODP)                                 | . 142 |

|    |       | 7.2.1 Issues and Fixes for ODP                      | . 142 |

|    |       | 7.2.2 IPv6 support for LPM Lookup in ODP            | . 143 |

|    |       | 7.2.3 Contribution for odp-thunderx                 | . 143 |

|    | 7.3   | Additional Open-source Contributions                | . 143 |

|    | 7.4   | Concluding Remarks                                  | . 145 |

| 8  | Futu  | ure Works & Conclusions                             | 146   |

|    | 8.1   | Future Works                                        | . 146 |

|    | 8.2   | Conclusions                                         | . 147 |

| Bi | bliog | raphy                                               | 149   |

| A  | NNE)  | K A Layer 2 Forwarding (L2FWD)                      | 155   |

|    | A.1   | L2FWD $P4_{14}$ Program                             | . 155 |

|    | A.2   | L2FWD $P4_{16}$ Program                             | . 156 |

|    | A.3   | Dependency Graphs for L2FWD Use Case                | . 159 |

| A  | NNE>  | K B Layer 3 Forwarding (L3FWD)                      | 160   |

|    | B.1   | L3FWDv4 $P4_{14}$ Program                           | . 160 |

|    | B.2   | L3FWDv6 $P4_{14}$ Program                           | . 162 |

|    | B.3   | L3FWDv4 $P4_{16}$ Program                           | . 164 |

|    | B.4   | Dependency Graphs for L3FWDv4 Use Case              | . 167 |

|    | B.5   | Dependency Graphs for L3FWDv6 Use Case              |       |

| A  | NNE)  | K C Network Address Translation (NAT)               | 169   |

|    | C.1   | NAT $P4_{14}$ Program                               | . 169 |

| C.2   | Dependency Graphs for NAT Use Case  | 174 |

|-------|-------------------------------------|-----|

| ANNEX | C D Data Center Gateway (DCG)       | 175 |

| D.1   | DCG $P4_{14}$ Program               | 175 |

| D.2   | Dependency Graphs for DCG Use Case  | 185 |

| ANNEX | K E Broadband Network Gateway (BNG) | 186 |

| E.1   | BNG $P4_{16}$ Program               | 186 |

| E.2   | Dependency Graphs for BNG Use Case  | 197 |

## 1 Introduction

Internet ubiquity paints networking devices as gateways which guides the network packets across, and depicts the task as simple and mundane. In fact, according to (CLARK, 1988), the design philosophy behind the fundamental structure of the Internet was to make it simple and easy for the Internet to grow, and to allow different networks to connect together using routers. The advancements in switch & router hardware technologies tell a different story though. To bring myriads of different networks of Internet together, and to accommodate newer requirements of data centers and other private networks, switches & routers are becoming much more complex supporting multitudes of protocols.

Although switch evolution is predominantly performance driven, recent past has seen a steady increase in the number of protocols too. supported raising the complexity of switch design. This protocol driven development process is archaic and relatively slow being of 3-5 years cycle. while slow development cycle limits the fallback option for manufacturer when the new protocol is not adopted by consumers, it also keeps increasing the complexity of hardware design making the maintenance a difficult task. This inherent inflexibility in switch design, or simply data plane design, restricts manufacturers to stay involved in proprietary switch development driving platform specific developments. Research works focusing on network flexibility are sparse at best. The difficulty in understanding the flexibility of network design and data plane design can be attributed to its multiple definitions focusing on different aspects of network. To strengthen our understanding of flexibility, our thesis tries conceptualizing innovative ideas of networking to bring flexibility to switches describable in terms of many different measures, such as *programmability, portability, performance,* and *scalability* (3PS).

### 1.1 Background and Motivation

Networking industry has been virtuous to borrow different technologies from other fields of research. A cursory throwback at the history of network evolution reveals that two of the promising solutions for networking hardwares namely *Disaggregation* and *Virtualization* are borrowed from other industries to bring flexibility to networking hardware, network functions and the network itself. Disaggregation was the key to 'open networking' and allowed the industry to move towards standard products with an open design to drive the networking industry. It gave birth to today's bare metal switches followed by numerous Network Operating System (NOS). By opening the hardware design, Switch costs plummeted and put hardware in the hands of the researchers and academicians. Similarly, following the footsteps of server and storage virtualization, network professionals started rethinking networking devices as virtualized devices instead as standalone devices helping data center advancements. Then the advent of cloud pushed networking industry to adopt virtualization as a first citizen and put central control as a new requirement bringing centrally managed networks. Although these developments did not directly translate to bringing programmability to devices for which SDN strives for, they indeed set the foundation for our current research discussions and for the future networks.

In general, any packet switch<sup>1</sup> architecture comprises of two main components consisting of data plane and control plane where data plane is responsible for packet forwarding, while control plane serves data plane to define the datapath and its rules. Software-Defined Networking (SDN) (KREUTZ et al., 2015) paradigm, a new school of thought, advocates separation of the control plane from the data plane in the switch. It allows programming the network control plane by managing the routing protocols on a logically centralized server instead of at the switch. To truely adopt SDN paradigm, a equally similar level of flexibility is necessary from data plane too. However, only limited programmability was also brought to data plane by the programmable chips. Programmable chips bring flexibility, specifically programmability, to switch in terms of loosely defined tables characterized by its size, lookup algorithm, and so forth. To be exact, OpenFlow protocol (MCKEOWN et al., 2008) became fundamental in guiding the industry to popularize and adopt match + action abstractions to configure switch tables, and can be considered as a *de facto* standard for defining programmable data planes facilitated by programmable chip designs. As a result of this movement, some equipment vendors successfully released products in limited numbers supporting SDN and OpenFlow. But none the less a data plane design independent of supported protocol and underlying target remained far from reach.

This brief history leads us to our current research work and discussion. In a conventional network, each comprising network device maintain a set of network applications running routing algorithms to generate the network rules for the network traffic to follow. The control plane of these devices are responsible to propagate these rules to the data planes which simply forward packets accordingly. The co-existence of both control plane and data plane has limited the development to the opening and standardization of the APIs between them. *Disaggregation* bridles the inflexibility to a small extent in designing the network devices and brings support for different NOSs ushering *Portability*. Furthermore, following SDN principle, control plane and data plane i.e., software and hardware entity of switches can be separated in every network device in a network by centralizing all the control planes in a separate unified logical entity leaving the data planes to operate individually bringing programmability to the network architecture over its control plane.

<sup>&</sup>lt;sup>1</sup> Switch is used to refer both switch and router in this thesis as modern literature considers switches as L2-L7 switches.

And we envision the proliferation of *Programmability* into the less explored entity, the data plane too; realization of a fully flexible network device. With this we bring focus to the flexibility requirements in terms of Portability and Programmability of switches.

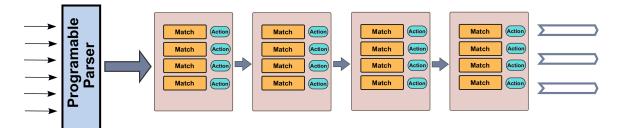

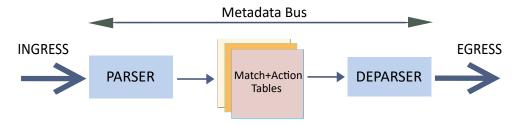

Data plane programmability related research mainly focuses on three different levels: data plane architecture, domain specific language and low-level SDK to define a data plane. Current advancements in programmable data plane architectures, Reconfigurable Match Tables (RMT) (BOSSHART et al., 2013), disaggregated Reconfigurable Match-Action Table (DRMT) (CHOLE et al., 2017), or Protocol Independent Switch Architecture (PISA) (MCKEOWN, 2015) to name a few, promise to offer flexibility in data plane allowing post-fabrication reconfiguration by manufacturers and consumers. In a simple manner, a switch data plane extracts network packet header informations and matches the extracted information against the flow table rules followed by performing associated actions before forwarding the network packet out. These two packet processing activities, also known as header parsing & table lookup, are identified as design abstractions in data plane architectures: parser and match + action table abstractions. Domain Specific Languages (DSLs) such as Protocol-oblivious Forwarding (POF) (SONG, 2013) and Programming Protocol-Independent Packet Processors (P4) (P. Bosshart et al, 2014) understand these design abstractions and offers intuitive language constructs to implement these design abstractions. Meanwhile, OpenDataPlane (ODP) (OPENDATA-PLANE, 2018), a powerful low-level SDK, provides a compiler system necessary to define a target switch using these design abstractions. In a nutshell, we feel the necessity of a unified multi-architecture compiler system comprising of compatible set of data plane architecture, DSL, low-level SDK, and a target compiler crucial for flexible programmable data plane.

Introduction of programmability into data plane has its own side effects and brings new challenges. Data plane programmability gives away with the fixed protocol set, and allows consumers and operators to define custom protocols transforming the data plane from fixed-function *Protocol Dependent* into *Protocol Independent*. Flexibility in data plane brings challenges to control plane which until recently have been benefited by standardized Application Programming Interfaces (APIs) towards data plane. With custom protocols in place, the control plane needs to adapt to the pipeline definition every time the consumer redefines it. This gives rise to a new school of thought which advocates a alternate way to define a pipeline which can be input to both data plane and control plane, and helps in defining the messages and APIs among them. P4Runtime (PRT) (P4API, 2018), Openconfig, etc are some of the solutions currently available exploring this ideology. This allows a control plane to control any forwarding plane regardless of what protocols and features the underlying data plane supports.

### 1.2 Research Hypothesis

In the previous section, we explored data plane flexibility and the three aspects of data plane development. We have also identified different aspects of flexibility such as programmability, portability, performance, and scalability (3PS). The advancements in data plane architectures, availability of supported DSL to implement data plane design abstractions, and a powerful low-level SDK over a compiler system are the dictating factors to achieve a flexible data plane. By defining a data plane using the 'parser' & 'match+action' design abstractions from data plane architectures, it is possible to have a protocol independent data plane. We identify protocol independent nature as Programma*bility* aspect of Flexibility in a data plane. Following up, by adopting a multi-architecture low-level SDK we can bring the same data plane to different platforms while focusing on portability aspect of flexibility of the data plane. While Programmability & Portability are related to the design of the data plane, Performance & Scalability aspects of flexibility are more apt for the evaluation of the data plane. Simply put, our research encompasses both design and evaluation of flexible data plane. To define, our research hypothesis to aim for would be, An open-source multi-architecture compiler system towards data plane flexibility satisfying the ever so important contending features 3PS; programmability, portability, performance, and scalability; in our advancement to the future networks.

### 1.3 Thesis Approach & Contributions

The breadth of this research proposal spans along data plane flexibility while ignoring the interaction towards the control plane. Being said that, the primary focus is towards the practical aspects of building our proposed compiler system, MACSAD, with open-source or free components (whenever possible) available addressing data plane features and a thorough evaluation of MACSAD addressing different aspects of flexibility (i.e., 3PS). The contributions of this thesis includes different facets of MACSAD development and evaluation: A muti-architecture compiler system, MACSAD, to achieve flexible data plane; Evaluation of MACSAD inline to different aspects of flexibility; Complexity analysis of different use case pipelines & performance prediction using machine learning algorithms; Additional compiler optimization for MACSAD performance improvement; Multiple open-source artifacts developed along with MACSAD development. All the contributions are briefly explained and summarized in Table 1.

Table 1 – Research Directions.

#### Continuation of Table 1

#### multi-architecture compiler system

**Our Solution:** We explore our proposed **MACSAD** compiler system which can define a protocol-independent and target-independent pipeline by bringing P4 and ODP together.

Challenges: Lack of SOA. Slim research community.

Missing supporting tools such as benchmarking.

Explored In: chapter 3.

Related Publication: (PATRA et al., 2016)

#### multidimensional evaluation of MACSAD

**Our Solution:** MACSAD is evaluated for programmability, portability, performance, and scalability (3PS). We also evaluate MACSAD as VNF towards functional scalability. Finally we evaluate resource scalability with adaptive dynamic CPU allocation method.

Challenges: Creating similar test bed for different target architectures.

Choosing a common tool across architectures for benchmarking.

Explored In: chapter 4.

Related Publications: (PATRA et al., 2017)(PATRA et al., 2018)

#### use case complexity analysis

Our Solution: We compiled a list of complexity factors for different use cases.

We apply Regression based Machine Learning algorithms to create a model and predict performance of MACSAD.

**Challenges:** Lack of SOA related to complexity analysis. Difficulty in collecting data for Machine Learning algorithm.

Explored In: chapter 5.

#### compiler optimization

**Our Solution:** We improved MACSAD code auto-generation phase maximizing CPU-memory parallelism.

**Challenges:** Identifying common approach to code auto-generation for different pipelines where the underlying compiler can optimize the generated code efficiently. **Explored In:** chapter 6.

#### Continuation of Table 1

#### additional open-source artifacts

**Our Solution:** We created BB-Gen packet generator tool, and used it for all our evaluation experiments. We have multiple contributions as bug fixes and feature additions to P4 and ODP code bases.

**Challenges:** Necessity to have modular and user-friendly code base for BB-Gen. Adding P4 support for BB-Gen. Developing competence over the complex P4 and ODP code base to contribute.

Explored In: chapter 7.

Related Publications: (RODRIGUEZ et al., 2018) (CESEN et al., 2018a)

End of Table 1

#### 1.3.1 Multi-Architecture Compiler System for Abstract Dataplanes

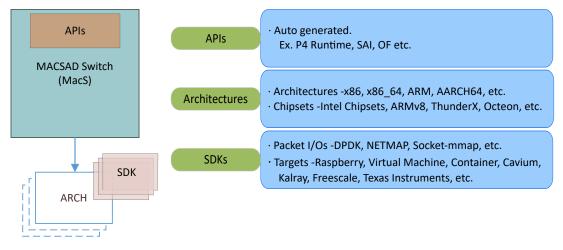

Our thesis proposal Multi-Architecture Compiler System for Abstract Dataplanes (MACSAD) blends the Top-Down approach of P4 towards protocol-independence and Bottom-Up approach of ODP towards target-independence. It is a cross-platform compiler system which incorporates low-level but target-independent (HW & SW) APIs from ODP to offer data plane over various network platforms including CPUs (flexible data path, lower performance) based on Complex Instruction Set Computing (CISC) like x86, Reduced instruction set computing (RISC) like Advanced RISC Machine (ARM) (highly multi-core) etc., In addition, MACSAD brings support to different packet I/Os too. In the big picture,dd MACSAD incorporates support for a number of features as shown in Figure 1 and provides us with numerous opportunities, albeit challenging, for carrying out different research activities.

Figure 1 – Supported Features envisioned by MACSAD

#### 1.3.2 Multidimensional Evaluation

We evaluate MACSAD with respect to Programmability, Performance, Portability, and Scalability (3PS) factors as explained here.

**Programmability** of MACSAD is affirmed by various use case pipelines presented in (PATRA *et al.*, 2018), (MEJIA *et al.*, 2018), (CESEN *et al.*, 2018b). In our effort towards protocol-independence, we bring diverse use cases with increasing complexity in terms of number of table lookups and table actions, and present a detailed evaluation of the use cases. The use cases supported on MACSAD include Layer 2 Forwarding (L2FWD), Layer 3 Forwarding (L3FWDv4/L3FWDv6), Network Address Translation (NAT), Data Center Gateway (DCG), and Broadband Network Gateway (BNG), to name them all.

**Portability** of MACSAD is explored by bringing the aforementioned use cases to different platforms like x86, ARMv6, and ARMv8 spanning Intel Servers, Raspberry Pi2, and Cavium switches. Apart from showing the feasibility of running MACSAD based data planes, we also evaluate the performance of data planes on the supported target platforms.

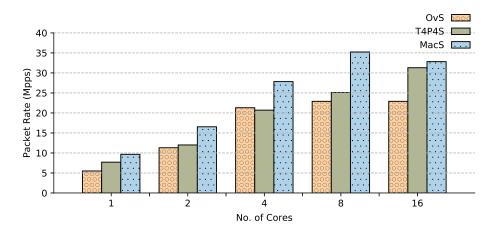

**Performance & Scalability** of MACSAD are evaluated and measured in terms of packet rate and latency of different use cases. We explore the performance results of on different platforms with a varied number of CPUs exploring the scalability aspect. We also put MACSAD against two related works (such as the P4 based switch T4P4S (LAKI *et al.*, 2016) and the DPDK-capable production quality open source software switch Open-vSwitch (OvS) (PFAFF *et al.*, 2015)) from Table 4 and evaluated their performance over different use cases.

In addition to the 3PS, we also explore two other aspects flexibility during evaluation of MACSAD. We evaluate the *resource scalability* by analyzing a novel technique providing dynamic CPU scaling through run-time (de)allocation of CPU cores in MAC-SAD data plane. Scaling up/down can be adaptive based on system load, on traffic workload, or other factors (e.g., energy consumption). Such behavior is instrumental in a multi-tenant environment, where de-allocated CPU cores could be used for other tasks.

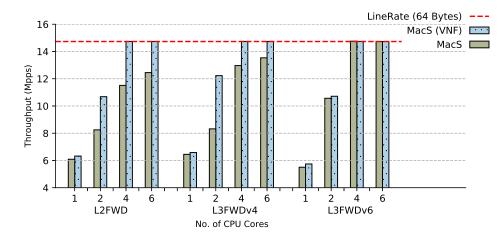

We stretched our evaluation activities to include functional scalability too. Functional scaling is achieved by deploying multiple instances of the network function, MAC-SAD data plane in our case, to achieve higher performance. This behavior is more prominent in a Network Function Virtualization (NFV) environment where scaling is achieved by instantiating a network function in multiple. We present MACSAD as a Virtual Network Function (VNF) and carry out the performance evaluation for the same to provide a glimpse into how MACSAD will behave in a NFV environment.

#### 1.3.3 Use Case Complexity Analysis

For evaluation of a switch or a Network Function (NF), it is necessary to build a methodology to identify the key components and factors (a.k.a. Complexity Factors) influencing the performance. This gives us an insight into the complexity of the use cases and opens more opportunity to bring complexity into consideration while discussing performance, portability or scalability. With sufficient information, it might be possible to come up with techniques to bring performance improvements too to the use cases. An earlier work (SAPIO et al., 2015) tried to measure the performance of NFs by identifying recurring execution patterns Elementary Operation (EO) and mapping them to the hardware. This work solely focuses on measuring performance in terms of packet rate. This gives us a glimpse into the Complexity Factors responsible for a NFs. We present our take on complexity analysis of P4 based pipelines and extend it to MACSAD. Based on (DANG et al., 2017), we have identified our *Complexity Factors* from the P4 programming language constructs. We explored all the use cases supported by MACSAD, and present the complexity details for all the P4 programs in Table 4. Then, we bring machine learning algorithms to analyze the complexity of the use cases using the *Complexity Factors* as features. We use Regression methodologies to learn the relationship between the use case complexities and their performance, and train different machine learning models to predict the performance of a MACSAD use case from its P4 program. This will allow to predict performance a data plane defined by a P4 program even before compiling it over to the target platform.

#### 1.3.4 Compiler Optimization

MACSAD implements a number of optimization techniques across its different modules. However, our work towards exploiting the memory-level parallelism between CPU and main memory (BHARDWAJ *et al.*, 2017) is important due to its clear impact on performance by targeting the memory-bound steps of packet processing, i.e., the table lookup step which consists of table key creation and the actual lookup step. Taking into account that the steps involved in different types of table lookups are most of the times similar, we implement batched table key creation and table lookup to exploit the memory level parallelism while hiding the CPU-memory latency. As explored in (WANG *et al.*, 2018), more than 70% of packet processing time is spent on table lookup in the datapath, and therefore this task focuses explicitly on table lookup.

#### 1.3.5 Additional Open-source Artifacts

Our work with MACSAD has pushed us to work on different ideas and projects giving rise to multiple contributions to the research community. We faced many difficulties in procuring test traffic data to evaluate MACSAD use cases. This inspired us to come up with our own tool BB-Gen (RODRIGUEZ et al., 2018) to overcome the hurdles towards agile data plane performance evaluation by its simplicity and effectiveness to generate network traffic and P4 table entries for different P4 use cases with augmenting complexity. Our other contributions are more focused on P4 and ODP source code and their features. We have contributed with new features such as IPv6 based LPM lookup method, and an extension to dependent graph generation module to the ODP and P4 repositories respectively. Apart from this, we have offered our help in providing a testbed for bug reproduction, for validating the patches for bug fixes, and also directly contributing patches to fix issues in ODP and P4 code repositories. In addition to these, we have provided all our research artifacts as open source for the research community to take advantage of.

#### 1.3.6 Noted Contributions

We present here all the contributions in terms of scientific publications accomplishing the breadth of this thesis from different fronts. All the collaborative efforts are described and referenced to the corresponding scientific article indicating the co-authors and their contributions. The inclusive list of publications is shown below.

- (A) Towards a Sweet Spot of Dataplane Programmability, Portability and Performance: On the Scalability of Multi-Architecture P4 Pipelines, *IEEE JSAC issue on Scalability Issues and Solutions for Software Defined Networks*, 2018, P. Gyanesh Patra, F. R. Cesen, J. S. Vallejo, D. L. Feferman, L. Csikor, C. E. Rothenberg, and G. Pongrácz.

- (B) Towards Realization of High Performance Programmable Datapaths using Domain Specific Language, Décimo Primeiro Encontro dos Alunos e Docentes do Departamento de Engenharia de Computação e Automação Industrial (XI EADCA), Campinas, Brazil, 2018, P. Gyanesh Patra, C. E. Rothenberg.

- (C) BB-Gen: A Packet Crafter for P4 Target Evaluation, ACM SIGCOMM'18 Demo and Poster Session, 2018, F. R. Cesen, P. Gyanesh Patra, L. Csikor, C. Rothenberg, P. Vörös, S. Laki, and G. Pongrácz.

- (D) Design, Implementation and Evaluation of IPv4/IPv6 Longest Prefix Match support in P4 Dataplanes, Csbc 2018 – 17° wperformance, 2018, F. R. Cesen, P. Gyanesh Patra, C. E. Rothenberg, and G. Pongrácz.

- (E) MACSAD: An Exemplar Realization of Multi-Architecture P4 Pipelines, 5th P4 Workshop, June 2018, P. Gyanesh Patra, F. Rodriguez, J. Mejia, D. Feferman, C. Rothenberg and G. Pongrácz.

- (F) BB-Gen: A Packet Crafter for Performance Evaluation of P4 Data Planes, 5th P4 Workshop, June 2018, Fabricio Rodriguez Cesen, P. Gyanesh Patra, Christian E. Rothenberg, Gergely Pongrácz.

- (G) BB-Gen: A Packet Crafter for Data Plane Evaluation, Salão de Ferramentas, 36th Brazilian Symposium on Computer Networks and Distributed Systems (SBRC 2018), May 2018, F. R. Cesen, P. Gyanesh Patra, and C. E. Rothenberg.

- (H) MACSAD: high performance dataplane applications on the move, 18th IEEE international conference on high performance switching and routing (HPSR), Brazil, 2017, P. Gyanesh Patra, C. E. Rothenberg, and G. Pongrácz.

- (I) MACSAD: Multi-Architecture Compiler System for Abstract Dataplanes (aka Partnering P4 with ODP), Acm sigcomm'16 demo and poster session, August 2016, P. Gyanesh Patra, C. E. Rothenberg, and G. Pongrácz.

The complete effort around MACSAD incorporates a number of collaborative activities which comprises tasks such as writing of P4 programs, contributing to open source projects and more. We acknowledge the contributions towards the development of P4 programs of the use cases such as L3FWDv6, Data Center Gateway (DCG), and Broadband Network Gateway (BNG) by the co-authors from item (A) (PATRA et al., 2018). In addition to the P4 programs, efforts contributing towards MACSAD source code in line to the DCG and BNG use cases are also acknowledged here. Likewise, item (D) shows the contributions to MACSAD implementing L3FWDv6 use case by the co-author. The contributions from the collaborators helping in carrying out the experiments, and collecting the results for burst size analysis and latency evaluation of MACSAD are detailed in chapter 4. Furthermore, a big credit to the co-author of (CESEN et al., 2018b) and (RODRIGUEZ et al., 2018) for the contributions towards additional artifacts of MACSAD (subsection 1.3.5) identified as IPv6 based LPM support for ODP and BB-Gen. Continuing on acknowledgments, we want to mention the Translator for P4 Switches (T4P4S) project team as the MACSAD development was bootstrapped from a part of the seed code that we shared with the initial phase of T4P4S project and became a part of Transpiler sub-module of MACSAD mentioned in subsubsection 3.1.3.1. Finally, We also acknowledge Ericsson Research Brazil for the financial support, and Ericsson Research Hungary for their support during the development of this thesis proposal.

We are delighted to receive contributions touching upon different aspects of MAC-SAD, and at the same time also immensely satisfied to be able to contribute to other's works as part of this thesis proposal and related tasks.

### 1.4 Outline

We begin with the state of the art and literature review of related technologies and related works presented in chapter 2. Following on, this thesis explores different problem classes while explaining the design and development of our proposed MACSAD (PATRA *et al.*, 2016; PATRA *et al.*, 2017; PATRA *et al.*, 2018) project in chapter 3. We present our evaluation of MACSAD around four characteristics of flexibility, namely, *performance*, *portability*, *programmability* and *scalability* (3PS) in chapter 4. We explore data plane complexity of different use cases followed by complexity analysis using machine learning algorithms in chapter 5. Then we bring our findings on compiler optimization activities in chapter 6. In chapter 7, we explain all our additional contributions that came out from our research activities which include an open source tool, addition of features to open source code repositories, bug fixes and many more. Finally, we present our conclusion with remarks for future goals and activities in chapter 8.

## 2 Literature Review

Programmable switches go way back to the beginning when the first ever switch, also known as Interface Message Processors (IMPs), was implemented in software with an initial data rates of 56kbit/s. Broad adoption of internet and growing demand of the World Wide Web (WWW) pushed the bandwidth requirement which was not feasible with the software switches anymore. In 1998 Juniper brought to market the wire-speed ASIC based router M40 with ten times the throughput of comparable contemporary Cisco products like CISCO 12000. After this, we see a flurry of ASIC based switches came out providing higher throughput year on year. Switches adhere to a vertically integrated two layers design with control plane and data plane, and referred as fixed-function devices. Although manufacturers kept adding more programmability to the hardware, it was always to support newer features whereas switches remain fixed-function for the consumers and operators.

OpenFlow (OF) (MCKEOWN *et al.*, 2008) came as a new effort from the research community to bring flexibility to the data plane. It permits flow entry updates of the switch lookup tables at runtime using standardized interfaces. Although this brings configurability to the data plane, OF still is restricted with its reliance on the fixed header structures of the supported standardized protocols. But, SDN (KREUTZ *et al.*, 2015) sought to break the vertical integration and advocates decoupling of control and data plane in a switch. It also takes the control plane to a centralized server bringing programmability to the control plan. A SDN control plane can control, configure and manage a whole network as it can have a network-wide view instead of a standalone device local view. Without vertical integration in a switch, and with sufficient programming capability of the hardware made the research community to rethink the internet in terms as it was created, i.e., over software. However, we extend the thought and present the idea as protocol-independent and target-independent data plane instead of just software based. We focus our discussion on the switch data plane aligning the discussions to our thesis.

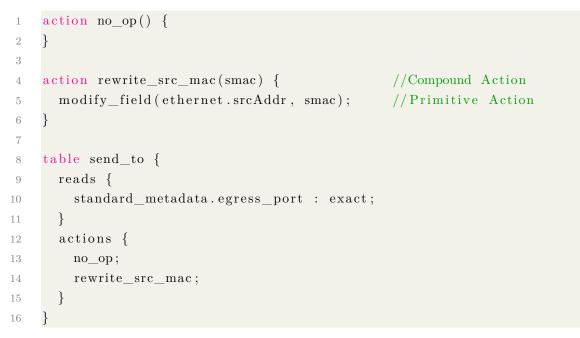

Data plane programmability is reimagined after the match+action table abstraction popularized by OF. Different DSLs (such as POF (SONG, 2013), P4 (P. Bosshart et al, 2014), Frenetic (FOSTER *et al.*, 2011), etc,.) tried to present the data plane in terms of design abstractions based on match action abstractions, and are explained later in this chapter. RMT (BOSSHART *et al.*, 2013) and DRMT (CHOLE *et al.*, 2017) are some of the packet switch architectures for designing the data plane which explored these abstractions in a more detailed manner as explained later. These DSL based design abstractions and packet switch architectures bring newer way to define protocol-interdependent and target-independent data plane which does not depend on any fixed header structures or protocols. This provides researchers an opportunity to run experimental protocols in their switches and internal networks.

Without the fixed protocols the controller or control plane are not aware of the data plane constructs to configure or manage the data plane. As a result project like PRT (P4API, 2018) came out of incubation which is a protocol-independent API and can be auto-generated from data plane definitions written in P4 DSL. PRT envisions to be able to control any data plane and remain auto updated when data plane features changes. We will present a brief description of PRT in this chapter for the sake of completeness of the discussion though PRT is out of the purview of this thesis.

Apart from these a number of different tools and projects are also discussed which are essential in shaping our research proposal. We present the state of the art under two different sections such as "related technologies" and "related works". *Related Technologies* section includes the tools and projects which has been part of our proposal project and been an influencer. Similarly, *Related Works* section presents the many projects form the community which are more closer to our research proposal among the state of the art and had direct or indirect impact towards finalizing this thesis.

In a nutshell, our research proposal integrates PISA (MCKEOWN, 2015) (subsubsection 2.1.2.3) design abstraction, P4 DSL (subsubsection 2.1.3.4), and ODP (OPEN-DATAPLANE, 2018) (subsubsection 2.1.1.4) packet IO framework under the MACSAD umbrella system to create programmable software switch for multiple target architectures.

### 2.1 Related Technologies

Given the reborn interest in network programmability through SDN and the growing interest in data plane abstraction activities (e.g., P4, SAI, ODP), we focused ourselves on studying the emergent ecosystem of data plane abstraction technologies. Feasibility studies along with performance and portability comparison among various data plane abstraction technologies and HW targets will provide the required understanding about where the current solutions stand at and where we are heading to. Results from these studies contribute to the roadmap of our proposal by contributing knowledge about different technologies and in general contributing towards making more informed technological decisions.

#### 2.1.1 Packet IOs

Until recently the software-based packet forwarding was limited by the capability of Linux kernel based packet forwarding infrastructure. Soon it became clear that to achieve better packet rate it is necessary to take the feature out of the kernel and provide more flexibility to the user. Features such as userspace memory-mapping to the packet buffers of NICs and introduction of hugepage memory system were a boost to this development giving rise to fast packet processing solution like DPDK (DPDK..., 2010). We witness a number of new advancements in relation to different packet IO frameworks leading the race headed for high forwarding throughput in programmable software switches.

#### 2.1.1.1 FD.io (Fast data – Input/Output)

FD.io is the recent entrant and brings several open source projects and libraries to support flexible and programmable data plane application on a generic hardware platform. It can deliver high-throughput and low-latency services over different architectures and deployment environments. The key component of FD.io would be the Vector Packet Processing (VPP) library donated by Cisco which is extremely modular and allows adding new capabilities as additional graph nodes with zero modification to the underlying code base. It was adopted under The Linux Foundation Networking Fund ("LFN") in January 2018 demonstrating the confidence of the Linux community for this project and providing long term support for the code base.

#### 2.1.1.2 Netmap

Netmap (RIZZO, 2012) is also a fast packet processing I/O framework implemented as a kernel module. It allows the data applications to work using *netmap* seamlessly driver when available without requiring any changes to the applications. It offers zero-copy, batched IO and other features while limited by the absence of any APIs supporting inherent hardware acceleration. It achieves high performance by implementing memory mapping to the packet buffers of NICs. Netmap drivers exist completely in the kernel, and the system does not rely on IOMMU or other special mechanisms. It is a clean solution without disrupting the Linux Kernel-based packet IO framework and is integrated by the BSD kernel. It can be a go-to solution if upstream support of Netmap for relevant NIC drivers and kernel developers can be possible.

#### 2.1.1.3 Data Plane Development Kit (DPDK)

Data Plane Development Kit (DPDK) (DPDK..., 2010) is the most commonly used and widely adopted user space fast packet processing IO driver collection used for defining data plane and fast packet processing on a wide variety of CPU architectures. Started by Intel in 2010, it is currently an open-source project under the Linux Foundation. It offers a multi-core framework for users to build vendor-neutral software and data plane applications. DPDK is heavily optimized for Intel® architectures. It uses hugepages to reduce TLB flushes and achieve higher packet throughput performance. It also implements features like zero-copy, batched I/O and Non-Uniform Memory Access (NUMA) support.

#### 2.1.1.4 OpenDataPlane (ODP)

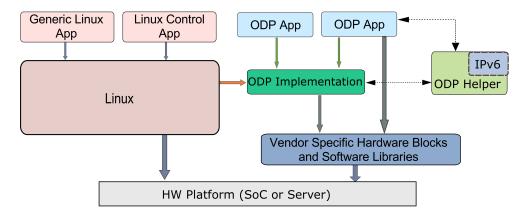

OpenDataPlane (ODP) (OPENDATAPLANE, 2018), a new entrant, has emerged to provide an abstract APIs specification to support Linux based network applications. ODP establishes a set of higher level common APIs spanning equivalent features across multiple targets mentioned in Table 2 making data plane applications portable. ODP can be compared to OpenGL as being the common standard for programming networking devices instead of video graphics. ODP establishes itself as a higher abstraction than DPDK and Netmap, and provide support for them as underlying fast packet IO technologies. It extends the highly-optimized vendor-specific Software Development Kits (SDKs) while abstracting the hardware acceleration features (e.g., Crypto) of the underlying hardware. OpenDataPlane project is created to offer an open-source, and cross-platform set of APIs for any networking data plane. Two important components of ODP are ODP API specification and ODP API implementation.

Figure 2 – Where ODP is situated?

ODP API specification describes a functional model for data plane applications. It covers the common features across multiple targets and also common programming requirements. Basic data plane application programming requirements such as packet receive and send (also known as Packet IO) are defined under the specification without specifying their implementation. It goes beyond this by describing the ODP APIs using abstract data types leaving their definition to the ODP implementers. For example, ODP packets are referenced by abstract type odp\_packet\_t whereas the actual implementation of it is the responsibility of ODP implementers.

Under current practice, the ODP implementations available for different platforms are implementations of the ODP API specification tailored for each platform. This design practice allows hardware offloading to be implemented for some APIs in a specific platform which might not be possible in another platform. From the application point of view, the underlying functional behavior is independent of the platform level implementation details of the ODP APIs. This is very important as ODP thrives on the balance of ODP Implementations to be open sourced vs. left up to the semiconductor vendor. The vendors decide whether to opt for open sourced or proprietary implementation of the ODP APIs. Developers can write data plane applications without being an expert of the underlying platform only by confirming to the ODP API specification.

Figure 2 shows the scope of ODP in a switch platform complementing the vendor specific SDKs by providing common set of APIs transforming ODP portable across supported platforms mentioned in Table 2. The blue rectangle in Figure 2 shows how the data plane applications and ODP APIs co-relate to the vendor specific hardware blocks and libraries. We use ODP as part of our compiler system to bring portability for the data plane applications.

| Company           | Supported Platforms                           | Architecture    |

|-------------------|-----------------------------------------------|-----------------|

| Cavium Networks   | Cavium Octeon <sup><math>TM</math></sup> SoCs | MIPS64          |

| Cavium networks   | Cavium ThunderX <sup>TM</sup> SoC             | ARMv8           |

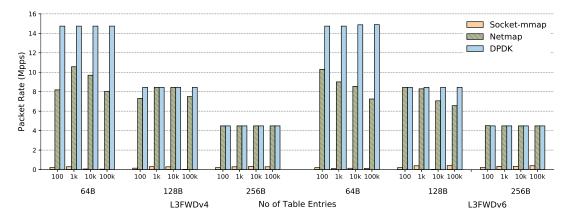

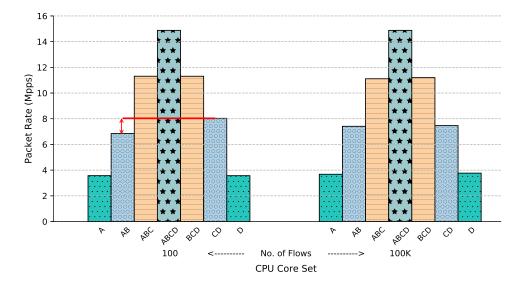

| Kalray            | MPPA platform                                 | MPPA            |