Universidade Estadual de Campinas Instituto de Computação

Luan Cardoso dos Santos

# Software implementation of authenticated encryption algorithms on ARM processors

Implementação em software de cifradores autenticados para processadores ARM

> CAMPINAS 2018

### Luan Cardoso dos Santos

# Software implementation of authenticated encryption algorithms on ARM processors

# Implementação em software de cifradores autenticados para processadores ARM

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science.

#### Supervisor/Orientador: Prof. Dr. Julio César López Hernández

Este exemplar corresponde à versão final da Dissertação defendida por Luan Cardoso dos Santos e orientada pelo Prof. Dr. Julio César López Hernández.

### CAMPINAS 2018

Agência(s) de fomento e nº(s) de processo(s): Não se aplica.

Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Santos, Luan Cardoso dos, 1993-Software implementation of authenticated encryption algorithms on ARM processors / Luan Cardoso dos Santos. – Campinas, SP : [s.n.], 2018.

Orientador: Julio César López Hernández. Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Microprocessadores ARM. 2. Arquitetura de computador. 3. Criptografia de dados (Computação). 4. Engenharia de software. 5. Engenharia de software - Medidas de segurança. 6. Software - Medidas de segurança. 1. López Hernández, Julio César, 1961-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: Implementação em software de cifradores autenticados para processadores ARM Palavras-chave em inglês: ARM microprocessors Computer architecture Data encryption (Computer science) Software engineering Software engineering - Safety measures Software – Safety measures Área de concentração: Ciência da Computação Titulação: Mestre em Ciência da Computação Banca examinadora: Júlio Cesar López Hernández Marcos Antonio Simplicio Junior Diego de Freitas Aranha Data de defesa: 12-06-2018 Programa de Pós-Graduação: Ciência da Computação

Universidade Estadual de Campinas Instituto de Computação

### Luan Cardoso dos Santos

# Software implementation of authenticated encryption algorithms on ARM processors

# Implementação em software de cifradores autenticados para processadores ARM

#### Banca Examinadora:

- Prof. Dr. Julio César López Hernández IC UNICAMP

- Prof. Dr. Marcos Antônio Simplicio Junior LARC - USP

- Prof. Dr. Diego de Freitas Aranha IC - UNICAMP

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 12 de junho de 2018

## Dedicatória Dedicated to

I dedicate this work to my father, Devaldite, who will always be in my heart, and will always be my inspiration to walk forward, to be a good man like him.

*Eu dedico esse trabalho a meu pai, Devaldite, que sempre está em meu coração, e que sempre será minha inspiração para seguir em frente, ser um homem bom como ele.*

The secret to doing anything is believing that you can do it. Anything that you believe you can do strong enough, you can do. Anything. As long as you believe.

## Acknowledgements

I want to thank all my friends, for their company helped me continue walking forward, even in hard times. My laboratory friends, who helped me with both life and research, always by my side. Some names to cite are Hayato and Renna, Camila and Klairton, Samuel and Fabianna, Amanda, Alisson, Rafael, Marcelo, Armando, Sheila, Renan, so many wonderful people I met in Unicamp –So many that it is impossible to type them all– they will always have a special place in my memory. And I thank my old friends as well, for Guilherme, Victor and Zé Lourenço were always there for me.

I thank my family, for trusting in me, and staying by my side, even if the distance and time make the contact difficult. *Enezina*, *Gabriel*, *Bruno*, *familia* é para sempre, e para sempre amo vocês.

I thank my teachers, Julio and Diego, which whom I worked closely, and learned a lot with. I have to thank you for helping me grow as a student, scientist, and most importantly, as a person. And I also thank all the teachers I had, even if our time was short, every lesson was important.

I also thank LGE, and it's team, for financing the research, and directly helping me, financially and technically with this Master's Degree.

And a very special thanks to Michael Trautsch, a great friend, that adopted me as his little brother, and who helped me and guided me through hard times. And also a very special thanks to his parents, Ute and Winfried, for they received me with open arms, as part of their family. *Mike*, *Ute*, *Winfried*, *Ihr seid meine zweite Familie; mein zweites Zuhause. Ich werde immer dafür dankbar sein*, *Euch in meinem Leben zu haben*.

And to all those that I may not have mentioned by name, but were with me during these years, my sincere thank you.

## Resumo

Algoritmos de cifração autenticada são ferramentas usadas para proteger dados, de forma a garantir tanto sigilo quanto autenticidade e integridade.

Implementações criptográficas não possuem apenas exatidão e eficiência como seus principais objetivos: sistemas computacionais podem vazar informação sobre seu comportamento interno, de forma que uma má implementação pode comprometer a segurança de um bom algoritmo. Dessa forma, esta dissertação tem o objetivo de estudar as formas de implementar corretamente algoritmos criptográficos e os métodos para optimizá-los sem que percam suas características de segurança. Um aspecto importante a ser levado em consideração quando implementando algoritmos é a arquitetura alvo. Nesta dissertação concentra-se na família de processadores ARM. ARM é uma das arquiteturas mais utilizadas no mundo, com mais de 100 bilhões de chips vendidos.

Esta dissertação foca em estudar e implementar duas famílias de cifradores autenticados: NORX e Ascon, especificamente para processadores ARM Cortex-A de 32 e 64 bits. Descrevemos uma técnica de optimização orientada a *pipeline* para NORX que possui desempenho melhor que o atual estado da arte, e discutimos técnicas utilizadas em uma implementação vetorial do NORX. Também analisamos as características de uma implementação vetorial do Ascon, assim como uma implementação vetorial de múltiplas mensagens.

## Abstract

Authenticated encryption algorithms are tools used to protect data, in a way that guarantees both its secrecy, authenticity, and integrity.

Cryptographic implementations do not have only correctness and efficiency as its main goals: computer systems can leak information about their internal behavior, and a bad implementation can compromise the security of a good algorithm. Therefore, this dissertation aims to study the forms of correctly and efficiently implementing cryptographic algorithms and the methods of optimizing them without losing security characteristics. One important aspect to take into account during implementation and optimization is the target architecture. In this dissertation, the focus is on the ARM family of processors. ARM is one of the most widespread architectures in the world, with more than 100 billion chips deployed.

This dissertation focus on studying and implementing two different families of authenticated encryption algorithms: NORX and Ascon, targeting 32-bits and 64-bits ARM Cortex-A processors. We show a pipeline oriented technique to implement NORX that's faster than the current state-of-art; and we also discuss the techniques used on a vectorial implementation of NORX. We also describe and analyze the characteristics of a vectorial implementation of Ascon, as well as a multiple message vectorial implementation.

# **List of Figures**

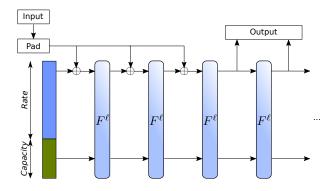

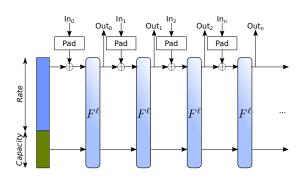

| 2.1  | The basic design of a sponge function                                      | 23 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | The basic design of a duplexed sponge                                      | 23 |

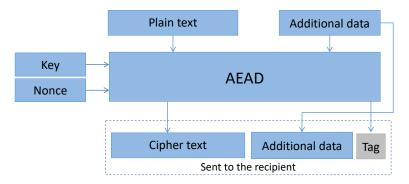

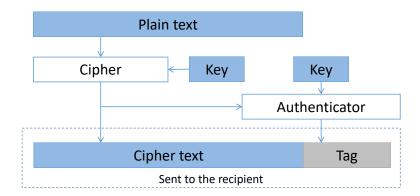

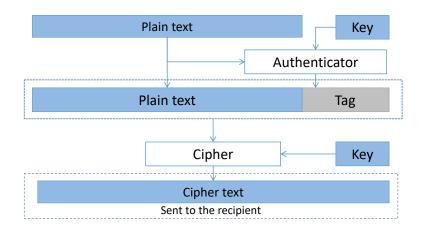

| 2.3  | Basic block design of AEAD                                                 | 24 |

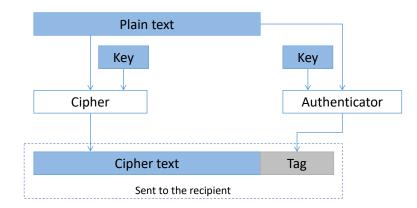

| 2.4  | Basic block diagram of a E&M authenticated mode of operation               | 25 |

| 2.5  | Basic block diagram of a EtM authenticated mode of operation.              | 25 |

| 2.6  | Basic block diagram of a MtE authenticated mode of operation.              | 26 |

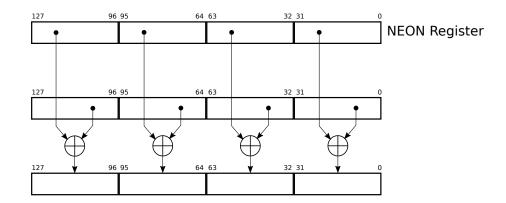

| 2.7  | Conceptual layout of a NEON instruction                                    | 35 |

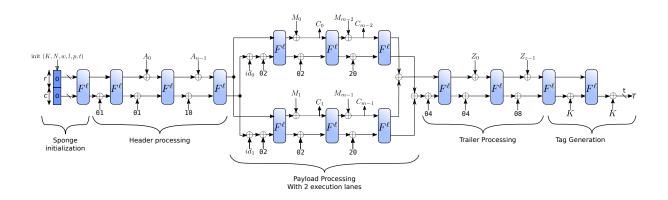

| 3.1  | The layout of NORX with parallelism degree $p = 2$                         | 42 |

| 3.2  | The layout of NORX with parallelism degree $p = 1 \dots \dots \dots \dots$ | 42 |

| 3.3  | Column and diagonal steps of NORX                                          | 43 |

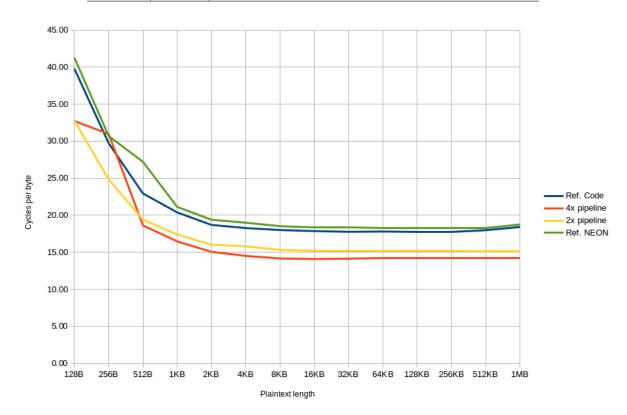

| 3.4  | Overheads for NORX 3261 running on a Cortex-A15(32-bit processor) .        | 52 |

| 3.5  | Overheads for NORX 6461 running on a Cortex-A53(64-bit processor) .        | 53 |

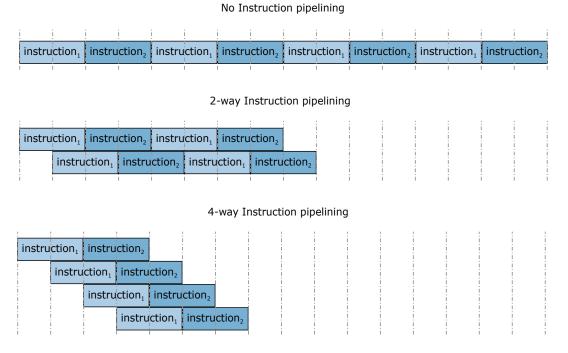

| 3.6  | Pipeline/instruction parallelism                                           | 54 |

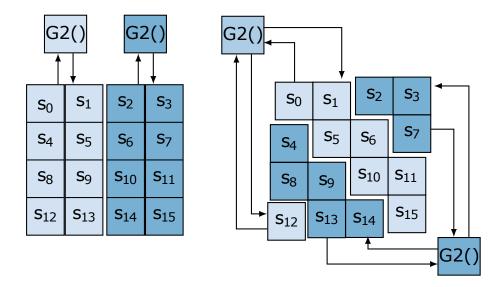

| 3.7  | $2 \times$ optimization of the NORX <i>F</i> function                      | 55 |

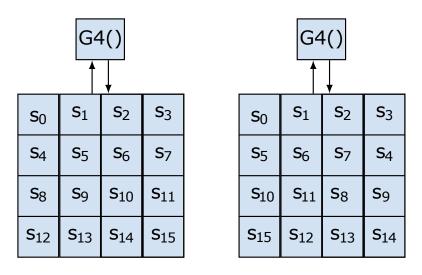

| 3.8  | $4 \times$ optimization of the NORX <i>F</i> function                      | 56 |

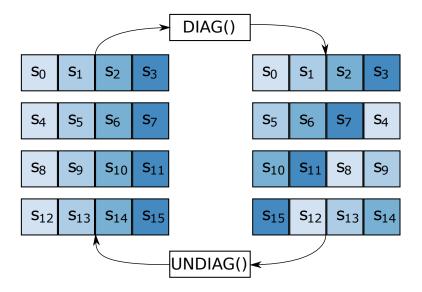

| 3.9  | Transformations needed for the diagonal step                               | 58 |

| 3.10 |                                                                            | 66 |

| 3.11 |                                                                            | 67 |

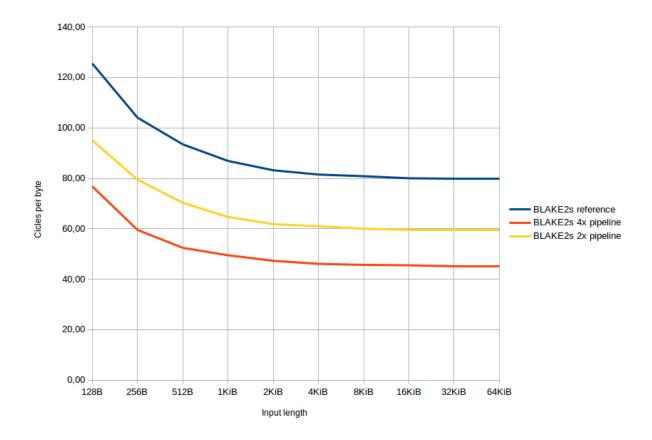

| 3.12 | Cycles per byte results for BLAKE2s on Cortex A15                          | 70 |

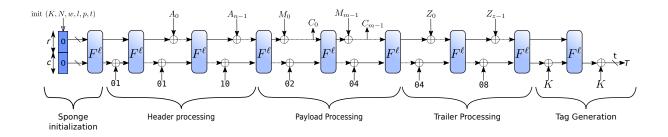

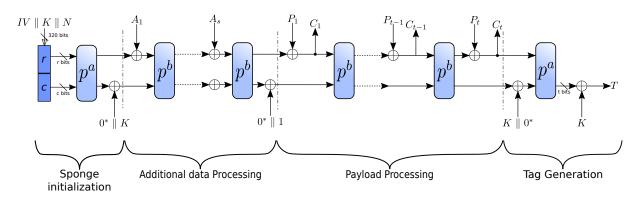

| 4.1  | Ascon mode of operation                                                    | 73 |

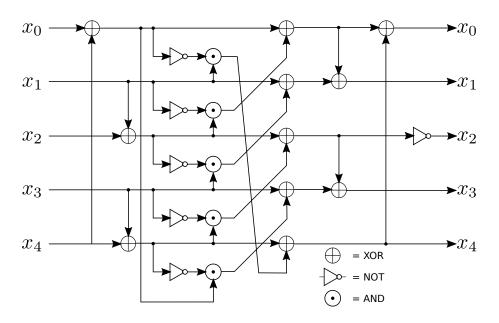

| 4.2  | Ascon Sbox                                                                 | 79 |

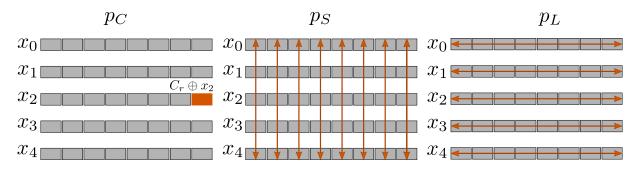

| 4.3  | Scopes in the internal state for each step of the permutation              | 80 |

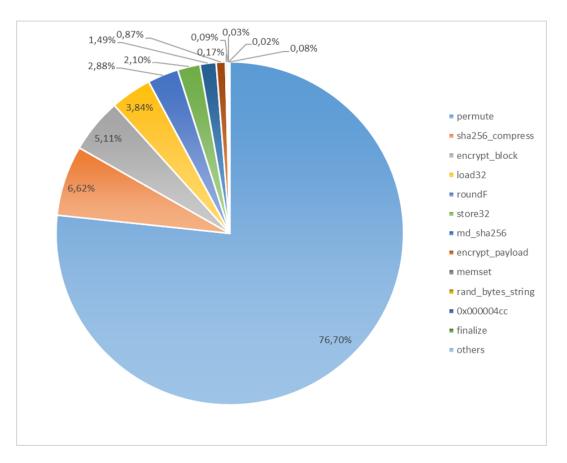

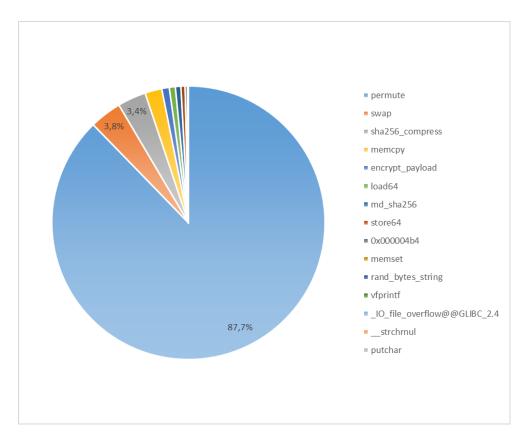

| 4.4  | Overheads for ASCON128 running on a Cortex-A15 (32-bit processor) .        | 81 |

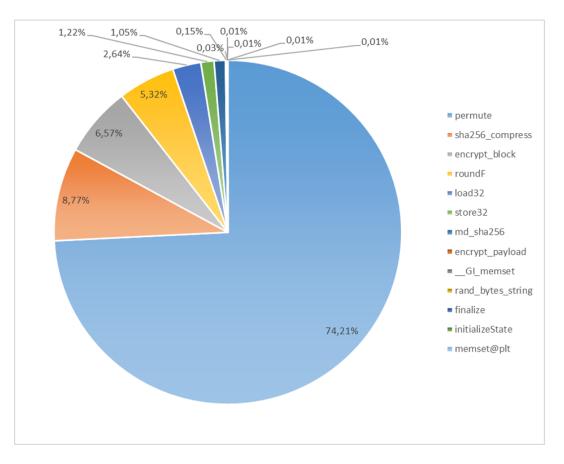

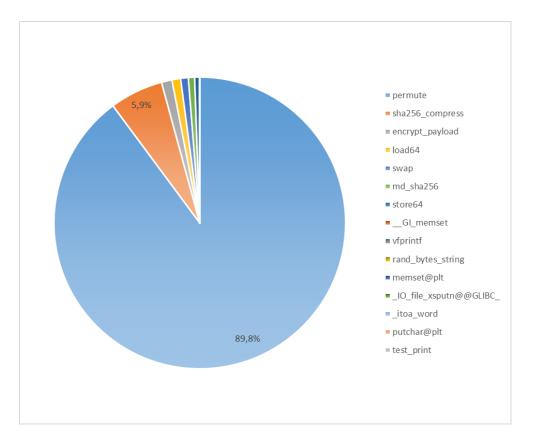

| 4.5  | Overheads for ASCON128 running on a Cortex-A53 (64-bit processor) .        | 82 |

| 4.6  | Sponge layout for the NEON implementation of ASCON                         | 84 |

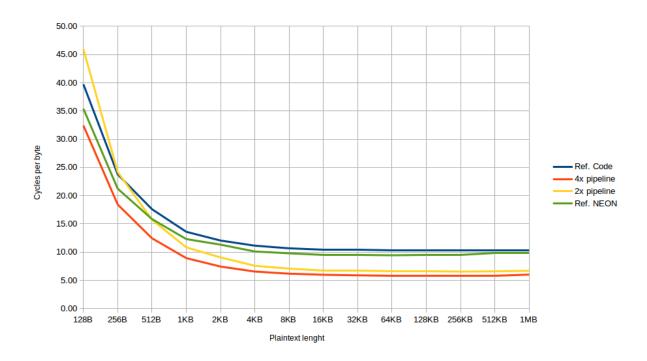

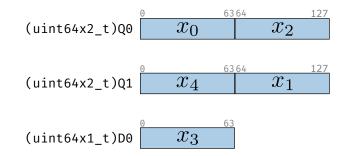

| 4.7  | CPB results for ASCON128 on Cortex A7                                      | 88 |

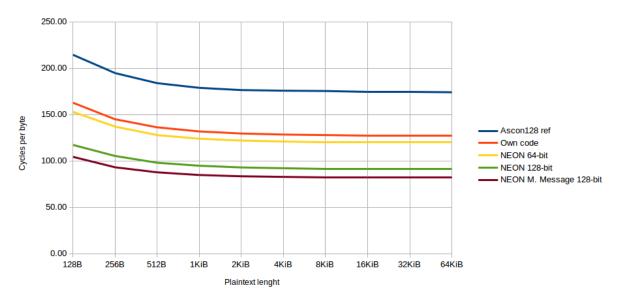

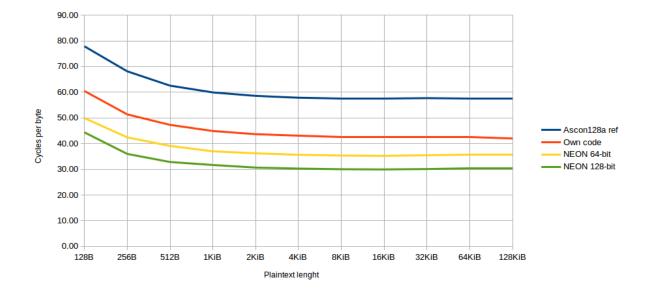

| 4.8  | CPB results for ASCON128a on Cortex A7.                                    | 89 |

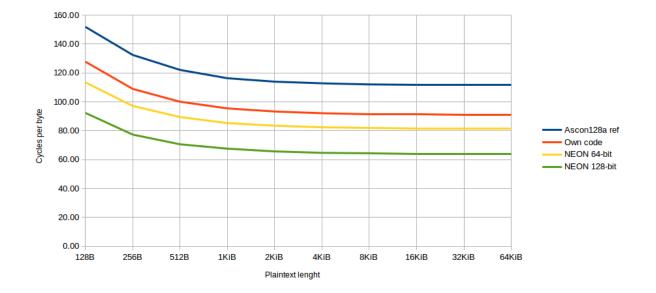

| 4.9  | CPB results for ASCON128 on Cortex A15                                     | 89 |

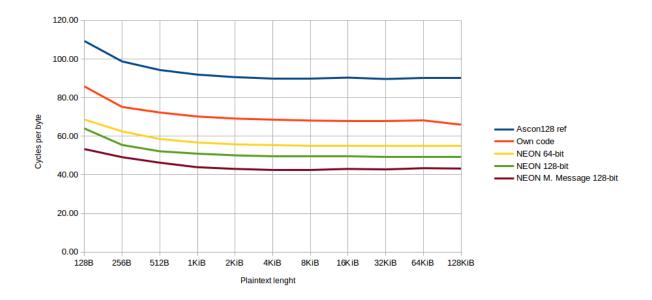

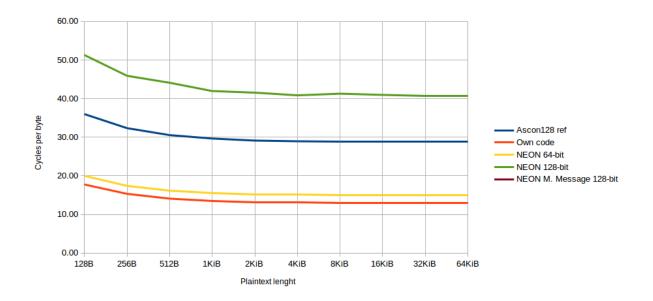

| 4.10 | CPB results for ASCON128a on Cortex A15                                    | 90 |

|      | CPB results for ASCON128 on Cortex A53.                                    | 90 |

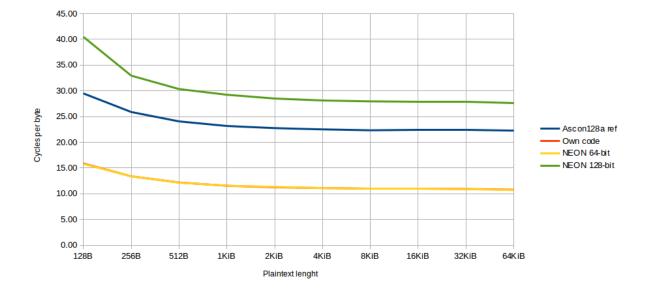

| 4.12 | CPB results for ASCON128a on Cortex A53                                    | 91 |

# **List of Tables**

| 1.1        | Notations used throughout this dissertation                            |

|------------|------------------------------------------------------------------------|

| 2.1<br>2.2 | Fourth round candidates of CAESAR.28Third-round candidates of CAESAR29 |

| 3.1        | The five instances of NORX 41                                          |

| 3.2        | Common Norx variables                                                  |

| 3.3        | NORX's rotation constants                                              |

| 3.4        | Norx domain separation constants                                       |

| 3.5        | Norx Initialization constants                                          |

| 3.6        | Cycles per byte for NORX encryption                                    |

| 3.7        | Cycles per byte for NORX encryption on the 64-bit platform             |

| 3.8        | Perfomance of NORX3261 on Cortex-M                                     |

| 3.9        | Cycles per byte for BLAKE2s digest                                     |

| 017        |                                                                        |

| 4.1        | Recommended instances of Ascon                                         |

| 4.2        | Common Ascon variables                                                 |

| 4.3        | Ascon Sbox                                                             |

| 4.4        | Times in CPB for ASCON128 on 32-bit processors                         |

| 4.5        | Times in CPB for ASCON128 on 64-bit processors                         |

| 4.6        | Costs of Ascon permutation on A53                                      |

| A.1        | Inputs for NORX 100                                                    |

| B.1        | Inputs for Ascon128                                                    |

| E.1        | Results in cycles per byte for NORX3261 on Cortex-A7                   |

| E.2        | Results in CBP for NORX3261 on Cortex-A15                              |

| E.3        | Results in cycles per byte for NORX3261 on Cortex-A53                  |

| E.4        | Results in cycles per byte for NORX3264 on Cortex-A7                   |

| E.5        | Results in cycles per byte for NORX3264 on Cortex-A15                  |

| E.6        | Results in cycles per byte for NORX3264 on Cortex-A53                  |

| E.7        | Results in cycles per byte for NORX6461 on Cortex-A7                   |

| E.8        | Results in cycles per byte for NORX6461 on Cortex-A15                  |

| E.9        | Results in cycles per byte for NORX6461 on Cortex-A53                  |

|            | Results in cycles per byte for NORX6464 on Cortex-A7                   |

|            | Results in cycles per byte for NORX6464 on Cortex-A15                  |

|            | Results in cycles per byte for NORX6464 on Cortex-A53                  |

|            |                                                                        |

| F.1        | Results in cycles per byte for ASCON128 on Cortex-A15                  |

| F.2        | Results in cycles per byte for ASCON128 on Cortex-A7                   |

| F.3 | Results in cycles per byte for ASCON128 on Cortex-A53  | 119 |

|-----|--------------------------------------------------------|-----|

| F.4 | Results in cycles per byte for ASCON128a on Cortex-A15 | 119 |

| F.5 | Results in cycles per byte for ASCON128a on Cortex-A7  | 119 |

| F.6 | Results in cycles per byte for ASCON128a on Cortex-A53 | 120 |

|     |                                                        |     |

# List of abreviations and acronyms

| AEAD Authenticated encryption with additional data                                                   |

|------------------------------------------------------------------------------------------------------|

| AES Advanced Encryption Standard                                                                     |

| AEAuthenticated encryption                                                                           |

| ARM Advanced RISC Machine                                                                            |

| ARXAdd-Rotate-XOR                                                                                    |

| CISC Complex instruction set computing                                                               |

| CPBCycles per byte                                                                                   |

| DDoS Distributed denial of service                                                                   |

| eBAEADECRYPT Benchmarking of Authenticated Ciphers                                                   |

| ECRYPTEuropean Network of Excellence for Cryptology                                                  |

| ENISA European Union Agency for Network and Information Security                                     |

| IoT Internet of Things                                                                               |

| LSB Least significant bit                                                                            |

| MAC Message authentication code                                                                      |

| MSB Most significant bit                                                                             |

| NIST National Institute for Standards and Technology                                                 |

| NSA National Security Agency                                                                         |

| RISC Reduced instruction set computing                                                               |

| SHASecure hashing algorithm                                                                          |

| SIMD                                                                                                 |

| SPN                                                                                                  |

| SUPERCOPSystem for Unified Performance Evaluation Related to Cryptographic Operations and Primitives |

| VM Virtual Machine                                                                                   |

|                                                                                                      |

## Contents

| 1 | Intr | oduction 17                                         |

|---|------|-----------------------------------------------------|

|   | 1.1  | Contributions of this work                          |

|   | 1.2  | Document structure                                  |

| 2 |      | kground 20                                          |

|   | 2.1  | Cryptography 20                                     |

|   |      | 2.1.1 Block ciphers                                 |

|   |      | 2.1.2 Lightweight cryptography                      |

|   |      | 2.1.3 Sponge Functions                              |

|   | 2.2  | Authenticated encryption                            |

|   |      | 2.2.1 Authenticated mode of operations              |

|   |      | 2.2.2 Dedicated AE(AD) schemes                      |

|   |      | 2.2.3 Current Standards                             |

|   | 2.3  | Cryptographic competitions                          |

|   |      | 2.3.1 CAESAR                                        |

|   |      | 2.3.2 CAESAR selection criteria                     |

|   | 2.4  | ARM Architecture                                    |

|   |      | 2.4.1 Cortex A processors                           |

|   |      | 2.4.2 SIMD instructions - NEON                      |

|   |      | 2.4.3 Cortex M processors                           |

|   |      | 2.4.4 Other lines of processors                     |

|   | 2.5  | Algorithm choice                                    |

|   | 2.6  | Software implementation for cryptographic functions |

|   | 2.7  | ARM Architecture: Target processors                 |

|   | 2.8  | Testing methodology                                 |

| 3 | Soft | ware implementation: NORX AEAD 40                   |

|   | 3.1  | Description of NORX family of algorithms            |

|   |      | 3.1.1 Padding                                       |

|   |      | 3.1.2 Domain separation constants                   |

|   |      | 3.1.3 Sponge initialization                         |

|   |      | 3.1.4 Absorption                                    |

|   |      | 3.1.5 Branching and Merging                         |

|   |      | 3.1.6 Encryption and decryption                     |

|   |      | 3.1.7 Finalization                                  |

|   |      | 3.1.8 Tag verification                              |

|   | 3.2  | Code profiling                                      |

|   | 3.3  | Permutation optimization 51                         |

|   |      |                                                     |

|        | 3.4                                                                         | Pipeline oriented optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 3.5                                                                         | NEON implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                  |

|        |                                                                             | 3.5.1 NEON word-wise rotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57                                                                                                                                                                                  |

|        |                                                                             | 3.5.2 Register wide rotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                                                                                                  |

|        |                                                                             | 3.5.3 NEON Permutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                                                                                                  |

|        | 3.6                                                                         | Other implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                                                                                  |

|        | 3.7                                                                         | Results and considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                                                                                                                                  |

|        | 3.8                                                                         | Applying the ideas to the BLAKE2 hash algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                                                                                                                                                                  |

| 4      | Soft                                                                        | ware implementation: Ascon AEAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                  |

|        | 4.1                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                                                                                                                  |

|        |                                                                             | 4.1.1 Ascon Mode of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72                                                                                                                                                                                  |

|        |                                                                             | 4.1.2 Padding rule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74                                                                                                                                                                                  |

|        |                                                                             | 4.1.3 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                                                                                                                                                                  |

|        |                                                                             | 4.1.4 Additional data processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                                                                                                                                                  |

|        |                                                                             | 4.1.5 Plaintext processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76                                                                                                                                                                                  |

|        |                                                                             | 4.1.6 Finalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77                                                                                                                                                                                  |

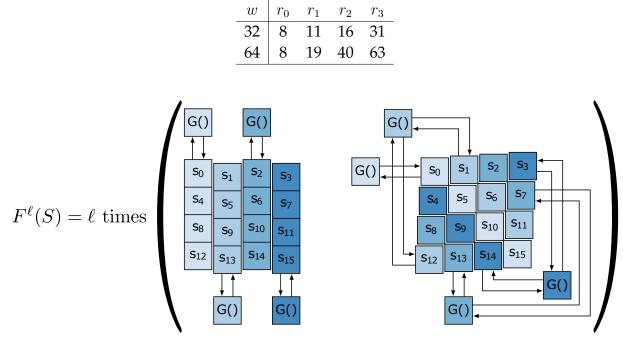

|        | 4.2                                                                         | Ascon permutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78                                                                                                                                                                                  |

|        | 4.3                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80                                                                                                                                                                                  |

|        | 4.3<br>4.4                                                                  | Code profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80                                                                                                                                                                                  |

|        | 4.4<br>4.5                                                                  | Results and considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86                                                                                                                                                                                  |

|        | 4.0                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00                                                                                                                                                                                  |

| 5      | Con                                                                         | clusion and final remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 92                                                                                                                                                                                  |

|        |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| Re     | feren                                                                       | nces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94                                                                                                                                                                                  |

|        | NOI                                                                         | RX test vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94<br>100                                                                                                                                                                           |

|        | NOI                                                                         | RX test vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

|        | NOI<br>A.1                                                                  | <b>RX test vectors</b> Computations of F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100                                                                                                                                                                                 |

|        | NOI<br>A.1                                                                  | <b>RX test vectors</b> Computations of F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>100</b><br>100                                                                                                                                                                   |

|        | NOI<br>A.1                                                                  | RX test vectors       Computations of F       Full AEAD computations       Full AEAD computations       Full AEAD computations         A.2.1       NORX32-4-1       Full AEAD computations       Full AEAD computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>100</b><br>100<br>100<br>100                                                                                                                                                     |

|        | NOI<br>A.1                                                                  | <b>RX test vectors</b> Computations of F Full AEAD computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>100</b><br>100<br>100<br>100<br>101                                                                                                                                              |

|        | NOI<br>A.1                                                                  | RX test vectors       Computations of F       Full AEAD computations       Full AEAD com | <b>100</b><br>100<br>100<br>100<br>101<br>101                                                                                                                                       |

|        | NOI<br>A.1                                                                  | RX test vectors       Computations of F         Full AEAD computations       A.2.1 NORX32-4-1         A.2.2 NORX32-6-1       A.2.3 NORX64-4-1         A.2.4 NORX64-6-1       A.2.4 NORX64-6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>100</b><br>100<br>100<br>101<br>101<br>101<br>102                                                                                                                                |