## Universidade Estadual de Campinas Instituto de Computação

# Marcus Felipe Botacin

# Hardware-Assisted Malware Analysis

Análise de *Malware* com Suporte de *Hardware*

#### Marcus Felipe Botacin

### Hardware-Assisted Malware Analysis

### Análise de Malware com Suporte de Hardware

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação, na área de Sistemas de Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science, in the Computer Systems area..

Supervisor/Orientador: Prof. Dr. Paulo Lício de Geus

Co-supervisor/Coorientador: Prof. Dr. André Ricardo Abed Grégio

Este exemplar corresponde à versão final da Dissertação defendida por Marcus Felipe Botacin e orientada pelo Prof. Dr. Paulo Lício de Geus.

#### Agência(s) de fomento e nº(s) de processo(s): CAPES

**ORCID:** http://orcid.org/0000-0001-6870-1178

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Márcia Pillon D'Aloia - CRB 8/5180

Botacin, Marcus Felipe, 1991-

B657h

Hardware-assisted malware analysis / Marcus Felipe Botacin. – Campinas, SP: [s.n.], 2017.

Orientador: Paulo Lício de Geus.

Coorientador: André Ricardo Abed Grégio.

Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Malware (Software). 2. Tecnologia da informação - Sistemas de segurança. I. Geus, Paulo Lício de,1956-. II. Grégio, André Ricardo Abed. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações para Biblioteca Digital

Título em outro idioma: Análise de malware com suporte de hardware

Palavras-chave em inglês: Malware (Computer software)

Information technology - Security measures Área de concentração: Ciência da Computação Titulação: Mestre em Ciência da Computação

Banca examinadora:

Paulo Lício de Geus [Orientador]

Carlos Alberto Maziero

Sandro Rigo

**Data de defesa:** 28-07-2017

Programa de Pós-Graduação: Ciência da Computação

### Universidade Estadual de Campinas Instituto de Computação

# Marcus Felipe Botacin

# Hardware-Assisted Malware Analysis

# Análise de Malware com Suporte de Hardware

#### Banca Examinadora:

- Prof. Dr. Paulo Lício de Geus IC/UNICAMP

- Prof. Dr. Carlos Alberto Maziero DInf/UFPR

- Prof. Dr. Sandro Rigo IC/UNICAMP

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 28 de Julho de 2017

# Acknowledgements

To my family, for supporting me.

To my friends, for walking along me.

To Paulo and André, for advising me since I was an undergraduate student.

# Resumo

O mundo atual é impulsionado pelo uso de sistemas computacionais, estando estes presentes em todos aspectos da vida cotidiana. Portanto, o correto funcionamento destes é essencial para se assegurar a manutenção das possibilidades trazidas pelos desenvolvimentos tecnológicos. Contudo, garantir o correto funcionamento destes não é uma tarefa fácil, dado que indivíduos mal-intencionados tentam constantemente subvertê-los visando benefíciar a si próprios ou a terceiros. Os tipos mais comuns de subversão são os ataques por códigos maliciosos (malware), capazes de dar a um atacante controle total sobre uma máquina. O combate à ameaça trazida por malware baseia-se na análise dos artefatos coletados de forma a permitir resposta aos incidentes ocorridos e o desenvolvimento de contramedidas futuras. No entanto, atacantes têm se especializado em burlar sistemas de análise e assim manter suas operações ativas. Para este propósito, faz-se uso de uma série de técnicas denominadas de "anti-análise", capazes de impedir a inspeção direta dos códigos maliciosos. Dentre essas técnicas, destaca-se a evasão do processo de análise, na qual são empregadas exemplares capazes de detectar a presença de um sistema de análise para então esconder seu comportamento malicioso. Exemplares evasivos têm sido cada vez mais utilizados em ataques e seu impacto sobre a segurança de sistemas é considerável, dado que análises antes feitas de forma automática passaram a exigir a supervisão de analistas humanos em busca de sinais de evasão, aumentando assim o custo de se manter um sistema protegido. As formas mais comuns de detecção de um ambiente de análise se dão através da detecção de: (i) código injetado, usado pelo analista para inspecionar a aplicação; (ii) máquinas virtuais, usadas em ambientes de análise por questões de escala; (iii) efeitos colaterais de execução, geralmente causados por emuladores, também usados por analistas. Para lidar com malware evasivo, analistas tem se valido de técnicas ditas transparentes, isto é, que não requerem injeção de código nem causam efeitos colaterais de execução. Um modo de se obter transparência em um processo de análise é contar com suporte do hardware. Desta forma, este trabalho versa sobre a aplicação do suporte de hardware para fins de análise de ameaças evasivas. No decorrer deste texto, apresenta-se uma avaliação das tecnologias existentes de suporte de hardware, dentre as quais máquinas virtuais de hardware, suporte de BIOS e monitores de performance. A avaliação crítica de tais tecnologias oferece uma base de comparação entre diferentes casos de uso. Além disso, são enumeradas lacunas de desenvolvimento existentes atualmente. Mais que isso, uma destas lacunas é preenchida neste trabalho pela proposição da expansão do uso dos monitores de performance para fins de monitoração de malware. Mais especificamente, é proposto o uso do monitor BTS para fins de construção de um tracer e um debugger. O framework proposto e desenvolvido neste trabalho é capaz, ainda, de lidar com ataques do tipo ROP, um dos mais utilizados atualmente para exploração de vulnerabilidades. A avaliação da solução demonstra que não há a introdução de efeitos colaterais, o que permite análises de forma transparente. Beneficiando-se desta característica, demonstramos a análise de aplicações protegidas e a identificação de técnicas de evasão.

# Abstract

Today's world is driven by the usage of computer systems, which are present in all aspects of everyday life. Therefore, the correct working of these systems is essential to ensure the maintenance of the possibilities brought about by technological developments. However, ensuring the correct working of such systems is not an easy task, as many people attempt to subvert systems working for their own benefit. The most common kind of subversion against computer systems are malware attacks, which can make an attacker to gain complete machine control. The fight against this kind of threat is based on analysis procedures of the collected malicious artifacts, allowing the incident response and the development of future countermeasures. However, attackers have specialized in circumventing analysis systems and thus keeping their operations active. For this purpose, they employ a series of techniques called anti-analysis, able to prevent the inspection of their malicious codes. Among these techniques, I highlight the analysis procedure evasion, that is, the usage of samples able to detect the presence of an analysis solution and then hide their malicious behavior. Evasive examples have become popular, and their impact on systems security is considerable, since automatic analysis now requires human supervision in order to find evasion signs, which significantly raises the cost of maintaining a protected system. The most common ways for detecting an analysis environment are: i) Injected code detection, since injection is used by analysts to inspect applications on their way; ii) Virtual machine detection, since they are used in analysis environments due to scalability issues; iii) Execution side effects detection, usually caused by emulators, also used by analysts. To handle evasive malware, analysts have relied on the so-called transparent techniques, that is, those which do not require code injection nor cause execution side effects. A way to achieve transparency in an analysis process is to rely on hardware support. In this way, this work covers the application of the hardware support for the evasive threats analysis purpose. In the course of this text, I present an assessment of existing hardware support technologies, including hardware virtual machines, BIOS support, performance monitors and PCI cards. My critical evaluation of such technologies provides basis for comparing different usage cases. In addition, I pinpoint development gaps that currently exists. More than that, I fill one of these gaps by proposing to expand the usage of performance monitors for malware monitoring purposes. More specifically, I propose the usage of the BTS monitor for the purpose of developing a tracer and a debugger. The proposed framework is also able of dealing with ROP attacks, one of the most common used technique for remote vulnerability exploitation. The framework evaluation shows no side-effect is introduced, thus allowing transparent analysis. Making use of this capability, I demonstrate how protected applications can be inspected and how evasion techniques can be identified.

# List of Figures

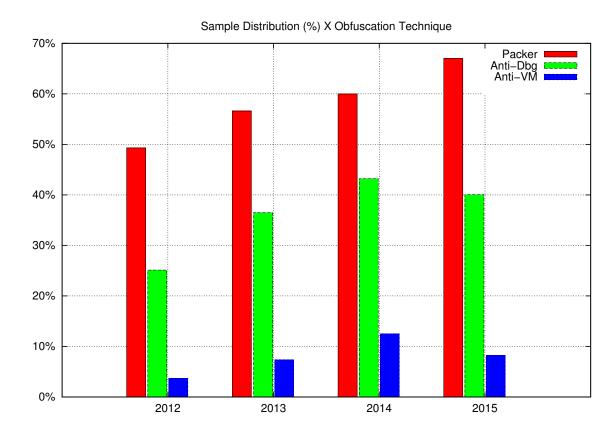

| 1.1                      | Anti-analysis technique usage evolution by sample (A sample may use more than one at a time). Source: [28]                      | 17             |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.1<br>2.2<br>2.3<br>2.4 | Abstraction levels for distinct monitoring techniques                                                                           | 26<br>26<br>28 |

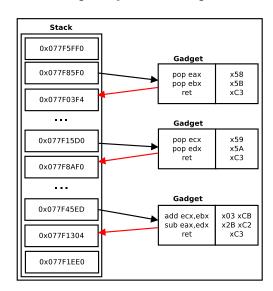

| 2.5<br>2.6               | right side illustrates how the possible gadgets look like                                                                       | 61<br>62       |

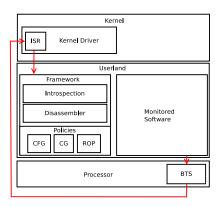

|                          | and policies are applied                                                                                                        | 66             |

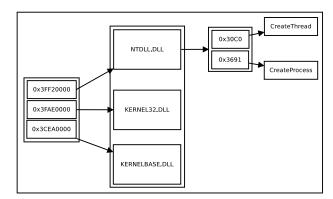

| 2.7                      | Instrospection mechanism: from raw addresses to functions                                                                       | 70             |

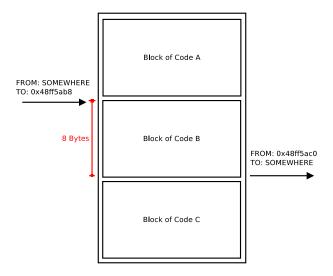

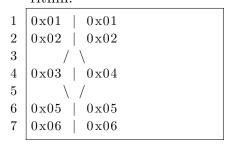

| 2.8                      | Block identification of two 8-bytes consecutive branches                                                                        | 72             |

| 2.9                      | Step-Into call graph, all intermediate calls represented                                                                        | 74             |

| 2.10                     | Step-Over call graph, only CALL/RET represented                                                                                 | 74             |

|                          | Reconstructed CFG from Listing 2.5 example code                                                                                 | 75             |

|                          | Step-into CFG                                                                                                                   | 77             |

| 2.13                     | Step-over CFG                                                                                                                   | 77             |

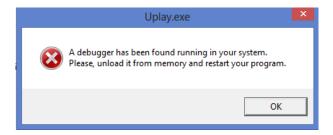

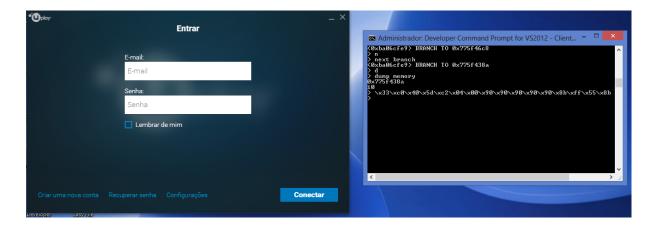

|                          | Uplay execution under an ordinary debugger                                                                                      | 82             |

| 2.15                     | Uplay execution under our solution                                                                                              | 82             |

| 2.16                     | Alert raised by our solution when an attack is detected                                                                         | 83             |

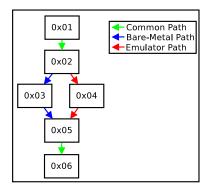

| 2.17                     | Example of a flow divergence between the code running on bare metal and                                                         | 0.0            |

| 0.10                     | on the emulated monitor                                                                                                         | 86             |

|                          | True divergence                                                                                                                 | 87             |

| 2.19                     | False divergence                                                                                                                | 87             |

| 3.1                      | Code Coverage. Example A. The blue values come from the green CALLs.  The last green value is the function return               | 104            |

| 3.2                      | Code Coverage. Example B. The blue value is the target of an external function call. The green value is an unconditional branch | 104            |

| 3.3                      | Code Coverage. Even Values. The gray instructions correspond to the                                                             |                |

| n 4                      | non-executed odd function                                                                                                       | 104            |

| 3.4                      | Code Coverage. Odd Values. The gray instructions correspond to the                                                              | 104            |

| 2 5                      | non-executed even function.                                                                                                     |                |

| 3.5                      | Dead Code Identification. The gray instructions were not executed                                                               | col            |

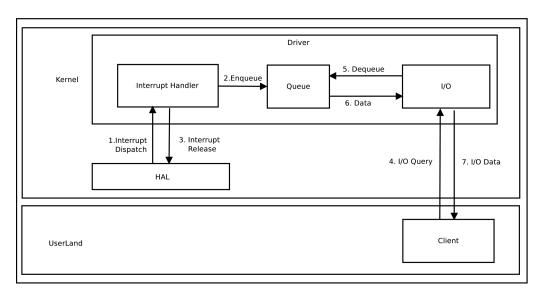

| 3.6   | System Architecture. The data acquisition procedure in user-land is decoupled from kernel-land, allowing lower overheads by core-offloading client |     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | processing                                                                                                                                         | 109 |

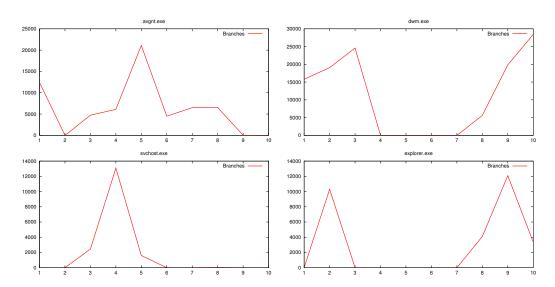

| 3.7   | Simultaneous multi-process monitoring: Accumulated branches for each 1-second interval. The branch-rate for each process may be used for system    |     |

|       | profiling and side-channel attack detection                                                                                                        | 111 |

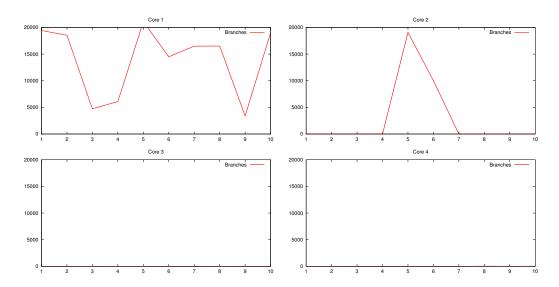

| 3.8   | Multi-core monitoring: Accumulated branches for each 1-second interval.                                                                            |     |

|       | Enabling the mechanism on all system cores eases whole-system profiling.                                                                           | 112 |

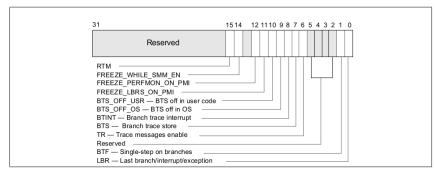

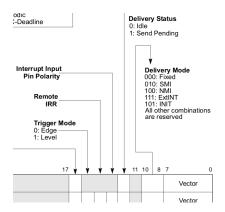

| A.1   | Enabling monitoring: Flags should be set in this MSR in order to activate                                                                          |     |

|       | LBR, BTS and interrupts. The bitmask also defines the data capture scope                                                                           |     |

|       | (user and/or kernel-land). Source: Intel manual [78]                                                                                               | 135 |

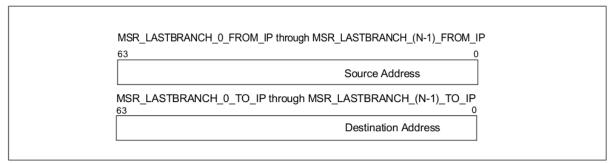

| A.2   | LBR MSRs. When LBR is activated, data is stored on LBR MSRs. Branch                                                                                |     |

|       | source addresses are stored on FROM MSRs whereas branch target ad-                                                                                 |     |

|       | dresses are stored on TO MSRs. These MSR registers are numbered from                                                                               |     |

|       | 0 to N-1, according the number of MSR registers available on the processor.                                                                        |     |

|       | Source: [78]                                                                                                                                       | 136 |

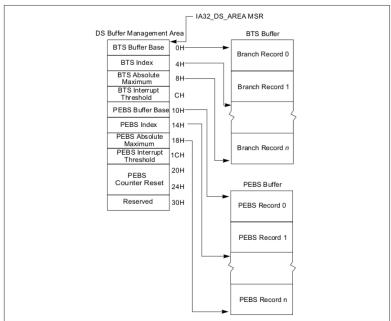

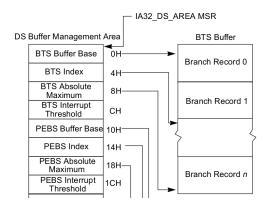

| A.3   | DS MSR. The address pointed by the DS MSR is an OS allocated page                                                                                  |     |

|       | having pointers for the BTS and PEBS mechanisms. Source: [78]                                                                                      | 136 |

| A.4   | DS fields. The BTS and/or PEBS fields should be filled with the base                                                                               |     |

|       | address of another OS allocated page, which will store the captured data                                                                           |     |

|       | itself. Besides, it should be filled with pointers to the current stored entry,                                                                    |     |

|       | maximum allowed entry, and threshold addresses. Source: [78]                                                                                       | 137 |

| A.5   | BTS Filtering. By setting the proper flags, data is captured only when the                                                                         | 10. |

|       | capture condition is satisfied. Source: [78]                                                                                                       | 137 |

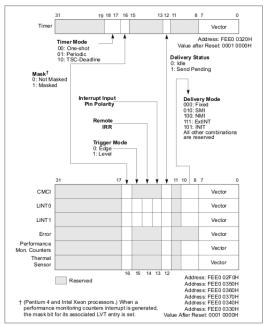

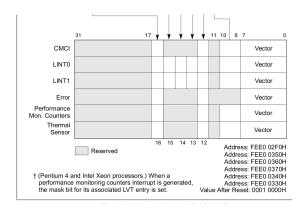

| A.6   | LVT. A series of entries which control interrupts according their source.                                                                          | 10. |

|       | Source: [78]                                                                                                                                       | 138 |

| A.7   | Performance Counter at LVT. When an PMI occurs, the processor looks                                                                                |     |

|       | into the performance counter entry to identify how the interrupt has to be                                                                         |     |

|       | handled. Source: [78]                                                                                                                              | 138 |

| A.8   | Interrupt Configuration. For a given interrupt type, we should set delivery                                                                        | -50 |

| - 1.0 | mode and the vector number, whose IDT entry points to the correct ISR.                                                                             |     |

|       | Source: [78]                                                                                                                                       | 130 |

|       |                                                                                                                                                    | 100 |

# List of Tables

| 1.1  | $Identified \ anti-VM \ techniques \ and \ number \ of \ samples \ showing \ them. \ Source: [28]$  | ] 17 |

|------|-----------------------------------------------------------------------------------------------------|------|

| 2.1  | Summary of HVM-based tools and solutions                                                            | 0    |

| 2.2  | Summary of SMM-based tools and solutions                                                            | 1    |

| 2.3  | Summary of privileged rings-based tools and solutions 5                                             | 2    |

| 2.4  | Summary of hardware-based tools and solutions                                                       | 2    |

| 2.5  |                                                                                                     | 3    |

| 2.6  | Protection mechanisms used by overviewed solutions                                                  | 4    |

| 2.7  | Comparison of solutions according to their purposes                                                 | 5    |

| 2.8  | Comparison of solutions according to their overhead                                                 | 6    |

| 2.9  | Comparison of solutions according to development effort                                             | 6    |

| 2.10 | ASLR - Library placement after two consecutive reboots 6                                            | 9    |

| 2.11 | Function Offsets from ntdll.dll library                                                             | 0    |

| 2.12 | CALL Opcodes                                                                                        | 1    |

| 2.13 | RET Opcodes                                                                                         | 1    |

|      |                                                                                                     | 3    |

| 2.15 | Excerpt of the ROP payload's branch window                                                          | 34   |

| 2.16 | Anti-analysis tricks found due to branch-diverged behavior                                          | 37   |

| 2.17 | Benchmarking the system with and without the monitor                                                | 3    |

| 3.1  | Solutions Comparison. Comparing our solution to other approaches regarding distinct usage scenarios | 18   |

# **Abbreviation List**

| <b>AMT</b> | Active Management Technology               |

|------------|--------------------------------------------|

| APIC       | Advanced Programmable Interrupt Controller |

|            | Advanced Persistent Threats                |

| ASLR       |                                            |

| AV         |                                            |

| BIOS       | Basic Input Output System                  |

| BPU        | Branch Prediction Unity                    |

| BTS        | Branch Trace Store                         |

| DBG        |                                            |

| CG         |                                            |

| CFG        |                                            |

| CFI        |                                            |

| DBI        | Dynamic Binary Instrumentation             |

| DBT        | Dynamic Binary Translation                 |

| DEP        | Data Execution Prevention                  |

| DLL        | Dynamic Linked Library                     |

| DMA        | Direct Memory Access                       |

| EPT        | Extended Page Table                        |

| GDB        |                                            |

| GPU        | Graphical Processing Unity                 |

| HAL        | Hardware Abstraction Layer                 |

| HAW        |                                            |

| HPC        | Hardware Performance Counter               |

| HVM        |                                            |

| I/O        |                                            |

|            | Intrusion Detection System                 |

|            | Interrupt Descriptor Table                 |

|            | Internet Of Things                         |

|            | Intelligent Platform Management Interface  |

|            | Intrusion Prevention System                |

| IRQ        | Interrupt Request                          |

|            |                                            |

| JOP        | Jump Oriented Programming                  |

|            | Kernel Patch Protection                    |

|            | Last Branch Record                         |

|            | Loop Oriented Programming                  |

|            | Logical Volume Manager                     |

|            | Local Vector Table                         |

| MALWARE    | Malicious Software                         |

| <b>ME</b>                            | Engine       |

|--------------------------------------|--------------|

| MITM                                 | v            |

| MMU                                  |              |

| MSR                                  |              |

| MTF                                  |              |

| NDIS Network Driver Interface Spec   |              |

| NMI                                  | *            |

| NPT                                  | -            |

| NX                                   |              |

| OSOperating                          |              |

| PAE Physical Address E.              | 0            |

| PCI Peripheral Component Inter       |              |

| PEPortable Ex                        |              |

| PEBS Precise Event Based S           |              |

| PMI Performance Monitoring In        | nterrupt     |

| PXE                                  | _            |

| ROP Return Oriented Progr            | amming       |

| SGX Software Guard Ex                | tensions     |

| SMI System Management I              | nterrupt     |

| <b>SMM</b>                           | $nt \; Mode$ |

| SMRAMSystem Managemen                | nt RAM       |

| <b>SOC</b>                           | ı a Chip     |

| STM                                  | Memory       |

| SVDSingular Value Decom              | position     |

| SVM Secure Virtual I                 | Machine      |

| TCB                                  | de Base      |

| TLB Translation Look-Aside           | 00           |

| TPM Trusted Platform                 |              |

| TSC Time Stamp                       |              |

| TSX Transactional Synchronization Ex |              |

| USB                                  |              |

| USB-HC                               |              |

| VMVirtual I                          |              |

| VMCB Virtual Machine Contr           |              |

| VMCS Virtual Machine Control S       |              |

| VMIVirtual Machine Intro             | -            |

| VMM                                  |              |

| XD Execute                           | Disable      |

# Contents

| 1        | Intr | oducti  | on                                                                 | 16 |

|----------|------|---------|--------------------------------------------------------------------|----|

|          | 1.1  | Motiva  | ation                                                              | 16 |

|          | 1.2  | Object  | ives                                                               | 18 |

|          | 1.3  | -       | butions                                                            | 19 |

|          |      | 1.3.1   | Publications                                                       | 20 |

|          | 1.4  | Backgr  | round                                                              | 21 |

|          |      | 1.4.1   | Semantic Gap                                                       | 21 |

|          |      | 1.4.2   | Introspection                                                      | 21 |

|          | 1.5  | Outline | e                                                                  | 22 |

| <b>2</b> | Pap  | ers     |                                                                    | 23 |

|          | 2.1  |         | vatches the watchmen: A review of techniques, tools and methods to |    |

|          |      | counte  | rfeit anti-analysis techniques on modern platforms                 | 23 |

|          | 2.2  | Abstra  | et                                                                 | 23 |

|          | 2.3  | Introdu | uction                                                             | 24 |

|          | 2.4  | Initial | Approaches and their limitations                                   | 25 |

|          | 2.5  | Hardw   | are Assisted Hypervisor-Based Approaches                           | 27 |

|          |      | 2.5.1   | HVM background                                                     | 27 |

|          |      | 2.5.2   | HVM threats                                                        | 29 |

|          |      | 2.5.3   | Malware Analysis                                                   | 29 |

|          |      | 2.5.4   | Malware Debugging                                                  | 31 |

|          |      | 2.5.5   | A Combined Approach                                                | 32 |

|          |      | 2.5.6   | HVM for Security Policy Enforcement                                | 33 |

|          |      | 2.5.7   | HVM for Attack Prevention and System Integrity                     | 33 |

|          |      | 2.5.8   | HVM for Forensic Procedures                                        | 34 |

|          |      | 2.5.9   | VMI limits                                                         | 35 |

|          | 2.6  | SMM-l   | based techniques                                                   | 36 |

|          |      | 2.6.1   | SMM Background                                                     | 36 |

|          |      | 2.6.2   | SMM Threats                                                        | 38 |

|          |      | 2.6.3   | SMM for Debugging                                                  | 39 |

|          |      | 2.6.4   | SMM for Forensic Purposes                                          | 39 |

|          |      | 2.6.5   | SMM for attack detection and prevention                            | 40 |

|          |      | 2.6.6   | SMM for I/O Integrity                                              | 41 |

|          |      | 2.6.7   | Who protects the hypervisor?                                       | 41 |

|          |      | 2.6.8   | SMM security issues                                                | 42 |

|          | 2.7  | The ba  | attle of the rings                                                 | 43 |

|          |      | 2.7.1   | Management Engine: the lord of the rings                           | 43 |

|          |      | 2.7.2   | Isolated rings and SGX                                             | 43 |

| 2.8  | Hardware-based techniques                                            | . 44 |

|------|----------------------------------------------------------------------|------|

|      | 2.8.1 A brief discussion on hardware-based approaches                | . 46 |

| 2.9  | Other Approaches                                                     | . 46 |

|      | 2.9.1 Performance Counters                                           | . 47 |

|      | 2.9.2 Graphics Processing Units                                      | . 48 |

|      | 2.9.3 Transactional Memories                                         |      |

| 2.10 | Summary                                                              | . 49 |

| 2.11 | Conclusions                                                          | . 54 |

| 2.12 | Enhancing Branch Monitoring for Security Purposes: From Control Flow |      |

|      | Integrity to Malware Analysis and Debugging                          | . 56 |

| 2.13 | Abstract                                                             | . 57 |

| 2.14 | $Introduction \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                | . 57 |

| 2.15 | Background and threat model                                          | . 58 |

|      | 2.15.1 Malware analysis and evasion                                  | . 58 |

|      | 2.15.2 Current solutions for evasive malware                         | . 59 |

|      | 2.15.3 Transparency                                                  | . 59 |

|      | 2.15.4 Debuggers: requirements and implementations                   | . 60 |

|      | 2.15.5 Current debugger implementations                              | . 60 |

|      | 2.15.6 ROP attacks                                                   | . 61 |

|      | 2.15.7 Performance monitoring                                        | . 62 |

|      | 2.15.8 Threat model                                                  | . 63 |

| 2.16 | Related work                                                         | . 63 |

| 2.17 | Proposed framework                                                   |      |

|      | 2.17.1 Driver: all about the basis                                   |      |

|      | 2.17.2 Handling Interrupts                                           |      |

|      | 2.17.3 Handling Data                                                 |      |

|      | 2.17.4 Performing I/O                                                |      |

|      | 2.17.5 What happens after an interrupt                               |      |

|      | 2.17.6 Handling monitor branch data                                  |      |

|      | 2.17.7 Clients: where the magic happens                              |      |

|      | 2.17.8 Introspection                                                 |      |

|      | 2.17.9 Looking into memory                                           |      |

|      | 2.17.10 Validation                                                   |      |

| 2.18 | Applications                                                         |      |

|      | 2.18.1 Malware Tracer                                                |      |

|      | 2.18.2 Call Graph                                                    |      |

|      | 2.18.3 Control Flow Graph                                            |      |

|      | 2.18.4 Modular malware                                               |      |

|      | 2.18.5 Real malware tests                                            |      |

|      | 2.18.6 Debugger                                                      |      |

|      | 2.18.7 Project                                                       |      |

|      | 2.18.8 Debugger client implementation                                |      |

|      | 2.18.9 Validation test                                               |      |

|      | 2.18.10 ROP Detector                                                 |      |

|      | 2.18.11 Anti-Analysis tricks detection                               |      |

|      | 2.18.12 Execution deviation detection at branch-level                |      |

| 2.19 | Discussion, limitations and future work                              |      |

|      | 2.19.1 Suggestions for Branch Monitoring improvement                 | . 95 |

|    | 2.20       | 2.19.2 Future Work       98         Conclusion       98                                                                           |        |

|----|------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|

| 3  | Disc       | ussion 9'                                                                                                                         | 7      |

|    | 3.1        | Contributions $\dots \dots \dots$ | 7      |

|    |            | 3.1.1 Solutions comparison                                                                                                        | 7      |

|    | 3.2        | The Framework                                                                                                                     | 3      |

|    |            | 3.2.1 Process Isolation                                                                                                           | 3      |

|    |            | 3.2.2 Transparency                                                                                                                | 9      |

|    |            | 3.2.3 Implementation efforts                                                                                                      | 9      |

|    |            | 3.2.4 Portability                                                                                                                 | 9      |

|    |            | 3.2.5 Tracer                                                                                                                      | J      |

|    |            | 3.2.6 CG Reconstruction                                                                                                           | J      |

|    |            | 3.2.7 CFG Reconstruction                                                                                                          |        |

|    |            | 3.2.8 Trace example                                                                                                               |        |

|    |            | 3.2.9 Code Coverage                                                                                                               |        |

|    |            | 3.2.10 Debugger                                                                                                                   |        |

|    |            | 3.2.11 ROP Detection                                                                                                              |        |

|    |            | 3.2.12 ROP Detection Policies                                                                                                     |        |

|    |            | 3.2.13 Performance                                                                                                                |        |

|    |            | 3.2.14 Framework Architecture and performance                                                                                     |        |

|    | 3.3        | Other branch monitor-based solutions                                                                                              |        |

|    | 3.4        | Future Directions                                                                                                                 |        |

|    |            | 3.4.1 Multi Process                                                                                                               |        |

|    | ~ <b>~</b> | 3.4.2 Multi-core                                                                                                                  |        |

|    | 3.5        | Reproducibility                                                                                                                   | 2      |

| 4  | Con        | clusion 11:                                                                                                                       | 3      |

|    | 4.1        | Future Work                                                                                                                       | 3      |

| Bi | bliog      | raphy 115                                                                                                                         | 5      |

| A  |            | Branch Monitor Implementation                                                                                                     | 5<br>5 |

|    |            | A.1.2 Handling branch-related structures                                                                                          | J      |

# Chapter 1

# Introduction

### Motivation

In today's world, computer systems mediate most of our interactions, with either physical or digital media. In this scope, the proper working of such systems is always worrisome. One of the main threats against computer systems is malicious code (also referred to as malware—malicious software), since it directly affects systems' capabilities.

Malware can compromise systems—by luring users or exploiting vulnerabilities—and thus cause a wide range of damage, from data leaks to financial losses. As the technology is widespread, malware has potential to reach a significant fraction of the world population.

As an example of damage extension caused by malware, FEBRABAN—the Brazilian Bank Federation—estimated losses of around US\$ 500 million in 2015 [62, 81]. RSA researchers, in turn, estimated losses of US\$ 3.8 billion on Brazilian bank payment bills (a.k.a. boletos) [104]; according to the FBI, the Cryptowall ransomware has yielded US\$ 18 million from its victims [188].

The usual way of handling malware is through analysis procedures, in which a given sample is run in a controlled environment in order to provide to the analyst information about its behavior [179]. By relying on collected data, security professionals are able to understand attacks, develop patches, vaccines and other countermeasures.

The effectiveness of incident responses depends on the capabilities of sample analysis, since a malware will keep infecting users if no countermeasure is taken. However, the analysis of an unknown piece of code may fail due to a lot of reasons: corrupted files, missing components and anti-analysis techniques.

Anti-analysis techniques are pieces of code intended to detect if a process is running under an analysis environment. If so, the execution is terminated and the analysis is unable to proceed. Some samples also rely on split personalities, in which, on detection of an analysis environment, the malicious behavior is averted and only mild or completely benign behavior is observed. This way, as no countermeasure could possibly be developed, the piece of code keeps threatening users.

Given this scenario, concerns about the samples that do employ some kind of antianalysis trick arise naturally. A previous work of mine [28] analyzed more than 25 thousand malware samples operating in the Brazilian cyberspace between 2012 and 2015 and allowed observation of the first signs of evasive malware usage, which indicates armored malware analysis may become a problem for our country in the near future.

The graph from Figure 1.1 shows how distinct anti-analysis technique usage evolved over time. In the 2012 to 2014 period, all techniques showed growth, which may indicate a tendency for future years.

Figure 1.1: Anti-analysis technique usage evolution by sample (A sample may use more than one at a time). Source: [28]

A particular set of techniques of interest are those related to virtual-machine evasion. By looking at Table 1.1, we are able to identify its use in Brazilian samples. Although not prevalent yet, the knowledge of such techniques by some criminals is clear, so increased use is expected in the future.

| Technique                | # Samples      |

|--------------------------|----------------|

| VMCheck.dll              | 2,729 (10.48%) |

| VMware trick             | 850 (3.26%)    |

| VirtualBox Detection     | 306 (1.17%)    |

| Bochs & QEmu CPUID trick | 340 (1.31%)    |

| VirtualPC trick          | 17 (0.07%)     |

Table 1.1: Identified anti-VM techniques and number of samples showing them. Source: [28]

In addition to the Brazilian scenario, many other anti-analysis techniques can be found

spread worldwide [30, 15], which was the main motivation to consider evasive malware is the primary concern of this work.

Recent studies about malware evasion have pointed that the key factor for analysis detection is that analysis solutions are not transparent—the analysis environment behaves in different ways in comparison to an ordinary user environment. If we could make those environments look more similar, samples would not have enough information to decide whether they are in an analysis environment or not.

In a more technical way, transparency is achieved by keeping samples' integrity and not introducing side effects. These two points are strong constraints for analysis solutions, since no code injection, hooking or emulation is allowed. As such, hardware-assisted approaches have appeared as an alternative way of fulfilling the transparency requirement, which was chosen to be this work's research line.

To start with, I present a comprehensive literature review on hardware-assisted techniques in the security context. This review provides a broad comparison of techniques, highlighting strong and weak points, and also pinpointing development gaps—security solutions which would benefit from hardware support. One significant gap I have identified is the use of performance counters for monitoring tasks. This way, I made a significant effort on developing their use on broader scenarios—for debugging and tracing—than they were originally designed to work with. Both contributions are presented as a paper collection, whose full content is presented in the next chapter.

# **Objectives**

My main goal in this dissertation is to evaluate the use of transparent solutions to handle anti-analysis-armored malicious code. The literature review, presented further ahead, has revealed a gap in the use of performance counters for such purpose, thus I dedicated a great effort on studying this mechanism. This way, in general terms, my goals are presented as questions to be answered during the research development:

- Could I develop a performance-counter-based malware analyzer? This topic aims to answer whether the branch-collected data along with introspection procedures are enough to analyze malware and what limitations they present.

- Could I isolate processes' actions? This topic aims to answer whether the branch monitor mechanism can isolate malware actions from its system-wide collected data.

- Is the conceived solution's overhead acceptable? This topic aims to answer whether the added introspection procedures make the analysis still feasible when compared to the state-of-the-art tools.

- Could the solution run in real-time? This topic aims to answer whether the added introspection procedures allows for real-time monitoring or is limited to offline analysis.

- Is the final solution transparent? This topic aims to answer whether the data collection required for introspection interferes with analysis' transparency or not.

- Is the solution easy to implement? This topic aims to answer what the development cost is when compared to state-of-the-art solutions.

- Is the solution portable? This topic aims to answer whether the adopted introspection procedure can be ported to other systems or not.

My specific goals are the following:

- Is Call Graph (CG) reconstruction possible? This topic aims to answer which level of granularity I am able to achieve when handling function call data.

- Is Control Flow Graph (CFG) reconstruction possible? This topic aims to answer which level of granularity I am able to achieve when handling executed instruction data.

- Could I develop a Debugger? This topic aims to answer whether my solution can be used for real-time inspection or not, regarding inspected-state consistency.

- Does the solution handle Return-Oriented Programming (ROP) attacks? This topic aims to provide a comparison with existing branch-based monitoring tools.

## Contributions

The contributions of this dissertation are those from the included papers. In order to make my claims clearer, I summarized them below.

The contributions from the paper "Who watches the watchmen" are the following:

- I present current state-of-the-art malicious code attacks and current tools' limitations.

- I claim the need for transparent systems to overcome current tools' limitations.

- I introduce the working mechanism of hardware-assisted, transparent approaches to a range of security tools.

- I present security tools based on this mechanism.

- I evaluate this mechanism according to several criteria, such as protection, transparency, overhead and development efforts.

- I highlight existing development gaps in the evaluated techniques.

The contributions from the paper "Enhancing Branch Monitoring for Security Purposes" are the following:

- Current Threats and Solutions scenario review: I present a review of the threat landscape scenario and current countermeasure and analysis tools, discussing their advantages and weaknesses. Specifically, I review transparent analysis solutions as well as branch-based ones.

- Branch monitoring framework: I propose a complete, modular framework based on hardware monitoring features, allowing for further applications that overcome current and future state-of-the-art limitations and weak points.

- Transparent malware analysis: I leverage my framework to build a transparent malware analysis tool with lower development efforts than the current state-of-the-art ones. As far as I know, no other malware tracer is based on this kind of monitoring.

- Transparent debugger: I demonstrate how to implement granular debugging based on my framework without using single-step flags. Again, I have no knowledge of other debugging solutions based on branch monitors.

- ROP attack detector: I present an improved implementation of current ROP detection heuristics, based on my framework, which does not require code injection and is a limitation of other approaches.

- Hardware Improvements: I suggest possible hardware enhancements for branch monitors based on the challenges I faced when developing my solution.

#### **Publications**

While the research was being pursued, some work have been accepted or submitted for publication, although not all of them were included in this dissertation. However, as each work contributed to the dissertation one way or another, I think it is reasonable to give them a mention. Below I discuss each one's implication for this dissertation.

- The paper "The Other Guys: Automated Analysis Of Marginalized Malware" was published in the "Springer Journal of Computer Virology and Hacking Techniques" (JCVHT) [26]. This paper is the result of a previous research and the presented sandbox was used as a ground-truth for detecting evasive samples. It also presents the sandbox mentioned in the TOPS article.

- The paper "One Thousand and One Nights: Brazilian Malware Stories" was also submitted to the JCVHT [28]. This paper is the result of a previous research and its threat review is used as underlying support for the Brazilian scenario landscape presented in the dissertation's introduction.

- The paper "Who watches the watchmen: A review of techniques, tools and methods to counterfeit anti-analysis techniques on modern platforms" was submitted to "ACM Computing Surveys" (CSUR) [29] and is embedded in this work as part of my contributions. This paper may be understood as my literature review and critical evaluation of the current hardware-assisted security scenario.

• The paper "Enhancing Branch Monitoring: From Control Flow Integrity to Malware Analysis and Debugging" was submitted to "ACM Transactions On Privacy and Security" (TOPS) [27] and is embedded in this work as part of my contributions. This paper may be understood as my final solution proposal for the stated problem. Preliminary results from this work were published in the "XVI Brazilian Symposium on Information and Systems Security" (SBSEG) in the form of the following articles: "VoiDbg: Projeto e Implementação de um Debugger Transparente para Inspeção de Aplicações Protegidas" [25]; "Detecção de ataques por ROP em tempo real assistida por hardware" [24]; "Análise Transparente de Malware com Suporte por Hardware" [23].

# Background

Along the referred papers, I have assumed some concepts are known to the reader. In order to allow any reader to follow this text, I define them here.

### Semantic Gap

The semantic gap problem is the information representation difference on distinct levels. As an example, consider the differences between programming languages and assembly code. As can be noticed, the first is richer than the second, given that it provides, for instance, independent, context-related variable names whereas the second works over context-independent, shared registers. The semantic gap problem can also be seen in other contexts, such as computer forensics. When handling memory dumps, data is seen as a byte-array whereas at the OS level bytes are seen as parts of complex context structures, such as processes, descriptors and handlers. It is important to notice that such representation difference is intrinsic to the distinct technologies involved and as such is present along this work, since we are interested in hardware solutions to monitor OS-level structures.

# Introspection

Considering the stated semantic gap problem, we notice that fully bridging such gap, thus having the same representation, may be theoretically impossible, since it is technology-inherent. However, some information may be retrieved. As an example, low-level instruction addresses can be mapped to libraries' base address when these are known. Similarly, memory-dumped bytes can be interpreted as structs when these are known. This information recovering process is often named introspection, since one is outside looking to an inside structure, for a given representation level. Introspection procedures are discussed along this work, since all hardware-assisted approaches have to bridge this gap to some extent.

# Outline

This dissertation is based on a two-paper collection, presented in Chapter 2 as they were submitted for publication. Chapter 3 summarizes my results and presents a discussion of their implications. Finally, I draw my conclusions and present future work in Chapter 4.

# Chapter 2

# **Papers**

# Who watches the watchmen: A review of techniques, tools and methods to counterfeit anti-analysis techniques on modern platforms

**Publication:** This paper was submitted for publication to the ACM Computing Surveys (CSUR)

Marcus Botacin<sup>1</sup>, Paulo de Geus<sup>2</sup>, André Grégio<sup>3</sup>,

(1) University of Campinas

Email: marcus@lasca.ic.unicamp.br

(2) University of Campinas

Email: paulo@lasca.ic.unicamp.br

(3) Federal University of Paraná

Email: gregio@inf.ufpr.br

# Abstract

Malicious software are still threatening users on a daily basis and their evolution goes from social-engineering-based bankers to advanced persistent threats (APTs). Recent research and discoveries have presented us to a wide range of anti-analysis and evasion techniques, in-memory attacks, such as Returned Oriented Programming (ROP), and systems subversion, including BIOS and hypervisors. This work presents a survey on techniques able to detect, mitigate and analyze these kinds of attacks, which require transparent and fine-grained environments as analysis resources. We cover current tools' limitations, such as not being fully-transparent, and introduce systems and techniques to overcome and/or mitigate these constraints. The work presents approaches based on hypervisor introspection, System Managment Mode (SMM) instrumentation as well as some hardware-based ones. We also present some threats based on the same techniques. Our main goal is to give to the reader a broader and more comprehensive understanding

of recently-surfaced tools and techniques.

# Introduction

Malicious software (also known as malware) attacks are one of the main computer system security threats and their importance and spreading continuoe to grow. Reported data[9] shows malware dissemination exceeds rates of 60 thousand new samples per day, with malware for mobile devices having had a particular growth[189]. In all, losses amounted to around 200 million dollars in 2016's first quarter[63]. In order to handle security incidents generated by malware actions, researchers have proposed a lot of tools to mitigate (Intrusion Detection Systems), prevent (Intrusion Prevention Systems, packet filters), remedy (antivirus, vaccines) and analyze (sandboxes) such malware. But more than growing in number, malware also have been growing in complexity, being able to bypass filters by applying polymorphism, evade sandboxes by detecting virtualized environments and even to subvert whole system operation by taking hypervisor control on virtualized systems.

As threats have been evolving, security has been taking a reactive posture and engaging the opposing sides into an arms race. Some new tools were recently proposed in order to handle new security issues related to modern malware, but a clear scenario/panorama is yet to be formed, which motivates us to work on this survey.

Most new approaches are based on techniques to stealthly and transparently acquire data from analyzed systems, notably System Managment Mode (SMM) and Hardware-Assisted Introspection, which are explored in detail in further sections. Having this kind of system introspection allows the analyst to get a fine-grained view of samples, even from those employing common evasion techniques, given that the systems are hardware-supported and run on the most priviledged ring, as is desired for reliable experiments[159]. Moreover, these systems natively handle kernel data, which allows for rootkit analysis and detection, a recurrent limitation from analysis systems running on the guest OS.

This survey is not limited to sandbox analysis, rather also covering forensic procedures that can be performed with these new techniques and allow live-procedure without malware sample-awareness. Besides, we review whole system monitoring tools and present tools for system and hypervisor integrity, which are on the frontend of new malware attacks. In addition, we extend our overview to general attack classes when it is allowed by the investigated solution. In summary, we aim to provide a deep understanding of hardware-assisted isolated execution environments, as stated by Zhang [222].

As these techniques are still in their early uses, new threats to them are also still evolving, leading to a dangerous scenario of stealth and Operating System-independent threats, which we deem important to provide a current overview. Finally, we will present applications built with these underlying techniques and related work that might lead research in that area.

This work is organized as follows: Section 2.4 presents current monitoring tool approaches and their limitations, with special emphasis on their drawbacks and how malware are exploiting them. Section 2.5 describes the hardware-assisted hypervisor, its inner workings, current threats and how tools can be deployed using current processor support

for virtualization. Section 2.6 introduces the use of this priviledged processor mode to get a complete system view for both malicious and legitimate use cases. Section 2.7 presents the concepts of privileged rings and isolated execution environments. Section 2.8 presents some hardware-design tools to achieve system independent monitoring. Section 2.9 introduces complementary approaches to perform system introspection and behavior analysis. Section 2.10 show tables that aim to summarize the presented approaches. Finally, in Section 2.20 we present our conclusions and some directions for the future.

# Initial Approaches and their limitations

Considering the limitations from static analysis[129], dynamic monitoring is the most effective technique for system monitoring and analysis, since the extracted behavioral information may support a diversity of incident-response measures[84]. However, the quality of these measures is directly affected by the quality of the dynamic analysis data extraction process. If a malware could evade the analysis process or subvert some monitoring mechanism, the incident response effort would be ineffective. Handling evasive and subversive malware is one of biggest challenges system monitors face nowadays. The particular challenges each monitor type faces are discussed below.

The survey by Egele et al. [59] points to analysis that can be done by instrumenting the monitored binary or system. Binary monitoring usually employs some kind of code injection, such as Microsoft detours or DLL injection, in order to instrument the binary. The injection may be detected by a malware that checks its memory integrity, thereby leading to an analysis evasion. System instrumentation may be added in or outside the monitored environment. When monitoring from inside the environment, the approaches often involve kernel changes by SSDT/IDT hooking, installing kernel callbacks or filters or wrapping handlers. Its main drawback is its uneffectiveness against rootkits, which run on the same privileged level and are able to perform the same kind of flow redirection in order to subvert the system, and in the process detecting the analysis monitor.

The system can be externally instrumented by performing a Dynamic Binary Instrumentation (DBI) or a virtual machine instrospection (VMI) procedure. DBI may be accomplished in either kernel or user-land, allowing for a fine-grained analysis at the instruction level. DBI's use in security was made popular by DynamoRIO[58] and PIN[79], with lots of tools built on top of it. However, execution in a DBI environment may be detected by executing an instruction whose translation turns into an abnormal behavior.

In order to overcome such limitations, some proposed work have the ability to translate some known failure-prone instructions into surely successful ones, notably VAMPIRE[196] and SPIKE[198], which allowed for stealth-fine-grained tools such as Cobra[197]. However, this approach has the disadvantage that all known fail-prone instructions have to be translated, which is not only impractical[87] but also prone to evasion by a malware that employs a new and unknown "evasion trick".

VMI, in turn, provides a native whole system view and fine-grained analysis capabilities through instruction-level inspection, being suitable for malware analysis, security policy enforcement and integrity checks. VMI-based techniques have also the advantage

of being able to monitor systems that prevent or restrict in-system monitoring, such as 64 bit Windows Kernel Patch Protection (KPP)[109], Many tools were build with the underlying VMI, like Anubis[16, 83] on top of QEMU[17], for malware analysis and its Danubis[134] version for drivers, exploring whole-system view capabilities. Bitblaze[182] and Virtice[152] are built on top of TEMU, a tiny version of QEMU, and provide a complete framework for malware analysis and system inspection. VMI has become popular to the point of having automatic instrumentation tools, such as Libvmi[100].

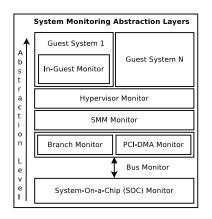

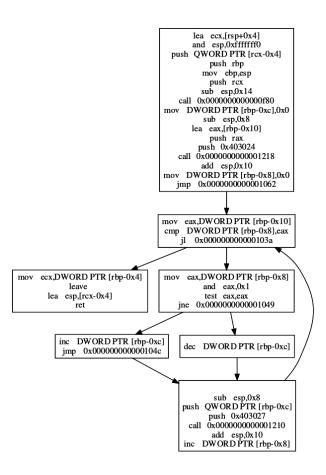

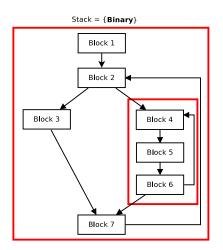

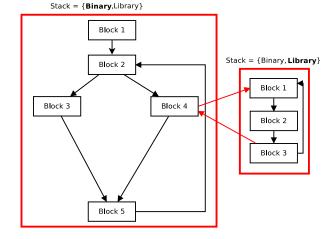

However, external monitoring approaches, such as VMI, have a major drawback, which is the gap between high-level (what is running at the O.S. level, e.g. a file opening) and low-level information (the machine instruction sequence being processed), also called semantic gap[127]. Despite some proposed automated techniques[64, 167, 164, 56], handling the semantic gap is still considered hard and requires specific knowledge and big development efforts. The semantic gap grows as one gets deeper into abstraction levels. Figure 2.1 shows abstraction levels for techniques presented in the following sections.

Figure 2.1: Abstraction levels for distinct monitoring techniques.

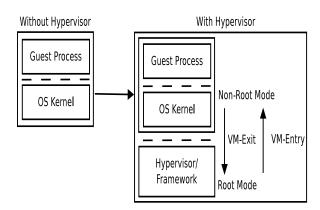

Figure 2.2: VM operating layers.

While possibly being able to bridge the semantic gap, VMI is not perfect since malware can detect virtualized environments in order to evade an analysis procedure[37]. Given that most VMI systems run on top of an emulator, such as QEMU, malware can detect the virtualized environment by testing instruction behavior, which often differs from the ones presented on a real CPU. Martignoni et al. [107] describe a method, called Red Pill, of fuzzy-testing a CPU emulator and being able to generate tests for emulator identification, soon extended by Shi et al. [177]. In addition, Paleari et al [140] developed a way of automatically generating red pills.

Although research efforts have been done to overcome these challenges, proposed solutions are very expensive, since they either require execution on multiple environments, such as BareCloud[89] and Splitmal[13] or require a physical machine, such as Barebox[88]. In order to overcome all these limitations, virtualization has to be made more transparent, something that can be achieved by hardware-assisted virtualization or, to go deeper into instrospection, by using SMM or similar.

# Hardware Assisted Hypervisor-Based Approaches

This section focus on techniques based on hardware-assisted hypervisor (HVM) monitoring. Initially, we introduce the concepts of HVM operation, focused on the x86-64 architecture and covering implementations over both Intel VT-x[78] and AMD-v/SVM[5] platforms. We follow by introducing tools and applications developed over these platforms.

### **HVM** background

Apart from 32 and 64-bit addressing modes, x86 and x86-64 CPUs have 3 operating modes: *Protected Mode*, which is the processor's native mode; *Real-Address Mode*, which extends the previous mode; and *System Management Mode*, covered in details in Section 2.6.

Virtualization instructions augment the CPU instruction set by adding two new operating modes, root and non-root modes, in a way so that guests and the host (VMM) are associated with the non-root and the root modes, respectively. The transitions from non-root to root mode are known as VM-EXITS, which work like an exception or a trap, but the set of spanning actions can be dynamically configured. After handling these events, the execution is resumed through VM-RESUME or VM-ENTRY. Figure 2.2 shows an overview of these new modes and events.

The extended instruction set offers many features to help a hypervisor implementation and improve system performance. Given that the new memory management unit can be used to track memory uses and guest registers are directly accessible from the hypervisor, we can implement a variety of security-oriented techniques that enforce policies. However, the main advantage offered is the capability of running code directly on the processor, with no need for instruction translation. This is particularly desirable for malware analysis and often a drawback for DBI-based systems, for instance, subject to instruction translation side-effects (Section 2.4). Since this analysis system is not susceptible to CPU emulation bugs, a malware running on such a system is not able to identify whether it is running inside a virtual environment or not, achieving the transparency requirement.

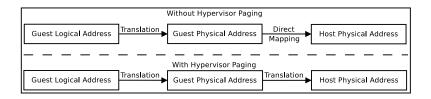

An important change when using virtualization instructions is the memory controller. There are different monitoring mechanisms according to the virtualization platform used, Intel or AMD, since the AMD's implementation has the memory controller on-die whereas Intel's has it externally. However, the main change is due to the double address translation mechanism. In a traditional hypervisor, guest virtual addresses are translated into guest physical ones, which are the host's physical ones. Intel and AMD have deployed techniques called Extended Page Table (EPT) and nested page table (NPT), respectively, that add an additional translation layer. On these systems, guest virtual addresses are translated into guest physical ones, but contrary to the previous implementations they are further translated before getting to the host's physical address lines. This process can be seen in Figure 2.3.

Knowledge of this mechanism is important since this second translation level could be instrumented so that memory access is monitored through translation-faults. However, such memory monitoring is not enough to cover the system as a whole, given that these

Figure 2.3: VM memory operation.

are CPU memory accesses; Direct Memory Access (DMA) may also happen and those are external to the CPU. DMA monitoring is enabled by another mechanism called IOMMU that intercepts Input/Output (I/O) actions. By following both approaches a more robust monitoring may take place.

A Hardware-assisted Virtual Machine (HVM) is configured through special control structures named Virtual Machine Control Structure (VMCS) and Virtual Machine Control Blocks (VMCB) on Intel and AMD systems, respectively. These blocks include the initial system state, memory allocation and vm-exits configuration. An advantage of using this technique is that the system does not need to be booted up in a virtualizated environment, but can be conveniently moved to one at runtime, which is called *late launch*. Late launch broadens the options for analysts, such as live-forensics, since it does not require reboot or shutdown. In the late launch case, the initialization blocks are set to the current system state, but this does require a driver to set specific registers at a privileged execution level.

When aiming to implement a security framework based on HVM, the usual approach is to instrument the hypervisor layer in root mode to collect information from non-root mode and then send them to an external client running on the host userland. In this case, the abstraction is similar to the one used in Operating Systems (OS): the VM monitor running in kernelspace and the analyzer in userspace. Even though the client is stealth for a malware, the hypervisor itself is not, given that the malware could map its memory to the hypervisor one and so find the monitor. A solution for that is to put the instrumented framework in a page without malware access, which is done through the new presented memory mechanism and its fault handler. Even more than the hypervisor analyzer, the internal driver could also be detected. To counter that, a tool may employ rootkit techniques to hide itself from the system or to use the same method to map the HVM-loader driver to a protected physical page.

The challenges faced when developing such kind of tool vary according to its monitoring goal: i) to register monitored values, as presented, is straightforward, since monitoring memory access can be done through translation faults and IOMMU; ii) system call tracing requires bridging the semantic gap by employing taint tracking and event static stack analysis; iii) finally, breakpoints and step-by-step execution require a more sophisticated approach.

Breakpoints are usually classified as software and hardware breakpoints. Software breakpoints are not transparent since they modify instruction bytes. Hardware breakpoints are limited in number and are shared between host and guest. Another way of implementing it is then required. Step-by-step execution has the same sort of limitation. The way tools overcome these limitations is to monitor the system by raising exceptions,

such as hooking the memory management unit to set a given page as read-only, thus causing a page fault at each execution, or to set performance counter registers to their maximum value in order to raise an overflow exception at each running step.

The next sections present practical tools and solutions developed using HVM, starting with an introduction to some threats based on this approach.

#### **HVM** threats

Given the transparency and system-wide view of HVM systems, as presented in previous sections, exploiting a system using this technique is a straightforward thinking. It is hard to say who was the first person to propose such application for HVM, since most releases happened in underground hacker forums. However, undoubtedly, the first famous one was the BluePill rootkit[160].

Bluepill is implemented on Windows Vista using AMD technology and is able to perform late launch; a network backdoor, with no need for NDIS modification, is shown as use case. Other examples appeared, like the HVM Rootkit[133], which is AMD based and targets Windows XP machines. This tool takes a multi-core approach, setting up each core for an HVM. Its driver loading routine employs the physical page mapping for stealthiness.

In fact, in-guest, ordinary kernel rootkits are stealth enough against casual analysis, but to remain stealth before a specialized forensic procedure requires HVM-based ones. Despite none of these tools being a complete, definitive solution, similar ones have been improved by both analysts and criminals.

# Malware Analysis

The previous HVM rootkit strategies can also be used for well-intended security purposes, such as malware analysis and debugging. It is not easy to identify this approach's emergence, as most of the poorly documented rootkits mentioned in the latter section have already proposed such instrumentation as a countermeasure. Presentations at hacker conferences have also shown incipient insights on HVM use for malware analysis.

A deeper understanding of HVM for malware analysis uses was provided by Dinaburg et al. [54], establishing formal foundations to attain transparency, from requirements—"higher privilege, no non-privileged side effects, identical basic instruction execution semantics, transparent exception handling and identical measurement of time"—to ways of fulfilling these requirements. The developed tool, Ether, is implemented as a Xen patch and runs Windows XP guests. The Analyzer architecture is client-server based and no internal code is required. Fine grained analysis is enabled by setting a trap flag for each instruction, causing considerable overhead. Memory access is traced by fault trapping on shadowed page tables. The same trap mechanism is employed to handle system calls, both on the new, fast syscall mechanisms and on the deprecated sysenter mode. System data is retrieved by classical VM instrospection techniques. In order to remain stealth, the Ether hypervisor changes PUSHF instruction behavior, since this instruction could detect the trap flags for single-step execution. It also changes the Timestamp Counter

(TSC) in order to avoid being detected through timing attacks. The study cases provided (a syscall tracer and an unpack tool, using shadow memory write tracking) show the tool's effectiveness against evasion tools available then. Despite its results, Ether is not a perfectly transparent tool, since some ways of fingerprinting it are known[145]. However, most of them are overcome by applying patches or by new VM extensions of modern processors. Moreover, Ether was a sound step towards being ahead of evasion tricks of its time.

CXPInspector[210] leverages Intel VT-x support on KVM to perform malware analysis on 64-bit Windows 7. Analysis challenges faced on 64-bit Windows Kernel include handling Address Space Layout Randomization (ASLR) and overcoming Kernel Patch Protections hook limitations, for which VMI is an alternative. In order to reconstruct high level semantics, it bridges the gap by using debug symbols and parsing PE executables. Branch addresses are reconstructed by using hardware branch facilities (discussed in Section 2.9). It also changes the TSC to prevent timing attacks. In addition to malware analysis capabilities, CXP is also able to perform application/system profiling by measuring the execution time spent on each memory page.

The CXPInspector also presents a more fine-grained concept for memory handling, named Currently eXecutable Pages (CXP), which allows for multiple scopes and granularities of the analysis. The three CXP granularities are: one memory region, a set of memory regions or one single memory page. By capturing transitions and flows among such CXPs, the system can trace events. In pratice, it is a way of implementing memory traps based on EPT or NPT facilities. CXP provides study cases of the Purple Haze 64-bit rootkit analysis and a profile of the Apache web server and its modules.

As an evolution of the ideia of analyzing malware on HVM, authors started to care about developing an *ad-hoc* malware analyzer VMM. The main reason behind it was reducing the Trusted Code Base (TCB), which is the code that should be trusted *a priori*. General-purpose VMM implements much more features than the one required for malware analysis, such as virtual devices and plenty of drivers. As is known, larger numbers of lines of code tend to generate more bugs, which increases the opportunity for malware evasion.

Given the above, Nguyen et al. [136] presented MAVMM, a malware analysis lightweight VM hypervisor. The TCB is reduced to 4K lines of code on MAVMM in comparison to millions of lines on well-known VMMs like Xen and VMWare. MAVMM is implemented using AMD-v instructions and runs a Ubuntu Linux as guest system. The hypervisor is loaded at boot time, in contrast to the late launch approach of Ether and others. The memory is protect using nested page technology. The tool is able to extract different features from the system, such as instructions, syscalls and memory accesses, by leveraging single-step execution and handling VM-Exits. It has 2 modes of feature extraction: Full and Compact modes. The first is a single step extraction whereas the second reduces the number of VM-Exits to a set of pre-registered reasons, achieving a significant analysis speed up. Authors pointed different possibilities of tool usage, such as syscall tracing and sample unpacking. The study case provided is a Linux rootkit analysis. The tool is also transparent as the HVM is employed. However, we should consider how likely to be fingerprinted and detected the environment is, as the hypervisor neither provides virtual

devices nor supports multiple guests.

More than just building analysis tools themselves, some authors have employed such tools for analysis improvements. Quist et al. [151], for instance, proposed using a modified version of the Ether HVM to improve AV detection accuracy. The work adds to Ether features for "deobfuscation: section and header rebuilding as well as automated kernel virtual address descriptor import rebuilding". With these repair mechanisms, AV showed detection rate improvements as high as 45%.