### Universidade Estadual de Campinas Instituto de Computação

## Liana Dessandre Duenha Garanhani

# MPSoCBench: a Framework for High-Level Evaluation of Multiprocessor System-on-Chip Tools and Methodologies

MPSoCBench: um Framework para Avaliação de Ferramentas e Metodologias para Sistemas Multiprocessados em Chip

#### Liana Dessandre Duenha Garanhani

MPSoCBench: a Framework for High-Level Evaluation of Multiprocessor System-on-Chip Tools and Methodologies

MPSoCBench: um Framework para Avaliação de Ferramentas e Metodologias para Sistemas Multiprocessados em Chip

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutora em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

Supervisor/Orientador: Prof. Dr. Rodolfo Jardim de Azevedo

Este exemplar corresponde à versão final da Tese defendida por Liana Dessandre Duenha Garanhani e orientada pelo Prof. Dr. Rodolfo Jardim de Azevedo.

#### Agência(s) de fomento e nº(s) de processo(s): Não se aplica.

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

Garanhani, Liana Dessandre Duenha, 1977-

G161m

MPSoCBench: a framework for high-level evaluation of Multiprocessor System-on-Chip tools and methodologies / Liana Dessandre Duenha Garanhani. – Campinas, SP: [s.n.], 2015.

Orientador: Rodolfo Jardim de Azevedo.

Tese (doutorado) – Universidade Estadual de Campinas, Instituto de Computação.

Simulação (Computadores).

Sistemas embarcados (Computadores).

Energia - Consumo.

Multiprocessadores.

Arquitetura de computador.

Azevedo, Rodolfo Jardim de,1974-.

Universidade Estadual de Campinas.

Instituto de Computação.

Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** MPSoCBench : um framework para avaliação de ferramentas e metodologias para sistemas multiprocessados em chip

#### Palavras-chave em inglês:

Computer simulation

Embedded computer systems

Energy consumption

Multiprocessors

Computer architecture

**Área de concentração:** Ciência da Computação **Titulação:** Doutora em Ciência da Computação

Banca examinadora:

Rodolfo Jardim de Azevedo [Orientador]

Fernando Gehm Moraes Alexandro Baldassin

Guido Araújo Lucas Wanner

**Data de defesa:** 27-11-2015

Programa de Pós-Graduação: Ciência da Computação

#### Universidade Estadual de Campinas Instituto de Computação

#### Liana Dessandre Duenha Garanhani

MPSoCBench: a Framework for High-Level Evaluation of Multiprocessor System-on-Chip Tools and Methodologies

MPSoCBench: um Framework para Avaliação de Ferramentas e Metodologias para Sistemas Multiprocessados em Chip

#### Banca Examinadora:

- Prof. Dr. Rodolfo Jardim de Azevedo Universidade Estadual de Campinas (UNICAMP)

- Prof. Dr. Fernando Gehm Moraes Pontifícia Universidade Católica do Rio Grande do SUL (PUCRS)

- Prof. Dr. Alexandro José Baldassin

Universidade Estadual Paulista Campus de Rio Claro (UNESP)

- Prof. Dr. Guido Costa Souza de Araújo Universidade Estadual de Campinas (UNICAMP)

- Prof. Dr. Lucas Francisco Wanner Universidade Estadual de Campinas (UNICAMP)

A ata da defesa com as respectivas assinaturas dos membros da banca encontra-se no processo de vida acadêmica do aluno.

Campinas, 27 de novembro de 2015

| Dedico este trabalho à minha linda família,<br>pela qual tudo vale a pena. |

|----------------------------------------------------------------------------|

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

## Acknowledgements - Agradecimentos

É uma ilusão pensar que os créditos por trabalhos concluídos são somente nossos. Não são! Qualquer que seja o projeto, inevitavelmente nós o realizamos em equipe, e da mesma forma devemos compartilhar os benefícios do seu sucesso. Com este trabalho não foi diferente, cada passo dessa trajetória foi realizada por uma equipe muito esforçada. Entrego aqui meus mais sinceros agradecimentos a estas pessoas tão especiais: às minhas filhas queridas, Iara e Anna, minhas companheiras, que quantas vezes, sem reclamar, devem ter sentido minha falta. Filhas, obrigada pela paciência e compreensão; nada faria sentido sem vocês! Ao Rafael, esposo dedicado e amoroso, que adiou seus próprios planos para me acompanhar e sempre esteve ao meu lado nos bons e maus momentos. Aos meus pais e irmãos por todo amor que me dão e pelos revigorantes e animados domingos com música e boa comida. Ao meu orientador, Prof. Rodolfo, sempre tão presente e motivador, minha admiração e infinitos agradecimentos por conduzir-me nessa jornada. Aos queridos colegas do LSC Tiago, Maxiwell, Gabriel, Raoni e Rafael Auler pelas inúmeras vezes que me ajudaram a entender o GIT (sinto muito, ainda vou precisar de vocês). Ao Diretor da Faculdade de Computação (UFMS), Prof. Nalvo, e ao meu colega de trabalho Prof. Ricardo Santos, por serem sempre tão compreensivos e prontos a ajudar. E aos que me ajudaram sem nem mesmo saber.

Quaisquer que sejam as contribuições técnicas desse trabalho, elas não se comparam à realização pessoal e sensação de dever cumprido que sinto nesse momento. Muito mais do que os resultados profissionais da tese, perdurará em mim e nos mais próximos a mim, o aprendizado obtido em cada etapa vencida. A todos que ajudaram nessa conquista, eterna gratidão!

## Resumo

Recentes metodologias e ferramentas de projetos de sistemas multiprocessados em chip (MPSoC) aumentam a produtividade por meio da utilização de plataformas baseadas em simuladores, antes de definir os últimos detalhes da arquitetura. No entanto, a simulação só é eficiente quando utiliza ferramentas de modelagem que suportem a descrição do comportamento do sistema em um elevado nível de abstração. A escassez de plataformas virtuais de MPSoCs que integrem hardware e software escaláveis nos motivou a desenvolver o MPSoCBench, que consiste de um conjunto escalável de MPSoCs incluindo quatro modelos de processadores (PowerPC, MIPS, SPARC e ARM), organizado em plataformas com 1, 2, 4, 8, 16, 32 e 64 núcleos, cross-compiladores, IPs, interconexões, 17 aplicações paralelas e estimativa de consumo de energia para os principais componentes (processadores, roteadores, memória principal e caches). Uma importante demanda em projetos MPSoC é atender às restrições de consumo de energia o mais cedo possível. Considerando que o desempenho do processador está diretamente relacionado ao consumo, há um crescente interesse em explorar o trade-off entre consumo de energia e desempenho, tendo em conta o domínio da aplicação alvo. Técnicas de escalabilidade dinâmica de frequência e voltagem fundamentam-se em gerenciar o nível de tensão e frequência da CPU, permitindo que o sistema alcance apenas o desempenho suficiente para processar a carga de trabalho, reduzindo, consequentemente, o consumo de energia. Para explorar a eficiência energética e desempenho, foram adicionados recursos ao MPSoCBench, visando explorar escalabilidade dinâmica de voltaegem e frequência (DVFS) e foram validados três mecanismos com base na estimativa dinâmica de energia e taxa de uso de CPU.

## Abstract

Recent design methodologies and tools aim at enhancing the design productivity by providing a software development platform before the definition of the final Multiprocessor System on Chip (MPSoC) architecture details. However, simulation can only be efficiently performed when using a modeling and simulation engine that supports system behavior description at a high abstraction level. The lack of MPSoC virtual platform prototyping integrating both scalable hardware and software in order to create and evaluate new methodologies and tools motivated us to develop the MPSoCBench, a scalable set of MP-SoCs including four different ISAs (PowerPC, MIPS, SPARC, and ARM) organized in platforms with 1, 2, 4, 8, 16, 32, and 64 cores, cross-compilers, IPs, interconnections, 17 parallel version of software from well-known benchmarks, and power consumption estimation for main components (processors, routers, memory, and caches). An important demand in MPSoC designs is the addressing of energy consumption constraints as early as possible. Whereas processor performance comes with a high power cost, there is an increasing interest in exploring the trade-off between power and performance, taking into account the target application domain. Dynamic Voltage and Frequency Scaling techniques adaptively scale the voltage and frequency levels of the CPU allowing it to reach just enough performance to process the system workload while meeting throughput constraints, and thereby, reducing the energy consumption. To explore this wide design space for energy efficiency and performance, both for hardware and software components, we provided MPSoCBench features to explore dynamic voltage and frequency scalability (DVFS) and evaluated three mechanisms based on energy estimation and CPU usage rate.

# List of Figures

| 1.1                          | Accuracy and Performance Trade-off                                                                                                                             | 14                                                                               |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.1                          | Relation between accuracy and performance in system simulators                                                                                                 | 19                                                                               |

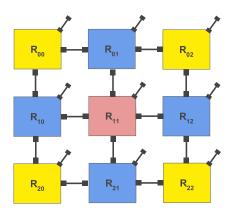

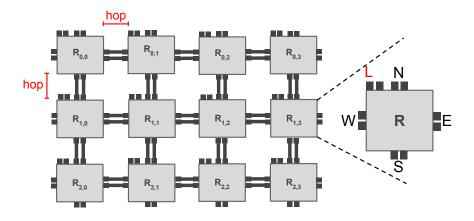

| 3.12<br>3.13                 | Example of a mesh-based platform                                                                                                                               | 34<br>34<br>35<br>37<br>37                                                       |

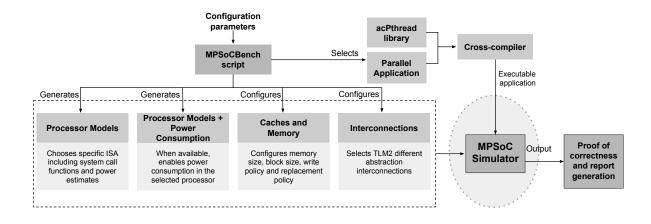

|                              | Development flow of a MPSoC simulator using MPSoCBench                                                                                                         | 53                                                                               |

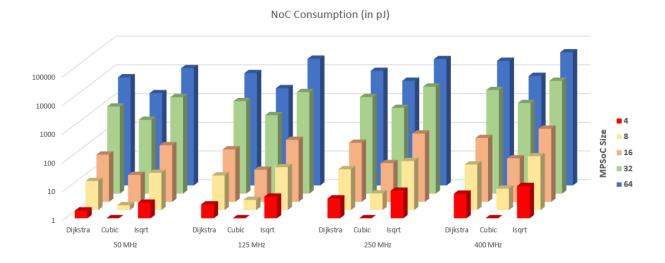

| 4.12<br>4.13<br>4.14<br>4.15 | Relation between simulation time using NoC-LT and Router Power estimation in MIPS dual-core and quad-core platforms Energy consumed in 2- and 8-MIPS platforms | 56<br>57<br>58<br>58<br>61<br>62<br>63<br>64<br>66<br>70<br>71<br>73<br>74<br>74 |

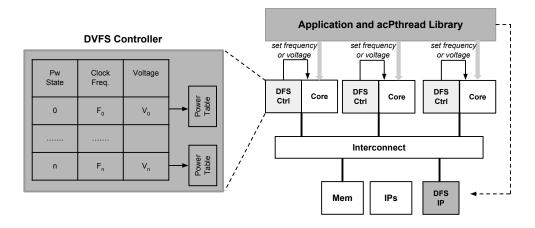

| 5.1<br>5.2<br>5.3<br>5.4     | The System Architecture including the DVFS controllers                                                                                                         | 78<br>79<br>83<br>83                                                             |

| 5.5 | Reevaluation method to establish new CPU usage rate bounds       | 84  |

|-----|------------------------------------------------------------------|-----|

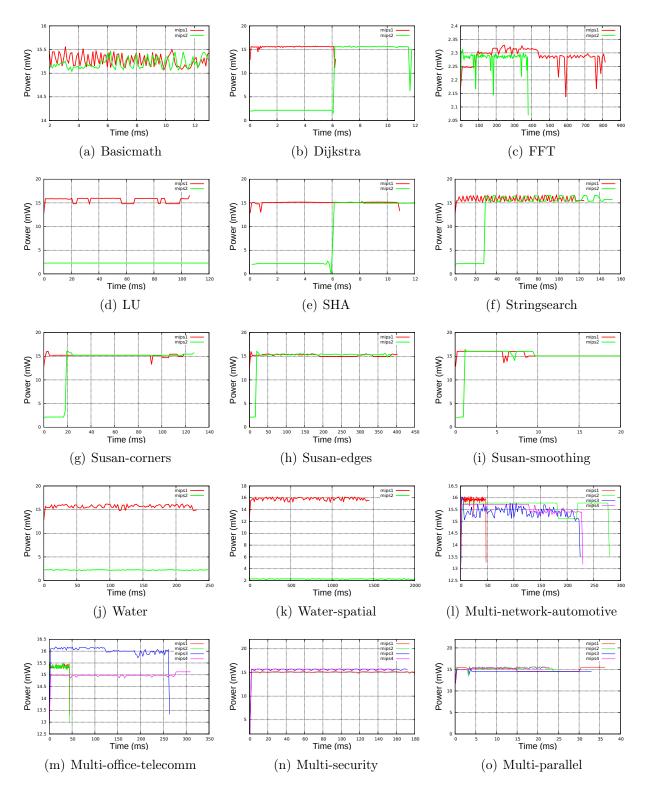

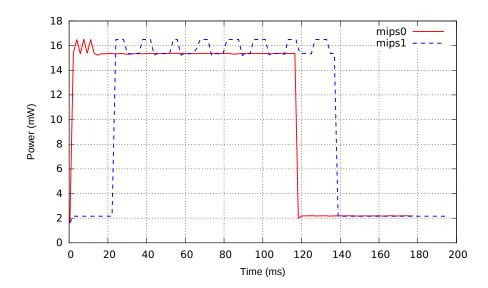

| 5.6 | Power vs Time in a dual-core MIPS platforms running Stringsearch | 86  |

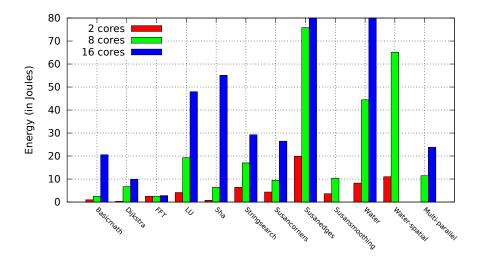

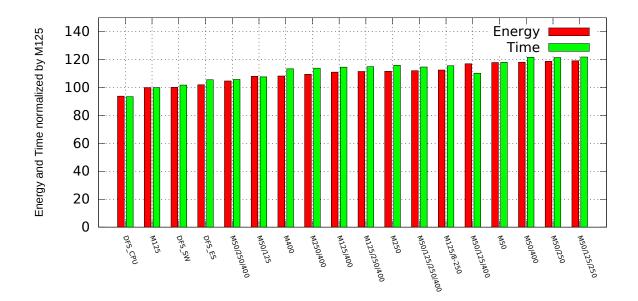

| 5.7 | Energy Consumption and Time                                      | 87  |

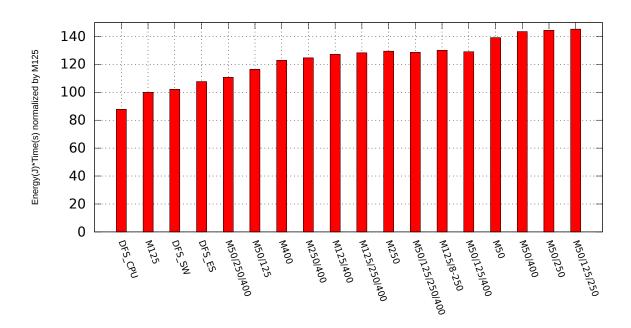

| 5.8 | Energy Delay Product                                             | 88  |

| В.1 | Example of an MPSoCBench report                                  | 114 |

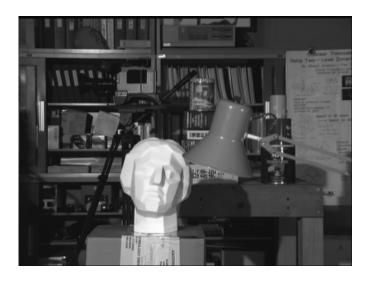

| B.2 | The susan-edges input file                                       | 115 |

| В.3 | The susan-edges output file                                      | 115 |

## List of Tables

| 2.1  | Comparison among Simulators and the MPSoCBench                      | 30 |

|------|---------------------------------------------------------------------|----|

| 2.2  | Comparison among Design Space Exploration Tools and the MPSoCBench. | 31 |

| 3.1  | Power Profiles Description for MIPS model                           | 48 |

| 3.2  | Energy characterization per MIPS instructions                       | 50 |

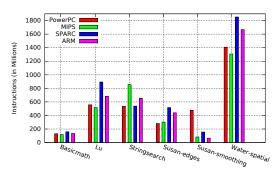

| 4.1  | Architecture and ISA general information                            | 56 |

| 4.2  | Number of packets transmitted through each Router in a $4x3$ NoC-AT | 59 |

| 4.3  | Memory average dynamic power                                        | 65 |

| 4.4  | Timing Information                                                  | 65 |

| 4.5  | Simulation Time using Router, PowerPC and MIPS models               | 67 |

| 4.6  | Simulation Time using Router, SPARC and ARM models                  | 68 |

| 4.7  | Simulation Time using NoC-LT, PowerPC and MIPS models               | 68 |

| 4.8  | Simulation Time using NoC-LT, SPARC and ARM models                  | 69 |

| 4.9  | Simulation Time using NoC-AT, PowerPC and MIPS models               | 69 |

| 4.10 | Simulation Time using NoC-AT, SPARC and ARM models                  | 70 |

| 4.11 | Most appropriate interconnections for each MPSoCBench use case      | 71 |

| 5.1  | Mechanism to adaptively establish bounds for each power state       | 84 |

| 5.2  | Average power saving with DVFS                                      | 85 |

| 5.3  | Energy Savings with DVFS-SW                                         | 87 |

| 5.4  | Performance Slowdown                                                | 88 |

## Contents

| 1 | Intr | roduction                                    | 14 |

|---|------|----------------------------------------------|----|

|   | 1.1  | Contributions                                | 15 |

|   | 1.2  | Organization                                 | 16 |

| 2 | Lite | erature Review                               | 17 |

|   | 2.1  | Modeling and Simulation Background           | 17 |

|   | 2.2  | Modeling and Simulation Tools                | 18 |

|   |      | 2.2.1 Functional Simulators                  | 19 |

|   |      | 2.2.2 Cycle Accurate Simulators              | 22 |

|   | 2.3  | Energy Consumption Concepts                  | 23 |

|   | 2.4  | DVFS Approaches                              | 24 |

|   | 2.5  | DVFS Simulators                              | 26 |

|   | 2.6  | Design Space Exploration Tools (DSE Tools)   | 28 |

|   | 2.7  | Benchmarks                                   | 29 |

|   | 2.8  | Characterizing Simulation and DSE Tools      | 29 |

| 3 | MP   | SoCBench                                     | 32 |

|   | 3.1  | Components                                   | 32 |

|   |      | 3.1.1 Processor Models                       | 33 |

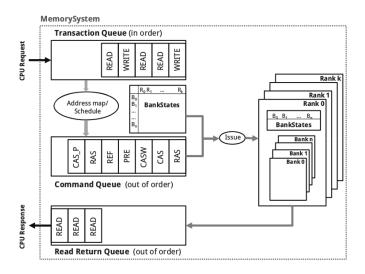

|   |      | 3.1.2 Memory                                 | 36 |

|   |      | 3.1.3 Caches                                 | 36 |

|   |      | 3.1.4 Interconnections                       | 38 |

|   |      | 3.1.5 Interrupt Controller                   | 39 |

|   |      | 3.1.6 DVFS                                   | 41 |

|   |      | 3.1.7 Lock                                   | 41 |

|   | 3.2  | Library for PThread Support and Applications | 41 |

|   | 3.3  | Timing Model for Communication               | 45 |

|   | 3.4  | Power Consumption Estimation                 | 47 |

|   | 0.1  | 3.4.1 Caches Power Estimation Model          | 51 |

|   |      | 3.4.2 NoC Power Estimation Model             |    |

|   | 3.5  | The MPSoCBench Simulation flow               | 53 |

|   | 3.6  | Conclusion                                   |    |

| 4 | MP   | SoCBench Characterization                    | 55 |

| _ | 4.1  | Processor Model Evaluation                   | 55 |

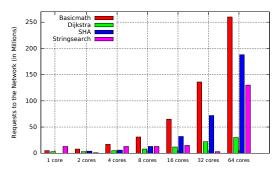

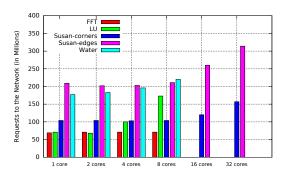

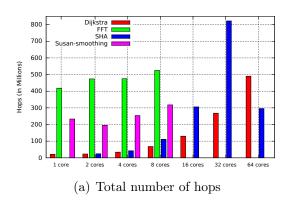

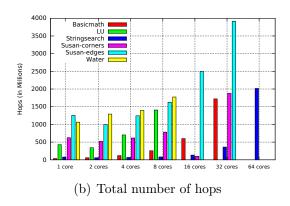

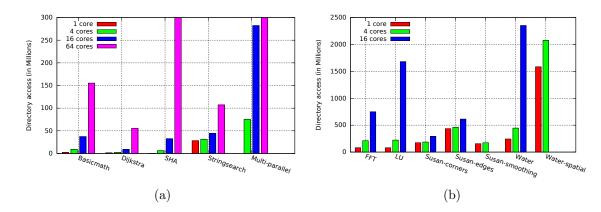

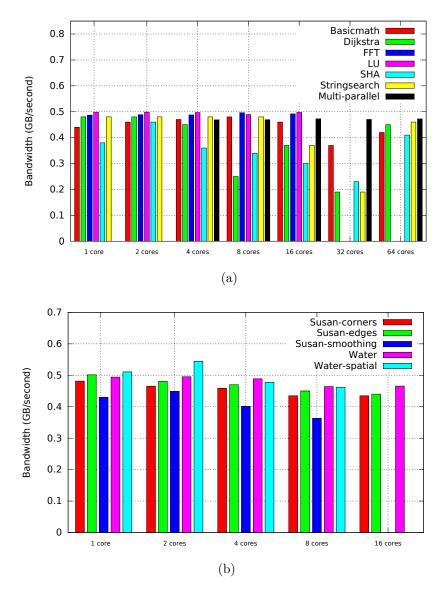

|   | 4.2  | Network Traffic                              | 57 |

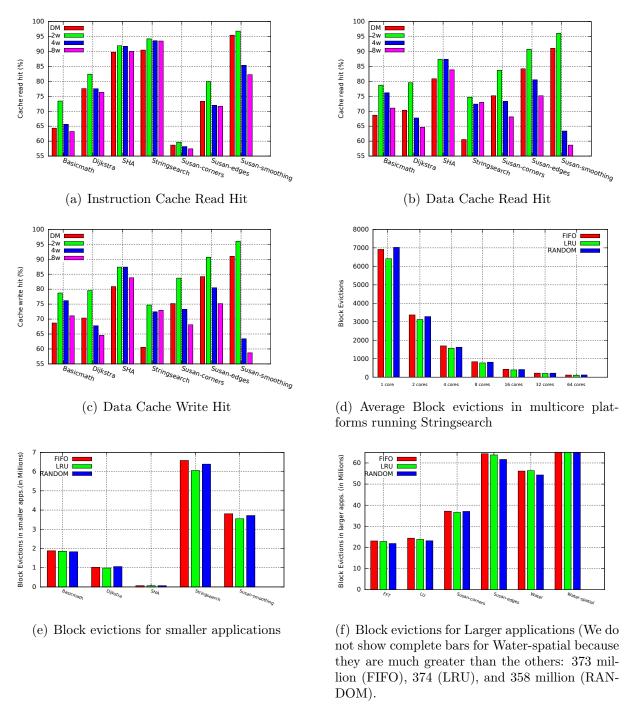

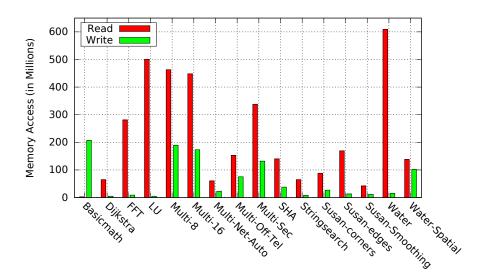

|   | 4.3  | Memory and Cache Evaluation                  | 60 |

|   | 4.4  | Timing Accuracy                              | 63 |

|   | 4.5  | Simulation Performance                       | 65 |

|    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <sub>3</sub> 7                         |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    |            | 4.5.2 How to improve performance                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

|    | 4.6        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72                                     |

|    | 4.7        | Other Usage Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                     |

| 5  | Dyr        | namic Voltage and Frequency Scaling                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>7</b> 6                             |

|    | 5.1        | Overall Energy Infrastructure                                                                                                                                                                                                                                                                                                                                                                                                                        | 77                                     |

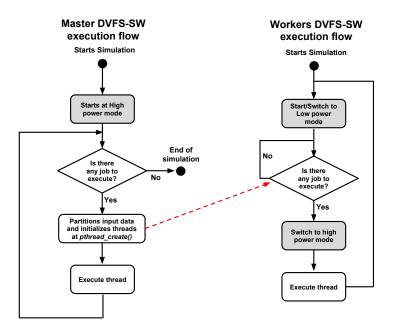

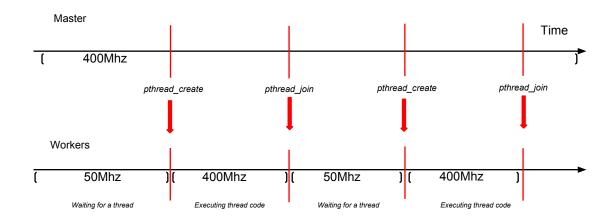

|    | 5.2        | DVFS controlled by Software (DVFS-SW)                                                                                                                                                                                                                                                                                                                                                                                                                | 78                                     |

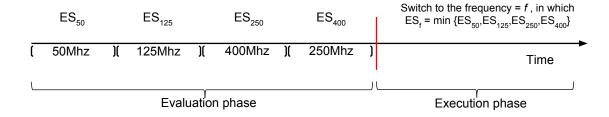

|    | 5.3        | DVFS based on the energy consumption (DVFS-ES)                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                     |

|    | 5.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                     |

|    | 5.5        | DVFS Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                     |

|    | 5.6        | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                     |

| 6  | Con        | nclusion                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90                                     |

|    | 6.1        | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91                                     |

|    | 6.2        | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                          | 93                                     |

| ъ. | 1. 1       | graphy                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95                                     |

| Bı | pnog       | 3 apriy                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,,,                                    |

|    |            | v To Install the MPSoCBench                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

|    | Hov        | v To Install the MPSoCBench                                                                                                                                                                                                                                                                                                                                                                                                                          | )4                                     |

|    | Hov        | v To Install the MPSoCBench  Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                             | <b>)4</b><br>)4                        |

|    | Hov        | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | <b>)4</b><br>)4                        |

|    | Hov        | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | <b>)4</b><br>)4<br>)4                  |

|    | Hov        | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | <b>)4</b><br>)4<br>)4<br>)4            |

|    | How<br>A.1 | v To Install the MPSoCBench  Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                             | )4<br>)4<br>)4<br>)4<br>)5             |

|    | How<br>A.1 | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | )4<br>)4<br>)4<br>)5<br>)6<br>)7       |

|    | How<br>A.1 | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | )4<br>)4<br>)4<br>)5<br>)6<br>)7       |

|    | Hov<br>A.1 | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | )4<br>)4<br>)4<br>)6<br>)7<br>)7       |

| A  | How<br>A.1 | v To Install the MPSoCBench       10         Source Code - Installing all tools manually       16         A.1.1 Requirements       16         A.1.2 Installing SystemC       16         A.1.3 Installing ArchC and Cross-Compilers       16         A.1.4 MPSoCBench       16         Virtual Machine       16         A.2.1 Requirements       16         A.2.2 Preparing the Virtual Environment       16         v To Use the MPSoCBench       10 | )4<br>)4<br>)4<br>)5<br>)6<br>)7<br>)7 |

| A  | How<br>A.1 | v To Install the MPSoCBench Source Code - Installing all tools manually                                                                                                                                                                                                                                                                                                                                                                              | 04<br>04<br>04<br>05<br>06<br>07<br>07 |

## Chapter 1

## Introduction

The use of multiprocessors in design of embedded systems introduces new significant challenges for system architects and hardware/software designers. In particular, it is necessary to develop tools based on new paradigms, able to deal with MPSoC complexities [63].

From the design perspective, productivity may be improved by evaluating and optimizing system components through a virtual platform before implementing the final system version. However, simulation can only be efficiently implemented when using a modeling and simulation engine that supports the system behavior description at high abstraction level [20].

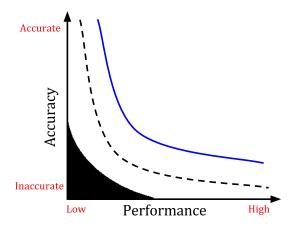

By dealing with the disagreement between increasingly complexity and shorter time-to-market, abstract models have been widely used, exhibiting significant gains in simulation speed, allowing fast evaluation and extensive design space exploration. This trade-off essentially allows models at different levels of accuracy and speed. However, it is typically not possible to achieve both high speed and high accuracy at the same time. High-level models fall into the area next to the dashed line in Figure 1.1. Models in the dark area obviously exist, but are practically unusable, because they present low performance and low accuracy, whereas models placed above the blue line are highly desirable although typically not achievable [85].

Figure 1.1: Accuracy and Performance Trade-off. Figure reproduced from [85]

Nowadays, there is a massive use of software-based models to verify the accuracy and quantitatively evaluate the system performance. In this scenario, architecture simulators play a significant role in computer architecture design. However, the obvious direction is to explore CMP (chip multiprocessor) designs, which include several new challenges, both in hardware management and development of software that take advantage of the parallelism capabilities.

With the emergence of Multiprocessor Systems on Chip (MPSoCs), power and energy consumption have become the most delicate and limiting issue for the proper functioning of the system. Designers need a global vision of the system power consumption in the earlier design stages to evaluate the effectiveness of the power management strategies beforehand [29].

The first simulators for public use emerged nearly fifteen years ago and have become increasingly robust since then [23]. Recently, some resources have been added to them to achieve power management, mostly through mathematical models for accurate power consumption estimates. The most widely used simulators that include support for power consumption are based on mathematical analysis and estimates rather than based on running applications, as we will see in the literature review presented in Section 2. Therefore, they need to be integrated with data obtained from performance simulators. Although effective, this technique has the disadvantage of having a simulation infrastructure based on two or more tools that do not always have a friendly interface for integration [66, 90].

Summarizing, our hypothesis is that MPSoC virtual platforms integrating high-level description of hardware components, scalable applications, and a target toolchain, focused on architectural exploration, power consumption, and performance estimation have the potential to be used on evaluation of new techniques and methodologies in the early stages of MPSoC and embedded designs.

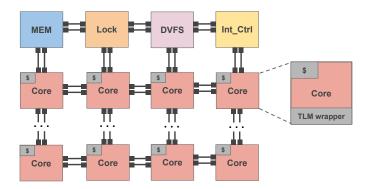

This thesis presents **MPSoCBench**, a simulation toolset consisting of a scalable set of MPSoCs to enable the development and evaluation of new tools, methodologies, parallel software, and hardware components. The toolset supports four distinct processors (ARM, MIPS, SPARC, and PowerPC) in many configurable and scalable MPSoC platforms with 1, 2, 4, 8, 16, 32, or 64 cores, with different interconnections that define different simulation abstraction levels.

This infrastructure includes 17 parallel benchmarks from SPLASH-2 [96], ParMiBench [57], Mibench [52] benchmarks, and a POSIX PThread emulation library. The tool also provides power consumption estimation for MIPS and SPARC processors, even in multicore environments. A total of 864 distinct configurations are available and automated through an execution script that also allows easy integration with a cluster for parallel execution. The number of possible configurations is even much higher if we consider different cache or power consumption parameters.

## 1.1 Contributions

The main contribution of MPSoCBench is to provide a completely open source simulation infrastructure including scalable hardware and software components, with easy

instrumentation and fast simulation at high abstraction levels to be used on evaluation of new techniques and methodologies in the early stages of MPSoC and embedded designs. We can cite the following specific contributions:

- A System level simulation infrastructure to address requirements in MPSoCs designs;

- Simulation at different abstraction levels, allowing exploring the trade-off between performance and accuracy at the early design stages;

- Easy configuration templates, enabling its use for both research and academic purposes;

- Basic infrastructure for dynamic estimation of power/energy consumption and DVFS techniques exploration;

- A significant set of parallel and scalable applications that use all available models, which characterizes the tool as a benchmark for MPSoCs;

## 1.2 Organization

This Thesis is organized as follows:

Chapter 2 explores the prior tools or libraries related to this work and exposes how they compare to the MPSoCBench main goals. It introduces basic modeling and simulation concepts and tools, describes prior work related to Dynamic Voltage and Frequency Scaling approaches, and also shows some tools for design space exploration. The main goal of this Chapter is to contextualize the MPSoCBench and compare it with the main tools and approaches that have usually been used.

Chapter 3 introduces the MPSoCBench toolset, which is a scalable, configurable, and extensible set of MPSoCs, useful to improve development and evaluation of the MPSoC ecosystem, using well-known methodologies and tools. We describe the hardware and power models available in the toolset, and the applications adapted to execute in the MPSoCBench virtual platforms.

Chapter 4 provides the MPSoCBench characterization, evaluating its main features, applications and issues related to simulators accuracy and performance. The Chapter includes discussions about simulation speed, simulation accuracy, network traffic, memory analysis, power estimation, TLM coding styles, and timing abstraction levels.

Chapter 5 presents the infrastructure of the MPSoCBench DVFS support, describing power models and evaluating three DVFS techniques based on energy estimation and CPU-usage rate. The main goal of this Chapter is to show that MPSoCBench can be used to perform full-system power efficiency studies in a fast simulation environment;

Chapter 6 concludes the text and presents our main contributions, published papers and future work. Appendix A presents a tutorial on how to installing necessary tools to use the MPSoCBench. Appendix B presents a tutorial on how to use the MPSoCBench.

## Chapter 2

## Literature Review

This Chapter describes basic concepts and previous work related to our research. To improve clarity, we have divided the review in seven main areas: Section 2.1 introduces some basic concepts, tools and languages related to modeling and simulation; Section 2.2 describes prior work on simulation tools; Section 2.3 reviews basic concepts about Dynamic Voltage and Frequency Scaling (DVFS), Section 2.4 details relevant DVFS approaches, and Section 2.5 presents tools that implement DVFS; Section 2.6 shows tools for design exploration of MPSoCs. Finally, Section 2.7 exposes the benchmark suites that we use to evaluate our tools and methodologies. At the end of each Section we briefly compare the tools previously presented with the MPSoCBench features.

## 2.1 Modeling and Simulation Background

The best choice of the abstraction level in the modeling process is essential to find balance between productivity and modeling level of details. In RTL (Register Transfer Level) design, circuit behavior is described in terms of signals representing data transfer between registers and logic operations conducted over these signals. RTL abstraction is used in hardware description languages like Verilog and VHDL to represent low-level circuits, which are derived from the hardware connections.

Considering the increasing complexity of system designs, the approach adopted by SoC industry is to keep abstraction above RTL during the early stages of the project and reach RTL level in the synthesis stage after successive stages of design refinement. This approach is known as System Level and is characterized by the system specification as a set of software components, hardware components and applications, with a primary focus in the relationship among the subsystems.

**SystemC** [2] is a collection of C++ classes and templates that provides powerful mechanisms to model system architecture with hardware timing, concurrency and reactive behavior, allowing the creation of an executable specification of the system. SystemC is one of the most suitable choices for system design.

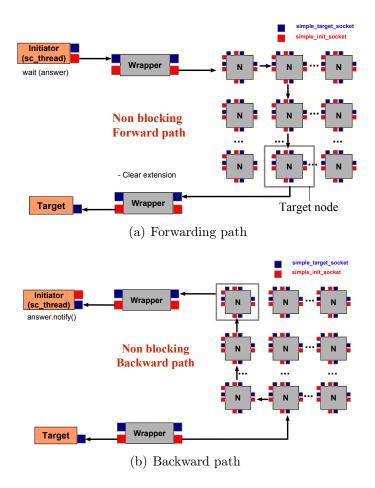

In the context of this work, we describe a hardware system as a virtual platform, which is typically implemented as several Transaction-Level (TLM) [1] models, which are a higher level representation of hardware behavior, focusing on discrete events such

as register reading and writing. Although TLM is language independent, SystemC fits perfectly in its representation style, allowing adequate abstraction levels and providing elements to isolate computation and communication.

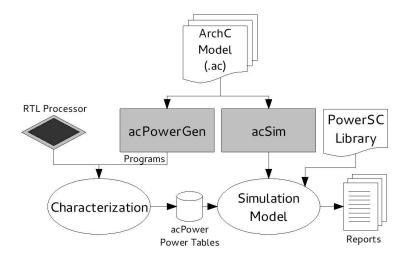

ArchC [12] is an Architecture Description Language (ADL) following a SystemC syntax style, which provides enough information in order to allow users to explore and verify a (new or legacy) processor architecture. This ADL automatically generates not only software tools for code generation and inspection (like assemblers, linkers, and debuggers), but also executable processor models for platform representation. PowerSC is a SystemC extension designed to collect and process switching activity [59]. As ArchC generates a SystemC processor description, it is an eligible candidate to PowerSC workflow. acPower is a library that connects ArchC to PowerSC, thus enabling the power analysis of ArchC processor modules [50].

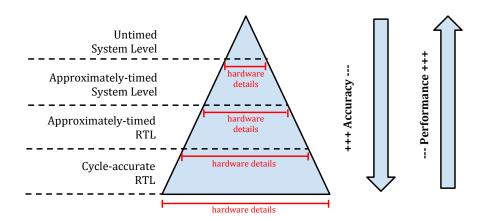

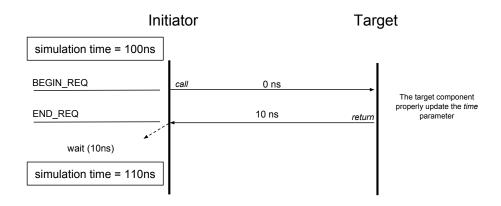

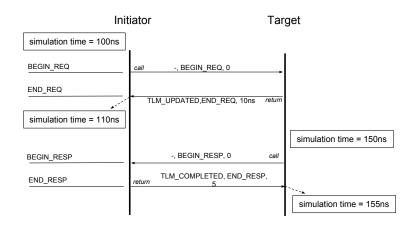

An important feature of TLM models is their ability to provide data related to the timing and synchronization of devices. Thus, it is possible to establish different abstractions related to the accuracy of the simulator timing information:

- Untimed: At this level, the behavior of the components is described without time information associated with the model. Any statistics related to performance can be expressed in terms of the amount and the type of activities performed during the simulation. The CPU models described in this level are called functional models;

- **Approximately timed:** Any time information is added into the model, even if not very accurate, making it possible to couple timed peripherals to the model without difficulty;

- Cycle-accurate: At this abstraction level, the microarchitecture is simulated on a cycle-by-cycle basis. Although not always synthesizable, the model behaves exactly like the real implementation of the circuit in regard to the timing. A precise amount of time should be associated with each functionality of the component and the simulated time should take place according to this value.

Figure 2.1 shows that the accuracy increases as the design description progresses from a high level untimed models to cycle-accurate RTL abstraction level. In contrast, the performance decreases when we move from high level to accurate levels.

MPSoCBench uses SystemC 2.3 [2] as simulation infrastructure, TLM2 for standard interconnection, ArchC 2.3 [12] to generate processor models and cross-compilers, and the PowerSC extension for power models. It is open source, and available under GPL license.

In the following sections we describe tools for modeling and simulation in accordance with different abstraction levels.

## 2.2 Modeling and Simulation Tools

A large number of processor simulation tools have been developed in the last decade. In the context of this research, we divide them into roughly two categories: functional simulators and cycle accurate simulators. Functional simulators precisely emulate each

Figure 2.1: Relation between accuracy and performance in system simulators. Figure reproduced from [83].

instruction in the target instruction set, but do not provide any cycle accurate timing information. Cycle accurate simulators, on the other hand, construct a complete microprocessor pipeline in software and simulate the flow of each instruction through this pipeline, to collect much more accurate timing information down to individual cycles. This extra accuracy comes at the cost of longer simulation times.

There are also simulators in lower abstraction level, such as RTL models and circuit level models, but we consider them out of the scope of this work.

#### 2.2.1 Functional Simulators

Proceeding from high-level to low-level, the simulations become more accurate, but they also become progressively more complex and take longer to run. Once a behavioral or functional simulation predicts that a system works correctly, it ignores accuracy of timing. Although it may set fixed delays to measure time, this is not the major concern.

A functional simulator is an abstract description of the hardware architecture and its behavior, and it has been widely used in the early stages of hardware design evaluation. The following paragraphs contain a brief description of the existing functional simulators, used both in industry or academic research.

Bochs [61] is one of the first well-known open source x86 functional simulator, which supports nearly all its features. Bochs provides complete x86 PC emulation, including the ISA, hardware devices, and memory. This allows users to run OS's and software within the emulator on their workstation. In fact, Bochs is much like a virtual machine that emulates the hardware of interest. The guest OS interacts with the virtual machine, which in turn interacts with the host hardware. The virtual machine collects the instructions the guest is about to run, and emulate them replacing instructions with alternatives as necessary. The disadvantage is that emulation has a substantial computational overhead, and can be slow.

A commercial simulation suite available since 2002 is **Simics** [71], a functional simulation suite for various processor families (including x86) as well as user-designed plug-in

models of real hardware devices. It uses x86-to-x86 binary translation to achieve good performance. However, it does not include cycle-accurate simulation features below the x86 instruction level (just like any other functional simulator). The purpose of simulation in Simics is often to develop software for a particular embedded hardware, using Simics as a virtual platform.

Leveraging the power of Simics as an underlying foundation, Martin et al. presented **GEMS** [73], a full-system multiprocessor simulator that uses Simics as its base and incorporates extensive features to design, specify and validate new cache coherence protocols. The GEMS toolset adds a fairly detailed out-of-order processor simulation model and detailed memory model on top of the functional full-system simulation environment provided by Simics.

Another well known and more robust emulator is **QEMU** [13], that is a fast machine emulator using an original portable dynamic translator, which emulates several CPUs (x86, PowerPC, ARM and SPARC) on several hosts (x86, PowerPC, ARM, SPARC, Alpha and MIPS). It uses dynamic compilation to achieve significantly faster simulation speeds compared to pure interpretation.

One of the first ARM-based platform was presented by Benini et al. [15] as the MP-ARM, a complete platform for MPSoC research, including processor models (ARM) modeled in SystemC, SoC bus models (AMBA), memory models, hardware support for parallel programming, a fully operational operating system port (UCLinux) and code development tools (GNU toolchain). The main disadvantages is that the processor cores supported in the MP-ARM framework are relatively simple and the automatic construction of performance models for coprocessors from high-level functional specifications is not supported. Using MP-ARM, Loghi, Poncino and Benini [68] run realistic applications in order to obtain accurate functional behavior and power and performance analysis of the system.

Few years later, Mahadevan et al. [72] proposed a traffic generator model (TG) that is aimed at faithfully replicating traffic patterns generated by a processor running an application. At the same time, this approach allows a straightforward path towards deployment of the TG device on a silicon NoC test chip. To evaluate the concept, the proposed model was integrated into MP-ARM [15].

The first important results about the use of a parallel simulation infrastructure to evaluate techniques for application-to-platform mapping was presented by Paulin et al. in 2004 and 2006 [79,80] and extended by Beltrame, Sciuto and Silvano in 2008 [14]. First of all, Paulin presented the **MultiFlex** [79,80] environment as an application-to-platform mapping tool that integrates heterogeneous parallel components (HW and SW) into a platform programming environment; this tool is more focused in network and multimedia applications. Next, in 2008, Beltrame, Sciuto and Silvano [14] showed how it is possible to map applications to the MultiFlex platform. Once the application has been partitioned and mapped to the target platform according to its performance and power constraints, it is possible to further optimize its power consumption with the use of a proper Dynamic Power Management System (DPMS).

In 2007, a single-application simulator named Multi2Sim was proposed by Ubal et al. [94], which intended to simulate final MIPS-32 executable machine. The tool includes cross-compiler and three simulation techniques: functional, detailed and event-driven.

The Michigan M5 Simulator proposed by Binkert et al. in [17] provides a highly configurable simulation framework, multiple ISAs, and diverse CPU models; It supports the booting of entire operating systems, as well as the execution of unmodified application binaries using system-call emulation. However, only a shared-bus model is supported to model interconnection of multiple processor cores, and only four processor cores can be simulated at a time. In 2011, Nathan et al. [16] presented the merge of the best aspects of the M5 and GEMS [73] simulators, resulting in the **gem5** Simulator. In 2012, the accuracy of this new powerfull tool was evaluated by Butko et al. in [27].

Another extension of the gem5 infrastructure was presented by Power et al. [82] and contains a simulator built on gem5 [16,27] and GPGPU-Sim, a detailed GPGPU simulator. This extension routes most memory accesses through Ruby, which is a highly configurable memory system in gem5. Applications can launch non-blocking kernels, allowing the CPU and GPU to execute simultaneously.

The OVP [56] is a hardware simulator written in C language, instruction-accurate, open-source and able to simulate an entire platform. OVP offers a large model database, supporting several processor families (like MIPS, ARM and PowerPC) besides many peripherals.

In 2014, Endo, Courouss and Charles [42] described the implementation and accuracy evaluation of a micro-architectural simulator of Cortex-A cores, supporting in-order and out-of-order pipelines and based on the open-source gem5 simulator. They showed how to simulate Cortex-A8 and Cortex-A9 cores in gem5, and the execution time of ten benchmarks were compared against real hardware.

In order to provide an open repository of SystemC models, Mello et al. [75] introduced SoCLib, which is an open platform for virtual prototyping of MPSoCs. The core of the platform is a library of SystemC models for virtual components (IP cores). Although there are many components available in SoCLib design repositories, modeling platforms containing multiple devices to evaluate MPSoCs demands a significant effort of joining them together. None of them provides neither a comprehensive set of scalable software to run on platforms nor a framework to simplify new hardware integration.

The SESC (SuperESCalar Simulator) [78] is an event driven simulator for the MIPS processor architecture, in which the instructions are executed in an emulation module that emulates the MIPS Instruction Set Architecture (ISA). In 2013, Ardestani et al. [10] presents ESESC, an architectural simulator for multicore processors, based on Time-Sampling with virtually no limitation in terms of application type (multiprogrammed or multithreaded), number of cores, homogeneity or heterogeneity of the simulated configuration. They modify SESC and use QEMU as the functional emulator executing ARM instructions.

In the previous paragraphs, we described some of the most popular functional simulators of processors or complete systems, of which some are very elaborate and other pretty simple. Although MPSoCBench contain high level processor models and devices,

its interconnection mechanism allows timed communication using TLM2, placing the MP-SoCBench on the edge between functional and timed simulation.

## 2.2.2 Cycle Accurate Simulators

In the following paragraphs we describe some cycle-accurate simulators released in the last decade. Since cycle-accurate models tend to have low performance, most simulators have a hybrid approach, where only part of their components is accurate (for instance: the interconnection, caches, or single processor). Simulation of complete cycle-accurate platforms tend to be very inefficient.

In 1996, Todd Austin et al. [11,25,26] introduced **SimpleScalar**, a simulator for outof-order superscalar processor pipelines, with the ability to model multiple application

workloads or shared-memory parallel applications, as well as the simulation of multiple

processor cores. It can model a variety of platforms ranging from simple unpipelined processors to detailed dynamically scheduled microarchitectures with multiple-level memory

hierarchies. The tool set's instruction interpreters also support several popular instruction

sets, including Alpha, PPC, x86, and ARM. Although robust, SimpleScalar is becoming

obsolete due to a dependence to an outdated compiler version. **PTLSim** [98] was the

first open source cycle-accurate that that really simulates the x86 instruction set, instead

of just interpreting it. PTLsim has models for out of order x86-64 processor cores at a

configurable level of detail ranging from RTL-level models of all key pipeline structures,

caches and devices up to full-speed native execution on the host CPU. Released two years

later by Zeng et al. [99], the **MPTLSim** is a cycle-accurate, full-system simulator for

multicore designs based on the x86-64 ISA, a natural multicore extension of PTLSim.

One of the most complete work on MPSoC platforms was proposed by Boukhechem and Bourennane (StarSoC, in [20]), which contains an OpenRISC processor as the central part of the system and includes SystemC communication models (Whishbone bus). It made use of an open source ISS of or1Ksim simulator platform, which is designed for uni-processor simulation. In order to use it for the simulation of multiprocessor systems, several ISSs with SystemC communication platform models were connected by using UNIX Inter Process Communication. As an extension of this previous work, Boukhechem, Bourennane and Samahi have compared in [21] three abstraction levels using the StarSoC platform: the traditional register-transfer level modeling (Verilog model) and transaction-level modeling at instruction accurate level and cycle-accurate level. In 2008, Boukhechem et al. [22] defined the methodology to construct the STARSoC TLM simulation environment, which provides a rapid and accurate design space exploration at higher abstraction levels for multiprocessor system on chip architectures.

Ferri et al. [44] provide a cycle-accurate cache-coherent ARM-based cluster similar to ARM's MPCore. This infrastructure is useful for evaluating hardware transactions memory solutions for embedded architectures. Their experiments show that transactional memory can provide clear performance advantages, but it is essential to consider carefully the hardware design in order to conform energy constraints of the system.

Agarwal et al. [4] developed a detailed cycle-accurate interconnection network model (GARNET), inside the GEMS full-system simulation framework, which includes models

with microarchitectural details, such as flit-level input buffers, routing logic, allocators and the crossbar switch. GARNET, along with GEMS, provides a detailed and accurate memory system timing model.

Recently, Alali, Assayad, and Sadik [6] introduced an MPSoC composed of MicroBlaze microprocessors, memory, a timer, a VGA and an interrupt handler with two examples of software. The main contribution of this work was to show that simulators using Timed Programmer's View (PV+T) can achieve timing fidelity with high performance.

In the previous paragraphs we briefly discussed about prior cycle-accurate simulation tools and applications, along with their strengths and weaknesses.

## 2.3 Energy Consumption Concepts

The total power consumption  $P_{total}$  of the computer system may be separated into two components, as we show in Equation 2.1:

$$P_{total} = P_{system} + P_{CPU} \tag{2.1}$$

$P_{CPU}$  is consumed by the CPU itself and  $P_{system}$  by the rest of system. The power consumption  $P_{CPU}$  of the CPU can also be split into two parts, as we show in Equation 2.2:

$$P_{CPU} = P_{dyn} + P_{leak} (2.2)$$

$P_{dyn}$  is the power consumed by the CPU during the computation, resulted from the transistors switching activities, and  $P_{leak}$  is the power due to leakage effects inherent to silicon-based transistors, originated from currents that flow between differently parts of the transistor. Notwithstanding the existence of multiple sources of leakage in CMOS<sup>1</sup> transistors and their particularities, leakage current models are accurate yet complex since thay depend on the multiple parameters [3].

Given the different sources of power consumption, the total power can be rewritten as we show in Equation 2.3:

$$P_{total} = P_{system} + P_{leak} + P_{dyn} (2.3)$$

The dynamic power consumption in CMOS can be described by Equation 2.4, where f is the switching activity, C is average capacitance loading of the circuit, and V is the supply voltage. To minimize power consumption, we can reduce f, C or V [91].

$$P_{dyn} = f.C.V^2 (2.4)$$

Since it was first proposed in 1994 by Weiser et al. [95], *Dynamic Voltage and Frequency Scaling (DVFS)* techniques have proven to be highly effective in achieving low power consumption on a wide range of computing systems.

DVFS deals with the management of a system power consumption and its main idea is to adaptively scale the supply voltage and frequency levels of the CPU so as to reach

<sup>&</sup>lt;sup>1</sup>CMOS is short for complementary metal oxide semiconductor, a widely used type of semiconductor for constructing integrated circuits.

just enough performance to process the system workload while meeting throughput constraints, and thereby, reduce the energy dissipation [62]. The technique is able to reduce the dynamic power consumption of a CMOS integrated circuit by reducing the voltage and the clock frequency at which it operates.

The relationship between the power P(t) (Watts or Joules/s) and the energy  $E(\Delta t)$  (Joules) consumed by an electrical system over a time period  $\Delta t$  is given by equation 2.5.

$$E(\Delta t) = \int_0^{\Delta t} P(t) \tag{2.5}$$

In a computing system, the time factor is the execution time, which is inversely proportional to the frequency that the CPU operates. On the other hand, the power P in a CMOS-based circuit is directly proportional to the frequency and the square of the voltage that the system operates (2.6), and therefore, so as the energy (2.7) [89].

$$P \propto f.V^2 \tag{2.6}$$

$$E \propto V^2$$

(2.7)

Voltage and Frequency are determined together based on system requirements. The voltage can be reduced if the frequency is also reduced. This can yield a significant power saving because of the aforementioned  $V^2$  relationship [62]. Therefore, DVFS techniques are able to save power and energy of a CMOS integrated circuit by reducing the frequency and/or voltage at which it operates.

One of the main metrics to evaluate the trade-off between energy consumption and the system performance obtained by power saving techniques is the energy delay product (EDP), which was initially proposed by Horowitz [54] and has been largely applied since then [24]. The Energy curve is produced similar to the runtime curve using measured CPU energy instead of measured runtime. The EDP is described by the equation 2.8, where E is the energy consumed, T is the execution time and w=1,2 or 3. The value of w represents how the metric might differ depending on the weight given to time or performance.

$$EDP = E.T^w (2.8)$$

In the next section we describe several DVFS approaches implemented and evaluated in the last few years.

## 2.4 DVFS Approaches

Although relatively recent, DVFS literature is rich and diversified. This section describes relevant applications of DVFS, algorithms and tools that implement them.

In general, most DVFS algorithms work predicting future processing demands, usually from observed past behavior, and use that information to determine the appropriate processor speed and the corresponding frequency and voltage.

Kong et al. [60] propose an energy management technique to explore the trade-off between energy/power consumption and performance. They use a DVFS algorithm which manages energy and power consumption adaptively. Their scheme is based on a previous profiling: they calculate the EDP metric for each application in the workload, in order to characterize the best power-state for each application. The EDP metric is based on the energy consumption (Joules), CPI (clock cycle per instruction) and cycle time.

All information is stored in two tables, such that one is stored in a volatile memory and the other is saved in a non-volatile memory for future use. Next, they consult one of these tables *on-the-fly* to choose the adequate power state for each application. The great advantage of this technique is that considering both energy and delay of the applications, it reduces EDP significantly and effectively.

Although DVFS techniques promise to reduce power consumption while leading to significant reduction in the energy required for a computation, recent developments in processor and memory technology have resulted in the saturation of processor clock frequencies and larger static power consumption, which limit the potential energy savings resulting from DVFS.

Le Sueur et al. [62] exam the potential of DVFS across three platforms with recent generations of AMD processors and they find that while DVFS is effective on the older platforms, it actually increases energy usage on the most recent platform, even for highly memory-bound workloads. They justify this argument because when the first DVFS proposal was published by Weiser [95] in 1994, transistor feature sizes were approximately  $0.8 \,\mu m$  and typical core voltages were 5V. Furthermore, the ratio of dynamic power (which DVFS can reduce) to static leakage power was high. Therefore, energy savings resulting from DVFS could be significant.

However, modern CPUs have transistors with feature sizes smaller than  $32\eta m$  and core voltages at the highest frequency are around 1V. According to Le Sueur, "The small feature sizes result in leakage power reaching or exceeding dynamic power, and the low core voltages reduce the voltage-scaling window (which is limited by the 0.7~V threshold voltage of silicon transistors). Therefore, the potential to save energy via DVFS is dramatically reduced". This result is strong but limited, since their analysis is simplified by only considering a single memory-bound benchmark, and server-class platforms, which are not very representative for embedded, for example. In their point of view, the industry must adopt ultra-low-power sleep modes to save energy.

Also in this context, Castagnetti et al. [29] discuss that the relation  $E \propto P$  that relates energy and power is simplistic and not applicable for complete system designs. So, they propose a power and energy model for a DVFS enabled mobile computing platform, and the results show that the CPU energy saving is far less than when using a model that does not take into account the effect of the static power.

Notwithstanding to all those results about the effect of the static power in modern CPUs, a lot of research has been published proposing DVFS techniques that obtained gains when focused on different approaches. Genser et al. [48] have concentrated on voltage regulators to propose a new DVFS hardware extension to a power emulation approach for modeling the voltage regulator behavior, which allow for performance, power and energy efficiency investigations for embedded.

Lu, Lai and Huang [70] examine many previous parallel processing architetures and DVFS mechanisms. They propose two different orientations of parallel DVFS-enabled H.264/AVC decoders, and implement a multimedia heterogeneous multi-core platform. Halimi et al. [53] propose FoREST, a new runtime DVFS controller able to estimate the energy savings it can achieve from power gains. It determines the potential energy gains from two phases: an offline phase exploiting energy probes embedded in processors, and runtime speedup measurements for the most interesting frequencies.

There is a large amount of work for energy efficient communication via different DVFS scheduling algorithms. Kappiah et al. [58] devised a system that exploits slack arising at synchronization points of MPI programs by reducing inter-node energy gear via DVFS. Li et al. [65] proposed to characterize energy saving opportunities in executions of hybrid MPI/OpenMP applications without performance loss. Predictive models and novel algorithms were presented via statistical analysis of power and time requirements under different configurations. Next, Li et al. [92] extend theses previous works proposing an adaptively DVFS scheduling strategy to achieve energy efficiency for data intensive applications, and further save energy via speculation to mitigate DVFS overhead for imbalanced branches; their A2E scheduling method adaptively schedules an appropriate CPU frequency for the hybrid energy saving block, which is defined as a statement block of one specific type of workload such as computation, communication, memory access, etc, where runtime energy savings may be achieved by different means.

Yadav et al. [97] come up with LAURA-NoC, a NoC with distributed approach to dynamic DVFS, in which very simple local DVFS controllers automatically determine the appropriate clock frequency and voltage, eliminating the need for a global controller. 2 voltages and 16 frequencies values are available in each switch.

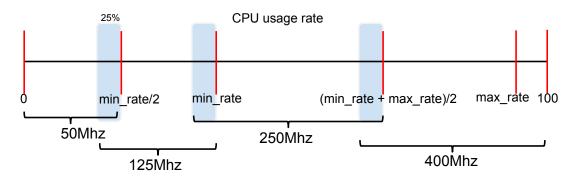

In Chapter 5 we describe and evaluate three different DVFS techniques in the MP-SoCBench (DVFS-SW, DVFS-ES, DVFS-CPU) confirming the argument that the tool has sufficient infrastructure to explore the trade-off between performance and energy constraints. The DVFS-SW perform frequency and voltage scaling managed by software; DVFS-ES and DVFS-CPU are frequency and voltage auto-selection techniques performed by each core of the platform: the first of them uses the energy consumption as the main metric and the second one uses the CPU workload to choose the best values of frequency and voltage dynamically.

## 2.5 DVFS Simulators

By improving simulators with some DVFS support, it is possible to carefully plan the DVFS mechanisms at design time, optimizing system thermal profile, preventing runtime emergencies, and controlling the trade-off between system performance and power consumption. Although there are several performance simulators, few of them have power modeling and power control features. We describe in this section some relevant tools with DVFS support.

One of the first tools including power features was presented by Brooks [23]. The **Wattch** deal with power-related issues and it was successfully used as an extension for several performance simulators, such as the SimpleScalar simulator.

McPAT (Multicore Power, Area, and Timing) [66] is a tool for modeling and estimation of physical parameters (power, area, clock frequency) for multiprocessor systems. Its main focus is to model accurately, based on performance parameters and manufacturing technology information, a set of physical parameters, providing real statistics that can be used to support design decisions of MPSoCs.

In combination with performance simulators, McPAT uses input parameters from an XML-based interface that defines the target system design: cache levels, cores, pipelines per core, cores homogeneity/heterogeneity and other parameters. The McPAT output shows results, organized by components (CPU, cache, arithmetic units, buses, and so forth), and for each one of them, it shows the area and power consumed according to the manufacturing technology and clock frequency. McPAT is not a simulator itself and produces estimation data that, although accurate, does not reflect the dynamic behavior of the applications.

One of the aforementioned integration between performance and power tools was obtained joining gem5 and McPAT to get system power estimation. Performance statistics are collected from gem5 and fed through McPAT to provide the final estimation. Voltage and frequency are some of the design parameters expected by the McPAT. So, the designer is not allowed to change these values unless he starts a new system design; this is an important limitation of this infrastructure. Furthermore, the interface of McPAT is hard to feed, due to the great amount of architecture and design parameters, which can not always be achieved.

To improve the aforementioned limitations, Spiliopoulos et al. [90] propose to make the Gem5 suitable for full-systems DVFS studies, including clock and voltage domain declaration, online power-estimation, a DVFS controller, and libraries for DVFS support. As limitations, this infrastructure does not have yet idle-power management or power/thermal monitoring sensors.

Created in the context of joining performance simulators and thermal analysis, the SST framework [55] is useful for architecture-level power, area, and thermal simulation, which focus on large-scale systems, but application traces are emulated, rather than collected from cycle-accurate simulation, with higher simulation rate at the cost of lower accuracy. In the same context, Zoni, Corbetta and Fornaciari [100] introduce HANDS, a novel framework for joint thermal, performance and power analysis to be used both at early design stages, while the extracted information can be used for further localized platform optimizations and trade-off exploration.

The MPSoCBench already has both power and DVFS features based on high level power estimation, which are described in Chapters 3 (power models) and 5 (DVFS features).

## 2.6 Design Space Exploration Tools (DSE Tools)

It is well known that MPSoCs design complexity induces the use of automatic design space exploration (DSE) tools to explore design alternatives before real implementation.

There are several proposals to characterize a system with multiple processing cores on a single chip. Proposals range from specification models [81], up to the development of tools and frameworks to offer more support to the design space exploration at different abstraction levels [5,33,45,86]; we will describe several of them in the following paragraphs.

Angioline et al. [9] propose a methodology to integrate pre-existing standalone CAD tools in a complete virtual platform, therefore paving the way for faster and more thorough analysis of the available architectural choices. They explored alternative ways to implement such an integration, defining two wrapping policies to give different emphasis to the cache design. Subsequently, they applied the methodology to state-of-the-art CAD tools, such as the commercial LISA [30] suite and the academic MPARM [15] environment.

Maintaining the accuracy by low-level simulation-based tools together with the performance in execution time of analytical-based tools was the goal achieved by Johann Filho et al. in [45]. In this sense, they propose a platform, a design flow and a tool for execution time and energy consumption estimation of homogeneous MPSoCs. The platform is composed of four processors interconnected by a bus system and described in VHDL used as a case study for estimation tool evaluation. After synthesizing the VHDL high-level description of the platform into a gate-level (RTL), time execution and energy consumption estimations are taken from RTL descriptions and organized in a high-level tool, to speedup simulation times.

The focus of the work in [86] is on the Transaction Accurate (TA) level which uses Transaction Level Modeling (TLM) for MPSoC architecture to speed up simulation at the cost of less accurate performance. Instead of using traditional Instruction Set Simulators (ISS), software tasks are annotated with timing information and executed locally with much higher speed. The annotated execution time for each software task is based on statistical processor properties.

The **Sniper** [28] simulator has been used to estimate application performance by employing an analytical model to raise the abstraction level. A similar proposal adopts the M5 simulator [33] to address the trade-off between power and performance by constructing an analytical model based on an extension of Pollack's Rule [19] and Amdahl's Law [8].

In 2011, the **Multicube** was proposed by Silvano et al. [88]. It is an open-source framework for multiprocessors design space exploration. The goal is to drive an architecture designer towards near-optimal parameters, using a set of strategies (multi-objective model formulation and heuristics) to model and solve the problem of architectural exploration.

Petry et al. [81] approach the use of a set of models that describe a whole MPSoC at several abstraction levels. Models of processors, memories, network interfaces, NoCs and software applications can be combined using an integration framework, which is capable of generating a complete executable MPSoC model. Design elaboration, simulation of real

and synthetic applications and debugging can be accessed directly from the integrating environment, in most cases.

We have an ongoing project which includes mechanisms to use a performance-based simulator like MPSoCBench with a low-level power and an area estimation tool like Mc-PAT for design space exploration. We've apply this mechanism in a tool named **Multi-explorer**. Although this tool has been improved to cover other issues (dark silicon, for instance), we published the first version of Multiexplorer in [32]. We describe briefly this project in the conclusion (Chapter 6).

## 2.7 Benchmarks

On the software scenario, there are also benchmarks that we adapted to run on the MP-SoCBench simulation infrastructure. The SPLASH-2 [96] and ParMiBench [57] benchmarks have a set of parallel software using POSIX Threads, able to use up to 16 threads. We also joined several Mibench [52] single-threaded benchmarks to create multi-threaded benchmarks that do not share data resources, and we included them in the MPSoCBench software repositories. All applications adapted for the MPSoCBench are detailed in Section 3.2

The MPSoCBench tool fills the gap of a virtual prototyping tool integrating both scalable and configurable hardware and software useful for design and evaluation in the MPSoC modeling and simulation scenario.

## 2.8 Characterizing Simulation and DSE Tools

System simulators have fundamental differences, like the features they contain, detailing level, accuracy, and especially the main purpose of their use. Although this large number of parameters makes difficult to compare them, we present in Table 2.1, in chronological order, several aforementioned simulators and show how they compare with the MPSoCBench, according with requisites like simulation speed, abstraction level, power evaluation and DVFS support. We could not find the simulation speed for all frameworks, so we used a "-" in several of them. Similarly, Table 2.2 shows design space exploration tools and compare them with the MultiExplorer tool.

Table 2.1: Comparison among Simulators and the MPSoCBench.  $HL=High\ level,\ CA=Cycle\ accurate$

| Tool            | Year | Abstr. | Features     | Multicore | Speed      | Power   | DVFS    |

|-----------------|------|--------|--------------|-----------|------------|---------|---------|

|                 |      | Level  |              | Support   |            | Support | Support |

| Bochs [61]      | 1996 | HL     | Emulation    | No        | -          | No      | No      |

| Simple-         | 2002 | CA     | Emulation    | Yes       | ≈150 K     | No      | No      |

| Scalar [11]     |      |        |              |           | instr./sec |         |         |

| Simics [71]     | 2002 | HL     | Simulation   | No        | ≈7.5 K     | No      | No      |

|                 |      |        | (x86-to-x86) |           | instr./sec | No      | No      |

| MP-ARM [15]     | 2004 | HL     | Simulation   | Yes       | 60 K       | Yes     | Yes     |

|                 |      |        | (ARM)        |           | cycles/sec |         |         |

| SESC [78]       | 2004 | HL     | Emulation    | No        | -          | No      | No      |

| GEMS [73]       | 2005 | HL     | Simulation   | Yes       | Simics     | No      | No      |

| QEMU [13]       | 2005 | HL     | Dyn. transl. | No        | -          | No      | No      |

| M5 [17]         | 2006 | HL     | Emulation    | 4-core    | -          | No      | No      |

| Multi2Sim [94]  | 2007 | HL     | Simulation   | No        | -          | No      | No      |

| PTLSim [98]     | 2007 | CA     | Sim. and VM  | No        | -          | No      | No      |

| OVP [56]        | 2008 | HL     | Simulation   | Yes       | -          | Yes     | No      |

| StarSoc [22]    | 2007 | CA     | Simulation   | Yes       | -          | No      | No      |

| MPTLSim [99]    | 2009 | CA     | Simulation   | Yes       | 200-300    | No      | No      |

|                 |      |        |              | 16-core   | cycles/sec |         |         |

| gem5 [16]       | 2011 | HL     | Emulation    | Yes       | -          | No      | No      |

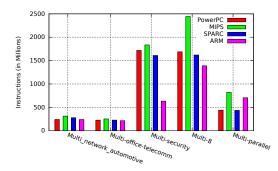

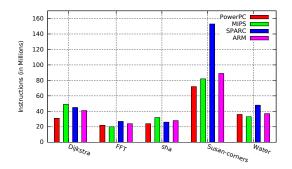

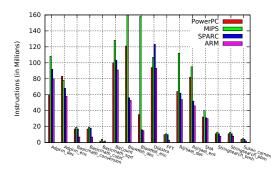

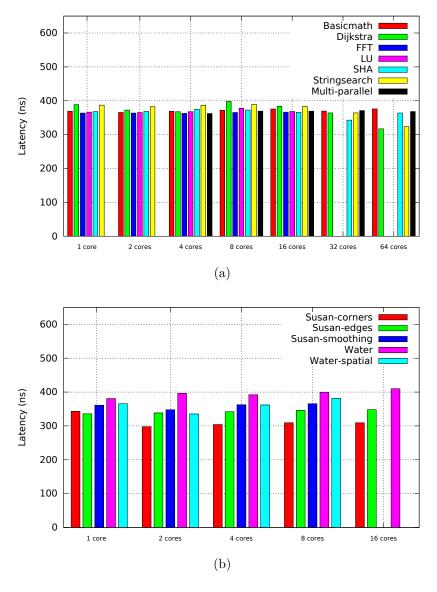

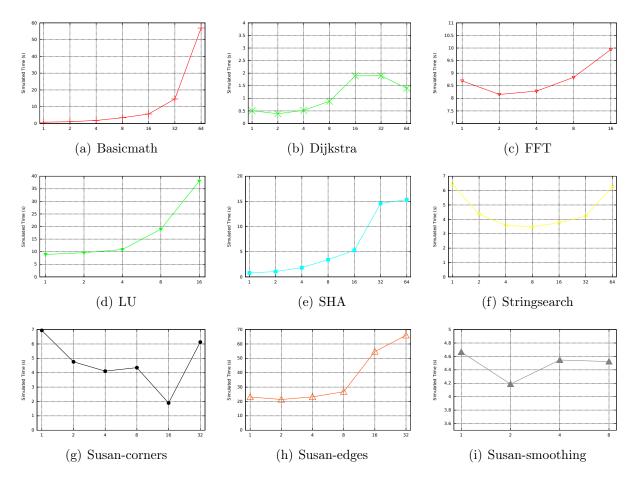

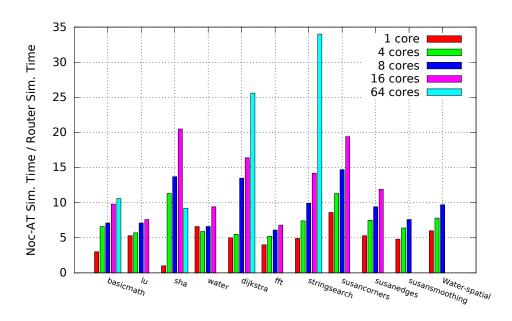

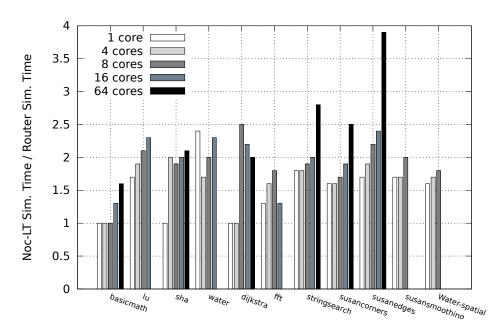

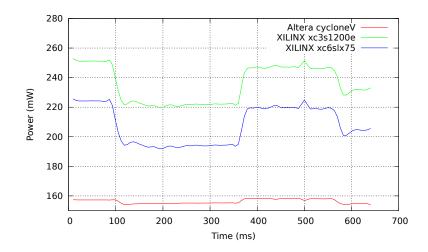

| ESESC [10]      | 2013 | HL     | Emulation    | Yes       | -          | Yes     | No      |