# PBIW: Um Esquema de Codificação Baseado em Padrões de Instrução

Este exemplar corresponde à redação final da Dissertação devidamente corrigida e defendida por Rafael Fernandes Batistella e aprovada pela Banca Examinadora.

Campinas, 28 de Fevereiro de 2008.

Rodolfo Jardin de Azevedo Rodolfo Jardin de Azevedo (Orientador)

Dissertação apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Mestre em Ciência da Computação.

# FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DO IMECC DA UNICAMP

Bibliotecária: Maria Júlia Milani Rodrigues – CRB8a / 2116

Batistella, Rafael Fernandes

B32p PBIW: um esquema de codificação baseado em padrões de instrução / Rafael Fernandes Batistella -- Campinas, [S.P. :s.n.], 2008.

Orientador: Rodolfo Jardim de Azevedo

Dissertação (mestrado) - Universidade Estadual de Campinas, Instituto de Computação.

Memória cache. 2. Compressão de dados (Computação). 3.

Arquitetura de computador. 4. Compiladores (Computadores). I.

Azevedo, Rodolfo Jardim de. II. Universidade Estadual de Campinas.

Instituto de Computação. III. Título.

Título em inglês: PBIW: an encoding technique based on instruction patterns.

Palavras-chave em inglês (Keywords): 1. Cache memory. 2. Data compression (Computer science). 3. Computer architecture. 4. Compiling (Electronic computers)

Área de concentração: Arquitetura de Computadores

Titulação: Mestre em Ciência da Computação

Banca examinadora: Prof. Dr. Rodolfo Jardim de Azevedo (IC-UNICAMP)

Prof. Dr. Paulo César Centoducatte (IC-UNICAMP) Profa. Dra. Edna Natividade da Silva Barros (UFPE) Prof. Dr. Guido Costa de Araújo (IC-UNICAMP)

Data da defesa: 28-02-2008

Programa de Pós-Graduação: Mestrado em Ciência da Computação

### TERMO DE APROVAÇÃO

Dissertação Defendida e Aprovada em 28 de fevereiro de 2008, pela Banca examinadora composta pelos Professores Doutores:

Elue Mondade de Ma Bos

Prof<sup>a</sup>. Dr<sup>a</sup>. Edna Natividade da Silva Barros CIN - UFPE

Prof. Dr. Paulo Cesar Centoducatte

IC - UNICAMP

Prof. Dr. Rodolfo Jardim de Azevedo

IC - UNICAMP

### Instituto de Computação Universidade Estadual de Campinas

# PBIW: Um Esquema de Codificação Baseado em Padrões de Instrução

#### Rafael Fernandes Batistella

Fevereiro de 2008

#### Banca Examinadora:

- Rodolfo Jardim de Azevedo (Orientador)

- Edna Natividade da Silva Barros Centro de Informática - UFPE

- Paulo Cesar Centoducatte

Instituto de Computação UNICAMP

- Guido Costa Souza de Araújo

Instituto de Computação UNICAMP (Suplente)

### Resumo

Trabalhos não muito recentes já mostravam que o aumento de velocidade nas memórias DRAM não acompanha o aumento de velocidade dos processadores. Mesmo assim, pesquisadores na área de arquitetura de computadores continuam buscando novas abordagens para aumentar o desempenho dos processadores. Dentro do objetivo de minimizar essa diferença de velocidade entre memória e processador, este trabalho apresenta um novo esquema de codificação baseado em instruções codificadas e padrões de instruções - PBIW (Pattern Based Instruction Word). Uma instrução codificada não contém redundância de dados e é armazenada em uma I-cache. Os padrões de instrução, de forma diferente, são armazenados em uma nova cache, chamada Pattern cache (P-cache) e são utilizados pelo circuito decodificador na preparação da instrução que será repassada aos estágios de execução. Esta técnica se mostrou uma boa alternativa para estilos arquiteturais conhecidos como arquiteturas VLIW e EPIC. Foi realizado um estudo de caso da técnica PBIW sobre uma arquitetura de alto desempenho chamada de 2D-VLIW. O desempenho da técnica de codificação foi avaliado através de experimentos com programas dos benchmarks MediaBench, SPECint e SPECfp. Os experimentos estáticos avaliaram a eficiência da codificação PBIW no aspecto de redução de código. Nestes experimentos foram alcançadas reduções no tamanho dos programas de até 81% sobre programas codificados com a estratégia de codificação 2D-VLIW e reduções de até 46% quando comparados à programas utilizando o modelo de codificação EPIC. Experimentos dinâmicos mostraram que a codificação PBIW também é capaz que gerar ganhos com relação ao tempo de execução dos programas. Quando comparada à codificação 2D-VLIW, o speedup alcançado foi de até 96% e quando comparada à EPIC, foi de até 69%.

### Abstract

Past works has shown that the increase of DRAM memory speed is not the same of processor speed. Even though, computer architecture researchers keep searching for new approaches to enhance the processor performance. In order to minimize this difference between the processor and memory speed, this work presents a new encoding technique based on encoded instructions and instruction patterns - PBIW (Pattern Based Instruction Word). An encoded instruction contains no redundancy of data and it is stored into an I-cache. The instruction patterns, on the other hand, are stored into a new cache, named Pattern cache (P-cache) and are used by the decoder circuit to build the instruction to be executed in the execution stages. This technique has shown a suitable alternative to well-known architectural styles such as VLIW and EPIC architectures. A case study of this technique was carried out in a high performance architecture called 2D-VLIW. The performance of the encoding technique has been evaluated through trace-driven experiments with MediaBench, SPECint and SPECfp programs. The static experiments have evaluated the PBIW code reduction efficiency. In these experiments, PBIW encoding has achieved up to 81% code reduction over 2D-VLIW encoded programs and up to 46% code reduction over EPIC encoded programs. Dynamic experiments have shown that PBIW encoding can also improve the processor performance. When compared to 2D-VLIW encoding, the speedup was up to 96% while compared to EPIC, the speedup was up to 69%.

## Agradecimentos

Primeiramente gostaria de agradecer a DEUS que, com certeza, me acompanhou durante todo o desenvolvimento deste mestrado e também durante todo a minha vida. Sem ELE não seria possível concluir este grande desafio.

Devo toda minha gratidão à minha namorada Amanda que, desde as primeiras disciplinas que cursei, tem sido paciente com minha "ausência presencial" pois, mesmo estando juntos, boa parte do tempo minha atenção estava voltada ao mestrado. Nos momentos difíceis a Amanda teve um papel decisivo para me ajudar a buscar forças e chegar ao dia de hoje para concluir este mestrado.

Meus pais Antônio e Maria e, meus irmãos Rafaelle e Diego, sempre tiveram, durante toda a minha vida, um papel muito importante nas minhas conquistas. Os conselhos de meus pais sobre meu futuro profissional tiveram grande influência para eu decidir iniciar este mestrado. Durante todo o mestrado eles também me apoiaram bastante e souberam me ajudar quando eu mais precisava. Minha irmã sempre foi um exemplo de perseverança e sucesso para mim. Além disso, mesmo estando longe, ela sempre me apoiou durante todo o mestrado. Meu irmão mais novo sempre foi um motivo de alegria para mim. Em todas as vezes que eu fui visitá-lo em Franca, desde pequeno, ele soube respeitar os momentos em que eu precisava estudar e ajudou a me distrair e pensar em outras coisas nos momentos difíceis.

Gostaria de agradecer ao professor Rodolfo pela sua ajuda e paciência desde à nossa primeira conversa em 2002, onde ele me explicou suas áreas de pesquisa e trabalhos em andamento, até hoje, nas últimas revisões desta dissertação. Também foi ele o responsável por despertar em mim um grande interesse pela área. Agradeço pelas dicas e por cada reunião semanal nas quais pude aprender muito.

No ambiente da UNICAMP eu gostaria muito de agradecer ao meu amigo Ricardo, ex-aluno de doutorado do IC. Desde o primeiro trabalho que fizemos juntos em uma disciplina sobre VHDL ele me ajudou bastante. Ao iniciar os trabalhos de mestrado, comecei estudando parte do trabalho dele. Escrevemos artigos juntos e durante todo meu mestrado, até a escrita da dissertação, o Ricardo colaborou muito comigo e teve bastante paciência ao esclarecer minhas dúvidas.

Gostaria de agradecer também ao Dr. Cincinato, que foi meu terapeuta e me ajudou muito durante todo o período deste mestrado. Infelizmente ele partiu desta vida de forma inesperada sem poder participar comigo deste momento tão importante.

Também agradeço muito ao CPqD, onde trabalho desde 2001, principalmente por me liberar para assistir as aulas das disciplinas do mestrado e à UNICAMP pela infraestrutura, pelos docentes e pelos funcionários que ajudaram a tornar possível a realização deste mestrado.

### Lista de Acrônimos

**2D-VLIW**: Arquitetura de alto desempenho utilizada como referência durante o desenvolvimento deste trabalho de mestrado.

**ARC**: Argonaut RISC Core. Processador RISC configurável e de propósito geral, desenvolvido pela empresa ARC International.

**ARM**: Acorn RISC Machine. Processador RISC de 32 bits, desenvolvido pela empresa ARM Limited.

AVR: Processador RISC de 8 bits, desenvolvido pela empresa Atmel.

CISC: Complex Instruction Set Computer. Um modelo de arquitetura de processadores baseado em um conjunto de instruções complexas, capazes de executar várias tarefas em uma única instrução.

**DRAM**: Dynamic Read Access Memory. Memória de acesso dinâmico.

**DSP**: Digital Signal Processor. Processador especializado, desenvolvido especificamente para processamento de sinais digitais, geralmente em computação de tempo real.

**EPIC**: Explicitly Parallel Instruction Computing. Um modelo de arquitetura que explora paralelismo em nível de instrução através de diversas otimizações de compilação. Neste modelo as instruções são compactas e compostas por operações dependentes e independentes.

GRF: Global Register File. Banco de registradores globais.

**HMDES**: Hardware Machine Description language. Linguagem para descrição de arquiteturas de processadores acoplada ao compilador Trimaran.

**HPL-PD**: HP Labs PlayDoh. Processador parametrizável que implementa o modelo arquitetural EPIC para execução de operações de um programa.

IA64: Intel Architecture. Arquitetura Intel de 64 bits, sendo a primeira implementação

EPIC disponível comercialmente.

**IBM**: International Business Machines. Empresa multinacional, com origem nos Estados Unidos, voltada para a área de informática.

ILR: Instruction Level Reuse. Técnica de Reuso de Instruções.

IM: Instruction Memoization. Técnica de Reuso de Instruções.

IPC: Instruções Por Ciclo. Unidade de medida utilizada para avaliar o desempenho dos processadores.

IR: Instruction Reuse. Técnica que reutiliza resultados de instruções previamente calculados, ao invés de executar novamente as instruções.

LSC: Laboratório de Sistemas de Computação, localizado no Instituto de Computação da UNICAMP.

MIPS: Microprocessor without Interlocked Piped Stages. Designa uma família de microprocessadores que implementam o padrão RISC.

**NOP**: No Operation. Tipo de instrução que não realiza nenhuma operação, utilizada quando é necessário aguardar alguns ciclos antes da próxima instrução.

**PA-RISC**: Precision Architecture - Reduced Instruction Set Computing. Processador RISC desenvolvido pela HP.

**PBIW**: Pattern Based Instruction Word. Esquema de codificação baseado no reuso de padrões de instrução, proposto nesta Dissertação.

**PDP-11**: Série de miniprocessadores CISC comercializados pela Digital Equipment Corporation.

**RB**: Reuse Buffer. Buffer de reuso, utilizado para armazenar resultados que serão reutilizados na técnica de Reuso de Instruções.

RISC: Reduced Instruction Set Computer. Um modelo de arquitetura de processadores baseado em um conjunto de instruções reduzido.

RST: Register Source Table. Estrutura utilizada na técnica de Reuso de Instruções para fazer o mapeamento entre uma instrução consumidora e a última instrução produtora de valores de um determinado registrador.

RT: Registrador Temporário. É o registrador que armazena resultados temporários das computações na arquitetura 2D-VLIW. Existem vários bancos de RTs no interior da ma-

triz de UFs 2D-VLIW.

RUF: Registrador da Unidade Funcional . Registrador presente em cada unidade funcional da arquitetura 2D-VLIW.

**SPARC**: Scalable Processor ARChitecture. Arquitetura de processador desenvolvida pela Sun em 1987 baseada na arquitetura RISC.

SPEC: Standard Performance Evaluation Corporation. Uma empresa que comercializa uma família de programas benchmarks muito usada na avaliação do desempenho de processadores. Além disso, SPEC também define um conjunto de métricas que podem ser usadas na avaliação de desempenho de arquiteturas de processadores.

SPECfp: Conjunto de programas SPEC com valores de ponto flutuante.

SPECint: Conjunto de programas SPEC com valores inteiros.

TMS: Família de processadores DSP desenvolvidos pela Texas Instruments.

**TP**: Tabela de Predicados. Estrutura utilizada para mapeamento entre registradores globais e registradores de predicado, na arquitetura 2D-VLIW.

**UF**: Unidade Funcional. É a unidade que executa o processamento das operações em várias arquiteturas como, por exemplo, 2D-VLIW.

**ULA**: Unidade de Lógica e Aritmética. Elemento de hardware responsável pela execução de operações aritméticas e lógicas.

**VAX**: Processador CISC desenvolvido pela Digital Equipment Corporation (DEC) em meados dos anos 70.

**VLIW**: Very Long Instruction Word. Um estilo de arquitetura de processadores que buscam instruções longas na memória e executam as operações que compõem essas instruções de maneira paralela.

# Sumário

| R  | esum     | .0      |                                    | vii  |

|----|----------|---------|------------------------------------|------|

| A  | Abstract |         |                                    |      |

| A  | grade    | eciment | tos                                | xi   |

| Li | sta d    | le Acrô | onimos                             | xiii |

| 1  | Intr     | odução  |                                    | 1    |

|    | 1.1      | Propos  | sta e Contribuições da Dissertação | . 2  |

|    | 1.2      | Organi  | zação da Dissertação               | 3    |

| 2  | Tra      | balhos  | Relacionados                       | 5    |

|    | 2.1      | Esquer  | mas de Codificação                 | . 5  |

|    | 2.2      | Técnic  | as para Redução de Código          | 11   |

|    |          | 2.2.1   | Instruções Pequenas                | . 12 |

|    |          | 2.2.2   | Compressão de Código               | 15   |

|    |          | 2.2.3   | Agrupamento de Instruções          | 18   |

|    |          | 2.2.4   | Discussão sobre Redução de Código  | 21   |

|    | 2.3      | Reuso   | de Instruções                      | 21   |

|    | 2.4      | Desem   | penho em Caches                    | . 25 |

|    | 2.5      | Arquit  | etura 2D-VLIW                      | . 29 |

|    |          | 2.5.1   | Instruções 2D-VLIW                 | 30   |

|    |          | 2.5.2   | Modelo de Execução                 | 31   |

|    |          | 2.5.3   | Estruturas de Armazenamento        | 32   |

|    |                                  | 2.5.4                       | Considerações sobre a Arquitetura 2D-VLIW | 33  |

|----|----------------------------------|-----------------------------|-------------------------------------------|-----|

|    | 2.6                              | Consid                      | derações Finais                           | 33  |

| 3  | $\mathbf{E}\mathbf{s}\mathbf{q}$ | Esquema de Codificação PBIW |                                           |     |

|    | 3.1                              | Visão                       | Geral                                     | 39  |

|    | 3.2                              | Estrut                      | ura da Instrução                          | 42  |

|    | 3.3                              | Patter                      | n Cache                                   | 45  |

|    | 3.4                              | Codifi                      | cação da Palavra                          | 49  |

|    | 3.5                              | Decod                       | ificação da Palavra                       | 61  |

|    | 3.6                              | Estude                      | o de Caso: Arquitetura 2D-VLIW            | 64  |

|    | 3.7                              | Consid                      | derações Finais                           | 69  |

| 4  | Exp                              | Experimentos e Resultados   |                                           | 71  |

|    | 4.1                              | Exper                       | imentos e Medidas de Desempenho           | 72  |

|    | 4.2                              | Infraes                     | strutura para Execução dos Experimentos   | 74  |

|    |                                  | 4.2.1                       | Trimaran                                  | 74  |

|    |                                  | 4.2.2                       | Escalonador 2D-VLIW                       | 77  |

|    |                                  | 4.2.3                       | Gerador Estático PBIW                     | 78  |

|    |                                  | 4.2.4                       | Gerador Estático VLIW / EPIC / IA64       | 81  |

|    |                                  | 4.2.5                       | Analisador Estático PBIW                  | 82  |

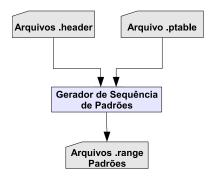

|    |                                  | 4.2.6                       | Gerador de Seqüência de Padrões           | 84  |

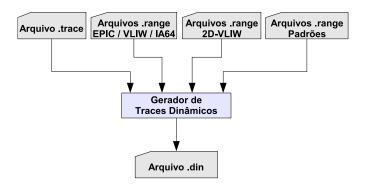

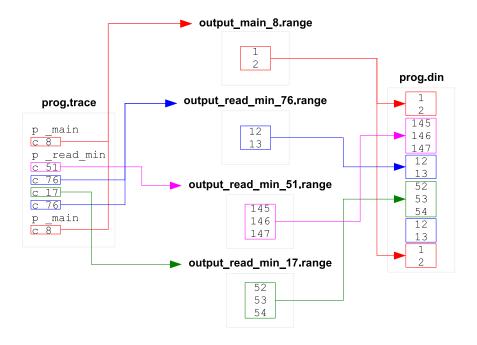

|    |                                  | 4.2.7                       | Gerador de Traces Dinâmicos               | 85  |

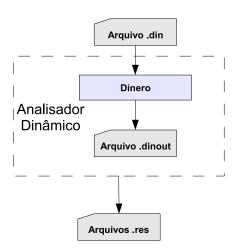

|    |                                  | 4.2.8                       | Analisador Dinâmico                       | 87  |

|    | 4.3                              | Avalia                      | ção Estática                              | 88  |

|    | 4.4                              | Avaliação Dinâmica          |                                           | 96  |

|    | 4.5                              | Consid                      | derações Finais                           | 109 |

| 5  | Con                              | clusõe                      | $\mathbf{s}$                              | 111 |

|    | 5.1                              | Contri                      | buições desta Dissertação                 | 112 |

|    | 5.2                              | Propo                       | stas de Trabalhos Futuros                 | 112 |

| Bi | bliog                            | grafia                      |                                           | 117 |

# Lista de Tabelas

| 3.1  | Quantidade de instruções codificadas (128 bits) e padrões por programa $$ 66            |

|------|-----------------------------------------------------------------------------------------|

| 3.2  | Comparação entre PBIW de 64 e 128 bits. Valores expressos em bits $\dots$ 68            |

| 4.1  | Programas utilizados nos experimentos                                                   |

| 4.2  | Número de instruções (× mil) sobre programas $SPEC$ e $MediaBench$ 90                   |

| 4.3  | Número de instruções (× mil) e Fator de Redução (%) sobre programas                     |

|      | SPECe $MediaBench$ utilizando instruções PBIW de 64 bits 92 $$                          |

| 4.4  | Número de instruções (× mil) e Fator de Redução (%) sobre programas                     |

|      | $SPEC$ e $MediaBench$ utilizando instruções PBIW de 128 bits $\ \ldots \ \ldots \ \ 94$ |

| 4.5  | Fatores de Redução (%) de PBIW com 64 bits sobre EPIC baseado em                        |

|      | 2D-VLIW variando o número de bits de template de EPIC 95 $$                             |

| 4.6  | Fatores de Redução (%) de PBIW com 128 bits sobre EPIC baseado em                       |

|      | 2D-VLIW variando o número de bits de template de EPIC 96 $$                             |

| 4.7  | Misses (× mil) por tamanho de $cache$ (KB) no programa 168<br>wupwise $$ 100            |

| 4.8  | Misses (× mil) por tamanho de $cache$ (KB) no programa 175vpr $$ 101                    |

| 4.9  | Misses (× mil) por tamanho de $cache$ (KB) no programa 179<br>art   101                 |

| 4.10 | Misses (× mil) por tamanho de $cache$ (KB) no programa 183<br>equake $$ 101             |

| 4.11 | Misses (× mil) por tamanho de $cache$ (KB) no programa 197<br>parser 102                |

| 4.12 | Misses (× mil) por tamanho de $cache$ (KB) no programa 256bzip2 102                     |

| 4.13 | Misses (× mil) por tamanho de $cache$ (KB) no programa g721decode 102                   |

| 4.14 | Misses (× mil) por tamanho de $cache$ (KB) no programa g721encode 103                   |

| 4.15 | Misses (× mil) por tamanho de $cache$ (KB) no programa gsmdecode 103                    |

| 4.16 | Misses (× mil) por tamanho de $cache$ (KB) no programa pegwit 103                       |

|      |                                                                                         |

| 4.17 | Número de fetches ou ciclos de execução (× mil) considerados no cálculo     |

|------|-----------------------------------------------------------------------------|

|      | do Tempo de Execução                                                        |

| 4.18 | Tempo de Execução (milhões de ciclos) e $speedup$ (%) considerando $caches$ |

|      | (KB) menores do que a $cache$ PBIW e palavras de 64 bits $$                 |

| 4.19 | Tempo de Execução (milhões de ciclos) e $speedup$ (%) considerando $caches$ |

|      | (KB) maiores do que a $cache$ PBIW e palavras de 64 bits                    |

| 4.20 | Tempo de Execução (milhões de ciclos) e $speedup$ (%) considerando $caches$ |

|      | (KB) menores do que a $cache$ PBIW e palavras de 128 bits                   |

| 4.21 | Tempo de Execução (milhões de ciclos) e $speedup$ (%) considerando $caches$ |

|      | (KB) maiores do que a $cache$ PBIW e palavras de 128 bits 108               |

# Lista de Figuras

| 2.1  | Instrução VLIW composta por 5 operações                                  | 8  |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Instrução EPIC composta por 5 operações                                  | 9  |

| 2.3  | Formato básico de uma instrução TMS                                      | 9  |

| 2.4  | Formato de uma instrução IA64                                            | 10 |

| 2.5  | Pipelines dos processadores ARM, Thumb e Thumb-2                         | 13 |

| 2.6  | Visão geral do processador MIPS16                                        | 14 |

| 2.7  | Visão geral da Descompressão por Instrução                               | 16 |

| 2.8  | Visão geral da Descompressão por Fatoração de Instrução                  | 17 |

| 2.9  | Strand composto por três instruções                                      | 19 |

| 2.10 | Entradas no RB para os esquemas (a) $S_v$ , (b), $S_n$ e (c) $S_{n+d}$   | 23 |

| 2.11 | Datapathda arquitetura 2D-VLIW                                           | 31 |

| 3.1  | Instrução EPIC derivada de 2D-VLIW                                       | 38 |

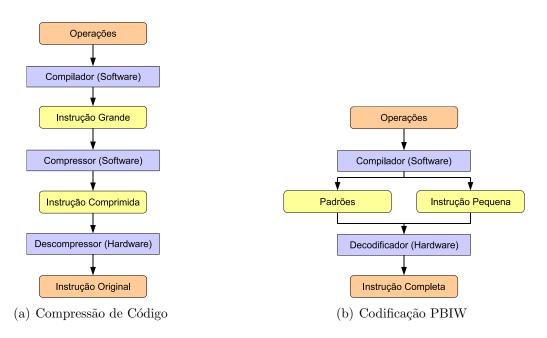

| 3.2  | Fluxo convencional de compressão (a) e Fluxo da codificação PBIW (b)     | 40 |

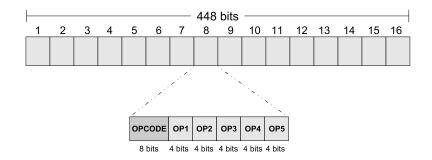

| 3.3  | Exemplo de uma instrução PBIW com 64 bits                                | 43 |

| 3.4  | Exemplo de uma padrão com 448 bits                                       | 44 |

| 3.5  | Ilustração dos ponteiros utilizando uma instrução codificada e um padrão |    |

|      | hipotéticos                                                              | 44 |

| 3.6  | Instruções compartilhando o mesmo padrão                                 | 45 |

| 3.7  | Intersecção de ocorrência                                                | 47 |

| 3.8  | Fluxo de execução da técnica de codificação                              | 49 |

| 3.9  | Fragmento de código                                                      | 53 |

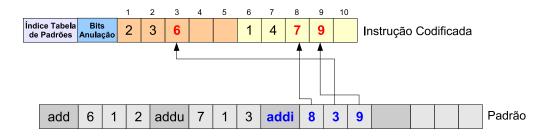

| 3.10 | Codificação da operação add r1, r2, r3                                   | 53 |

| 3.11 | Codificação da operação addu r4, r2, r6                                  | 54 |

| 3.12 | Codificação da operação addi r7, r6, 9                                    | 54 |

|------|---------------------------------------------------------------------------|----|

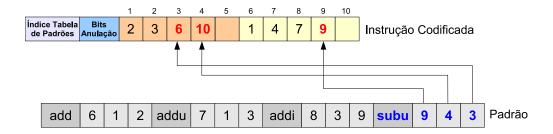

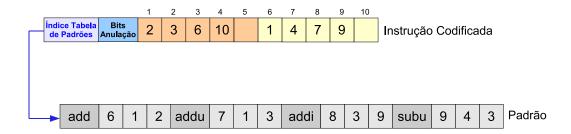

| 3.13 | Codificação da operação subu r9, r10, r6                                  | 55 |

| 3.14 | Atualização do endereço do padrão na instrução codificada                 | 55 |

| 3.15 | Ilustração de um esquema de anulação                                      | 56 |

| 3.16 | Disposição de UFs em uma matriz 4 × 4                                     | 57 |

| 3.17 | Padrões que podem ser unidos (a) e padrões que não podem ser unidos (b)   |    |

|      | considerando utilização de colunas                                        | 58 |

| 3.18 | Junção por colunas e a representação da utilização das linhas             | 59 |

| 3.19 | Bits de anulação decorrentes da junção ocorrida na Figura 3.18            | 59 |

| 3.20 | Junção por colunas seguida de junção por linhas                           | 61 |

| 3.21 | Fluxo de decodificação de uma instrução PBIW                              | 63 |

| 3.22 | Visão geral do circuito de decodificação PBIW                             | 63 |

| 3.23 | Instrução PBIW com 128 bits definida para a arquitetura 2D-VLIW           | 65 |

| 3.24 | Padrão de uma instrução PBIW de 128 bits definido para a arquitetura      |    |

|      | 2D-VLIW                                                                   | 65 |

| 3.25 | Utilização dos campos da palavra PBIW de 128 bits por programa codificado | 67 |

| 3.26 | Instrução PBIW com 64 bits definida para a arquitetura 2D-VLIW $$         | 68 |

| 3.27 | Padrão de uma instrução PBIW de 64 bits definido para a arquitetura       |    |

|      | 2D-VLIW                                                                   | 69 |

| 4.1  | Fluxo das ferramentas utilizadas nos experimentos                         | 75 |

| 4.2  | Fluxo de execução do Trimaran                                             | 76 |

| 4.3  | Trecho de código um arquivo .<br>HS_el                                    | 76 |

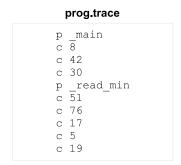

| 4.4  | Trecho de código de um arquivo . $trace$                                  | 77 |

| 4.5  | Fluxo de execução do Escalonador 2D-VLIW                                  | 77 |

| 4.6  | Trecho de um arquivo $output$                                             | 78 |

| 4.7  | Fluxo de execução do Gerador Estático PBIW                                | 79 |

| 4.8  | Trecho de um arquivo .info.out                                            | 80 |

| 4.9  | Trecho de um arquivo .header                                              | 80 |

| 4.10 | Trecho de um arquivo .range                                               | 81 |

| 4.11 | Fluxo de execução do Gerador Estático VLIW / EPIC / IA64                  | 82 |

| 4.12 | Fluxo de execução do Analisador Estático PBIW                                   | 83 |

|------|---------------------------------------------------------------------------------|----|

| 4.13 | Arquivo .<br>info do programa pegwit - Informações sobre a instrução codificada | 83 |

| 4.14 | Arquivo .<br>info do programa pegwit - Resumo da codificação do programa $$ .   | 84 |

| 4.15 | Trecho do arquivo .ptable referente ao programa pegwit                          | 84 |

| 4.16 | Fluxo de execução do Gerador de Seqüência de Padrões                            | 85 |

| 4.17 | Fluxo de execução do Gerador de Traces Dinâmicos                                | 86 |

| 4.18 | Formação do arquivo .din a partir dos arquivos .trace e .range                  | 86 |

| 4.19 | Fluxo de execução do Analisador Dinâmico                                        | 87 |

| 4.20 | Exemplo de conteúdo de um arquivo .res                                          | 88 |

## Capítulo 1

## Introdução

Trabalhos não muito recentes já mostravam que a taxa de melhora na velocidade dos microprocessadores supera a taxa de melhora na velocidade das memórias DRAM. A velocidade dos processadores aumentava à aproximadamente 80% ao ano, enquanto que a velocidade das DRAMs aumentava apenas 7% ao ano. Entretanto, a comunidade de arquitetura de computadores ainda está amplamente focada em aumentar o desempenho dos processadores [23]. Como resultado, a diferença entre a velocidade do processador e da memória tem crescido exponencialmente levando a um fenômeno conhecido como Memory Wall [23, 43, 47].

Recentemente, várias empresas anunciaram que a freqüência do processador não irá mais aumentar como vinha ocorrendo. Da mesma forma, a velocidade dos processadores também já não está mais aumentando como antes. Mesmo assim, o problema de *Memory Wall* será ainda uma preocupação para a comunidade de arquitetura de computadores, uma vez que a quantidade de processadores utilizados em um sistema e a necessidade de leitura da memória têm aumentado.

Um grande número de técnicas foram desenvolvidas na tentativa de minimizar o problema de *Memory Wall*. Muitas delas focaram em novos esquemas de codificação enquanto outras utilizavam técnicas para redução do tamanho dos programas, como as técnicas de compressão. Todas possuem um único objetivo: reduzir a quantidade de dados armazenados na memória principal. Especificamente, estas técnicas têm sido aplicadas em arquiteturas que buscam grandes instruções da memória e em arquiteturas voltadas para

domínios específicos de aplicações, como os sistemas embarcados [24, 26, 31, 34].

### 1.1 Proposta e Contribuições da Dissertação

Devido ao grande problema imposto pela diferença expressiva de velocidade entre processadores e memórias, esta dissertação de mestrado propõe uma nova abordagem para tentar minimizar o efeito da latência na busca de instruções e seu impacto no desempenho dos programas, utilizando uma estratégia diferente das técnicas de compressão de código e codificação já apresentadas.

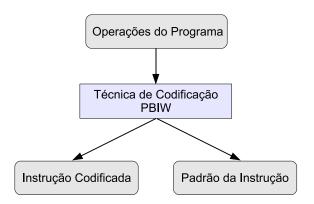

Especificamente, este trabalho apresenta a técnica de codificação PBIW (Pattern Based Instruction Word), voltada para arquiteturas que buscam instruções grandes da memória como processadores EPIC, arquiteturas reconfiguráveis com várias unidades funcionais e arquiteturas de alto desempenho baseada em matriz de unidades funcionais. A técnica é composta por um algoritmo baseado em fatoração de operandos [2, 9, 11] e por uma memória cache chamada de Pattern Cache (P-cache).

O novo modelo de codificação proposto nesta dissertação é baseado em técnicas para redução de código, esquemas de codificação e reuso de instruções. Parte solução da proposta consiste em utilizar uma *cache* de padrões cuja estrutura foi definida a partir de estudos sobre desempenho em *caches*. Para validar o novo esquema de codificação, foi realizado um estudo de caso através de sua implementação na arquitetura de alto desempenho 2D-VLIW.

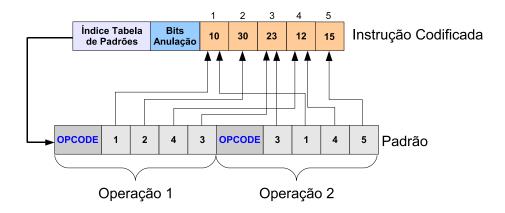

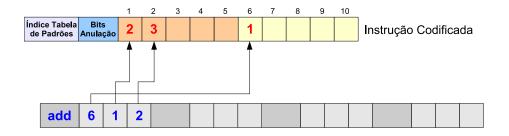

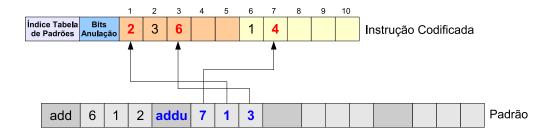

Depois das atividades de escalonamento das instruções e alocação dos registradores realizadas pelo back-end do compilador, o algoritmo de codificação PBIW extrai operandos redundantes entre as operações, criando uma instrução codificada sem redundância de operandos. Esta instrução é armazenada em uma I-cache. O algoritmo mantém o registro da posição original dos operandos criando um padrão de instrução que é armazenado na P-cache. Este padrão é uma estrutura de dados que contém informações necessárias para compor a instrução utilizada nos estágios de execução.

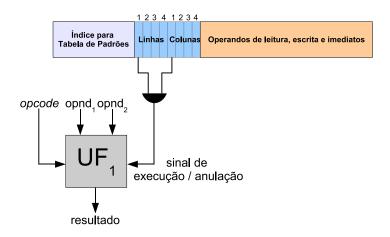

Uma instrução PBIW é composta por um valor utilizado na busca do respectivo padrão na P-cache, um conjunto de bits de anulação que indicam quais UFs da matriz de execução

devem ser executadas ou anuladas e um conjunto de campos de dados que armazenam números dos registradores e valores imediatos.

O padrão armazena os *opcodes* das operações e um conjunto de valores que indicam posições dos campos de dados da instrução PBIW. Ou seja, o padrão aponta para os campos de dados da instrução PBIW.

Ao adotar a técnica PBIW, a arquitetura passa a buscar instruções pequenas na I-cache e, no estágio de decodificação, busca um padrão na P-cache. É importante observar que as latências de busca da I-cache e da P-cache não são as mesmas em todas as buscas. Misses na I-cache não implicam em misses na P-cache uma vez que os padrões são reutilizados por instruções diferentes, pois, existe uma sobrejeção entre o conjunto de instruções codificadas e o conjunto de padrões. Depois do estágio de decodificação, uma instrução pode executar suas operações nos elementos de processamento (ou unidades funcionais) do processador.

Os impactos desta nova técnica de codificação foram avaliados através de simulações da I-cache e da P-cache com programas dos benchmarks MediaBench, SPECint e SPECfp. Os resultados mostram que, adotando esta estratégia de codificação, o desempenho (tempo de execução) é até 96% melhor do que a estratégia de codificação da arquitetura 2D-VLIW e até 69% melhor do que a codificação EPIC.

Outros experimentos realizados também mostram que, utilizando a técnica PBIW, o tamanho total do programa codificado, incluindo os dados da P-cache é até 81% menor do que o tamanho do programa codificado na estratégia 2D-VLIW e até 46% menor do que o código gerado através do esquema de codificação EPIC.

### 1.2 Organização da Dissertação

O texto desta dissertação está organizado em cinco capítulos que fornecem toda a base conceitual e empírica para o entendimento completo da técnica PBIW e comprovação de seus resultados. Os parágrafos a seguir descrevem o conteúdo de cada um destes capítulos.

O Capítulo 2 apresenta os trabalhos que formaram o alicerce teórico para o desenvolvimento do novo modelo de codificação PBIW. Neste capítulo são apresentados esquemas

de codificação, técnicas de redução de código, reuso de instruções, desempenho em *caches* e uma breve descrição da arquitetura 2D-VLIW.

O esquema de codificação PBIW é descrito no Capítulo 3. Este capítulo inclui a estrutura da palavra PBIW assim como a estrutura de um padrão. Também são apresentados neste capítulo o algoritmo de codificação e o circuito decodificador utilizado nesta técnica.

No Capítulo 4 são apresentados experimentos envolvendo o esquema de codificação PBIW. Esse capítulo detalha a infraestrutura utilizada, os experimentos realizados e, principalmente, justifica e discute os resultados obtidos para os experimentos estáticos e dinâmicos.

O Capítulo 5 fecha a dissertação apresentando as conclusões sobre o que foi realizado durante o desenvolvimento deste trabalho e relata as contribuições que foram alcançadas. Ao final, sugere-se a extensão desta proposta através de vários projetos que podem ser realizados como trabalhos futuros.

### Capítulo 2

### Trabalhos Relacionados

Algumas das alternativas para minimizar o gargalo existente na comunicação entre memória e processador estão diretamente associadas às técnicas utilizadas para reduzir o tamanho dos programas. Diminuindo a quantidade e/ou o tamanho das instruções, conseqüentemente o número de buscas e a largura de banda da memória serão reduzidos. Além disso, com instruções menores e em menor quantidade, o processador poderá atingir um desempenho melhor.

Na Seção 2.1 são apresentados os principais e mais utilizados Esquemas de Codificação. Na Seção 2.2 são apresentadas três abordagens distintas para reduzir o tamanho dos programas: Codificação com Instruções Pequenas, Compressão de Código e Agrupamento de Instruções. Dentro de cada uma destas abordagens são explicadas diferentes técnicas e aplicações. Os trabalhos apresentados Seção 2.3 mostram como diminuir o tempo de execução através do Reuso de Instruções. Na Seção 2.4 são apresentadas algumas técnicas para atingir alto desempenho em *caches* e a arquitetura 2D-VLIW é apresentada na Seção 2.5.

### 2.1 Esquemas de Codificação

O objetivo de representar os programas com instruções cada vez menores e em menor quantidade pode ser vislumbrado durante a definição do esquema de codificação de uma nova arquitetura. O conjunto de instruções determina o nível de complexidade e o custo do hardware a ser implementado.

O desafio encontrado pelos projetistas ao definir um esquema de codificação é desenvolver instruções pequenas o suficiente para simplificar o estágio de execução, grandes o suficiente para minimizar a quantidade de instruções buscadas na memória e simples o suficiente para não impactar muito o estágio de decodificação. Nesta seção são apresentados algumas das estratégias de codificação de instruções mais conhecidas e utilizadas.

O esquema de codificação CISC (Complex Instruction Set Computer) [1] teve sua primeira aplicação na arquitetura System/360, apresentada pela IBM em 7 de Abril de 1964 como resultado de pesquisas iniciadas nos anos 50. Este computador foi o primeiro a utilizar micro-programação e, só mais tarde, ele seria conhecido como uma arquitetura CISC. O sucesso do System/360 resultou no domínio das arquiteturas CISC sobre o desenvolvimento de computadores e microprocessadores por duas décadas.

Em um processador CISC, cada instrução pode executar várias operações de baixo nível como leitura da memória, operação aritmética e armazenamento em memória, todas em uma única instrução. A vantagem da arquitetura CISC é ter muitas das operações armazenadas no próprio processador, o que facilita o trabalho dos programadores de linguagem de máquina e gera código executável menor.

Do ponto de vista de desempenho, a codificação CISC têm algumas desvantagens em relação ao RISC, entre elas a impossibilidade de se alterar alguma instrução composta para melhorar o desempenho. Um outro fator é que as arquiteturas CISC possuem instruções mais compactas já por construção, de modo que a compressão de código nestas arquiteturas não produz resultados tão expressivos quanto em arquiteturas RISC [18]. As arquiteturas System/360, VAX, PDP-11, família Motorola 68000 e Intel x86 são exemplos de utilização do esquema de codificação CISC.

O primeiro computador com instruções RISC (Reduced Instruction Set Computer) [28, 29] surgiu em 1979, como resultado de uma pesquisa iniciada em Outubro de 1975 pelo Centro de Pesquisa Watson da IBM. Esta pesquisa teve como motivação o fato de que em meados dos anos 70, muitas ferramentas de medição de desempenho demonstraram que a execução de boa parte dos programas em sistemas CISC eram dominadas por um conjunto pequeno de instruções simples e as instruções complexas eram pouco utilizadas.

Este modelo de codificação é uma filosofia que recomenda um conjunto de instruções reduzidas em termos de complexidade e de tamanho com o objetivo de permitir uma implementação mais simples, maior paralelismo no nível de instrução e compiladores mais eficientes. As características da arquitetura RISC como desempenho, facilidade de decodificação das instruções, simplicidade do código e melhor capacidade de geração de código tornam esta codificação mais adequada ao uso em sistemas dedicados.

Por possuírem um pequeno conjunto de instruções de tamanho fixo e, com isso, uma grande quantidade de bits não utilizados, os programas gerados para esta arquitetura são extremamente redundantes. Atualmente, as famílias mais comuns de processadores RISC incluem DEC Alpha, ARC, ARM, AVR, MIPS, PA-RISC, Power Architecture (incluindo PowerPC), SPARC, HP Precision, PMC-Sierra's 64-bit e ARCtangent-A4.

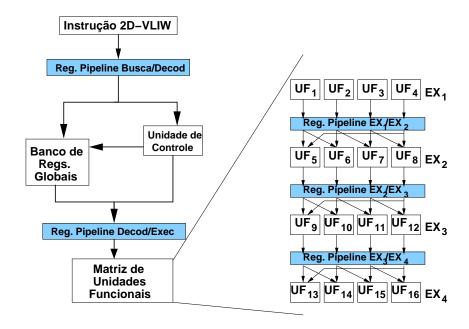

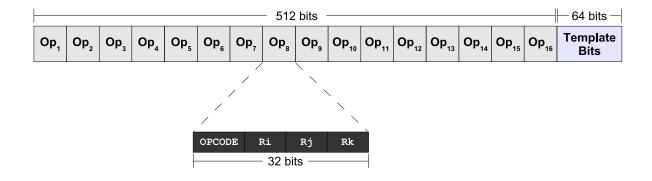

O conceito de arquiteturas **VLIW** (*Very Long Instruction Word*) [10, 20] foi apresentado por Josh Fisher e seu grupo de pesquisa da Universidade Yale, no inicio de 1980. A pesquisa de Fisher era em torno de um compilador que pudesse gerar micro-código horizontal a partir de programas escritos em uma determinada linguagem de programação. Os primeiros computadores VLIW reais foram lançados no começo dos anos 80 pela Multiflow Computer, Inc.

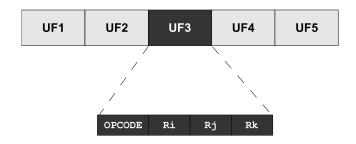

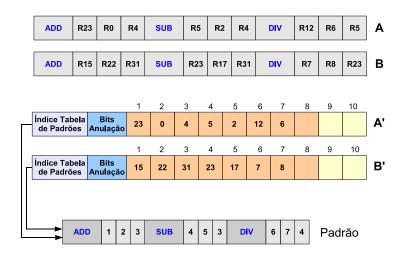

Neste esquema de codificação, as instruções são compostas por um número fixo N de operações independentes (paralelas). O total de bits utilizado por uma instrução VLIW é  $N \times$  bits por operação. Quando existem menos do que N operações para compor uma instrução, são inseridas operações do tipo NOP ( $No\ OPeration$ ) para completar a instrução. O código VLIW fornece um plano de execução (criado estaticamente em tempo de compilação) explícito ao processador. Este plano é montado utilizando conhecimento total do processador. A Figura 2.1 mostra um esquema hipotético de uma instrução VLIW composta por cinco operações.

O código gerado indica quando cada operação deve ser executada, quais unidades funcionais serão utilizadas e quais registradores serão acessados. O compilador comunica o plano de execução através de um conjunto de instruções que representam o paralelismo explicitamente ao hardware. Este plano permite utilizar um hardware relativamente simples

Figura 2.1: Instrução VLIW composta por 5 operações

que pode alcançar altos níveis de paralelismo em nível de instrução. Apenas duas empresas produziram comercialmente máquinas puramente VLIW: a Multiflow Computer, Inc. e a Cydrome, Inc. Pelo fato de não atingirem sucesso de mercado, há pouquíssimos dados sobre a eficiência real dessas máquinas, que ficaram restritas a poucas unidades entregues.

As instruções **EPIC** (Explicitly Parallel Instruction Computing) [44, 45] surgiram nos anos 90 com o objetivo de aumentar a habilidade dos microprocessadores em executar instruções em paralelo, utilizando o compilador, ao invés de hardware complexo, para identificar as oportunidades de execução paralela. Este esquema de codificação pode ser considerado como uma evolução do modelo VLIW.

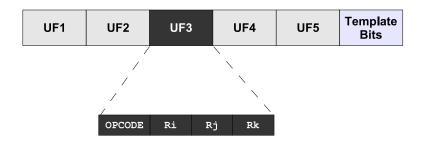

Assim como as instruções VLIW, uma instrução EPIC é composta por um número fixo N de operações. Neste caso as operações podem ser dependentes ou independentes. O total de bits utilizado por uma instrução EPIC é  $(N \times \text{bits por operação}) + \text{bits que indicam dependência}$ . A principal modificação em relação ao modelo VLIW foi criar um conjunto de bits  $(Template\ Bits)$  para indicar possíveis dependências entre as operações que compõe a instrução. A Figura 2.2 mostra um esquema hipotético de uma instrução EPIC composta por cinco operações.

O esquema de codificação **TMS** é uma outra abordagem que também utiliza instruções compostas por várias operações. Esta codificação é utilizada pela arquitetura TMS320C6x [14] que é uma nova geração do TMS32010 (o primeiro DSP da família TMS320), apresentado pela Texas Instruments em 1982. Atualmente, a família TMS320 consiste em várias gerações: C1x, C2x, C2xx, C5x, e C54x que são DSPs para operações

Figura 2.2: Instrução EPIC composta por 5 operações

de inteiros; C3x, C4x e C6x que são DSPs de ponto flutuante, e os multiprocessadores DSP C8x.

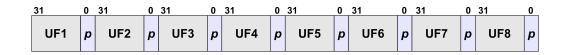

As instruções TMS são compostas por oito operações sendo que o grupo de execução de uma instrução é especificado por um bit denominado p-bit de cada operação. As instruções possuem 256 bits (8 palavras  $\times$  32 bits). Os p-bits controlam a execução paralela das operações e são lidos da esquerda para a direita (menor para maior endereço). Se o p-bit da instrução i for 0, então a instrução i+1 será executada um ciclo após a instrução i.

Todas as operações que executam em paralelo constituem um pacote de execução. Um pacote de execução pode conter até 8 operações. Cada operação em um pacote de execução deve utilizar uma unidade funcional diferente. A Figura 2.3 mostra o formato básico de uma instrução TMS320C6x. Um pacote de execução não pode cruzar a fronteira das 8 operações. Por isso, o último p-bit em uma instrução sempre possui o valor 0 e, cada nova instrução buscada na memória, inicia um novo pacote de execução.

Figura 2.3: Formato básico de uma instrução TMS

Existem 3 tipos de padrões de p-bits para as instruções buscadas da memória. Estes três padrões resultam na seguinte seqüência de execução para as oito instruções: totalmente serial (todos os p-bits setados para 0), totalmente paralelo (todos os p-bits setados

para 1) ou parcialmente serial (alguns dos p-bits setados para 0 e outros para 1). Caso ocorra um branch para o meio de uma instrução, todas as operações anteriores à operação alvo do branch são ignoradas.

O modelo de codificação IA64 [7] foi a primeira implementação EPIC disponível comercialmente. Trata-se de uma implementação da Intel que segue a filosofia EPIC, mas com algumas diferenças no que diz respeito ao modelo mais teórico EPIC, descrito anteriormente nesta seção.

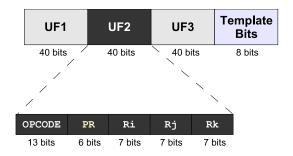

As instruções IA64 possuem praticamente o mesmo algoritmo de escalonamento das instruções EPIC mas com apenas 120 bits que armazenam 3 operações (cada operação com 40 bits). Além destas 3 operações, a instrução possui um conjunto de 8 bits para evitar que operações dependentes sejam executadas ao mesmo tempo. Então, uma instrução IA64 possui 128 (120 + 8) bits. O compilador examina as dependências de todo o código e empacota as instruções em pacotes de 128 bits que podem ser executados em paralelo com segurança. A Figura 2.4 mostra o formato de uma instrução IA-64.

Figura 2.4: Formato de uma instrução IA64

Cada pacote de 128 bits possui 3 instruções e um conjunto de bits que especifica à CPU qual instrução depende da outra. Como estes bits especificam a dependência entre grupos de instruções, as unidades funcionais saberão como elas poderão processar estas instruções. Cada uma das 3 operações que compõe a instrução IA64 possui 40 bits divididos em 3 operandos de 7 bits, um registrador de predicado de 6 bits e *opcode* de 13 bits. As unidades funcionais assumem que o compilador tenha construído código seguro para ser executado em paralelo e que ele tenha utilizado os *Template Bits* (Figura 2.4)

para alertar a CPU de todas as dependências. Como a CPU não precisa examinar ou otimizar o código, tudo que é preciso fazer é colocar estes pacotes o quanto antes nas unidades funcionais.

Os esquemas de codificação RISC e CISC são os mais antigos e formam a base para todos os outros modelos utilizados atualmente. VLIW e EPIC são nomes mais conceituais do que práticos, são filosofias de codificação, modelos de execução de arquiteturas e podem ser considerados duas formas diferentes de se empacotar um conjunto de instruções RISC ou CISC. As codificações TMS320C6x e IA64 são exemplos de implementações EPIC criadas para fins diferentes e por empresas distintas. Não se pode afirmar diretamente qual técnica é a melhor. Durante o desenvolvimento de uma nova arquitetura devese avaliar as restrições do projeto como, por exemplo, quantidade máxima de memória disponível, consumo de energia desejado, desempenho mínimo exigido e área máxima do circuito para que se possa escolher o esquema de codificação mais adequado.

Mesmo com a melhor codificação para a arquitetura ainda pode ser possível melhorar o desempenho do processador através da utilização de alguma técnica complementar de redução de código. Na próxima seção são apresentadas algumas abordagens que podem ser utilizadas com o objetivo de reduzir o tamanho do código e conseqüentemente diminuir a quantidade de acessos à memória.

### 2.2 Técnicas para Redução de Código

O tamanho do código executável de um programa pode determinar a viabilidade de sua implementação em sistemas embarcados e também o desempenho em qualquer outro tipo de sistema. Quanto menor o código, menor o efeito do gargalo existente na comunicação entre memória e processador, especialmente em arquiteturas como VLIW e EPIC (Seção 2.1), que buscam instruções longas em memória. Mesmo utilizando codificações eficientes, estas podem demandar muitos acessos à memória prejudicando diretamente o desempenho do programa executado.

Nesta seção são apresentadas três abordagens diferentes que compartilham o mesmo objetivo: reduzir o tamanho do código de um programa. A primeira delas adota a uti-

lização de instruções pequenas, representando cada instrução com menos bits e, depois, durante a decodificação realiza o mapeamento destas instruções para as instruções maiores que serão interpretadas pelo processador. A segunda utiliza técnicas de compressão, que comprimem o código em memória e depois reconstroem o código original no interior do processador. A última técnica apresentada mostra como agrupar instruções. Nesta técnica as instruções dependentes são empacotadas em macro-instruções que são executadas por ULAs adaptadas.

### 2.2.1 Instruções Pequenas

Uma das primeiras abordagens utilizadas para diminuir o tamanho do código de um programa foi substituir o uso de instruções convencionais de 32 bits por instruções menores (16 bits). Esta idéia foi adotada no desenvolvimento de processadores como Thumb [22] e MIPS16 [17], definidos como subconjuntos das arquiteturas ARM [21] e MIPS respectivamente. As composições destes subconjuntos foram determinadas após análise de um grande conjunto de aplicações, onde foram escolhidas as instruções utilizadas com grande freqüência, que não utilizam 32 bits ou que são importantes para o compilador durante a geração do código intermediário.

O conjunto de instruções **Thumb** foi projetado a partir do conjunto padrão de instruções ARM de 32 bits que foi recodificado em instruções de 16 bits. Isto traz uma alta densidade de código pois as instruções Thumb possuem metade dos bits das instruções ARM. Antes da execução, estas instruções de 16 bits são mapeadas para instruções de 32 bits, pertencentes ao conjunto de instruções ARM. Desta forma, um programa Thumb roda normalmente em um processador ARM convencional.

Em um programa escrito para Thumb apenas os branches podem ser condicionais e muitos dos opcodes não possuem acesso a todos os registradores da CPU. O primeiro processador com um decodificador de instruções Thumb foi o ARM7TDMI. Este processador é capaz de executar tanto instruções de 16 bits quanto instruções de 32 bits e a distinção é feita através de um bit de estado do processador que pode ser alterado com a instrução BX. Depois deste processador, todos os ARM9 e famílias de processadores mais novas, incluindo o XScale, utilizaram um decodificador de instruções Thumb. O fator

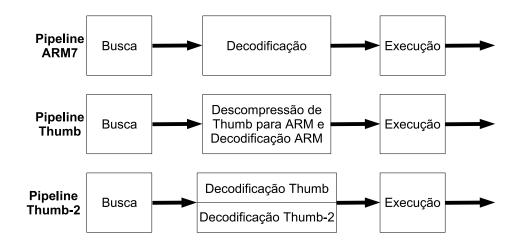

de redução<sup>1</sup> dos códigos convertidos para Thumb pode chegar a até 30%, ou seja, um programa Thumb pode ser até 30% menor do que o mesmo programa ARM convencional. A Figura 2.5 mostra uma visão geral dos *pipelines* ARM, Thumb e Thumb-2.

Thumb-2 [30] é um superconjunto do conjunto de instruções Thumb. O conjunto de instruções Thumb-2 é composto por todas as instruções Thumb de 16 bits além de um grande conjunto de instruções de 32 bits para conseguir quase a funcionalidade total do conjunto original de instruções ARM. Isto significa que instruções de 16 e 32 bits podem ser utilizadas em conjunto permitindo ao compilador selecionar o conjunto ótimo de instruções. O resultado é que o código Thumb-2 pode conseguir o alto desempenho do código ARM e ao mesmo tempo o benefício da densidade do código Thumb. Os resultados apresentados em [35] mostram que um programa Thumb-2 pode ser até 25% mais rápido do que Thumb e 26% menor do que ARM.

Figura 2.5: Pipelines dos processadores ARM, Thumb e Thumb-2

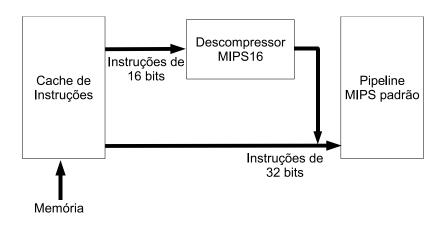

O processador MIPS16 foi apresentado como uma solução para os problemas de densidade de código e largura de banda do MIPS RISC. Ele é classificado como uma extensão da arquitetura MIPS. O suporte para MIPS16 não é obrigatório para todas as implementações posteriores de MIPS, mas é o mecanismo padrão para compressão de

<sup>&</sup>lt;sup>1</sup>Fator de Redução é a medida (%) que indica quanto foi a redução do tamanho de código de um programa quando codificado em outro esquema de codificação.

código dentre todos os fornecedores de CPUs MIPS RISC.

Como o nome sugere, MIPS16 é uma codificação de instrução de 16 bits. Ele foi projetado para ser 100% compatível com a arquitetura e programação dos outros processadores MIPS de 32 bits (MIPS-I/II) e de 64 bits (MIPS-III). De forma equivalente ao processador Thumb, MIPS16 possui a instrução JALX para trocar o conjunto de instruções utilizado (16 ou 32 bits). O processador MIPS16 oferece um fator de redução de até 40% sobre código MIPS convencional. A Figura 2.6 mostra uma visão geral do MIPS16.

Figura 2.6: Visão geral do processador MIPS16

Reduzir o número de bits para representar uma instrução realmente pode trazer grandes benefícios relacionados ao tamanho final de um programa, porém o custo desta abordagem é a grande limitação de recursos de programação como menor número de registradores representáveis, imediatos com menos bits e, conseqüentemente, mais instruções para escrever o mesmo programa. Esta última conseqüência pode afetar diretamente o desempenho do processador pois o número de instruções que serão buscadas na memória, decodificadas e executadas será bem maior.

Para evitar a limitação de recursos utilizados pelo programador, pode-se utilizar uma outra abordagem de redução de código como, por exemplo, uma técnica de compressão. Neste caso, as instruções em memória são representadas em um formato comprimido, idealmente criado pelo compilador e, durante o estágio de decodificação, a instrução volta

ao seu formato original para que possa ser executada. A próxima seção descreve algumas das diversas técnicas de compressão de código conhecidas na literatura.

### 2.2.2 Compressão de Código

A compressão de código é uma técnica diferente do que foi utilizado em MIPS16 e Thumb pois os algoritmos de compressão vão além de realizar um simples mapeamento entre instruções menores e maiores. Após o estágio de busca, o mecanismo descompressor reconstrói cada uma das instruções comprimidas para que possam ser utilizadas no estágio de execução. Além disso, ao utilizar uma técnica de compressão não há necessidade de um conjunto de instruções especiais. Para o programador, isto é totalmente transparente. Diante disso, vários trabalhos com foco em redução do tamanho de instruções utilizaram conceitos e técnicas da área de compressão de código, sendo uma parte destes estudos voltados para as arquiteturas VLIW [27, 31, 34, 48, 49, 50], que é o foco deste trabalho de mestrado.

O grande desafio de uma técnica de compressão é ter um mecanismo de compressão eficiente o bastante para reduzir ao máximo o tamanho do código em memória e ao mesmo tempo, um esquema de descompressão muito simples a ponto de influenciar o mínimo possível na área, no consumo de energia e no tempo de execução do processador. Entretanto, algumas das propostas tentam melhorar a taxa de compressão do programa mas degradam o desempenho do processador ao realizar a descompressão [49]. Dentre as diversas técnicas de compressão de código, boa parte utiliza uma estrutura de armazenamento conhecida como dicionário. Este hardware mantém informações que são utilizadas durante o processo de descompressão.

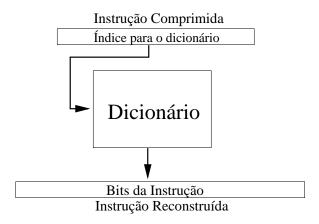

A Compressão por Instrução [26] é a técnica mais simples das que utilizam dicionário. Nesta abordagem, cada vez que se encontra uma instrução diferente, é criada uma entrada em um dicionário. Esta entrada no dicionário (índice) representa a instrução no código comprimido. O método de descompressão também é o mais simples, conforme pode ser visto na Figura 2.7. Basta utilizar o índice armazenado na instrução comprimida e buscar a instrução correspondente no dicionário. Experimentos realizados [34] mostram um fator de redução de até 18,5% para esta técnica.

Figura 2.7: Visão geral da Descompressão por Instrução

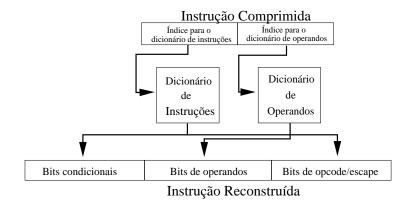

A Compressão por Fatoração de Instrução [34] é semelhante ao método anterior mas, neste caso, existem dois dicionários: um para os opcodes e outro para os operandos. Nesta técnica uma instrução é dividida em dois campos: campo de bits de instrução, onde estão opcode, seqüências de escape, bits condicionais, bits específicos de hardware, etc, e campo de operandos, conforme pode ser visto na Figura 2.8. Como este método não é adequado para arquiteturas com instruções de formato variável, foi criada uma extensão dele através da utilização de mais um conjunto de bits para identificar a classe a qual pertence uma determinada instrução. Assim, a instrução comprimida possui quatro campos: índice para o dicionário de instruções, índice para o dicionário de operandos, bits de seleção de classe e outros bits, estes últimos podem ser bits especiais que aparecem em alguns tipos de instrução para indicar, por exemplo, que a instrução será executada em paralelo. Experimentos realizados mostram que esta técnica atinge um fator de redução de até 31,7%.

Na Compressão por Fatoração de Operandos [2] a estratégia é separar as árvores de expressões do programa em seqüências de *opcodes* e operandos (registradores e imediatos). Nos experimentos apresentados em [34], esta técnica é aplicada de forma um pouco diferente: as instruções são agrupadas em grupos de oito e os seus bits correspondentes são utilizados para formar uma entrada no dicionário. Estes experimentos mostram um fator de redução de até 15,3% para esta técnica.

Figura 2.8: Visão geral da Descompressão por Fatoração de Instrução

A Compressão por Isomorfismo de Instrução [27] utiliza instruções isomorfas que são instruções com o mesmo opcode mas com pequenas diferenças no conjunto de operandos ou o mesmo conjunto de operandos com diferentes opcodes. Sua abordagem consiste em selecionar as instruções mais freqüentes e separar seus operandos e opcodes em dois dicionários. As instruções isomorfas entre si apontam para o mesmo índice nos dicionários. Neste trabalho os autores conseguiram um fator de redução de até 37%.

O trabalho apresentado em [3] mostra que é possível obter, ao mesmo tempo, ganho de desempenho, redução de código e redução no consumo de energia através de uma compressão de código eficiente e um descompressor bastante simples. Este método de compressão é baseado em dicionários e, para definir as instruções que serão comprimidas, propõe uma mistura de duas abordagens: avaliação estática (instruções que mais aparecem no código) e avaliação dinâmica (instruções mais executadas). Neste esquema de compressão o percentual de instruções selecionadas estaticamente ou dinamicamente é parametrizado através de um fator f. Isto permite avaliar qual a melhor proporção de cada abordagem. Se f=30% significa que pelo menos 30% das instruções foram selecionadas pelo critério dinâmico. Os resultados mostraram que quando f=70% consegue-se obter o melhor desempenho, redução de código e redução de energia. O descompressor utilizado é do tipo PDC (Processor-Decompressor-Cache), o qual posiciona o descompressor entre a cache e o processador. A técnica foi validada através de benchmarks executados em

uma implementação real do circuito descompressor sobre um processador Leon (SPARC V8). O fator de redução variou de 12% a 28%, o ganho de desempenho foi de até 45% e a redução no consumo de energia atingiu 35%.

As técnicas de compressão são uma alternativa interessante quando o desafio é minimizar a diferença de velocidade entre processador e memória pois muitas delas oferecem fatores de redução de código bastante significativos, permitindo reduzir drasticamente o número de acessos à memória. Porém, de uma forma geral, ao utilizar técnicas de compressão ocorre um aumento natural do tempo de compilação (compressão das instruções) proporcional à complexidade do algoritmo de compressão. Além disso, por mais simples que seja o circuito descompressor, ele influencia a área ocupada pelo processador e, dependendo da eficiência da técnica, pode aumentar o consumo de energia e até o tempo de ciclo do processador.

Outra linha de pesquisa que visa melhorar o desempenho dos processadores e pode ser utilizada como alternativa à compressão de código é o agrupamento de instruções. Nesta técnica as instruções dependentes são agrupadas de forma a constituir uma única macro-instrução que será executada dentro de uma ULA adaptada. Esta abordagem será explicada na próxima seção.

### 2.2.3 Agrupamento de Instruções

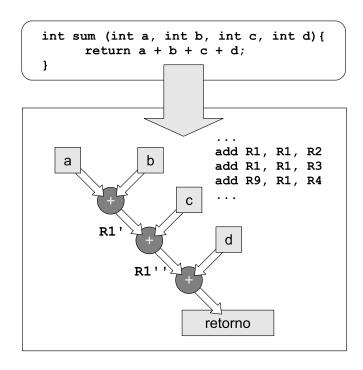

Com uma estratégia bem diferente das técnicas de compressão de código mas com o objetivo comum de melhorar o desempenho dos processadores, a técnica de Agrupamento de Instruções [15, 40, 41, 42] tem como foco principal reduzir o número de instruções a serem executadas. Nesta técnica são analisadas as cadeias de dependência das instruções e cada grupo de instruções dependentes é transformado em uma única instrução.

A proposta apresentada em [40] visa detectar cadeias de instruções conectadas por operandos temporários (R1 na Figura 2.9), ou seja, operandos que fazem parte de operações, mas que são descartados pois o resultado final será armazenado em um único consumidor (R9 na Figura 2.9). Estas instruções são agrupadas em uma única instrução e as instruções originais são removidas da linha de execução. Para isso é necessário um circuito simples e

também uma *cache*, ambos fora do caminho crítico do *pipeline*. Neste trabalho, define-se como *strand* um conjunto de instruções ligadas por operandos temporários (Figura 2.9). Cada instrução composta pode ser formada por no máximo três instruções.

Figura 2.9: Strand composto por três instruções

Um dado interessante é que os operandos temporários têm vida curta, ou seja, em média, existem menos de quatro instruções separando o produtor do consumidor. As ULAs utilizadas nesta técnica possuem a capacidade de alimentar suas entradas com o último resultado processado. Segundo [40], as ULAs convencionais que gastam um ciclo, gastam na verdade meio ciclo para realizar a operação e meio ciclo para repassar o resultado. Como nesta técnica os resultados produzidos são reutilizados pela própria ULA, é possível realizar duas operações por ciclo. Assim, a latência total para se obter o resultado final de um strand é de  $((0,5 \times H) + 0,5)$ , onde H é a quantidade de instruções agrupadas no strand. Ao final do processamento de todo o strand gasta-se meio ciclo para repassar o valor. Os resultados mostraram que mais de 25% das instruções que são processadas em ULAs convencionais podem ser agrupadas. Em média, houve até 20% de

melhora no número de instruções executadas por ciclo (IPC).

Outro trabalho [41] nesta mesma linha aplicou a técnica de forma híbrida (estático + dinâmico), ou seja, a detecção de *strands* foi realizada em tempo de compilação (estaticamente) e a otimização dos mesmos em tempo de execução (dinamicamente). A principal motivação para esta proposta foi o fato de que para fazer todo o processo dinamicamente é necessário um hardware muito complexo e que consome energia suficiente para tornar sua aplicação impraticável em sistemas embutidos. Os experimentos realizados neste trabalho mostram que é possível reduzir o consumo de energia dos circuitos em até 24%, dos barramentos em até 20% e do banco de registradores em até 14%. Além disso, houve um aumento na capacidade efetiva dos recursos de *pipeline* em quase um terço e, em média, houve um aumento 15% no IPC.

A técnica que propõe o agrupamento de instruções dependentes realmente é bastante interessante no sentido de diminuir os acessos ao banco de registradores e a quantidade de instruções percorrendo o datapath. Isso pode levar a um ganho de desempenho e economia de energia. Porém, como descrito em [41], quando esta técnica é aplicada apenas em hardware, os circuitos se tornam muito complexos e o consumo de energia é relativamente alto. Além disso, é necessário pelo menos mais um estágio no pipeline para detecção de cadeias dependentes e também uma nova cache para armazenar os strands. Outra característica que pode ser alterada é o tempo de ciclo do processador.

A proposta da técnica de agrupamento de instruções é permitir que duas instruções possam ser executadas na mesma ULA em um único ciclo mas, em contrapartida, o tamanho do ciclo pode acabar sendo maior devido a troca de instruções RISC por instruções mais complexas (strands).

A forma como foi empregada a técnica em [41], a torna bem mais viável para qualquer tipo de processador, visto que além de reduzir o consumo de energia, produz um aumento significativo no IPC. Um ponto que não fica muito claro neste trabalho é com relação ao tamanho final do programa estático após o agrupamento das instruções dependentes. Ao agrupar instruções é necessário armazenar a identificação do início e o tamanho dos strands. Sendo assim, pode-se entender que esta representação, apesar de diminuir o

número de instruções, pode gerar um programa maior do que o original em memória, o que pode exigir uma largura de banda maior.

### 2.2.4 Discussão sobre Redução de Código

Nas seções anteriores foram apresentadas três abordagens bem diferentes com o objetivo comum de reduzir o tamanho do código de um programa. Enquanto que em alguns trabalhos a estratégia é utilizar um conjunto especial de instruções menores, outros mostram que é possível comprimir as instruções sem precisar definir um novo conjunto de instruções. Em outra abordagem, os autores mostram que as instruções podem ser agrupadas através da análise de suas dependências.

As técnicas de compressão de código foram as primeiras a surgir, dentre as três abordagens. O número de trabalhos encontrados na literatura é bem maior para as técnicas de compressão e os estudos mais recentes estão na área de agrupamento de instruções.

As três abordagens possuem vantagens e portanto, sem uma análise muito aprofundada é praticamente impossível afirmar qual é a melhor. Nos três casos o circuito necessário para a implementação da técnica gera *overhead* significativo no processamento mas em compensação, o desempenho alcançado é bem interessante. Dentre todas as abordagens apresentadas, talvez a mais promissora seja o agrupamento de instruções que utiliza a detecção de *strands* estaticamente conforme apresentado por [41].

Outra abordagem que pode ser utilizada para melhorar o desempenho do processador é evitar a execução de instruções desnecessárias cujo resultados já foram calculados em algum ponto do programa. Na próxima seção são apresentadas algumas técnicas de reuso que mostram resultados interessantes quando se consegue aproveitar valores previamente calculados ao invés de executar novamente um determinado conjunto de instruções.

## 2.3 Reuso de Instruções

Estudos mostram que boa parte dos resultados das instruções de um programa já foram computados previamente no mesmo programa [25, 33, 46]. As técnicas utilizadas para tirar proveito desta característica intrínseca aos programas têm como principal objetivo

evitar que a mesma instrução seja executada novamente sem que haja de fato necessidade. Ao evitar estas re-execuções é possível obter um ganho de desempenho considerável. Nesta seção são apresentadas técnicas que mostram como reutilizar instruções.

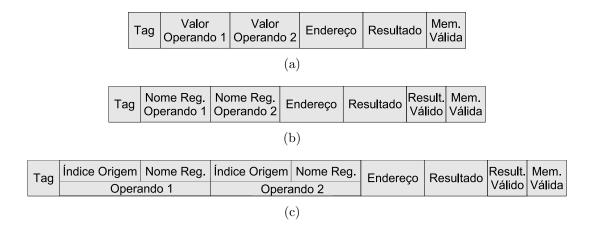

Na técnica chamada de *Instruction Reuse* (IR) [46], os resultados das instruções são armazenados para que possam ser reutilizados pelas mesmas instruções em outros pontos do programa. A estrutura de armazenamento dos resultados é chamada de *Reuse Buffer* (RB). Existem três esquemas para reutilizar instruções. Independente de qual for utilizado, deve-se atentar para três fatores: quais as informações armazenadas no RB, a forma como é realizado o teste para descobrir se será possível reutilizar a instrução e atualização/invalidação da informação no RB.

O primeiro esquema, chamado de  $S_v$ , é o mais simples e sua entrada no RB é representada por: valores dos operandos, resultado da operação, endereço calculado (para operações de leitura ou escrita na memória), flag que indica a validade do endereço de memória calculado, além de uma tag que armazena parcialmente o PC (Program Counter) e funciona como um índice para localizar a instrução (Figura 2.10(a)). Ao decodificar uma instrução, é verificada se existe uma entrada no RB correspondente e, caso exista, o resultado da operação é reutilizado. No segundo esquema, denominado  $S_n$ , a única diferença é que são armazenados os nomes dos registradores, ao invés dos valores (Figura 2.10(b)). Sendo assim, qualquer escrita em um registrador faz com que todas as linhas no RB que estejam utilizando este registrador sejam invalidadas. O campo Resultado Válido indica se o valor ainda pode ser reutilizado.

O terceiro esquema, conhecido por  $S_{n+d}$ , tenta minimizar as linhas que são invalidadas pelo esquema  $S_n$ , aumentado assim o número de instruções reutilizadas. O princípio utilizado é de que, se uma instrução pode ser reutilizada, então suas instruções dependentes também podem. Para implementar esta idéia é necessário a utilização de mais uma tabela (além do RB), a Register Source Table (RST) cujo papel é fazer uma ligação entre uma instrução consumidora e a última instrução produtora de valores de um determinado registrador. A entrada do RB para esta estratégia é bem parecida com a entrada do RB na estratégia  $S_n$ , porém, além dos nomes dos registradores, também são armazenados os índices (referentes ao RB) das instruções que geram valores para o registrador

Figura 2.10: Entradas no RB para os esquemas (a)  $S_v$ , (b),  $S_n$  e (c)  $S_{n+d}$

(Figura 2.10(c)). Uma instrução que possua dependência pode ser reutilizada se as instruções das quais a primeira depende forem as últimas produtoras para seus operandos (esta verificação é realizada através da RST).

Os experimentos realizados com programas SPEC'92 e SPEC'95 mostraram que utilizando o esquema  $S_v$  é possível conseguir um reuso de até 76%, enquanto que utilizando o  $S_n$  obtém-se reuso de até 25% e no  $S_{n+d}$  de até 59%. Este resultado pode ser explicado devido à quantidade de invalidações ocorridas nos esquemas  $S_n$  e  $S_{n+d}$ . As linhas do RB são raramente invalidadas quando se utiliza o esquema  $S_v$ , pouco invalidadas no esquema  $S_{n+d}$  mas são invalidadas com grande freqüência no esquema  $S_n$  pois qualquer escrita em um registrador invalida todas as linhas que referenciam este registrador no RB. Conseqüentemente, o speedup foi maior no esquema  $S_v$ , chegando a até 43%, enquanto que no esquema  $S_n$  foi de no máximo 17% e no esquema  $S_{n+d}$  foi de até 30%

Além da técnica Instruction Reuse, existem outras técnicas de reuso como Instruction Memoization (IM) [33] e Instruction Level Reuse (ILR) [25]. Em IM a procura por resultados já computados é realizada apenas na fase de execução e além disso, somente alguns tipos de instrução fazem parte do esquema de reuso, aquelas instruções que normalmente precisariam de mais de um ciclo para executar. No caso de IR, a procura por resultados ocorre no estágio de despacho (issue) (um estágio anterior à execução) e todas as ins-

truções são consideradas no esquema de reuso. A técnica ILR apresenta como principal vantagem sobre as outras duas o fato de considerar instruções que não são idênticas mas que geram os mesmos resultados, ou seja, instruções com o mesmo *opcode* que produzem o mesmo resultado podem ser reutilizadas. Desta forma, o reuso acaba sendo bem maior do que nas técnicas anteriores.

Um trabalho mais recente [6] propõe um novo estudo e revalidação destas três técnicas de reuso de instruções no contexto dos atuais microprocessadores para comprovar se realmente vale mais a pena recuperar o resultado computado por uma instrução em uma tabela ou simplesmente re-executar a instrução. Ao reproduzir os experimentos realizados pelos autores das três técnicas os resultados mostraram que no quesito reuso a técnica IM levou uma pequena vantagem na maior parte dos programas mas o speedup foi melhor quando se utilizou a técnica ILR.

Conforme pode ser visto em [6], o custo de se procurar por um resultado já computado pode ser maior do que simplesmente deixar que a instrução seja re-executada. É importante observar que boa parte das buscas nos buffers de reuso serão apenas um overhead para a fase de execução caso a instrução não esteja lá. De qualquer forma, é possível constatar com os trabalhos apresentados que existe um percentual considerável de instruções que se repetem durante a execução dos programas e que esta é mais uma característica que pode ser explorada para conseguir um melhor desempenho para os processadores.

Ao utilizar técnicas de reuso para melhorar o IPC do processador deve-se ter em mente que a latência da memória ainda pode continuar sendo o principal gargalo e, então, o desempenho alcançado pelo processador pode não ser tão evidente ao avaliar o sistema como um todo. Para minimizar esta diferença de velocidade entre memória e processador é importante melhorar o tempo de resposta da memória cache. Existem vários estudos realizados neste sentido e algumas estratégias como estruturar os dados dentro da cache, definir a organização da cache e até mesmo organizar ou reordenar o próprio programa para minimizar a quantidades de misses. Na próxima seção serão abordadas algumas técnicas que podem ser utilizadas para alcançar um bom desempenho em caches.

## 2.4 Desempenho em Caches

Enquanto que as técnicas de reuso de instruções possuem foco total em reduzir o número de instruções executadas, os trabalhos relacionados a *caches* se preocupam em conseguir responder às requisições do processador no menor tempo possível. Melhorando apenas o desempenho do processador, o tempo real de execução dos programas pode não ter ganhos significativos se o gargalo continuar sendo a comunicação entre processador e memória.

Muitos estudos já foram realizados com foco em minimizar o tempo da comunicação entre processador e memória. Mais especificamente, entre o processador e a memória cache. Segundo [16], a taxa de miss de uma cache normalmente pode ser reduzida aumentando o tamanho da cache, do bloco e/ou a associatividade. Porém, o tempo de acesso dos hits pode ser prejudicado se aumentar muito o tamanho da cache ou a associatividade. Além disso, o aumento do bloco freqüentemente reduz a taxa de miss mas aumenta o custo do miss. Para [4], quando a taxa de miss está acima de 30%, o desempenho é considerado baixo. Similarmente, a menos que o custo do miss seja alto (centenas de ciclos), uma taxa de miss menor que 0,3% terá pouco impacto na execução do programa.

A técnica apresentada em [16] visa melhorar o desempenho de caches (minimizar a taxa de miss e o custo do miss) através de otimizações em tempo de compilação. A estratégia é excluir da cache os itens com baixa freqüência de uso. O esquema proposto pode ser utilizado em caches de instrução ou de dados. A essência do esquema é permitir apenas que as partes do código que são altamente utilizadas passem pelas caches e que as partes raramente utilizadas entrem direto nos buffers de instrução ou registradores do processador.

Para caches de instrução, a análise é realizada nos programas com o objetivo de identificar os blocos básicos mais utilizados. De acordo com a freqüência de utilização dos blocos básicos, eles são classificados em High Usage (HU), Medium Usage (MU) ou Low Usage (LU). A mesma análise e classificação é realizada para caches de dados, porém, ao invés de analisar blocos básicos, são analisadas as estruturas de dados utilizadas pelo programa.

O estudo mostra que, na prática, é difícil encontrar demarcações claras entre HU, MU e LU. Os limites não precisam ser fixos, podem variar de acordo com o tamanho do programa e da *cache*. Se o conjunto de código/dado for muito pequeno comparado ao tamanho da *cache*, o programa inteiro pode ser marcado como HU. Se tiver apenas um nível de *cache*, só são necessárias as categorias HU e LU. Baseado na análise do compilador, as instruções HU são marcadas para utilizarem a *cache* L1, as instruções MU a *cache* L2 e as LU, a *cache* L3. Os experimentos realizados mostraram que para *cache* de dados, houve um *speedup* de 12% a 41% em *caches* de 4kb a 64kb. Para *cache* de instrução, *speedup* de 0% a 12% em *caches* de 1kb a 4kb.

Diferente da proposta anterior, o trabalho apresentado em [4] visa melhorar o desempenho de *caches* através da reorganização do código dos programas. O *layout* dos programas pode ser alterados em três granularidades: módulo, procedimento e blocos básicos. Enquanto que o rearranjo de módulos e procedimentos pode ser feito de forma arbitrária, para rearranjar os blocos básicos é necessário adicionar instruções de salto incondicional para preservar o fluxo original. Isto faz com que o código fique maior. Por isso, este último tipo de arranjo foi desconsiderado nos experimentos.

A expectativa dos autores com relação ao rearranjo dos programas é de que a variação de miss aumente quando ocorrer rearranjos em granularidades mais finas, devido à localidade intra-módulo e intra-procedimento. Depois de referenciar um procedimento, espera-se que outro procedimento do mesmo módulo seja referenciado logo em seguida. Caches com mapeamento direto devem mostrar maior variação de miss, sendo que esta variação vai diminuindo com o aumento da associatividade. Além disso, espera-se que, diminuindo o nível de otimização do compilador, diminua a variação de miss. Após a realização de vários experimentos com variação de layout, configuração de cache e otimização em tempo de compilação, foram apresentadas algumas conclusões bastante interessantes:

- Não existe variação típica das taxas de miss para os programas: a variação vai desde zero até uma grande variação.

- A variação de *miss* é pequena em *caches* de tamanho pequeno (alta taxa de *miss*): ao aumentar o tamanho das *caches*, a variação também aumenta ou permanece

baixa. Os dois tamanhos de linha experimentados (16 e 64 bytes) tiveram quase que as mesmas variações.

- Caches de mapeamento direto apresentam muito mais variações de miss do que as caches 4-associativas que não demonstram variação.

- Diminuir a otimização normalmente diminui a variação: foram vistos dois exemplos e um contra exemplo. Alterando o conjunto de entrada não muda a variação, com apenas uma exceção.

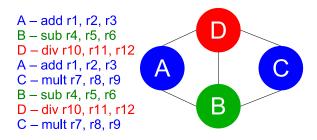

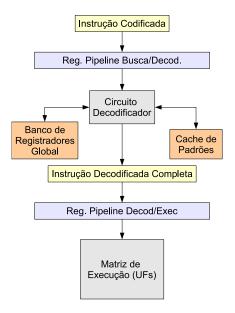

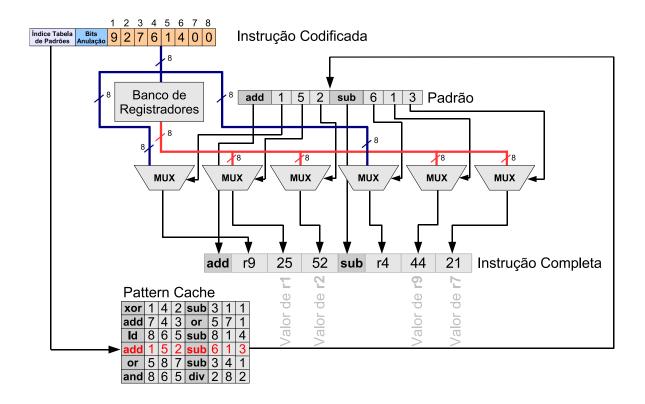

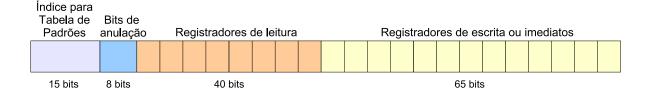

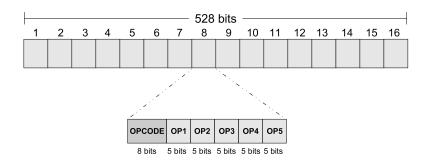

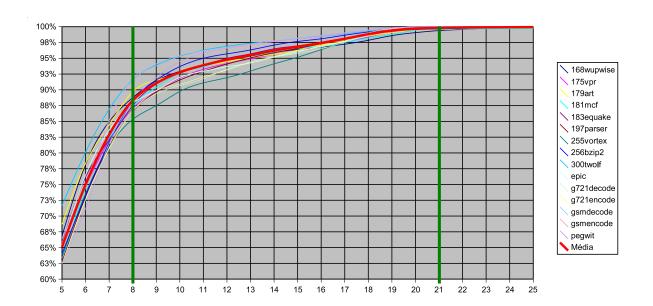

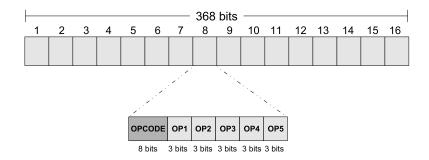

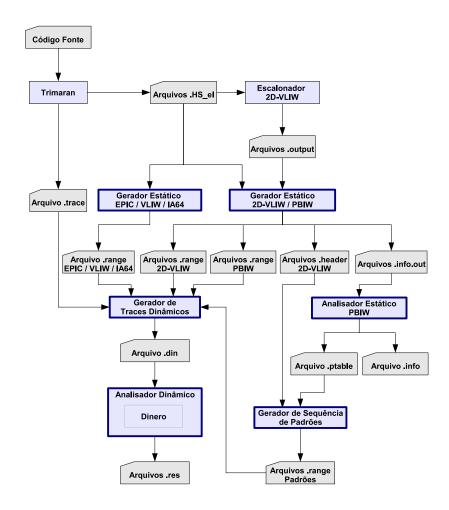

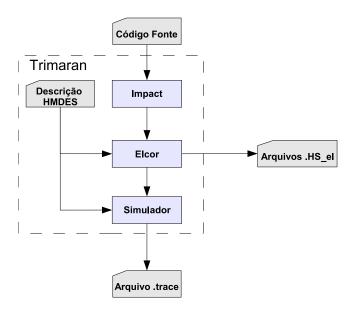

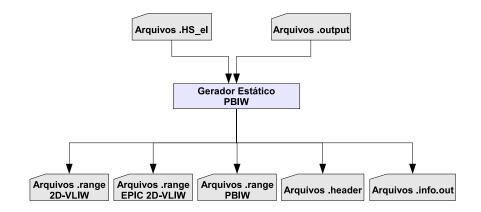

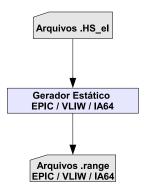

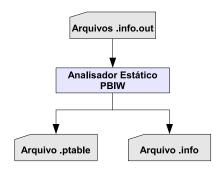

- Alterar o tamanho da *cache* não influencia na classificação dos *layouts*: os ruins continuam ruins, mas não existem *layouts* bons consistentes.