### A NEW, WATER-COOLED, 250KW, MODULAR MATRIX CONVERTER WITH HYBRID MODULATION AND INTELLIGENT GATE DRIVERS

### A DISSERTATION SUBMITTED TO THE DEPARTMENT OF DITEN AND THE COMMITTEE ON GRADUATE STUDIES OF THE UNIVERSITY OF GENOA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Alvise Zorzi April 2020

© Copyright by Alvise Zorzi 2020 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Maurizio Mazzucchelli) Principal Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Andrea Formentini)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

(Angelo Tani)

Approved for the University Committee.

### Abstract

Matrix converter are direct AC/AC converters that directly connect each input phase to each output phase through an array of controlled semiconductors, inherently capable of bidirectional power flow. The main advantage of Matrix Converters is the absence of bulky reactive elements, that are subject to aging, and reduce the system reliability. In addition, Matrix Converter can work with high efficiency levels, that can be further enhanced by adopting a new PMW-based modulation technique, that reduces switching losses. These characteristics, combined with the complete custom design of the hardware components, permit to obtain a converter characterized by an excellent power density value.

### Preface

Matrix converters are a kind of direct AC to AC power converters, consisting in an array of controlled semiconductor switches that directly connect each input phase to each output phase, and so they provide bidirectional power flow. The main advantage of Matrix Converters is that they are devoid of an intermediate DC link and, consequently, of bulky intermediate reactive elements, that are subject to aging and typically are the most unreliable element in any converter. In addition to this, Matrix Converters provide nearly sinusoidal input and output waveforms and controllable input power factor. In the light of the above, it's not surprising that Matrix Converters have received considerable attention as a good alternative to the typical Active Front End back to back with a Voltage Source Inverter configuration, which provides similar performances, albeit with some differences, the most notable one being the voltage levels. The early work dedicated to unrestricted frequency changers used thyristors with external forced commutation circuits to implement the bidirectional controlled, which were bulky and inefficient, but the advent of the power transistor gave momentum to the research in this field, resulting in the works of A. Alesina and M.

Venturini in the early 1980's [Venturini and Alesina(1980)], where they presented the Matrix topology as we know it today and invented its first modulation technique. Afterwards the research in this fields continued mainly in two lines. One line focuses on the development of bidirectional switches: in fact it must be noted that currently there are no discrete semiconductor devices that allow four quadrant switching operation, and so it is necessary to obtain it by combining discrete devices. The other line focused instead on alternative modulation techniques allowing higher voltage transfer ratio and better current quality. The first modulation technique presented by Alesina and Venturini, in fact, were limited to a voltage transfer ratio of 0.5. This ratio was then raised to 0.866 by means of third harmonic injection, a value which represents an intrinsic limitation of three-phase Matrix Converters with balanced supply voltages [Alesina and Venturini(1988)]. Other modulation techniques were then presented, like the "indirect method" [Huber and Borojevic(1989)], which describes the system as a traditional Active Front End connected by means of a "virtual DC-link" with a Voltage Source Inverter, and applies the well-known SVM technique.

However, Matrix Converters present several difficulties in their actual realization. First, the absence of free-wheeling diodes means that during the commutations it is necessary to actively provide the current with an alternative flowing path. Second, dangerous events like short-circuits and over-voltages must be managed with additional circuitry (like clamp units). Last, many switching techniques require additional information regarding voltages and currents flowing in the converter.

Chapter 1 gives an overview of the basic principles of matrix converters.

Chapter 2 proposes a novel modulation technique, namely the "Calvini Modulation" that allows obtaining a better performance in terms of efficiency.

Chapter 3 presents the complete design and the specifications of the converter, with the aim to obtain a product able to dominate the single-axis application market.

Chapter 4 presents the hardware development and the new solutions applied to obtain the wanted performances

Chapter 5 presents the various hardware tests of the isolated single components and their result.

Chapter 6 presents the whole assembled machine and the measurements made on it.

Chapter 7 is dedicated to the closing comments

### **Bibliography**

- [Alesina and Venturini(1988)] A. Alesina and M. Venturini. Intrinsic amplitude limits and optimum design of 9-switches direct pwm ac-ac converters. In PESC '88 Record., 19th Annual IEEE Power Electronics Specialists Conference, pages 1284–1291 vol.2, April 1988. doi: 10.1109/PESC.1988.18273.

- [Huber and Borojevic(1989)] L. Huber and D. Borojevic. Space vector modulator for forced commutated cycloconverters. In *Conference Record of the IEEE Industry Applications Society Annual Meeting*, pages 871–876 vol.1, Oct 1989. doi: 10.1109/IAS.1989.96746.

- [Venturini and Alesina(1980)] M. Venturini and A. Alesina. The generalised transformer: A new bidirectional, sinusoidal waveform frequency converter with continuously adjustable input power factor. In *1980 IEEE Power Electronics Specialists Conference*, pages 242–252, June 1980. doi: 10.1109/PESC.1980.7089455.

# Contents

| Al | ostrac | et                                                  | iv   |

|----|--------|-----------------------------------------------------|------|

| Pr | eface  |                                                     | v    |

| Bi | bliog  | raphy                                               | viii |

| 1  | Intr   | oduction                                            | 1    |

|    | 1.1    | Overview                                            | 1    |

|    | 1.2    | The bidirectional switch problem                    | 2    |

|    | 1.3    | Commutation strategies                              | 5    |

|    | 1.4    | Comparison with traditional solutions               | 8    |

|    |        | 1.4.1 Diode Bridge Rectifier + Full Bridge Inverter | 9    |

|    |        | 1.4.2 Active Front End + Full Bridge Inverter       | 10   |

|    |        | 1.4.3 Cycloconverter                                | 11   |

|    |        | 1.4.4 Comparison                                    | 12   |

|    | 1.5    | Aim of the thesis                                   | 12   |

| Bi | bliog  | raphy                                               | 13   |

| 2  | The    | Calvini Modulation                                  | 14   |

|    | 2.1    | Overview                                            | 14   |

|    | 2.2    | The Calvini Modulation                              | 15   |

|    | 2.3    | Calvini Modulation VTR and operative range          | 20   |

|    | 2.4    | Hybrid Venturini-Calvini modulation                 | 24   |

|    |        |                                                     |      |

#### Bibliography

| 3   | Тор-   | Level co | onverter design                        | 26 |

|-----|--------|----------|----------------------------------------|----|

|     | 3.1    | Matrix   | converter diffusion                    | 26 |

|     | 3.2    | Comme    | ercial availability                    | 27 |

|     | 3.3    | Existin  | g solution                             | 28 |

|     | 3.4    | Propos   | ed solution                            | 30 |

|     |        | 3.4.1    | Overview                               | 30 |

|     |        | 3.4.2    | Power quality and loss estimation      | 31 |

|     |        | 3.4.3    | Ratings and main components parameters | 36 |

|     |        |          |                                        |    |

| Bil | bliogr | aphy     |                                        | 38 |

| 4  | Con   | verter d | lesign                           | 39 |

|----|-------|----------|----------------------------------|----|

|    | 4.1   | Overv    | iew                              | 39 |

|    | 4.2   | Power    | Stage                            | 40 |

|    |       | 4.2.1    | Power stage architecture         | 40 |

|    |       | 4.2.2    | Matrix Converter layout          | 41 |

|    |       | 4.2.3    | Cold plate heat sink             | 43 |

|    |       | 4.2.4    | Input filter : capacitors busbar | 52 |

|    |       | 4.2.5    | Input filter : Inductor          | 54 |

|    |       | 4.2.6    | Clamp unit                       | 62 |

|    | 4.3   | Contro   | ol system                        | 64 |

|    |       | 4.3.1    | Control system layout            | 64 |

|    |       | 4.3.2    | Control Board                    | 68 |

|    |       | 4.3.3    | Gate drivers                     | 69 |

| Bi | bliog | raphy    |                                  | 76 |

| 5  | Test  | ing      |                                  | 77 |

|    | 51    | 0        | •                                |    |

| 5.1 | Overv  | iew              | 77 |

|-----|--------|------------------|----|

| 5.2 | Heat s | ink tests        | 78 |

|     | 5.2.1  | Aim of the tests | 78 |

|   |                   | 5.2.2    | Test 1 - water tightness                       | 78 |

|---|-------------------|----------|------------------------------------------------|----|

|   |                   | 5.2.3    | Test 2 - surface temperature and pressure drop | 30 |

|   | 5.3               | Induct   | or test                                        | 34 |

|   |                   | 5.3.1    | Aim of the test                                | 34 |

|   |                   | 5.3.2    | Test setup and results                         | 34 |

|   | 5.4               | Capaci   | itor busbar test                               | 36 |

|   |                   | 5.4.1    | Aim of the test                                | 36 |

|   |                   | 5.4.2    | Test setup                                     | 36 |

|   | 5.5               | Clamp    | unit tests                                     | 37 |

|   |                   | 5.5.1    | Aim of the test                                | 37 |

|   |                   | 5.5.2    | Test setup                                     | 38 |

|   | 5.6               | Gate D   | Driver tests                                   | 39 |

|   |                   | 5.6.1    | Aim of the test                                | 39 |

|   |                   | 5.6.2    | Test setup                                     | 39 |

|   |                   | 5.6.3    | Active Clamp                                   | 91 |

|   |                   | 5.6.4    | Gate driving voltage                           | 93 |

|   |                   | 5.6.5    | Communication signal integrity test            | 94 |

|   |                   | 5.6.6    | Measurement signals test                       | 95 |

|   | 5.7               | Interfa  | ce board tests                                 | 95 |

|   |                   | 5.7.1    | System power supply test                       | 95 |

|   |                   | 5.7.2    | Communication interfaces test                  | 97 |

| 6 | Resi              | ılts     |                                                | 98 |

|   | 6.1               | Pream    | ble                                            | 98 |

|   | 6.2               |          | ench setup                                     | )0 |

|   |                   | 6.2.1    | First operative point                          |    |

|   |                   | 6.2.2    | Second operative point                         |    |

|   |                   | 6.2.3    | Efficiency                                     |    |

| 7 | Cor               | clusions | s 11                                           | 17 |

| , | <b>Con</b><br>7.1 |          |                                                |    |

|   | 7.1               |          | g Comments                                     |    |

|   | 1.2               | ruture   | work                                           | 13 |

| 7.3 | Acknowledgments | • | • |  |  | • | • | • |  | • | • |  | • | • | • | • |  |  | • | • | • | • | • |  |  |  | • |  | • | • | 11 | 14 |

|-----|-----------------|---|---|--|--|---|---|---|--|---|---|--|---|---|---|---|--|--|---|---|---|---|---|--|--|--|---|--|---|---|----|----|

|-----|-----------------|---|---|--|--|---|---|---|--|---|---|--|---|---|---|---|--|--|---|---|---|---|---|--|--|--|---|--|---|---|----|----|

# **List of Tables**

| 3.1 | Yaskawa's 560kW Matrix converter assembly data  | 30  |

|-----|-------------------------------------------------|-----|

| 3.2 | Matrix Converter 250kW module ratings           | 37  |

| 3.3 | Matrix Converter 250kW module filter parameters | 37  |

| 4.1 | Heat sink design data                           | 45  |

| 4.2 | Heat sink performances                          | 51  |

| 5.1 | Water tightness test readings data              | 80  |

| 5.2 | Pressure drop and surface temperature test data | 84  |

| 5.3 | Inductor test data                              | 86  |

| 5.4 | Busbar measured capacitance values              | 87  |

| 6.1 | Final assembled converter parameters            | 99  |

| 6.2 | Output load parameters                          | 101 |

# **List of Figures**

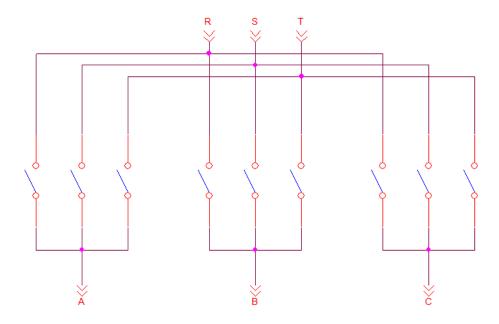

| 1.1        | Matrix Converter core structure                                              | 2              |

|------------|------------------------------------------------------------------------------|----------------|

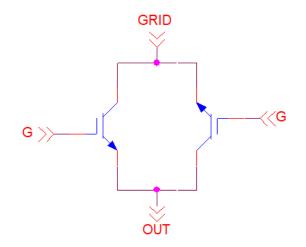

| 1.2        | Bidirectional switch realized with reverse blocking IGBTs                    | 3              |

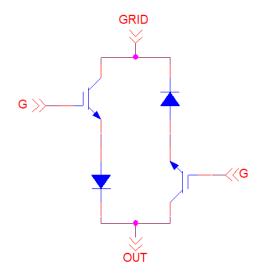

| 1.3        | Bidirectional switch realized with two diodes and two traditional IGBTs      | 4              |

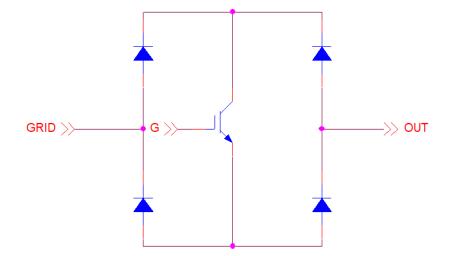

| 1.4        | Bidirectional switch realized with single traditional IGBTs and diode bridge | 5              |

| 1.5        | Simplified commutation circuit                                               | 6              |

| 1.6        | Elementary commutation cell with positive load current                       | 7              |

| 1.7        | Elementary commutation cell with negative load current                       | 8              |

| 1.8        | Matrix converter schematic                                                   | 9              |

| 1.9        | Diode bridge rectifier with full bridge inverter schematic                   | 9              |

| 1.10       | Active Front End with full bridge inverter schematic                         | 10             |

| 1.11       | Cycloconverter schematic                                                     | 11             |

| 2.1        | Quantities under investigation in the Matrix Converter                       | 16             |

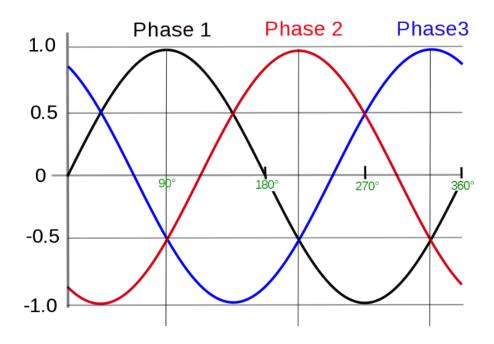

| 2.2        | Normalized three phase system                                                | 20             |

| 2.3        | Voltage Transfer Ratio with Calvini modulation                               | 23             |

| 3.1        | Yaskawa's U1000 family                                                       | 28             |

| 3.2        | Yaskawa's Matrix Converter outer dimensions                                  | 29             |

|            |                                                                              | 29             |

| 3.3        | Proposed Matrix Converter line filter configuration                          | 29<br>32       |

| 3.3<br>3.4 |                                                                              |                |

|            | Proposed Matrix Converter line filter configuration                          | 32             |

| 3.4        | Proposed Matrix Converter line filter configuration                          | 32<br>33       |

| 3.4<br>3.5 | Proposed Matrix Converter line filter configuration                          | 32<br>33<br>34 |

| 4.1  | Power Stage high level schematic                                       | 40 |

|------|------------------------------------------------------------------------|----|

| 4.2  | Semikron custom Matrix AXT and AXB modules                             | 41 |

| 4.3  | IGC193T120T8RM die                                                     | 42 |

| 4.4  | SKCD31C120I4F die                                                      | 42 |

| 4.5  | Actual matrix topology obtained with Semikron's custom power modules . | 43 |

| 4.6  | Proposed coolant circuit layout                                        | 45 |

| 4.7  | Cold plate CFD model with highlighted boundary conditions              | 46 |

| 4.8  | Coolant temperature distribution                                       | 47 |

| 4.9  | Coolant static pressure distribution                                   | 47 |

| 4.10 | Temperature distribution on the surface of the receptacle              | 48 |

| 4.11 | Temperature distribution on the surface of the cover                   | 48 |

| 4.12 | Cold plate receptacle wet area                                         | 49 |

| 4.13 | Cold plate cover                                                       | 50 |

| 4.14 | Displacement caused by water pressurized at 500kPa                     | 51 |

| 4.15 | Cold plate assembly                                                    | 52 |

| 4.16 | Capacitors direct soldering on busbar with thermal relief pad          | 53 |

| 4.17 | Busbar capacitors arrangement                                          | 54 |

| 4.18 | Traditional laminated E-core                                           | 55 |

| 4.19 | Traditional five-column shell core with three through bars             | 56 |

| 4.20 | Custom 4 columns, through bars design                                  | 56 |

| 4.21 | Custom inductor positioning                                            | 59 |

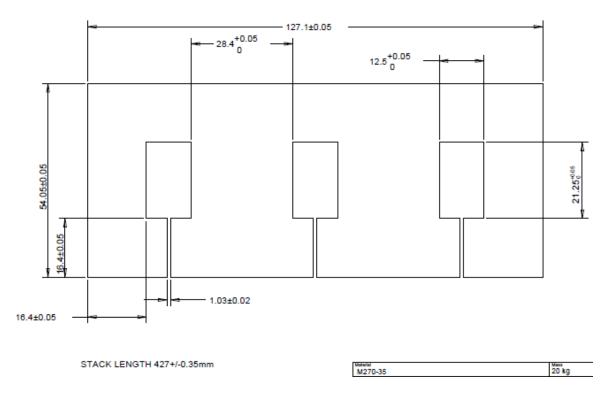

| 4.22 | Custom inductor lamination with actual dimensions                      | 60 |

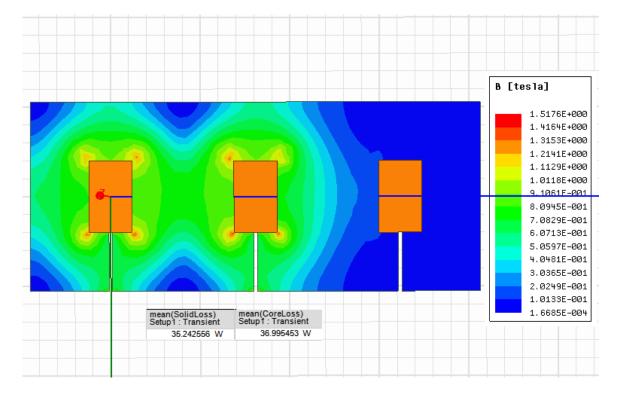

| 4.23 | 2D FEM analysis of the custom inductor                                 | 61 |

| 4.24 | CFD analysis of the thermal behavior of the custom inductor            | 62 |

| 4.25 | Matrix clamp unit schematic                                            | 63 |

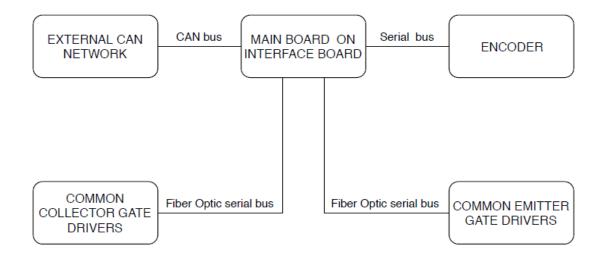

| 4.26 | Communication ring layout                                              | 65 |

| 4.27 | Master board - gate drivers communication frame                        | 67 |

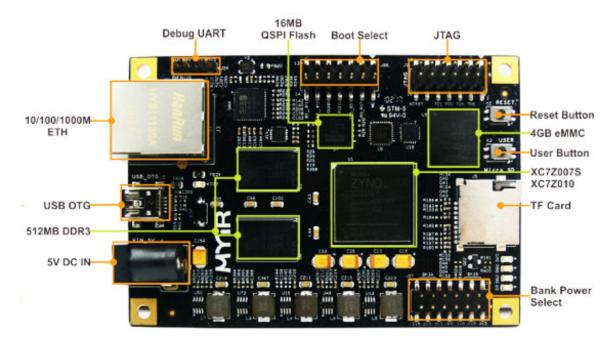

| 4.28 | Z-turn Lite board                                                      | 68 |

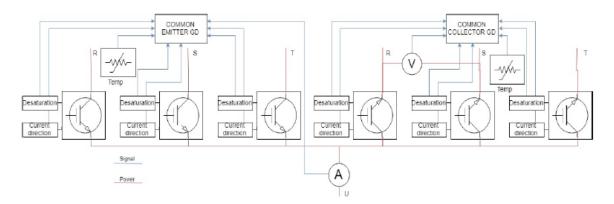

| 4.29 | Common emitter gate driver board                                       | 70 |

| 4.30 | Common collector gate driver board                                     | 70 |

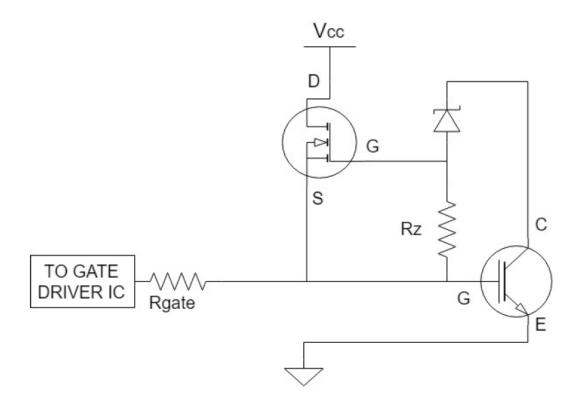

| 4.31 | Active clamp principle schematic                                       | 72 |

| 4.32 | Gate Driver to Control Board daisy chain communication ring                | 73 |

|------|----------------------------------------------------------------------------|----|

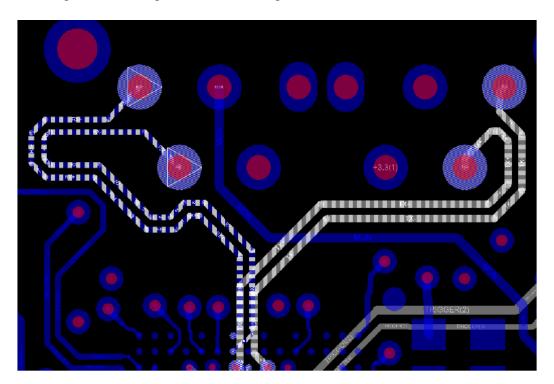

| 4.33 | Optical Fiber module LVDS routes                                           | 75 |

| 5.1  | Water tightness test bench                                                 | 79 |

| 5.2  | IGBTs connection schematic                                                 | 81 |

| 5.3  | Test piping schematic                                                      | 82 |

| 5.4  | Pressure drop and surface temperature test bench                           | 83 |

| 5.5  | Inductor under test                                                        | 85 |

| 5.6  | Capacitor Busbar                                                           | 87 |

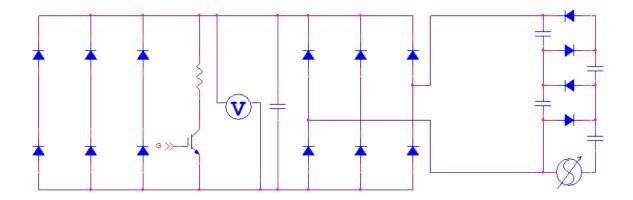

| 5.7  | Clamp unit test connection schematic                                       | 88 |

| 5.8  | Clamp unit intervention acquisition                                        |    |

|      | IGBT Gate-Emitter Voltage(violet, $5V/div$ )                               |    |

|      | IGBT Collector-Emitter Voltage (yellow, $200V/div$ )                       |    |

|      | Time scale : $20\mu s/div$                                                 | 89 |

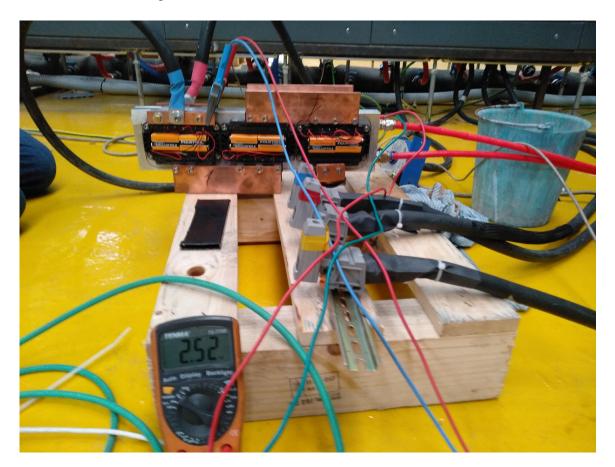

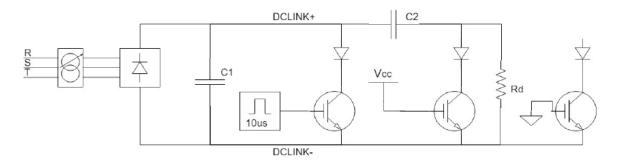

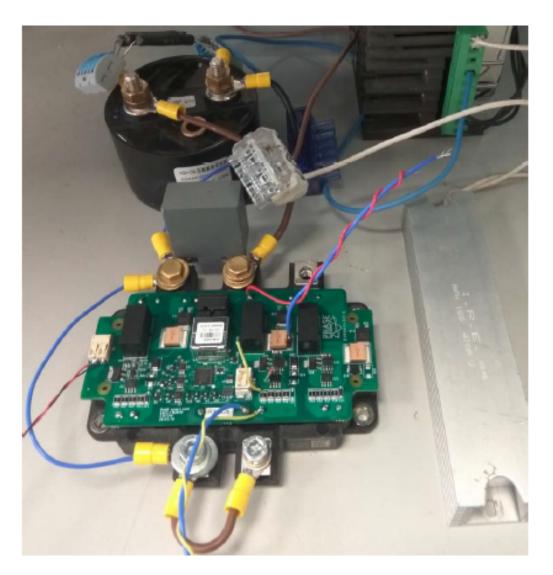

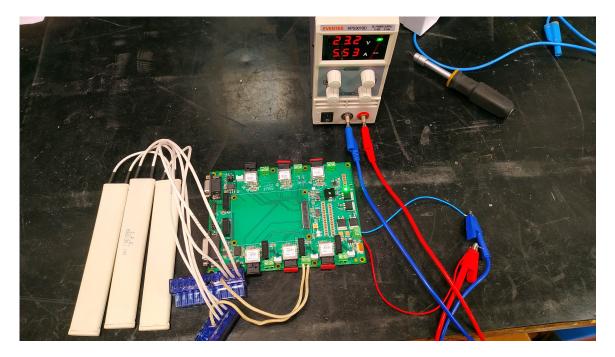

| 5.9  | Test bench scheme                                                          | 90 |

| 5.10 | Actual test bench                                                          | 91 |

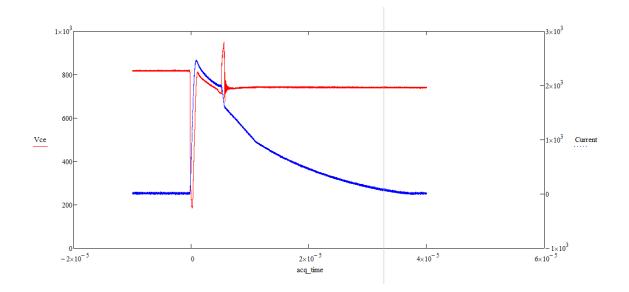

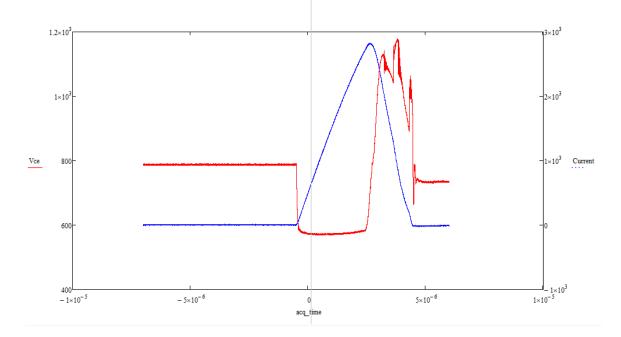

| 5.11 | Active clamp intervention during short circuit with free-wheeling path     |    |

|      | IGBT Collector current (blue, $1kA/div$ )                                  |    |

|      | IGBT Collector-Emitter Voltage (red, 200V/div)                             |    |

|      | Time scale : $20\mu s/div$                                                 | 92 |

| 5.12 | Active clamp intervention during short circuit without free-wheeling path  |    |

|      | IGBT Collector current (blue, $1kA/div$ )                                  |    |

|      | IGBT Collector-Emitter Voltage (red, 200V/div)                             |    |

|      | Time scale : $5\mu s/div$                                                  | 93 |

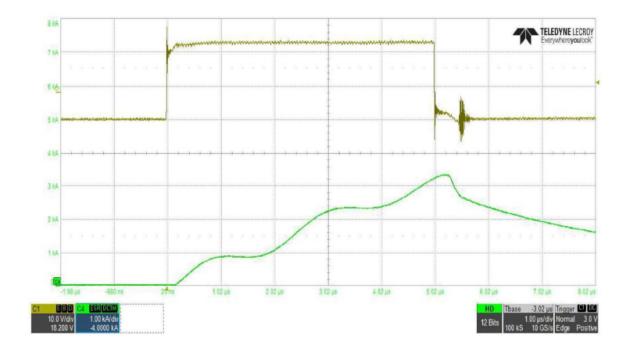

| 5.13 | Simultaneous acquisition of gate driving signal (yellow) and short circuit |    |

|      | current(green)                                                             |    |

|      | IGBT Collector current (Green, $1kA/div$ )                                 |    |

|      | IGBT Gate-Emitter Voltage (Ocher, $10V/div$ )                              |    |

|      | Time scale : $1\mu s/div$                                                  | 94 |

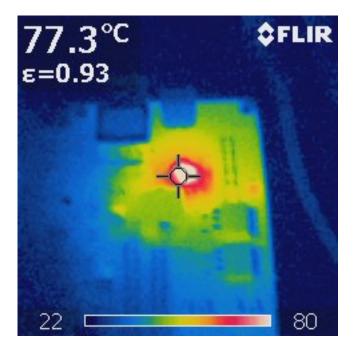

| 5.14 | Interface Board with power resistors connected                             | 96 |

| 5.15 | Thermal image of the buck converter area                                   | 97 |

|      |                                                                            |    |

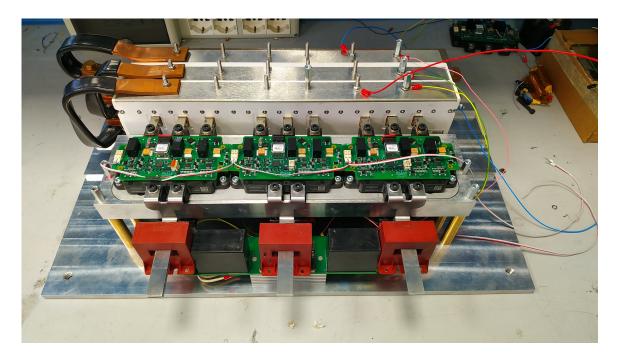

| 6.1  | Assembled Matrix converter                                                                                                               | 99  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

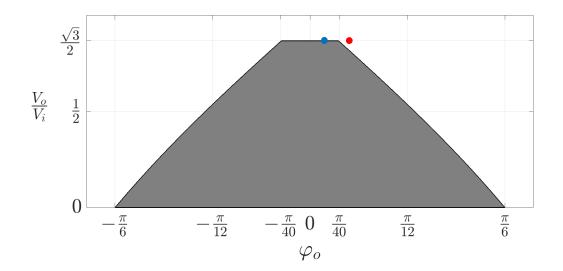

| 6.2  | Maximum VTR operative region and reference working points                                                                                | 100 |

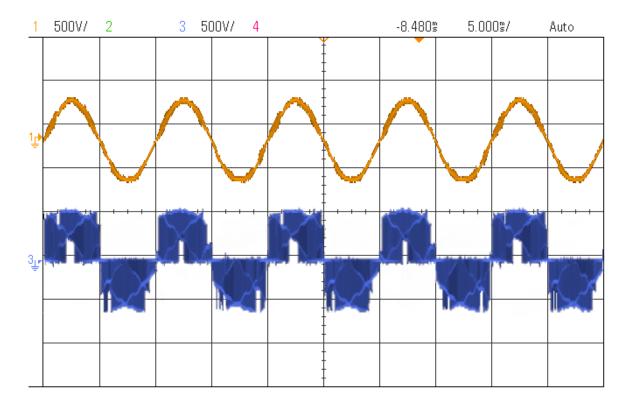

| 6.3  | Hybrid modulation output waveform acquisitions                                                                                           |     |

|      | Line-to-line filtered Input Voltage (ocher,500V/div)                                                                                     |     |

|      | Line-to-line unfiltered Output Voltage (blue, $500V/div$ )                                                                               |     |

|      | Time scale : $5ms/div$                                                                                                                   | 102 |

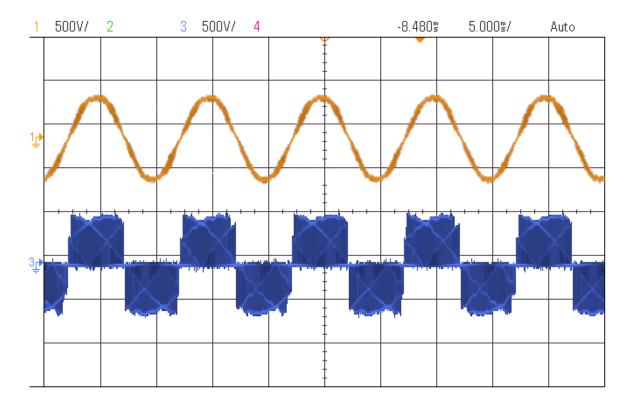

| 6.4  | Venturini's modulation output waveform acquisitions                                                                                      |     |

|      | Line-to-line filtered Output Voltage (ocher, $500V/div$ )                                                                                |     |

|      | Line-to-line unfiltered Output Voltage (blue, $500V/div$ )                                                                               |     |

|      | Time scale : $5ms/div$                                                                                                                   | 103 |

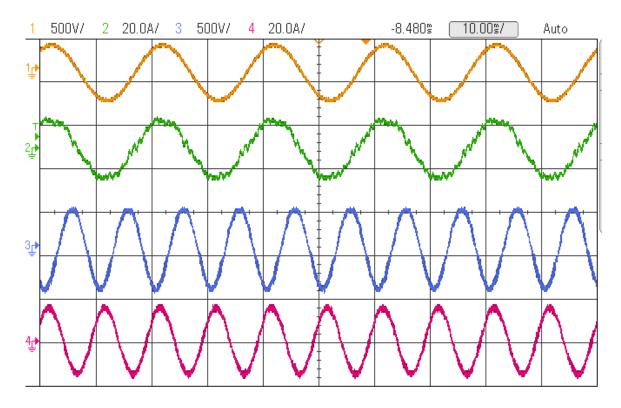

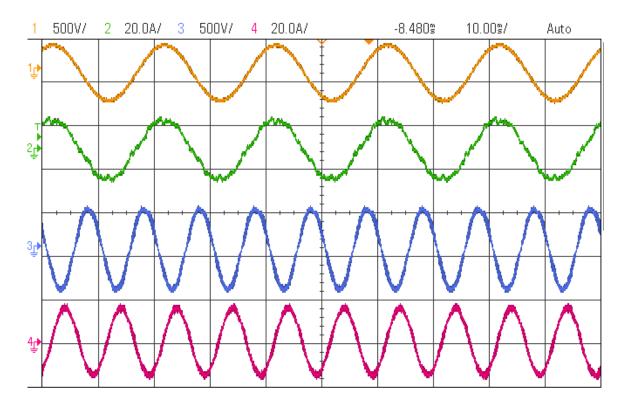

| 6.5  | Hybrid modulation acquisitions in operative point 1                                                                                      |     |

|      | Line-to-line Input Voltage (ocher, $500V/div$ )                                                                                          |     |

|      | Line input current (green, $20A/div$ )                                                                                                   |     |

|      | Line-to-line filtered Output Voltage (blue, $500V/div$ )                                                                                 |     |

|      | Line output current (violet, $20A/div$ )                                                                                                 |     |

|      | Time scale : $10ms/div$                                                                                                                  | 104 |

| 6.6  | Venturini modulation acquisitions in operative point 1                                                                                   |     |

|      | Line-to-line Input Voltage (ocher, $500V/div$ )                                                                                          |     |

|      | Line input current (green, $20A/div$ )                                                                                                   |     |

|      | Line-to-line filtered Output Voltage (blue, $500V/div$ )                                                                                 |     |

|      | Line output current (violet, $20A/div$ )                                                                                                 |     |

|      | Time scale: $10ms/div \dots \dots$ | 105 |

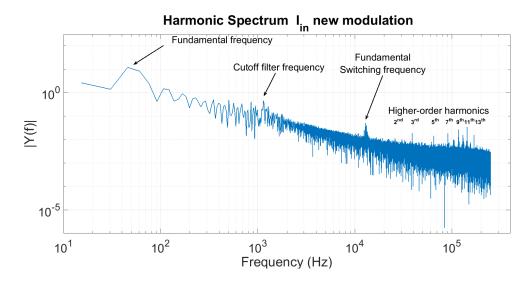

| 6.7  | Harmonics Spectrum of input current achieved with Hybrid modulation                                                                      |     |

|      | with output frequency 100Hz                                                                                                              | 106 |

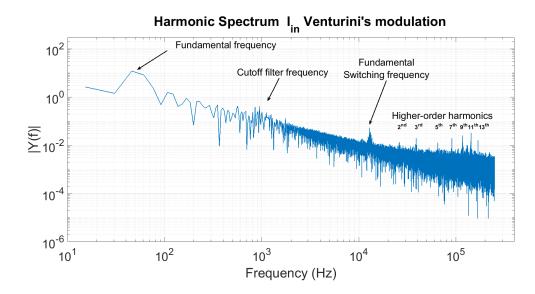

| 6.8  | Harmonics Spectrum of input current achieved with Venturini's modulation                                                                 |     |

|      | with output frequency 100Hz                                                                                                              | 106 |

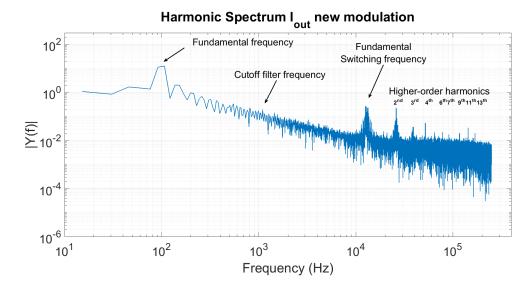

| 6.9  | Harmonics Spectrum of output current achieved with hybrid modulation                                                                     |     |

|      | with output frequency set to 100Hz                                                                                                       | 107 |

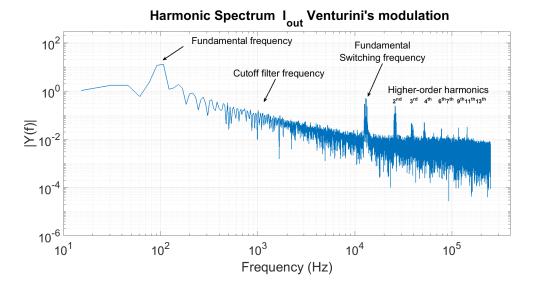

| 6.10 | Harmonics Spectrum of output current achieved with Venturini's modula-                                                                   |     |

|      | tion with output frequency set to 100Hz                                                                                                  | 108 |

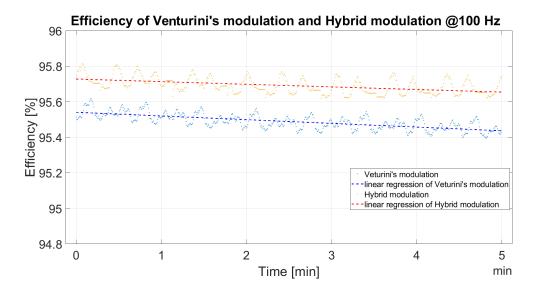

| Efficiency graph of Hybrid modulation vs. Venturini's modulation with        |

|------------------------------------------------------------------------------|

| output frequency 100Hz                                                       |

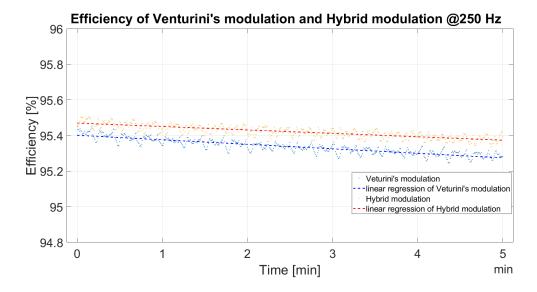

| Efficiency graph of Hybrid modulation vs. Venturini's modulation with        |

| output frequency 250Hz                                                       |

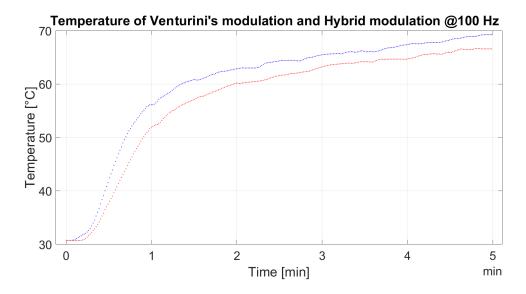

| Thermal results with output frequency 100Hz                                  |

| Temperature with Hybrid modulation (red dotted line, $10^{\circ}C/div$ )     |

| Temperature with Venturini modulation (blue dotted line, $10^{\circ}C/div$ ) |

| Time scale: $1min/div$                                                       |

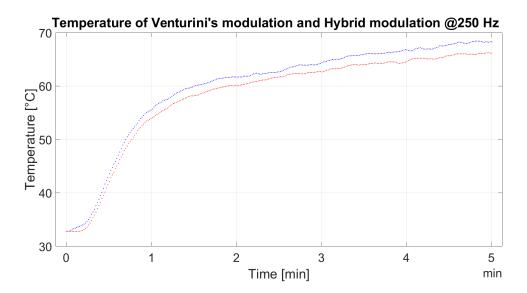

| Thermal results with output frequency 250Hz                                  |

| Temperature with Hybrid modulation (red dotted line, $10^{\circ}C/div$ )     |

| Temperature with Venturini modulation (blue dotted line, $10^{\circ}C/div$ ) |

| Time scale: $1min/div$                                                       |

|                                                                              |

## **Chapter 1**

### Introduction

### 1.1 Overview

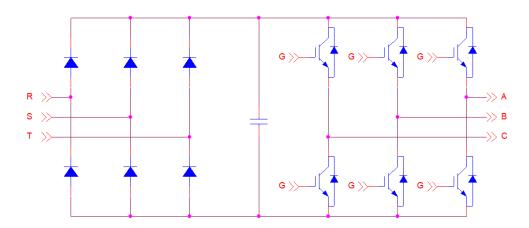

Matrix Converters, due to their ability to convert waveforms in a single stage, can be considered the most efficient AC/AC converter topology, capable of reducing various operation losses associated with conventional AC/DC/AC converters. At their core, matrix converters can be seen as "phase selector" devices, that directly transfer one input phase to an output phase. Fig.1.1 shows the core structure for a three-phase to three-phase Matrix Converter, when the converter is fed from a three phase voltage source at the input and provides power to an inductive load, but the available topologies are not limited this one, among them the three-phase to single-phase topology

Figure 1.1: Matrix Converter core structure

Obviously, due to some physical and technological limitations that are not taken in consideration in this idealization, an actual Matrix Converter is a more complex device, consisting at least in a power conversion section, an input filter and a clamp unit, as it will be discussed in the following chapters.

### **1.2** The bidirectional switch problem

The ideal bidirectional switches that appear in Fig.1.1 are not readily available as discrete semiconductors and must be obtained starting from traditional unidirectional devices. Three main different configurations have been proposed in literature [[Neft and Schauder(1988), S. Bernet and Lipo(1996), Ziogas and Khan(1986)]] and are shown in Fig. 1.2, Fig. 1.3 and Fig. 1.4.

Figure 1.2: Bidirectional switch realized with reverse blocking IGBTs

The first configuration is the simplest from the topological point of view and uses two anti-paralleled reverse blocking IGBTs. In this switch arrangement there are two separated internal current conduction paths in both directions, and these paths can be independently controlled in order to safely commutate the load current between different bidirectional switches. In this way it would be theoretically possible to eliminate local snubbers on the switches. However, reverse blocking IGBTs did not receive the favors of the market, and consequently have not improved much in comparison with traditional IGBTs or SiC FETs, and they topically present very high switching losses, while they do not behave much better in terms of conduction losses when compared with the IGBTs in series with a blocking diode.

Figure 1.3: Bidirectional switch realized with two diodes and two traditional IGBTs

In the light of the above, the second bidirectional switch configuration retains the same advantages of the first while enabling higher switching frequencies, at the cost of doubling the number of components (but not their cost or the die area). Higher switching frequencies mean smaller reactive components, which are always the bulkiest elements of a converter. Since the aim of this thesis was to design and develop a ready-to-market product, this was the chosen configuration for the switches, albeit with some tiny differences that will be discussed in the following chapters.

Figure 1.4: Bidirectional switch realized with single traditional IGBTs and diode bridge

The third switch configuration is listed for the sake of completeness; it uses a diode bridge that permits current flow in both directions when the central IGBT is closed. While this solution it is certainly the one that costs less, since diodes are way cheaper than IGBTs, it presents two big drawbacks. The first and most evident is that current needs to flow in three different devices, resulting in higher conduction losses when compared to the two aforementioned configurations. The second is that this configuration needs additional local snubbers, due to the fact that there are no separate conduction paths for the two possible current directions, and so, in order to perform a commutation, it is necessary to choose between closing the in-going switch before opening the outgoing one (resulting in an over-current), or, vice versa, opening the outgoing switch before closing the in going one (resulting in an over-voltage).

#### **1.3** Commutation strategies

One of the main issues related to the control of Matrix Converters is the current commutation: the (bidirectional) switches are not protected by the DC-link capacitors and there are no natural freewheeling paths. It can be said that the current commutation between switches in the Matrix topology is more difficult to achieve than in other, more traditional, solutions.

When considering commutation strategies for matrix converters two general basic rules must be adhered:

- commutation should not cause a short circuit between the two input phases, because the consequent high circulating current might destroy the switches

- commutation should not cause an interruption of the output current because the consequent overvoltage might likely destroy the switches.

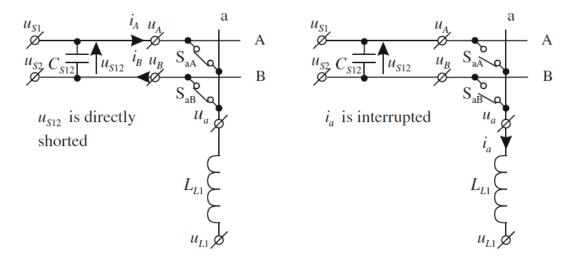

Consider the simplified commutation circuit shown in Fig.1.5

Figure 1.5: Simplified commutation circuit

When the switches are turned on simultaneously, the voltage sources will be shorted directly and the switches will be damaged due to overcurrents. On the other hand, if all the switches are turned off simultaneously, in the first instant after the switching-off an over-voltage will be generated which could destroy the semiconductors. The spikes of over-voltage depend on load current and duration of current interruption. However, the semiconductor devices cannot be switched instantaneously between states because of propagation delays and finite switching times, and various methods have been proposed to avoid these difficulties and to ensure a safe and successful commutation. The most common one (and

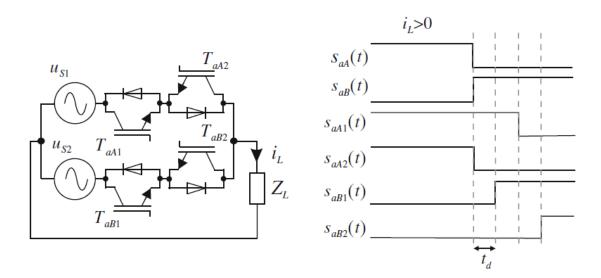

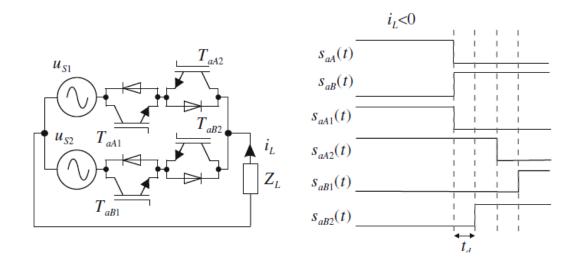

the one which was utilized in the converter developed during this thesis) is the four-step commutation strategy, also known as "semi-soft current commutation". In order to explain the strategy it is helpful to refer to the elementary commutation cell shown in Fig.1.6.

Figure 1.6: Elementary commutation cell with positive load current

The strategy assumes that when the output phase is connected to an input phase, both the IGBTs of the bi-directional switch S1 have to be turned on simultaneously. The following example assumes that the load current is in the direction as shown in Fig.1.6 and the upper bi-directional switch (S1) is closed. In this method, it is needed to know the current direction, which is used to determine which device in the active switch cell is not current conducting. The commutation process is shown as a timing diagram in Fig.1.6. In the beginning, both IGBTs of switch S1 are turned on in the same instant. In the first step, the IGBT  $T_{aA2}$ , which is not conducting the load current, is turned off. In the second step, after delay interval time  $t_d$ , the transistor  $T_{aB1}$  that will conduct the current is turned on. This allows both cells to be turned on without short circuiting the input phases and provides a path for the load current. Depending on the instantaneous input voltages, there are two kinds of commutation process after the second step. If  $u_{S2} > u_{S1}$  and  $i_L > 0$ , then the conducting diode of switch cell S1 could be reverse biased and a natural commutation could take place. In the third step the IGBT  $T_{aA1}$  is turned off. If there is no natural commutation during the second step, then a hard commutation happens when, in the third step, IGBT  $T_{aB1}$  is turned off. It must be noted that this uncertainty is reflected in the actual output voltage in terms of  $V \cdot s$ , but can usually be considered neglectable. In the fourth step, transistor  $T_{aB2}$  is turned on to also allow the conduction of negative currents. The time delay has to be set to a value higher than the maximum propagation time of the IGBT signals. In this strategy half of the commutation process is soft switching and half is hard switching, hence the name "semi-soft current commutation". However, when the currents are around the zero value, the current direction is not certain, and incorrect decisions can be made as to which switches conducts the load current. This can be a problem if no protection device (a clamping unit) is employed, however it is also true that the resulting overvoltages around the zero current value are usually limited. Fig.1.7 shows the commutation circuit and timing diagram for the condition  $i_L < 0$ .

Figure 1.7: Elementary commutation cell with negative load current

### **1.4** Comparison with traditional solutions

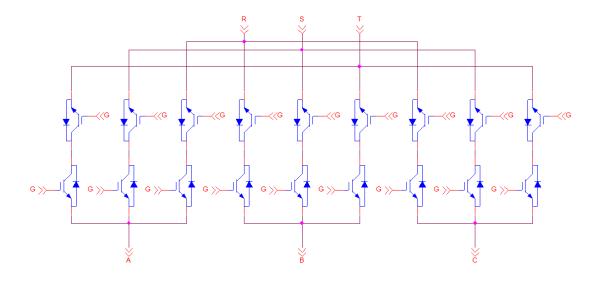

Following the considerations of 1.2, the circuit of Matrix Converter topology is presented in Fig.1.8, where the switches are implemented with the double anti-paralleled IGBTs configuration.

In this section the Matrix topology will be compared with the traditional AC/AC solutions that are listed below, along with their principal characteristics.

Figure 1.8: Matrix converter schematic

#### 1.4.1 Diode Bridge Rectifier + Full Bridge Inverter

Figure 1.9: Diode bridge rectifier with full bridge inverter schematic

In this indirect AC/DC/AC topology, shown in Fig.1.9, the input diode bridge rectifies an AC source into a DC, which is then smoothed out by some bulky and prone to aging DC-link capacitors and made available to a full bridge inverter, which then feeds the load. It is possible to feed multiple Full Bridge Inverters on the same Diode Bridge Rectifier.

This solution is still the most diffused, being consolidated and available at low cost, albeit presenting some serious limitations. First, the input diode bridge prevents bidirectional power flow. This not only prevents this topology for being used in power generation applications, but also from carrying out any regenerative braking operation in any motor application. In fact, the most diffused braking solution makes use of a chopper unit dissipating the motor energy that is made available on the DC-link by inverting the power flow in the full bridge.

Second, the pulsating current absorption of the diode bridge rectifier on the capacitors causes a large amount of harmonics that produces distortion of the input line voltages. This gives rise to a series of problems regarding the performance of sensitive loads and equipment connected to the same supply, causes additional losses on the utility system, lowers power factor due to waveform form factor and may excite electrical resonances. After all, this topology is the one that raised the problem of the power quality.

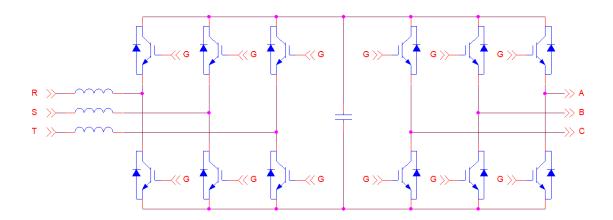

#### **1.4.2** Active Front End + Full Bridge Inverter

Figure 1.10: Active Front End with full bridge inverter schematic

In this indirect AC/DC/AC topology (also known as back-to-back converter), shown in Fig.1.10, the input Active Front End rectifies an AC source into a DC, which is then smoothed out by DC-link capacitors and made available to a full bridge inverter, which

then feeds the load. It is possible to feed multiple Full Bridge Inverters on the same Active Front End.

The Active Front End is capable of shaping the input current, and enables the operation with near-unity power factors with almost perfectly sinusoidal current and, consequently, low harmonic distortion. In addition, the converter is capable of bidirectional power flow and, of course, of regenerative braking. This solution is virtually capable of supplying any possible output voltage, since the the Active Front End can step up the voltage while the Full Bridge Inverter can step it down. With that said, it must be noted that while addressing many of the problems of the Diode Bridge Solution, this topology is still affected by the necessity of adopting a large DC-link capacitor.

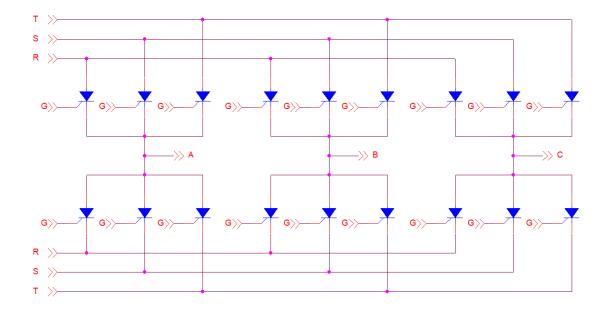

#### 1.4.3 Cycloconverter

Figure 1.11: Cycloconverter schematic

A cycloconverter, shown in Fig.1.11, is basically a self-commutated Matrix Converter based on thyristors, and it is effectively a direct AC/AC converter. Since a cycloconverter is capable of turning its (bidirectional) switches off only when the AC supply current crosses the zero, it is capable of supplying its load only with a fundamental frequency that it is a

fraction (typically less than one-third) of the AC input frequency. Moreover, in a cycloconverter the input current always lag behind the input voltage, effectively making impossible unity-power factor operation. Last, both output and input current are heavily distorted, and this distortion increases proportionally with output frequency. This relevant drawbacks limits the usage of cycloconverters typically to low number of poles, slow rotating, high power motors, operating off of the mains grid. In fact, cycloconverters are usually seen only in naval traction applications, where they are fed from the relatively high frequency (typically 400Hz) on-board generators and provide power to large motors directly connected to the propeller.

#### 1.4.4 Comparison

After this analysis it's possible to say that in comparison with the other converters, the Matrix Converter shines in high-performance, highly reliable single-axis applications, where space and efficiency are at premium. In fact, the Matrix Converter presented in this thesis was mainly developed for supplying HVAC systems and high performance medium size (500 kW) direct-drive motors.

#### **1.5** Aim of the thesis

As already mentioned, the aim of this thesis was to develop a state-of-the-art converter using the Matrix Topology and take advantage of the DC-link absence in order to create a converter as small as possible in pursue of motor-drive integration. To do that a new modulation technique, called "Calvini modulation", able to reduce switching losses (and so heat sink dimensions) when compared to the traditional ones, was developed for this specific drive and every design choice, that will be discussed in the next chapters, was made with system miniaturization in mind. All the possible aspects, from the electronic boards to the mechanical assembly were pointed towards compactness.

### **Bibliography**

- [Neft and Schauder(1988)] C.L. Neft and C.D. Schauder. Theory and design of a 30-hp matrix converter. *Conference Records of IEEE/IAS Annual Meeting*, pages 934–939, 1988.

- [S. Bernet and Lipo(1996)] T. Matsuo S. Bernet and T.A. Lipo. A matrix converter using reverse blocking nptigbts and optimised pulse patterns. *Proceedings of IEEE/PESC96*, pages 107–113, 1996.

- [Ziogas and Khan(1986)] P. D. Ziogas and S. I. Khan. Analysis and design of forced commutated cycloconverter structures with improved transfer characteristics. *IEEE Transactions on Industrial Electronics*, IE-33(3):271–280, Aug 1986. ISSN 1557-9948. doi: 10.1109/TIE.1986.350233.

### Chapter 2

### The Calvini Modulation

#### 2.1 Overview

The first rigorous mathematical analysis of a Matrix Converter modulation technique has been developed by Venturini and Alesina, and enabled a maximum voltage transfer ratio (VTR) of 50%. Venturini and Alesina then discovered that it was possible to increase the value of the maximum VTR, by introducing a common-mode voltage (CMV) by means of injecting a third harmonic, effectively raising its value to  $\frac{\sqrt{3}}{2}$ . This third harmonic is not a fixed value, but instead it must be calculated as a combination of third harmonic grid frequency and third harmonic output frequency. This value not only can only be obtained in presence of balanced supply voltages and balanced load, but also represents an intrinsic limitation [[Alesina and Venturini(1988)]] of the three-phase to three-phase matrix converter. In fact, the subsequent space-vector modulation (SVM) approach, proposed in [[Huber and Borojevic(1989)]] achieves the same voltage transfer ratio of  $\frac{\sqrt{3}}{2}$ .

The converter presented in this thesis was developed in conjunction with a new modulation approach presented in [[Pipolo and Formentini(2019)]] the Calvini Modulation, in which a new common-mode-voltage addition technique is exposed, which calculates the common-mode voltage components by taking into account the knowledge of output power demand , maintaining the same maximum VTR of 86.6%. However, this technique, when compared to the Venturini's method, enables the reduction of the commutation losses. At the very core, in fact, the Calvini modulation tries to always switch only between the two closest input phases. This also has the intuitive side effect of reducing the output ripple and current harmonic distortion.

### 2.2 The Calvini Modulation

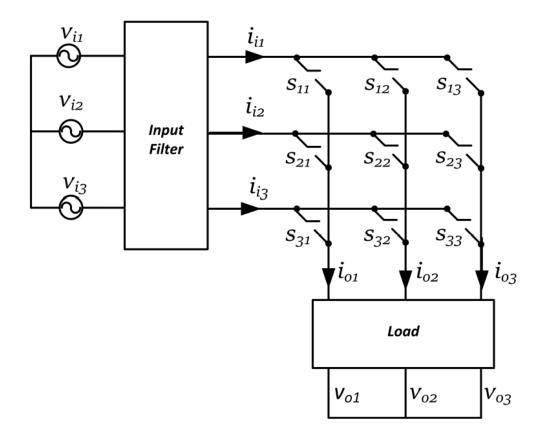

The detailed Calvini Modulation analysis is reported in the following section, as it was covered in [[Pipolo and Formentini(2019)]]. The electrical quantities under investigation are shown in Fig.2.1.

It is clear that, in every time instant, in a three phase system the three sinusoidal input waveforms will be at three different levels, except in an infinitesimal time lapse where two phases could be equal. This means that there will exist a phase with the highest voltage, a middle one, and the lower one.

Figure 2.1: Quantities under investigation in the Matrix Converter

We will assume that in a specific time instant :

$$v_{i1} > v_{i2} > v_{i3}$$

$v_{o1} > v_{o2} > v_{o3}$  (2.1)

As we said, it is our desire to obtain the output voltages starting from the closest input phase, and so, if we also assume that, in a certain moment

$$v_{o2}^* + v_o < v_{i2} \tag{2.2}$$

Where the asterisk denotes a reference quantity and  $v_o$  the common mode voltage to be injected.

Then, in order to obtain  $v_{o1}$  we will switch between  $v_{i1}$  and  $v_{i2}$ , while in order to obtain vo2 and vo3 we will switch between vi2 and vi3.

In the light of the above, it will hold true that

$$v_{o1} + v_o = d_{11}v_{i1} + d_{21}v_{i2} \tag{2.3}$$

Where  $d_{11}$  is the duty cycle associated with switch  $s_{11}$ ,  $d_{21}$  is the duty cycle associated with switch  $s_{21}$ , etcetera. Since it must always be that

$$d_{11} + d_{21} = 1 \tag{2.4}$$

we will then solve the system formed by 2.3 and 2.4 for the duty cycles obtaining

$$d_{11} = (v_{o1}^* + v_o - v_{i2})(v_{i1} - v_{i2})$$

$$d_{21} = (v_{i1} - v_{o1}^* - v_o)(v_{i1} - v_{i2})$$

(2.5)

In the same manner we can solve the two other systems formed by,

$$v_{o2} + v_o = d_{22}v_{i2} + d_{32}v_{i3}$$

$$d_{22} + d_{32} = 1$$

(2.6)

and

$$v_{o3} + v_o = d_{23}v_{i2} + d_{33}v_{i3}$$

$$d_{23} + d_{33} = 1$$

(2.7)

that result in

$$d_{22} = \frac{(v_{o2}^* + v_o - v_{i2})}{(v_{i2} - v_{i3})}$$

$$d_{32} = \frac{(v_{i1} - v_{o2}^* - v_o)}{(v_{i2} - v_{i3})}$$

$$d_{23} = \frac{(v_{o3}^* + v_o - v_{i3})}{(v_{i2} - v_{i3})}$$

$$d_{33} = \frac{(v_{i2} - v_{o3}^* - v_o)}{(v_{i2} - v_{i3})}$$

(2.8)

Also input currents can be expressed as function of duty cycles and output currents resulting in

$$i_{i1} = i_{o1}d_{11} \tag{2.9}$$

$$i_{i2} = i_{o1}d_{21} + i_{o2}d_{22} + i_{o3}d_{23} \tag{2.10}$$

$$i_{i3} = i_{o2}d_{32} + i_{o3}d_{33} \tag{2.11}$$

If we then substitute the aforementioned duty cycles in 2.9 we obtain

$$i_{i1} = \frac{i_{o1}(v_o + v_{i2} + v_{o1}^*)}{(v_{i1} + v_{i2})}$$

(2.12)

In order to ensure sinusoidal input currents, an input current reference can be defined. Equation 2.12 can then be solved for  $v_o$  resulting in

$$\mathbf{v}_{o}^{I} = \left(\frac{i_{i1}^{*}}{i_{o1}}\right)\left(v_{i1} - v_{i2}\right) + v_{i2} - v_{o1}$$

(2.13)

We can then calculate the input current reference  $i_{i1}^*$

by assuming unitary power factor and imposing a power balance between input and output

$$i_{i1}^{*} = P_{o}v_{i1}/V_{i}^{2} = (i_{o1}v_{o1}^{*} + i_{o2}v_{o2}^{*} + i_{o3}v_{o3}^{*})\frac{v_{i1}}{(v_{i1}^{2} + v_{i2}^{2} + v_{i3}^{2})}$$

(2.14)

If 2.2 does not hold true and we have instead

$$v_{o2}^* + v_o > v_{i2} \tag{2.15}$$

then, in order to obtain  $v_{o1}$  and  $v_{o2}$  we will switch between  $v_{i1}$  and  $v_{i2}$ , while in order to obtain  $v_{o3}$  we will switch between  $v_{i2}$  and  $v_{i3}$ .

Following that, we reapply the same steps and we find that in this case we have

$$d_{11} = \frac{(v_{o1}^{*} + v_{o} - v_{i2})}{(v_{i1} - v_{i2})}$$

$$d_{21} = \frac{(v_{i1} - v_{o1}^{*} - v_{o})}{(v_{i1} - v_{i2})}$$

$$d_{12} = \frac{(v_{o2}^{*} + v_{o} - v_{i2})}{(v_{i1} - v_{i2})}$$

$$d_{22} = \frac{(v_{i1} - v_{o2}^{*} - v_{o})}{(v_{i1} - v_{i2})}$$

$$d_{23} = \frac{(v_{o3}^{*} + v_{o} - v_{i3})}{(v_{i2} - v_{i3})}$$

$$d_{33} = \frac{(v_{i2} - v_{o3}^{*} - v_{o})}{(v_{i2} - v_{i3})}$$

(2.16)

$$i_{i1} = i_{o1}d_{11} + i_{o2}d_{12}$$

$$i_{i2} = i_{o1}d_{21} + i_{o2}d_{22} + i_{o3}d_{23}$$

$$i_{i3} = i_{o3}d_{33}$$

(2.17)

$$\mathbf{v}_o^{II} = (\frac{i_{i3}^*}{i_{o3}})(v_{i3} - v_{i2}) + v_{i2} - v_{o3}$$

(2.18)

$$i_{i3}^{*} = P_{o}v_{i3}/V_{i}^{2} = (i_{o1}v_{o1}^{*} + i_{o2}v_{o2}^{*} + i_{o3}v_{o3}^{*})\frac{v_{i3}}{(v_{i1}^{2} + v_{i2}^{2} + v_{i3}^{2})}$$

(2.19)

So, the common mode voltage from 2.13 must be added whenever 2.2 does hold true, and 2.18 must be added when 2.15 holds true.

## 2.3 Calvini Modulation VTR and operative range

With the assumption of studying a balanced three phase system (Fig.2.2), we can restrict the system analysis to a voltage input and output angle between  $\left[-\frac{\pi}{3}, \frac{\pi}{3}\right]$ , since the waveforms present a periodicity of  $\frac{2\pi}{3}$ .

Figure 2.2: Normalized three phase system

If we want 2.1 to hold true in a three phase system we can express it as

$$v_{i1} = V_i cos(\theta_i)$$

$$v_{i2} = V_i cos(\theta_i - \frac{2\pi}{3})$$

$$v_{i3} = V_i cos(\theta_i + \frac{2\pi}{3})$$

$$[0, \frac{\pi}{3}]$$

(2.20)

and

$$v_{i1} = V_i cos(\theta_i)$$

$$v_{i2} = V_i cos(\theta_i - \frac{2\pi}{3})$$

$$v_{i3} = V_i cos(\theta_i + \frac{2\pi}{3})$$

$$[-\frac{\pi}{3}, 0]$$

(2.21)

the same can be said for output reference voltages and output currents, which can be written in the following form

$$v_{o1}^{*} = V_{o}cos(\theta_{o})$$

$$v_{o2}^{*} = V_{o}cos(\theta_{o} \pm \frac{2\pi}{3})$$

$$v_{o3}^{*} = V_{o}cos(\theta_{o} \mp \frac{2\pi}{3})$$

$$i_{o1} = I_{o}cos(\theta_{o} + \phi_{o})$$

$$i_{o2} = I_{o}cos(\theta_{o} + \phi_{o} \pm \frac{2\pi}{3})$$

$$i_{o3} = I_{o}cos(\theta_{o} + \phi_{o} \mp \frac{2\pi}{3})$$

(2.22)

The reference current can be expressed as

$$i_{i1}^{*} = I_{i}^{*} \cos(\theta i)$$

$$i_{i2}^{*} = I_{i}^{*} \cos(\theta_{i} \pm \frac{2\pi}{3})$$

$$i_{i3}^{*} = I_{i}^{*} \cos(\theta_{i} \pm \frac{2\pi}{3})$$

(2.23)

Where  $I_i^*$  is obtained imposing power balance between input and output

$$I_i^* = \frac{I_o V_o \cos(\phi_o)}{V_i} \tag{2.24}$$

Now that we have an expression for all the voltages and currents, we can now replace them in 2.13 and 2.18, thus obtaining the expressions for the common mode voltages to be added

$$\mathbf{v}_o^I = \left(\frac{\cos(\phi_o)\cos(\theta_i)(\cos(\theta_i) - \cos(\theta_i \mp \frac{2\pi}{3}))}{\cos(\theta_o + \phi_o)} - \cos(\theta_o)\right) V_o + \cos(\theta_i \mp \frac{2\pi}{3}) V_i \quad (2.25)$$

$$\mathbf{v}_{o}^{II} = \left(\frac{\cos(\phi_{o})\cos(\theta_{i}\pm\frac{2\pi}{3})(\cos(\theta_{i}\pm\frac{2\pi}{3})-\cos(\theta_{i}\pm\frac{2\pi}{3}))}{\cos(\theta_{o}\pm\frac{2\pi}{3}+\phi_{o})} - \cos(\theta_{o}\pm\frac{2\pi}{3})\right)V_{o} + \cos(\theta_{i}\pm\frac{2\pi}{3})V_{i}$$

$$(2.26)$$

which are valid only if  $\left[-\frac{\pi}{6} < \phi < \frac{\pi}{6}\right]$ .

Now, we can evaluate the maximum voltage transfer ratio. The analysis is restricted to

$$\theta_o \in [0, \frac{\pi}{3}], \theta_i \in [0, \frac{\pi}{3}]$$

$v_{o2}^* + v_o^I < v_{i2}$

but it's applicable to all the other cases.

In this interval it follows that

$$v_{o1}^* + v_o^I < v_{i1} \tag{2.27}$$

$$v_{o3}^* + v_o^I > v_{i3} \tag{2.28}$$

Since we already know the expressions for all the voltages in 2.27 from 2.20, 2.22 and 2.25, we can rewrite the expression as

$$\sqrt{3}\left(\cos(\theta_i + \frac{\pi}{3})\right)\frac{\left(V_i\cos(\phi_o + \theta_o) + V_o\cos(\phi_o)\cos(\theta_i)\right)}{\cos(\phi_o + \theta_o)} < 0$$

(2.29)

being  $cos(\theta_i + \frac{\pi}{3})$  and  $cos(\phi_o + \theta_o)$  always positive in the aforementioned interval, we can rewrite it as

$$\frac{V_o}{V^i} < \frac{\cos(\phi_o + \theta_o)}{\cos(\phi_o)\cos(\theta_i)}$$

(2.30)

which is the expression of the VTR.

The maximum value of the VTR that respects 2.27 is then found numerically. By applying the same steps it can also be found the maximum VTR respecting 2.28.

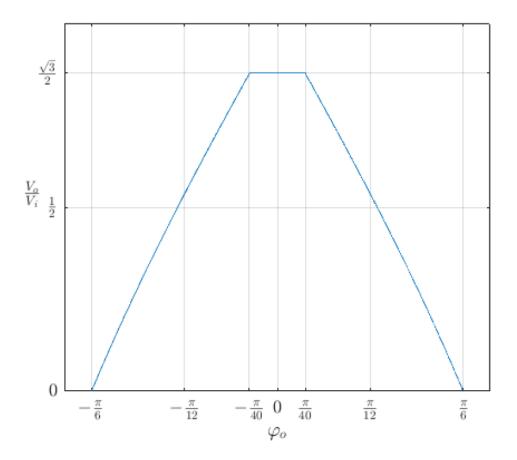

Thus said, for each angle  $\phi_o$ , the lowest VTR will be the one that can be obtained in order to obtain a balanced three phase output. In this way it is possible to obtain the Calvini Modulation operative range, which is reported in Fig. 2.3.

Figure 2.3: Voltage Transfer Ratio with Calvini modulation

It is evident that this new modulation technique is capable of obtaining the same VTR permitted by the Venturini's method, but the choice of always switching between the closest input phases narrows the output current displacement angle limits at which it is obtainable.

### 2.4 Hybrid Venturini-Calvini modulation

From the practical point of view, the Calvini Modulation is capable, when pushed to VTR limit, only of feeding an almost purely resistive load, and, in any cases, its VTR decreases very rapidly with the decrease of the output current power factor. In order to (partially) retain the advantages of the reduced switched voltage while extending its operative range, it was chosen to "assist" the Calvini's modulation with the Venturini's.

Basically the idea is to get the advantages of both modulations by adding the Calvini's common mode voltage were applicable, and then switching to the Venturini's one when outside of the Calvini's range. In particular, whenever the modulation is running and applied to the converter, it is necessary to switch to Venturini's modulation if the sum of the common mode voltage and the voltage reference, computed with the aforementioned method, exceeds the maximum (or the minimum) input voltage.

This means, however, that the switching losses obtained with this method depend somewhat from the load characteristics.

In the following chapter this intermediate modulation technique will be evaluated for usage in the converter in object.

# **Bibliography**

- [Alesina and Venturini(1988)] A. Alesina and M. Venturini. Intrinsic amplitude limits and optimum design of 9-switches direct pwm ac-ac converters. In PESC '88 Record., 19th Annual IEEE Power Electronics Specialists Conference, pages 1284–1291 vol.2, April 1988. doi: 10.1109/PESC.1988.18273.

- [Huber and Borojevic(1989)] L. Huber and D. Borojevic. Space vector modulator for forced commutated cycloconverters. In *Conference Record of the IEEE Industry Applications Society Annual Meeting*, pages 871–876 vol.1, Oct 1989. doi: 10.1109/IAS.1989.96746.

- [Pipolo and Formentini(2019)] S. Pipolo and A. Formentini. A new modulation approach for matrix converter. In 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia), pages 1021–1027, May 2019.

# **Chapter 3**

## **Top-Level converter design**

### 3.1 Matrix converter diffusion

At the current time, Matrix Converters did not receive the favors of the industry and are rarely seen outside the research laboratories. This can be due to the fact that they present a relatively complex topology when compared with the alternative solutions, and also due to the fact that, until now, they were not cost-competitive.

In fact, with regard to the mostly impacting components, in terms of economic costs, a matrix converter requires 18 power transistors and 18 power diodes, whether a back-to-back converter requires only 12 power transistors and 12 power diodes. However, as mentioned in the previous chapters, a matrix converter requires a small second-order input filter just to reduce the input current harmonic distortion, whether a back-to-back converter requires large input inductors and even larger DC-link capacitors.

Nowadays, the price of power semiconductors are steadily dropping year by year, while the costs of reactive elements is remaining stable. The author and his colleagues found that, at the start of the development of their matrix converter, the price for a back-to-back converter of the same power rating would have been comparable.

### **3.2** Commercial availability

The world's first commercial Matrix Converter, for the low voltage variable-frequency drives (VFDs) market, was manufactured by Yaskawa Electric in 2005 and presented with the name of "Varispeed AC", implemented with 1200V reverse-blocking Fuji IGBTs. The product was mainly advertised from Yaskawa for its bidirectional power flow capability and its performances in terms of total harmonic distortion.

One year later, in 2006, also Fuji Electric announced a Matrix Converter, presented under the name of "Frenic-MX", using, of course, their own semiconductors devices. Fuji, however, did not heavily advertise the product and retired it from its products portfolio shortly after. Currently Fuji does not sell Matrix Converters to the public.

Yaskawa Electric, on the contrary, extended their Matrix Converter product line in the medium voltage market (3.3kV to 6.6kV, 2.5MW to 5MW, obtained by means of interconnecting multiple three-phase Matrix Converters) and continued with the development and the improvement of its low-voltage drives, which peaked with the introduction of its latest U1000 Industrial Matrix Drive, which covers the 4 - 650kW power range.

Currently Yaskawa Electric its the only company which is present on the market with a Matrix Converter.

Figure 3.1: Yaskawa's U1000 family

## **3.3** Existing solution

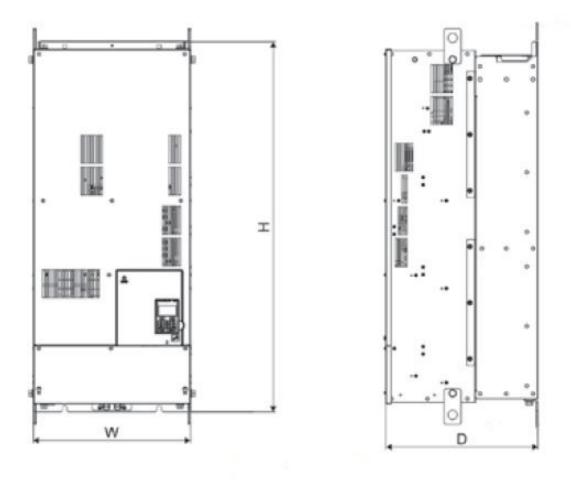

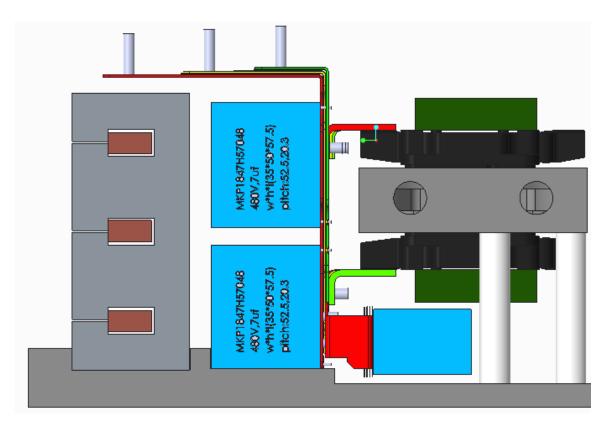

A good starting point for the development of the new device is the analysis of the mechanical dimensions of Yaskawa's U1000 0930AUB, a 560kW Matrix Converter. This converter's "all-out" dimensions, as reported from the datasheet in Fig.3.2, are roughly 1835mm[H]X1070mm[W]X445mm[D], for a total volume of  $0.873m^3$  and a total mass of 630kg, resulting in a power density of  $641\frac{kW}{m^3}$  and a volumetric power density  $0.888\frac{kW}{kg}$ .

Figure 3.2: Yaskawa's Matrix Converter outer dimensions

The Yaskawa's converter uses forced air cooling and switches up to at a frequency of 4kHz, for a maximum fundamental output frequency of 400Hz. It already includes the clamp unit for over-voltage protection inside the frame and accepts an input voltage as high as 480V with a nominal output current of 900A. However, U1000 0930AUB it does not include the PWM input filter EUJ711820M, which must be installed separately and which all out dimensions are roughly 1350mm[H]X700mm[W]X440mm[D], while its mass is 345kg. This means that the most significant converter data when assembled can be represented by those of Tab 3.1.

| Quantity                 | Value | U.M.             |

|--------------------------|-------|------------------|

| Rated power              | 560   | kW               |

| Total volume             | 1.289 | $m^3$            |

| Total weight             | 975   | kg               |

| Mass power density       | 434   | $\frac{kW}{m^3}$ |

| Volumetric power density | 0.667 | $\frac{kW}{kg}$  |

Table 3.1: Yaskawa's 560kW Matrix converter assembly data

No further construction details regarding this converter are known, neither the bandwidth of the current control loop.

### **3.4 Proposed solution**

#### 3.4.1 Overview

One of the goal of this thesis was to create a converter as small as possible, which could compete with the Yaskawa's solution in the 500kW power range. Furthermore, it was deemed necessary to give special care to the communication loop bandwidth, in order to decrease its delays that tend to decrease the bandwidth having in mind to develop a product ready for high-end single axis applications.

Considering these design constraints, as a first attempt it was decided that the converter would have been characterized by the following features :

- Input voltage from 380V<sub>rms</sub> to 480V<sub>rms</sub> (400V<sub>rms</sub> nominal)

- Nominal current 800A<sub>rms</sub>

- Water cooling, in order to maximize its power density

- Custom IGBT modules to enable a low leakage inductance layout

- Intelligent ad programmable gate driver with on-board fast acting protection systems and on-board measurements

- High-bandwidth fiber optic communication between gate drivers and control board

#### **3.4.2** Power quality and loss estimation

In chapter 2 we presented the Hybrid modulation technique, but before deciding if implementing it or not in our converter, a comparison with the traditional Improved Venturini's modulation is due.

To compare the power quality and the losses between the Venturini's modulation and the Hybrid modulation, it is necessary to choose a load that, for convenience, can be considered representative of a typical single-axis high power application, like a permanent magnet synchronous motor with stator inductance  $I_{rms} = 800A L_s = 100\mu H$ , stator resistance  $R_s = 0.24\Omega$  and top speed (in field weakening region)  $\omega_{max} = 3500rpm = 550rad/s$ .

This would result, at top speed, in having a  $cos\phi$  equal to

$$\phi = tan^{-1}\left(\frac{\omega_{max}L_s}{R_s}\right) = 0.16rad$$

which is a value valid for the Hybrid modulation since

$$0.52rad \cong \frac{\pi}{6} > \phi > \frac{\pi}{40} \cong 0.0785rad$$

After that, it is necessary to choose a non ideal IGBT, the same that will be then used for the converter's design in the following chapter, the IGC193T120T8RM from Infineon. A first-attempt switching frequency of 12kHz (for reactive elements evaluation) is then chosen on the basis of the criteria of having equal conduction and switching losses, if those would happen in a back to back converter. In addition, to drive these IGBTs, a commutation pattern must be chosen along with a feasible dead time, i.e. 4 step current commutation [[Deng(2014)]] and  $1\mu s$ .

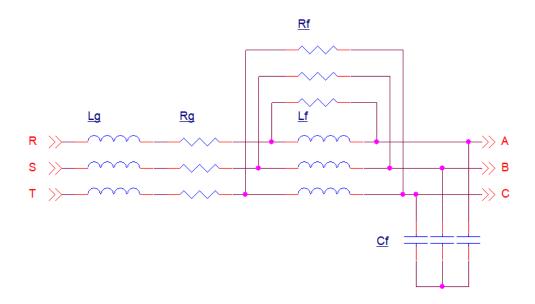

To evaluate the actual behavior of the converter, also an input filter must be considered. According to [[Trentin and Zanchetta(2012)]] it was chose to use a capacitance of  $300\mu F$ and a  $5\mu H$  line inductance with parallel damping resistor of  $500m\Omega$  assisted by the already available grid impedance, estimated to be around at least  $15\mu H$  in series with  $40m\Omega$ . This results in a filter configuration like the one that can be seen in Fig.3.3.

Figure 3.3: Proposed Matrix Converter line filter configuration

The VTR is then set to the maximum achievable value of  $\frac{\sqrt{3}}{2}$  in order to evaluate the worst-case conditions.

Usually the reason for increasing switching frequency is to reduce ripple and, consequently, harmonic distortion, in order to satisfy the requirements of the regulations on power quality. In the light of the above, a simulation in the MATLAB environment is then run comparing both the modulations for the same input current THD, which occurs at different switching frequencies. It must be noted that, whenever switching between the two modulations is not required, i.e. when it is possible to always compute the duty cycles with the Calvini's modulation technique, both Venturini's and Calvini's modulation obtain the same results in terms of distortion. However, this is not the case that was analyzed, and, due to the introduction of the "modulation switching" non linearity in the hybrid technique, the harmonic content is worsened. This means that with the hybrid technique it will be necessary to increase the switching frequency in order to obtain the same THD of the Venturini's modulation.

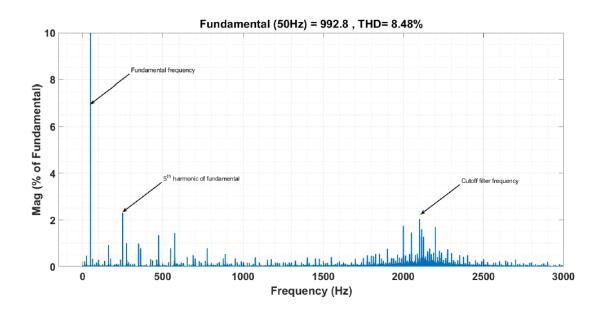

In Fig.3.4 it is shown the FFT of grid input current obtained with the Hybrid modulation, with a switching frequency of 10kHz for a THD% of 8.48%. It can be noted that the most relevant contribution to the THD% is located at the cutoff frequency of the input filter, while the highest harmonic introduced by the Hybrid technique is located at 5th harmonic of the fundamental frequency.

Figure 3.4: Simulation results of grid input current FFT with Hybrid modulation

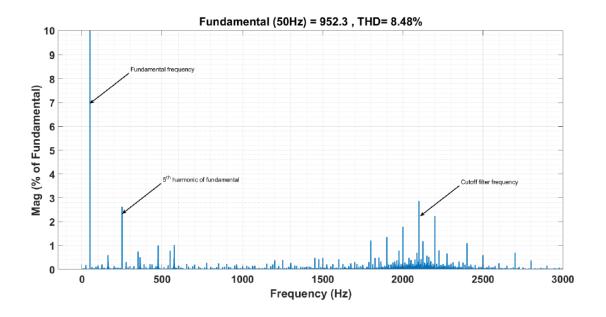

In Fig.3.5 it is shown instead the FFT of grid input current obtained with the traditional Venturini's modulation, which obtains the same THD of 8.48% with a switching frequency of 7.1*kHz*. Also for Venturini's modulation, the most relevant contribution to the THD% is located at the cutoff frequency of the input filter, with the highest harmonic due to the modulation itself located at 5th harmonic of the fundamental frequency.

Figure 3.5: Simulation results of grid input current FFT with Venturini's modulation

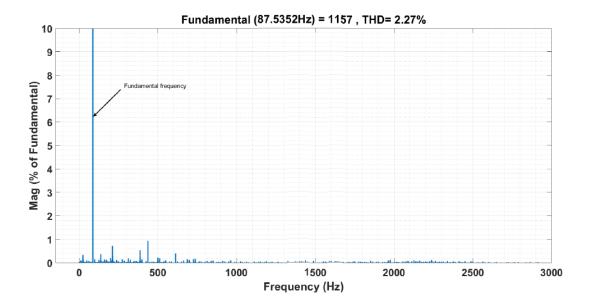

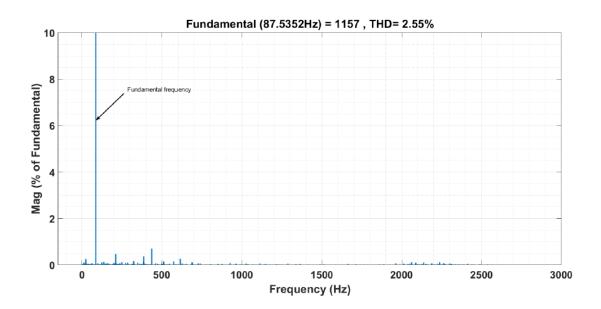

The output currents are then evaluated in the same operating points, and shown in Fig.3.6 and Fig.3.7. The two results are very close to each other, but it can be stated that the Hybrid modulation performs better in this terms. The main reason behind this lies into the higher switching frequency, which reduces the current ripple in the load.

Figure 3.6: Simulation results of output current FFT with Hybrid modulation

Figure 3.7: Simulation results of output current FFT with Venturini's modulation

Last, it is essential to evaluate the losses in the semiconductors with the two aforementioned modulation techniques, since they are needed to design the thermal management part of the converter.

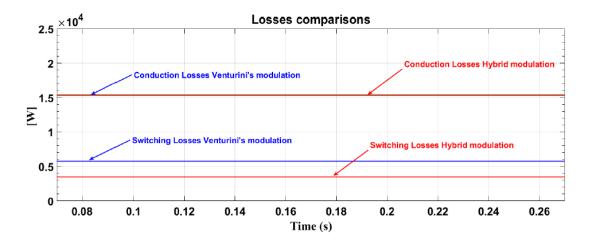

In Fig.3.8 is reported a comparison between both conduction and switching losses with the two different techniques. Since the current which feeds load is the same for both techniques, it does not surprise that the conduction losses are quite similar for both approaches. In fact, the type and number of devices simultaneously in conduction does not change between the two modulation strategies, with current flowing in two switches, i.e. two IGBTs and two diodes. On the contrary, since the proposed approach acts on the closest input voltages rather than of using all three phases voltages, the switching losses are significantly reduced. In the end, the new approach attains a 3.5 kW of switching losses versus 5.8 kW of traditional modulation, and so it was decided to use it in our converter.

Figure 3.8: Simulation results of the losses in the semiconductor devices

#### **3.4.3** Ratings and main components parameters

All this considered, it was evaluated convenient to split the machine in multiple 250kW modules, in order to cover different power sizes with the same product. Please note that from now on, if not made explicit, all the considerations regarding the converter will be related to the single  $400A_{rms}$  module.

| Quantity                       | Value | U.M.             |

|--------------------------------|-------|------------------|

| Nominal voltage                | 400   | V <sub>rms</sub> |

| Maximum working voltage        | 480   | V <sub>rms</sub> |

| Nominal output current         | 400   | A <sub>rms</sub> |

| Nominal maximum output voltage | 415   | V <sub>rms</sub> |

| Nominal Switching frequency    | 16    | kHz              |

| Maximum Switching frequency    | 32    | kHz.             |

| Maximum output frequency       | 2     | kHz.             |

Following the same process of section 3.4.2, the main electrical values were evaluated for the 250kW size and are presented in Tab 3.2 and Tab 3.3.

Table 3.2: Matrix Converter 250kW module ratings

| Name | Description                         | Value         |

|------|-------------------------------------|---------------|

| Lg   | Grid inductance (estimated)         | 15µH          |

| Rg   | Grid resistance                     | $40m\Omega$   |

| Lf   | Filter inductance                   | 10µ <i>H</i>  |

| Rf   | Filter damping resistor             | 1Ω            |

| Cf   | Filter phase-to neutral capacitance | 180µ <i>F</i> |

Table 3.3: Matrix Converter 250kW module filter parameters

# **Bibliography**

- [Deng(2014)] Y. Guo W. Deng. An improved 4-step commutation method application for matrix converter. In 2014 17th International Conference on Electrical Machines and Systems (ICEMS), pages 3590–3593, Oct 2014. doi: 10.1109/ICEMS.2014.7014112.

- [Trentin and Zanchetta(2012)] A. Trentin and P. Zanchetta. Automated optimal design of input filters for direct ac/ac matrix converters. *IEEE Transactions on Industrial Electronics*, 59(7):2811–2823, July 2012. ISSN 1557-9948. doi: 10.1109/TIE.2011. 2163283.

# **Chapter 4**

# **Converter design**

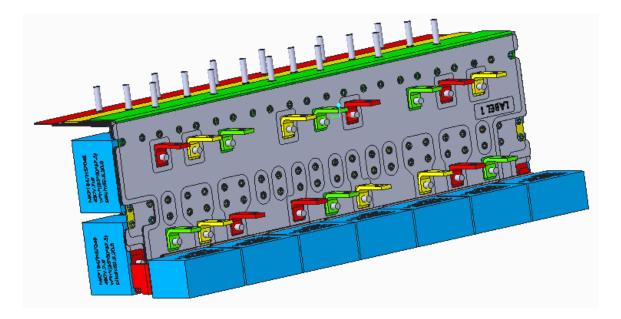

### 4.1 Overview

In the following paragraphs the principal design decisions will be presented. The converter can be divided mainly in two macro components, that is the power stage and the control system.

Anyways, our objective will be to optimize the converter as a whole entity, and not the single components, so many dimensioning criteria will be linked together.

### 4.2 **Power Stage**

#### 4.2.1 Power stage architecture

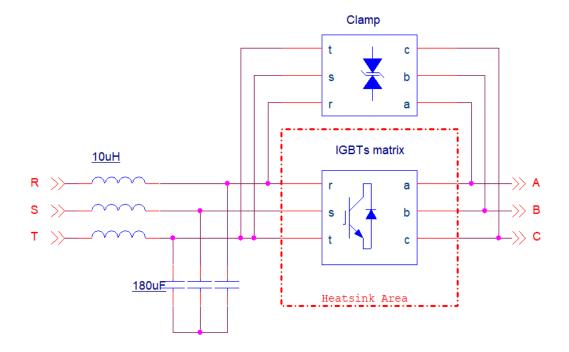

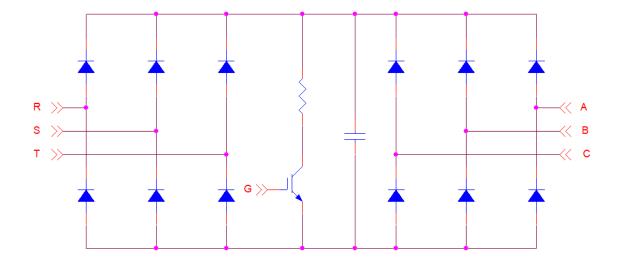

Figure 4.1: Power Stage high level schematic

Fig.4.1 is an high level schematic of the main power stage components that had to be designed for our converter. Please note that the Rf damping resistor is absent since it was chosen to incorporate it inside the inductor, as it will be explained later.

The power comes from the three-phase grid and passes through the L-C input filter, which is responsible for reducing the THD% induced in the grid.

After the filter we encounter the input side of the actual Matrix Converter, consisting in 9 bidirectional switches.

On the load side of the Matrix Converter we directly find the load with no further inductance added in series, since the load itself is typically inductive in its nature.

Last, a clamp unit is put in parallel with the load, and it also presents a connection with the input side of the Matrix Converter for system startup (details will be discussed further).

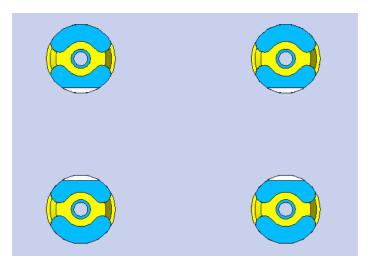

### 4.2.2 Matrix Converter layout

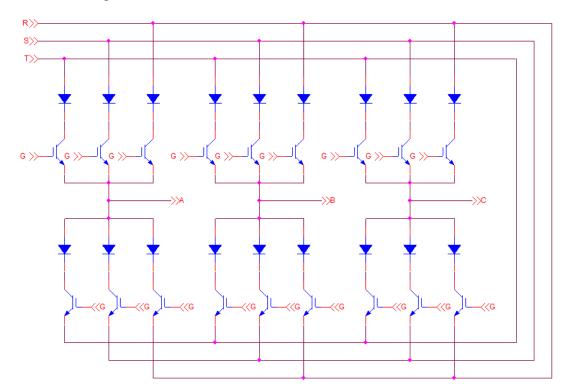

The first and most basic decision revolves around the actual semiconductor devices to be used in the Matrix Converter.

Due to the current. frequency and voltage levels of our converter, it was deemed necessary to create the bidirectional switches with the switch topology involving two IGBTs and two diodes.

Two custom modules were then produced by Semikron for this specific application, composed by three star-connected IGBTs, each in series with a diode, one module in common emitter configuration and one module in common collector configuration.

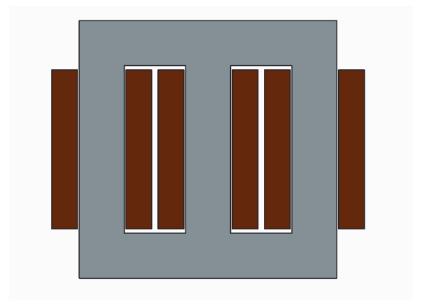

Figure 4.2: Semikron custom Matrix AXT and AXB modules

This unusual configurations, as we will discuss later, of course increases the number of isolated power supplies needed for the operation of the gate drivers, but also permits to fully exploit the internal space available inside of a standard Semix5 package.

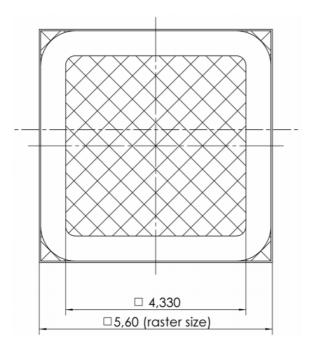

In actual fact, inside the module, each IGBT is composed by two paralleled Infineon IGC193T120T8RM IGBTs and each diode is composed by eight paralleled Infineon SKCD31C120I4F diodes. Fig.4.3 and Fig.4.4 show the dies of the aforementioned components, along with their most relevant mechanical dimensions.

Figure 4.3: IGC193T120T8RM die

Figure 4.4: SKCD31C120I4F die

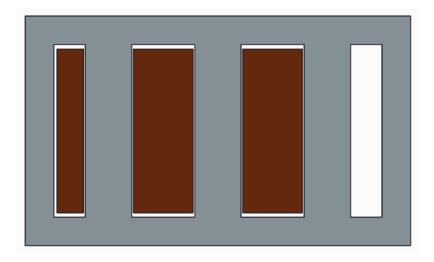

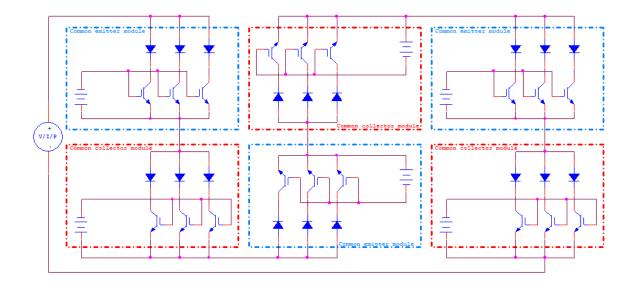

In the light of the above, to obtain the desired matrix topology, it is necessary to use a common emitter module and a common collector module per output phase, for a total of six modules (Fig.4.5).

Figure 4.5: Actual matrix topology obtained with Semikron's custom power modules

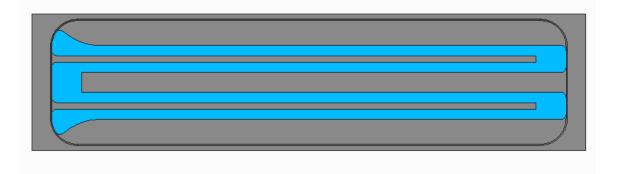

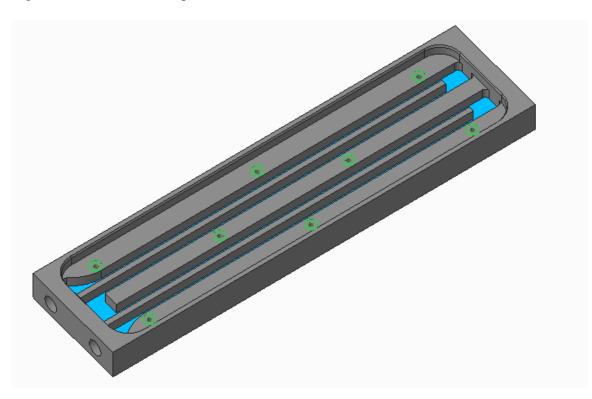

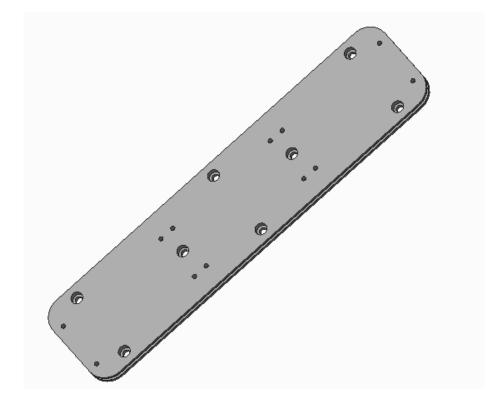

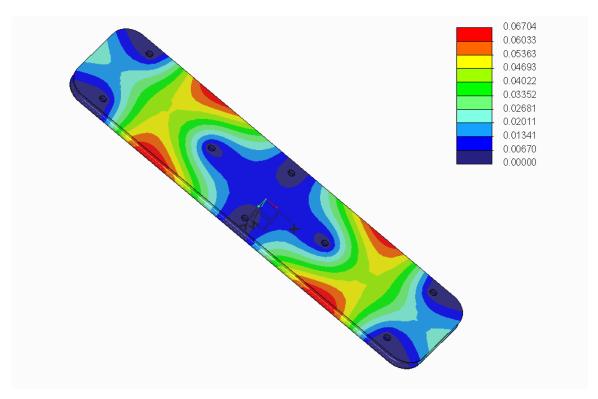

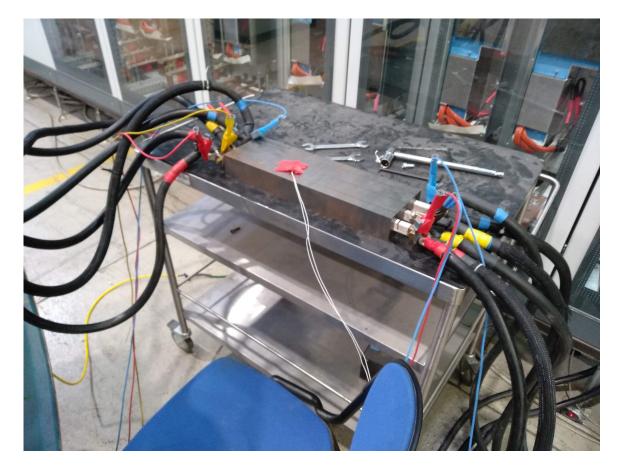

#### 4.2.3 Cold plate heat sink

Heat sinks, along with reactive elements, are usually among those components that are critical for the dimensions of a converter so, as mentioned in chapter 3, to obtain a high power density, it was chosen to use a water cooled plate, with mixture of water and ethylene glycol as coolant.

Due to the layout of the Semix5 modules, it was evaluated to be convenient to arrange them in a in-line, two layers fashion, with one layer formed by the common collector modules and the other formed by the common emitter ones. This way it was possible to cool the IGBTs with a single heat sink put in between the modules, and also to have the same output phases of the converter facing each other, thus simplifying the connections. For this same last reason, it was also decided to put the water inlet and outlets on the same heat sink surface.

The core of a water-cooled cold plate lies in the design of the coolant circuit, which, for a given flow rate, has the aim to decrease as much as possible the convective thermal resistance  $R_{th_{convective}}$  between the fluid and the surfaces of the ducts, all while obtaining a pressure drop  $\Delta p$  that should be as low as possible, since the flow losses, and so the work that has to be done by the plant's pumps, are proportional to it.

These two objectives, however, are in contrast to each other, since under the imposed constant flow rate condition :

$$R_{th_{convective}} \propto \frac{1}{u} \tag{4.1}$$

while

$$\Delta p \propto u^2 \tag{4.2}$$

where *u* is the velocity of the fluid. In general, for constant laminar flow rate

$$u \propto \frac{1}{A_w} \tag{4.3}$$

where  $A_w$  is the cross section of the duct.

However, another consideration that must be made is that, to reduce  $R_{th_{convective}}$  and to have an homogeneous temperature distribution, it is beneficial to cover all the possible surface available under the modules. If, in order to increase fluid velocity, we want to cover the same cold plate surface with a narrow channel with low  $A_w$ , the channel length has to increase, and so the pressure drop accordingly. So, what we see is that, in this specific design, (2) becomes

$$\Delta p \propto u^3 \tag{4.4}$$

To worsen this situation further, is must be also taken into account that, for the same reasons, a longer channel means an higher number of U turns, and so higher concentrated pressure drops. The system is strongly non-linear, but it is already clear from this surfacelevel analysis that it leans towards large and short water channels.

Last, a consideration from the manufacturing point of view: large and short channels can be realized with a limited number of passes of large milling tools.

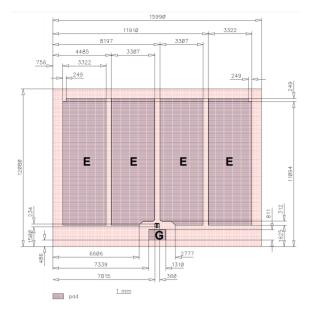

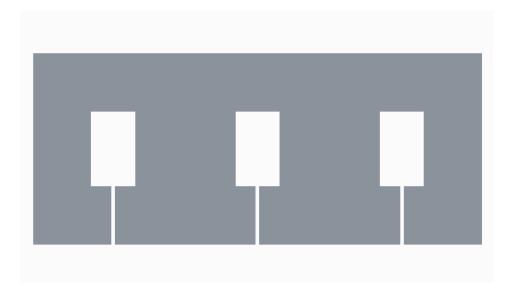

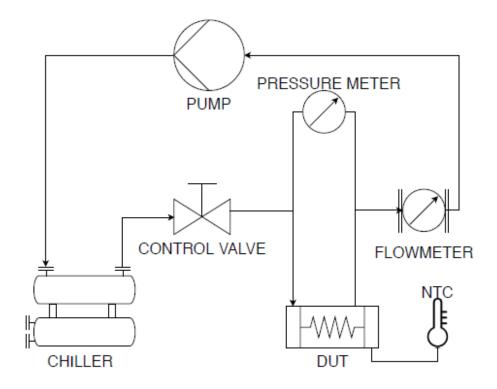

In the light of the above, the cooling circuit was iteratively designed and optimized with the aid of PTC Creo CAD software and Menthor Graphic FloEFD CFD tool. Table 4.1 contains the constraints and requirements used for the design process, while Fig.4.6 presents the resulting channel layout, where it can be noted a cross-section enlargement in the turns, to reduce the pressure drops.

Figure 4.6: Proposed coolant circuit layout

| Quantity                                   | Value | U.M.            | Source              |

|--------------------------------------------|-------|-----------------|---------------------|

| Heat generated per module                  | 1000  | W               | Loss analysis       |

| Target maximum surface temperature         | 75    | °C              | Semix5 thermal data |

| Nominal coolant flow rate                  | 2.78  | $\frac{m^3}{s}$ | Industry standard   |

| Target maximum pressure drop               | 30    | kPa             | Industry standard   |

| Target maximum channel-to-ambient pressure | 500   | kPa             | Industry standard   |

| Inlet fluid temperature                    | 40    | °C              | Industry standard   |

| Water/ethylene glycol ratio                | 1:1   | unitless        | Industry standard   |

Table 4.1: Heat sink design data

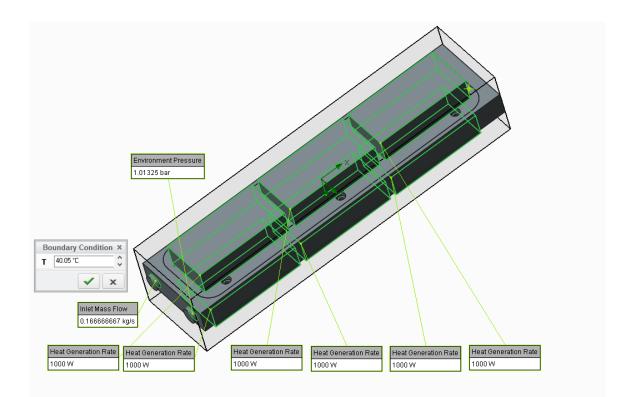

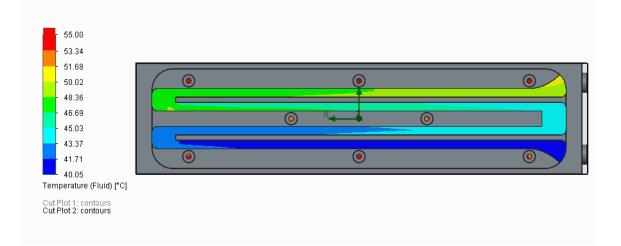

Figure 4.7: Cold plate CFD model with highlighted boundary conditions

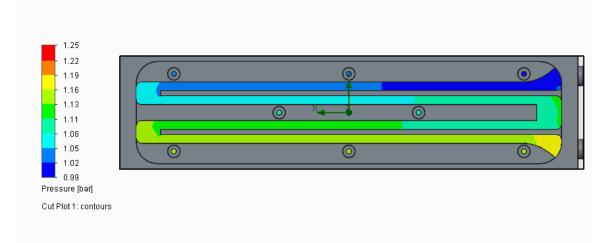

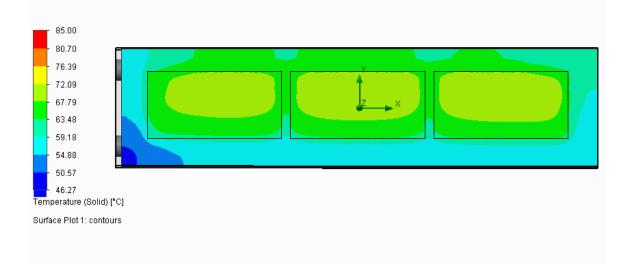

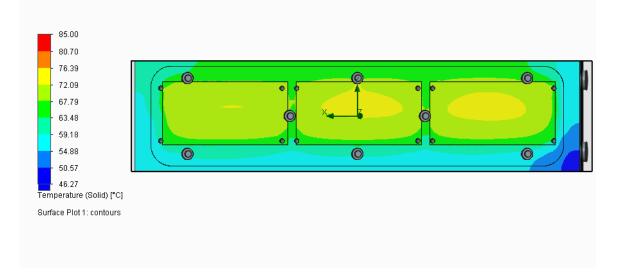

Fig.4.7 represents the model used in the simulation, along with its boundary conditions. To speed up the simulation, the Semix5 are not represented and are replaced with their thermal pad footprint, and neither gravity nor heat radiation were considered, since the former is not influential, while neglecting the latter is both conservative and only marginally influential. In Fig.4.8 it can be seen the fluid temperature distribution , while the static pressure distribution is presented in Fig.4.9. Fig.4.10 and Fig.4.11 show the temperature distributions of both the cold plate surfaces.

Figure 4.8: Coolant temperature distribution

Figure 4.9: Coolant static pressure distribution

Figure 4.10: Temperature distribution on the surface of the receptacle

Figure 4.11: Temperature distribution on the surface of the cover

Fig.4.12 and Fig.4.13 show the two parts that form the heat sink, and also highlight the o-rings positions, used for guaranteeing the water tightness up to the required maximum channel-to-ambient pressure.