# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

GENNARO SEVERINO RODRIGUES

# Approximate Computing Strategies for Low-Overhead Fault Tolerance in Safety-Critical Applications

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. Fernanda Kastensmidt Coadvisor: Prof. Dr. Alberto Bosio

Porto Alegre October 2019 Severino Rodrigues, Gennaro

Approximate Computing Strategies for Low-Overhead Fault Tolerance in Safety-Critical Applications / Gennaro Severino Rodrigues. – Porto Alegre: PGMICRO da UFRGS, 2019.

137 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2019. Advisor: Fernanda Kastensmidt; Coadvisor: Alberto Bosio.

1. Approximate Circuits. 2. Approximate-TMR. 3. Fault Tolerance. 4. Critical Systems. I. Kastensmidt, Fernanda. II. Bosio, Alberto. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# ABSTRACT

This work studies the reliability of embedded systems with approximate computing on software and hardware designs. It presents approximate computing methods and proposes approximate fault tolerance techniques applied to programmable hardware and embedded software to provide reliability at low computational costs. The objective of this thesis is the development of fault tolerance techniques based on approximate computing and proving that approximate computing can be applied to most safety-critical systems.

It starts with an experimental analysis of the reliability of embedded systems used at safety-critical projects. Results show that the reliability of single-core systems, and types of errors they are sensitive to, differ from multicore processing systems. The usage of an operating system and two different parallel programming APIs are also evaluated. Fault injection experiment results show that embedded Linux has a critical impact on the system's reliability and the types of errors to which it is most sensitive. Traditional fault tolerance techniques and parallel variants of them are evaluated for their fault-masking capability on multicore systems. The work shows that parallel fault tolerance can indeed not only improve execution time but also fault-masking. Lastly, an approximate parallel fault tolerance technique is proposed, where the system abandons faulty execution tasks. This first approximate computing approach to fault tolerance in parallel processing systems was able to improve the reliability and the fault-masking capability of the techniques, significantly reducing errors that would cause system crashes.

Inspired by the conflict between the improvements provided by approximate computing and the safety-critical systems requirements, this work presents an analysis of the applicability of approximate computing techniques on critical systems. The proposed techniques are tested under simulation, emulation, and laser fault injection experiments. Results show that approximate computing algorithms do have a particular behavior, different from traditional algorithms. The approximation techniques presented and proposed in this work are also used to develop fault tolerance techniques. Results show that those new approximate fault tolerance techniques are less costly than traditional ones and able to achieve almost the same level of error masking.

**Keywords:** Approximate Circuits. Approximate-TMR. Fault Tolerance. Critical Systems.

# RESUMO

Este trabalho estuda a confiabilidade de sistemas embarcados com computação aproximada em software e projetos de hardware. Ele apresenta métodos de computação aproximada e técnicas aproximadas para tolerância a falhas em hardware programável e software embarcado que provêem alta confiabilidade a baixos custos computacionais. O objetivo desta tese é o desenvolvimento de técnicas de tolerância a falhas baseadas em computação aproximada e provar que este paradigma pode ser usado em sistemas críticos.

O texto começa com uma análise da confiabilidade de sistemas embarcados usados em sistemas de tolerância crítica. Os resultados mostram que a resiliência de sistemas *singlecore*, e os tipos de erros aos quais eles são mais sensíveis, é diferente dos *multi-core*. O uso de sistemas operacionais também é analisado, assim como duas APIs de programação paralela. Experimentos de injeção de falhas mostram que o uso de Linux embarcado tem um forte impacto na confiabilidade do sistema. Técnicas tradicionais de tolerância a falhas e variações paralelas das mesmas são avaliadas. O trabalho mostra que técnicas de tolerância a falhas paralelas podem de fato melhorar não apenas o tempo de execução da aplicação, mas também seu mascaramento de erros. Por fim, uma técnica de tolerância a falhas paralela aproximada é proposta, onde o sistema abandona instâncias de execuções que apresentam falhas. Esta primeira experiência com computação aproximada foi capaz de melhorar a confiabilidade das técnicas previamente apresentadas, reduzindo significativamente a ocorrência de erros que provocam um *crash* total do sistema.

Inspirado pelo conflito entre as melhorias trazidas pela computação aproximada e os requisitos dos sistemas críticos, este trabalho apresenta uma análise da aplicabilidade de computação aproximada nestes sistemas. As técnicas propostas são testadas sob experimentos de injeção de falhas por simulação, emulação e laser. Os resultados destes experimentos mostram que algoritmos aproximados possuem um comportamento particular que lhes é inerente, diferente dos tradicionais. As técnicas de aproximação apresentadas e propostas no trabalho são também utilizadas para o desenvolvimento de técnicas de tolerância a falhas aproximadas. Estas novas técnicas possuem um custo menor que as tradicionais e são capazes de atingir o mesmo nível de mascaramento de erros.

**Palavras-chave:** Computação Aproximada, TMR aproximado, tolerância a falhas, sistemas críticos.

# LIST OF ABBREVIATIONS AND ACRONYMS

- ABFT Application-Based Fault Tolerance

- AMBA ARM Advanced Microcontroller Bus Architecture

- API Application Programming Interface

- ATMR Approximate Triple Modular Redundancy

- CDMR Conditional Double Modular Redundancy

- CMP Chip Multiprocessor

- COTS Commercial Off-The-Shelf

- CRC Cyclic Redundancy Check

- DD Displacement Damage

- DUT Design Under Test

- DVFS Dinamic Voltage and Frequency Scaling

- DWC Duplication With Comparison

- ECC Error Correction Code

- EDDI Error Detection by Duplicated Instructions

- FFT Fast Fourier Transform

- FI Functional Interruption

- FIM Fault Injection Module

- FIT Failure in Time

- FPGA Field-Programmable Gate Array

- HDL Hardware Description Language

- HLS High-Level Synthesis

- HPC High-Performance Computing

- ICAP Internal Configuration Access Port

- IC Integrated Circuit

- IP Intellectual Property

- LET Linear Energy Transfer

- MBU Multibit Upset

- MCU Multicell Upaset

- MSE Mean Square Error

- MWTF Mean Work To Fail

- NIEL Non-Ionizing Energy Loss

- NVP N-Version Programming

- OCM On-Chip Memory

- OpenMPOpen Multi-Processing

- OS Operating System

- **OVPSim OVP Simulator**

- PAED Parallel Approximate Error Detection

- PL Programmable Logic

- PS Processing System

- PSNR Peak Signal-to-Noise Ratio

- ROI Region of Interest

- RTCA Radio Technical Comission for Aeronautics

- SDC Silent Data Corruption

- SEB Single Event Burnout

- SEE Single Event Effect

- SEFI Single Event Functional Interrupt

- SEGR Single Event Gate Rupture

- SEL Single Event Latch-up

- SER Soft Error Rate

- SET Single Event Transient

- SEU Single Event Upset

- SHE Single Hard Error

- SIHFT Software-Implemented Hardware Fault Tolerance

- SoC System-on-a-chip

- TID Total Ionizinf Dose

- TMR Triple Modular Redundancy

- TPA Two-Photon Absorption

- UT Unexpected Termination

- $\mu$ SEL Micro Single Event Latch-Up

# LIST OF FIGURES

| Figure 2.1 Approximate computing classification                                                                     |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 3.1 Radiation effects in electronic devices                                                                  |

| Figure 4.1 The Zynq-7000 APSoC                                                                                      |

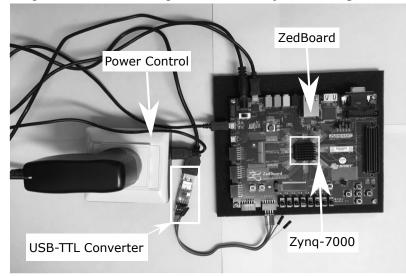

| Figure 4.2 Onboard register file fault injection setup view                                                         |

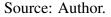

| Figure 4.3 Onboard fault injection emulation procedure flow                                                         |

| •                                                                                                                   |

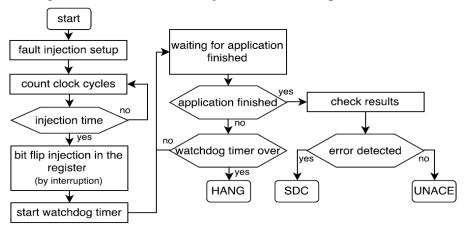

| Figure 4.4 Infrared microphotograph of the DUT core under test, showing the scanned areas (L1 Data Cache and OCM)   |

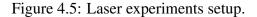

| Figure 4.5 Laser experiments setup                                                                                  |

| I gale 1.5 Daser experiments setup.                                                                                 |

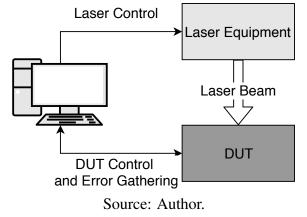

| Figure 5.1 Fault tolerance techniques classification                                                                |

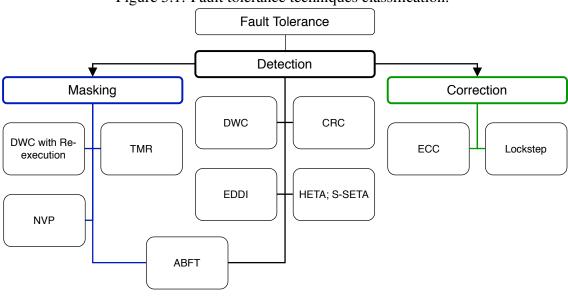

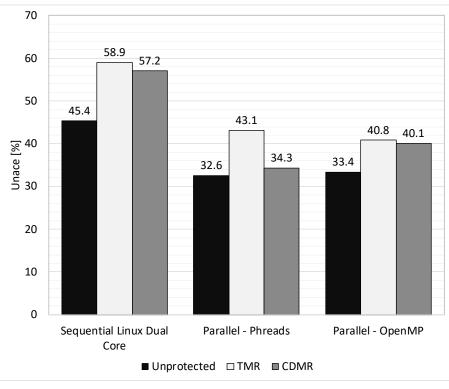

| Figure 5.2 Percentage of unaces on Vector Sum application running on top of Linux<br>OS                             |

| Figure 5.3 Percentage of unaces on Matrix Multiplication application running on top of Linux OS                     |

| Figure 5.4 Percentage of unaces on Bit Count application running on top of Linux<br>OS                              |

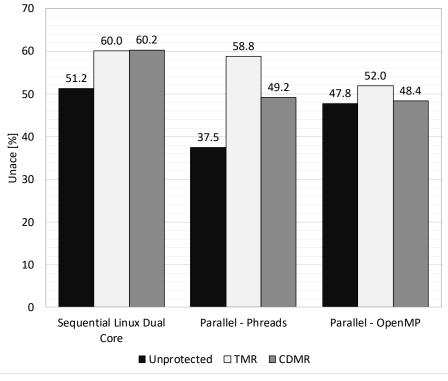

| Figure 5.5 Percentage of unaces on all algorithms running bare metal                                                |

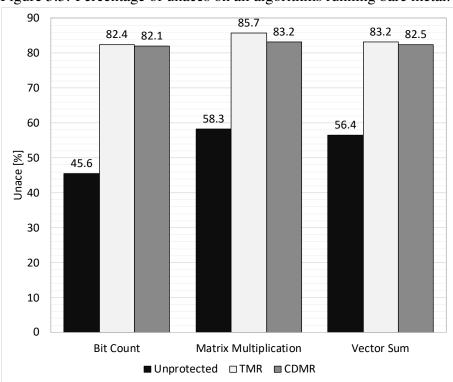

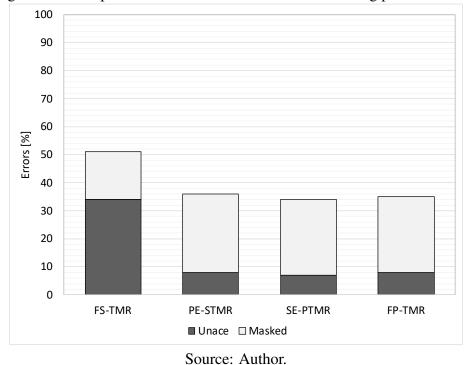

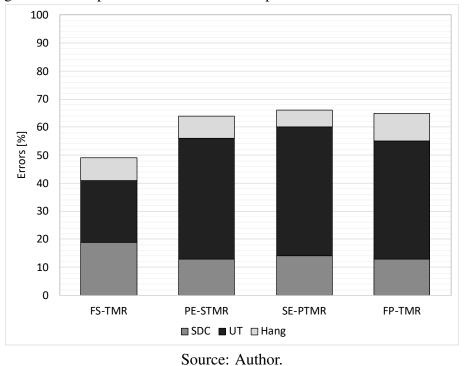

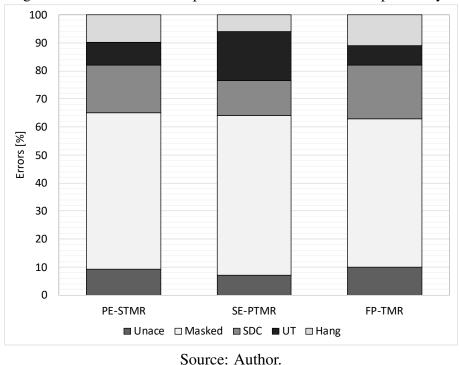

| Figure 5.6 Comparison between all the TMR fault masking performances                                                |

| Figure 5.7 Comparison between all the implementations error occurrence                                              |

| Figure 5.8 Parallel TMR implementations with thread disposability                                                   |

|                                                                                                                     |

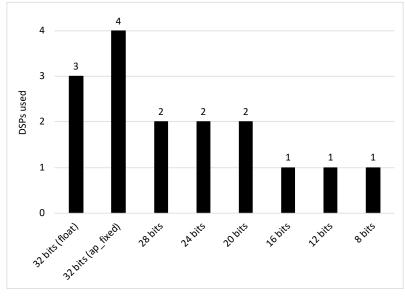

| Figure 6.1 DSP usage for multiplication using different data type configurations to represent floating point values |

|                                                                                                                     |

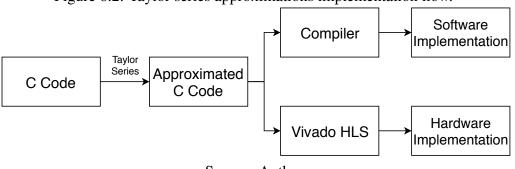

| Figure 6.2 Taylor series approximations implementation flow                                                         |

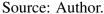

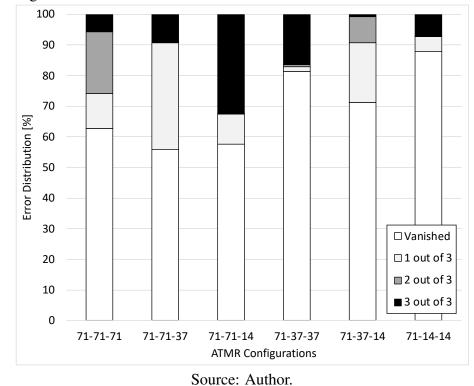

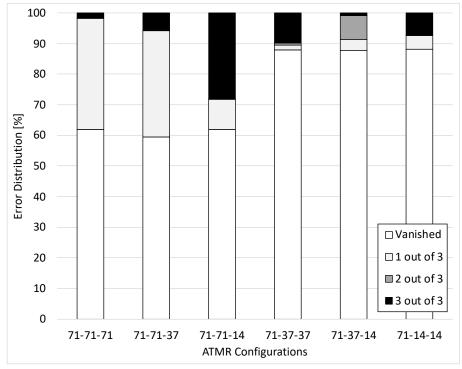

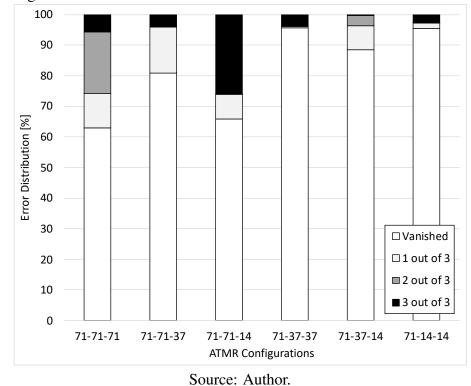

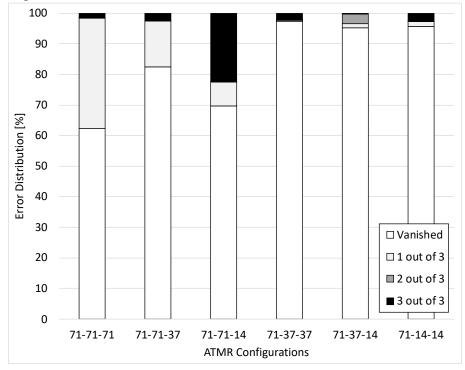

| Figure 6.3 Inaccuracy for each ATMR by data precision design applied to a $2 \times 2$ matrix multiplication        |

|                                                                                                                     |

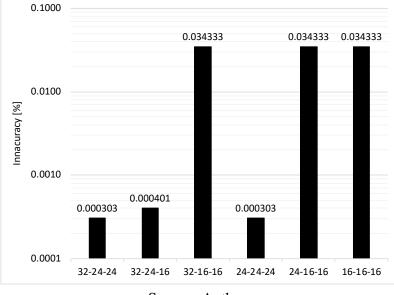

| Figure 6.4 Diagram of the proposed ATMR method                                                                      |

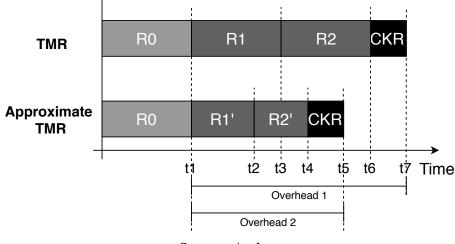

| Figure 6.5 Functional flow of the PAED technique                                                                    |

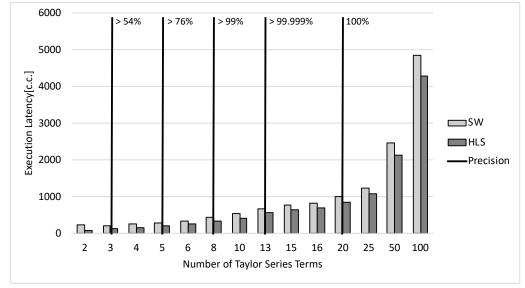

| Figure 7.1 Execution latency comparison between HLS without pipeline and SW                                         |

| (software) implementations for double-precision                                                                     |

| Figure 7.2 Execution latency comparison between HLS without pipeline and SW                                         |

| (software) implementations for single-precision (float type variables)91                                            |

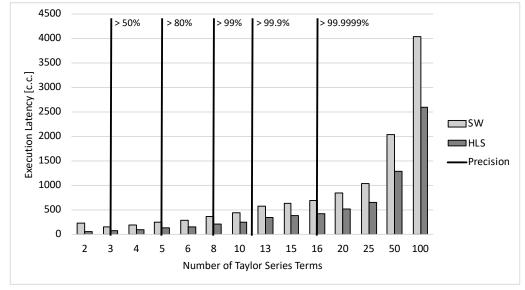

| Figure 7.3 Time comparison between HLS without pipeline and SW (software)                                           |

| implementations for both data precisions92                                                                          |

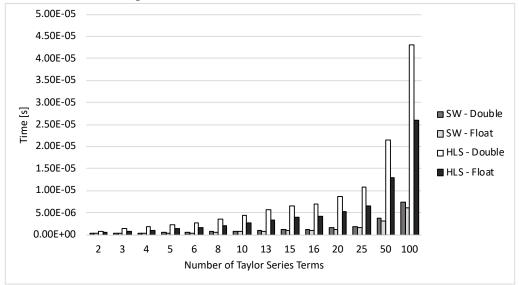

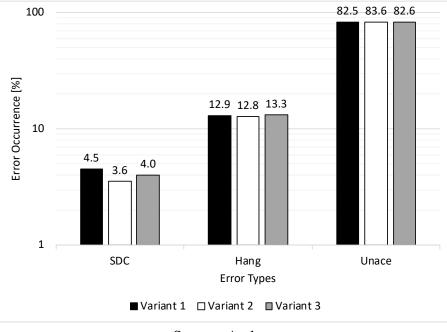

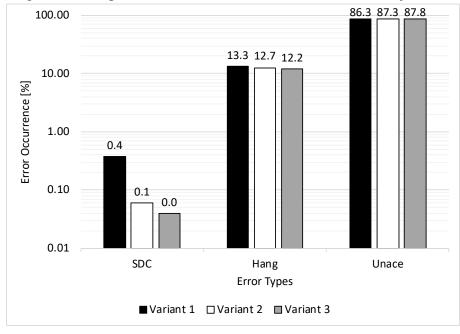

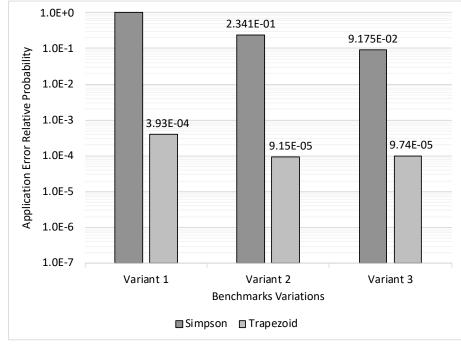

| Figure 7.4 Simpson error occurrence for emulation fault injection96                                                 |

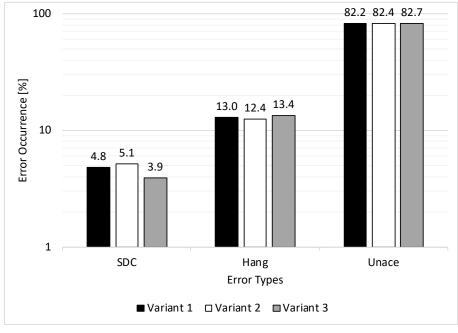

| Figure 7.5 Trapezoid error occurrence for emulation fault injection                                                 |

| Figure 7.6 Newton-Raphson error occurrence for emulation fault injection                                            |

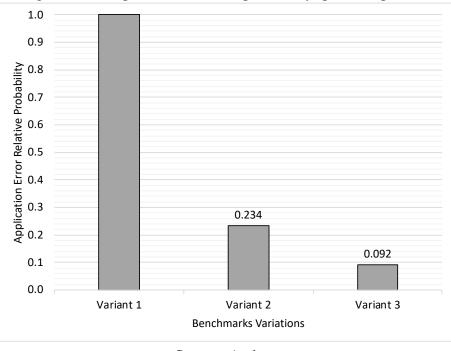

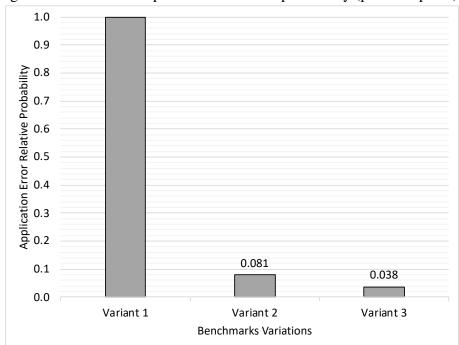

| Figure 7.7 Simpson error relative probability (per laser pulse)                                                     |

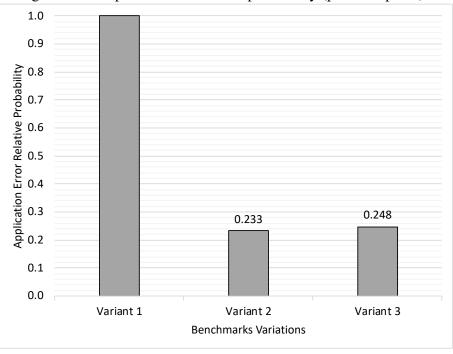

| Figure 7.8 Trapezoid error relative probability (per laser pulse)100                                                |

| Figure 7.9 Application error relative probability (per laser pulse) calculated for                                  |

| Trapezoid and Simpson together101                                                                                   |

| Figure 7.10 Newton-Raphson error relative probability (per laser pulse)101                                          |

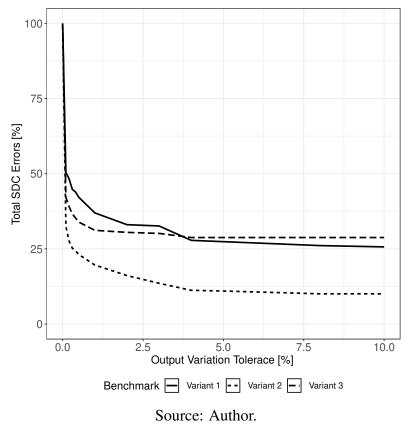

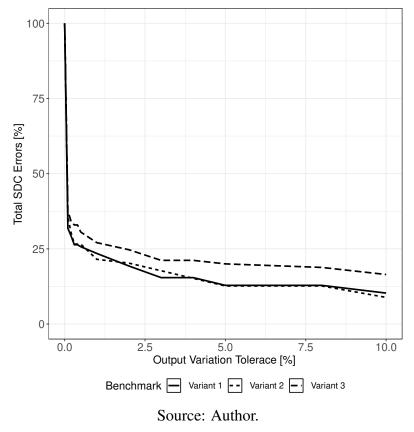

| Figure 7.11 Error occurrence drop in relation to output variation tolerance for Simp-                               |

| son benchmark102                                                                                                    |

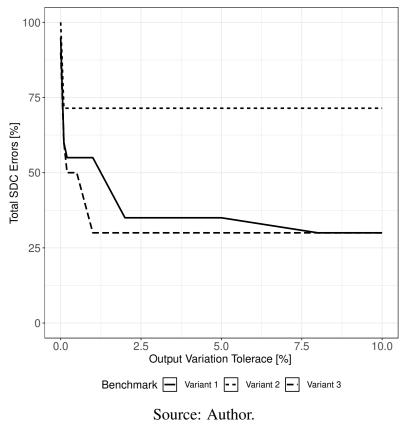

| Figure 7.12 Error occurrence drop in relation to output variation tolerance for Trape-<br>zoid benchmark                                                                                                | 03 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 7.13 Error occurrence drop in relation to output variation tolerance for Newton-                                                                                                                 |    |

| Raphson benchmark                                                                                                                                                                                       | 04 |

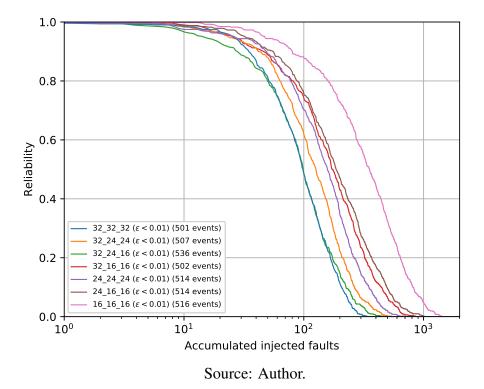

| Figure 7.14 Reliability for each ATMR configuration for an acceptance threshold                                                                                                                         | 00 |

| of 0.01                                                                                                                                                                                                 |    |

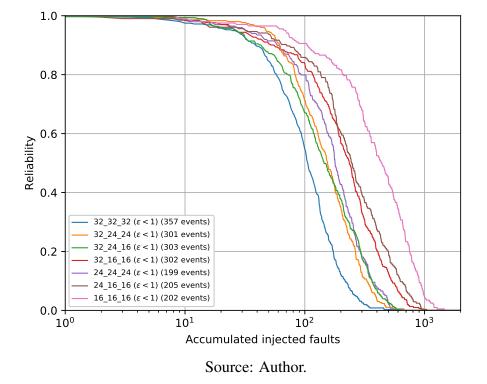

| of 1                                                                                                                                                                                                    | 10 |

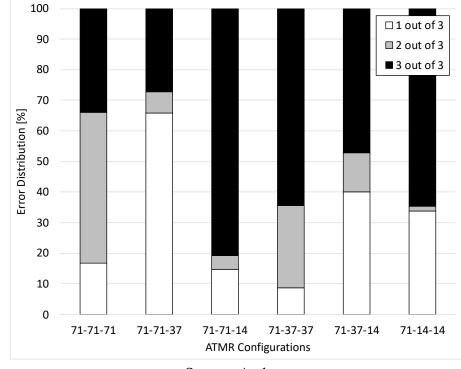

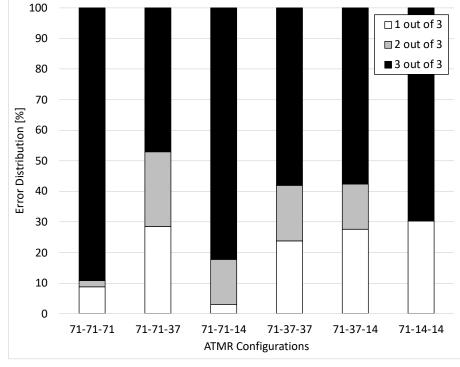

| Figure 7.16 Number of ATMR tasks with errors for a $\approx 0\%$ difference threshold<br>between the tasks outputs and golden value, on the single-precision version<br>of the Newton-Raphson algorithm | 13 |

| Figure 7.17 Number of ATMR tasks with errors for a 2% difference threshold be-<br>tween the tasks outputs and golden value, on the single-precision version of                                          |    |

| the Newton-Raphson algorithm. $1$ Figure 7.18 Number of ATMR tasks with errors for a $5\%$ difference threshold be-                                                                                     | 14 |

| tween the tasks outputs and golden value, on the single-precision version of the Newton-Raphson algorithm                                                                                               | 14 |

| Figure 7.19 Number of ATMR tasks with errors for a $\approx 0\%$ difference threshold<br>between the tasks outputs and golden value, on the double-precision version<br>of the Newton-Raphson algorithm |    |

| Figure 7.20 Number of ATMR tasks with errors for a 2% difference threshold be-<br>tween the tasks outputs and golden value, on the double-precision version of<br>the Newton-Raphson algorithm          | 16 |

| Figure 7.21 Number of ATMR tasks with errors for a 5% difference threshold be-<br>tween the tasks outputs and golden value, on the double-precision version of<br>the Newton-Raphson algorithm          | 16 |

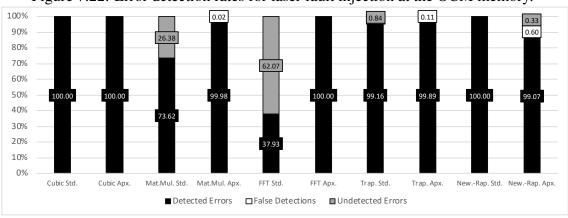

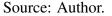

| Figure 7.22 Error detection rates for laser fault injection at the OCM memory1<br>Figure 7.23 Error detection rates for laser fault injection at the L1 data cache mem-                                 | 20 |

| ory1                                                                                                                                                                                                    | 20 |

# LIST OF TABLES

| Table 3.1 SEE classification and key characteristics                                     | 1 |

|------------------------------------------------------------------------------------------|---|

| Table 4.1 Error type classifications for simulated fault injections using OVPSim-FIM.42  | 2 |

| Table 4.2 Error type classifications for laser fault injections.    44                   |   |

| Table 5.1 Fault injection results in percentage of errors, running sequential appli-     |   |

| cations on single-core ARM Cortex-A9                                                     | 3 |

| Table 5.2 Fault injection results in percentage of errors, running sequential and        |   |

| parallel applications on dual-core ARM Cortex-A953                                       |   |

| Table 5.3 Performance overhead of fault-tolerance techniques.    59                      | 9 |

| Table 6.1 Performance and resource usage analysis from HLS hardware implemen-            |   |

| tation of Taylor series approximation                                                    | 5 |

| Table 6.2 Performance analysis from embedded ARM software implementation of              |   |

| Taylor series Approximation                                                              | 6 |

| Table 6.3 Area usage and performance latency of the ATMR by data reduction               |   |

| designs for $2 \times 2$ and $3 \times 3$ matrix multiplications                         | 1 |

| Table 6.4 Execution time overheads of ATMR configurations applied to the Newton-         |   |

| Raphson algorithm                                                                        | 3 |

| Table 7.1 Successive approximation experiments benchmarks details                        | 4 |

| Table 7.2 Laser fault injection details on successive approximation benchmarks           |   |

| Table 7.3 Error distribution for simulated fault injections using OVPSim                 |   |

| Table 7.4 Exhaustive onboard fault injection emulation results for a $2 \times 2$ matrix |   |

| multiplication                                                                           | 1 |

| Table 7.5 Error masking for each ATMR configuration variating thresholds                 | 7 |

| Table 7.6 Details of the benchmarks used to evaluate PAED                                | 8 |

| Table 8.1 Summary of results                                                             | 3 |

# CONTENTS

| 1 INTRODUCTION                                                     |     |

|--------------------------------------------------------------------|-----|

| 2 APPROXIMATE COMPUTING                                            | 19  |

| 2.1 Quality Metrics and Approximation Methods                      | 20  |

| 2.2 Technological Implementations                                  | 25  |

| <b>3 RADIATION EFFECTS ON ELECTRONIC DEVICES</b>                   | 27  |

| 3.1 Single Event Effects (SEE)                                     | 29  |

| 3.2 Total Ionizing Dose (TID)                                      | 31  |

| 3.3 Displacement Dammage (DD)                                      | 32  |

| 3.4 Analyzing Radiation Effects                                    |     |

| 4 ANALYSIS METHODOLOGIES                                           |     |

| 4.1 Onboard Fault Injection Emulation on FPGA                      | 35  |

| 4.2 Onboard Fault Injection Emulation on Embedded Processor        | 37  |

| 4.3 Fault Injection Simulation                                     | 39  |

| 4.4 Laser Fault Injection                                          |     |

| 5 EMBEDDED SYSTEMS FAULT TOLERANCE                                 |     |

| 5.1 Fault Tolerance                                                |     |

| 5.2 Parallel Embedded Software on Multicore Processors Reliability | 49  |

| 5.3 Parallel Fault Tolerance                                       | 59  |

| 5.4 Approximating Parallel Fault Tolerance                         |     |

| 5.5 Approximate Fault Tolerance: Discussion and Motivations        |     |

| 6 PROPOSED WORK                                                    |     |

| 6.1 Approximation Methods                                          |     |

| 6.1.1 Data Precision Reduction                                     |     |

| 6.1.2 Successive Approximation                                     |     |

| 6.1.3 Taylor Series Approximation                                  | 71  |

| 6.2 Approximate Triple Modular Redundancy (ATMR)                   |     |

| 6.2.1 Hardware ATMR based on Data Precision Approximation          |     |

| 6.2.1.1 Accuracy Assessment                                        |     |

| 6.2.1.2 Area Usage Assessment                                      | 79  |

| 6.2.2 Software ATMR based on Successive Approximation              |     |

| 6.3 Parallel Approximate Error Detection (PAED)                    | 84  |

| 7 EXPERIMENTAL RESULTS AND DISCUSSION                              |     |

| 7.1 Approximation Methods                                          | 87  |

| 7.1.1 Taylor Series Approximation                                  |     |

| 7.1.1.1 Hardware Implementation Analysis                           | 88  |

| 7.1.1.2 Software Implementation Analysis                           | 89  |

| 7.1.1.3 Discussion on the Software and Hardware Implementations    | 90  |

| 7.1.2 Successive Approximation                                     |     |

| 7.1.2.1 Fault Injection Emulation on Register File                 | 95  |

| 7.1.2.2 Laser Fault Injection on Data Cache Memory                 | 98  |

| 7.1.3 Behaviour and Application Evaluation on Operating Systems    | 104 |

| 7.2 Hardware ATMR                                                  |     |

| 7.2.1 Random Accumulated Fault Injection                           | 108 |

| 7.2.2 Exhaustive Fault Injection                                   |     |

| 7.3 Software ATMR                                                  | 111 |

| 7.4 PAED                                                           |     |

| 8 CONCLUSION                                                       | 122 |

| 8.1 Future Works                                                   | 125 |

| 8.2 Publications | 125 |

|------------------|-----|

| 8.2.1 Awards     | 128 |

| REFERENCES       | 129 |

# **1 INTRODUCTION**

Safety-critical systems must be extremely reliable. Those systems often deal with human lives or costly apparel; therefore, an error can be catastrophic. In recent years the industry has turned to commercial off-the-shelf (COTS) devices for their projects because of their relatively low cost and high performance. COTS, however, usually do not provide reliability, thus needing the implementation of fault tolerance techniques in order to be safely used for safety-critical systems development. Approximate computing has emerged as a computing paradigm capable of achieving good performances on execution time and energy consumption, as well as inherent reliability. However, it pays the price for it in precision loss and has to consider "good enough" results as acceptable (i.e., near the expected traditional computation output). Using approximate computing on safetycritical systems could improve their performances while also making them inherently more reliable. However, it can be conflicting with some of the safety-critical systems requirements, such as accuracy.

Factors such as power efficiency and execution performance are of great importance for embedded systems, and can be improved through approximate computing (HAN; ORSHANSKY, 2013). The approximate computing paradigm works with the idea that most applications are able to tolerate some flexibility in the computed result, based on a quality threshold specified by the application requirements. Indeed, several algorithms can present a *good enough* result even when executing inexact computations. An image processing algorithm, for example, might be able to tolerate some variations in the output quality, given the fact that the human eye is not able to perceive small differences between images. Such an algorithm might therefore skip some computation in order to execute faster and have a lower memory footprint, causing an acceptable degradation on the output image. In that context, approximate computing has been proposed as a means to provide computational resources savings, alongside with execution time and energy consumption improvements, with controlled quality degradation. Approximate computing techniques can be applied on every level of the computational stack, from circuit and hardware to embedded software. Those techniques (VENKATARAMANI et al., 2015) have been used in many scenarios, from big data to scientific applications (NAIR, 2014).

The literature presents a plethora of approximation strategies, both for software and hardware. The loop-perforation technique is an excellent software approximation example, being able to achieve useful outputs while not executing all the iteration of an iterative code (SIDIROGLOU-DOUSKOS et al., 2011). Indeed, the authors claim this approach typically delivers performance increases of over a factor of two while introducing an output deviation of less than 10%. Another approximation technique for software applications consists of reducing the bit-width used for data representation (RUBIO-GONZALEZ et al., 2013), also achieving a better execution speed than their non-approximate counterparts. Hardware-based approximation techniques usually make use of alternative speculative implementations of arithmetic operators. An example of this approach is the implementation of variable approximation modes on operators (SHAFIQUE et al., 2015). Hardware approximation is also present in the image processing domain in the form of approximate compressors (MOMENI et al., 2015).

The quality degradation inherent to approximate computing is, however, not to be forgotten. Although some quality degradation is acceptable for image processing algorithms, as exemplified before, it might not be acceptable for high dependability systems. A 10% quality degradation on an image might pass by unperceived, but an error of 10% in a banking system that computes the profits and taxes from a conglomerate will indeed be a severe problem. Even the perfect example of acceptable quality degradation (image processing) calls for an in-depth analysis on the acceptance lever for that degradation: surely no graphics processing units manufacturer wants to be known as the one which provides low-quality graphics in a very fast frame rate.

Safety-critical applications are an excellent example of a category on which approximate computing can indeed bring good fruits but are of delicate implementation. Applications defined as safety-critical deal with human lives and high-cost equipment, and therefore call for high dependability, i.e., low error rates. Safety-critical systems such as aerospace and avionics applications are often exposed to space radiation. Indeed, even systems that operate at ground level can be subject to space radiation (BAUMANN, 2005), and some of those are also categorized as safety-critical systems (e.g., self-driven cars and their collision avoidance algorithms).

Radiation effects in semiconductor devices vary from data disruptions to permanent damage. The state of a memory cell, register, latch, or any part of the circuit that holds data can be changed by a radiation event. Single radiation events might cause *soft* or *hard* errors. Soft errors are the primary concern for commercial applications (POIVEY et al., 2003) and occur when this radiation event is strong enough to change the data state without permanently damaging the system (TYLKA et al., 1996), manifesting as many types of errors. In software applications, those errors can be categorized into two major groups: SDCs (silent data corruption) and FIs (functional interruption) (HSUEH; TSAI; IYER, 1997). An SDC occurs when the application finishes properly, but its final memory state differs from the expected gold state. FIs are considered when the application hangs or terminates unexpectedly. Hard errors are permanent damages to the system and are often related to dose-rate radiation effects (i.e., associated with the accumulation of radiation and its impacts on the behavior of the transistor).

The new transistor technologies' reduction of the dimensions and operation thresholds have improved their energy consumption and performance. Their sensitivity to radiation, however, is often not a concern for the industry that focuses their efforts on higher transistor density and functionality at low cost. Indeed, the reduction of the transistor sizes on new technologies can now lead to radiation-induced faults, that would otherwise occur on space environments, to occur at ground level (TAUSCH et al., 2007). Although those fault-induction-related issues are not a significant concern for the traditional consumer, which can accept sparse little errors, they are indeed a severe concern for safety-critical systems.

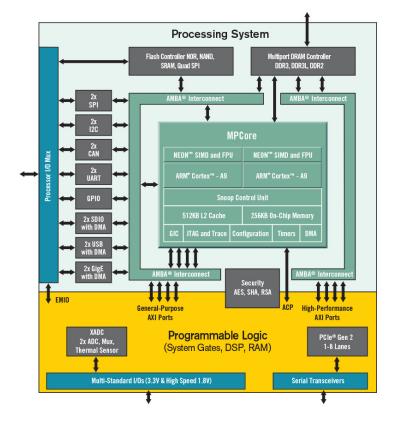

The traditional hardware manufacturers are not motivated to develop new radiationhardened technologies because of their high development cost and, consequently, lowprofit margin due to limited application (BAUMANN, 2005). On the other side, the safety-critical industry is also often not interested in radiation-hardened hardware, which is expansive and does not provide the same performance as the state-of-the-art hardware devices. The industry has turned to COTS (commercial off-the-shelf) embedded processors and systems-on-a-chip (SoC) combined with fault tolerance techniques (PIGNOL, 2010). COTS are typically low cost, very flexible, and consume little power. They do not provide, however, inherent fault tolerance (apart from traditionally used methods such as memory error correction codes, which alone does not provide all the reliability required for safety-critical systems), and therefore call for hardware- and software-based fault tolerance techniques to provide reliability. The Zynq<sup>TM</sup>-7000 All Programmable SoC (KADI et al., 2013), for instance, is an example of COTS system composed of two ARM processor cores and a field programmable gate array (FPGA) that is capable of serving a wide range of safety-critical applications, such as avionics communications, missile control, and smart ammunition control systems. COTS devices provide a myriad of system configuration parameters, which may directly affect fault tolerance.

Fault tolerance can be applied at the hardware level by duplicating or triplicating an entire component and adding voters and checkers that verify the consistency of the processed data. Those techniques, however, introduce a prohibitive area and power overhead. Software-based fault tolerance does not need extra hardware and is widely presented and discussed in the literature (SAHA, 2006; OSINSKI; LANGER; MOTTOK, 2017). In that case, redundancy is applied at the task level and executed in single or multiple processing cores. Although software-based techniques may present no hardware area overhead, it pays the cost on execution time and memory footprint, as well as energy consumption (that derive from those). One example of a fault tolerance mechanism that can be applied to both hardware and software is duplication with comparison (DWC), which duplicates the application and implements a checker to compare any discrepancy between the data generated by the two independent executions. DWC is capable of finding errors, but not masking them. A third execution would be needed to mask the error, making a vote for the correct data possible.

Concerning fault tolerance, approximate computing can mask a higher number of errors by relaxing data precision requirements. On systems that do not need high accuracy or quality, the approximation can be used because the small errors it introduces are not big enough to be considered a problem. Besides, the execution time reduction attained by approximate computing can improve an application reliability by reducing its exposure time: it is evident that an application that executes faster will be subject to less radiation, and therefore less to radiation-induced faults. SoCs arise as perfect implementation platforms for approximate computing. Industry-leading companies offer SoC presenting both an FPGA logic layer (PL) and an embedded processor as a processing system (PS), such as the aforementioned Zynq<sup>TM</sup>-7000 All Programmable SoC. Approximate computing projects can profit from the hardware-software co-design made available from COTS systems to implement any level of approximation, or as means of co-processing. Indeed, as will be further detailed, many approximation techniques consist of executing on programmable hardware approximate versions of standard functions that would otherwise be executed on hardcore microprocessors.

This work investigates the use of approximate computing on safety-critical systems. The approximate computing paradigm can be used to achieve several fundamental requirements of embedded safety-critical systems, such as low power consumption and high performance. Those, however, are achieved at the cost of precision and accuracy, which are serious concerns regarding critical applications. Another significant point of interest is reliability: approximation methods shall be able to tolerate errors or at least support traditional fault tolerance techniques. Therefore, it is essential to study not only the improvements approximate computing can bring to a project, but also its costs, and how it affects the dependability of those projects.

Approximation is presented in this work applied at the hardware and software level. On hardware projects, the techniques are implemented in hardware description language (HDL) with and without the aid of high-level synthesis. In a first analysis, the implementation cost and precision loss of approximation methods are assessed. Then, they are subject to fault tolerance analysis by fault injection experiments. Those experiments are intended to evaluate both the approximation fault tolerance by itself and the efficacy of traditional fault tolerance mechanisms when applied to an approximate application. Alternatively, novel approximate fault tolerance techniques, based on the traditional ones, are proposed and evaluated. The proposed techniques intend to provide fault coverage close to the traditional ones but at lower costs.

The fault injections are performed in four different methodologies: fault injection emulation, fault injection simulation, and laser and heavy-ion radiation experiments. Each one of those methodologies serves better for a specific evaluation purpose. The fault injection emulation on programmable hardware, for example, can be used to evaluate the behavior of the design under a situation of cumulative faults, in an effort to find out on which point (given the number of accumulated injected faults) the design begins to present errors. It can also be used to perform exhaustive studies on programmable hardware, to find out which bits of the bitstream used to program the FPGA are critical (i.e., a bit-flip on this bit will provoke errors). On the other hand, fault injection simulation can be used to inject faults on the register file of the processor to analyze which are the most critical registers and how faults affecting the register file propagate to become errors in a given context.

The work will start by presenting an overview and the state-of-the-art of the primary subject of the thesis: approximate computing. The first chapter is a survey with discussions over the approximation techniques most present at the literature, their impacts on the system that implement them, and how they can be applied to all the computation stacks. Following, the text presents an overview of radiation effects on electronic devices: the types of faults that the devices are subject to, their source, and how they affect the system becoming errors. The work then follows by a chapter that covers the methodologies that are used in this work and their peculiarities.

As an introductory discussion on the findings and to develop the justification of the proposals of this work, this work analyses the reliability of embedded systems, especially

embedded microprocessors. This chapter will develop a discussion on fault tolerance techniques and discuss the reliability of applications running bare-metal and on top of both Linux and FreeRTOS operating systems. It will also evaluate the reliability of parallel algorithms running on top of multicore processors, with different parallelization APIs. All that is essential to the development of the rest of the thesis, because it defines the basis of our theory: before evaluating the impact of approximation on reliability, it is fundamental to understand the need for fault tolerance of the systems that will be approximated, and the fact that they have characteristics independent from approximation.

The following chapters then present the approximation methods proposed by this work, as well as the developed approximate fault tolerance techniques and how they corelate. The results are then presented, categorized by every different methodology used to evaluate each technique. The work concludes by presenting the final conclusions and discussing how the present research will be expanded in future works.

The document is organized in the following chapters:

Chapter 1, Introduction: this chapter, presenting the introduction of the works.

**Chapter 2, Approximate Computing:** presents the state-of-the-art of the approximate computing, as well as how it motivates the work.

**Chapter 3, Radiation Effects on Electronic Devices:** presents the radiation effects on electronic devices, their sources and effects on the system.

**Chapter 4, Analysis Methodologies:** details the methodologies used to evaluate the proposed approximate computing and approximate fault tolerance techniques.

**Chapter 5, Embedded Systems Fault Tolerance:** discusses state-of-the-art fault tolerance techniques and how they relate and motive this work. Also presents a practical introduction on the reliability of embedded systems.

**Chapter 6, Proposed Work:** proposes approximation methods and approximate fault tolerance techniques.

**Chapter 7, Experimental Results and Discussion:** presents experimental results of the proposed techniques and discusses them.

**Chapter 8, Conclusion:** presents the conclusions and the ideas for expanding the research. Also presents the list of publications that originated from this work.

## **2 APPROXIMATE COMPUTING**

Approximate computing has been proposed as an approach for developing energyefficient systems (HAN; ORSHANSKY, 2013), lowering hardware resources usage and presenting better execution times, and has been used in many scenarios, from big data to scientific applications (NAIR, 2014). It can be achieved from a multitude of ways, ranging from transistor-level design to software implementations. Many systems do not take precision and accuracy as an essential asset. Those are the ones that can profit from this computational paradigm (XU; MYTKOWICZ; KIM, 2016). An example of this type of application is real-time systems, which have very strict deadlines and require strong performance. The approximation can also be unavoidable. Floating-point operations, for instance, have frequent rounding of values, making it inherently approximate. Numerical algorithms are also frequently of approximate nature: the calculation of an integral, for example, is not natural for a computer, and consists of an iterative calculation of a finite sum of terms (and not an infinite one, as the mathematical theory defines it).

Even on systems where quality and accuracy are essential, the mere definition of a good quality result can be malleable. On image processing, for example, the final output is evaluated by a human perspective (the quality of the image). This perspective is subjective: some people are more capable of analyzing the quality of an image than others, and the definition of a "good enough" quality is even more debatable. Typical error-resilient image processing algorithms can indeed accept errors of up to 10% (RAHIMI et al., 2015), which would be unacceptable for a military system calculating the trajectory of a ballistic projectile, for example. This margin of error acceptance can be exploited to improve energy consumption and execution performance.

The weak definition of "error acceptance" can also be used by approximate computing for quality configuration. Given that different systems have different quality requirements, a designer might make use of just the necessary energy, hardware area, or execution time, to meet the needs of his project. An excellent example of how a circuit can be configured in that manner is by using different refresh rates for memories (CHO et al., 2014), or different precision for data storage and representations (TIAN et al., 2015). The image processing domain is particularly interesting because it is an example of how approximation can be implemented on different levels. A minor loss in precision can be accepted by applying approximation via hardware, by reducing the refresh rates of eDRAM/DRAM and the SRAM supply voltage, which reduces the energy consumption (MITTAL, 2014). On a higher level of implementation, the approximation can be used by loop-perforation (finishing a loop execution earlier than expected) (SIDIROGLOU-DOUSKOS et al., 2011) or by executing specific functions on neural accelerators (MOREAU et al., 2015).

# 2.1 Quality Metrics and Approximation Methods

Given the plethora of approximation methods and systems that make use of them, the literature also presents an extensive list of error metrics definitions. Some examples of how precision loss is measured on approximate systems are:

- **Pixel Difference:** consists of a full comparison of two images pixel-by-pixel, where every pixel is represented by a value. Normally used to compare gray-scale images, where the pixel value defines the grey intensity (the higher value being complete darkness).

- Peak signal-to-noise ratio (PSNR): it is calculated using the mean square error (MSE) between the two images (the original and the approximate one), and indicates the ratio of the maximum pixel intensity to the distortion. It is calculated by the formula  $PSNR = 10log_{10}(MAX^2/MSE)$ , where MAX stands for the maximum value of a pixel in the images.

- Hamming Distance: when comparing data bit-wise, the hamming distance consists of the number of positions where the bit values are different between binary strings.

- **Ranking Accuracy:** when approximate computing is applied to ranking algorithms, such as the ones used by search engines, it can generate different results depending on the ranking definitions and the algorithms used. A research result from Bing and Google search engines, for example, will likely be different. The accuracy is defined based on pre-established parameters.

- Error Probability: consists of the error rate of all the possible outputs, comparing the result of an approximate function and its non-approximate counterpart. This metric gives the probability for an approximation to present an error but does not evaluate the criticality or impact of that error.

- **Relative Difference:** presents the error in relation to the standard non-approximate output. This metric is capable of evaluating the criticality of an error.

The presented quality evaluation metrics are not mutually exclusive. One applica-

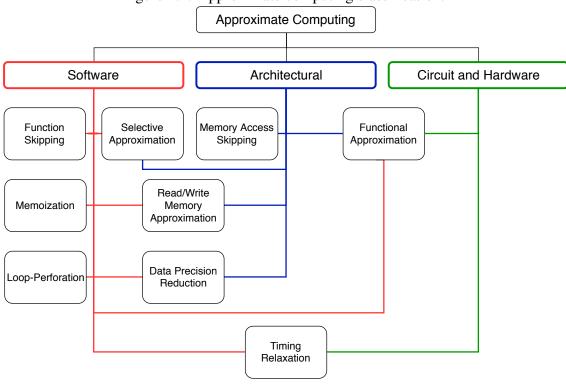

Figure 2.1: Approximate computing classification.

Source: Author.

tion might use several different parameters to evaluate its quality loss. Both PSNR and pixel difference are used as image quality metrics, for example.

Approximation techniques can be applied to all the computation stack levels. Figure 2.1 divides approximation techniques into three groups that define their implementation level: software, architectural, and hardware. As Figure 2.1 shows, some approximation methods can even be implemented in more than one level. Load value approximation, for example, can be both implemented by purely software approaches or at memory control units. Figure 2.1 presents only some of the most used approximation methods and the most discussed in the literature. However, there are uncountable ways of approximating an application, and the very definition of what is to be considered an approximation or not is debatable.

The techniques presented at Figure 2.1 are defined below:

**Functional Approximation:** Consists of implementing approximate versions of an algorithm. The literature presents a multitude of functional approximation techniques for circuits and architecture levels that implement approximate adders. One approach is to remove the carry chain from the circuit to reduce delay and energy consumption. This can be done by altering the subadders of a standard adder cell of n bits (KAHNG; KANG, 2012). In (KULKARNI; GUPTA; ERCEGOVAC, 2011),

the authors presented an approximate  $2 \times 2$  multiplier design that gives correct outputs for 15 of the 16 possible input combinations and uses half of the area of a standard non-approximate multiplier. Functional approximation can be implemented at software and architectural level using neural networks. A neural network can learn how a standard function implementation behaves in relation to different inputs via machine learning. In a complex system, the neural network can be used to implement approximate functions via software-hardware co-design. Traditional approximable codes can be transformed into equivalent neural networks that present a lower output accuracy but better execution time performance (AMANT et al., 2014).

- Selective Approximation: some systems are made of parts that don't need to provide accuracy as much as others. The idea is to take advantage of the fact that even inside an algorithm, some parts affect more the final accuracy than others. Those parts can be approximated to provide energy consumption reduction and improve execution time performance (VASSILIADIS et al., 2015). On the architectural level, selective approximation can appear as alternative speculative implementations of arithmetic operators. An example of this approach is the implementation of variable approximation modes on operators (SHAFIQUE et al., 2015). When applied to software applications, approximate computing usually consist of inexact computations, which provide results with lower accuracy than usual (VENKATARAMANI et al., 2015). Most approximate computing techniques for software consist of modifying the algorithm so that it executes approximately, providing a final result more rapidly.

- **Function Skipping:** in a system composed of tasks that complement each other in the sense of providing a final result, some of the tasks can be skipped while maintaining a level of accuracy and error resiliency defined by the user (GOIRI et al., 2015).

- **Memoization:** traditionally, memoization consists of saving outputs of functions for given inputs to be reused later. Given that some input data are frequently reused, their calculated outputs can be stored and used without the need for the re-execution of the function. Memoization can also be used to approximate applications: if *similar* inputs are to provide *similar* outputs from a given function, it means that the already-calculated function output can approximately cover a range of inputs. In (KERAMIDAS; KOKKALA; STAMOULIS, 2015), the authors propose approximate value reuse for memoization, providing very low accuracy loss.

- **Loop-Perforation:** In loop-based algorithms, loop-perforation can be used to highly reduce the execution time. An excellent example of this type of application is numerical algorithms. The calculation of an integral using the trapezoidal method, for example, consists of calculating the area of a high number of trapezoids under the curve of a function, providing an approximation of the area beneath it. Reducing the number of calculated trapezoids, the final value will be less accurate, but the program will finish earlier. The literature also presents techniques to apply this approximation method on general-use algorithms, filtering out the loops that cannot be approximated and using loop-perforation on those that can (SIDIROGLOU-DOUSKOS et al., 2011). The authors claim this approach typically delivers performance increases of over a factor of two while introducing an output deviation of less than 10%. Loop-perforation is an algorithm-based approximate technique, as it is only applicable to loop-based code, which limits its coverage.

- **Data Precision Reduction:** Data precision reduction is one of the techniques that can be implemented both at software and architectural level. Reducing the data precision of an application (i.e., the number of bits used to represent the data) is a straightforward technique to reduce memory footprint. Reducing memory usage also reduces energy consumption at the cost of accuracy. In (HSIAO; CHU; CHEN, 2013), the authors show that reducing floating point precision on mobile GPUs can bring energy consumption reduction with image quality degradation. This degradation, however, can be acceptable and even unperceivable for the human eye. Lower memory utilization is suitable for safety-critical systems because it reduces the essential and critical bit count, making them less susceptible to faults. Reducing the bit-width used for data representation is also a popular approximation method (RUBIO-GONZALEZ et al., 2013).

- **Timing Relaxation:** the operating voltage can be scaled at the circuit level, impacting the effort expended on the computation of processing blocks inside the clock period. It affects the accuracy of the final result and also the energy consumption (CHIPPA et al., 2014). In (CHIPPA et al., 2014), the authors propose the voltage overscaling of individual computation blocks, assuring that the accuracy of the results will "gracefully" scale with it. Voltage scaling can be implemented in hardware dynamically. Dynamic voltage and frequency scaling (DVFS), for example, is a power management technique used to improve power efficiency, reducing the clock frequency and the supply voltage of the processor (SUEUR; HEISER, 2010).

DVFS can cause data cells to be stuck with a specific value because it diminishes the threshold between a logical one and zero. This type of approximation impacts the integrity of the hardware and the precision of the data. Timing relaxation can also be implemented in software. On parallel programs, it is achieved by relaxing the synchronization between execution tasks (MISAILOVIC; KIM; RINARD, 2013).

- Read/Write Memory Approximation: Consists of approximating data that is loaded from or written in the memory, or the read/write operations themselves. This is primarily used on video and image applications, for example, where accuracy and quality can often be relaxed, to reduce memory operations (RANJAN et al., 2015; FANG; LI; LI, 2012). In (TIAN et al., 2015), the authors propose a technique that uses dynamic bit-width based on the application accuracy requirements, where a control system determines the precision of data accesses and loads. The authors claim that it can be implemented to a general-processor architecture without the need for hardware modifications by communicating with off-chip memory via a software-based memory management unit. Approximation can also be applied to the cache memory. In the event of a load data cache miss, the processor must fetch the data from the following cache level, or at the main memory. This can be a very time-consuming task. Load value approximation can be used to estimate an approximate value instead of fetching the real one from memory. In (SUTHER-LAND; MIGUEL; JERGER, 2015), the authors present a technique that uses the GPU texture fetch units to generate approximate values. This approximation causes an error of less than 0.5% in the final image output while reducing the kernel execution time in 12%. In (SAMPAIO et al., 2015), the authors propose an approximation technique for multi-level cell STT-RAM memory technologies by lowering its reliability up to a user-defined accuracy loss acceptance. This memory technology has a considerable reliability overhead, which can be reduced. They selectively approximate the storage data of the application and reduce the error-protection hardware minimizing error consumption.

- **Memory Access Skipping:** using a combination of the memoization and function skipping techniques, it is likewise possible to skip memory accesses. Uncritical data can be omitted, as long as it will not heavily damage the output accuracy. Approximate neural networks can skip reading entire rows of their weight matrices as long as those neurons are not critical, reducing energy consumption and memory access,

and improving performance (ZHANG et al., 2015).

The presented approximation techniques can be implemented in a multitude of ways, on various device levels with different impacts on the system behavior. Approximate computing at the software level is less presented in the literature than it is at the architecture level. This is probably due to the origins of approximation being on energy consumption reduction and neural network applications.

### **2.2 Technological Implementations**

Approximation techniques are applied to all the computational levels, as showed Figure 2.1. Likewise, they can be implemented in many abstraction levels. Selective approximation is an example of a technique that can be applied at the software and architectural computation stacks, and implemented via software code modification, programmable hardware, and even circuit level. Loop-perforation can also be achieved via code modification for embedded software and programmable hardware (using HLS), or directly with HDL project modifications. The way the approximation techniques are technologically implemented also has an important impact on their performance.

One of the problems with selective and functional approximation is it introduces error on the system output that is sometimes too big to be acceptable. The works at architectural level of approximate operators (SHAFIQUE et al., 2015), for example do not present a significant hardware implementation area reduction when compared to a traditional operator. Indeed, some of the approximate operators presented by (SHAFIQUE et al., 2015), not only have no hardware area gains, but take more area than traditional operators. The size of the used area on programmable hardware devices has a direct impact on system reliability (WIRTHLIN, 2015). Therefore, the quality loss (in this case manifested as errors in some operation results) introduced by the approximation would only be acceptable by safety-critical systems if it sharply reduced its area.

Developing alternate approximate versions of an algorithm is a very time-consuming and intellectually demanding work. To deal with this issue, some works propose frameworks that identify approximable portions of code. At (ROY et al., 2014), the authors present a framework to discover what are the data that can be approximated without significantly interfering with the output of the system. They do so by injecting faults in the variables and analyzing how they affect the quality of the output. Another method is to identify parts of an application code that can be executed on approximated hardware, saving resources and energy (ESMAEILZADEH et al., 2012). The type of approximation to be applied to the approximable parts of the application would depend on the application in question and the project requirements. Although those frameworks are presented as general-use, the question remains if they really can be applied to every type of algorithm. Because they base their methodology on simulation, it is hard to believe that they are able to cover every possible kind of fault that can affect every system.

One of the techniques with the most straightforward implementation is data precision reduction. The way it can be used to approximate software and FPGA applications is obvious: it is a matter of code modification. In software, the precision of floatingpoint units can be easily modified with the use of dedicated libraries, or even by merely changing the type of the variable. The same can be done at VHDL/Verilog projects: a design can be adapted to process smaller vectors of data. Data precision reduction can bring good improvements in area and energy costs for hardware projects, but frequently do not present high costs reduction on software. Fixed-point arithmetic, for example, can be used to approximate mathematical functions, such as logarithm, on FPGA implementations providing low area usage (PANDEY et al., 2013). On software, however, it can increase the execution time of the application because all the operations and data handling routines are implemented at the software level.

Similarly, the loop-perforation technique can be implemented both at software and programmable hardware code. The difference is that, on programmable hardware, a loop might be implemented either as many circuits executing in parallel (one being each iteration of the loop) or one circuit that is re-executed in a timeline. Therefore the impact of loop-perforation on software and hardware implementations can be very different. On software, it will mainly impact the execution time of the application, while in an FPGA implementation, it could also affect the energy and area consumption.

The timing relaxation through voltage scaling technique can be applied at both the processor architecture level and programmable hardware. At the architecture level, voltage scaling is implemented during the design of the circuit. Most FPGA manufacturers make the voltage scaling of the device possible through easy-to-use design tools. Even though it will impact the performance of a software application, it is not part of the software approximation group because its implementation has no direct connection with software development.

#### **3 RADIATION EFFECTS ON ELECTRONIC DEVICES**

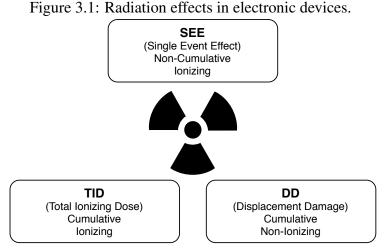

Radiation can affect electronics devices in multiple ways, as expressed in Figure 3.1. Single event effects (SEE) are non-cumulative and caused by single events that trigger transient upsets. Total ionizing dose (TID) and displacement damage (DD) are cumulative, which means their effects get worse over time as the system is exposed to radiation. Notice that not all radiation effects are ionizing. As will be further detailed, DD is caused by the kinetic energy of particles. For DD, another physical measurement for energy transfer is used in place of LET, but with similar modeling purposes.

The rate at which soft errors occur in a system is called soft error rate (SER). SER is caused in semiconductor devices mainly because of three sources of radiation: alpha particles, high-energy cosmic rays, and low-energy cosmic rays (BAUMANN, 2005). An ion traveling through a silicon substrate loses energy, generating one electron-hole pair for each 3.6eV lost. The linear energy transfer (LET) of an ion defines how much it can interfere with the proper device operation. It depends not only on the mass and energy of the particle but also on the material it is traveling in (represented in units of  $MeVcm^2/mg$ ).

Alpha particles are an important source of ionizing radiation and derive from the naturally present impurities in device materials. It is one of the radiations that can be emitted when the nucleus of unstable isotopes decay to a state of lower energy. Uranium and thorium are the most active radioactive isotopes, and therefore the dominant source of alpha particles in materials alongside their daughter products. Their decay can produce alpha and beta particles, but the latter is not critical for SER because they do not

Source: Author.

emit enough energy to cause ionization and provoke a soft error. Alpha particles induce electron-holes pairs in their awake and traveling in the silicon. In a packaged semiconductor product, the main source of alpha particles is the package materials, not the materials of the semiconductor device (BAUMANN, 2001).

Neutrons from cosmic radiation with high energy can react with the silicon nuclei and produce secondary ions that induce soft errors. Indeed, cosmic radiation is one of the leading sources of errors in DRAM (NORMAND, 1996), and neutrons are the most likely cosmic radiation to cause soft errors in devices at ground level. Cosmic rays interact with the earth's atmosphere and produce cascades of secondary particles, which continue deeper, creating tertiary particles and so on. Less than 1% of the original flux reaches sea-level altitudes, and most of the particles that arrive consist of muons, pions, protons, and neutrons (ZIEGLER; LANFORD, 1980). Muons and pions have a short life, and protons and electrons are attenuated by Coulombic interactions with the planet atmosphere. Neutrons, however, have a higher flux and stability. Neutrons do not generate ionization in silicon alone. They interact with the chip materials breaking excited nuclei into lighter fragments.

Low-energy cosmic rays induce radiation with the interaction of their neutrons with boron, producing ionizing particles. Very low energy neutrons ( $\ll 1 MeV$ ) react with the nucleus of <sup>10</sup>B, which breaks releasing energy in the form of a <sup>7</sup>Li recoil nucleus and an alpha particle. The alpha particle and the lithium nucleus generated from the absorption of the neutron by the <sup>10</sup>B are launched in opposite directions in order to conserve momentum. They are both capable of inducing soft errors, especially in new technologies of lower voltage.

The faults induced by radiation can become errors that might evolve into failures. By definition, a fault is the event itself, manifested as a bit-flip on a memory component, for example. The error, on the other hand, is the effect of the fault on the system. It can pass by unperceived, or be masked by a fault tolerance mechanism. When the system misbehaves, and this is noticed by the user or propagated to another part of the system that, in its turn, shows a problematic external behavior, we say that a failure happened. Taking the example of a fault affecting the memory circuit, the definition of the events would be the following: the bit-flip on the memory data is a fault, the error is the impact it has in the data being stored in the word where the fault was raised, and the failure would be the malfunction of the software that could, for example, use this data as a control variable of a loop, causing the application to never finish its execution. Notice that the fault could have happened in an unused word of memory, causing no errors. Similarly, the error could have been overwritten by a store instruction shortly before happening, and never turn into a failure.

## 3.1 Single Event Effects (SEE)

When radiation particles transfer enough energy into the silicon of circuits, they generate transient upsets. Upsets are manifested as bit-flips in any part of the circuit that holds data, causing errors (POIVEY et al., 2001; BAUMANN, 2005). In microprocessors, bit-flips can occur in all registers and memories of the processor. Table 3.1 summarizes the different SEE types and their characteristics. The characteristics exposed at Table 3.1 stand for:

- Non-Destructive: an SEE that do not cause permanent damage to the system.

- **Destructive:** an SEE that can cause permanent damage to the system.

- **Reset Needed:** the SEE requires a full reset of the system so that it can vanish (i.e., it is a not permanent error).

- **Power Cycle Needed:** A simple reset of the system might not be enough to clean the error. Those errors are often related to physical problems affecting operation of the transistors or logic gates.

Notice that it is possible for an SEE to be both destructive and non-destructive: some of them can be destructive only in some cases, normally related to the intensity or locality of the fault. The SEE types presented at Table 3.1 are defined with more details below:

- **Single Event Upset (SEU):** as soft errors are commonly referred to. Those are nonpermanent errors affecting one single bit of one word of data.

- **Multibit Upset (MBU):** occurs when the radiation event has energy high enough to flip multiple bits on a single word. This can be especially problematic for memory circuits that make use of error correction codes, compromising those that cover and mask only one bit (MAIZ et al., 2003).

- Multicell Upset (MCU): occurs when the radiation event has energy high enough to affect multiple bits on different localities. The difference between and MBU and an MCU is that the latter consists of bit-flips affecting various parts of a system (e.g.,

different memory words), while the former consists of multiple bit-flips in a single word (IBE et al., 2006).

- **Single Event Transient (SET):** considered when transient upsets occur in the combinational logic part of the circuit. If propagated and latched into memory elements, those can lead to soft errors (BENEDETTO et al., 2004).

- Single Event Functional Interrupt (SEFI): when a soft error occurs in a critical control circuitry (e.g., branch prediction or jump address), it can cause the processing to misbehave to the point where its proper execution is compromised (KOGA et al., 1997). SEFIs lead to a direct malfunction that is easily noticed by the user (e.g., when the application ceases to respond), instead of soft memory errors that may pass unperceived.

- Single Event Latch-Up (SEL): SEEs can induce a latch-up by turning on CMOS parasitic bipolar transistors between the well and the substrate (BRUGUIER; PALAU, 1996). SELs are debilitating because a reset (powering it off and back on again) is necessary to remove it. They can also cause permanent damages.

- **Micro Single Event Latch-Up** ( $\mu$ SEL): this type of latch-up is related to the reduction of the transistor size and operating voltages. One of the major differences between  $\mu$ SEL and SEL is that the latter usually occurs in the terminals of a logic gate, while the former occurs in different areas and levels of the die, provoking different effects (AZIMI; STERPONE, 2017). Also,  $\mu$ SEL can occur under ground-level radiation (TAUSCH et al., 2007).

- **Single Event Burnout (SEB):** when a heavy ion passes through a power MOSFET biased in the off state (blocking a high drain-source voltage), transient currents generated by it might turn on a parasitic bipolar-junction transistor that is inherent to this device structure. A permanent short between the source and the drain of the MOSFET is then created due to a regenerative feedback mechanism affecting the new parasitic transistor, which increases collector currents provoking a breakdown (JOHNSON et al., 1996).

- Single Event Gate Rupture (SEGR): provoked by a dielectric breakdown of the gate oxide, caused by heavy ions. The heavy ion accumulates charge at the  $Si-SiO_2$  interface in the gate-drain overlap region and results in electric fields in the gate oxide that cause a localized rupture. That rupture causes a permanent short between the gate and the drain of the transistor (JOHNSON et al., 1996).

| SEE       | Meaning        | Characteristics |             |        |             |

|-----------|----------------|-----------------|-------------|--------|-------------|

| SEE       |                | Non-            | Destructive | Reset  | Power Cycle |

|           |                | Destructive     | Destructive | Needed | Needed      |

| MBU       | Multibit       | X               |             |        |             |

|           | Upset          |                 |             |        |             |

| MCU       | Multicell      | X               |             |        |             |

|           | Upset          |                 |             |        |             |

| $\mu$ SEL | Micro Single   | X               |             |        | X           |

|           | Event Latch-Up |                 |             |        | Λ           |

| SEL       | Single Event   | Х               |             |        | Х           |

| SEL       | Latch-Up       |                 | Х           |        |             |

| SEB       | Single Event   |                 | Х           |        |             |

| SED       | Burnout        |                 | Λ           |        |             |

| SEGR      | Single Event   |                 | X           |        |             |

|           | Gate Rupture   |                 | Λ           |        |             |

| SHE       | Single Hard    | Х               |             |        | X           |

|           | Error          |                 | Х           |        |             |

| SEFI      | Single Event   |                 |             |        |             |

|           | Functional     | Х               |             | Х      | Х           |

|           | Interrupt      |                 |             |        |             |

| SET       | Single Event   | X               |             |        |             |

|           | Transient      |                 |             |        |             |

| SEU       | Single Event   | X               |             |        |             |

|           | Upset          |                 |             |        |             |

Table 3.1: SEE classification and key characteristics.

**Single Hard Error (SHE):** a sufficiently energetic heavy ion that strikes a MOS transistor gate can locally transfer enough ionizing dose to affect its electrical parameters permanently (DUFOUR et al., 1992). It consists of a total ionizing dose error from a single ion, that can affect SRAM memories (POIVEY et al., 1994)

## **3.2 Total Ionizing Dose (TID)**

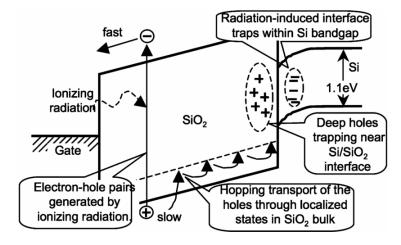

Apart from non-cumulative SEE, radiation can also provoke cumulative effects. This type of effect accumulates over time, altering the regular operation of the devices, to the point where they start to become a severe problem. Such is the case of total ionizing dose (TID), which is caused by the same physical event that can cause SEEs: the generation of electron-hole pairs. The difference between SEE and TID is that TID is accumulated over time in the device and provoke gradual and permanent changes in the

Figure 3.2: TID in a CMOS transistor.

Source: (ANDREOU et al., 2015).

device behavior.

TID accumulates in the device when the electron-hole pair caused by radiation effects is separated by the electric field concentrated in the transistor gate or field oxide. The electric field prevents the electron-hole pair recombination, and because the now free electrons have high mobility, they are swept from the oxide, leaving holes behind (with low mobility). The holes get trapped in the oxide bulk and at the Si-SiO<sub>2</sub> interface, as shown in Figure 3.2. Those trapped holes modify the threshold voltage of the transistor by attracting electrons in the inversion channel, affecting the drain-source current. Because the number of electron-hole pairs is directly proportional to the total amount of radiation dose which the device is subject to, this effect will increase over time and change the characteristics of the transistors. The number of pairs also depends on the dose rate and the gate-oxide electric field, as well as the thickness of the oxide (ANDREOU et al., 2015).

#### **3.3 Displacement Dammage (DD)**

Devices can also be subject to non-ionizing cumulative effects. Non-ionizing dose deposited by radiation can be a source of failures in the form of displacement damage (DD). The kinetic energy of the irradiated particles is transferred to the material and can produce atomic displacements. The rate on which this energy is passed to the material is called non-ionizing energy loss (NIEL). The DD energy deposition per unit of mass of material can be calculated by the product of the NIEL and the particle fluence ( $\Phi_i$ ) (JUN

et al., 2003), as expressed in (3.1).

$$DD = NIEL_i \cdot \Phi_i \tag{3.1}$$

The NIEL can be calculated as (3.2) shows, where N is the number of atoms per cubic centimeters of the area being affected,  $T_M$  is the maximum transferred energy by the collision of an ion with the atoms of the material, T is the energy of the recoiling atoms,  $T_d$  is the threshold energy for atomic displacements (21eV for silicon),  $\frac{d\sigma}{dT}$  is the differential cross section for atomic displacements and L(T) stands for the Lindhard partition factor. L(T) takes into account that only some of the energy of the recoil will actually go into producing displacements (MESSENGER et al., 2003).

$$NIEL = N \int_{T_d}^{T_M} T \frac{d\sigma}{dT} L(T) dT$$

(3.2)

Displacement damage can be caused by protons, neutrons, alpha particles, and high energy photons. As the equations induce, the displacement damage depends on the type of particle radiation, its energy, the total dose, and radiation flux. Some characteristics of the device also impact the possible displacement damage, such as the operating voltage, frequency, and shielding (both intrinsic and extrinsic).

## **3.4 Analyzing Radiation Effects**

This chapter presented the radiation effects on electronic devices that are discussed in the literature. Although knowing them and their impacts is indispensable, some of them are out of the practical scope of this work. The TID and DD are related to circuit-level hardware malfunctions manifested in the system behavior as errors related to the intensive exposure of the device to a hazardous environment. Much like aging effects on electronic devices, those errors can hardly be deal with by the use of programming methods or design strategies. Because of that, the fault tolerance and approximation techniques presented in this work will not have as their main target the effects by TID nor DD. Instead, the techniques presented in this work will focus on dealing with errors caused by non-destructive SEEs such as SEUs, MBUs, SETs, and SEFIs.

## **4 ANALYSIS METHODOLOGIES**

The reliability of a system to radiation-induced transient faults can be measured in many different ways, depending on the available data and experiments performed. Some of the most used metrics for reliability and fault tolerance of safety-critical systems under radiation are the mean work to failure (MWTF)(REIS et al., 2005), the cross-section, and failure in time (FIT) (BAUMANN, 2005), alongside with the already discussed SER (soft error rate). The cross-section ( $\sigma$ ) is defined as the area of the device that is sensitive to radiation, with (4.1). A larger cross-section means that a particle that hits the device is more likely to produce a failure. Thus, a design of smaller area (such as an approximate one) will typically present a smaller cross-section. The FIT is commonly as a means to express SER and is equivalent to one failure in 10<sup>9</sup> hours of device operation. MWTF is particularly interesting for this works discussing because it presents a correlation between performance and the fault tolerance of a technique, and is presented in (4.2).

$$\sigma = \frac{\text{number of errors/failures}}{\text{fluence of particles}}$$

(4.1)

$$MWTF = \frac{\text{amount of work completed}}{\text{number of errors encountered}}$$

(4.2)

When analyzing data from simulation experiments, the error occurrence is often presented as a simple percentage. In this type of analysis, faults are injected into the system, and it is often possible to trace the types of errors and their origin. Thus, it is easy to calculate the percentage of faults that caused errors (and failures) and their types. When analyzing fault tolerance techniques, especially those implemented on embedded software, metrics like cross-section might not be the most appropriate (in fact, using this type of metric would need an adaptation, because there is no particle fluence in this type of experiment). In those cases, data might be better presented merely as the reduction of the percentage of faults capable of inducing failures.