# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# OTTO AURELIANO ROLLOFF

# PROJETO E AVALIAÇÃO DE CÉLULAS PADRÃO PARA A CONCEPÇÃO DE CIRCUITOS INTEGRADOS ASSÍNCRONOS EM NANOTECNOLOGIA DE BAIXO CONSUMO

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# PROJETO E AVALIAÇÃO DE CÉLULAS PADRÃO PARA A CONCEPÇÃO DE CIRCUITOS INTEGRADOS ASSÍNCRONOS EM NANOTECNOLOGIA DE BAIXO CONSUMO

Projeto de Diplomação apresentado ao Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul, como parte dos requisitos para Graduação em Engenharia Elétrica. Este trabalho foi desenvolvido no Laboratório TIMA (Grenoble, França) no contexto de estágio de fim de estudos durante intercâmbio acadêmico na escola de engenharia Télécom Bretagne (Brest, França).

Orientador UFRGS: Prof. Dr. Tiago R. Balen

Orientador TIMA: Prof. Dr. Rodrigo Possamai Bastos

Porto Alegre

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

## OTTO AURELIANO ROLLOFF

# PROJETO E AVALIAÇÃO DE CÉLULAS PADRÃO PARA A CONCEPÇÃO DE CIRCUITOS INTEGRADOS ASSÍCRONOS EM NANOTECNOLOGIA DE BAIXO CONSUMO

Este projeto foi julgado adequado para fazer jus aos créditos da Disciplina de "Projeto de Diplomação", do Departamento de Engenharia Elétrica e aprovado em sua forma final pelo Orientador e pela Banca Examinadora.

| Orientador:                              |

|------------------------------------------|

| Prof. Dr. Tiago Roberto Balen, UFRGS     |

| Doutor pela UFRGS – Porto Alegre, Brasil |

## Banca Examinadora:

Prof. Dr. Rodrigo Possamai Bastos, Lab. TIMA / Université Grenoble Alpes Doutor pela UFRGS e Grenoble INP – Grenoble, França

Prof. Dr. Hamilton Duarte Klimach, UFRGS Doutor pela UFSC – Florianópolis, Brasil

# **DEDICATÓRIA**

Aos meus pais, Otto e Sloane.

# **AGRADECIMENTOS**

Aos meus pais, Otto e Sloane, pelo amor incondicional, por terem percorrido todo esse caminho comigo de mãos dadas. Vocês sempre foram minha inspiração

Às minhas irmãs Bianca, Sharlise, Shymene e Sophia; pelo amor, pela admiração e pelo apoio.

À Roberta, por tudo, não haveria linhas suficientes aqui para agradecer.

Aos colegas, agora amigos íntimos, pela horas memoráveis. Entre eles, e em especial, à minha pequena família da elétrica: Charlez; Douglas; Renan; Rodrigo; Silvio e Taís.

Ao Brasil, por me permitir e me dar condições para desenvolver meus estudos no meu país e no país por mim escolhido para intercâmbio.

Ao TIMA, pelo ambiente esplêndido de trabalho, me permitindo de fazer o que eu mais gosto.

Aos meus colegas e professores do LAPROT e LAPSI pelo companheirismo, colaboração e amizade.

Aos meus colegas e professores do Laboratório de Sedimentos (UFRGS) e IPH pelo verdadeiro ensino e inspiração para que eu me tornasse pesquisador.

À Universidade, UFRGS, mãe para todos os meus momentos.

À Télécom Bretagne, pelo convite, acolhimento e pelos ótimos momentos de aprendizado com as diferenças.

Aos funcionários de ambas as instituições, pela atenção, auxílio e boas conversas.

Aos professores, meus mestres, mas também amigos e conselheiros.

Por último, mas não menos importantes, aos meus orientadores Gustavo H. Merten, Jean P. G. Minella, Luis A. Segovia Gonzalles, Gilson I. Wirth, Tiago R. Balen, Laurent Fesquet e Rodrigo P. Bastos.

## **RESUMO**

A indústria de semicondutores inova sistematicamente com a criação de nanotecnologias de fabricação de circuitos integrados voltadas ao projeto de sistemas eletrônicos de baixo consumo. Este trabalho avalia a nova nanotecnologia 28 nm Fully-Depleted Silicon On Insulator (FD-SOI) aplicada na concepção de células padrão de sistemas assíncronos. Diferente das tecnologias convencionais, a tensão do substrato de um transistor FD-SOI é variável, permitindo através de mecanismos de polarização a gestão do consumo local de células do sistema. Complementarmente, os circuitos assíncronos apresentam-se como uma solução sólida para a redução do consumo dinâmico. Um estudo sobre a polarização de células básicas em tecnologia FD-SOI foi realizado neste trabalho visando sua aplicação na concepção de sistemas assíncronos de baixo consumo. Foi visto que o consumo pode ser reduzido em até 25 % unicamente com a polarização do circuito. A partir de opções de transistor em uma biblioteca standard-cell, obtem-se circuitos até duas vezes mais rápidos e um consumo de energia até 2,5 vezes menor. Foram analisadas duas arquiteruras para célula de polarização, possuindo uma diferença de 30 % em relação ao atraso. Para circuitos assíncronos C-Elements a diferença pode chergar a 29 % em velocidade e de 8,5 vezes em consumo de energia. Essas variações de performance e consumo demonstram a amplitude que se pode alcançar quando no emprego de tecnicas de controle de performace automáticos com uso de lógica de concepção assíncrona.

Palavras-chaves: sistemas de baixo consumo, circuitos assíncronos, tecnologia FD-SOI.

## **ABSTRACT**

The focus of this work is on the static power reduction for microelectronics systems. In one hand, the FD-SOI technology (*Fully-Depleted Silicon on Insulator*) allows the reduction of the static power consumption by biasing control. Complementarily, asynchronous circuits are known as an interesting solution for dynamic power saving. Both circuit design methodologies permits not just a gain on static and dynamic power consumption, but also open new prospects for devices layout and arrangement. This, in turn, provides new power saving techniques. Therefore, this work presents a study about the biasing effects on power saving using FD-SOI 28nm technology. Simulation results showed the possibility to reduce power consumption in 25 % thanks to the biasing scheme. A standard cell library offers a viriaty of transistors giving circuits 2 times faster and a range of approximatly 2.5 times in power consumption. Two architectures for automatic biasing circuits are presented, showing a difference of 30 % in delay and 2 times in power consumption. For the asynchronous C-Elements, 4 archtectures were compared showing a difference of 29 % in delay and nearly 8.5 in power consumption. Those ranges of performances and power consumptions justifys the use of automatic performance control using asynchronous circuits desing.

Keywords: Low-power systems. Asynchronous Circuits. FD-SOI.

# **SUMÁRIO**

| 1     | INTRODUÇÃO                                           | 1              |

|-------|------------------------------------------------------|----------------|

| 2     | TECNOLOGIA FULLY-DEPLETED SILICON ON INSULATOR (FD-S | 5 <i>01</i> )5 |

| 2.1   | Da tecnologia SOI à tecnolobia FD-SOI                | 6              |

| 2.2   | Fabricação de Wafers para a Tecnologia FD-SOI        | 8              |

| 2.3   | Óxido Enterrado                                      | 9              |

| 2.4   | Tensão de Limiar                                     | 11             |

| 2.5   | Polybiasing                                          | 15             |

| 2.6   | Conclusões                                           | 17             |

| 3     | CIRCUITOS ASSÍNCRONOS                                | 19             |

| 3.1   | Quasi Insensíveis ao Atraso                          | 21             |

| 3.2   | Protocolo de 4 Fases                                 | 23             |

| 3.3   | C-Element                                            | 25             |

| 3.4   | Conclusões                                           | 27             |

| 4     | CONTROLE DE POLARIZAÇÃO DE SUBSTRATO                 | 28             |

| 4.1   | Células de Aceleração                                | 28             |

| 4.1.1 | Tipos de Desviadores de Nível                        | 31             |

| 4.1.2 | Conventional Level Shifter                           | 33             |

| 4.1.3 | Contention Mitigated Level Shifter                   | 34             |

| 4.2   | Conclusões                                           | 35             |

| 5       | AVALIAÇÃO DE CÉLULAS LÓGICAS PARA A CONCEPÇÃO DE                                   |  |  |

|---------|------------------------------------------------------------------------------------|--|--|

| CIRCU   | ITOS ASSÍNCRONOS DE BAIXO CONSUMO36                                                |  |  |

| 5.1     | Método de cálculo para a normalização37                                            |  |  |

| 5.2     | Biblioteca Standard-Cell FD-SOI 28nm39                                             |  |  |

| 5.3     | Inversores Lógicos40                                                               |  |  |

| 5.3.1   | Funcionamento do circuito em baixas tensões de alimentação41                       |  |  |

| 5.3.2   | Avaliação dos 3 diferentes corners de simulação42                                  |  |  |

| 5.3.3   | Efeito da polarização do substrato dos transistores47                              |  |  |

| 5.3.4   | 4 Efeito do Polybiasing e do Tamanho da Célula na performance dos inversores<br>49 |  |  |

| 5.3.4.1 | Polybiasing com inversor como carga50                                              |  |  |

| 5.3.4.2 | Polybiasing com Capacitor como carga51                                             |  |  |

| 5.3.4.3 | Diferença de consumo com cargas idênticas e distintas51                            |  |  |

| 5.4     | C-Elements53                                                                       |  |  |

| 5.5     | Boost cells56                                                                      |  |  |

| 6       | CONCLUSÕES E TRABALHOS FUTUROS59                                                   |  |  |

| REFER   | RÊNCIAS BIBLIOGRÁFICAS62                                                           |  |  |

# LISTA DE ILUSTRAÇÕES

| Figura 1 Evolução histórica da computação por consumo [kWh] os anos de 1940 à 2010               |

|--------------------------------------------------------------------------------------------------|

| (KOOMEY et al., 2011). A amostra do gráfico consiste de 80 dentre os principais                  |

| computadores e microprocessadores já desenvolvidos. Uma curva de regressão é também              |

| apresentada. O coeficiente de determinação (R2) da curva é igual à 98,3%                         |

| Figura 2. Representação em corte transversal de transistores em tecnologia convencional          |

| (Bulk) e em FD-SOI (ST MICROELECTRONICS, 2014a)                                                  |

| Figura 3 – Ilustração de um transistor FinFET. [Adaptado de PAYNE, 2012]6                        |

| Figura 4 – Representação comparativa dos cortes transversais de transistores feitos em           |

| tecnologias com canais Parcialmente (a) e Completamente Depletados (b), ambos utilizando         |

| wafer SOI. (MENTOR GRAPHICS, 2008)7                                                              |

| Figura 4 – Etapas do processo SmartCut para a fabricação de wafers da tecnologia FD-SOI          |

| (HARS, 2012)9                                                                                    |

| Figura 6 – Transistores FD-SOI com BOX de 10 nm (a) e de 25 nm (b). (LIU et al., 2011)12         |

| Figura 7 - Configurações de poço convencional (Conventional Well) e poço invertido (Flip-        |

| Well) em tecnologia FD-SOI juntamente com suas respectivas margens de tensão de                  |

| polarização de substrato (FLATRESSE, 2013)14                                                     |

| Figura 8 – Apresentação do comprimento do polisilício (a) em um corte transversal de um          |

| transistore FD-SOI. Ilustração da variação do comprimento do canal entre mínimo/original (b)     |

| e aumentado/alargado (c). (FLATRESSE, 2013)15                                                    |

| Figura 9 – Exemplo de uma confluência isocrônica: a variação dos sinais C e D são resultado      |

| da variação de um mesmo sinal (sinal B) e devem chegar na porta OR com uma diferença             |

| temporal não significativa                                                                       |

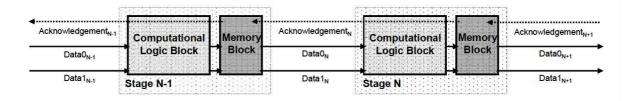

| Figura 10 - Estrutura de um circuito QDI em analogia à um circuito síncrono. (BASTOS,            |

| 2010)23                                                                                          |

| Figura 11 - Comunicação entre dois estágios através de 4-Phase Protocol. (BASTOS, 2010)24        |

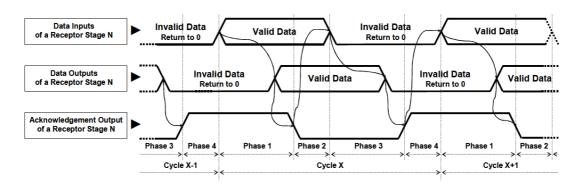

| Figura 12 - Esquemáticos dos 4 tipos básicos de C-Elements: Dynamic (A), Conventional (B),       |

| Symmetric (C) e Weak Feedback (D). (BASTOS, 2010)26                                              |

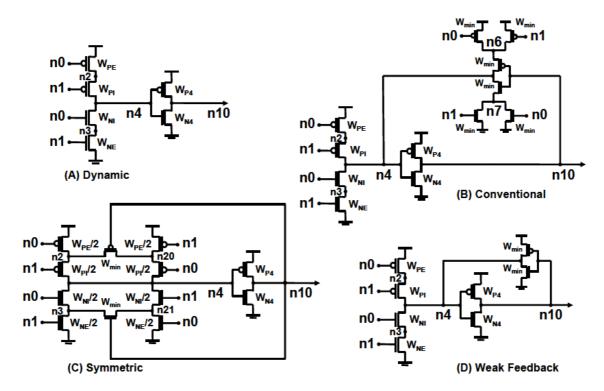

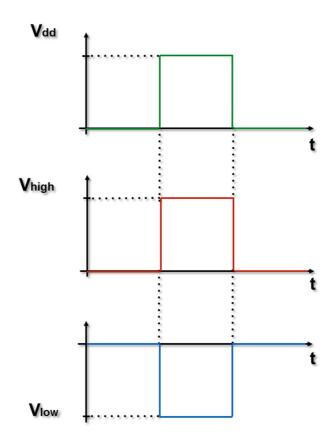

| Figura 13 – Entada (em verde) e saída (em vermelho) de um circuito <i>Level Shifter</i> típico30 |

| Figura 14 – Entrada (em verde) e saídas positiva (em vermelho) e negativa (em azul) para um      |

| circuito Level Shifter adaptado para funcionar como uma Boost Cell31                             |

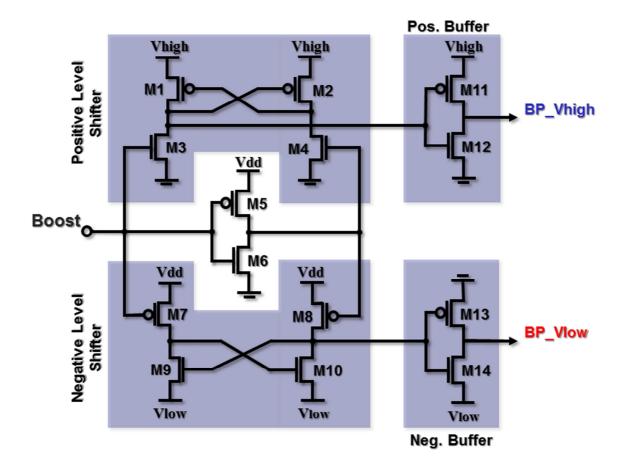

| Figura 15 - Esquemático elétrico de um Conventional Level Shifter incluindo sua parte            |

| complementar para tensões negativas                                                              |

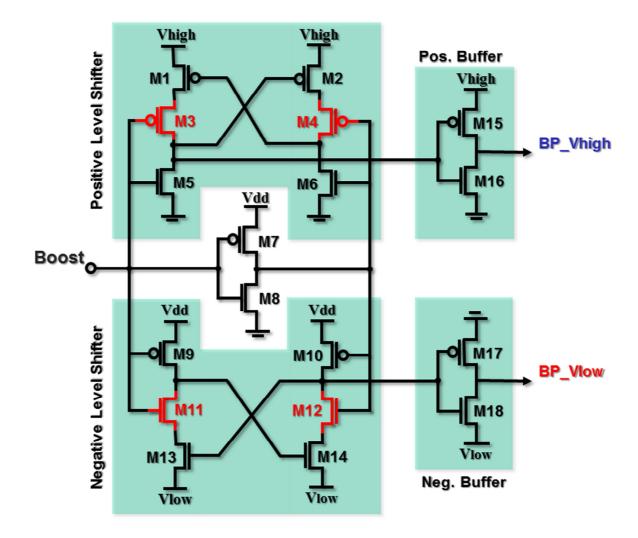

| Figura 16 - Esquemático elétrico de um Conventional Level Shifter                                |

| Figura 17 – Resposta à uma onda quadrada de um inversor lógico LL P0 com corner SS. A            |

| tensão máxima da onda e da tensão é a mesma da tensão de alimentação, variando de 0,10 V à       |

| 0,40 V com passo de 0,05 V41                                                                     |

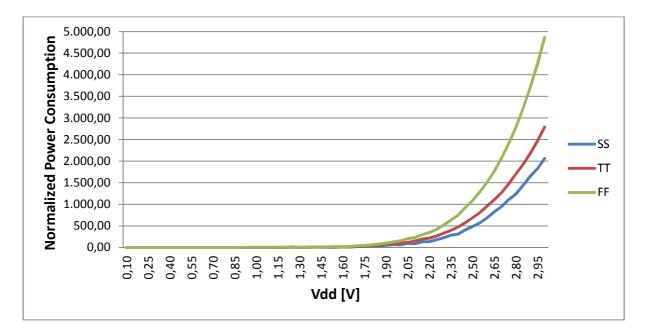

| Figura 18 – Comparativo do consumo de energia de células inversoras lógicas com                  |

| transistores Low-Vt. A comparação é feita: para diferentes valores de tensão de alimentação      |

| (de 0,10 V à 3,00 V com passo de 0,05 V); e para os 3 tipos de corners analisados (SS, TT e      |

| FF). As normalizações foram feitas em relação ao consumo de um Inversor com transistor LR        |

| P0 TT com tensão de alimentação de 1,00 V                                                        |

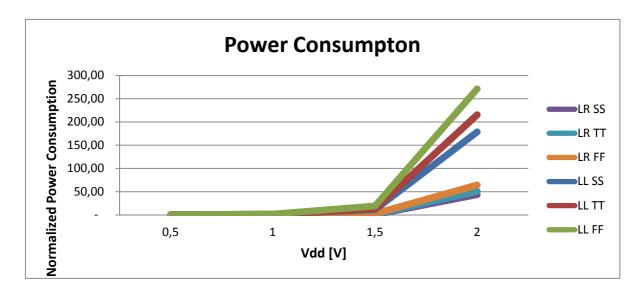

| Figura 19 – Comparativo do consumo de energia de células inversoras lógicas com                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| transistores Regular-Vt e Low-Vt. A comparação é feita: para diferentes valores de tensão de                                                                                          |

| alimentação (de 0,50 V à 2,00 V com passo de 0,5 V); e para os 3 tipos de corners analisados                                                                                          |

| (SS, TT e FF). As normalizações foram feitas em relação ao consumo de um Inversor com                                                                                                 |

| transistor LR P0 TT com tensão de alimentação de 1,00 V                                                                                                                               |

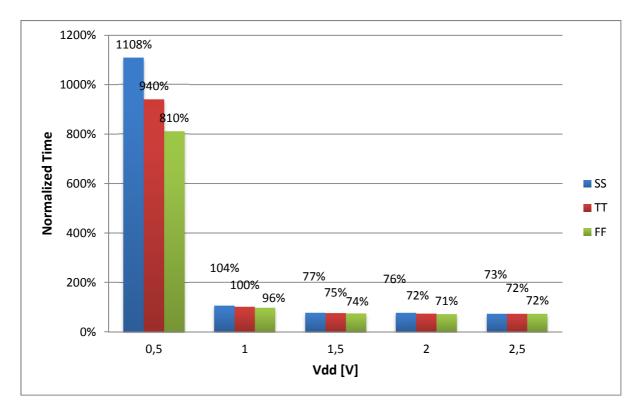

| Figura 20 – Tempos de subida normalizados para células inversoras lógicas com transistores                                                                                            |

| Regular-Vt. A comparação é feita: para diferentes valores de tensão de alimentação (de 0,50 V à 2,50 V com passo de 0,5 V); e para os 3 tipos de corners analisados (SS, TT e FF). As |

| normalizações foram feitas em relação aos tempos e atrasos de um Inversor com transistor LR                                                                                           |

| P0 TT com tensão de alimentação de 1,00 V                                                                                                                                             |

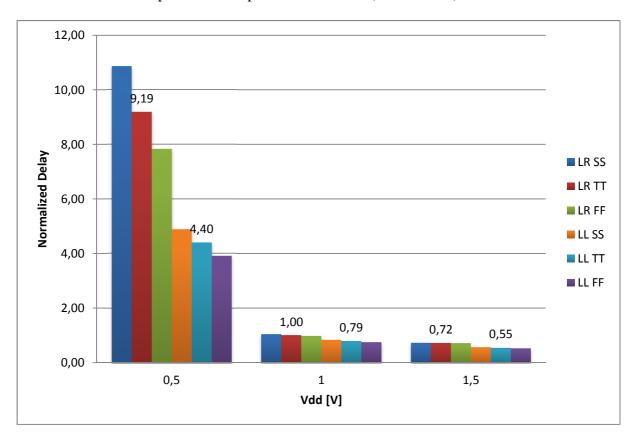

| Figura 21 – Média entre os atrados de subida e de descida para células inversoras lógicas com                                                                                         |

| transistores Regular-Vt e Low-Vt. A comparação é feita: para diferentes valores de tensão de                                                                                          |

| alimentação (de 0,50 V à 1,50 V com passo de 0,5 V); e para os 3 tipos de corners analisados                                                                                          |

| (SS, TT e FF). As normalizações foram feitas em relação aos tempos e atrasos de um Inversor                                                                                           |

| com transistor LR P0 TT com tensão de alimentação de 1,00 V                                                                                                                           |

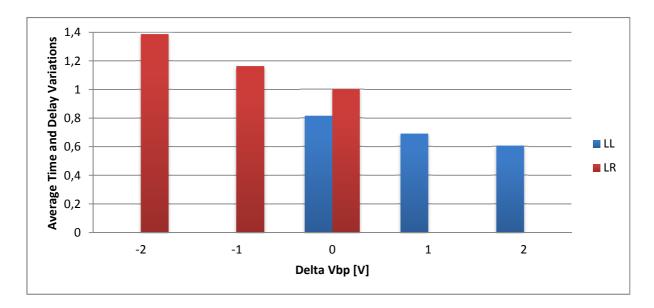

| Figura 22 – Média dos valores normalizados de Tempos de subida e de descida; e dos Atrados                                                                                            |

| de subida e de descida para células inversoras lógicas com transistores Regular-Vt e Low-Vt                                                                                           |

| para diferentes condições de polarização. A comparação é feita: para diferentes valores de                                                                                            |

| tensão polarização (de -2,00 V à 2,00 V com passo de 1,00 V); e para corners P e N típicos                                                                                            |

| (TT). As normalizações foram feitas em relação aos tempos e atrasos de um Inversor com                                                                                                |

| transistor LR P0 TT com tensão de alimentação de 1,00 V                                                                                                                               |

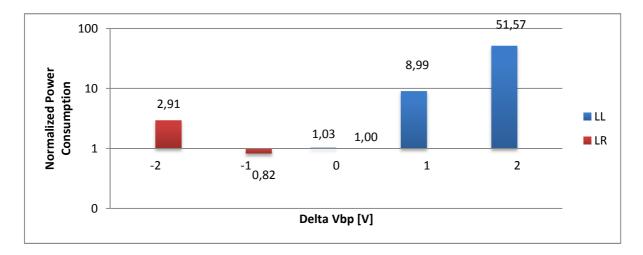

| Figura 23 – Consumo médio normalizado para células inversoras lógicas com transistores                                                                                                |

| Regular-Vt e Low-Vt para diferentes condições de polarização. O eixo do consumo                                                                                                       |

| normalizado está em escala logarítmica. A comparação é feita: para diferentes valores de                                                                                              |

| tensão polarização (de -2,00 V à 2,00 V com passo de 1,00 V); e para corners P e N típicos                                                                                            |

| (TT). As normalizações foram feitas em relação aos tempos e atrasos de um Inversor com                                                                                                |

| transistor LR P0 TT com tensão de alimentação de 1,00 V                                                                                                                               |

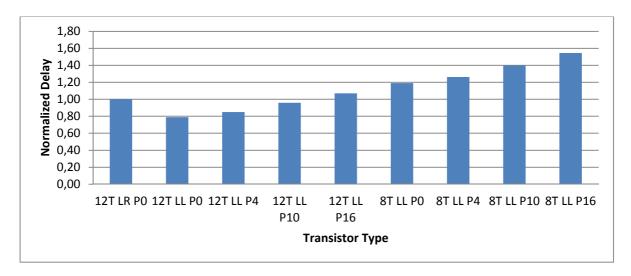

| Figura 24 – Atrasos normalizados para células inversoras lógicas com transistores Regular-Vt                                                                                          |

| e Low-Vt com os diferentes tamanhos polybiasing e de altura de célula. O mesmo tipo de                                                                                                |

| célula foi utilizado como carga. A tensão de alimentação é de 1,00 V usando-se polarização                                                                                            |

| típica nos corners P e N típicos. As normalizações foram feitas em relação aos tempos e                                                                                               |

| atrasos de um Inversor com transistor LR P0 TT com tensão de alimentação à 1,00 V50                                                                                                   |

| Figura 25 – Temos e Atrasos normalizados para células inversoras lógicas com transistores                                                                                             |

| Regular-Vt e Low-Vt com os diferentes tamanhos polybiasing e de altura de célula. A tensão                                                                                            |

| de alimentação é de 1,00 V usando-se polarização típica nos corners P e N típicos, todos                                                                                              |

| usando carga capacitiva de 14 pF. As normalizações foram feitas em relação aos tempos e                                                                                               |

| atrasos de um Inversor com transistor LR P0 TT com tensão de alimentação à 1,00 V51                                                                                                   |

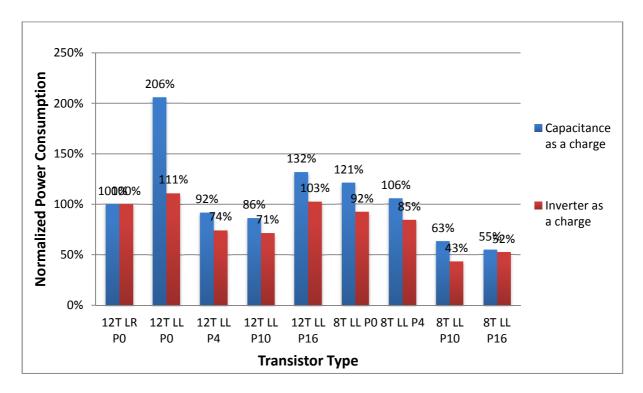

| Figura 26 – Consumo médio normalizado para células inversoras lógicas com transistores                                                                                                |

| Regular-Vt e Low-Vt com os diferentes tamanhos polybiasing e de altura de célula. Em                                                                                                  |

| vermelho, foi utilizado o mesmo tipo de célula como carga e em azul uma carga capacitiva de                                                                                           |

| 14 pF. A tensão de alimentação é de 1,00 V usando-se polarização típica nos corners P e N                                                                                             |

| típicos. As normalizações foram feitas em relação aos tempos e atrasos de um Inversor com                                                                                             |

| transistor LR P0 TT com tensão de alimentação de 1,00 V                                                                                                                               |

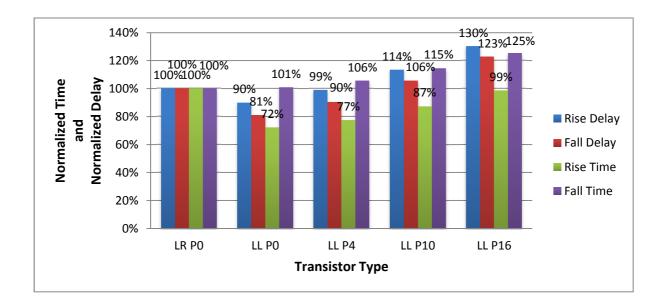

| Figura 27 – Tempos e atrasos de subida e descida normalizados de um circuito C-Element                                                                                                |

| Conventional com tensão de alimentação à 1,00 V em corner típico. As normalizações foram                                                                                              |

| feitas em relação aos tempos e atrasos do C-Element Conventional com transistor LR P0 TT.                                                                                             |

| Figure 28 Módio, entre os etrosos de subide e descido permelizados de um circuito C                                                                                                   |

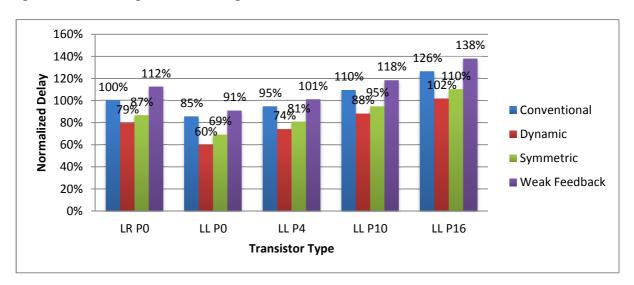

| Figura 28 – Média entre os atrasos de subida e descida normalizados de um circuito C-                                                                                                 |

| Element Conventional com tensão de alimentação à 1,00 V em corners P e N típicos (TT). As                                                                                             |

| normalizações foram feitas em relação aos tempos e atrasos do C-Element Conventional com    |

|---------------------------------------------------------------------------------------------|

| transistor LR P0 TT à mesma tensão54                                                        |

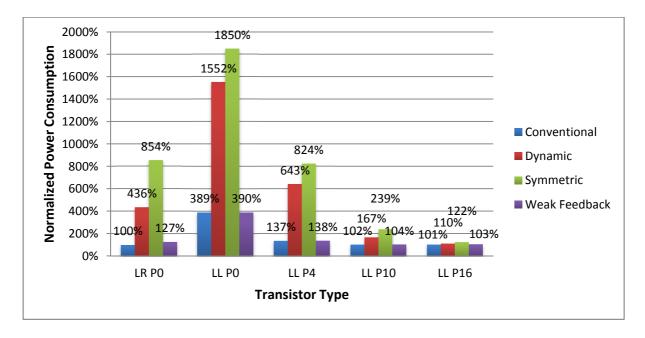

| Figura 29 – Consumo normalizado de um circuito C-Element Conventional com tensão de         |

| alimentação de1,00 V em corners P e N típicos (TT). As normalizações foram feitas em        |

| relação ao consumo do C-Element Conventional com transistor LR P0 TT à mesma tensão. 55     |

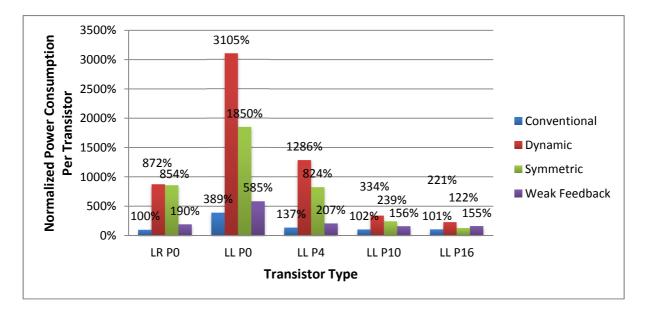

| Figura 30 – Consumo por número de transistores para 4 arquiteturas básicas de C-Elements    |

| em corners P e N típicos (TT) e com tensão de alimentação de 1,00 V. As normalizações       |

| foram feitas em relação ao consumo normalizado por número de transistores do circuto C-     |

| Element Conventional com transistor LR P0 TT à mesma tensão                                 |

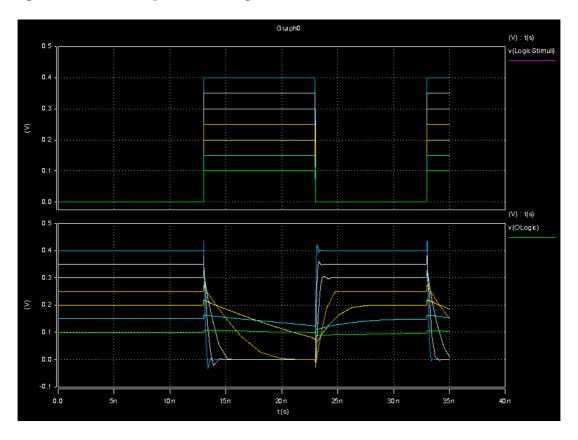

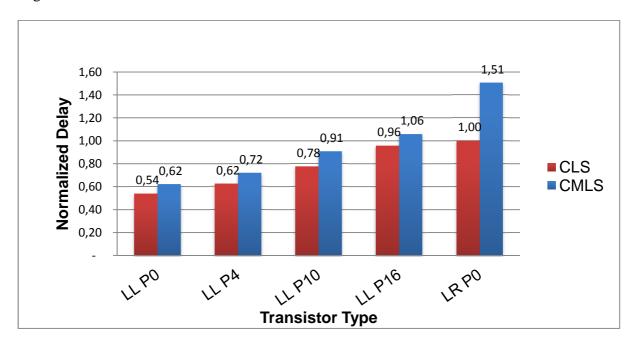

| Figura 31 – Média entre o atraso de subida e de descida para circuitos CLS e CMLS em em     |

| corners P e N típicos (TT) e com tensão de alimentação básica à 1,00 V e com fontes Vhigh e |

| Vlow à 2,00 V e à -2,00 V. As normalizações foram feitas em relação ao consumo              |

| normalizado por número de transistores do circuto CLS com transistor LR P0 TT nas mesmas    |

| tensões                                                                                     |

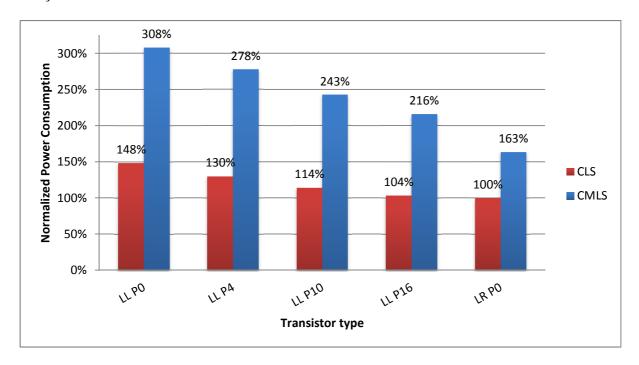

| Figura 32 – Comparativo entre a potência média de circuitos CLS e CMLS em em corners P e    |

| N típicos (TT) e com tensão de alimentação básica à 1,00 V e com fontes Vhigh e Vlow à      |

| 2,00 V e à -2,00 V. As normalizações foram feitas em relação ao consumo normalizado por     |

| número de transistores do circuto CLS com transistor LR P0 TT nas mesmas tensões58          |

# LISTA DE TABELAS

| Tabela 1 Opções de Polybiasing disponíveis para biblioteca standard cell e seus respectivo | S  |

|--------------------------------------------------------------------------------------------|----|

| comprimentos de projeto e comprimentos efetivos                                            | 16 |

| Tabela 2 Tabela verdade de uma porta C-Element de duas entradas                            | 25 |

| Tabela 3 Gama de valores de tensão polarização para os diferentes tipos de transistores    |    |

| disponíveis na tecnologia                                                                  | 29 |

| Tabela 4 Tipos de célula e seus equivalentes em termos de poço, altura de célula e         |    |

| comprimento adicional de polybiasing                                                       | 39 |

| Tabela 5 Configurações de Polarização de substrato para diferentes tipos de transistores   | 47 |

|                                                                                            |    |

# LISTA DE ABREVIATURAS

**BOX: Buried Oxide**

BP: Back Plane

CAD: Computer Aided Design

CLS: Conventional Level Shifter

CMLS: Contention Mitigated Level Shifter

CMOS: Complementary Metal-Oxide-Semiconductor

DIBL: Drain-Induced Barrier Lowering

DIMS: Delay Insensitive Min-terms Synthesis

FB: Function Blocks

FBB: Forward Body Biasing

FD-SOI: Fully Depleted SOI

GO: Gate Oxide

HB: Half-Buffers

HDL: Hardware Description Language

LS: Level Shifter

MOS: Metal-Oxide-Semiconductor

MOSFET: MOS Field-effect transistor

NMOS: N-channel MOS

PMOS: P-channel MOS

PD: Pull-Down

PD-SOI: Partially Depleted SOI

PU: Pull-Up

QDI: Quasi Delay Insensitive

**RBB**: Reverse Body Biasing

RDF: Random-Dopant Fluctuations

SCE: Short Channel Effects

SOI: Silicon On Insulator

UTBB: Ultra-Thin-Body and Buried Oxide

VHDL: VHSIC HDL

VHSIC: Very High Speed Integrated Circuit

WCHB: Weak Conditioned Half-Buffer

# 1 INTRODUÇÃO

Os microprocessadores fabricados atualmente cabem na ponta de nossos dedos, algo que seria inimaginável no começo do desenvolvimento desta área. Toda essa evolução da indústria microeletrônica deu origem a um universo de inventos que nos rodeiam, facilitam e fazem parte de diversas atividades da nossa vida cotidiana. Depois desta tão rápida evolução, os dispositivos tornaram-se, e continuam a se tornar, cada vez menores e mais rápidos. Esta redução de tamanho deu origem ao termo microeletrônica por conta das distâncias envolvidas nos circuitos fabricados e hoje chegamos ao ponto de denominá-la nanoeletrônica. A portabilidade dos equipamentos eletrônicos é algo decorrente disso, bem como o aumento da complexidade e da diversidade de funções lógicas implementadas, permitindo-nos empregá-los nas mais variadas aplicações.

Gordon Moore, em seu clássico artigo "Cramming More Components onto Integrated Circuits" de 1965, previu, com base no histórico da época, que o número de transistores dos chips duplicaria a cada 18 meses (MOORE, 1965). Esta previsão é conhecida como Lei de Moore e comprova-se, desde então, como uma real tendência para a evolução da microeletrônica. Já se sabe que, para dar continuidade à esta lei, deve-se procurar inovar nos diversos níveis de projeto que compreendem a concepção de sistemas microeletrônicos; algo que já vem sendo feito desde os primórdios desta indústria.

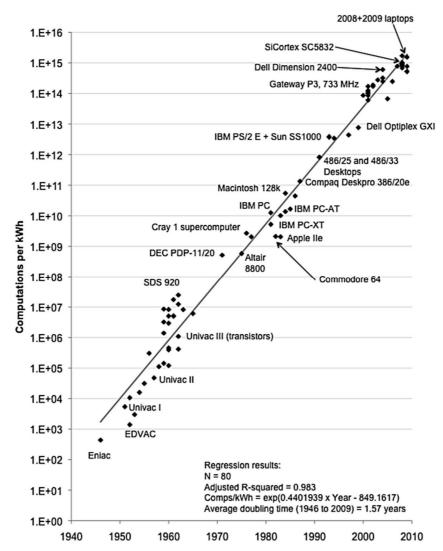

Complementarmente à ideia de G. Moore, porém não tão difundida, há uma outra proposta de análise, feita por Koomey et al. (2011), para a evolução da indústria eletrônica. Esta proposição, denominada de Lei de Koomey, apresenta a evolução do número de computações pelo consumo em kWh entre os anos de 1940 à 2010 e é apresentada graficamente na figura 1. A Lei de Koomey está, portanto, relacionada à eficiência energética dos dispositivos. A recentidade da análise de Kommey para um histórico de algumas décadas é concomitante com o atual interesse na busca por sistemas com menor

consumo de energia. E o consumo de energia é, por sua vez, um fator-chave para a portabilidade de sistemas microeletrônicos.

Figura 1 Evolução histórica da computação por consumo [kWh] os anos de 1940 à 2010 (KOOMEY et al., 2011). A amostra do gráfico consiste de 80 dentre os principais computadores e microprocessadores já desenvolvidos. Uma curva de regressão é também apresentada. O coeficiente de determinação ( $R^2$ ) da curva é igual à 98,3%.

Verifica-se a partir da figura que houve um crescimento considerado do número de dados computados pelo consumo de energia dos circuitos para os principais microprocessadores, resultante dos diversos avanços da área. Todavia, com o recente surgimento de novas tecnologias de transistores com dimensões próximas às dos átomos, evidenciou-se os efeitos físicos que antes eram pouco ou mesmo não influentes.. O impacto destes fatores no desempenho dos transistores tem aumentado cada vez mais, contribuindo

para o aumento das perdas elétricas por corrente de fuga, na aceleração do processo de envelhecimento dos circuitos e na variabilidade do processo de fabricação.

Uma solução atual para a redução dos impactos negativos da miniaturização é a tecnologia *Ultra Thin Body & Buried Fully-Depleted Silicon On Insulator* (UTBB FD-SOI). Esta tecnologia é proveniente da obtenção de *Silicon On Insulator* (SOI). SOI nada mais é do que a criação de uma camada de silício monocristalino sobre uma óxido isolante. O que se produz atualmente com esta tecnologia são wafers que contém esta camada de óxido. A camada de Silício sobre Isolante pode ser produzida atualmente em escala industrial com uma expessura de cerca de 7 nm (ST MICROELECTRONICS, 2014a).

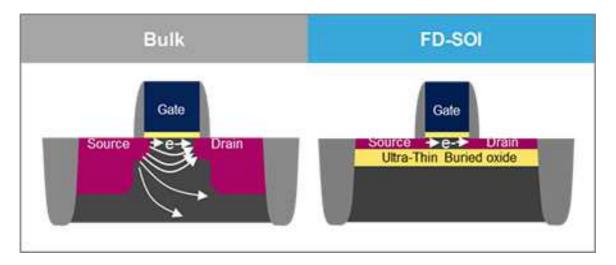

Field Effect Transistors (FET) feitos com estes wafers conseguem gerar um campo elétrico suficientemente forte para que o canal do transistor fique Completamente Depletado. Isso significa que a , quando na ativação do transistor, ocorre a inversão dos portadores desde o óxido de porta até o óxido enterrado. FETs desse tipo são chamados de Fully-Depleted (FD), ou Completamente Depletados. Na figura a seguir, é apresentado um comparativo entre as tecnologias convencional (também chamada de tipo bulk) e de um transistor do tipo Completamente Depletado em substrato SOI.

Figura 2. Representação em corte transversal de transistores em tecnologia convencional (Bulk) e em FD-SOI (ST MICROELECTRONICS, 2014a)

Os inconvenientes da diminuição dos transistores também podem, e devem, ser mitigadas em níveis superiores de abstração do projeto de um circuito integrado. Uma emergente solução é o uso do paradigma de projeto da lógica assíncrona (SPARSØ, 2006). Diferentemente dos circuitos síncronos, que seguem o ritmo do sinal de relógio para a ativação das funções de envio, processamento e registro de informações, os circuitos assíncronos funcionam em função do fluxo de eventos do seus dados através de um protocolo de transferência de informação entre blocos do sistema (BASTOS, 2010; BEREEL, 2010; RENAUDIN, 2000; SPARSØ, 2006).

Uma fusão do uso de dispositivos feitos em tecnologia UTBB FD-SOI, juntamente com a aplicação de uma lógica de concepção assíncrona seria duplamente vantajosa do ponto de vista de redução do consumo de energia. Novas arquiteturas podem ser exploradas a partir das novas possibilidades provenientes da tecnologia FD-SOI e com uso de lógica de concepção assíncrona, permitindo assim novos métodos de redução de consumo.

Este trabalho consiste, portanto, no levantamente do estado da arte e na análise dessas tecnologias para o seu emprego em conjunto no desenvolvimento de sistemas eletrônicos de baixo consumo.

No capítulo 2, a tecnologia FD-SOI será apresentada, da mesma forma que as principais diferenças em relação as tecnologias já maduras. Uma introdução aos circuitos assíncronos é feita no capítulo 3. O capítulo 4 explorará o controle automático e independente da polarização de partes do circuito visando a redução do consumo conforme uso. O capítulo 5 apresenta avaliações de desempenho das células padrão fundamentais dos circuitos assíncronos tirando proveito das vantagens da tecnologia FD-SOI. Por fim, no capítulo 6 serão apresentadas as conclusões e contribuições desta pesquisa, bem como proposições para a continuidade da mesma.

# 2 TECNOLOGIA FULLY-DEPLETED SILICON ON INSULATOR (FD-SOI)

A tecnologia Silicon On Insulator (SOI) consiste na implementação de uma camada isolante de óxido de silício entre duas redes monocristalinas de átomos de silício. Existem diversos métodos desta camada de óxido (CELLER: para obtenção CRISTOLOVENEAUNU, 2003). Por sua vez, Fully-Depleted Silicon On Insulator (FD-SOI) é uma nova tecnologia que faz uso de aperfeiçoados wafers SOI que possibilitam transistores de efeito de campo (FETs) com canais completamente depletados. Ser completamente depletado significa que a espessura da camada de silício sobre isolante é igual à profundidade da região de depleção (SINGH; SAXENA; RASTOGI, 2011).

As perspectivas desta tecnologia não se limitam apenas às características de design, mas passam também pelo aspecto econômico da fabricação de transistores. A fabricante ST Microelectronics (2014a, 2014b) útiliza a vantagem do preço compeditivo para justificar a FD-SOI como uma possibilidade de dar-se continuidade à tendência de evolução da Lei de Moore, já que tecnlogias concorrentes para os mais recentes nodos possuem custo de fabricação maiores (JONES, 2012).

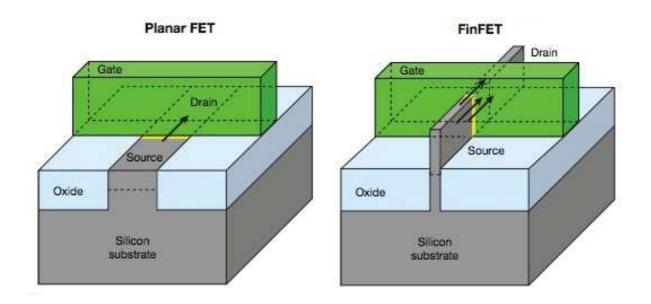

Em concorrência com a FD-SOI, a tecnologia FinFET também é feita em substrato SOI. FinFETs é um novo método de design para transistor de efeito de campo. A figura 3 ilustra o a forma de um transistor FinFET. Os FinFETs também possuem vantagens na busca pela continuidade do processo de miniaturização dos circuitos eletrônicos. Contudo, o processo de fabricação de FinFETs necessita de etapas adicionais específicas que resultam em um aumento de custos. Já a FD-SOI reaproveita boa parte do processo produtivo das tecnologias convencionais, acrescentando poucas etapas suplementares (ST Microelectronis 2014ª, 2014b; SKOTNICKI, 2011. FALTRESSE, 2013).

Este capítulo faz uma apresentação da tecnologia FD-SOI. Na sequência serão vistos o porquê da busca de um substrato SOI e os transistores que podem nele ser feitos. Após, é

visto o processo de fabricação do wafer SOI. Depois, serão tratados questões relacionadas ao óxido enterrado e também à tensão de limiar. Na última parte desta introdução à tecnologia, será visto o processo de variação de consumo e resposta temporal a partir do aumento da largura do canal, denominado de Polybiasing.

Figura 3 – Ilustração de um transistor FinFET. [Adaptado de PAYNE, 2012]

# 2.1 DA TECNOLOGIA SOI À TECNOLOBIA FD-SOI

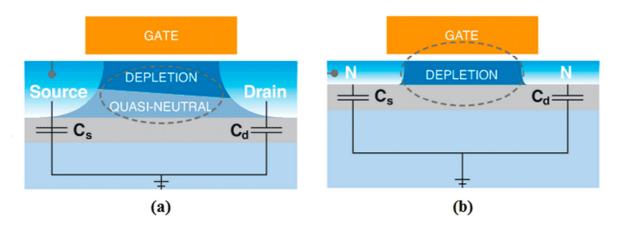

A tradicional tecnologia SOI, industrializada desde o final do século XX, usa um substrato silício-isolante-silício ao invés do histórico substrato de silício dos circuitos integrados convencionais, denominadas de tipo bulk para criar uma distinção entre ambas. A parte a da figura 4 apresenta um corte transversal de dois tipos de depleção de canal que podem ser obtidas em substrato SOI, no qual é possível identificar o dreno ("drain"), porta ("gate") e fonte ("source"). O canal de um transistor formado em um substrato SOI se encontra na camada superior de silício – regiões de azul mais escuro que ficam entre fonte e dreno. É nessa camada que ocorre a formação do canal do transistor. Esta região pode ser

parcialmente ou completamente depletada e isso dependerá da intensidade do campo elétrico produzido pela terminal de porta.

Na parte (a) da figura é apresentado um transistor com canal **parcialmente depletado**, onde ocorre uma abertura parcial da região que compreende desde o óxido de porta (camada em branco na figura, abaixo do "gate") até o óxido enterrado (camada em cinza). A geração de um campo elétrico na região do canal não é, portanto, suficientemente forte para que haja uma inversão completa do tipo de portador majoritário nesta área. Em outras palavras, o canal do transistor é apenas parcialmente depletado. Isso ocorre devido ao processo de fabricação do substrato SOI.

Para as primeiras tecnologias SOI, não era possível de se obter espessuras do cristal de silício e de óxido enterrado suficientemente finas para a formação de uma região de depleção completa (*Fully Depletaded*, FD) como mostra a figura 4b. Na parte (b) da figura, observa-se uma inversão completa dos portadores na região entre óxido, ou seja, obtém-se uma depleção completa do canal do transistor.

Figura 4 – Representação comparativa dos cortes transversais de transistores feitos em tecnologias com canais Parcialmente (a) e Completamente Depletados (b), ambos utilizando wafer SOI. (MENTOR GRAPHICS, 2008)

Com o desenvolvimento recente de um novo processo de fabricação, chamado de SmartCut, finas espessuras de silício do canal (entre 5 e 50 nm) são factíveis (HARS, 2012). Isso permite que o campo elétrico mais forte em toda a região entre-óxidos; o que, por sua

vez, permite a obtenção de canais de transistor completamente depletados e dando origem a tecnologia FD-SOI.

# 2.2 FABRICAÇÃO DE WAFERS PARA A TECNOLOGIA FD-SOI

O interesse pela obtenção de substratos SOI remonta à décadas atrás. A grande dificuldade para a sua obtenção está ligada à obtenção do crescimento de uma camada monocristalina de silício sobre o óxido de silício isolante. Quando isso é feito, obtém-se um silício policristalino, algo como pequenas ilhas de silício cristalino que se tocam. Para que isso fosse possível, alguns processos foram desenvolvidos, tais como o SIMOX e o processo de SmartCut, entre outros (CELLER; CRISTOLOVENEAUNU, 2003; SINGH; SAXENA; RASTOGI, 2011).

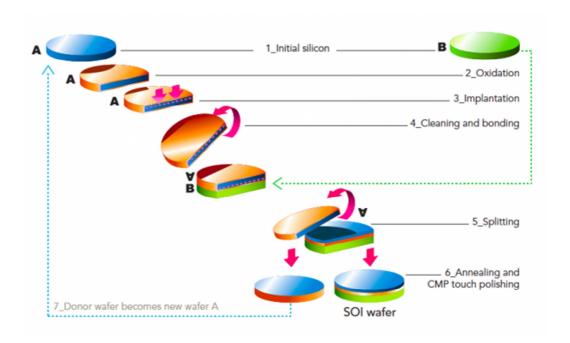

O SmartCut é processo industrial de colagem de wafers para a formação de uma fina camada de silício monocristalino. Este é o processo de fabricação de wafers que permitiu o surgimento da tecnologia FD-SOI, já que a fina camada de silício sobre isolante permitiu a existência de uma intensidade de campo elétrico suficiente para que se faça a inversão completa dos portadores na região entre os óxidos de porta e enterrado. A Figura 5 apresenta o passo-a-passo para a obtenção de um wafer SOI a partir desta tecnologia.

Portanto, podemos dividir o processo SmartCut da seguinte forma:

- 1. Inicia-se o processo de fabricação com dois wafers de silício convencionais (A e B);

- 2. O wafer A passa por um processo de oxidação;

- 3. Depois de oxidado, o wafer A passa pela implantação iônica;

- 4. E, em seguida, o mesmo wafer A passa por um processo de limpeza necessário para colá-lo com o wafer B;

- 5. Depois de colados, é feito um corte em um plano paralelo ao do wafer;

- 6. Um dos wafers obtidos do corte resulta no wafer SOI, que dá origem à tecnologia FD-SOI, constituído de uma fina camada de silício monocristalino na ordem de 7 nm sobre uma camada de óxido enterrado com espessura na ordem de 25 nm (podendo ser ainda menor) que, por sua vez, repousa sobre o segundo wafer (B);

- 7. O outro wafer resultante do corte torna-se um novo wafer (A) que pode ser reaproveitado na fabricação de novos substratos.

Figura 5 – Etapas do processo SmartCut para a fabricação de wafers da tecnologia FD-SOI (HARS, 2012)

# 2.3 ÓXIDO ENTERRADO

Na tecnologia FD-SOI 28nm, um transistor possui um canal de espessura máxima de aproximadamente 7 nm. O canal do transistor e o substrato são separados por uma pequena camada de óxido enterrado (*Buried Oxide*, BOX) (~ 25 nm), denominada *Ultra Thin Body & Buried* (UTBB).

Em alguns trabalhos da literatura especializada, o substrato na tecnologia FD-SOI (região abaixo da camada de óxido enterrado) é também chamado de *Back-Plane* (BP) (HAMON, BEIGNE, 2003). Desta forma, é possível de diferenciá-lo do substrato normal,

onde o mesmo é denominado de *Body* (corpo). *Back-Plane* pode ser traduzido como Plano de Fundo. A isolação entre o canal e o plano de fundo nos permite fazer 3 diferentes constatações:

- a) Exite uma isolação que dificulta o surgimento de uma corrente entre o plano de fundo e a Fonte/Dreno (CRISTOLOVENEAUNU, LI, 1995; CELLER, CRISTOLOVENEAUNU, 2003.);

- b) O canal do transistor é não-dopado, a não dopagem elimina as variações relativas à dopagem de canal, denominada de Random Dopant Fluctuation (RDF) (HAMON, BEIGNE, 2013; ST MICROELECTRONICS 2013; NAZAROV et al., 2011), enquanto que o ajuste da tensão de limiar é feito pelo metal da porta (NAZAROV et al., 2011); e

- c) A dopagem de fundo não precisa ser mais obrigatoriamente oposta à dopagem de canal, fonte e dreno; realizando-se, portanto, uma inversão do estilo de dopagem usado até hoje em FETs do tipo *bulk*. (HAMON, BEIGNE, 2003; JACQUET 2013).

Diretamente observa-se que a camada de óxido isolante existente entre o BP e o canal impede/dificulta o surgimento de correntes de fuga entre estes dois planos. Desta maneira, é possível dizer que o consumo do dispositivo é menor, devido à menor quantidade de perdas por correntes de fuga entre substrato, canal, Fonte e Dreno.

Randon-Dopant Fluctuations (RDF) são as variações na concentração de impurezas implantadas. Quando isso ocorre no canal do transistot, características como a tensão de limiar variam de um transistor para outro. Como a quantidade total de átomos que constituem o canal do transistor é cada vez menor para as novas tecnologias, uma diferença pequena na quantidade de impurezas, como um átomo a mais ou a menos em relação a quantidade total, tem um impacto mais significativo na performance do dispositivo. RDF é reconhecido como

um dos efeito de variabilidade do processo que tem se tornado cada vez mais influente para os últimos nodos de tecnologia. Como o canal do transistor é não dopado, efeitos de RDF no canal do transistor são elimidados (HAMON, BEIGNE, 2003).

A inversão do tipo de dopante do plano de fundo abre possibilidades relacionadas à amplitude de tensão que pode ser aplicada sobre ele. Esta tensão influencia a Tensão de Limiar, a qual será tratada a seguir.

# 2.4 TENSÃO DE LIMIAR

A Tensão de Limiar (*Threshold Voltage*) nada mais é do que a menor diferença de potencial elétrico entre fonte e dreno necessária para a formação do canal de condução. O fator de substrato (*body-effect coeficient*) é, por sua vez, uma medida do grau de influência da polarização do substrato do transistor (*Body Biasing*, BB) na sua Tensão de Limiar (RABAEY, 2003). Para compreender melhor como essa influência e a relação com outras variáveis, pode-se observar a equação que define a Tensão de Limiar, obtida a partir do modelo de Shichman-Hodges:

$$V_{T} = V_{T0} + \gamma (\sqrt{|-2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|})$$

(1)

Onde:

V<sub>T</sub> é a Tensão de Limiar;

$V_{SB}$  é a Diferença de Potencial entre o Contato de Substrato (*Body Contact*) e o Contato da Fonte (*Source Contact*);

$V_{T0}$  é Tensão de Limiar para  $V_{SB}=0$ , normalmente dependente do processo de fabricação;

$\emptyset_F$  (Fi)é o Potencial de Fermi; e

$\gamma$  (gamma) é o chamado coeficiente de corpo, fator de substrato ou *body-effect* coefficient.

Vale observar que, para um FET convencional, a Tensão de limiar é positiva para transistores MOS do tipo N (NMOS) e negativas para transistores do tipo P (PMOS) (RABAEY, 2003). Observa-se também que quanto maior for o fator de substrato ( $\gamma$ ), maior será a influência da tensão de substrato, ou plano de fundo para a tecnologia FD-SOI, na Tensão de Limiar.

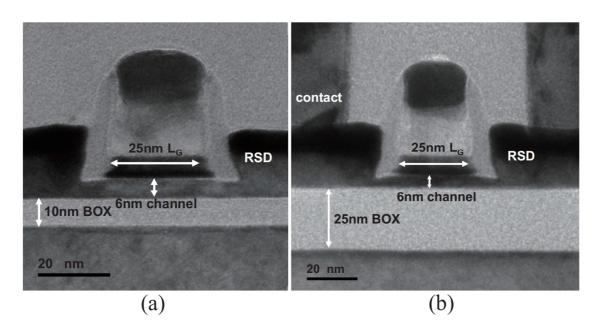

Um estudo de Cattaneo (2009) sobre o comportamento de transistores em tecnologia SOI mostrou que o efeito de corpo das tecnologias SOI é menor do que em outras tecnologias devido principalmente à espessura do óxido enterrado. Porém, transistores em tecnologia SOI com óxido ultra-fino enterrado possuem efeito de corpo mais expressivo do que outros tipos de transistores dessas tecnologias SOI precedentes (HAMON; BEIGNE, 2003; OHTOU; SARAYA; HIRAMOTO, 2008; NOEL et al., 2011).

O impacto da espessura do óxido fica evidente a partir do estudo comparativo entre o efeito de corpo de BOX com 10 e 25 nm feito por Liu et al. (2011), figuras 6 (a) e 6 (b), respectivamente. As modulações da Tensão de Limiar obtidas neste estudo foram:

- a) de 120 mV/V, para um BOX de 10 nm; e

- b) de 60 mV/V, para um BOX de 25 nm.

Figura 6 – Transistores FD-SOI com BOX de 10 nm (a) e de 25 nm (b). (LIU et al., 2011)

Um melhor efeito de corpo influencia diretamente no comportamento do transistor – suas velocidades de transição e suas correntes de fuga – quando na aplicação de uma polarização do BP. Quanto menor for a magnitude da Tensão de Limiar, por exemplo, mais fácil será a sua ativação, visto que é ativado por tensões de porta menores. Pode-se dizer igualmente que, para uma tensão menor, mais facilmente ocorrerá a passagem de corrente entre os terminais de Fonte e Dreno. Porém, o mesmo resulta em uma maior corrente de de subthreshold, decorrente da redução da energia necessária para que os elétrons atravessem a barreira de potencial existente entre Dreno e Fonte.

Opostamente à uma redução da Tensão de Limiar, o seu aumento também apresenta as suas vantagens e desvantagens. Com uma magnitude de Tensão de Limiar maior, maior será a barreira de potencial para a passagem dos elétrons. Portanto, será mais dificil que ocorra a condução do transistor, diminuindo assim as perdas por corrente de funga. Contudo, o mesmo resulta em transistores mais lentos.

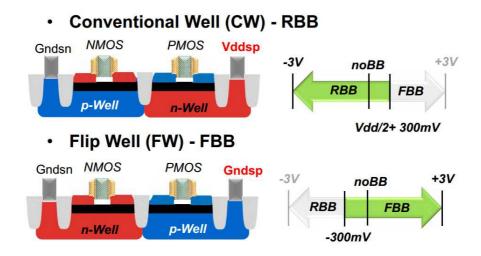

Quanto à inversão do BP, a mesma permite uma configuração a qual seria impossívem para tecnologias MOS anteriores. Um canal com mesmo tipo de dopantes que a Fonte e o Dreno seria um curto circuito e não um transistor. Essa inversão do BP é chamada de *Flip-Well* (FW), ou Poço Invertido, e um comparativo entre os dois tipos de substrato (invertido e convencional) é apresentado na figura 7.

Para distinguir um tipo de poço do outro, o tipo tradicional/convencional é chamado de Poço Convencional (*Conventional Well*, CW). Existe ainda um terceiro tipo de poço, o *Single-Well*. Este terceiro tipo, como seu nome o descreve, apresenta um poço único. No entanto, este tipo de poço não é utilizado neste trabalho. Com um poço único, aumentar a tensão de limiar para um tipo de transistor, reduziria a tensão de limiar para o seu complementar.

Observa-se na figura 7 que a inversão do poço inverte também as conexões da junção PN entre os dois poços. As amplitudes de tensão, as quais são limitadas pela corrente de polarização direta e reversa da junção, são inverdidas. No caso de um poço invertido, e considerando-se as novas amplitudes de tensão, os transistores podem ser mais rápidos quando polarizados com uma tensão adequada. A direita na imagem da figura 7 são apresentadas as amplitudes de tensão possíveis nas duas configurações de poço para a tecnologia FD-SOI 28nm.

Figura 7 - Configurações de poço convencional (Conventional Well) e poço invertido (Flip-Well) em tecnologia FD-SOI juntamente com suas respectivas margens de tensão de polarização de substrato (FLATRESSE, 2013).

Em uma configuração de substrato convencional, procura-se aplicar tensões de polarização que não causem a condução direta da junção PN existente entre os dois poços. Com um poço convencional, a polarização pró-condução (para a redução de  $V_{th}$ ) podem chegar a, no máximo, cerca de 300 mV.(FLATRESSE, 2013; JACQUET, 2013), conforme ilustrado na figura 7. Esta configuração de alimentação pró-condução é chamada de *Forward Body Biasing* (FBB). No modo FBB há uma redução da Tensão de Limiar devido ao fator de substrato e com isso o transistor se torna mais rápido. Em uma configuração do tipo *Flip-Well*, esta polarização pode variar até o valor da própria alimentação ou até mesmo valores maiores (HAMON; BEIGNE, 2013; FLATRESSE, 2013; JACQUET, 2013).

Por outro lado, há um aumento da corrente de fuga entre Fonte e Dreno devido a uma tensão de threshold (HAMON; BEIGNE, 2013). Este tipo de configuração é interessante para certas aplicações, ou mesmo para partes do circuito onde transistores mais rápidos são necessários. Nesta configuração (*Flip Well*), e juntamente com a inserção de um controle de polarização, é possível de obter-se o modo FBB quando necessário ou até mesmo o seu oposto RBB (*Reverse Body-Biasing*).

O processo de ativação/desativação permite, portanto, uma redução do consumo estático em períodos de desuso. O mesmo é sugerido pela ST Microelectronics em introduções e migração de tecnologias *bulk* para FD-SOI. Sinais de ativação/desativação são abundantes em alguns tipos de lógica de concepção de circuitos assíncronos (HAMON, BEIGNE, 2003), que será apresentada com mais detalhes no capítulo 3.

# 2.5 POLYBIASING

Polybiasing nada mais é do que a variação, em tempo de projeto, do comprimento do canal do transistor, ou seja, do polisilício de porta. A figura 8 serve para elucidar o que é o polybiasing e como o mesmo é feito em projeto.

# From 24nm (PB0) up to 40nm (PB16) (a) (b) (c)

Figura 8 – Apresentação do comprimento do polisilício (a) em um corte transversal de um transistore FD-SOI. Ilustração da variação do comprimento do canal entre mínimo/original (b) e aumentado/alargado (c). (FLATRESSE, 2013)

Na parte (a) da imagem, pode-se ver a dimensão do comprimento do canal do transistor com um exemplo de seção transversal de um transistor feito em tecnologia FD-SOI. Na parte (b) é mostrado um exemplo de como seria uma vista de uma ferramenta de *Computer Aided Design* (CAD) com o transistor desenhado com o comprimento mínimo de canal. As regiões em verde são a Fonte e Dreno e a parte em vermelho é o polisilício de porta. Na parte (c) da imagem, é mostrado como é feita a variação do comprimento do canal do transistor em relação à parte (b) para que se obtenha o efeito de polybiasing. Observa-se que o desenho do comprimento de porta maior é feito apenas na região do canal do transistor.

A variação do comprimento do canal resulta na alteração da Tensão de Limiar. Isso se faz da seguinte forma: quanto maior for o comprimento do canal, maior é o valor desta tensão. O emprego de comprimentos de canal de transitor simula uma resposta de tecnologias com comprimentos de canal maiores. Porém, a tecnlogia de fabricação com nodos menores possuem vantagens quando comparadas à qualidade de fabricação de transistores de nodos maiores. A variação dos valores de  $V_{th}$  com o uso dos desenhos permite a fabricação de circuitos compatíveis com arquiteturas multi-Vt. Além disso, conforme escolhas de projeto, pode-se usar diferentes valores de polybiasing para obter-se desempenhos e consumos diferentes.

O design kit da tecnologia FD-SOI 28nm da ST Microelectronics apresenta uma biblioteca stardard cell com 4 opções de comprimento de canal, conforme apresentado na tabela 1. Cada um representando, portanto, uma opção de polybiasing que varia de 0 à 16 nm (P0 à P16). Seu conprimentos efetivos variam, neste caso, de 24 (mínimo) à 40 nm (máximo).

Nota-se que, para a tecnologia de 28nm, o canal do transistor possui uma comprimento mínimo de desenho de 30 nm. Para esse comprimento de projeto, o comprimento efetivo – que é a distância real entre os terminais de Fonte e Dreno - será de 24 nm. A diferença entre as duas distâncias deve-se à difusão dos dopantes por baixo do óxido de porta.

Tabela 1 Opções de Polybiasing disponíveis para biblioteca standard cell e seus respectivos comprimentos de projeto e comprimentos efetivos.

| Opção de<br>Polybiasing | Comprimento de projeto [nm] | Comprimento<br>Effetiva [nm] |

|-------------------------|-----------------------------|------------------------------|

| P0                      | 30                          | 24                           |

| P4                      | 34                          | 28                           |

| P10                     | 40                          | 34                           |

| P16                     | 46                          | 40                           |

As diferenças entre a nomenclatura entre desenho (30 nm mínimo), a distância de referência da tecnologia (28 nm) e a distância efetiva (24 nm) são resultantes de decisões comerciais.

#### 2.6 CONCLUSÕES

Neste capítulo foram vistos o processo de fabricação de um substrato SOI, como se obter um transistor FD-SOI. Uma atenção foi também dada aos diferenciais de um transistor em FD-SOI em termos de fabricação, consumo de energia, perspectivas de continuidade da mesma devido ao menor custo e perspectivas de novos nodos.

Na busca por circuitos mais econômicos, as isolações adicionais viabilizadas pelo óxido enterrado ganham destaque na busca pela redução de perdas de energia. Mas resta também a busca pela economia em outros níveis da concepção.

Observa-se também uma possibilidade do uso do bom efeito de corpo que é destacado para a tecnologia FD-SOI. O melhor efeito de corpo vai de encontro com a procura por técnicas que possam ser integradas na variação de características elétricas do circuitos, viabilizando escolhas de comportamento elétrico conforme necessidade. A referida variação de características elétricas pode muito bem ser dependente do estado no qual um circuito se encontra. Seria interessante variar-se a velocidade do sistema conforme a necessidade. Regiões não utilizadas podem muito bem ser colocadas em um modo de operação mais econômico; e isso é possível através da variação da tensão de limiar.

Porém, é necessário que se identifique o uso ou não do circuito ou de regiões dele. Circuitos Assíncronos fazem uso de sinais através de protocolos de comunicação para descrever a execução ou o fim da execução de processamento. Sinais esses que podem muito bem ser utilizados para identificar a necessidade de variar-se a polarização dos transistores. No capítulo seguinte, tratar-se-á dos circuitos assíncronos, seu funcionamento e estrutura.

# 3 CIRCUITOS ASSÍNCRONOS

Circuitos assíncronos são também denominados de self-timed circuits (circuitos de tempo próprio ou auto-temporizados). A lógica de concepção assíncrona não é uma idéia nova e pode-se dizer ainda que os primeiros circuitos lógicos possuiam esta lógica de concepção, já que os mesmos não faziam uso de sinal de relógio (*clock*). Sua lógica de funcionamento se baseia em sinais que indicam a conclusão de instruções (*handshake protocol*). Esses sinais são usados através de protocolos de transferência de dados que ativam ou não a alteração de registradores (RENAUDIN; RIGAUD, 2000; BEEREL ;OZDAG; FERRETTI, 2010; SPARSØ, 2006).

Como os sinais de relógio não são necessários em circuitos assíncronos, as perdas na difusão desta informação no circuito são eliminadas. Concomitantemente, a não existência de sinal de relógio resulta em uma menor Interferência Eletromagnética (EMI, do inglês: *Electromagnetic Interference*) entre linhas de relógio e outras (BEEREL ;OZDAG ; FERRETTI, 2010; SPARSØ, 2006). Conforme demonstrado por Berkel et al. (1994), circuitos assíncronos podem ser substancialmente mais econômicos em termos de consumo de energia. A economia de energia, em relação à um circuito síncrono, pode cehgar a 80% conforme demonstrado por (BERKEL et al. 1994) em um circuito corretor de erros de um *Digital Compact Cassete*.

Sabendo-se que algumas funções lógicas necessitam de tempos de execução menores do que seria um ciclo de relógio para serem concluídas, um circuito assíncrono é capaz de ser mais rápido que circuitos síncronos de mesmas ou similares funções. Estes circuitos são limitados, portanto, apenas pelo atraso de propagação da informação (BEEREL ;OZDAG ; FERRETTI, 2010.). Há também uma menor dependência da variabilidade de características elétricas (Tensão de Limiar, velocidade etc) decorrentes do processo de fabricação ou mesmo

por condições de temperatura, algo que é cada vez mais significativo nas tecnologias mais atuais (BEEREL ;OZDAG ; FERRETTI, 2010.).

Entretanto, circuitos assíncronos podem necessitar mais área para a concepção de sua lógica. Isso se deve principalmente à necessidade dos circuitos de controle (BEEREL; OZDAG; FERRETTI, 2010.). Sendo maior a área, maiores serão as superfícies de contato por onde circulam as correntes de fuga. Deste modo, uma maior área pode resultar em um aumento do consumo por perdas, principalmente as estáticas (SPARSØ, 2006). Sabendo-se que a grande maioria dos circuitos eletrônicos produzidos segue uma lógica de concepção síncrona, as ferramentas de auxílio à concepção são majoritariamente feitas para este fim. A ausência de ferramentas de teste e vetores de testes também é, pelo mesmo motivo, uma problemática clássica da concepção assíncrona (SPARSØ, 2006).

Por terem principios de funcionamento diferentes das lógicas de concepção síncrona, as etapas de concepção de circuitos assíncronos são necessariamente também diferentes. Sendo assim, a concepção de um circuito assíncrono passa por 3 etapas: definição do modelo de atrasos do circuito, definição do protocolo de *handshake* com 2 ou 4 fases (ver item 3.2) e a escolha dos componentes básicos (MOREIRA; GUAZZELLI; CALAZANS, 2012).

O atraso significa a definição do tempo de propagação da informação no circuito, necessário para as definições das condições de funcionamento dos circuitos. O modelo mais simples, e também o mais otimista, é o de atraso fixo, onde se conhece o tempo de propagação. Um segundo é um atraso entre valores mínimo e máximo (min-max delay); com atraso desconhecido mas limitado entre  $t_{min} < t_{atraso} < t_{máximo}$ . O modelo mais pessimista analisa o circuito sem prever tempos de atraso que variam entre  $0 < t_{atraso} < \infty$ ; e, portanto, este modelo é possui atraso ilimitado ( $unbounded\ delay$ ) (SPARSØ, 2006).

O modelo de atraso está intimamente ligado à classe de circuito assíncrono a qual o circuito pertence. Diversas literaturas exploram com mais profundidade as classes de

assíncronos, como Renaudin e Rigaud (2000), SparsØ (2006), Beerel, Osdag e Ferretti (2010) entre tantos outros. A seguir serão descritos resumidamente os 5 tipos de classes de circuitos assíncronos existentes conforme as literaturas mensionadas anteriormente.

**Huffman** ou máquinas sequenciais assíncronas. Esta classe é a origem dos circuitos assíncronos. Estes circuitos são concebidos a partir de portas lógicas, onde são gerados os sinais para os próximos estados e possuem um modelo de atraso limitado (*bounded-delay*).

*Micropipeline* são circuitos onde há um sequenciamento local da informação. Sua execução baseia-se em sinais de verificação, ao invés do uso de sinal de relógio. Por conta dos sinais de verificação, o modelo de atraso é ilimitado nas partes onde são executadas as funções lógicas. Porém, no caminho dos dados, é utilizado um modelo de tempo limitado.

Speed Independent são circuitos que utilizam um modelo de atraso ilimitado em todas as suas portas. Em seu modelo, os atrasos na parte de transmissão são considerados insignificantes ou menores em relação aos das portas. Porém, as linhas de transmissão se tornam cada vez maiores e mais complexas e a afirmação de que os atrasos sejam insignigicantes ou menores do que as portasnão pode ser garantida.

**Delay Insensitive** (DI) são similar aos circuitos Speed Independent; porém, o fator de atraso ilimitado é estendido também as linhas de transmissão. Conforme descrito por Martin (1990), a implementação deste tipo de lógica é limitada e não prática.

*Quasi Delay Insensitive* (QDI) é a solução assíncrona mais robusta e factível, e tratase do tipo de implementação estudado neste trabalho e apresentado a seguir.

#### 3.1 QUASI INSENSÍVEIS AO ATRASO

Quasi Delay Insensitive – Quasi-Insensíveis aos Atrasos – é uma das diferentes classes de circuitos assíncronos e lembra a implementação de uma classe Delay Insensitive. Porém, diferentemente de um circuito DI, em um circuito QDI existe um caso no qual o

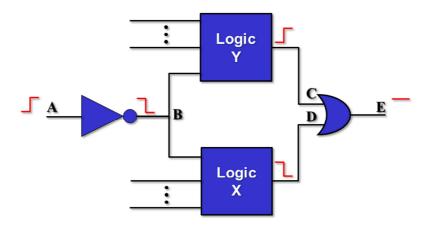

atraso não é ilimitado. É necessário que alguns pontos críticos do circuito sejam isocrônicos (MARTIN, 1990), ou seja, precisam ter tempos de atraso parecidos para a execução em conjunto das instruções lógicas. Para tanto, um circuito QDI utiliza um modelo de atraso ilimitado para todas as suas portas e para **quase** todas as linhas de transmissão. Com isso, um dado tratado por duas ou mais partes lógicas do circuito apresentará tempos de propagação semelhantes. Caso estes sinais se reencontrem em um ponto mais a diante do circuito, chegarão aproximadamente ao mesmo tempo. A Figura 9, a seguir, ilustra o que acontece com um sinal, originalmente igual no **ponto B**, quando se propaga por dois caminhos diferentes e chega à dois pontos isocrônicos do circuto lógico, **ponto C** e **ponto D**.

Figura 9 – Exemplo de uma confluência isocrônica: a variação dos sinais C e D são resultado da variação de um mesmo sinal (sinal B) e devem chegar na porta OR com uma diferença temporal não significativa.

Conforme a Figura 9, o sinal gerado chega em um ponto de divisão (**sinal B**) após passar pelo primeito inversor lógico. Este sinal passa por dois caminhos diferentes: Supõe-se para esse exemplo que ambos os circuitos X e Y tenham as demais entradas constantes. A variação do **sinal B**, na condição do exemplo, resulta em uma mesma variação idêntica para a **entrada D** da porta OR de duas entradas (também saída do circuito X). Já o **sinal B** que passa pelo circuito Y resulta no **sinal C**, que chega na outra entrada da referida porta OR.

Sendo o circuito da figura 9 isocrônico, a porta OR não deverá apresentar alteração perceptível para as portas adjacentes à sua saída (**sinal E**).

Circuitos QDIs são compostos basicamente de portas C-Elements (ver subção 3.3 C-Element, específica para este elemento de circuito) (BASTOS, 2010). Os mesmos permitem a propriedade característica do nome desta classe e, também, a sincronização entre diferentes estágios do circuito. Para que esse processo de sincronização seja realizado, se faz necessário o uso de um protocolo de comunicação (apresentado na subseção 4-phase protocol) para ativar e desativar a execução de operações lógicas.

Existem diferentes estilos de projeto de circuitos QDI: Weak Conditioned Half Buffer (WCHB), Pre-Charged Half-Buffer (PCHB), Null-Convention Logic, Delay Insensitive Minterm Synthesis (DIMS), entre outros (BEEREL; OSDAG; FERRETTI, 2010; SPARSØ, 2006). Uma análise mais aprofundada destes estilos fugiria do escopo deste trabalho. Porém, um exemplo demonstra mais claramente como um circuito QDI funciona e como é sua arquitetura. Na figura a seguir, é apresentada a estrutura lógica de um estágio para um circuito QDI.

Figura 10 - Estrutura de um circuito QDI em analogia à um circuito síncrono. (BASTOS, 2010)

Na figura 10, as ligas de dados **Data0** e **Data1** carregam a informação. O sinal de confirmação é enviado no sentido inverso, para informar que a ação foi terminada ou não. Cada estágio é composto por um bloco lógico computacional e elementos de memória.

#### 3.2 PROTOCOLO DE 4 FASES

Existem duas formas básicas de protocolos para circuitos assíncronos: com 2 ou 4 fases. Um protocolo tradicional de comunicação utiliza 2 fases para realizar um ciclo computacional. As transições que definem em qual das duas fases o circuito se encontra.

Um protocolo de 4 fases (4-Phase Protocol) consiste no uso de pelo menos três sinais: demanda/pedido (request), confirmação (acknowledge) e um ou mais sinais de dados (data). A implementação em protocolo de 4 fases é mais simples do que uma implementação em protocolo de 2 fases. A implementação mais simples se dá em decorrência da distinção entre fases ser feita em nível lógico (FRAGOSO, 2005). Porém, isso resulta em um circuito mais lento do que a execução em protocolo de comunicação em 2 fases (MOREIRA; GUAZZELLI; CALAZANS, 2012). Mesmo assim, as vantagens do protocolo de 4 fases se sobressaem, fazendo com que o mesmo seja o mais utilizado (MOREIRA; GUAZZELLI; CALAZANS, 2012; GREAVES, 2013).

Na figura 11 são apresentadas as 4 fases deste protocolo. A primeira linha apresenta as entradas neste estágio do circuito; a segunda, a saída; e a terceira, o sinal de confirmação do mesmo estágio. Na primeira fase, os dados válidos são detectados e processados; o sinal de confirmação passa para 0 após a detecção do início da saída de dados válidos. A segunda fase consiste na continuação desta até que a entrada de dados válidos esteja concluída. Na terceira fase, conclue-se o tratamento dos dados. Por último, o sinal de confirmação passa para 1 na quarta fase, indicando que o processo foi concluído.

Figura 11 - Comunicação entre dois estágios através de 4-Phase Protocol. (BASTOS, 2010)

Este tipo de protocolo apresenta sinais de conclusão de processamento, ou seja, possui sinais que indicam quando aquele estágio não é mais necessário. Este tipo de sinal é interessante para a detecção do fim da necessidade de ativação de um ou mais estágios. Sinais que indicam atividade podem muito bem ser utilizados no controle de consumo, por meio da ativação das células requisitadas.

#### 3.3 C-ELEMENT

Células C-Element, ou também denominado Muller C-Gate é um elemento de memória normalmente usado em circuitos assíncronos. O princípio de funcionamento de um C-Element de duas entradas é representado na tabela 2 através de uma tabela verdade.

Tabela 2 Tabela verdade de uma porta C-Element de duas entradas.

| A(n) | B(n) | Y(n)             |

|------|------|------------------|

| 0    | 0    | 0                |

| 0    | 1    | Y(n-1)           |

| 1    | 0    | Y(n-1)<br>Y(n-1) |

| 1    | 1    | 1                |

Esta tabela exemplifica as duas possíveis funções lógicas deste tipo de circuito:

- a) A de Buffer, quando suas entradas A e B são idênticas; e

- b) A de memória, preservando o valor anterior no caso de suas entradas A e B serem distintas;

Nota-se aqui que o funcionamento de uma porta C-Element é equivalente ao de um Latch SR. Porém, portas SR não garantem o atraso ilimitado, já que não se pode assegurar que suas duas entradas serão igual à 1 simultaneamente (WUU; VRUDHULA, 1993). O mesmo não ocorre com circuitos C-Elements, já que a alteração de estado só ocorre depois que as duas entradas passam a ter o mesmo valor. Devido ao seu funcionamento, portas Muller podem ser também usadas na sincronização de diversos sinais. Existem diversas arquiteturas para circuitos C-Elements, dentre estas, as quatro mais básicas são:

a) C-Element Conventional (Convencional);

- b) C-Element Dynamic (Dinâmica);

- c) C-Element Symmetric (Simétrica); e

- d) C-Element Week Feedback (de Realimentação Fraca).

As quatro arquiteturas fundamentais formam uma boa base para interpretação das funcionalidades e de suas possíveis aplicações. Cada uma possui suas vantagens e desvantagens. Para compreender e comparar cada uma delas, seus esquemáticos elétricos são apresentados na figura 12.

Figura 12 - Esquemáticos dos 4 tipos básicos de C-Elements: Dynamic (A), Conventional (B), Symmetric (C) e Weak Feedback (D). (BASTOS, 2010)

Observa-se que a única arquitetura de C-Element que não faz uso de realimentação é a do tipo Dynamic. Esta realimentação, conforme apresentado na figura acima, liga os pontos **n10** e **n4** do circuito. A arquitetura do tipo conventional possui realimentação que depende também de suas entradas. A do tipo *Symmetric* possui um processo de redundância, com a repetição das entradas com transistores em ordem inversa. Por último, a arquitetura do tipo

Week Feedback, possui uma realimentação feita apenas com um inversor lógico que possue as dimenções mínimas da tecnologia.

#### 3.4 CONCLUSÕES

Este capítulo tratou das características básicas de circuitos assíncronos. Foram vistos os principios de funcionamento e projeto de circuitos assíncronos; as suas principais classes; o funcionamento do processamento de dados juntamente com um protocolo de comunicação; e as células de registro C-Elements.

Foi mostrado que a classe QDI apresenta diversas vantagens quando comparadas às outras. Além disso, um protocolo de comunicação com 4 fases possui uma implementação mais simples. Os 4 tipos básicos de C-Elements apresentam diferentes vantagens e a escolha da arquitetura depende da aplicação do circuito. Por fim, dentre algumas outras vantagens deste tipo de lógica de concepção, pode-se citar

- a) A possibilidade de ser mais econômicos em termos de consumo de energia;

- b) Uma menor interferência eletromagnética e problemas de distribuição do sinal de relógio, ambos devido à inexistência e não necessidade deste sinal (SPARSØ, 2006);

- c) A possibilidade de serem ainda mais rápidos do que seus respectivos circuitos síncronos de mesmas funções (SPARSØ, 2006); e

- d) Uma maior robustez contra variações de alimentação, temperatura e outras devidas ao processo de fabricação (SPARSØ, 2006).

#### 4 CONTROLE DE POLARIZAÇÃO DE SUBSTRATO

O controle de polarização de substrato é uma forma de controle do consumo de energia de sistemas eletrônicos. O mesmo consiste no uso de diferentes tensões de polarização de FETs para reduzir automaticamente o consumo do circuito em períodos de não-uso.

Beigne & Hamon (2013) propuseram um esquema para sistemas assíncronos que utiliza os sinais do fluxo de dados para criar um controle de consumo automático em tecnologia FD-SOI. Para fazê-lo, criaram mecanismos de identificação dos eventos nos blocos lógicos dos sistemas assíncronos. Esta identificação resulta em um sinal de controle que, por sua vez, ativa a polarização do substrato através de células de aceleração diminuindo o  $V_{th}$  quando há uma atividade no caminho de dados do sistema. Quando o circuito termina de ser utilizado, gera-se um sinal de controle para inverter a polarização dos transistores, aumentando seu  $V_{th}$  e diminuindo seu consumo e sua velocidade.

Nas próximas sessões, o conceito de célula de aceleração será apresentado; bem como o uso de células Level Shifter de tensão para exercer essa funcionalidade. Na sequência, serão apresentados os tipos de Desviadores de Nível. O Desviador de Nível Convencional é apresentado na sequência, seguido do desviador com contenção mitigada.

#### 4.1 CÉLULAS DE ACELERAÇÃO

Para realizar a tarefa de converter os sinais de controle em ativação/desativação da polarização, criou-se o conceito de *Boost Cells*. As *Boost Cells* podem ser consideradas como Células de Aceleração para o circuito o qual promovem alimentação para a polarização de substrato. O conceito de acelerar células vem do fato de que o uso de Células de Aceleração resulta na possibilidade de se obter, para um mesmo circuito, transistores mais rápidos ou

mais lentos conforme a tensão de polarização fornecida. Em outros termos transistores mais rápidos ou mais lentos possuem, respectivamente, maior ou menor consumo de energia.

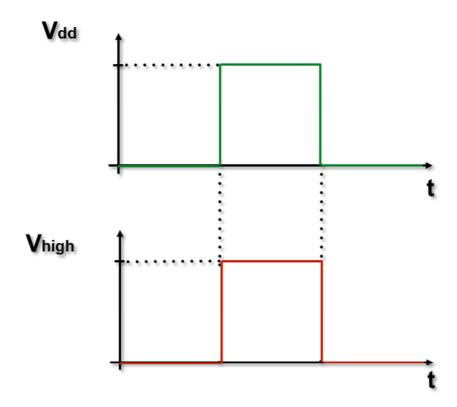

Os sinais de controle para uma Célula de Aceleração variam entre os valores 0 e 1 lógicos, ou, respectivamente, entre os valores de terra (*Ground*, **GND**) e de alimentação positiva (**Vdd**). Sua saídas, porém, variam:

- a) de 0 V (GND) à um segundo valor de tensão Vhigh (normalmente igual ou maior que Vdd) para a parte do circuito que é polarizada com tensões positivas; e

- b) de 0 V à **Vlow** (valor igual ou menor que **GND**) para a parte que possui polarização com tensões negativas.

Os valores de tensão de saída são, portanto, diferentes daqueles provenientes dos sinais de controle. Em suma, uma Célula de Aceleração deve converter valores de tensão: trabalhando com dois valores de entrada (GND e Vdd) e três de saída (Vlow, GND e Vhigh). Na tabela a seguir são apresentadas as gamas de tensão de polarização referentes a cada um dos tipos de transistores.

Tabela 3 Gama de valores de tensão polarização para os diferentes tipos de transistores disponíveis na tecnologia.

| Tipo de<br>tensão de<br>limiar | Tipo de<br>Transistor | Gama de<br>tensões de<br>polarização |

|--------------------------------|-----------------------|--------------------------------------|

| LVT                            | PMOS                  | -2 V < Vbp < 0 V                     |

|                                | NMOS                  | 0 V < Vbp < 2 V                      |

| RVT                            | PMOS                  | 1 V < Vbp < 3 V                      |

|                                | NMOS                  | -2 V < Vbp < 0 V                     |

Pensando nesta conversão de níveis de tensão, Hamon e Beigne (2013) propuseram o uso de uma célula *Level Shifter* (LS) para realizar esta operação. O nome *Level Shifters* pode ser traduzido como Desviadores de Nível (de Tensão). LS são células empregadas na mudança da amplitude de tensão entre partes do circuito que operam com níveis de tensão

diferentes como, por exemplo., em células I/O (*Input/Output*). Na figura 13 são apresentadas a entrada e saída de um *Level Shifter* típico.

Figura 13 – Entada (em verde) e saída (em vermelho) de um circuito Level Shifter típico.

Mesmo assim, para que este tipo de circuito possa ser usado como circuito de polarização dos transistores, ainda se faz necessária a obtenção de um valor negativo de tensão de saída parte complementar dos transistores a serem polarizados. O resultado em termos de sinais da inclusão da parte complementar do circuito *Level Shifter* para a obtenção de ambas as tensões de polarização resulta em uma resposta similar àquela apresentada na figura 13, porém com sinal a mais de saída conforme apresentado na figura 14.

A célula escolhida para o referido trabalho foi a *Contention Mitigated Level Shifter* (CMLS), que pode ser traduzida como Desviador de Nível (de Tensão) com Contenção Mitigada. Porém, existem outras arquiteturas de células LS que podem ser exploradas. E, também, uma melhor compreensão de como o controle é feito torna-se importante para um melhor desenvolvimento de circuitos que empreguem esta técnica.

Figura 14 – Entrada (em verde) e saídas positiva (em vermelho) e negativa (em azul) para um circuito Level Shifter adaptado para funcionar como uma Boost Cell.

#### 4.1.1 Tipos de Desviadores de Nível

Células que realizam a mudança de nível de tensão são diversas e suas arquiteturas dependem diretamente da função que exercerão. Exitem células que trabalham com multiplas tensões de saída e têm seu circuito adaptado para melhor executar estas funções. Outras utilizam apenas uma fonte de alimentação, para minimizar a quantidade de linhas de transmissão na região da célula, podendo ser até mais econômicas.

Para a aplicação de controle a partir de ativação e desativação, apenas duas tensões são necessárias: uma tensão na qual a Tensão de Limiar é elevada (transistor inativo/mais lento); e outra na qual ele será menor (transistor ativo/mais rápido). Esta operação pode ser

facilmente implementada com LS mais simples, possuindo dois níveis de tensão de sinal de entrada (*Ground* ou **GND** e **Vdd**) e dois de saída (**GND** e **Vhigh** > **Vdd**).

Estes tipos de circuito de conversão de tensão podem ser divididos em duas partes excenciais:

- a) uma parte na qual é realizada a transferência de nível de uma tensão de alimentação normal para uma outra com tensão mais elevada; e

- b) uma segunda parte na qual se inclui um inversor de saída, exercendo a função de buffer e sendo capaz de suprir a necessidade de carga (Fan-Out).

Dentro da linha de mudança de nível de tensão, existem circuitos que utilizam duas (GND e Vhigh) ou três (GND, Vdd e Vhigh) tensões de alimentação positivas. Para que se realize o circuito de *Boost* complementar, necessário para os transistores com dopagem de canal inversa; é preciso criar um segundo circuito de comportamento semelhante, porém para tensões de saída negativas (Vlow < GND).

Mesmo que apresentando uma menor quantidade de transistores, os circuitos com apenas duas tensões possuem uma limitação quando na elaboração de seu complementar para tensões negativas. É necessário que a parte negativa identifique a variação da entrada para um nível baixo (GND) e com isso altere sua saída de GND para a tensão de *Boost* negativa (Vlow < GND). É por isso que selecionou-se apenas circuitos com 3 alimentações, os quais serão vistos a seguir.

Duas células básicas, dentre as que possuem duas fontes de alimentação, foram aqui selecionadas. A primeira é o *Conventional Level Shifter* (CLS) e a segunda é a *Contention Mitigated Level Shifter* (CMLS). Uma arquitetura para operação em tensões negativas já foi proposta para o CMLS, porém o mesmo ainda não foi feito para o CLS. Nas sessões a seguir serão discutidas as operações de cada uma dessas arquiteturas e também serão propostas arquiteturas para saída em ambas as tensões necessárias para a polarização.

#### 4.1.2 Conventional Level Shifter