#### http://researchcommons.waikato.ac.nz/

#### Research Commons at the University of Waikato

#### **Copyright Statement:**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right

to be identified as the author of the thesis, and due acknowledgement will be

made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# Application of Nonlinear Transistor Characteristics

A thesis

submitted in fulfilment

of the requirements for the degree

of

Doctor of Philosophy in

Physics and Electronic Engineering

at

The University of Waikato

by

**Toby Balsom**

#### **Abstract**

This research presents three works all related by the subject of third-order distortion reduction in nonlinear circuits. Each one is a novel extension to previous work in that branch of electronics literature. All three follow the procedure of presenting a novel algebraic proof and following up with simulations and/or measurements to confirm the theoretical result. The works are generally themed around nonlinear low-frequency bipolar transistor circuits.

Firstly, an investigation is conducted into a well documented effect in bipolar-junction transistors (BJTs) called inherent third-order distortion nulling. This effect is shown to be a fundamental result of the transistor's transfer function acting upon an input signal. The proof of a single BJT emitter-follower amplifier's inherent null is examined which is well documented in the literature. This forms the basis for a novel extension in Darlington transistors where theory suggests the third-order null occurs at double the collector current of a single BJT. Discrete measurements of a CA3083 transistor array are undertaken and compared with theory and simulation data. These measurements confirm theory with reasonable accuracy.

A temperature and process variation independent bias circuit is developed to solve one issue with using third-order distortion nulling. This work is interesting in that it branches into series resistance compensation for translinear circuits and stands as a useful circuit in its own right. Using stacks of matched forward-biased semiconductor junctions which conform to translinear conditions, a bias current can be generated which theoretically removes temperature and series resistance dependence on the particular BJT used. This proves useful for the previous work in distortion nulling, but also allows direct and accurate measurement of series resistance. Again, simulation and measurement data is

obtained from discrete measurements of the proposed circuit, and the results conform with theory to a reasonable degree.

Lastly, this work presents the analysis of a cascoded-compensation (Cascomp) amplifier. It presents the first fully non-linear derivation of the Cascomp's transfer function and its associated harmonic and intermodulation distortion components. The derivation reveals an interesting characteristic in which the third-order intermodulation distortion has multiple local minima. This characteristic has not yet been presented in the literature, and allows better optimisation of Cascomp amplifiers in any application. Again, this characteristic and its potential benefits are confirmed with simulation and discrete measurements.

Observations of the presented works are discussed and built upon in the last chapter. This leads to suggestions on future research topics branching on from these works.

## Acknowledgements

To Jonathan, Bill and Marcus for the inspiration, guidance and wisdom. To Mark, Kyle, Steve and Benson for the entertaining diversions and enlightening support. To Tracey and my family for the love and sacrifice.

## **Table of Contents**

| Al | ostrac  | ct            |                             | i           |

|----|---------|---------------|-----------------------------|-------------|

| Ac | cknov   | vledgei       | ments                       | <b>ii</b> i |

| Ta | ıble o  | f Conte       | ents                        | iv          |

| Li | st of l | Figures       |                             | vii         |

| Li | st of ' | <b>Fables</b> |                             | xiii        |

| 1  | Out     | line          |                             | 1           |

|    | 1.1     | Thesis        | s Motivation                | . 2         |

|    |         | 1.1.1         | Third-Order Distortion Null | . 3         |

|    |         | 1.1.2         | Translinear Extraction      | . 3         |

|    |         | 1.1.3         | Cascoded Compensation       | . 3         |

|    |         | 1.1.4         | Aims and Goals              | . 4         |

|    | 1.2     | Thesis        | s Outline                   | . 4         |

|    | 1.3     | Origir        | nal Work                    | . 5         |

| 2  | Intr    | oducti        | on                          | 7           |

|    | 2.1     | Defin         | ition of Distortion         | . 8         |

|    | 2.2     | Measi         | ures of Distortion          | . 9         |

|    |         | 2.2.1         | Harmonic Distortion         | . 11        |

|    |         | 2.2.2         | Intermodulation Distortion  | . 12        |

|    |         | 2.2.3         | Third-Order Intercept Point | . 14        |

|    | 2.3     | Disto         | rtion in BJT Circuits       | . 16        |

|    |         | 2.3.1         | BJT Models                  | . 16        |

|    |         |               |                             |             |

#### vi TABLE OF CONTENTS

|   |            | 2.3.2   | BJT Distortion Characteristics     | 19        |

|---|------------|---------|------------------------------------|-----------|

|   |            | 2.3.3   | Effects of Frequency               | 20        |

|   |            | 2.3.4   | Heterojunction Bipolar Transistors | 22        |

|   | 2.4        | BJT N   | on-idealities                      | 23        |

|   |            | 2.4.1   | Temperature                        | 23        |

|   |            | 2.4.2   | Parasitic Resistance               | 24        |

|   |            | 2.4.3   | Base-width Modulation              | 25        |

|   |            | 2.4.4   | Nonlinear Beta                     | 27        |

|   |            | 2.4.5   | Process Variation                  | 28        |

|   |            | 2.4.6   | Summary of Non-idealities          | 29        |

|   | 2.5        | Linear  | risation Techniques                | 30        |

|   |            | 2.5.1   | Feedback                           | 30        |

|   |            | 2.5.2   | Feedforward                        | 32        |

|   |            | 2.5.3   | Predistortion                      | 33        |

|   |            | 2.5.4   | Harmonic Termination               | 34        |

|   | 2.6        | Gener   | ral Literature Review              | 35        |

| 3 | Thir       | ·d_Orde | er Distortion Null                 | 39        |

| J | 3.1        |         | luction                            | 40        |

|   | 3.2        |         | ture Review                        | 41        |

|   | 3.3        |         | retical Proof                      | 43        |

|   | 3.4        |         | ngton BJT Null                     | 46        |

|   | 3.4        | 3.4.1   | Theoretical Plotting               | 49        |

|   | 3.5        |         | ation                              | 50        |

|   | 3.6        |         | urement                            | 51        |

|   | 3.7        |         | ssion                              | 52        |

|   | 3.7        | 3.7.1   | Practical implementation           | 55        |

|   | 3.8        |         | usions                             | 55        |

|   | 3.0        | Conci   | usions                             | 33        |

| 4 | Trar       | ıslinea | r Extraction                       | <b>57</b> |

|   | 4.1        | Transl  | linear Principle                   | 58        |

|   |            | 4.1.1   | Nonideal Translinear Principle     | 60        |

|   |            |         |                                    |           |

|   | 4.2        | Litera  | ture Review                        | 61        |

|   | 4.2<br>4.3 |         | Resistance Compensation            | 61<br>62  |

|   |     | 4.3.2  | Series Resistance Extraction          | 66  |

|---|-----|--------|---------------------------------------|-----|

|   |     | 4.3.3  | Application to Amplifier Biasing      | 67  |

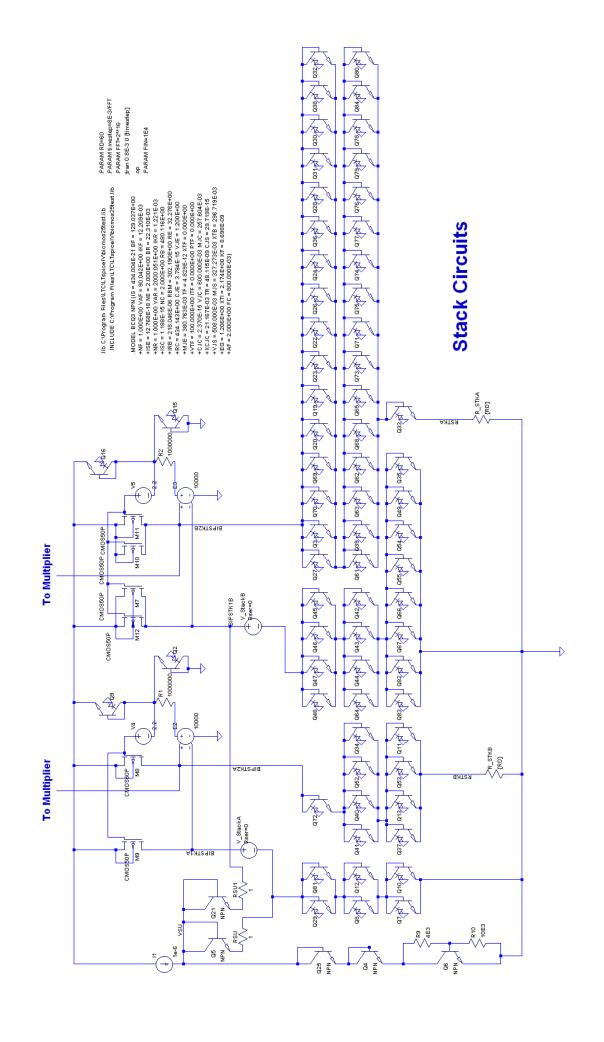

|   | 4.4 |        | ction Circuit Design                  | 68  |

|   |     | 4.4.1  | Translinear Stack Ratios              | 69  |

|   |     | 4.4.2  | Multiplier Divider design             | 70  |

|   |     | 4.4.3  | Bias Driver Circuit                   | 70  |

|   | 4.5 | Simul  | ation                                 | 71  |

|   |     | 4.5.1  | Multiplier Output Error               | 72  |

|   |     | 4.5.2  | Amplifier Bias Current Error          | 74  |

|   |     | 4.5.3  | IM3 Null Error                        | 74  |

|   | 4.6 | Measu  | irements                              | 76  |

|   |     | 4.6.1  | Series Resistance Measurements        | 77  |

|   | 4.7 | Discus | ssion                                 | 78  |

|   | 4.8 | Concl  | usion                                 | 79  |

|   |     |        |                                       |     |

| 5 |     |        | Compensation                          | 81  |

|   | 5.1 | Ü      | round                                 | 82  |

|   | 5.2 |        | ture Review                           | 83  |

|   | 5.3 |        | nt Theory                             | 84  |

|   | 5.4 | Full T | heory                                 | 87  |

|   |     | 5.4.1  | Main Amplifier                        | 87  |

|   |     | 5.4.2  | Ideal Error Amplifier                 | 88  |

|   |     | 5.4.3  | Amplifier Coefficients                | 88  |

|   |     | 5.4.4  | Non-Ideal Error Amplifier             | 90  |

|   | 5.5 | Casco  | mp Biasing                            | 92  |

|   |     | 5.5.1  | Fundamental Gain                      | 92  |

|   |     | 5.5.2  | Third-Order Gain                      | 94  |

|   | 5.6 | Simul  | ation                                 | 96  |

|   |     | 5.6.1  | Circuit Schematic                     | 96  |

|   |     | 5.6.2  | Optimisation                          | 97  |

|   | 5.7 | Proces | ss Errors                             | 101 |

|   |     | 5.7.1  | Transistor Parameters                 | 101 |

|   | 5.8 | Experi | imental Results                       | 104 |

|   |     | 5.8.1  | Measurements                          | 104 |

|   |     | 5.8.2  | Verification of Optimisation Benefits | 107 |

|   |     |        |                                       |     |

#### viii TABLE OF CONTENTS

|    | 5.9   | Conclusion                  | 108 |

|----|-------|-----------------------------|-----|

| 6  | Con   | clusions and Future Work    | 111 |

|    | 6.1   | Third-Order Distortion Null | 111 |

|    | 6.2   | Translinear Extraction      | 113 |

|    | 6.3   | Cascomp                     | 114 |

| A  | Seri  | es Expansion Coefficients   | 115 |

| В  | Trai  | nsistor Nulling Derivations | 127 |

| C  | Trai  | nslinear Extraction Data    | 141 |

| D  | Case  | comp Derivations            | 155 |

| Bi | bliog | raphy                       | 182 |

# List of Figures

| 2.1  | Linear and Nonlinear distortion waveforms. The right-hand col-              |    |

|------|-----------------------------------------------------------------------------|----|

|      | umn is the result of passing a pure square/sine wave through the            |    |

|      | common electronic transfer functions represented in the mid-                |    |

|      | dle column. Waveform 1 shows no distortion. Waveform 2 and                  |    |

|      | 3 show linear distortion through a high-pass and low-pass filter            |    |

|      | respectively. Waveform 4 and 5 show nonlinear distortion through            |    |

|      | nonlinear transfer functions                                                | 8  |

| 2.2  | Frequency spectrum of harmonic and intermodulation tones gen-               |    |

|      | erated by a two input signal through a generic transfer function            | 13 |

| 2.3  | Graphical representation of third-order intercept point (IP3) on a          |    |

|      | input power vs. output power plot for a generic amplifier                   | 15 |

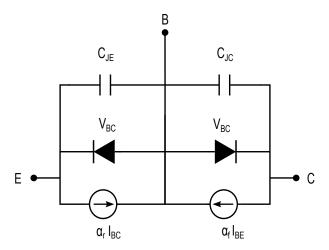

| 2.4  | Large signal equivalent circuit for the Ebers-Moll model                    | 17 |

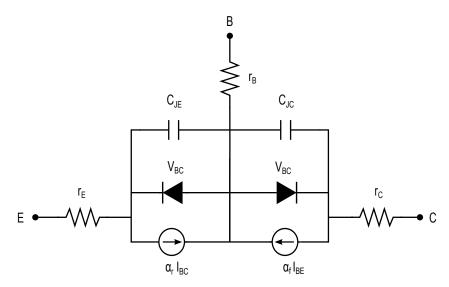

| 2.5  | Large signal equivalent circuit for the Gummel-Poon model                   | 17 |

| 2.6  | Gummel plot showing the nonlinear variation of collector current,           |    |

|      | $I_C$ , relative to base current, $I_B$ . This leads to the nonlinearity of |    |

|      | current gain and higher and lower collector currents                        | 18 |

| 2.7  | A typical single BJT transistor common-emitter amplifier used for           |    |

|      | transfer analysis                                                           | 19 |

| 2.8  | Ebers-Moll large signal equivalent model of a BJT, now including            |    |

|      | the two parasitic junction capacitances                                     | 21 |

| 2.9  | Plot of junction capacitance versus junction voltage, showing the           |    |

|      | nonlinearity of the capacitance at higher voltages                          | 22 |

| 2.10 | Ebers-Moll large signal equivalent model of a BJT, now including            |    |

|      | parasitic resistances                                                       | 24 |

|      |                                                                             |    |

#### x LIST OF FIGURES

| 2.11 | Graphical representation of base-width modulation, showing the                 |    |

|------|--------------------------------------------------------------------------------|----|

|      | dependence of collector current on collector-emitter voltage for a             |    |

|      | number of different $V_{BE}$ values                                            | 26 |

| 2.12 | $Graphical\ representation\ of\ the\ nonlinear\ variation\ in\ current\ gain.$ | 27 |

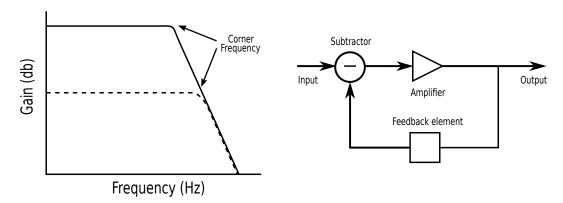

| 2.13 | Left: Bode plot for a generic amplifier. Solid line shows open-                |    |

|      | loop gain of a generic amplifier (no feedback). Dashed line shows              |    |

|      | feedback added to the generic amplifier, decreasing gain and in-               |    |

|      | creasing bandwidth. <i>Right:</i> General configuration of a feedback          |    |

|      | topology using a feedback element to adjust the input dependent                |    |

|      | on the output.                                                                 | 31 |

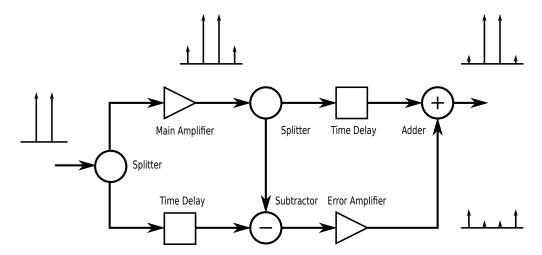

| 2.14 | General configuration of a feedforward topology using both a main              |    |

|      | and error amplifier stage.                                                     | 32 |

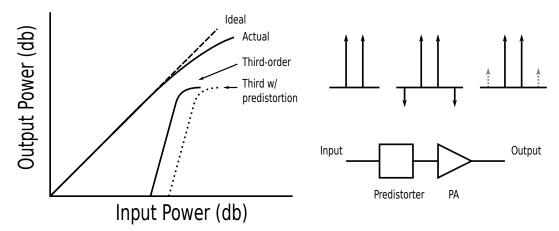

| 2.15 | <i>Left:</i> Power input vs. power output plot for a generic amplifier.        |    |

|      | Shows the original amplifier third-order relative to the fundamen-             |    |

|      | tal. <i>Right:</i> Shows the stages of predistortion. The three frequency      |    |

|      | spectrums show each stages contribution leading to cancellation                |    |

|      | of the third-order components in the final output                              | 34 |

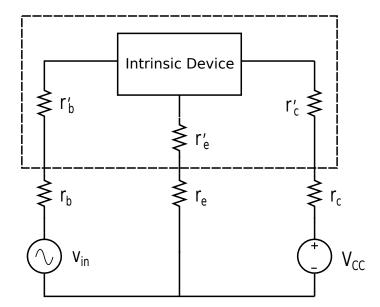

| 3.1  | A simple BJT amplifier showing the combination of intrinsic and                |    |

|      | extrinsic resistances associated with series resistance                        | 40 |

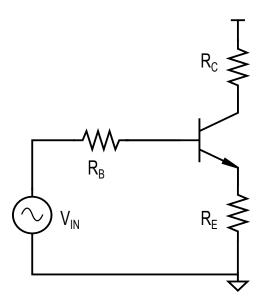

| 3.2  | A typical single BJT transistor common-emitter amplifier used for              |    |

|      | transfer analysis. Each shown resistor is the total combination of             |    |

|      | internal and external resistances                                              | 44 |

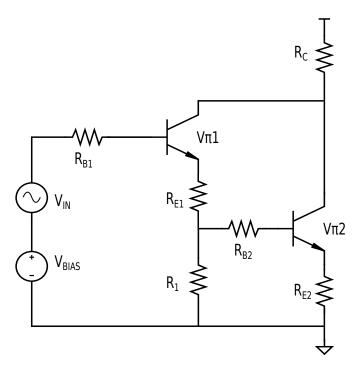

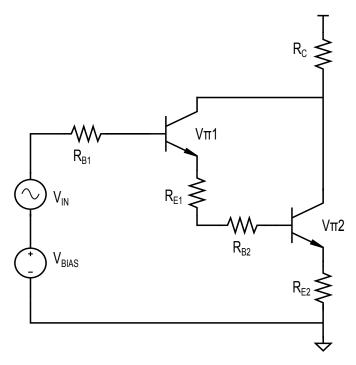

| 3.3  | Typical single Darlington transistor amplifier circuit used for small          |    |

|      | signal analysis. Each shown resistor is the total combination of               |    |

|      | internal and external resistances                                              | 47 |

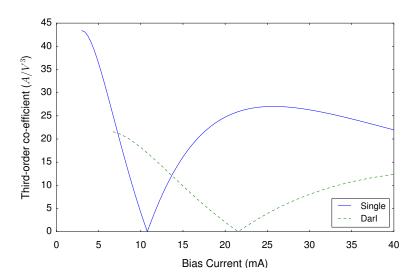

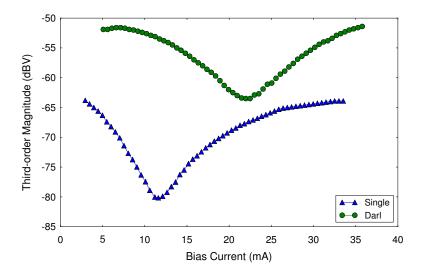

| 3.4  | Theoretical plot of third-order magnitude vs. collector current for            |    |

|      | a single BJT/Darlington common-emitter amplifiers                              | 49 |

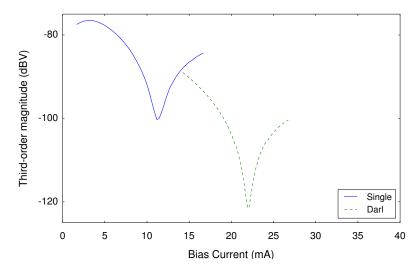

| 3.5  | Simulated third-order magnitude vs. collector current for a single             |    |

|      | BJT/Darlington common-emitter amplifiers                                       | 50 |

| 3.6  | Measured third-order magnitude vs. collector current for a single              |    |

|      | BJT/Darlington common-emitter amplifiers                                       | 51 |

| 3.7  | Typical single Darlington transistor amplifier circuit used for small          |    |

|      | signal analysis. Each shown resistor is the total combination of               |    |

|      | internal and external resistances                                              | 54 |

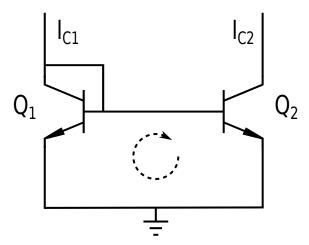

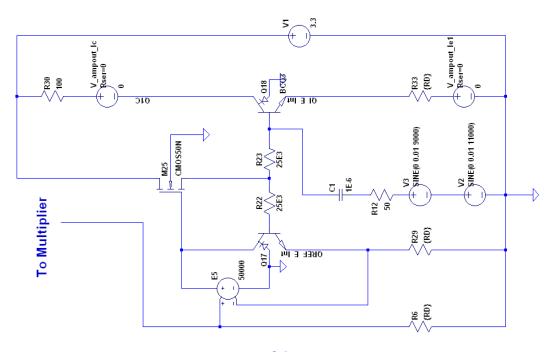

| 4.1             | Simple current mirror circuit, showing the transistor's base-emitter            |    |

|-----------------|---------------------------------------------------------------------------------|----|

|                 | junctions in closed loop                                                        | 58 |

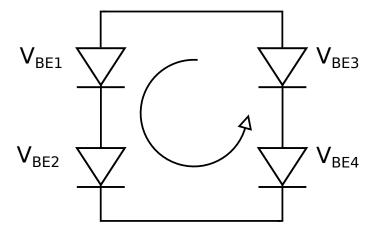

| 4.2             | Fundamental circuit used to describe the translinear principle                  | 59 |

| 4.3             | A two-transistor translinear stack circuit with the translinear con-            |    |

|                 | dition forced around the two branches                                           | 63 |

| 4.4             | A three-transistor translinear stack circuit with the translinear               |    |

|                 | condition forced around the two branches                                        | 65 |

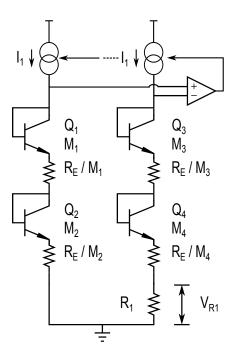

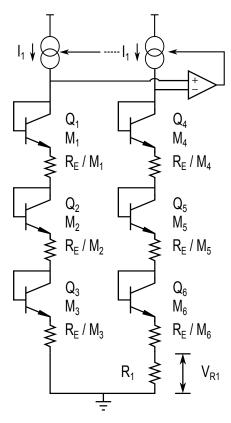

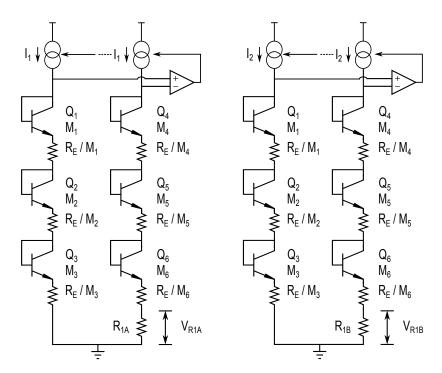

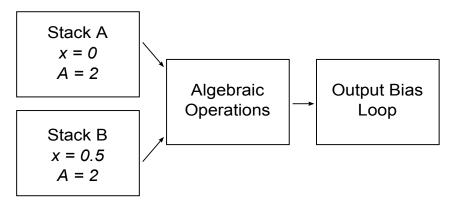

| 4.5             | Two three-stack translinear circuits which allow series resistance              |    |

|                 | to be resolved, due to the known difference in emitter area ratios.             | 66 |

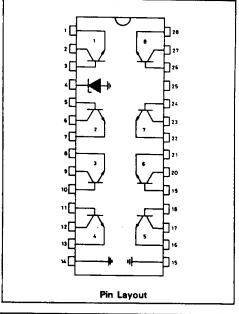

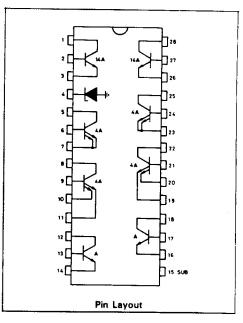

| 4.6             | Bias circuit blocks showing the three main stages of the circuit                | 69 |

| 4.7             | Translinear multiplier used to perform algebraic operations re-                 |    |

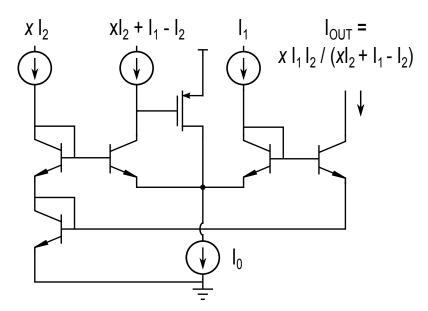

|                 | quired by the second circuit block                                              | 70 |

| 4.8             | Output bias loop used to set the bias current in the output transis-            |    |

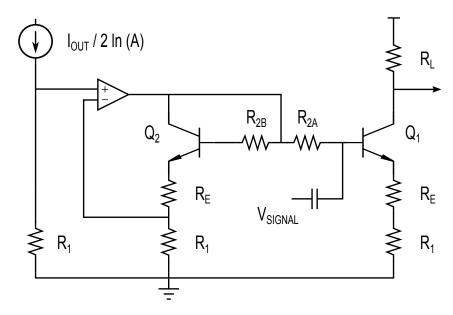

|                 | tor such that it operates at the third order null                               | 71 |

| 4.9             | Bias current vs. temperature variation compared with the ideal                  |    |

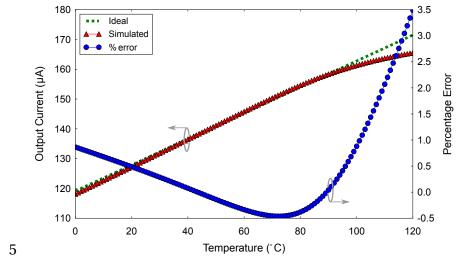

|                 | bias current, at the multiplier output                                          | 73 |

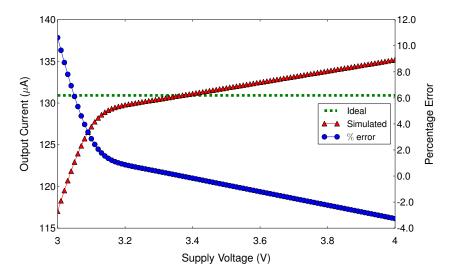

| 4.10            | Bias current vs. supply voltage variation compared with the ideal               |    |

|                 | bias current at the multiplier output                                           | 74 |

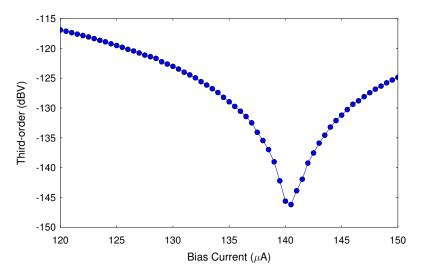

| 4.11            | Simulated IM3 null of the amplifier showing the null position in                |    |

|                 | bias current. Simulation uses the full BiCMOS transistor models.                | 75 |

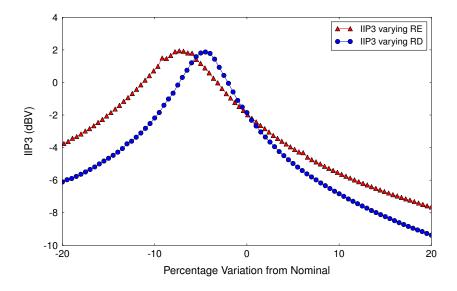

| 4.12            | Variation of $R_E$ and $R_1$ from the nominal values and the resulting          |    |

|                 | position in the IM3 null                                                        | 75 |

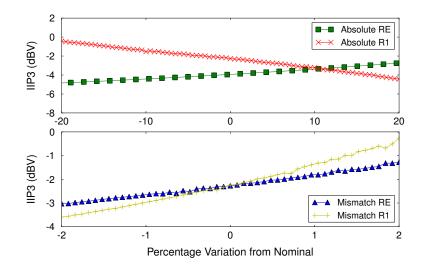

| 4.13            | Absolute and mismatch process variations of $R_E$ and $R_1$ and their           |    |

|                 | impact on the current position in the IM3 null                                  | 76 |

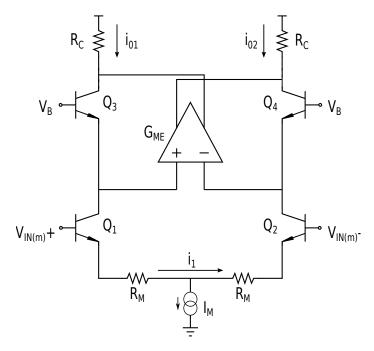

| 5 1             | Cascomp circuit with an ideal transcenductance error amplifier                  |    |

| J.1             | Cascomp circuit with an ideal transconductance error amplifier, $G_{ME}$        | 82 |

| 5.2             | $C_{ME}$                                                                        | 02 |

| J.Z             | error amplifier                                                                 | 85 |

| 5.3             | Ideal theoretical fundamental coefficient cancellation of a Cas-                | 00 |

| 5.5             | comp amplifier for fixed $R_M$ and $I_M$ . $R_E$ is swept for values of $I_E$ . |    |

|                 | The y-axis reflects the magnitude of the gain. $\dots$                          | 93 |

| 5.4             | Non-ideal theoretical fundamental coefficient cancellation of a                 | 33 |

| J. <del>4</del> |                                                                                 |    |

|                 | Cascomp amplifier for fixed $R_M$ and $I_M$ . $R_E$ is swept for values of      | വ  |

|                 | $I_E$ . The y-axis reflects the magnitude of the gain                           | 93 |

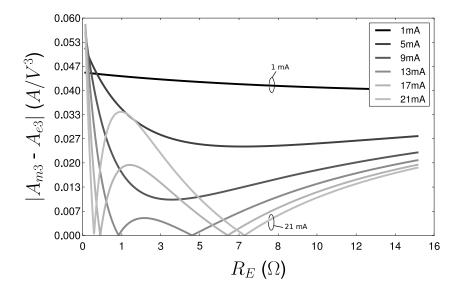

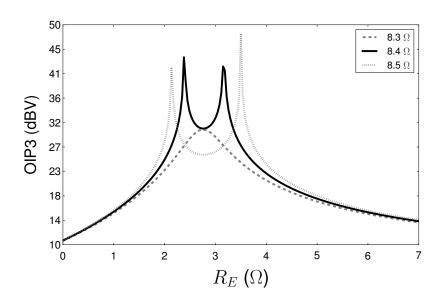

| 5.5  | Ideal theoretical third-order coefficient cancellation of a Cascomp                      |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | amplifier for fixed $R_M$ and $I_M$ . $R_E$ is swept for values of $I_E$ . The           |     |

|      | y-axis reflects the magnitude of the total IM3 product and the nulls                     |     |

|      | indicate IM3 cancellation                                                                | 95  |

| 5.6  | Non-ideal theoretical third-order coefficient cancellation of a Cas-                     |     |

|      | comp amplifier for fixed $R_M$ and $I_M$ . $R_E$ is swept for values of $I_E$ .          |     |

|      | The y-axis reflects the magnitude of the total IM3 product and the                       |     |

|      | nulls indicate IM3 cancellation                                                          | 95  |

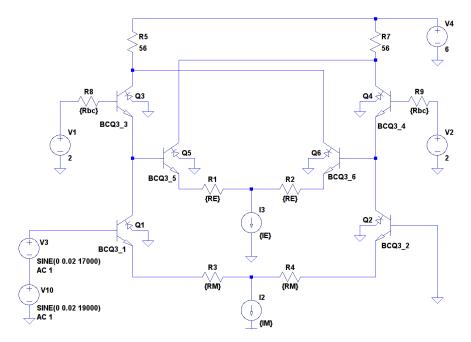

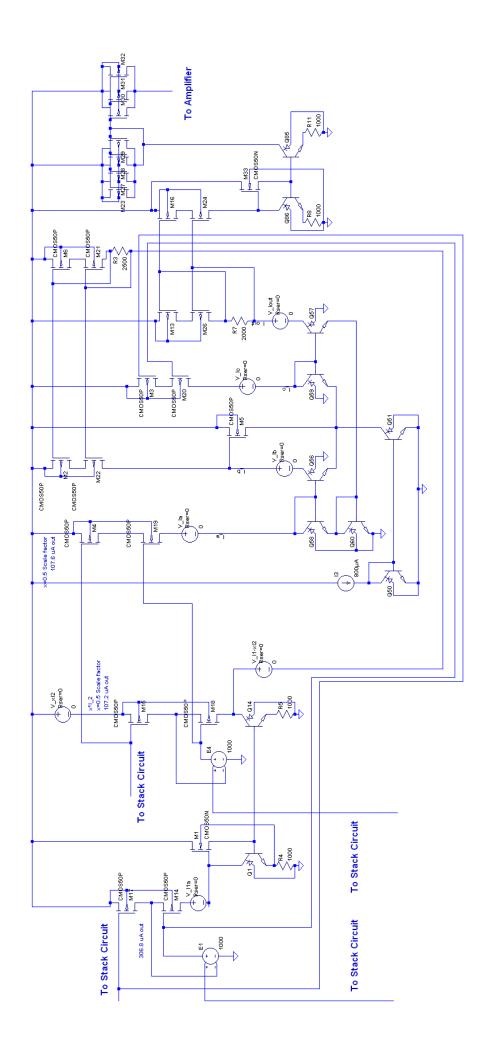

| 5.7  | Cascomp circuit as built in LTspice                                                      | 97  |

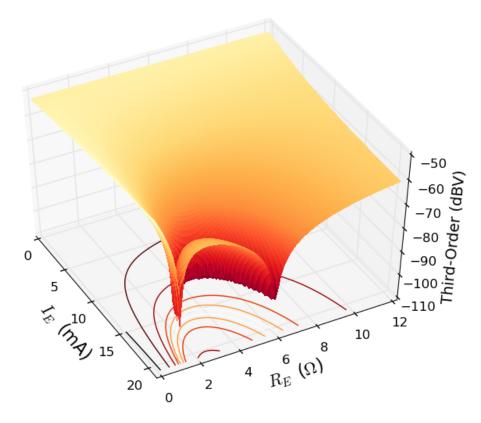

| 5.8  | Simulated third-order output (dBV) of a non-ideal Cascomp am-                            |     |

|      | plifier for fixed $R_M$ and $I_M$ over a $56\Omega$ load. Note that the z-axis           |     |

|      | values have been clipped (at -105 dBV) in the null positions to                          |     |

|      | allow for readability                                                                    | 98  |

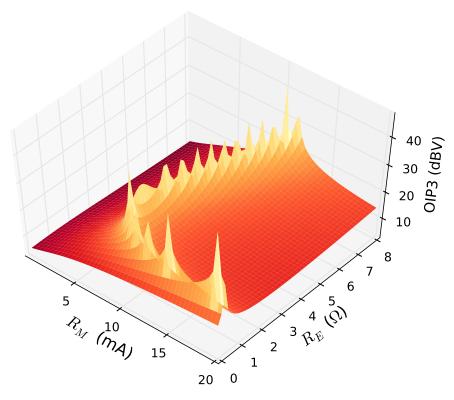

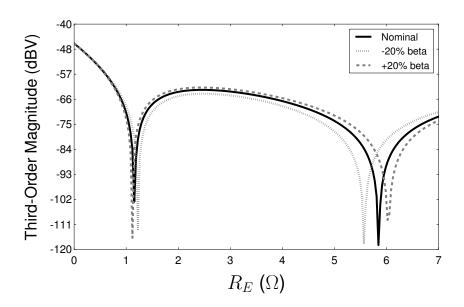

| 5.9  | Simulated OIP3 of a Cascomp circuit with $R_E$ and $R_M$ swept. $I_E$                    |     |

|      | and $I_M$ are fixed are at 20 mA each. Note the peaks are points that                    |     |

|      | fall deep into the IM3 null                                                              | 99  |

| 5.10 | Optimum bias point for a Cascomp circuit with $\mathcal{R}_E$ swept with $\mathcal{R}_M$ |     |

|      | varied                                                                                   | 100 |

| 5.11 | Optimum bias point for a Cascomp circuit with $R_E$ swept with                           |     |

|      | smaller $R_M$ values for comparison                                                      | 100 |

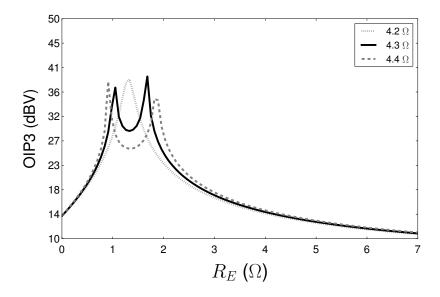

| 5.12 | Optimum bias point in $\mathbb{R}_E$ compared against a conventional Cas-                |     |

|      | comp (Nominal) and differential pair                                                     | 101 |

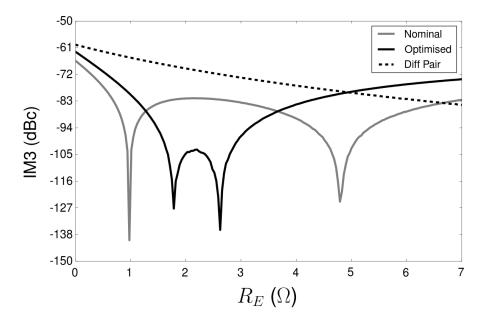

| 5.13 | Simulated third-order output (dBV) of a non-ideal Cascomp am-                            |     |

|      | plifier. 'Nominal' is the normal circuit parameters. '±20% beta'                         |     |

|      | show absolute process variation of $oldsymbol{eta}$ parameters in the circuit. $R_E$     |     |

|      | is swept for fixed $R_M$ , $I_M$ and $I_E$                                               | 102 |

| 5.14 | $Simulated\ third-order\ output\ (dBV)\ of\ a\ non-ideal\ Cascomp\ ampli-$               |     |

|      | fier. 'Nominal' is the normal circuit parameters. 'Mismatch' show                        |     |

|      | the $\pm 2\%$ mismatch process variation of $\beta$ , $V_{AF}$ , and $I_S$ parameters    |     |

|      | in the circuit. $R_E$ is swept for fixed $R_M$ , $I_M$ and $I_E$                         | 103 |

| 5.15 | Simulated third-order output (dBV) of a non-ideal Cascomp am-                            |     |

|      | plifier. 'Nominal' is the normal circuit parameters. ' $\pm 5\%$ RM '                    |     |

|      | indicates respective 5% absolute variation of the main amplifier                         |     |

|      | emitter resistance. $R_E$ is swept for fixed $R_M$ , $I_M$ and $I_E$                     | 104 |

| 5.16 | Measured experimental results of the Cascomp circuit's fundamental and third-order outputs | 106 |

|------|--------------------------------------------------------------------------------------------|-----|

| B.1  | A typical single BJT transistor common-emitter amplifier used for                          |     |

|      | transfer analysis. Each shown resistor is the total combination of                         |     |

|      | internal and external resistances                                                          | 128 |

| B.2  | Typical single Darlington transistor amplifier circuit used for small                      |     |

|      | signal analysis. Each shown resistor is the total combination of                           |     |

|      | internal and external resistances                                                          | 132 |

### List of Tables

| 2.1 | Comparison of linearisation techniques in amplifiers                | 30  |

|-----|---------------------------------------------------------------------|-----|

| 3.1 | Summary of error calculations and measurements for the single       |     |

|     | BJT configuration. Comparative error percentage is relative to      |     |

|     | 'Theoretical Ideal'                                                 | 53  |

| 3.2 | Summary of error calculations and measurements for the Dar-         |     |

|     | lington configuration. Comparative error percentage is relative to  |     |

|     | 'Theoretical Ideal'                                                 | 53  |

| 4.1 | Initial simulations of the translinear stack output currents versus |     |

|     | the calculated values. This shows the simulated current values and  |     |

|     | the resulting series resistances when using these values. The per-  |     |

|     | centage error is the error when compared with theoretical series    |     |

|     | resistance values                                                   | 72  |

| 4.2 | Calculations of multiplier output current with ideal and non-ideal  |     |

|     | circuit models. This shows the simulated current values and the re- |     |

|     | sulting series resistances when using these values. The percentage  |     |

|     | error is the error when compared with theoretical series resistance |     |

|     | values                                                              | 73  |

| 4.3 | Summary of process error impact on position in the IM3 null, at     |     |

|     | the amplifier output                                                | 76  |

| 5.1 | Comparison of bias points for a Cascomp at $I_M = 20 \mathrm{mA}$   | 108 |

# Outline

All electronic circuits are inherently nonlinear. Both passive and active components are often assumed linear because their nonlinearity is extremely subtle and goes unnoticed. However, due to rising demands on technologies where bandwidth is at a premium, circuit component's subtle nonlinearity can start to become significant. As more sophisticated telecommunications systems are developed, increased performance is required from their amplifying stages. Unfortunately, nonlinearity degrades the performance of these systems. Engineers therefore follow strict guidelines defining the levels of linearity and efficiency that an amplifying stage needs to achieve. Power amplifier design has a heavy focus on these two parameters.

Some relevant applications where the reduction of nonlinearity is paramount include Doherty power amplifiers for use in wireless communication networks [1] and heterojunction bipolar transistor (HBT) power amplifiers for use in wireless communications networks [2]. Both examples aim to increase linearity and efficiency through optimising the topology and the semiconductor device's transfer characteristics. Of course, nonlinearity is an important parameter in

many other fields of amplifier design. An example is analog-to-digital converters where voltage level shifts due to distortion [3]. The work in this thesis mainly focuses on nonlinearity in amplifiers and techniques to reduce distortion.

Common methods of distortion reduction in amplifiers generally fall into three categories; feedback, feedforward, and predistortion. Each offers its own advantages and disadvantages. A designer will generally consider all specifications imposed on the amplifier design, and choose the most suitable method. In modern radio-frequency applications, predistortion techniques dominate amplifier design in wireless communication systems due to its relative simplicity and low-cost. This is also partly due to power amplifiers operating close to compression. Predistortion excels at canceling distortion due to the compression effects of a semiconductor device and power amplifiers typically press this boundary [4]. However, predistortion still has its disadvantages so modern designs tend to combine and synergise different methods of distortion reduction.

This thesis presents a number of ideas and experiments related to the reduction of nonlinearity in different topologies of bipolar transistor amplifiers. The distortion of interest is weakly nonlinear which is a major focus in engineering literature surrounding modern radio-frequency and microwave amplifier design. Strong distortion components such as clipping are neglected in this work. Each of these ideas is expected to be a useful and novel contribution to their respective literature. Distortion reduction techniques for bipolar technologies are not as popular due to the heavy use of field-effect devices in industry. However, heterojunction transistors find use in many applications where distortion is required to be minimised. Because bipolar device models translate accurately into heterojunction devices models, these ideas translate well into the literature.

#### 1.1 Thesis Motivation

The three major works in this thesis are tied together under the general theme of distortion in amplifiers and circuit techniques which reduce it. However, the motivation for each is rather distinct and not necessarily related to the other works. This section describes the motivation for the three works in chapters 3, 4, and 5 respectively and then defines the specific aims and goals of each.

#### 1.1.1 Third-Order Distortion Null

A long-known characteristic that occurs in single bipolar transistor amplifiers is a minima or null appearing in its third-order distortion component. This has been addressed in the literature for a long time, but due to the characteristic occurring at low bias currents, the effect isn't useful in many cases. Amplifier designers often want to push bias current as high as possible, for example to increase the frequency performance of the device. Unfortunately, this is in conflict with utilising the distortion null for increased linearity, hence the characteristic is generally not useful.

One could make the characteristic useful if it could be made to occur at higher bias currents. This work focuses on analysing the characteristic in a different configuration of bipolar transistors, such that the third-order distortion null occurs at a higher bias current.

#### 1.1.2 Translinear Extraction

Following on from the previous work in utilising the distortion null in bipolar devices, it is observed that a limitation of using this null is its dependence on temperature and series resistance variation. A method is required for removing these dependencies from a bias current that is driving a bipolar device. The literature shows few practical entries on methods related to this.

Temperature dependence can be dealt with by invoking the translinear principle, for example the bandgap voltage reference circuit that produces a temperature independent voltage [5]. Based on this principle, one can develop a bias circuit to fit the criteria required for the distortion null. This work focuses on developing a bias circuit that rejects temperature dependence and series resistance variation by utilising the translinear principle.

#### 1.1.3 Cascoded Compensation

Agilent Technologies has expressed interest in understanding a cascoded compensation (Cascomp) amplifier and exploring techniques to increase its performance. The company produces many commercial HBT amplifier products for use in wide-band applications, and they are considering an HBT Cascomp ampli-

#### 4 CHAPTER 1. OUTLINE

fier as an alternative topology. Unfortunately, the conventional Cascomp setup does not meet the gain and linearity requirements to justify further research, but an analysis and implementation which shows better gain and linearity performance would be valuable to them.

In this work, a more rigorous method of analysing the nonlinearity of the Cascomp amplifier is explored. This leverages the fact that the current literature on the Cascomp amplifier does not consider all sources of nonlinearity.

#### 1.1.4 Aims and Goals

Here, the initial goals of the three novel pieces of work are summarised. These are:

- 1. Extend an analysis of bipolar transistor nonlinearity to the Darlington configuration.

- 2. Develop a biasing technique that compensates for temperature and series resistance variation.

- 3. Develop a full nonlinear analysis of a cascoded compensation amplifier.

Leading on from these goals, each chapter may explore some topics such as parameter optimisation, impact of second-order effects and practical application.

#### 1.2 Thesis Outline

This work is divided into six chapters:

Chapter 2 describes the associated background knowledge the work has used. It focuses on general concepts related to all works in this thesis. This includes the basis of distortion and the different types that manifest in amplifiers. The different measures of these distortion types are also defined. Bipolar transistor models are necessary to theoretically predict distortion. Hence, the two most common device models are described and are used for the majority of this work. The parameters of the bipolar models which describe the nonideality of a transistor are defined and discussed. Common distortion reduction techniques are also identified and explained.

Chapter 3 introduces the concept of an inherent third-order intermodulation null in a single bipolar transistor amplifier. This concept is reasonably well established in the literature, however we re-define this concept using a proposed derivation method. It is shown that this method agrees with existing derivations. This method is then used to theoretically show the inherent null occurs in Darlington transistors. The effect is confirmed with simulations and measurements.

**Chapter 4** presents the concept of the translinear principle. Following on from the last chapter, third-order distortion nulling requires a bias circuit which is independent of temperature and of process variation in the transistor's intrinsic and extrinsic resistances. The translinear principle is utilised to develop a circuit which can accurately bias a common-emitter amplifier in its inherent third-order null. The theory of this bias circuit is presented and it is shown how different emitter-ratios can be used to cancel series resistance effects. A circuit design is developed and investigated based on a BiCMOS technology. Measurements and simulations are presented regarding its operation.

A Cascomp circuit is investigated in **Chapter 5**. A leading RF amplifier design company has expressed interest in understanding this circuit to a higher degree. Up until this point, the literature has assumed a linear relationship between the main and error amplifiers of the Cascomp. This chapter describes a new method for deriving the transfer function of a Cascomp amplifier. A new nonlinear transfer function is presented and it is shown that new characteristics of the Cascomp arise in the third-order distortion components. This was previously masked by the linear assumption used in the literature. These new characteristics are analysed with simulations and measurements. Conclusions are drawn regarding the newly found characteristic and the amplifier transfer function's accuracy.

The research is concluded in **Chapter 6.** Observations are made on potential future work regarding all three of the presented circuit techniques.

#### 1.3 Original Work

The work presented in this thesis resulted in a number of publications. Two conference papers where presented and published; one national, one international. A contribution was made to a further conference paper as well. A journal paper

regarding the Cascomp work has also been accepted for publication.

#### List of Publications:

- Balsom, T., Scott, J. & Redman-White, W.. (2011). "Third-order nulling effect in Darlington transistors". In Proceedings of the 18th Electronics New Zealand Conference, ENZCon 2011, Massey University, Palmerston North, 21-22 November 2011, pp. 82-86.

- Balsom, T., Redman-White, W., & Scott, J. (2012). "Bipolar amplifier bias technique for robust IM3 null tracking independent of internal emitter resistance". 2012 IEEE 55th International Midwest Symposium on Circuits and Systems, vol 55, pp. 606-609.

- Jull, H., Balsom, T. & Scott, J. (2012). Cascomp BJT Amplifier vs. traditional configurations. Paper 97, Proceedings of The 19th Electronics New Zealand Conference (ENZCon), Dunedin, New Zealand, 10-12 December, 2012.

- [Accepted for Publication] Balsom, T., Redman-White, W., & Scott, J. (2012). "Analysis of Circuit Conditions for Optimum Intermodulation and Gain in Bipolar Cascomp Amplifiers with Non-Ideal Error Correction" (2014) IET Circuits, Devices & Systems.

# 2 Introduction

Three novel works are described in this thesis, tied together under the common theme of distortion reduction. Hence, each three works in the following three chapters contain their own literature reviews and background information that is directly relevant to its work. This introductory chapter is structured such that it acts as a linking chapter, giving context and background for the following novel works. It defines the fundamental concepts around distortion reduction for those unfamiliar with the topic. It also presents a general literature review on modern distortion techniques that are not directly relevant in each of the following chapters.

To begin, this chapter introduces a base definition for distortion and describes why it is an important research topic in modern electronics. This is followed by definitions of common measures of distortion which are used in the following chapters. The chapter then outlines the fundamental transistor models and their application. Also discussed are the non-idealities of BJTs and their impact on distortion through the device models. The chapter then presents a review of modern literature associated with distortion in amplifiers.

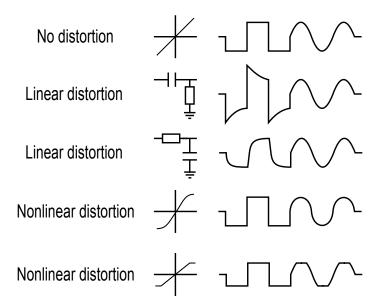

**Figure 2.1:** Linear and Nonlinear distortion waveforms. The right-hand column is the result of passing a pure square/sine wave through the common electronic transfer functions represented in the middle column. Waveform 1 shows no distortion. Waveform 2 and 3 show linear distortion through a high-pass and low-pass filter respectively. Waveform 4 and 5 show nonlinear distortion through nonlinear transfer functions.

#### 2.1 Definition of Distortion

As a signal passes through any electronic component it has some transfer function imposed on it, modifying the output signal from its original state. This is the definition of distortion in its simplest form. In order to give this definition any practical meaning we separate distortion into two categories, linear and nonlinear. Nonlinear distortion of a signal is identified by an event which adds new frequency components into the output signal. Linear distortion does not add new frequency components, but rather changes the size or ratio of the original frequency components. Graphical representations of both types are shown in Fig. 2.1.

Nonlinear distortion can further be separated into two sub-categories, strong and weak nonlinear distortion. Strong nonlinear distortion arises from gross changes to the output frequency spectrum, namely clipping or device saturation. This area has been well covered in the literature [6]. Weak nonlinear distortion arises from slight changes to the output frequency spectrum, generally produced

by the transfer function of active devices. The generated distortion tones are orders of magnitude smaller than the input signal's fundamental frequency, but not so small as to have an insignificant impact on the system. The following works have a major focus on this category of distortion. So for simplicity the general term of distortion will refer to weak nonlinear types of distortion.

Distortion is a major focus when it comes to amplifiers in modern electronics. Power amplifiers (PA) are regularly used in modern telecommunication systems with the purpose of amplifying a signal to be transmitted through an antenna. Examples of major driving technologies for this type of system are wireless local area networks (WLAN), cellular devices, and global positioning systems (GPS). When designing PA's the biggest design consideration can be the trade-off between power efficiency and linearity of the output signal. High power efficiency is required as a PA generally has to drive an antenna at high power levels, resulting in large amounts of power being drawn from the supply. Increasing efficiency reduces operating costs and extends performance capabilities of the wireless device. Nonlinearity effectively causes transmission error in the system. Typically a system operates in a limited transmission band and a decrease in linearity causes the distortion components of a signal to spread into neighboring transmission channels. Most systems will attempt to filter signal nonlinearity out before transmission but filters are not perfect and fail to filter frequency components close to the source frequency. Hence, to achieve optimal linearity in the system while not trading off other desired characteristics of transmission system, other techniques must be used to minimise distortion. This gives rise to much of the amplifier designs today, which aim to reduce an amplifier's weak nonlinear distortion inherently in the circuit design.

#### 2.2 Measures of Distortion

To accurately evaluate an amplifying stage we employ different measures of distortion. Each distortion measure is useful for specific applications but may not be useful in others. All measures are grounded by Taylor's Theorem, which states that any function can be represented as an infinite sum of the function's derivatives. In electronics, we often use the Maclaurin Series (a Taylor series centered around zero) to describe nonlinear devices as we are interested in

alternating current (AC) centered around a direct current (DC) bias. In weakly nonlinear distorting systems we can assume that the DC bias is the center of the input and output signals, therefore making our series expansion derivatives centered around zero. This makes the use of a Maclaurin series valid. We also assume that the system is operating in steady-state to avoid complex analysis of the start-up characteristics. This allows the less complex analysis of system transfer characteristics.

Let us consider a general transfer function,  $\gamma$ , to be some function of x,

$$y = f(x). (2.1)$$

Taylor's theorem allows us to replace the function applied to x with the following form,

$$y(a) = f(a) + f^{1}(a)(x-a) + \frac{f^{2}(a)}{2!}(x-a)^{2} + \frac{f^{3}(a)}{3!}(x-a)^{3} + \dots$$

(2.2)

where f(x) is expanded around the point x = a. Note that the series is truncated to the third-order for simplicity. Using a Maclaurin series allows us to simplify this to be

$$y(0) = f(0) + f^{1}(0)x + \frac{f^{2}(0)}{2!}x^{2} + \frac{f^{3}(0)}{3!}x^{3} + \dots$$

(2.3)

Since the derivatives are now constants with x going to zero, they can be treated as such. One more step of simplification allows the description of a transfer function to be written as

$$y = a_0 + a_1 x + a_2 x^2 + a_3 x^3 + \dots$$

(2.4)

where  $a_n$  is the nth-order constant describing the magnitude of each term. These are often called the coefficients of the expansion. This form allows the coefficients to describe the magnitude of each term in a simple manner with  $a_n$  containing the factorial along with the derivative term. Note that if the coefficients  $a_2$  and higher are zero, then the system is linear.

Each coefficient can be obtained using

$$a_n = \frac{1}{n!} \frac{d^n y}{dx^n} \bigg|_{x=0} \tag{2.5}$$

where again y = f(x) is the transfer function.

Due to the fundamental nature of signal transmission, sinusoidal waves are almost always used as an input to amplifying systems. Using Fourier theory, we know that any sinusoidal signal can be represented by a power series of pure sine or cosine signals. This law, combined with Taylor's theorem allows an accurate description of distortion in all systems.

#### 2.2.1 Harmonic Distortion

A fundamental result of distortion in nonlinear circuits is the generation of frequency components in the output signal which occur at integer multiples (harmonics) of the input frequency. This is called harmonic distortion, occurring due to a single sinusoidal input frequency.

Let a time-variant input function for an amplifier, x(t), be defined as a pure sinusoidal wave

$$x(t) = A_1 \cos(\omega_1 t). \tag{2.6}$$

Substituting this function into Eq. 2.3 for a generalised transfer function will yield a series of coefficients describing the magnitude of the harmonic distortion terms in the output signal. In the interest of simplicity, this is commonly truncated after the third-order term and higher order terms are assumed negligible. This derivation yields the following,

$$y = a_0 + \frac{a_2 A_1^2}{2}$$

$$+ \left( a_1 A_1 + \frac{3a_3 A_1^3}{4} \right) \cos(\omega_1 t)$$

$$+ \left( \frac{a_2 A_1^2}{2} \right) \cos(2\omega_1 t)$$

$$+ \left( \frac{a_3 A_1^3}{4} \right) \cos(3\omega_1 t).$$

(2.7)

Eq. 2.7 shows the fundamental output tone (occurring at  $\omega_1$ ), and the second and third-order harmonic components (occurring at  $2\omega_1$  and  $3\omega_1$  respectively). The bracketed term associated with each harmonic component is the term which describes the magnitude of that frequency component. This is dictated by the

transfer function the input signal is driven through, which set the coefficients,  $a_n$ . These bracketed terms can be observed individually to obtain the magnitude of any harmonic component that is of interest<sup>1</sup>. The two remaining terms describe the DC component in the output signal.

A simple way to characterise the components of harmonic distortion in a system is total harmonic distortion (THD). It is the ratio of the sum of harmonic component powers compared with the fundamental component's power. THD is expressed as a percentage of distortion relative to the fundamental tone or in decibels (dB). Mathematically, it is expressed as

$$THD = \frac{\sum P_{HDn}}{P_{Fund}},\tag{2.8}$$

where  $P_{HDn}$  is the power of the nth-order harmonic, and  $P_{Fund}$  is the power of the fundamental tone.

THD is a common measurement in high resolution data acquisition systems and high-fidelity audio equipment. For such systems it is important that all frequency components have minimal distortion, as it is not practical to filter the output [7]. Hence, THD is used to give an average of the distortion contribution of all harmonic components.

#### 2.2.2 Intermodulation Distortion

Intermodulation distortion (IMD) is the distortion that occurs due to two or more sinusoidal input frequencies. This measure is employed where the fundamental tones of the input signal are required to be linear and the remaining spectrum can be filtered upon receiving the signal. Unfortunately, the third-order intermodulation distortion components appear adjacent to the fundamental tones. In telecommunication systems, transmission bands can be closely neighboring each other in the frequency spectrum. Thus, third-order distortion components can leak over into neighboring transmission bands causing unwanted interference. As previously mentioned, this is difficult to filter because the components occur close to the fundamental tones.

<sup>&</sup>lt;sup>1</sup>Of interest to this work is the magnitudes of distortion components in transistor amplifiers. The full derivation of the single tone distortion components using the Ebers-Moll transfer function can be found in Appendix A.

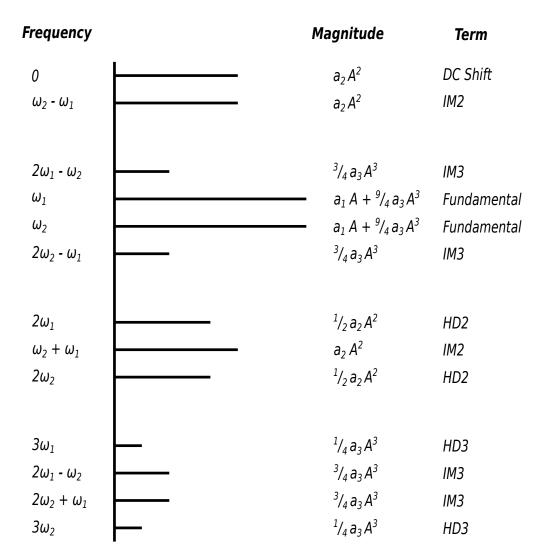

**Figure 2.2:** Frequency spectrum of harmonic and intermodulation tones generated by a two input signal through a generic transfer function.

Consider an input created by two sinusoidal tones,

$$x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t).$$

(2.9)

Again, substituting this into Eq. 2.3 yields second and third-order coefficients<sup>2</sup>. Fig. 2.2 summarises the output signals frequency components (again truncated to the third-order) for a generalised transfer function. The harmonic terms are

<sup>&</sup>lt;sup>2</sup>The full derivation of the two tone distortion components in a transistor amplifier using the Ebers-Moll transfer function can be found in Appendix A. This will make the coefficients specific to the Ebers-Moll function compared with the generalised form in Fig. 2.2

labeled as  $HD_n$  and the intermodulation terms  $IM_n$  for the nth-order power. Again, the series expansion coefficients are  $a_n$  for the nth-order power. Each coefficient shows the magnitude for each respective frequency component.

The intermodulation tones appear at different combinations of sums and differences of the fundamental frequencies. Of particular interest are the third-order components  $2\omega_1-\omega_2$  and  $2\omega_2-\omega_1$  which occur adjacent to the fundamental tones. As mentioned previously, these components are particularly difficult to filter due to their position. For this reason, circuit techniques which reduce third-order intermodulation distortion component are sought-after in amplifier design.

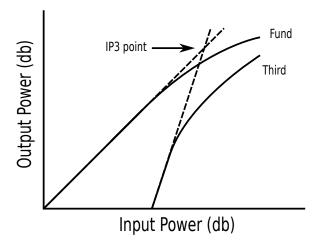

#### 2.2.3 Third-Order Intercept Point

Analysis of distortion performance in RF amplifiers is commonly measured by the "intercept point" of the important frequency component relative to the fundamental component. When addressing the third-order distortion, this measure is called the third-order intercept point (IP3). It is a purely theoretical position in the amplifier's operating state, where the third and fundamental components become equal in terms of output power. Typically, the third-order frequency component is used however the second and fifth order components are used in some applications. This is due to the third-order component's intermodulation property where it manifests close to the fundamental tones, making it the most significant distortion component in many cases. The benefit of this measure is it gives a value which is independent of compression that begins to occur due to device saturation. Therefore, system distortion characteristics can be compared without the need to model compression characteristics. Figure 2.3 shows a graphical example of an IP3 point, where the dashed lines indicate the gradients of the linear regions of each component. The intercept point of these gradient lines indicate the IP3 point.

IP3 can be calculated by assuming that the linear region of the third order component has a gradient of 3, and the linear region of the fundamental component has a gradient of 1. These gradients are the result of plotting functions of the form  $y = kx^n$  on a log-log scale. When a log function is applied, using basic logarithmic identities one can form the straight line equation as  $\log(y) = k \log(x) + \log(a)$ . Considering the form of a Taylor series expansion

**Figure 2.3:** Graphical representation of third-order intercept point (IP3) on a input power vs. output power plot for a generic amplifier.

describing the third-order component, one can see it matches the form  $y = kx^n$ , hence n will be the gradient.

This means that an estimate can be made directly from a spectral analysis of the output. Often, the IP3 is referred to the input or output power level. Input-referred third-order intercept point (IIP3) uses the input power of the fundamental tone. Output-referred third-order intercept point (OIP3) uses the output power of the fundamental tone. OIP3 and IIP3 can be calculated using the equations below,

$$OIP3 = P_{Fund} + \frac{\Delta P_3}{2},\tag{2.10}$$

$$IIP3 = (P_{Fund} - G) + \frac{\Delta P_3}{2},$$

(2.11)

where  $P_{Fund}$  is the magnitude of the output fundamental tone, G is the gain of the amplifier, and  $\Delta P_3$  is the difference in magnitude between the fundamental and the third-order components at the output.

Care must be used when using this measure. Eq. 2.10 assumes the power measurements are taken at a position where the gradients are close to 1 and 3 respectively. This only occurs at lower input powers. At higher input powers, 5th and higher order terms begin to affect the third-order component resulting in a skewed gradients [8].

#### 2.3 Distortion in BJT Circuits

The models commonly used to describe a BJTs transfer function are described in this section. In particular, the focus is on how distortion is generated through these models. This work is based around low-frequency input signals, however we will also explore how these models change with higher frequencies. This section aims to justify why low frequency will extend rather well into higher frequency works. This is based on the heterojunction bipolar transistor (HBT) and its close relationship to BJT operation.

#### 2.3.1 BJT Models

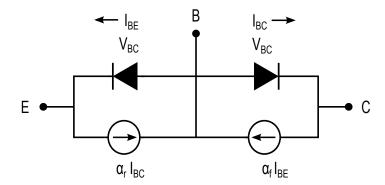

In order to predict how a transistor circuit will operate, theoretical models are used to describe the transfer of voltage or current from the input node to the output node. Ebers and Moll invented the first practical large-signal model for a BJT [9]. This was followed up by Gummel and Poon who extended the model to include more subtle characteristics of a BJTs transfer function [10]. In modern electronics, a further improved version of the Gummel-Poon model is used for circuit simulation software, generally labeled as SPICE Gummel-Poon (SGP).

The classic mathematical model used for BJTs is the Ebers-Moll model. In its simplest form, it is written as

$$I_C = \alpha_f I_S e^{\frac{V_{BE}}{V_T}} \tag{2.12}$$

where  $I_C$  is the collector current,  $V_{BE}$  is the input signal,  $I_S$  is the base-emitter reversed biased saturation current,  $\alpha_f$  is the unity gain factor, and  $V_T$  is the thermal voltage (written as  $V_T = \frac{nkT}{q}$ ).

The commonly used equivalent circuit for the Ebers-Moll model is shown in Fig. 2.4. The equations which further describe this equivalent circuit can be found readily in electronics literature.

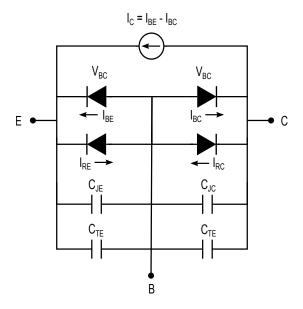

The Gummel-Poon model extends the Ebers-Moll model to account for other important phenomena in the transistor. For example, the transistor's current-gain being dependent on collector current, base-width modulation and high level-injection [11]. It is more comprehensive than the Ebers-Moll model and hence is used as the basis for most electronic simulation software like SPICE

Figure 2.4: Large signal equivalent circuit for the Ebers-Moll model.

Figure 2.5: Large signal equivalent circuit for the Gummel-Poon model.

(Simulation Program with Integrated Circuit Emphasis) [12].

as

The large-signal equivalent circuit used in the Gummel-Poon model is shown in Fig. 2.5. Two extra diodes, with the currents  $I_{RE}$  and  $I_{RC}$ , show the reverse currents when the transistor is under reverse-bias conditions. This model also includes junction capacitances which will be covered later in the chapter.

The Gummel-Poon collector current for a forward-biased transistor is defined

$$I_C = \frac{I_S}{q_b} e^{\frac{V_{BE}}{V_T}} - \frac{I_S}{q_b} e^{\frac{V_{BC}}{V_T}}$$

(2.13)

where  $q_b$  is the base charge to zero-bias base charge ratio. This ratio is described by more complex equations (containing modeling for temperature and current

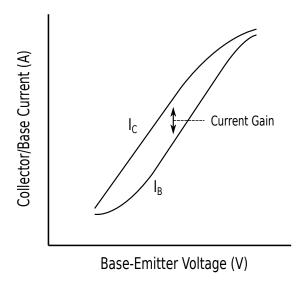

**Figure 2.6:** Gummel plot showing the nonlinear variation of collector current,  $I_C$ , relative to base current,  $I_B$ . This leads to the nonlinearity of current gain and higher and lower collector currents.

gain non-linearity) which can be found in the original paper [10].

With the definition of the Gummel-Poon model stated, we now explore one important phenomenon that the model considers over the Ebers-Moll model. The current gain dependence on collector current is elegantly displayed by a Gummel plot, which shows base-emitter voltage versus current for a BJT device. This is seen in Fig. 2.6, which shows as collector current increases we observe a nonlinear difference in the ratio of collector to base current.

Note that the region at mid-range currents is rather linear, and this is a fair assumption for most BJT devices as the current gain will have minimal variation in this region. This allows the use of simplified models when deriving distortion theoretical products. In the Ebers-Moll model this is considered to be a linear relationship. In some cases this nonlinearity in current gain must be considered to achieve accurate operation in a BJT amplifier.

Of course, the two presented models only describe the saturation region of operation while other equations are used to describe both the active and cutoff regions. For this thesis, we are only interested in the saturation region of amplification. There are also other more complex models that are used heavily in industry. Such examples are the vertical bipolar inter-company model (VBIC) and the MEXTRAM model. These models further account for the very subtle

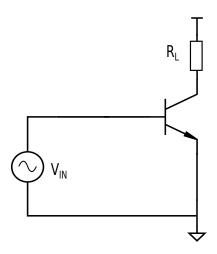

**Figure 2.7:** A typical single BJT transistor common-emitter amplifier used for transfer analysis.

characteristics of a bipolar transistor.

### 2.3.2 BJT Distortion Characteristics

Combining the presented Ebers-Moll model with the previously presented distortion theory allows the prediction of BJT circuit distortion characteristics. Let us consider the most simple BJT amplifier in the form of a common-emitter amplifier, seen in Fig. 2.7.

The input signal contains both AC and DC components as in Eq. 2.14. This is substituted into the Ebers-Moll model in Eq. 2.15.

$$V_{IN} = A_1 cos(\omega t) + V_{DC}, \qquad (2.14)$$

$$i_C = I_S e^{\frac{A_1 \cos(\omega t) + V_{DC}}{V_T}}. (2.15)$$

The DC component of the input signal is separated out by simplifying Eq. 2.15 to be

$$i_C = I_{CQ} e^{\frac{A_1 \cos(\omega t)}{V_T}}, \tag{2.16}$$

where  $I_{CQ}$  equals the DC portion of the input signal (given by  $I_{CQ} = I_S e^{\frac{V_{DC}}{V_T}}$ ). Using Eq. 2.4, a Taylor expansion is applied to Eq. 2.16 which yields the series

expansion<sup>3</sup> of the transfer function as

$$i_{C} = I_{CQ} + I_{CQ} \frac{A_{1}^{2}}{4V_{T}^{2}}$$

$$+ I_{CQ} \left( \frac{A_{1}}{V_{T}} + \frac{A_{1}^{3}}{8V_{T}^{3}} \right) cos(\omega t)$$

$$+ \frac{1}{4} I_{CQ} \left( \frac{A_{1}}{V_{T}} \right)^{2} cos(2\omega t)$$

$$+ \frac{1}{24} I_{CQ} \left( \frac{A_{1}}{V_{T}} \right)^{3} cos(3\omega t).$$

(2.17)

This equation describes the output distortion as a function of the input signal, for a fundamental input tone occurring at  $\omega$ . The second and third harmonic occur at  $2\omega$  and  $3\omega$  respectively and higher order terms have been truncated.

It is important to note that the distortion component's position in frequency is only dependent on the input signal frequency, while the magnitude of the component is dependent on temperature, DC bias, and input signal magnitude. It also depends on subtle BJT characteristics such as base-width modulation which will be discussed later in the chapter. This derivation gives a good representation of how distortion components are derived and how one can analyse an amplifier's transfer characteristics.

# 2.3.3 Effects of Frequency

A BJT's physical structure contains parasitic capacitances which are created between the different structural layers of the device. From basic theory, it is known that a capacitor's impedance decreases with increased frequency. Therefore, as input signal frequency increases, so does the effect of these capacitances upon the device's transfer characteristics. To understand this effect, consider the updated Ebers-Moll equivalent circuit in Fig. 2.8, including the important parasitic junction capacitances.  $C_{JE}$  is the capacitance from the base node to the emitter node, and  $C_{JC}$  is the capacitance from the base node to the collector node.

Consider the impedance looking into the base connection. If the impedance

<sup>&</sup>lt;sup>3</sup>The full derivation of the single tone coefficients for a BJT can be found in Appendix A.

**Figure 2.8:** Ebers-Moll large signal equivalent model of a BJT, now including the two parasitic junction capacitances.

of these capacitances is low, then the input signal leaks through to the emitter/collector node, decreasing the effective input signal level. From fundamental electronics theory we know that as frequency increases the gain of the amplifier will decrease. At some point the gain of an amplifier will reach unity; a current gain of 1 is reached. This is called the cutoff frequency,  $f_T$ , and can be calculated through Eq. 2.18. General purpose transistors have a  $f_T$  of roughly 50 MHz to 1 GHz.

$$f_T = \frac{1}{2\pi C_{ie} \, r_e} \tag{2.18}$$

where  $C_{ie}$  is the capacitance seen looking into the input node, and  $r_e$  is the resistance seen looking into the emitter [13].

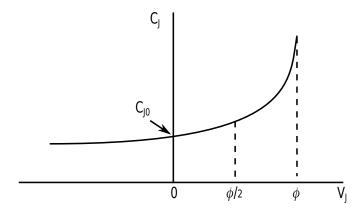

Junction capacitances are also inherently non-linear. They can be described by the functions below and a general plot is shown in Fig. 2.9.

$$C_{JE} = \frac{C_{JE0}}{(1 - V_{BE}/\phi_E)^{m_E}},\tag{2.19}$$

$$C_{JC} = \frac{C_{JC0}}{(1 - V_{BC}/\phi_C)^{m_C}},\tag{2.20}$$

where  $C_{JE0}$  and  $C_{JC0}$  are the capacitance values at zero-bias across the respective junction,  $\phi_E$  and  $\phi_C$  are the base-emitter and base-collector barrier potentials, and  $m_E$  and  $m_C$  are the base-emitter and base-collector gradient factors related to the doping of the junction [11]. The non-linearity of the capacitances make

**Figure 2.9:** Plot of junction capacitance versus junction voltage, showing the nonlinearity of the capacitance at higher voltages.

the algebraic derivations of distortion far more complex at high frequencies and hence it is ignored in a lot of cases. This includes most SPICE simulators which instead approximate the capacitor's nonlinear function to a simpler form.

In this work we focus on low-frequency application, so input signals used are well below the cutoff frequency of a standard transistor. Applications requiring distortion reduction still exist at low frequencies such as audio applications, low-noise amplifiers (LNAs) and mixers. There also exists different transistor structures which have far higher cutoff frequencies than a standard BJT, allowing low-frequency distortion analysis to be sufficiently accurate and insightful.

# 2.3.4 Heterojunction Bipolar Transistors

The performance of BJT devices can be increased through modifications to the base junction of the device. The base substrate can be built using differing materials from the emitter and collector, such as silicon-germanium, indiumphosphide or indium-gallium-arsenide. During manufacture, the base substrate is graded with these materials such that the device's bandgap is narrower at the collector than the emitter. This has the effect of increasing the switching speed, increasing current gain and increasing cut-off frequency of the device. The resulting device is called a heterojunction bipolar transistor (HBT).

HBTs are an attractive technology for use in radio-frequency (RF) applications. Among other reasons, this is due to their extremely high frequency cutoff, with literature confirming values well into the hundreds of GHz range [14, 15].

Practically, a BJT and a HBT operate under extremely similar theoretical laws. The Ebers-Moll equation will accurately describe the transfer function up until the junction capacitances become non-negligible. Because of the high cutoff frequency, distortion analysis is accurate up to very high frequencies [16]. Basewidth modulation and high level injection effects also have a decreased impact in HBTs [17].

One drawback of using HBTs is the increased manufacture complexity and cost. This is due to the multiple layers of diffusion required to fabricate the devices base junction. HBTs are only used in IC technologies and are rarely found as a discrete device.

# 2.4 BJT Non-idealities

Non-idealities of a BJT are characteristics of the device which skew the transfer function away from the idealised Eq. 2.12. Sometimes, a circuit design can force some system-wide condition in which a nonideality has a negligible impact, for example a bandgap voltage reference rejects changes in temperature. However, this is not always possible. It then becomes important to account for the impact of nonidealities in a system.

Here we will summarize five specific non-idealities that can skew the transfer function and affect distortion in a BJT device. Each one needs to be considered in order to make accurate predictions of distortion levels in amplifiers.

# 2.4.1 Temperature

Temperature is a fundamental factor in the operation of a semiconductor device. This stems from the semiconductor physics of a PN junction, in which the junction's built-in barrier voltage is a function of temperature [6]. It has a direct impact on the Ebers-Moll model in Eq. 2.1 through the thermal voltage,  $V_T$ , which increases proportionally with temperature. Second-order effects also occur due to device parameters having a dependence on the barrier junction voltages. This impacts model parameters such as the saturation current  $I_S$ , junction capacitors, and the current gain [11].

There is little one can do to minimise temperature variations in a single

**Figure 2.10:** Ebers-Moll large signal equivalent model of a BJT, now including parasitic resistances.

semiconductor component. However, some circuit design techniques lessen the impact of temperature, and in some cases make it negligible for a certain parameter. For example, using integrated transistors on an IC as opposed to discrete transistors, minimises the temperature difference between each transistor. This occurs because the displacement between each semiconductor junction is minimised in an IC therefore the junctions will experience a smaller temperature difference relative to each other. Consequently, the transistors are very close in terms of their temperature dependent parameters (current gain, saturation current etc) and a temperature resistant circuit can be designed around this relationship. One example is the centroid circuit layout [18].

#### 2.4.2 Parasitic Resistance

The imperfect structure of a BJT device means that there are some unwanted resistive components between the terminals of the device. This can be caused by the resistivity of the semiconductor material or the bonding and connections of the device package. These are often termed the parasitic or extrinsic resistances of the transistor and can be modeled by the inclusion of extra base, collector, and emitter resistances. Fig. 2.10 shows the Ebers-Moll equivalent circuit model adjusted to include parasitic resistances.

If parasitic resistances are large enough, they can change the operation of an

amplifier. Consider an applied DC base-emitter voltage for the device in Fig. 2.10. This voltage must now be divided between the base-emitter junction and the emitter and base resistors. This changes the DC operating point of the amplifier. The emitter resistor has the effect of degenerating the amplifier (commonly called emitter degeneration in the literature) which linearises the amplifier and reduces its gain. As shown later in the chapter, this is the implementation of feedback inside the packaged device.

Other BJT parameters depend on these parasitics. For example, at high frequencies,  $r_B$ , sets the input noise current which is important for low-noise applications [16]. Other parasitic resistances also exist in a BJT device. However for the purposes of this work they will have a negligible impact and therefore can be excluded.

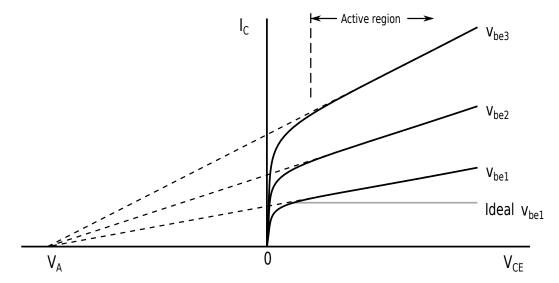

### 2.4.3 Base-width Modulation

Base-width modulation is the name given to the dependence of collector current on collector-emitter voltage. It is also commonly called the Early effect. The impact of this dependence is perhaps best represented as an  $I_C$  vs.  $V_{CE}$  plot, shown in Fig. 2.11. Ideally, a transistor should maintain a constant collector current  $I_C$  for any value of collector-emitter voltage  $V_{CE}$  while it is operating in the active region. However, as  $V_{CE}$  increases, the reverse-bias voltage across the collector-base junction also increases. In turn, this increases the junction's depletion region and decreases the effective base width of the device. We know from semiconductor physics that saturation current (and therefore collector current) will increase proportionally with base width [6]. Hence, the collector current will vary proportionally with collector-emitter voltage in the active region.

The effect can be modeled by including a term in Eq. 2.12. This is seen below in Eq. 2.21

$$I_C = I_S e^{\frac{V_{BE}}{V_T}} \left( 1 - \frac{V_{CE}}{V_A} \right),$$

(2.21)

where  $V_A$  is the Early voltage (shown on Fig. 2.11). Generally, discrete transistors have an Early voltage of roughly -50 V to -100 V. The effect can become negligible as the Early voltage increases and  $V_{CE}$  decreases.

Following from the series expansion of a common-emitter amplifier in Eqs. 2.15-2.17, we can include base-width modulation resulting a new term bound to

**Figure 2.11:** Graphical representation of base-width modulation, showing the dependence of collector current on collector-emitter voltage for a number of different  $V_{BE}$  values.

the distortion components. The DC quiescent current now contains the basewidth modulation effect.

$$i_{C} = I_{CQ} + I_{CQ} \frac{A_{1}^{2}}{2}$$

$$+ I_{CQ} \left( \frac{A_{1}}{V_{T}} + \frac{3A_{1}^{3}}{4V_{T}^{3}} \right) sin(\omega t)$$

$$+ \frac{1}{2} I_{CQ} \left( \frac{A_{1}}{V_{T}} \right)^{2} sin(2\omega t)$$

$$+ \frac{1}{6} I_{CQ} \left( \frac{A_{1}}{V_{T}} \right)^{3} sin(3\omega t),$$

(2.22)

where  $I_{CQ}$  is now defined as

$$I_{CQ} = I_S e^{\frac{V_{DC}}{V_T}} \left( 1 + \frac{V_{CE}}{V_A} \right).$$

(2.23)

From this derivation, we see the base-width modulation effect can be considered as a scale factor to the DC current, therefore having the effect of scaling the generated distortion components. It is commonly modeled as a resistor in parallel with the device output ports.

Consequently, due to the scaling of  $I_{CQ}$  from base-width modulation, the

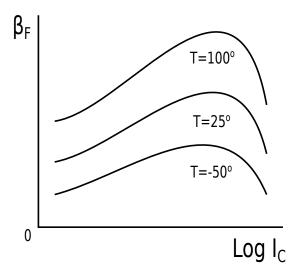

**Figure 2.12:** Graphical representation of the nonlinear variation in current gain.

current gain of a transistor is also scaled. This is modeled by Eq. 2.24 below.

$$\beta = \beta_0 \left( 1 + \frac{V_{CE}}{V_A} \right). \tag{2.24}$$

In some cases the entire effect is simply ignored and its impact assumed negligible due to a sufficiently high Early voltage. Good examples of this are many of the upcoming references [19, 20, 21, 22].

#### 2.4.4 Nonlinear Beta

Previously, Fig. 2.6 introduced a Gummel plot which shows a generalised relationship between base and collector current in a BJT. The ratio of the two currents represents the current gain,  $\beta$ . Observing this plot shows a clear nonlinear relationship between the two currents. If current gain is plotted, the result is a nonlinear curve as shown in Fig. 2.12. This nonlinearity stems partly from low and high current effects in the semiconductor junctions.

At low base currents, we observe a deviation from the expected log-linear base current. This is observed in Fig. 2.6 at the bottom end of the base current trace. This is caused partly by a recombination process occurring in the base region. As electrons travel into the base junction, some combine with the majority carriers of the region (holes for a NPN device). Usually, the base is thin and lightly doped

so the impact of base recombination is small. However, at low base currents the effect becomes non-negligible. This results in a nonlinear current gain at low base/collector currents [6] [11].

At high current levels, both the base and collector come under the effect called current crowding. Bipolar devices generally have a very thin base layer and a current will experience an intrinsic non-negligible base resistance as it travels through this region. This causes a non-uniform distribution of current-density in the emitter region, resulting in current crowding at the edges of the emitter junction. As current increases to high levels, the effect manifests as a decrease in the log-linear trend of collector current, and hence a nonlinear beta at higher currents.

Finally, both currents are modified by high-level injection and by base-width modulation [11]. High level injection effects can be assumed negligible if the devices are not operated at high currents.

This current gain nonlinearity is important to consider when devices in the same circuit are operating at different bias currents. This introduces error into output of the circuit due to the discrepancy in current gain between the two devices.

### 2.4.5 Process Variation

Unfortunately, transistor fabrication processes are imperfect and result in semiconductor devices having slightly different structural parameters. In particular, the current gain and saturation current parameters can vary due to mismatches in the emitter-area ratios [23]. Generally, smart fabrication techniques are employed to minimise the mismatch between devices in each fabrication run. This is a fundamental reason why integrated BJT circuits are more accurate compared to discrete circuits. In an IC, each transistor is fabricated on the same wafer under the same conditions, resulting in minimal variation of emitter-area ratios. This intra-wafer variation is called mismatch variation, and generally results in no more than 1-2% variation in modern processes<sup>4</sup>.

The parameters of all devices on an entire wafer can also vary from that ex-

<sup>&</sup>lt;sup>4</sup>These values are the authors estimates based on various references [24, 25, 26] and personal communication with the project supervisors [27, 28]. Exact process variations are dependent on factors such as the total area of the circuit layout.

pected from the fabrication process. Commercial devices state fixed parameter values on their respective datasheets and SPICE models. Therefore, measurements can have some variation from what theory and simulation predict, due to entire fabrication runs varying slightly from their stated norms. This interwafer variation is called absolute variation, and generally results in no more then 20% variation in modern processes. Note that the percentages for both variation types are dependent on the specific fabrication process, and the size of the device being fabricated.

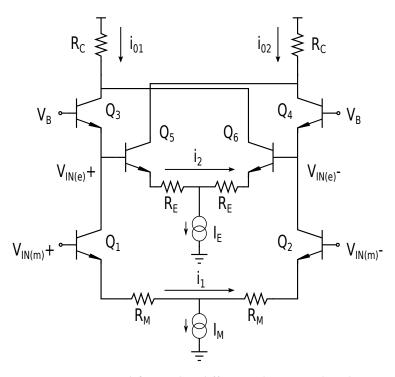

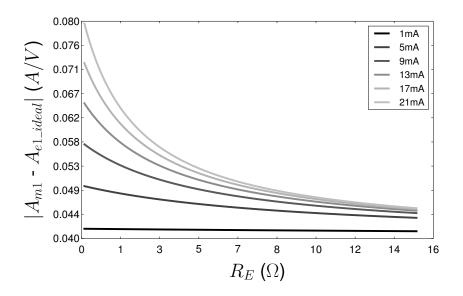

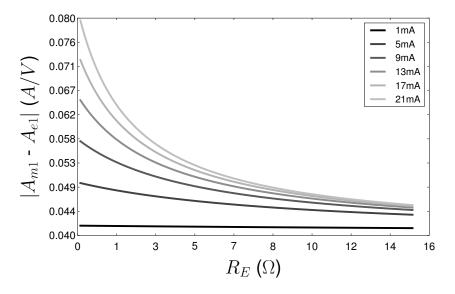

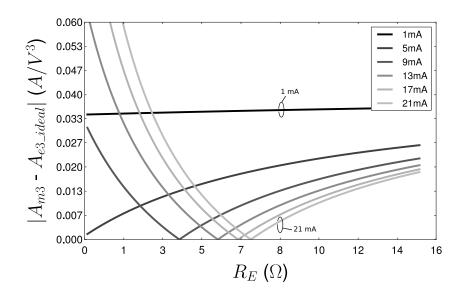

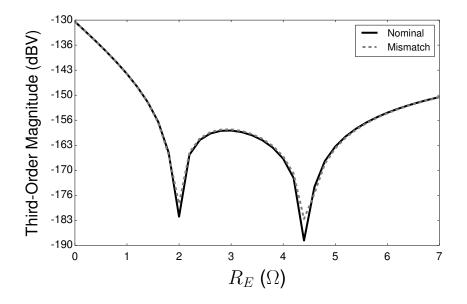

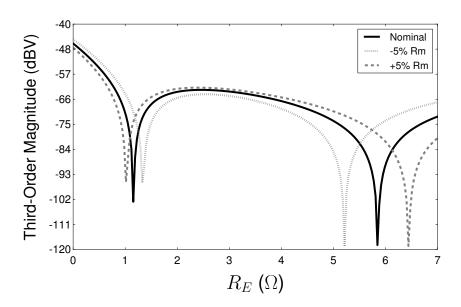

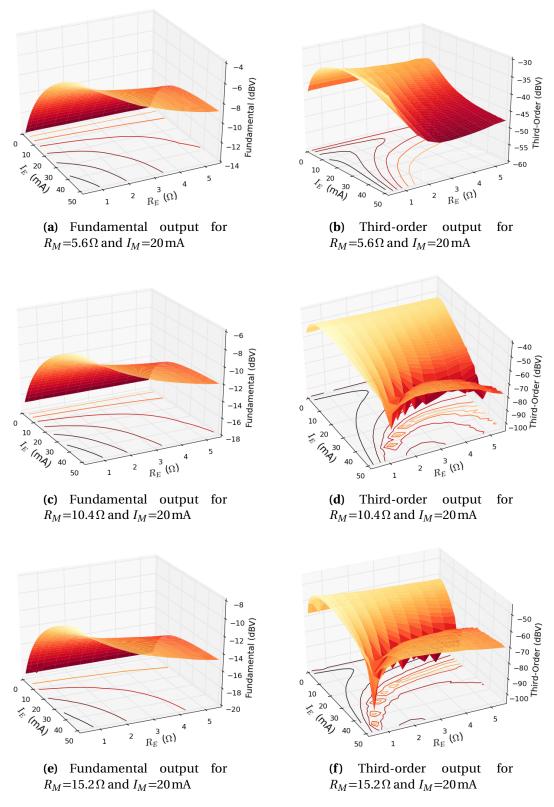

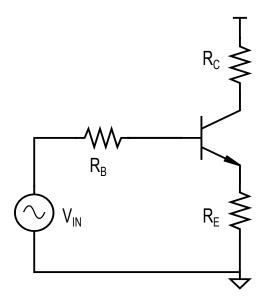

Both types of process variations can have varying degrees of impact depending on the application. For example, in translinear bias circuits both can result in non-negligible errors in the circuit [29]. A bias current is required to be a certain value, and both types of variations can shift the current. Conversely, in an differential amplifier circuit fabricated on a single wafer, absolute variation is not impactful in terms of input offset voltages. This offset is only determined by the mismatch between specific devices, and hence only the mismatch variation [23].