### http://researchcommons.waikato.ac.nz/

### Research Commons at the University of Waikato

### **Copyright Statement:**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right

to be identified as the author of the thesis, and due acknowledgement will be

made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# Development of a Supercapacitor based Surge Resistant Uninterruptible Power Supply

A thesis submitted in partial fulfilment of the requirements for the degree

of

**Master of Engineering**

at

The University of Waikato

by

## Parthasaradhy Kumaran Kozhiparambil

The University of Waikato 2011

### **Abstract**

Uninterruptible Power Supplies (UPSs) provide short-term power back-up to sensitive electronic and electrical equipments, where an unexpected power loss could lead to undesirable outcomes. They usually bridge the connected equipment between the utility mains power and other long term back-up power systems like generators. A UPS also provides a "clean" source of power, meaning they filter the connected equipment from distortions in electrical parameters of the mains power like noise, harmonics, surges, sags and spikes.

A surge resistant UPS or SRUPS is one that has the capability to withstand surges, which are momentary or sustained increases in the mains voltage, and react quickly enough to offer protection to the connected equipment from the same. Usually UPSs run off battery power when the utility mains power is absent. But the SRUPS developed in this design project uses super capacitors instead of battery packs. The reason for this is that the high energy-densities and medium power-densities offered by super capacitors allow for it to serve two purposes. One is to provide the DC power to operate the UPS in the absence of mains power, as an alternative to batteries. Secondly, super capacitors can withstand heavy momentary high current/voltage surges due to its high energy-density characteristics. Also as the life-time of super capacitors is much higher than that of conventional batteries and as they do not need regular topping-up or inspection, the end result is a truly maintenance-free UPS.

Most commercial UPSs do not have inherent surge protection capabilities. The UPS is one entity while a discrete surge protection module is inserted between the utility mains and the UPS to provide for transient surge suppression. In the proposed SRUPS, the super capacitor, because of their inherent capability to absorb transient surges, forms a protective front end to the actual UPS rather than needing to have the involvement of discrete protection devices.

.

## **Acknowledgements**

First off, I dedicate this thesis to my parents whose unwavering love and support made me what I am today. Words can't express my gratitude for all they have provided me with.

I am very much indebted to my academic supervisor, Mr. Nihal Kularatna, without whose brilliance, this research project wouldn't have taken form. He was the guiding light who unfalteringly led me through thick and thin, whose support and enthusiasm was quintessential for the successful completion of my Masters of Engineering degree at The University of Waikato.

Next I would like to express my heartfelt thanks to Mr. Stewart Finlay, the staff in charge at the labs where I did my project work, for putting up with my barrage of requests for electronic components, and never letting me walk back empty handed from his office room. On the same note, I am very much appreciative to Mr. Viking Zhou and Mr. Pawan Shrestha, the departmental technical officers who were always eager to help me with my quest for equipments and components.

A hearty thanks to everyone at College Hall, for being my family in New Zealand, for all the good times I had, and providing me with a vibrant atmosphere for me to study and work.

And I can't articulate my feelings for the two special girls in my life, Ruchi and Smruthi. Without your optimism and love, I would never have realized the value of true friendship. I am lucky enough to be a part of your lives, but I can never imagine how I would have got on with my work if it wasn't for your undying compassion during dire times. Roochie n Smurfie, I will always love you, and you girls will always be the special ones.

And a heartfelt thanks to our administrator Mary Dalbeth and librarian Cheryl Ward, keep up the good work. I was truly blessed to have someone like you to sort out all my stuff. Thank you all, with utmost sincerity.

# **Table of Contents**

| ABSTRACT                                        | i   |

|-------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                | iii |

| TABLE OF CONTENTS                               | v   |

| LIST OF TABLES                                  | ix  |

| LIST OF FIGURES                                 | xi  |

| NOMENCLATURE                                    | XV  |

| CHAPTER ONE: INTRODUCTION                       | 1   |

| 1.1 OVERTURE                                    | 3   |

| 1.2 SCOPE                                       | 4   |

| 1.3 UNINTERRUPTIBLE POWER SUPPLIES              | 4   |

| 1.3.1 STANDBY / OFF-LINE UPS                    | 5   |

| 1.3.2 LINE INTERACTIVE / STANDBY-FERRO UPS      | 6   |

| 1.3.3 ON-LINE UPS                               | 7   |

| 1.4RESEARCH OBJECTIVES AND SPECIFICATIONS       | 8   |

| 1.5 SYSTEM DESCRIPTION                          | 9   |

| 1.6 THESIS OUTLINE                              | 10  |

| CHAPTER TWO: BACKGROUND                         | 13  |

| 2.1 SUPER CAPACITORS                            | 15  |

| 2.1.1 APPLICATIONS OF SUPER CAPACITORS          | 17  |

| 2.1.1.1 PULSE POWER                             | 17  |

| 2.1.1.2 BRIDGE POWER                            | 17  |

| 2.1.1.3 MAIN POWER                              | 18  |

| 2.1.1.4 MEMORY BACKUP                           | 18  |

| 2.1.2 SIZING THE CAPACITANCE REQUIREMENT FOR AN |     |

| APPLICATION                                     | 18  |

| 2.1.3 SUPERCAPACITOR SPECIFICATIONS                        | 19    |

|------------------------------------------------------------|-------|

| 2.1.4 SUPER CAPACITOR AS A CIRCUIT ELEMENT                 | 21    |

| 2.1.5 CHARGING AND DISCHARGING OF SUPER CAPACITORS         | 22    |

| 2.1.6 VOLTAGE EQUALIZATION IN SERIES CONNECTED SUPER       |       |

| CAPACITORS                                                 | 26    |

| 2.2 TRANSIENTS AND SURGES                                  | 27    |

| 2.2.1 PROPAGATION MODES FOR TRANSIENTS AND NOIS            | 32    |

| 2.2.2 TRANSIENT IMMUNITY STANDARDS                         | 35    |

| 2.2.2.1 IEC 61000-4-2: ELECTROSTATIC DISCHARGE (ESD) STANI | OARD  |

|                                                            | 35    |

| 2.2.2.2 IEC 61000-4-4: ELECTRICAL FAST TRANSIENT/BURST (EF | Γ)    |

| STANDARD                                                   | 36    |

| 2.2.2.3 IEC 61000-4-5 : SURGE STANDAR                      | 37    |

|                                                            |       |

| CHAPTER 3: THEORETICAL SYNOPSIS OF THE DESIGN APPR         | COACH |

|                                                            | 47    |

| 3.1 BASIC SURGE PROTECTION BLOCK                           | 49    |

| 3.2 SOLID-STATE SURGE DETECTION AND ISOLATION CIRCUIT      |       |

|                                                            | 50    |

| 3.3 SOLID-STATE AC-DC STEP-DOWN CONVERTER                  | 51    |

| 3.4 MICROCONTROLLER BASED SUPER CAPACITOR BANK             |       |

| SWITCHING CIRCUIT                                          | 52    |

| 3.5 THREE 21.6V / 81.25F SUPER CAPACITOR BANKS             | 53    |

| 3.6 MICROCONTROLLER BASED SYNTHESIZED SINE-WAVE PW         | M     |

| FULL-BRIDGE INVERTER                                       | 54    |

| 3.7 STATIC BYE-PASS SWITCH                                 | 55    |

|                                                            |       |

| CHAPTER 4: SYSTEM IMPLEMENTATION                           | 59    |

| 4.1 BASIC SURGE PROTECTION BLOCK                           | 61    |

| 4.2 SOLID-STATE SURGE DETECTION AND ISOLATION CIRCUIT      |       |

|                                                            | 62    |

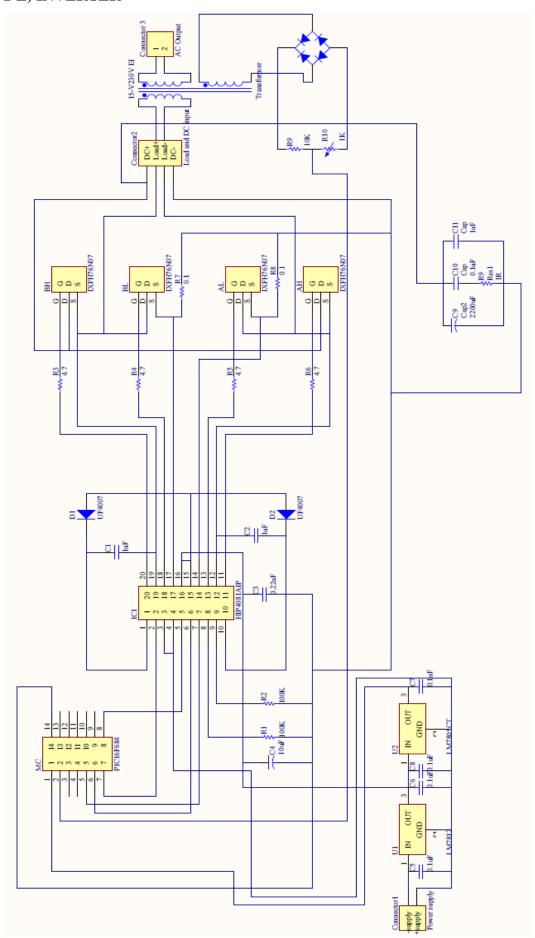

| 4.3 SOLID-STATE AC-DC CONVERTER                            | 63    |

| 4.3.1 HIGH VOLTAGE AC-DC RECTIFIER AND FILTE               | 64    |

| 4.3.2 LOW VOLTAGE SYNTHESIS                                | 64    |

| 4.3.3 BUCK CONVERTER                                       | 65    |

| 4.3.3.1 INDUCTOR SELECTION                            | 65         |

|-------------------------------------------------------|------------|

| 4.3.3.2 OUTPUT CAPACITOR SELECTION                    | 66         |

| 4.3.3.3 COMMUTATION DIODE SELECTION                   | 66         |

| 4.3.3.4 POWER MOSFET SWITCH                           | 66         |

| 4.3.3.5 ASTABLE MULTIVIBRATOR AND TOTEM-POLE DRIVER   |            |

|                                                       | 67         |

| 4.3.4 VOLTAGE SENSE AND LIMITER                       | 68         |

| 4.3.5 CURRENT SENSE AND LIMITER                       | 69         |

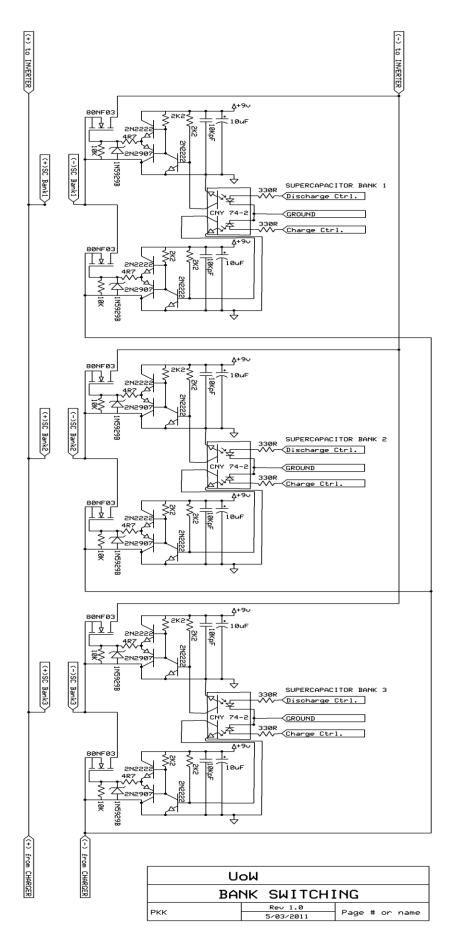

| 4.4 MICROCONTROLLER BASED SUPER CAPACITOR BANK        |            |

| SWITCHING CIRCUIT                                     | 70         |

| 4.5 MICROCONTROLLER BASED SYNTHESIZED SINE-WAVE PW    | 'M         |

| FULL-BRIDGE INVERTER                                  | 74         |

|                                                       |            |

| CHAPTER 5: PERFORMANCE EVALUATION AND RESULTS         | 79         |

| 5.1 SURGE TESTING OF THE BASIC SURGE PROTECTION BLOCK | ζ          |

|                                                       | 83         |

| 5.2 SURGE TESTING OF THE SURGE DETECTION AND ISOLATIO | N          |

| CIRCUIT                                               | 84         |

| 5.3 TESTING OF THE AC-DC CONVERTER                    | 85         |

| 5.4 TESTING OF THE BANK SWITCHING CONTROLLER          | 88         |

| 5.5 TESTING OF THE SINE WAVE PWM INVERTER             | 90         |

|                                                       |            |

| CHAPTER 6: CONCLUSION AND FUTURE DEVELOPMENTS         | 95         |

| 6.1 CONCLUSION                                        | 97         |

| 6.2 FUTURE DEVELOPMENTS                               | 98         |

| APPENDICES                                            | 101        |

| APPENDICES  APPENDIX 1: SCHEMATICS                    | 101        |

| 1-A) SURGE DETECTION AND ISOLATION MODULE             | 103        |

| 1-B) AC-DC STEP-DOWN CONVERTER                        | 103        |

| ,                                                     | 104        |

| 1-C) BANK SWITCHING CONTROLLER                        |            |

| 1-D) BANK SWITCHING CIRCUIT                           | 106<br>107 |

| 1-E) INVERTER APPENDIX 2:MICROCONTROLLER CODING       | 107        |

|                                                       | 108        |

| 2-A) BANK SWITCHING CONTROLLER                        | 100        |

| 2-B) INVERTER | 121 |

|---------------|-----|

| REFERENCES    | 131 |

# **List of Tables**

- Table 1.1: Super capacitor data summary and summary of test results (Kularatna, 2010)3

- Table 1.2: Characteristics of different types of UPSs7

- Table 1.3: Operational characteristics of different types of UPSs8

- Table 4.1: Description of states of super capacitor banks73

- Table 4.2: Description of LED status lights on controller board74

# **List of Figures**

| Figure 1.1: Block diagram of a basic UPS                                | 5         |

|-------------------------------------------------------------------------|-----------|

| Figure 1.2: Block diagram of a standby/off-line UPS                     | 6         |

| Figure 1.3: Block diagram of a line interactive / standby-ferro UPS     | 6         |

| Figure 1.4: Block diagram of an on-line UPS                             | 7         |

| Figure 1.5: Functional block diagram of SRUPS                           | 10        |

| Figure 1.5: Functional block diagram of SRUPS                           | 15        |

| Figure 2.1: Ragone chart of various energy storage devices (Nesscap     | Co. Ltd.  |

| 2008)                                                                   | 15        |

| Figure 2.2: Layered structure of a super capacitor (NEC Corp. 1994-     | 2011)     |

|                                                                         | 15        |

| Figure 2.3: Charge separation in super capacitors (Maxwell Technolo     | ogies,    |

| 2006)                                                                   | 16        |

| Figure 2.4: The first-order circuit model of a super capacitor          | 21        |

| Figure 2.5: The transmission line model equivalent circuit of an SC     | 22        |

| Figure 2.6: Constant current vs. constant power charging of a super     |           |

| capacitor (Maxwell Technologies, 2005)                                  | 23        |

| Figure 2.7: Setup for testing charging/discharging characteristics of S | SC        |

|                                                                         | 23        |

| Figure 2.8: Oscilloscope screenshot of constant current charging of So  | C bank    |

|                                                                         | 25        |

| Figure 2.9: Oscilloscope screenshot of SC bank discharging through a    | a         |

| resistive load                                                          | 25        |

| Figure 2.10: Active voltage balancing circuit for super capacitors (Ca  | ıp-XX     |

| Limited, 2008)                                                          | 26        |

| Figure 2.11: Waveform representation of surge, sag, overvoltage and     | under     |

| voltage conditions                                                      | 27        |

| Figure 2.12: Waveform representation of transients and noise on a po    | ower line |

|                                                                         | 28        |

| Figure 2.13: Harmonics generated non-linear loads                       | 29        |

| Figure 2.14: Voltage and current surge waveforms                        | 29        |

| Figure 2.15: Transient surge suppression devices                        | 31        |

| Figure 2.19: 6.8KV differential-mode surge measured between Line a         | nd       |

|----------------------------------------------------------------------------|----------|

| Neutral wires                                                              | 34       |

| Figure 2.20: 6KV common-mode surge measured between Line/Neutr             | al wires |

| with respect to Ground wire                                                | 34       |

| Figure 2.18: ESD Waveform                                                  | 36       |

| Figure 2.19: EFT burst waveform, repetition rate and burst period          | 37       |

| Figure 2.20: IEC 61000-4-5 Voltage impulse waveform                        | 38       |

| Figure 2.21: IEC 61000-4-5 current impulse waveform                        | 38       |

| Figure 2.22: 6.6KV voltage surge generated by the NoiseKen                 | 39       |

| Figure 2.23: Basic surge generator circuit                                 | 39       |

| Figure 2.24: Voltage surge waveform parameters                             | 40       |

| Figure 2.25: Rise time parameters for voltage surge waveform               | 41       |

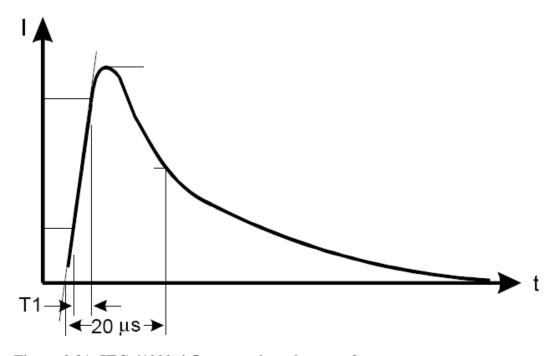

| Figure 2.26: Current surge duration waveform                               | 42       |

| Figure 2.27: Surge generator circuit in short circuit mode for current     | surge    |

|                                                                            | 42       |

| Figure 2.28: Voltage surge waveform parameters                             | 43       |

| Figure 2.29: Rise time parameters for current surge waveform               | 44       |

| Figure 2.30: Current surge duration waveform                               | 44       |

| Figure 3.1: Graphical representation of surge suppression (EPCOS ${\bf A}$ | G,       |

| 2008)                                                                      | 49       |

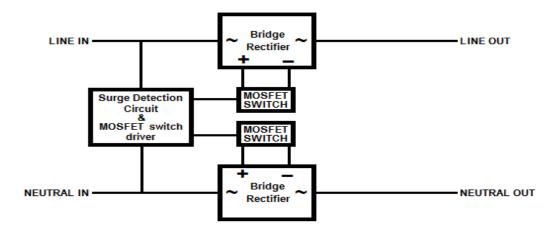

| Figure 3.2: Basic surge protection block                                   | 50       |

| Figure 3.3: Surge detection and isolation scheme                           | 51       |

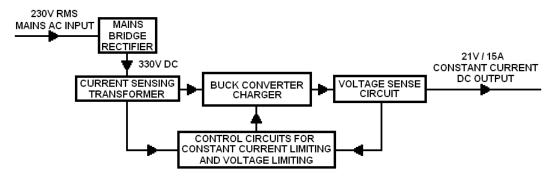

| Figure 3.4: Solid-State AC-DC Step-Down Converter                          | 52       |

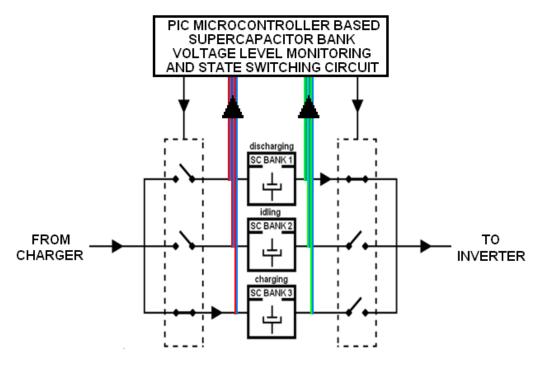

| Figure 3.5: Microcontroller based super capacitor bank switching sch       | eme      |

|                                                                            | 53       |

| Figure 3.6: A single 81.25F / 21.6V super capacitor bank                   | 54       |

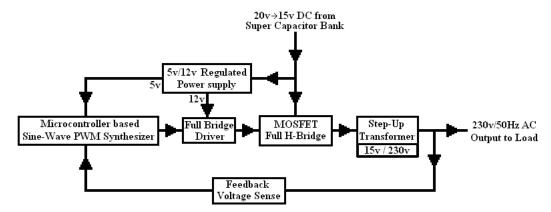

| Figure 3.7: Block diagram of the inverter                                  | 55       |

| Figure 3.7: Static bye-pass switch configuration                           | 56       |

| Figure 4.1 Circuit schematic for the basic surge protection block          | 61       |

| Figure 4.2: Circuit schematic for the surge detection and isolation circ   | cuit     |

|                                                                            | 63       |

| Figure 4.3: Circuit schematic for high voltage AC-DC rectifier and fil     | ter      |

|                                                                            | 64       |

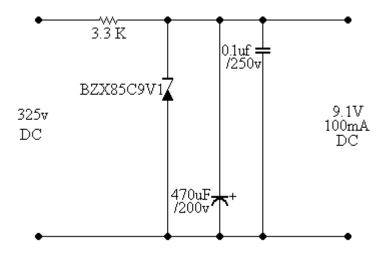

| Figure 4.4: Circuit schematic for the low voltage synthesis stage          | 65       |

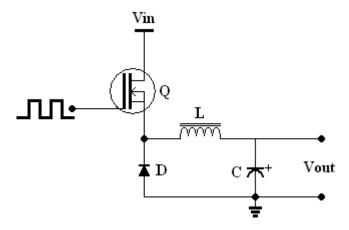

| Figure 4.5 Buck converter configuration                                    | 65       |

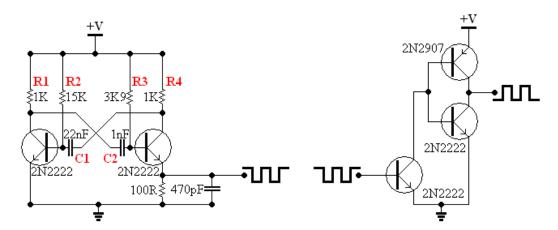

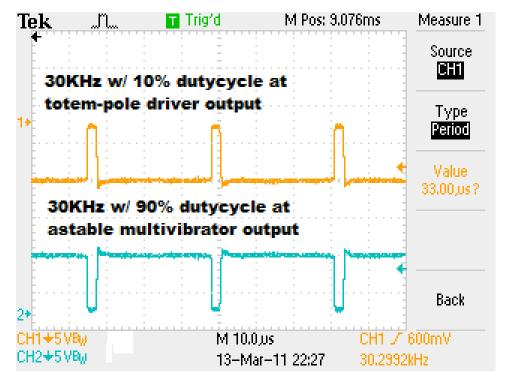

| Figure 4.6: Schematics for a stable multivibrator and totem-pole drive   | r         |

|--------------------------------------------------------------------------|-----------|

|                                                                          | 68        |

| Figure 4.7: Multivibrator and driver output waveforms                    | 68        |

| Figure 4.8: Circuit schematic for voltage sense and limiter circuit      | 69        |

| Figure 4.9: Circuit schematic for current sense and limiter circuit      | 70        |

| Figure 4.10: Start-up routine running in the PIC®16F690 microcontro      | oller     |

|                                                                          | 71        |

| Figure 4.11: Sub-routine for normal SRUPS operation running in the       | PIC®      |

| 16F690 microcontroller                                                   | 72        |

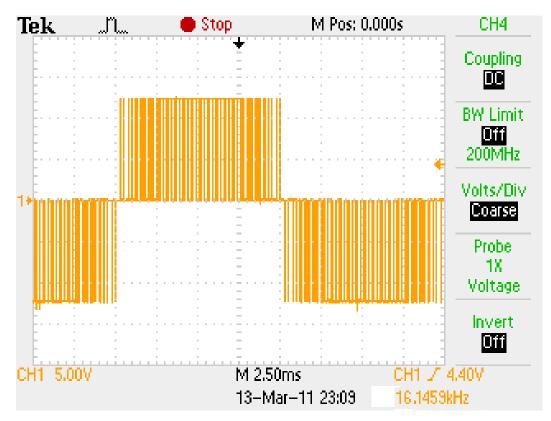

| Figure 4.12: Full-bridge PWM mode drive signals                          | <b>75</b> |

| Figure 4.13: No-load waveform at full H-Bridge output                    | <b>76</b> |

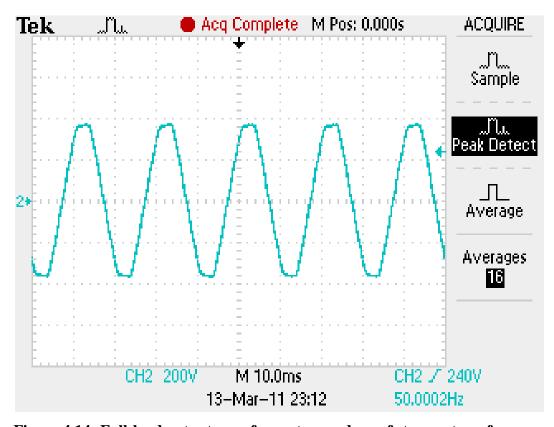

| Figure 4.14: Full-load output waveform at secondary of step-up transf    | former    |

|                                                                          | <b>76</b> |

| Figure 5.1: Block diagram of the final revision of the SRUPS system      | 81        |

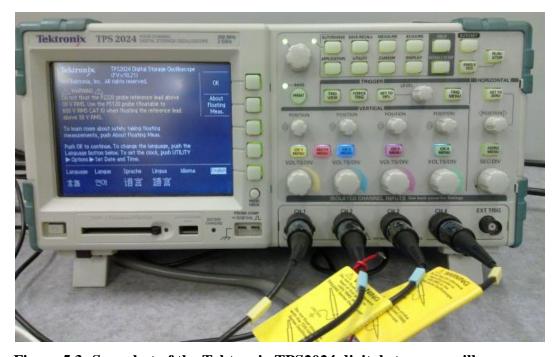

| Figure 5.2: Photograph of the NoiseKen LSS-6110 lightning surge sim      | ulator    |

|                                                                          | 82        |

| Figure 5.3: Snapshot of the Tektronix TPS2024 digital storage oscillos   | cope      |

|                                                                          | 82        |

| Figure 5.4: Connection topology for surge testing of the basic surge     |           |

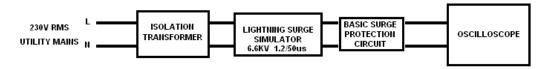

| protection block                                                         | 83        |

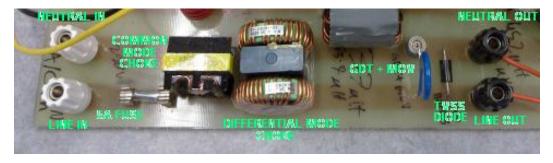

| Figure 5.5: Snapshot of the basic surge protection block                 | 83        |

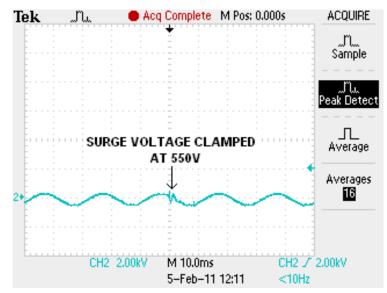

| Figure 5.6: Oscilloscope screenshot of surge suppression by basic surg   | e         |

| protection block                                                         | 83        |

| Figure 5.7: Connection topology for surge testing of the surge detection | n and     |

| isolation circuit                                                        | 84        |

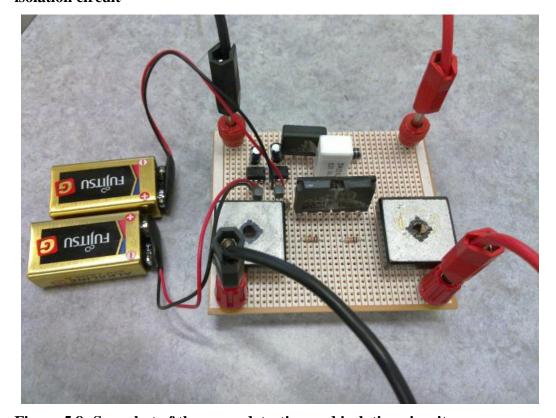

| Figure 5.8: Snapshot of the surge detection and isolation circuit        | 84        |

| Figure 5.9: Oscilloscope screenshost of the operation of the surge detec | ction     |

| and isolation circuit                                                    | 85        |

| Figure 5.10: Test setup for charging test of AC-DC converter             | 85        |

| Figure 5.11: Waveform for charge testing                                 | 86        |

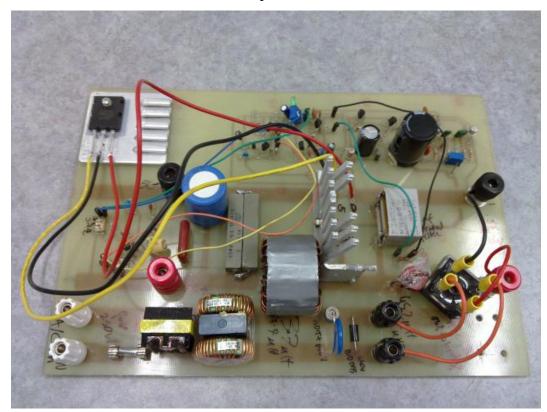

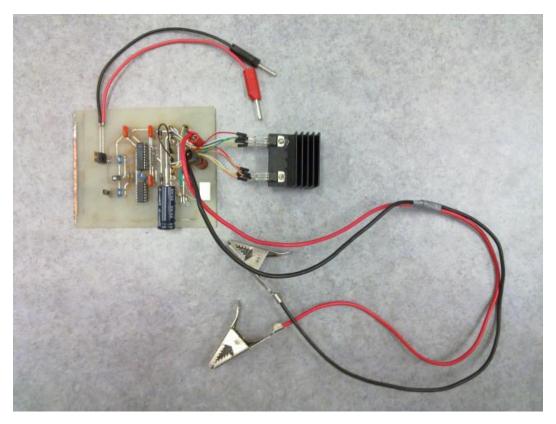

| Figure 5.11: Photograph of the charger circuit                           | 87        |

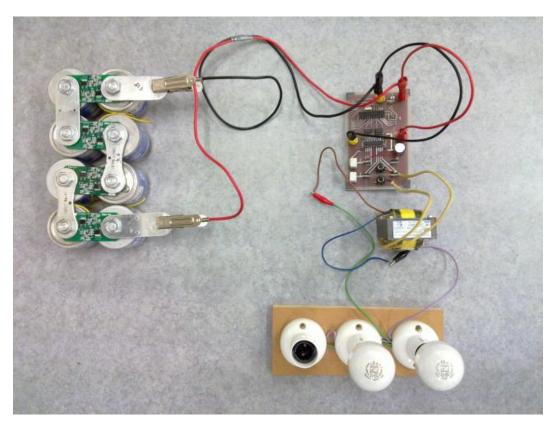

| Figure 5.12: Photograph of the bank switching controller and MOSFE       | ET        |

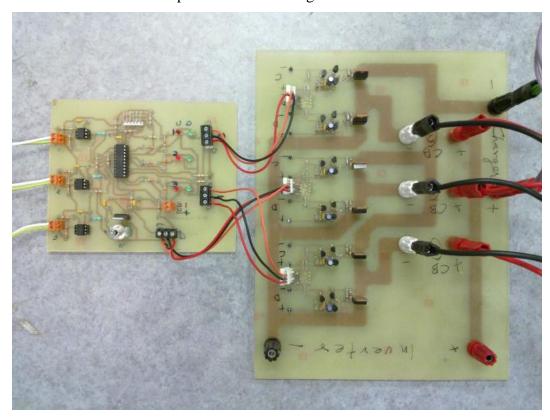

| switches                                                                 | 88        |

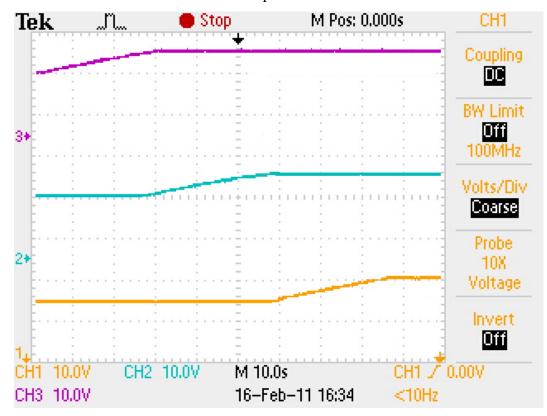

| Figure 5.13: Waveform for start-up routine                               | 88        |

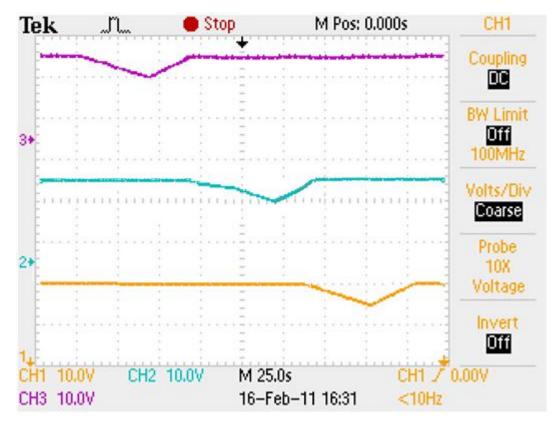

| Figure 5.14: Waveform for nominal operation sub-routine                  | 89        |

| Figure 5.15: Photograph of the first revision inverter  | 90 |

|---------------------------------------------------------|----|

| Figure 5.16: Photograph of the second revision inverter | 90 |

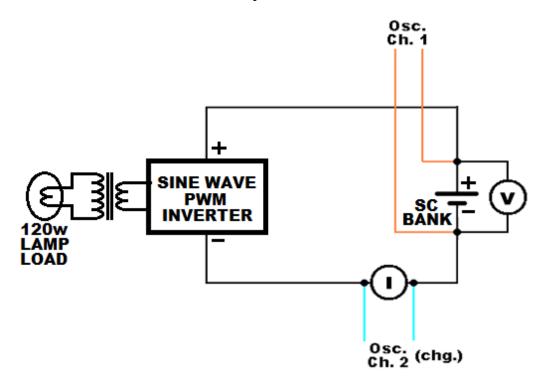

| Figure 5.17: Setup for the discharge testing            | 91 |

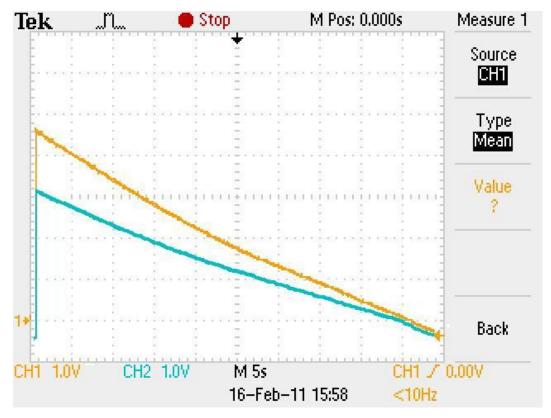

| Figure 5.18: Discharge test waveform                    | 91 |

| Figure 5.19: SRUPS input AC vs. output AC waveforms     | 92 |

# **Nomenclature**

**AC** Alternating Current

DC Direct Current

**EMI** Electro-Magnetic Interference

**ESR** Effective Series Resistance

GDT Gas Discharge Tube

LED Light Emitting Diode

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOV Metal Oxide Varistor

PIC® Peripheral Interface Controller

PWM Pulse Width Modulation

**RMS** Root Mean Square

SC Super Capacitor

**SRUPS** Surge Resistant Uninterruptible Power Supply

TVSS Transient Voltage Surge Suppressor

**UPS** Uninterruptible Power Supply

Chapter 1

Introduction

#### 1.1 OVERTURE

Super capacitors (SCs) or ultra capacitors are electrochemical double layer capacitors that have high power densities with limited energy density as compared to conventional batteries. Their beginnings can be traced back to the laboratories of Sohio Corporation of Cleveland, New Jersey some 40 years ago [2]. Nowadays SCs with capacitance values in the range of thousands of farads are commercially available, thus making them a promising energy storage device for niche power electronics applications. SCs are a reliable alternative to batteries in the sense they have enhanced life cycles as their operation involves only non-faradaic electrostatic phenomenon.

Recent research carried out by the author's supervisor opened up a previously uncharted application area for SCs. Their extremely high capacitance values theoretically allow them to absorb large amounts of energy which practically can be interpreted as surge endurance. Table 1.1 summarizes test results obtained from surge testing SCs from different vendors by exposing them to short duration surges with energy values specified in IEEE C62-41 and IEC 61000-4-5 and similar standards.

Table 1.1: Super capacitor data summary and summary of test results (Kularatna, 2010)

| Parameters as per data sheets | Cap-XX      | Nesscap           | Maxwell Boostcap  |

|-------------------------------|-------------|-------------------|-------------------|

| Capacitance                   | 0.18 F      | 90 F              | 230 F             |

| Rated DC Voltage              | 2.3 V       | 2.7 V             | 2.5 V             |

| Effective Series Resistance   | 45 mΩ       | 0.33 mΩ           | 2.2 mΩ            |

| Operating Temperature Range   | -40 - 70 °C | -40 - 65 °C       | -40 - 70 °C       |

| Leakage Current               | 3.5 μΑ      | 0.75 mA           | 0.45 mA           |

| Surges persevered             | 150-250     | Didn't fail after | Didn't fail after |

| before failure                |             | 600 hits          | 1000 hits         |

#### Chapter 1: Introduction

These results show that SCs with higher capacitances have extended surge withstanding capabilities. Therefore, SCs, with their increased functionality, life cycle costs, reliability and surge resistance capabilities offer the perfect energy storage solution to make successful mission-critical power backup systems.

#### **1.2 SCOPE**

The project aimed at developing a prototype super capacitor based on-line, double-conversion surge resistant uninterruptible power supply (SRUPS) to provide a clean and efficient reserve source of power for sensitive electronic equipments. The principal intention of this project is to demonstrate the feasibility of SCs, both as energy storage devices for power back up as well as its surge resistance capability when used as proposed in the system.

The prototype shall consist of a solid state AC-DC step-down converter, super capacitor based power reserve, a microcontroller based super capacitor bank switching circuit, a solid-state inverter, an automatic solid-state surge detection and isolation circuit and a static by-pass switch. As a prototype, the system is designed to work off the 230V/50Hz utility mains power and deliver clean useable power of at least100W at the load at 230V/50Hz using three consecutively switched super capacitor banks as the energy storage elements for providing power backup and as a system front end to offer surge protection.

The project was originally undertaken with funding from WaikatoLink, the commercialization and technology transfer arm of The University of Waikato with a view to visualize commercially viable patentable applications of SCs that haven't been developed elsewhere.

#### 1.3 UNINTERRUPTIBLE POWER SUPPLIES

UPSs arose by the turn of the century from the apparent need for clean and "break-free" power for electronic equipments that had ever increasing system complexities and sensitivities. UPSs act as a bridge and a back-up to stand between the utility mains power supply and the equipment. They generally have rechargeable batteries as the energy storage elements for use as the backup power source. Most UPSs are not inherently resistant to power surges or other line

anomalies. They have discrete suppression and filtering modules that are inserted in their initial stages to tackle these issues.

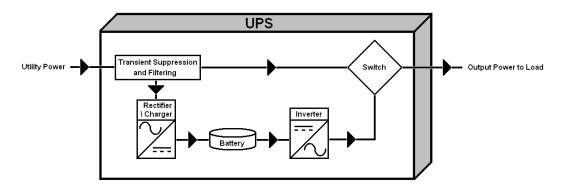

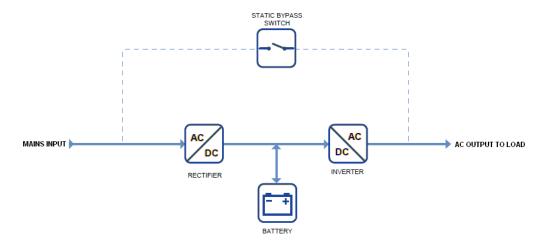

Figure 1.1 shows the basic building blocks of a UPS which are iterated in different topologies to create different types of UPSs.

Figure 1.1: Block diagram of a basic UPS

In a layman's point of view, there are only two types of UPS systems, namely the standby UPS and the online UPS, their operation being obvious from their naming terminology. But from a design approach point of view, UPSs can be classified as:

- Standby / Off-line

- Line Interactive / Standby Ferro

- Standby-Ferro

- On-Line

### 1.3.1 STANDBY / OFF-LINE UPS

This UPS is commonly found in domestic household environments. Figure 1.2 shows the operation of the standby UPS. The transfer switch normally connects the filtered AC input as the primary power source to run the load and in the event of a utility power failure, switches to the battery / inverter as the backup. The inverter is only operational when the power fails, hence the name "standby". These UPSs are cheap, offer high efficiency, and serves its intended purpose for low sensitivity equipmental power backup requirements. The level of utility line filtering and surge suppression available in standby UPSs are price dependent and may be even absent in low-end versions which make them highly unreliable when operated in environments prone to line transients and surges.

Figure 1.2: Block diagram of a standby/off-line UPS

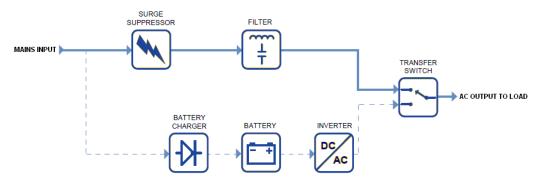

#### 1.3.2 LINE INTERACTIVE / STANDBY-FERRO UPS

These were formerly the prevailing type of UPSs used in the 0.5-15KVA range. This design relies on a special saturating transformer that has three windings, two bifilar wound primaries and a secondary. The primary power path runs from the mains AC input, through a transfer switch, via one of the transformer primaries and onto the connected load. In case of power failure, the transfer switch opens and the inverter picks up the output load via the second primary winding of the transformer. Here, the inverter is in standby mode during normal operation. The transformer, along with the isolation it provides, also has a special "ferroresonant" capability that ensures limited voltage regulation and output waveform "shaping". As these transformers are quite large, heavy and inherently inefficient these UPSs are large and generate a great deal of heat. Figure 1.3 demonstrates the standby-ferro topology.

Figure 1.3: Block diagram of a line interactive / standby-ferro UPS

#### 1.3.3 ON-LINE UPS

These UPSs are mainly used where power requirements exceed 10KVA. Here, there is no transfer switch as the connected load always runs off the inverter. The inverter runs directly off the rectified mains AC during normal operation and when there is a power failure, the inverter runs off the battery. The changeover switch is negated as the battery is always floating. If a low voltage battery bank is used, the UPS is called a Double-Conversion on-line UPS as the utility mains is rectified and stepped down to charge the battery and the battery power is boosted to the mains voltage before being fed to the inverter. For high power on-line UPS systems, high voltage battery banks (similar to utility mains voltage) are arranged and an active power factor correction circuit serves as the mains rectifier as its output DC voltage is automatically adjusted to float charge the battery bank and drive the inverter. These designs are called Delta-Conversion on-line UPSs. The working of on on-line UPS is depicted in Figure 1.4

Figure 1.4: Block diagram of an on-line UPS

Tables 1.2 and 1.3 describe the main characteristics of the different types of UPSs that have been discussed so far.

Table 1.2: Characteristics of different types of UPSs

| Type of UPS      | Practical         | Voltage      | Cost per |

|------------------|-------------------|--------------|----------|

| Type of Ors      | Power Range (KVA) | Conditioning | VA       |

| Standby/Off-line | 0-0.5             | Low          | Low      |

| Standby-Ferro /  | 0.5-15            | High         | High     |

| Line Interactive | 0.5 15            | 111511       | 111511   |

| On-Line          | 5-5000            | High         | Medium   |

Table 1.3: Operational characteristics of different types of UPSs.

| Type of UPS                                | Efficiency | Inverter Always Operating | Benefits                                         | Limitations                                                            |

|--------------------------------------------|------------|---------------------------|--------------------------------------------------|------------------------------------------------------------------------|

| Standby<br>/Off-line                       | Low        | No                        | Low cost, High efficiency, compact               | Uses battery during brownouts, Impractical over 2kVA                   |

| Standby-<br>Ferro /<br>Line<br>Interactive | High       | No                        | Excellent voltage conditioning, high reliability | Low efficiency, unstable in combination with some loads and generators |

| On-Line                                    | High       | Yes                       | Excellent voltage conditioning, high efficiency  | Impractical under 5kVA                                                 |

#### 1.4 RESEARCH OBJECTIVES AND SPECIFICATIONS

The intention of this research is to develop a prototype 230V/50Hz on-line double-conversion UPS that utilizes SC banks as its energy storage element. The prototype must be able to deliver at least 100W of useable power at the load side at 230V/50Hz. Three SC banks are proposed to power the system consecutively to enhance the backup capability of the UPS. Also as the SC banks form the front end of the UPS system, its inherent capability to withstand surges will be put to use as the surge suppression element in the system to ultimately create a surge resistant UPS.

The main objectives in developing the super capacitor based surge resistant uninterruptible power supply (SRUPS) are as follows:

- Runs off the utility mains power supply of 230v / 50Hz

- Run a connected 230v / 50Hz AC load at 100w

- Withstand surges as per IEEE C62-41 and IEC 61000-4-5 specifications

- Fast surge detection and system isolation

- Synthesized pure sinusoidal output AC

- Reliable with a high operational mean time between failure (MTBF) hours

- Economical with relation to component count and costs

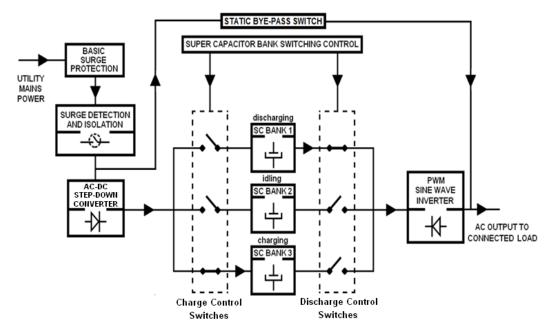

#### 1.5 SYSTEM DESCRIPTION

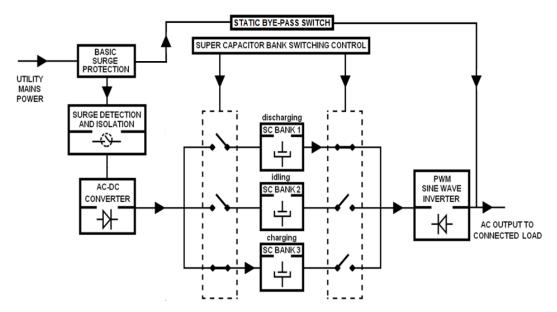

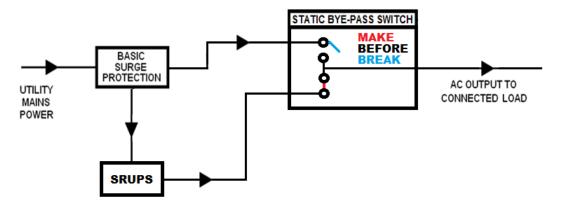

The SRUPS consists of six major parts.

- Basic surge protection block

- Solid-state surge detection and isolation circuit

- Solid-state AC-DC step-down converter

- Microcontroller based super capacitor bank switching circuit

- Three 21.6v / 81.25F super capacitor banks

- Microcontroller based synthesized sine-wave PWM full-bridge inverter

- Static bye-pass switch

Off the shelf transient voltage surge suppression devices form the initial surge protection. Opto-couplers and solid state switches are used in the surge detection and isolation circuit. A high-end power MOSFET is used in a buck converter based configuration for the AC-DC step-down converter to charge the SC banks. Eight 2.7v/650F Maxwell BOOSTCAP super capacitors connected in series are used in each of the three SC banks. A PIC® microcontroller based control and monitoring circuit incorporating MOSFET switches is used for switching between the charge/idle/discharge states of the SC banks. A MOSFET driven PIC® microcontroller based synthesized sine wave pulse width modulated full-bridge inverter is used for efficient DC-AC conversion. In the event that the UPS must be taken off-line for maintenance of UPS, or unforeseen emergency situations, the critical load shall be transferred to the utility mains source via the static switch.

The complete functional block diagram of the SRUPS is demonstrated in Figure 1.5.

Figure 1.5: Functional block diagram of SRUPS

#### 1.6 THESIS OUTLINE

**Chapter One: Introduction.** A basic outline and scope of the project is discussed and the background on the inception of the idea of using super capacitors as energy storage elements in power back—up systems and how the same could be used to offer protection against power line surges is brought to light. Also briefed are the different types of UPSs in existence. Finally a rundown of the overall system functionality of the proposed SRUPS is also given.

Chapter Two: Background. Here, the two main topics discussed will be super capacitors and transient surges. The literature survey carried out on these topics form the backbone for the ideologies used in the development of the prototype SRUPS. This chapter sheds light on the working and operational characteristics of super capacitors and then moves on to briefly explain principles of transient surges, surge protection and surge testing.

Chapter Three: Theoretical Synopsis of the Design Approach. The theories concerned in the design of the various electronic circuits involved in the different stages of the SRUPS are discussed in this chapter. The reasons why the circuits used to implement these stages are the better design choices amongst other available technologies are also brought to light.

**Chapter Four: System Implementation.** This chapter deals with how the individual modules involved in the SRUPS were realized and tested and then integrated to one single entity to form the complete operational system, which is the super capacitor based surge resistant uninterruptible power supply.

Chapter Five: Performance Evaluation and Results. After the implementation of the SRUPS, tests and measurements carried out to determine its operational performance characteristics and the corresponding results obtained are categorized in this chapter.

Chapter Six: Conclusion and Future Developments. The SRUPS developed in this research project is a prototype. There are certain areas in the modules of the SRUPS that could be fine-tuned to improve the overall performance and efficiency of the system. Technological and other constraints that limited the design of the SRUPS are also discussed. This chapter concludes with general idea that went into the SRUPS and what future improvements could be incorporated to progress on the prototype developed.

Chapter 2

Background

#### 2.1 SUPER CAPACITORS

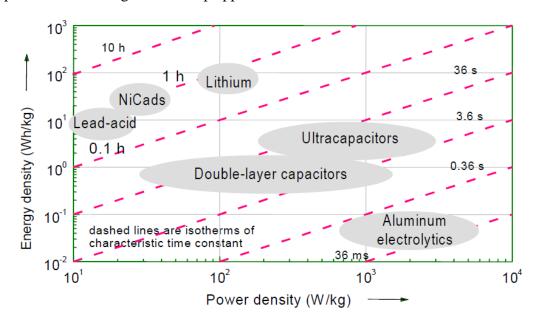

Electrochemical double layer capacitors are also known as super capacitors or ultra capacitors. Super capacitors (SCs) are reversible energy storage devices that have higher instantaneous power densities than conventional batteries and higher energy densities than electrostatic dielectric capacitors as can be seen depicted in Figure 2.1. Energy density is the amount of energy stored per unit mass. Power density is the maximum amount of power that can be supplied per unit mass. An SC stores energy via an electrostatic process by polarizing an electrolytic solution. Though it is an electrochemical device there are no chemical reactions involved in its energy storage mechanism. This mechanism is highly reversible, allowing the SC to offer high charge-discharge cycling capabilities, making them well suited in power conditioning and back-up applications.

Figure 2.1: Ragone chart of various energy storage devices (Nesscap Co. Ltd., 2008)

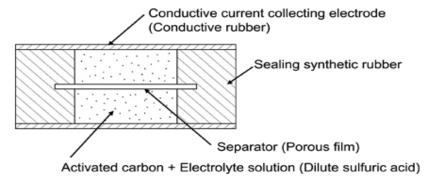

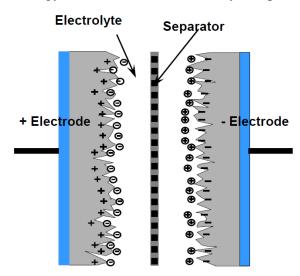

An SC can be visualized as two nonreactive porous plates suspended within an electrolyte with an applied voltage across the plates. This is shown in figure 2.2.

Figure 2.2: Layered structure of a super capacitor (NEC Corp. 1994-2011)

#### Chapter 2: Background

The applied potential on the positive plate attracts the negative ions in the electrolyte, while the potential on the negative plate attracts the positive ions. This effectively creates two layers of capacitive storage, as shown in figure 2.3, one where the charges are separated at the positive plate, and another at the negative plate, thus the terminology electrochemical double layer capacitors.

Figure 2.3: Charge separation in super capacitors (Maxwell Technologies, 2006)

The capacitance (C) of a parallel plate capacitor with permittivity of the dielectric  $(\varepsilon)$ , area of the plates (A) and inter-plate separation (d) is given as:

$$C = \varepsilon \frac{A}{d} \tag{1}$$

Conventional electrolytic capacitors storage area is derived from thin plates of flat, conductive material. High capacitance is achieved by winding great lengths of material. Further increases are possible through texturing on its surface, increasing its surface area. A conventional capacitor separates its charged plates with a dielectric material: plastic, paper or ceramic films. The thinner the dielectric the more area can be created within a specified volume. The limitations of the thickness of the dielectric define the surface area achievable. An SC on the other hand derives its area from a porous carbon-based electrode material. The porous structure of this material allows its surface area to approach 2000 square meters per gram, much greater than can be accomplished using flat or textured films and plates. An SC's charge separation distance is determined by the size of the ions in the electrolyte, which are attracted to the charged electrode. This charge separation (less than 10 angstroms) is much smaller than can be

accomplished using conventional dielectric materials. The combination of enormous surface area and extremely small charge separation gives the super capacitor its outstanding capacitance relative to conventional capacitors.

The energy storage (E) for a capacitor with a capacitance (C) and voltage rating (V) is given as:

$$E = \frac{1}{2}CV^2 \tag{2}$$

### 2.1.1 APPLICATIONS OF SUPER CAPACITORS

Typical applications of SCs span from a requirements of a few milliamps of current or milliwatts of power to several hundred amperes of current or several hundred kilowatts of power needs. Industries employing SCs have included: consumer electronics, traction, automotive, and industrial.

#### 2.1.1.1 PULSE POWER

SCs are ideally suited for pulse power applications. As the energy storage is not a chemical reaction, the charge/discharge behavior of the capacitors is efficient. Since SCs have low internal impedance they are capable of delivering extremely high currents and are often placed in parallel with batteries to level the loading of the batteries, extending battery life. The SC buffers the battery from seeing the high peak currents experienced in the application. This methodology is employed for devices such as digital cameras, hybrid drive systems and regenerative braking (for energy recapture).

#### 2.1.1.2 BRIDGE POWER

SCs are utilized as temporary energy sources in many applications where immediate power availability may be difficult. This includes UPS systems utilizing generators, fuel cells or flywheels which function as the main power backup for applications. All of these systems require a definite though short start up time before they are fully functional and can switch over the load, thereby generating momentary power interruptions. SC systems are utilized to provide the appropriate amount of ride-through time until the primary backup power source kicks in and becomes available to take up the load.

### **2.1.1.3 MAIN POWER**

SCs are perfectly suitable to be used as the primary source of power for applications requiring power for only short periods of time or if it is only acceptable to allow short charging time before use. Examples of such applications include toys, emergency flashlights, institutional paging devices, solar charged accent or mood lighting, and powering emergency access points.

#### 2.1.1.4 MEMORY BACKUP

When an application has an available power source to keep the SCs trickle charged as in computer systems, they may be suited for memory backup, system shutdown operations, or event notifications. The SCs can be maintained at its full charged state and can act as a power reserve to perform critical functions in the event of loss of power. This may include automatic monitoring and reporting systems for reporting power outage, micro-controllers based embedded systems and mother board memories in computers.

# 2.1.2 SIZING THE CAPACITANCE REQUIREMENT FOR AN APPLICATION

Determination of the proper capacitor and number of capacitors is dependent on the intended application. For sizing the system correctly a number of factors should be known. These factors include the maximum and minimum operating voltage of the application, the average current or power, the peak current or power, the operating environment temperature, the run time required for the application, and the required life of the application. Every super capacitor has a rated voltage ( $V_R$ ). Since SCs are low voltage devices, this rated voltage is generally less than what the required application voltage is. Knowing the maximum application voltage ( $V_{MAX}$ ) will determine how many capacitor cells are required to be series connected. The number of series connected cells (N) is determined by:

$$N = \frac{V_{MAX}}{V_R} \tag{3}$$

Next, by knowing the average current (I) in amps, the required run time (dt) in seconds and the minimum working voltage  $(V_{MIN})$  for the application, an approximate capacitance required to power the system  $(C_{SYS})$  can be calculated.

$$C_{SYS} = I * \frac{dt}{dv} = I * \frac{dt}{(V_{MAX} - V_{MIN})}$$

(4)

The total system capacitance requires is comprised of the capacitance of all the series connected capacitors for achieving  $V_{MAX}$ . For capacitors connected in series the total capacitance ( $C_{TOT}$ ) is determined by:

$$\frac{1}{C_{TOT}} = \frac{1}{C_1} + \frac{1}{C_2} + \dots + \frac{1}{C_n} \tag{5}$$

For n SC cells of equal capacitance (C) connected in series, the total capacitance is given by:

$$C_{TOT} = \frac{c}{n} \tag{6}$$

It may also be necessary to place one or more capacitors in parallel to attain the needed energy requirements. For n capacitors connected in parallel the equivalent capacitance ( $C_{EO}$ ) is determined by:

$$C_{EO} = C_1 + C_2 + ... + C_n \tag{7}$$

There are many other items to consider for properly sizing the capacitance value required for an application. This includes the internal resistance of the capacitor to account for the instantaneous voltage drop associated with an applied current, the ambient operating temperature which affects the internal resistance and the capacitor life, and the lifetime expected of the application. The super capacitor performance requirement at end of life of the application is necessary to ensure proper initial sizing for the system.

### 2.1.3 SUPER CAPACITOR SPECIFICATIONS

Given below are the technical specifications and ratings that need to be kept in mind and considered before and during the selection and application of super capacitors in a system.

- **Capacitance** the measurement of energy storage capacity in joules.

- Voltage the maximum operating voltage for a single capacitor. It is

possible for the capacitors to experience voltages in excess of the rated

voltage. The impact is dependent on the time and temperature during this

exposure. At no time should the capacitor be subjected to voltages in

excess of 10% of the rated voltage.

- Internal Resistance, DC the resistance corresponding to all the resistivecomponents within the super capacitor. It is compromised of resistive components attributed to contacts, electrode, electrolyte, and other material resistances.

- Internal resistance, 100 hz or 1 khz the measure of the high frequency resistance component and is mainly attributed to contact resistance. Because of the time constant of the super capacitors, operation at this frequency is highly inefficient.

- Thermal Resistance this may be used to determine the heat generation within the SC at any given current load and duty cycle. This value is based on free convection and would be considered for the worst case scenario. Forced convection would improve the thermal resistance.

- **Short Circuit Current** momentary current delivery possible by the SC if it is short circuited. This is intended purely for cautionary purposes and not for nominal usage.

- Leakage Current the stable parasitic current that is expected when the SC is held indefinitely on charge at its rated voltage. This value is voltage and temperature dependent.

- Operating Temperature Range represents the operating temperature range of the S and may not reflect the ambient temperature.

- **Storage Temperature Range** represents the safe storage temperature without affecting ultracapacitor performance when no voltage is applied to the ultracapacitor.

- Endurance Capacitance the maximum capacitance change expected

when the SC is held at rated voltage for a specified life-time and

temperature, which is intended to be considered as the upper operational

limit.

- Endurance Resistance the maximum resistance change expected if the SC is held at rated voltage for a specified life-time and temperature, which is intended to be taken as the upper operational limit.

- Maximum Energy the maximum energy available for SC while it is new, when it is discharged from its maximum rated working voltage to zero volts fully discharged condition

- Peak Power Density measurement of the instantaneous power from full rated voltage  $V_R$  to  $V_R^2/4R_{AC}$  where  $R_{AC}$  is the AC resistance. This value does not represent the sustainable power.

- **Power density** gravimetric power density calculated between the ranges of a 20% to 40% voltage drop from the rated voltage of SC.

- **Life Time** expected performance change for the super capacitor if held at rated voltage and 25°C for 10 years.

- Cycle Life expected performance change after cycling half to one million times from rated voltage to half the rated voltage. Cycling is to be performed at a duty cycle resulting in no heating of the super capacitor with the SC maintained at 25°C.

# 2.1.4 SUPER CAPACITOR AS A CIRCUIT ELEMENT

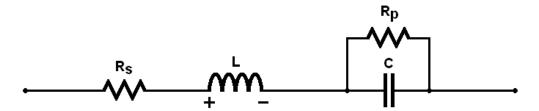

The circuit schematic in Figure 2.4 represents the first-order model for a super capacitor. It is comprised of four ideal circuit elements, which include a capacitance C, a series resistor R<sub>S</sub>, a parallel resistor R<sub>P</sub>, and a series inductor L. R<sub>S</sub> is called the equivalent series resistance (ESR) and contribute to energy loss during capacitor charging and discharging. R<sub>P</sub> simulates the energy loss due to capacitor self-discharge. It is often referred to as the leakage current resistance. Inductor L results primarily from the physical construction of capacitor and is usually small. However, it cannot be neglected in many applications, particularly those operating at high frequencies or subjected to hard switching.

Figure 2.4: The first-order circuit model of a super capacitor

Resistor  $R_P$  is always much higher than  $R_S$  in practical capacitors. Thus it can often be neglected, particularly in high-power applications. In that case, the impedance of the first-order circuit model Z is:

$$Z = R + i(2\pi f L - \frac{1}{2\pi f C}) \tag{8}$$

The impedance is purely resistive when  $2\pi f L - \frac{1}{2\pi f C} = 0$ , or  $f = \frac{1}{2\pi\sqrt{LC}}$ .

This particular frequency f is referred to as the resonance frequency of the super capacitor. Thus, the impedance of circuit is simply the resistance at self-resonance. However, SCs exhibit non-ideal behavior, which result primarily from the porous material used to form the electrodes that causes the resistance and capacitance to be distributed such that the electrical response mimics more of a

transmission line like behavior. The various parameters in this ladder circuit approximation; L,  $Rp,R_1$ ,  $R_2,...R_n,C_1$ ,  $C_2,...C_n$  can be derived by using the nonlinear least-squares fitting algorithm. Therefore, it would be more suitable to use a more generalized circuit as shown in Figure 2.5 for representing a more realistic electrical response of an SC.

Figure 2.5: The transmission line model equivalent circuit of an SC

### 2.1.5 CHARGING AND DISCHARGING OF SUPER CAPACITORS

Charging of SCs is simple while at the same time may present some unique challenges. Unlike batteries, SCs may be charged and discharged at similar rates. An SC with zero charge looks like a short circuit to the charging source. So day-to-day power supplies which fold back the output current in response to a perceived short circuit are not suitable for charging SCs.

A DC-to-DC constant current regulator is the simplest form of active charging for an SC. The power losses due to SC heating are proportional to current squared times the duty cycle of the converter.

When charge time is critical, constant power charging provides the solution for the fastest charging. Constant power charging can transfer all the available power from the charging source onto the SC.

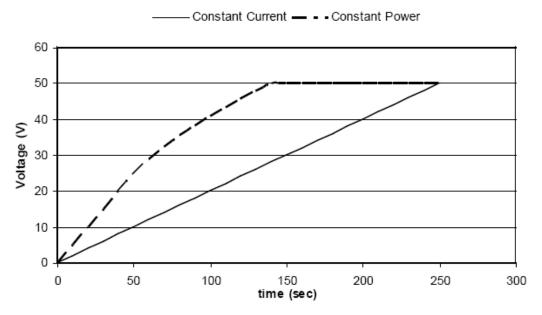

The graph in Figure 2.6 courtesy of Maxwell Technologies shows the charging characteristics for a 100F/50V super capacitor module in constant current and constant power charging topologies. In constant current mode, the module is charged from a 50 V, 20 amp power supply. In the constant power mode, it is charged at a constant power of 1000 watts with a voltage limiter of 50v. The constant 20 amp charge current required 250 seconds to charge the module to 50 volts while the 1000 watt constant power charger required 145 seconds to charge the module to 50 volts.

Figure 2.6: Constant current vs. constant power charging of a super capacitor (Maxwell Technologies, 2005)

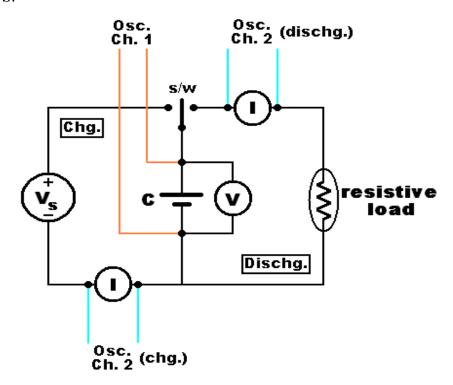

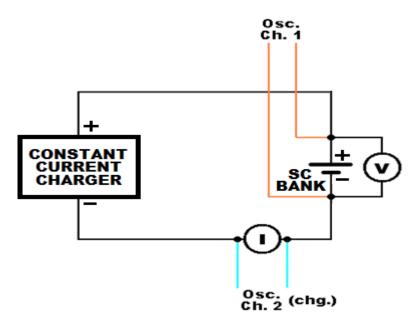

The setup shown in Figure 2.7 was used for timing the charging and discharging characteristics of the 21.6v/81.25F super capacitor module that is employed in the SRUPS.

Figure 2.7: Setup for testing charging/discharging characteristics of SC

The constant current charging circuit used in the charger section of the SRUPS was employed to perform the charging. This charger is a 15A constant current charger with a voltage limiter set at 21.6V. For a constant current charger, the

# Chapter 2: Background

momentary increase in voltage with respect to time ( $\Delta V/\Delta t$ ) is a constant. When Q denotes the charge, C is the capacitance and I is the current,  $\Delta Q = I \times \Delta t$  and  $\Delta V = \Delta Q / C$ , we get

$$\frac{\Delta V}{\Delta t} = \frac{I}{C} \tag{9}$$

The time taken for a capacitor to charge from 0 to 63% of its rated voltage is called the capacitor time constant  $\tau$ . When R and C is the corresponding total resistance and capacitance of the charging circuit where  $V_S$  is the source voltage,  $\tau$  is equated as

$$\tau = R \times C \tag{10}$$

and the capacitor voltage during charging V<sub>C</sub> is derived as

$$V_C = V_S (1 - e^{-t/RC}) (11)$$

From this equation, the charge time  $t_r$  required for charging the capacitor to .99  $V_S$  is found to be  $t_r = 5$  RC.

The discharge characteristics of super capacitors are similar to the charging curves. The voltage of the capacitor  $V_C$  discharging through a resistor from an initial voltage of  $V_i$  follows the equation derived the same way as equation (11).

$$V_C = V_i(e^{-t/_{RC}}) \tag{12}$$

The discharge test was performed using a resistive load and not a constant current sink load. The load was a wire wound rheostat set at  $0.9\Omega$  to mimic a 200w load that draws 15A, which is the same as the current limit on the charger. The fully charged 81.25F SC module at 21.6V was discharged to 0V for the test.

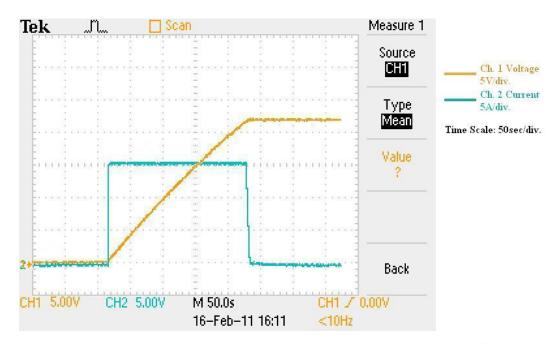

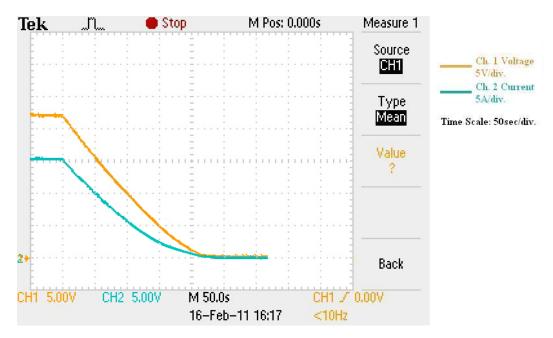

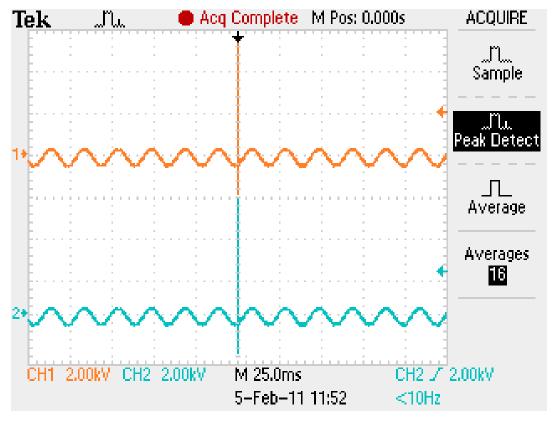

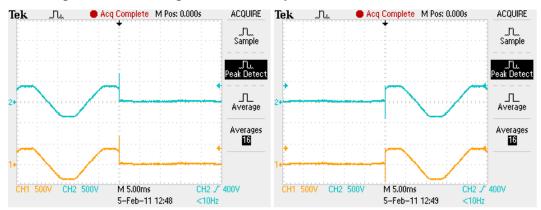

Shown below in Figures 2.8 and 2.9 are the oscilloscope screenshots for the charge and discharge tests.

Figure 2.8: Oscilloscope screenshot of constant current charging of SC bank

Figure 2.9: Oscilloscope screenshot of SC bank discharging through a resistive load

The tests conducted on the 21.6V / 81.25F super capacitor bank showed that constant current charging at from 0V to full rated voltage at 15A took ~210 seconds while discharging through a 200W resistive load from full rated voltage to 0V took ~215 seconds which are more or less similar.

# 2.1.6 VOLTAGE EQUALIZATION IN SERIES CONNECTED SUPER CAPACITORS

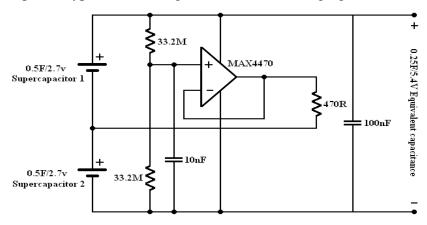

Many system applications require that capacitors be connected together, in series and/or parallel combinations, to form a "bank" with a specific voltage and capacitance rating as their voltage ratings are generally low. Because sustained over voltage can cause an SC to fail, the voltage across each cell in a series stack must not exceed the maximum continuous working voltage rating of individual cells in the stack. Provisions for either reducing the "rate of charge" being delivered to a cell, or to completely stop charging a cell whose voltage approaches its surge voltage rating should be made. The easiest way to reduce the current that is charging an SC cell is to divert some of it around the cell. One such method employs a passive bypass component. The other, more complicated procedure uses an active bypass circuit. After the stack has been held at a voltage for a period of time, voltage distribution becomes a function of internal parallel resistance. The cells with higher leakage current would have lower cell voltages, and vice versa in a series stack of SCs. One technique to compensate for variations in parallel resistance is to place a bypass resistor in parallel with each cell, sized to dominate the total cell leakage current. This effectively reduces the variation of equivalent parallel resistance between the cells. The active balancing circuit has an active switching device, like a bipolar transistor or a MOSFET, connected in series with each bypass element ladder. The switches are controlled by voltage-detection circuits that only turn a switch "on" when the voltage across that particular cell approaches a value just slightly below the continuous working voltage rating of the cell. This is called the bypass threshold voltage. Figure 2.10 depicts a typical block diagram of an active charging-current diversion circuit.

Figure 2.10: Active voltage balancing circuit for super capacitors (Cap-XX Limited, 2008)

#### 2.2 TRANSIENTS AND SURGES

The trend towards even smaller components and ever lower signal levels increases the susceptibility of electronic circuits to interference due to electrostatic disturbance. Electronic systems and circuits containing integrated circuits (IC) are sensitive to overvoltage transients such as ESD (electrostatic discharge) pulses. These pulses can enter an electrical device when the device port is touched or its connector is removed. Ports and connectors are probably the most common routes through which an ESD pulse can be introduced into a device. The pulse travels through the connector to the printed circuit board. It then propagates down the data and/or supply lines to the components on the board. Without sufficient protection, these components may become inoperable or even be destroyed.

Disturbances that electronic equipments have to be protected from can be broadly classified into three.

- Transients

- Noise and harmonics

- Voltage fluctuations

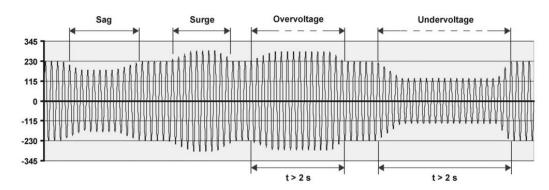

Voltage fluctuations mainly comprise of increase or decrease in the utility mains (root mean square) RMS voltage levels. They can be either momentary fluctuations that typically last from about 15 milliseconds to half a second in which case an over voltage is called a surge while an under voltage is called a sag, or if they last more than two seconds they are just referred to as over or under voltages. Under voltage situations cause brown-outs whereas a total power supply failure is termed a blackout.

Figure 2.11: Waveform representation of surge, sag, overvoltage and under voltage conditions

# Chapter 2: Background

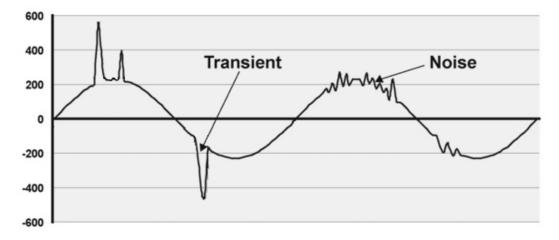

Noise disturbances may be caused by radio frequency interferences (RFI) or electro-magnetic interferences (EMI). These are high frequency elements in the order or kilohertz and megahertz at which conditions these are picked up by power lines, as transmission lines tend to act as antennas in this frequency spectrum. Noise usually is not critical is a strictly electrical sense, but can cause severe data malfunctions in electronic or magnetic data storage media.

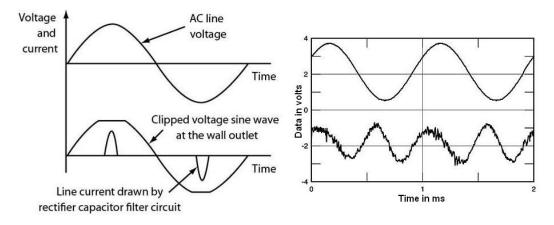

Figure 2.12: Waveform representation of transients and noise on a power line

Harmonics are currents or voltages with frequencies that are integer multiples of the fundamental power frequency. They are generally the result of operation of non-linear loads on the utility power by end users which draw current in a non-sinusoidal fashion from the power line. In such situations when there are distortions in the current and voltage waveforms, harmonics are injected back into the power line. Major causes of harmonic distortions are switched-mode power supplies using DC rectification and adjustable-speed drives. To counter this, standards and specifications laid out by authoritative agencies require active power factor correction in these systems so that current and voltage drawn are linearized with the intention that harmonic injection into the power line is kept to a minimum. Harmonics usually cause data corruption, false tripping of circuit breakers and general computer and telecom system down-times.

Figure 2.13: Harmonics generated non-linear loads

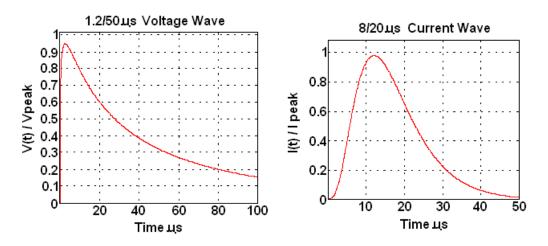

Transients are very sharp fluctuations that are formed in the power supply waveform. These have the appearance of spikes. Although there isn't an exact definition for a transient voltage surge (TVS), it can be considered a transient with voltage levels greater than 2000V and current levels greater than 100 ampere. It is not uncommon for the voltage levels to be 15kV to 20kV in amplitude and the current surge to exceed 2000Ampere. The IEEE and ANSI standards groups have defined two wave forms which are used to evaluate open circuit (voltage) and short circuit (current) transients. The voltage waveform is 1.2x50μsec, and the current waveform is 8x20μsec. These numbers indicate the rise time and duration of the waveform. Therefore, the rise time for the voltage waveform is 1.2μsec to the peak voltage and the duration to 50% of the wave form is 50μsec and for the current waveform the rise time to reach peak current is 8μsec and the time taken to reach 50% of the waveform is 20μsec.

Figure 2.14: Voltage and current surge waveforms

# Chapter 2: Background

Transient voltage surges are usually caused by:

- a) Switching of lighting and the starting and stopping of motors.

- b) Electrical fault conditions (equipment failure which passes high currents to ground or from phase to phase).

- c) Power failure and the subsequent return of power.

- d) Lightning strikes that hit the electrical system in your nearby geographical area.

- e) Lightning strikes that induce transients through radiation of electromagnetic fields (without hitting the electrical system).

Peak current for lightning strikes generally range from 2000 to 400,000 amps. The strongest strikes for three phase systems will induce currents of up to 320,000 amps per phase and up to 1,200,000 amps total.

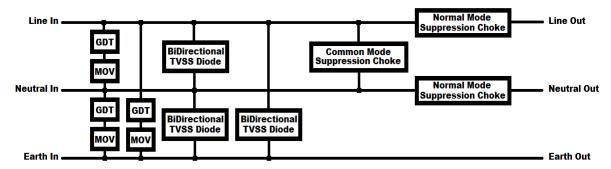

Typically used transient voltage surge suppression (TVSS) devices are gas discharge tubes (GDT), metal oxide varistors (MOV), silicon avalanche breakdown diodes or combinations of these devices in order to aid in protecting electrical equipment from power line surges.

Each of these TVSS elements has its own strengths and weaknesses:

- The GDT can handle very large voltage (~20kV) and current (~2500A) surges, but relatively speaking is slow (~1µsec) in responding to a transient surge.

- The MOV is very fast (~50nsec) responding, but has difficulties with large (~100Amp) currents which shorten the life cycle of the MOV.

- Silicon avalanche breakdown devices are fast (~1nsec) and can handle large (~1000Amp) currents, but are susceptible to dv/dt (instantaneous rate of change of voltage with time) and peak voltage failure modes.

- Other combinational products may use resistors, capacitors and/or SCRs in conjunction with these TVSS elements, which make them prone to the respective failure characteristics.

- Choke coils are inductors designed to block higher frequencies in an electrical transmission line. They use their property of self inductance to

attenuate electromagnetic interference and radio frequency interference from power supply lines

In some cases, MOVs and GDTs are connected in series or parallel as a single package that forms a device which has the speed of the MOV and the current handling capability of the GDT.

Manufacturers usually stack different types of clamping components across the power line in the hope that if one fails to clamp then the others might take over the clamping. Unfortunately, the device with the lowest clamping voltage will conduct all the current while the higher voltage devices will sit idle unless the lower voltage device blows out. This is why most surge protection units have low amperage fuses to blow out when such a situation arises.

Figure 2.15: Transient surge suppression devices

Given below are some of the criterions that should be taken into consideration while selecting a transient voltage surge suppression (TVSS) product:

- What Voltage levels of TVSS are expected?

- What Current levels of TVSS are expected?

- Will a high potential test need to be performed on the system?

- What type of life expectancy is required of the protection device?

- Does the system require other noise protection as well as TVSS?

The following are the major ratings used to describe TVSS devices:

Joules - indicates the amount of energy that the suppressor can dissipate. If

the incoming energy exceeds the suppressor's ability to dissipate, the

suppressor will be damaged and the excess energy will be passed to the

protected equipment.

- Peak Surge Current in Amperes maximum current allowed to pass without damage to the suppressor for a single standard test impulse. Surge currents exceeding that value will be passed to the protected equipment.

- Peak Let-Through Voltage The true effectiveness of a suppressor is given by the Let-Through Voltage rating, which is the maximum peak voltage of a transient that is allowed to pass on to the protected equipment by the suppressor. The rating gives the peak voltage that occurs within 100 microseconds following the application of a test impulse. It is the maximum voltage to which the protected equipment will be exposed due to the transient.

The Category B Impulse Test as defined by ANSI/IEEE C62.41 is the most widely used test standard for testing TVSS devices. It includes a 6000 volt, 3000 amp pulse which will rise to 90% of its peak voltage in 1.2 microseconds and will fall to 50% of peak in 20 microseconds.

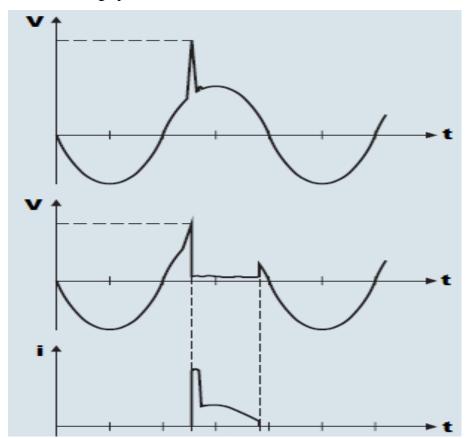

#### 2.2.1 PROPAGATION MODES FOR TRANSIENTS AND NOISE

Power line disturbances, namely transients and electrical noise can propagate through the power line as a super-imposition on the utility voltage. This happens in two modes, that is differential mode and common mode. Consider a three wire single phase AC mains utility line. The three wires consist of the two supply wires which are the line or live and the neutral; and the third wire which is the ground or earth. Any transient or noise appearing between the two supply lines, that is, when the wire-to-wire voltage is compromised, is termed normal mode or differential mode. A common mode transient occurs when the voltage differential appears between the ground and either of the two supply lines.

According to IEEE/ANSI Standard C62.41-1991, the worst normal mode surge expected inside a building is a 6,000V, 3,000A, 90 joule (J) combination wave. A normal mode surge is one that occurs between the hot (line) and neutral wires. This standard also states that the worst common mode surge — referred to in the standard as neutral-ground mode — is only found far from the service entrance and is a very weak 3,000V, 100A, 0.645J ring wave. This worst-case common-mode surge is already about nine times smaller than the suppressed surge left over

after typical suppression, also referred to as the let-through surge. Component audio and video systems are interconnected by cables that, for safety reasons, are often connected in some way to the electrical ground wire circuit. Their signals can be degraded by even mill volts of noise. On the other hand, computer systems may be able to tolerate several volts of noise on the ground system and continue to operate without problems

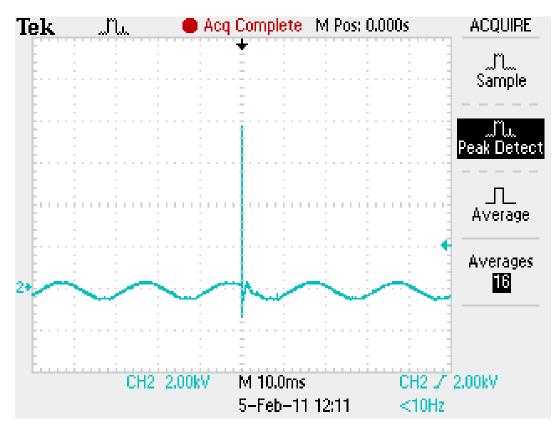

Most switch-mode power supplies, as used in most modern equipment, are inherently immune to common-mode surges and noise, due principally to the high-frequency transformers and filters used in these supplies. Hence, due to their relatively weak nature, common-mode surges do not deserve much attention and protection from differential or normal mode surges take higher priority. Surge protectors which have TVSS devices between live, neutral and ground divert energy to both neutral and ground, and will contaminate both the neutral and the ground wires. The safety ground is the same as the equipment chassis and system ground, and surges diverted to ground will allow energy to flow in chasses and cables that join interconnected equipment. Dumping surge energy onto the system ground instead of blocking and containing it can result in high-voltage energy travelling along interconnecting cables and causing permanent damage to input or output stages. Surge protectors which have TVSS devices only between live and neutral divert energy only to neutral and do not contaminate the ground wire, but they are also not effective at completely protecting equipment. Not having any shunt devices to ground, they allow live and neutral to float with respect to chassis ground up to dangerously high voltage levels during a surge event. In technical terms they convert normal mode surges to common-mode surges. Common-mode surges are normally only found at low, harmless levels on branch circuits, but when generated by such a piece of equipment they can be large and damaging. Common-mode filters often have capacitors from live and neutral to ground and these capacitors will be blown out by the large common-mode surges that are generated in these situations. Figures 2.19 and 2.20 shows oscilloscope screenshots of differential mode and common mode surges.

Figure 2.19: 6.8KV differential-mode surge measured between Line and Neutral wires

Figure 2.20: 6KV common-mode surge measured between Line/Neutral wires with respect to Ground wire

#### 2.2.2 TRANSIENT IMMUNITY STANDARDS

Both IEC 1000-4-5: 1995 "Surge Immunity Test" and IEEE C62.41-1991 "IEEE Recommended Practice on Surge Voltages in Low-Voltage AC Power Circuits" define a "1.2/50μs - 8/20μs combination wave" surge which has a 1.2μs voltage rise time with a 50μs decay across an open circuit. The specified current waveform has an 8μs rise time with 20μs decay into a short circuit. Open circuit voltages levels from 1 to 6kV are commonly used in both the positive and negative polarities, although, under some circumstances, voltages as high as 20kV may be applied.

The InternationalElectrotechnical Commission (IEC), a worldwide organization promoting international cooperation on questions concerning standardization in electrical & electronic fields, has developed transient immunity standards which have become minimum requirements for manufacturers. Three of the IEC standards that deal with transient immunity are:

- IEC 61000-4-2 : Electrostatic Discharge (ESD)

- IEC 61000-4-4 : Electrical Fast Transient/Burst (EFT)

- IEC 61000-4-5 : Surge Immunity

# 2.2.2.1 IEC 61000-4-2: ELECTROSTATIC DISCHARGE (ESD) STANDARD

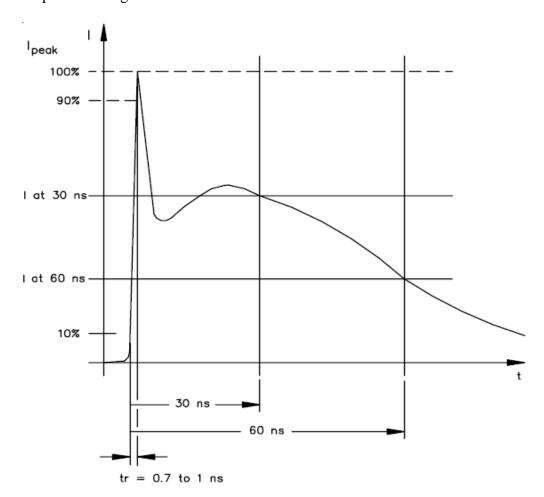

IEC 61000-4-2 addresses one of the most common forms of transients in electronic systems; electrostatic discharge (ESD). ESD results from conditions which allow the build up of electrical charge from contact and separation of two non-conductive materials. When the charged body is brought in proximity of another object of lower potential, energy is released in the form of electrostatic discharge. The standard defines immunity requirements for ESD which can be coupled into the equipment directly or through radiation. IEC 61000-4-2 also specifies the ESD current waveform and parameters shown in Figure 2.18. The rise time is extremely fast, defined as 0.7 to 1ns, with a second peak at 30ns and a total duration of only 60ns. The total energy contained within the pulse is approximately a few hundred micro joules.

Figure 2.18: ESD Waveform

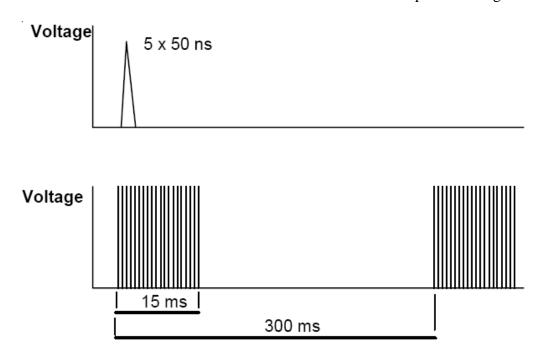

# 2.2.2.2 IEC 61000-4-4: ELECTRICAL FAST TRANSIENT/BURST (EFT) STANDARD

Electrical fast transients occur as a result of arcing contacts in switches and relays. **EFT** disturbances are in industrial environments where common electromechanical switches are used to connect and disconnect inductive loads. IEC 61000-4-4 specifies the EFT threat in both power and data lines. The electrical fast transient is described in terms of a voltage across a  $50\Omega$  load from a generator having a nominal dynamic source impedance of  $50\Omega$ . The output occurs as a burst of high voltage spikes at a repetition rate ranging from 2 KHz to 5 KHz. The burst length is defined as 15ms with bursts repeated every 300ms. Each individual burst pulse is a double exponential waveform with a rise time of 5ns and a total duration of 50ns. A diagram showing the EFT waveform and the EFT burst repetition rate and burst period is shown in Figure 2.19.

Figure 2.19: EFT burst waveform, repetition rate and burst period

### 2.2.2.3 IEC 61000-4-5: SURGE STANDARD

IEC 61000-4-5 addresses the most severe transient conditions on both power and data lines. These are transients caused by lightning strikes and switching. Switching transients may be the result of power system switching, load changes in power distribution systems, or short circuit fault conditions. Lightning transients may result from a direct strike or induced voltages and currents due to an indirect strike. The IEC 61000-4-5 standard defines a transient entry point and a set of installation conditions. The transient is defined in terms of a generator producing a given waveform and having specified open circuit voltage and source impedance. Two surge waveforms are specified: the 1.2x50μs open-circuit voltage waveform and the 8x20μs short-circuit current waveform; Figures2.20 and 2.21 respectively.

Figure 2.20: IEC 61000-4-5 Voltage impulse waveform

Figure 2.21: IEC 61000-4-5 current impulse waveform

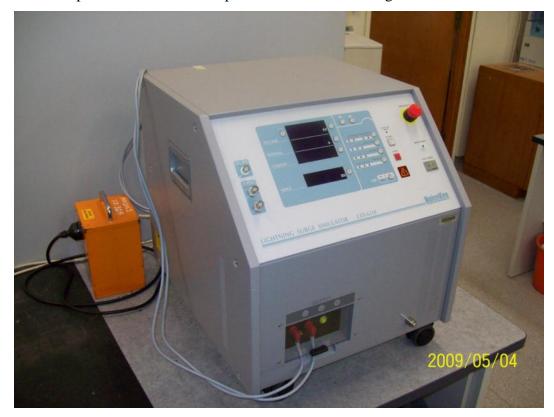

# 2.2.3 Lightning Surge Simulator

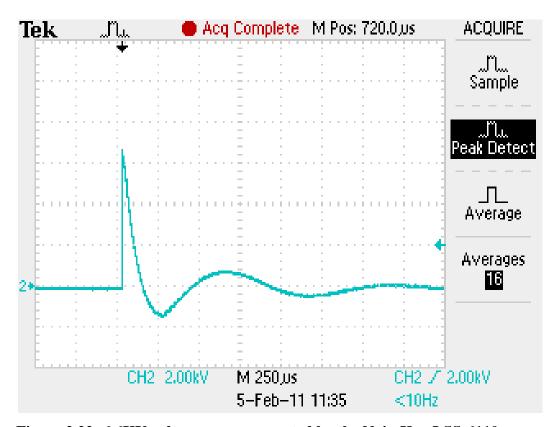

A lightning surge simulator or LSS is used to test the surge resistance capabilities of electronic and electric circuits and components. It is basically a high voltage pulse generator that can produce high current and voltage surges which correspond to stipulations specified by the IEC/IEEE surge testing and measurement strategies. The LSS used for testing purposes in this research project

is the NoiseKen LSS-6110 that is capable of generating voltage-current combination wave surges as specified in the IEC6100-4-5 standards. Figure 2.22 shows the oscilloscope screenshot of the 6.6KV voltage surge waveform used in carrying out the surge tests.

Figure 2.22: 6.6KV voltage surge generated by the NoiseKen LSS-6110

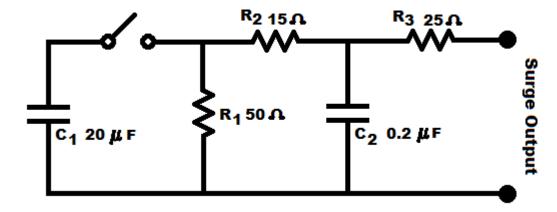

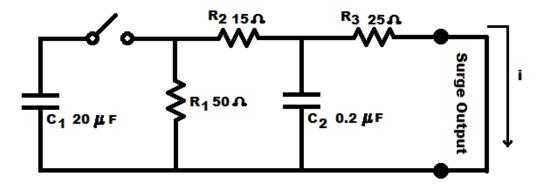

Figure 2.23 gives a basic understanding into the surge generator circuit that is employed inside an LSS.

Figure 2.23: Basic surge generator circuit

# Chapter 2: Background

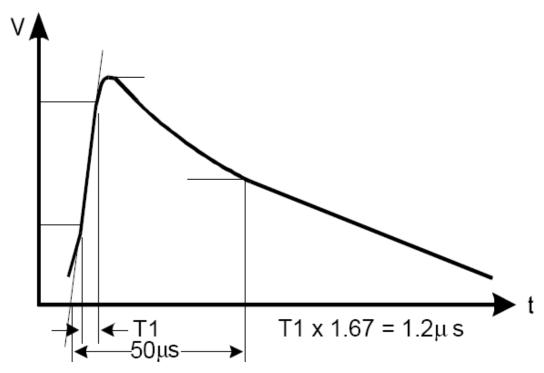

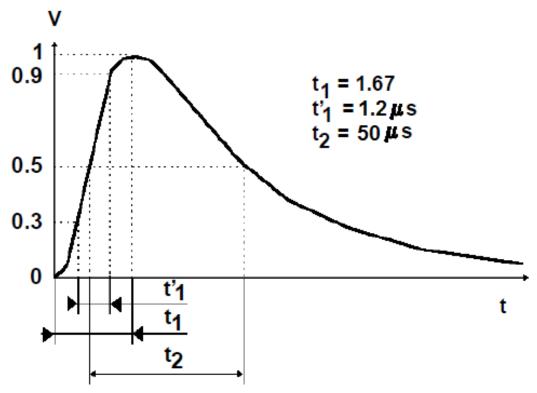

The surge generator can generate a high voltage surge when it is in open circuit Figure 2.24 shows the parameters of the 12/50µs voltage surge generated by the surge generation circuit when configured in open circuit mode.

Figure 2.24: Voltage surge waveform parameters

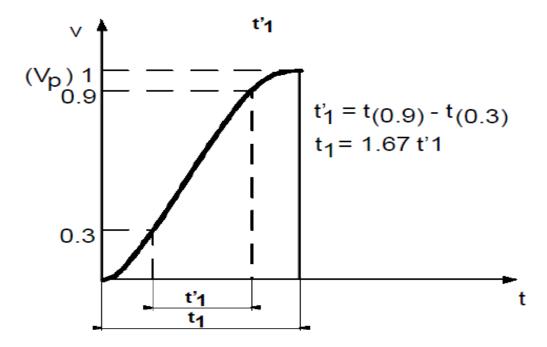

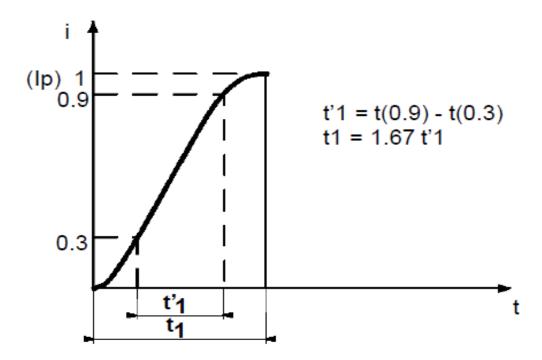

The equation for the rise time of the voltage surge waveform is as follows:

$$v(t) = V_p (1 - \exp(-t/T))$$

=> t = - T log n (1 - (v(t)/V\_p)) (13)

In this case the time constant T is essentially due to  $R_2$  and  $C_2$  and hence T may be estimated as :

$$T = R_2 * C_2$$

So  $t_{(0.3)}$  and  $t_{(0.9)}$  will be calculated respectively with  $v(t)/V_p$ =0.3 and  $v(t)/V_p$ = 0.9 where  $t_{(0.3)}$  = 0.1  $\mu$ s  $t_{(0.9)}$  = 0.8  $\mu$ s and so

$$t_1 = 1.67 \ (t_{(0.9)} \text{ - } t_{(0.3)})$$

$$t_1\!=1.169\mu s\approx\!1.2\mu s$$

Figure 2.25: Rise time parameters for voltage surge waveform

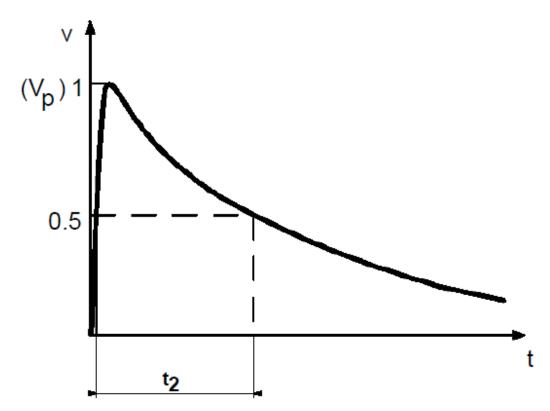

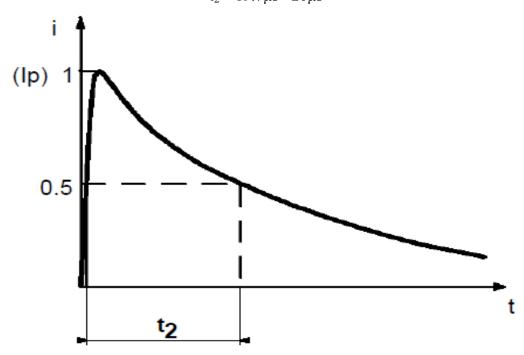

The equation for the voltage surge duration curve can be represented as

$$v(t) = V_p \exp(-t/T)$$

$$=> t = -T\log n (v(t)/V_p)$$

(14)

In this case the time constant T is essentially due to  $R_1$  and  $C_1$  and hence T may be estimated as :

$$T = R_1 * C_1$$

So  $t_2$  will be calculated with  $v(t)/V_p=0.5$  and so

$$t_2 = 49.3 \mu s \approx 50 \mu s$$

Figure 2.26: Current surge duration waveform

The surge generator can generate a high current surge when its output is short circuited as shown in Figure 2.27.

Figure 2.27: Surge generator circuit in short circuit mode for current surge

Figure 2.28 shows the parameters of the  $8/20\mu s$  voltage surge generated by the surge generation circuit when configured in short circuit mode.

Figure 2.28: Voltage surge waveform parameters

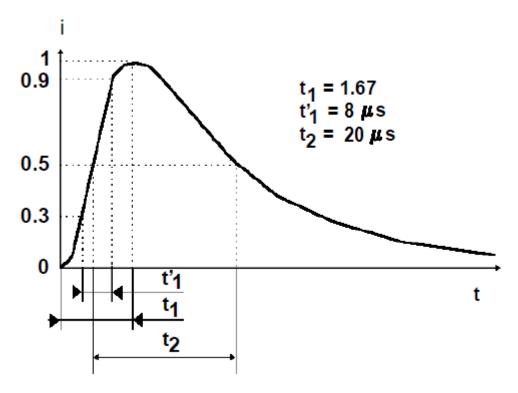

The equation for the rise time of the current surge waveform is same as Equation (13). But in this case the time constant T must take into account the presence of  $R_3$  along with  $R_2$  and  $C_2$  and hence T may be estimated as:

$$T = (R_2 * R_3 / (R_2 + R_3)) * C_2$$

(15)

So  $t_{(0.3)}$  and  $t_{(0.9)}$  will be calculated respectively with  $v(t)/V_p$ =0.3 and  $v(t)/V_p$ = 0.9 where  $t_{(0.3)}$  = 0.57  $\mu$ s  $t_{(0.9)}$  = 5.3  $\mu$ s and so

$$t_1 = 1.67 \ (t_{(0.9)} - t_{(0.3)})$$

$$t_1 = 7.899 \mu s \approx 8 \mu s$$

Figure 2.29: Rise time parameters for current surge waveform

The equation for the current surge duration curve is same as equation (14), but the time constant T is now due to  $C_1$  with  $R_1$  in parallel with  $R_2$  and  $R_3$ and hence T may be estimated as :

$$T = (R_1(R_2 + R_3) / (R_1 + R_2 + R_3) * C_1$$

(16)

So  $t_2$  will be calculated with  $v(t)/V_p=0.5$  and so

$$t_2 = 19.7 \mu s \approx 20 \mu s$$

Figure 2.30: Current surge duration waveform

# Chapter 3

Theoretical Synopsis of the Design Approach

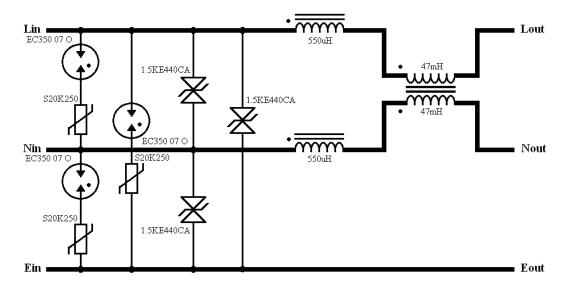

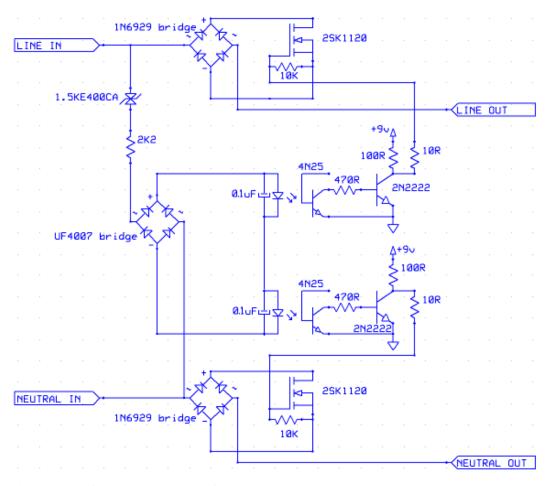

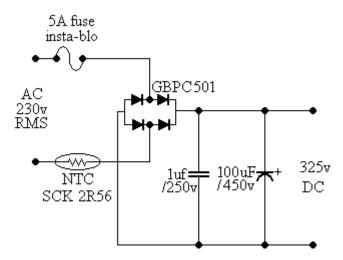

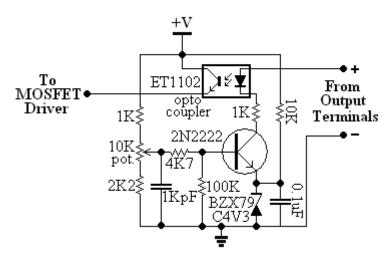

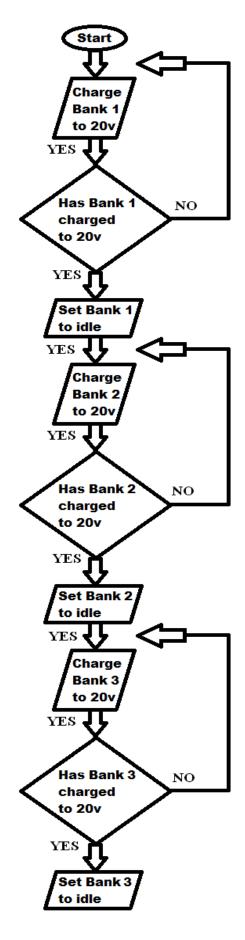

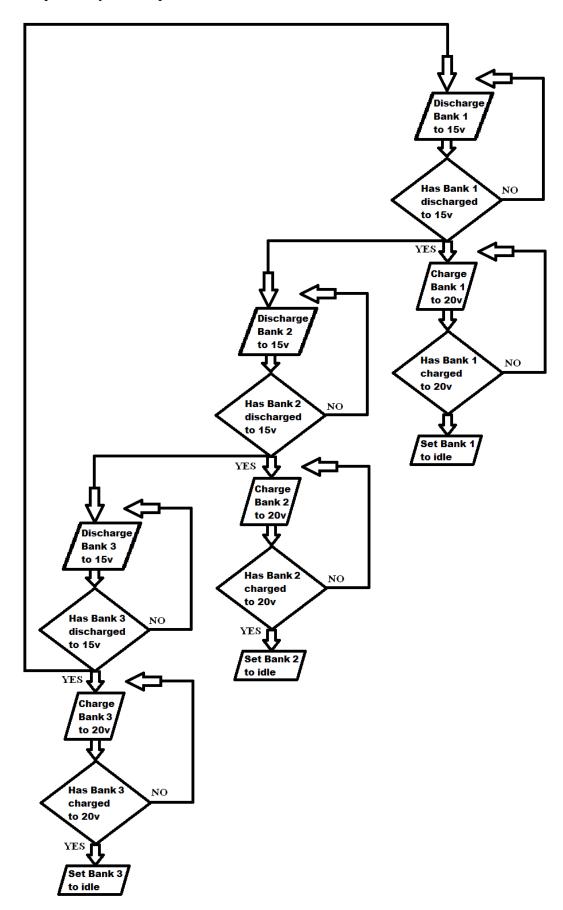

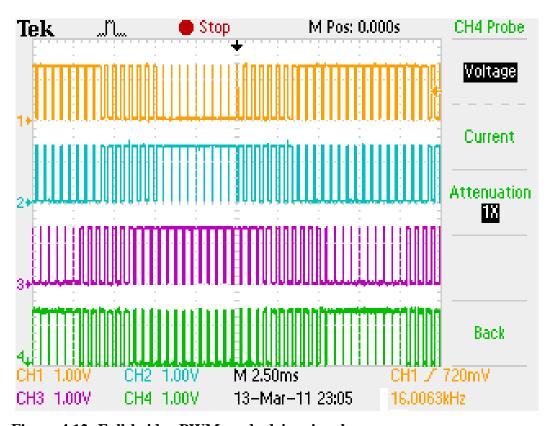

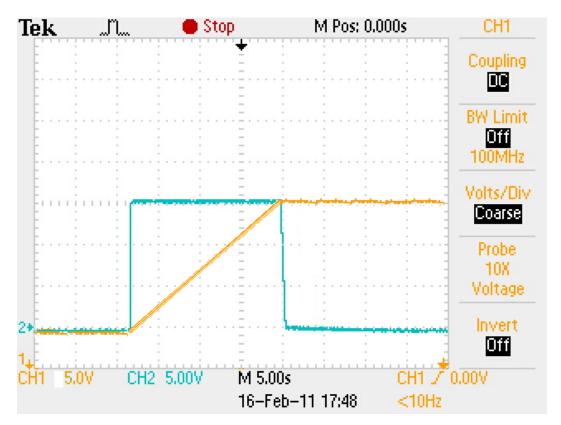

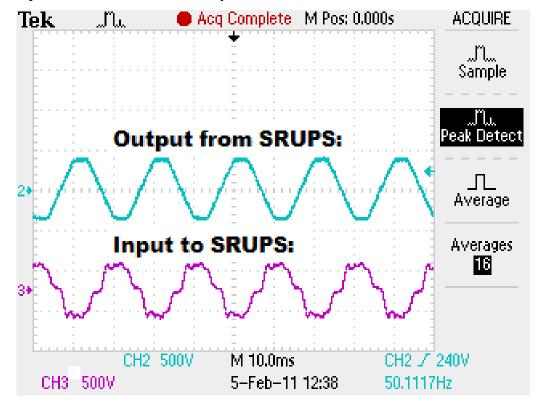

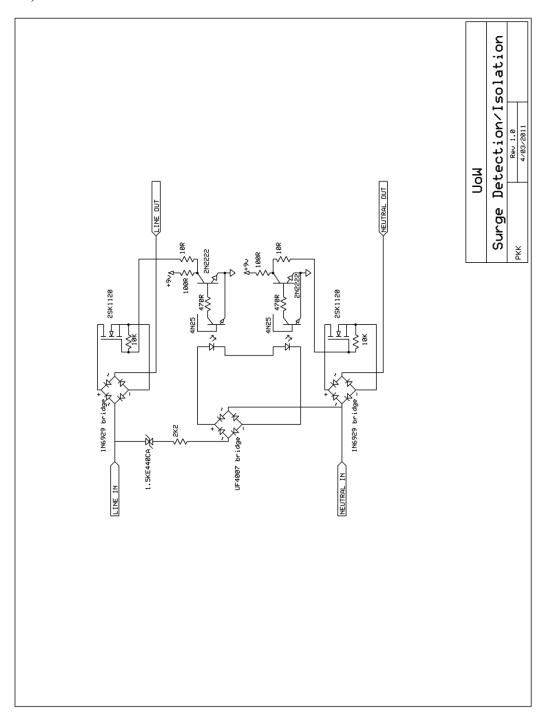

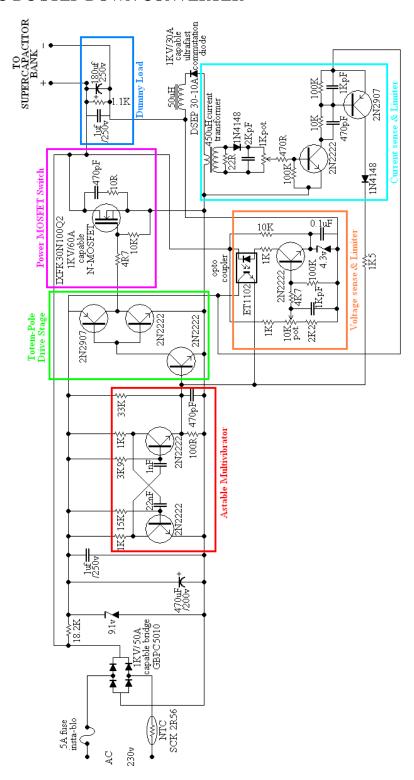

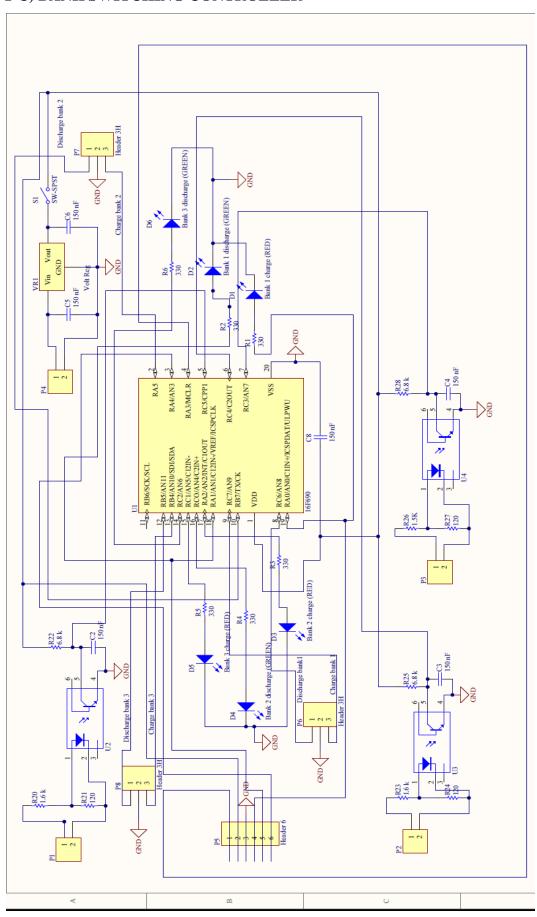

### 3.1 BASIC SURGE PROTECTION BLOCK