#### http://waikato.researchgateway.ac.nz/

#### **Research Commons at the University of Waikato**

#### **Copyright Statement:**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of the thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# High power linear AC Electronic Load for testing UPS Systems

A thesis submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF ENGINEERING

at

The University of Waikato

Hamilton, New Zealand

By

M.D.C.S.K.Jinadasa

To

My Loving Amma and Thaththa

# **Abstract**

Concept of a series bipolar transistor array for AC power control is already developed. However non-linearity issues, high power capability with load sharing at high voltages and digital control with better transient performance were not adequately adopted in early-developed stages.

This thesis is a description of the design approach of digitally controllable linear 230V/50 Hz AC line voltage capable electronic load with predictable characteristics based on spice simulation. The BJT array used in this project provides high power dissipation capability and uniform voltage and power distribution across the individual transistors. A set of optoisolators are used to have electrical isolation between power stage and digital control circuits. A Zilog Z8Encore! 64K series development kit is used in controlling the circuit.

# Acknowledgements

First and foremost I would like to place on record my deep gratitude to those who encouraged me in this difficult task of preparing the thesis. Especially to my mother and my sister who pray for me and encourage me at very difficult situations during this period.

Mr. Nihal Kularathne was my supervisor for this research and I am really grateful for his guidance, encouragement and for the motivation throughout the whole period. It was a grate honour for me to have had the chance to work with him. I certainly could not have come this far without his assistance.

My thanks go to several technical staff members for their enormous support given to me at all times. Thanks to Michel Crosgrove for his generous support in finding me equipment, purchasing electronic components and making PCB's. Stuart Finlay was always concerned about my safety as I was handling high voltages for this research. Thanks to Stuart Finlay for his valuable advice and supplying me an isolation transformer and safety switches.

When I was struggling with programming microcontrollers at the latter part of my research, a friend Terry Cavo taught me to overcome the situation. I am grateful to Terry for his massive effort. I am also grateful to my sincere friends Tissa Senanayake and Mahima Senanayake for giving me their full support in finding the equation for the data obtained.

I had to learn C programming for this research and Daniel Ho helped me in obtaining valuable books to learn the essentials. Thanks to Daniel Ho for the great support and

useful hints. I would also like to thank Richard Conrey for his discussions and helpful comments to make my project success.

While writing this thesis, my sincere friends Uma Paranawidana and Ruwan Paranawidana have given me a big hand in several ways. Thanks to Uma and Ruwan for their unforgettable assistance on this daunting task. I would also like to thank Heidi Eschmann for helping in photocopying and scanning of documents.

My family has put up with a lot in the past eighteen months and their support has never been forgotten. Thanks to my husband Galinda and my little son Rowin for your patience, support and encouragement.

M.D.C.S.K. Jinadasa

University of Waikato Hamilton, New Zealand November 2007

# **Table of Contents**

#### **List of Tables**

#### **List of Figures**

1. Introduction

|   | 1.1 | Background                                    | 1  |

|---|-----|-----------------------------------------------|----|

|   | 1.2 | Electronic Loads                              | 1  |

|   | 1.3 | Testing of Power Supplies                     | 5  |

|   |     | 1.3.1 Testing of DC power supplies            | 6  |

|   |     | 1.3.2 Testing of AC power systems             | 8  |

|   | 1.4 | Requirements                                  |    |

|   |     | 1.4.1 Linearity                               | 11 |

|   |     | 1.4.2 Reliability                             | 13 |

|   |     | 1.4.3 Economy                                 | 13 |

|   |     | 1.4.4 Stability                               | 14 |

|   |     | 1.4.5 Reproducibility                         | 14 |

|   | 1.6 | Research Objectives/ Specifications           | 14 |

|   | 1.7 | System Overview                               | 15 |

|   | 1.8 | Thesis Outline                                | 17 |

|   |     |                                               |    |

| 2 | Ba  | ckground and Related Work                     |    |

|   | 2.1 | Background work and literature survey         | 19 |

|   | 2.2 | Power Transistor options for electronic loads | 19 |

|   |     | 2.2.1 Bipolar junction Transistors            | 20 |

|   |     |                                               |    |

|   |     | 2.2.2   | Metal Oxide F     | ield Effect Transistors (MOSFET)                            | 20 |

|---|-----|---------|-------------------|-------------------------------------------------------------|----|

|   |     | 2.2.3   | Insulated Gate    | Bipolar Transistors (IGBT)                                  | 21 |

|   | 2.3 | Use o   | of Darlington pa  | ir                                                          | 21 |

|   |     | 2.3.1   | Large signal m    | odels of BJT in the forward active region                   | 22 |

|   | 2.4 | Need    | for a series con  | nected array                                                | 26 |

|   | 2.5 | Elect   | rical Isolation   |                                                             | 27 |

|   |     | 2.5.1   | Optical isolation | on                                                          | 28 |

|   | 2.6 | Sa      | mpling Circuit .  |                                                             | 29 |

| 3 | Po  | wer S   | tage –A Theor     | etical overview of design approach                          |    |

|   | 3.1 | Over    | view of the Syst  | em                                                          | 31 |

|   | 3.2 | Recti   | fication          |                                                             | 32 |

|   | 3.3 | Trans   | istor Array Des   | ign                                                         | 33 |

|   |     | 3.3.1   | Concept           |                                                             | 33 |

|   |     | 3.3.2   | Application of    | f the concept to multiple transistors in a series           |    |

|   |     |         | connected arra    | ny                                                          | 35 |

|   | 3.4 | Conti   | ollability advan  | tages of the proposed Technique                             | 42 |

|   | 3.5 | Assu    | mptions and the   | ir effects                                                  | 42 |

|   | 3.6 | Theo    | retical approach  | to correcting the non linear nature of the transistor array | 44 |

| 4 | Sp  | ice Sir | nulation          |                                                             |    |

|   | 4.1 | Simu    | lation Circuits . |                                                             | 45 |

|   | 4.2 | Simu    | lation Results    |                                                             | 47 |

|   | 4.3 | Probl   | ems encountere    | d                                                           | 49 |

| 5 | Ap  | proacl  | n to digital con  | ntrol and of the transistor array                           |    |

|   | 5.1 | Micro   | oprocessor Deve   | elopment System                                             | 51 |

|   |     | 5.2 A   | Analog to Digita  | l Converter                                                 | 53 |

|   |     |         | 5.2.1 ADC ref     | erence Voltage                                              | 55 |

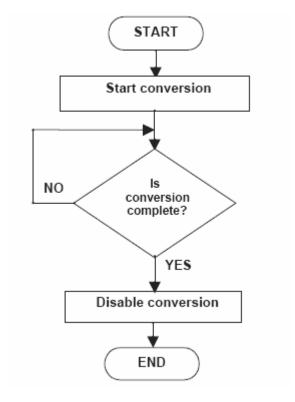

|   |     |         | 5.2.2 Operation   | n                                                           | 56 |

|   |     |         | 5.2.2.1           | Automatic power down                                        | 56 |

|   |     |         | 5222              | Modes of operation                                          | 56 |

|   |     | 5.2.2.2.1 Single shot conversion                                             | 56 |

|---|-----|------------------------------------------------------------------------------|----|

|   |     | 5.2.2.2.2 Continuous conversion                                              | 56 |

|   | 5.3 | Digital to Analog Converter                                                  | 57 |

|   | 5.4 | Digital Control overview                                                     | 59 |

|   | 5.5 | Signal Scaling                                                               | 60 |

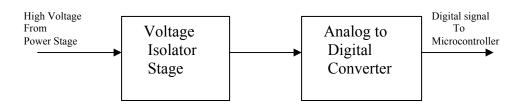

|   | 5.6 | Voltage Sampler                                                              | 62 |

| 6 | Imp | plementation                                                                 |    |

|   | 6.1 | Selection of components                                                      | 63 |

|   |     | 6.1.1 Diode selection                                                        | 63 |

|   |     | 6.1.2 Choice of bipolar junction power transistors                           | 64 |

|   |     | 6.1.2.1 High power BJT transistor                                            | 64 |

|   |     | 6.1.2.2 Medium power transistor                                              | 66 |

|   |     | 6.1.2.3 Selection of optocoupler                                             | 68 |

|   | 6.2 | Heat Sink Design                                                             | 70 |

|   |     | 6.2.1 Calculation and selection of heat sink                                 | 71 |

|   | 6.3 | Implementation of power Stage                                                | 71 |

|   | 6.4 | Digital Control                                                              | 73 |

|   |     | 6.4.1 Observations and measurements on the behavior of the array without the |    |

|   |     | digital control.                                                             | 73 |

|   |     | 6.4.2 Mathematical Approach                                                  | 76 |

|   | 6.5 | Digital Control algorithm                                                    | 83 |

|   | 6.6 | Program Code                                                                 | 85 |

| 7 | Re  | esults                                                                       |    |

|   | 7.1 | 1 Variables m and C                                                          | 89 |

|   | 7.2 | 2 Oscilloscope captures                                                      | 92 |

|   |     | 7.2.1 At bridge points                                                       | 92 |

|   |     | 7.2.2 Voltage waveform of the load                                           | 93 |

|   |     | 7.2.2.1 Voltage waveform of the load                                         | 93 |

|   |     | 7.2.2.2 Current waveform of the load                                         | 93 |

|   | 7.3 | 3 Fast Fourier transformers                                                  | 94 |

|    | 7.4 Total Harmonic Distortions |                                                          |     |  |  |

|----|--------------------------------|----------------------------------------------------------|-----|--|--|

|    |                                | 7.4.1 THD of the load current with constant load voltage | 95  |  |  |

|    |                                | 7.4.2 THD of the load voltage with constant load current | 98  |  |  |

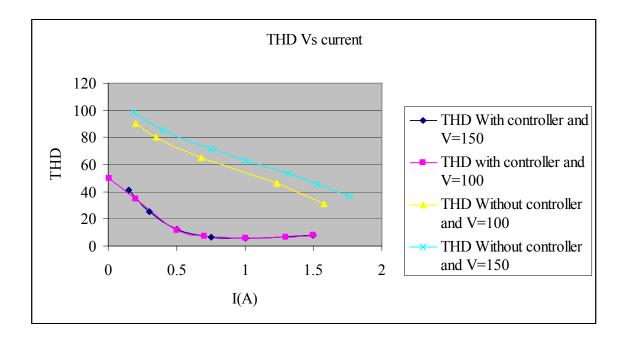

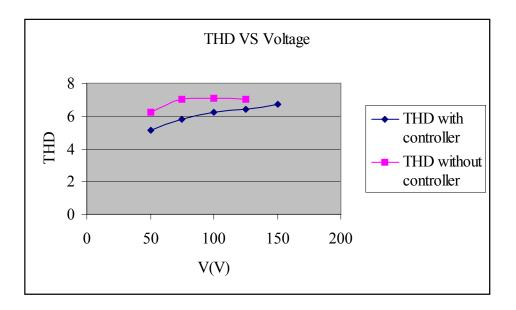

|    | 7.5                            | Variation of THD with voltage and current                | 100 |  |  |

|    |                                | 7.5.1 THD Vs Load current at different voltage levels    | 100 |  |  |

|    |                                | 7.5.2 THD Vs Load voltage at different voltage levels    | 101 |  |  |

| 8  | Cor                            | nclusion and Future Developments                         |     |  |  |

|    | 8.1                            | Summary of the Thesis                                    | 103 |  |  |

|    | 8.2                            | Conclusion                                               | 103 |  |  |

|    | 8.3                            | Future Developments                                      | 104 |  |  |

| Re | feren                          | ces                                                      | 105 |  |  |

| Ap | pendi                          | ix A                                                     |     |  |  |

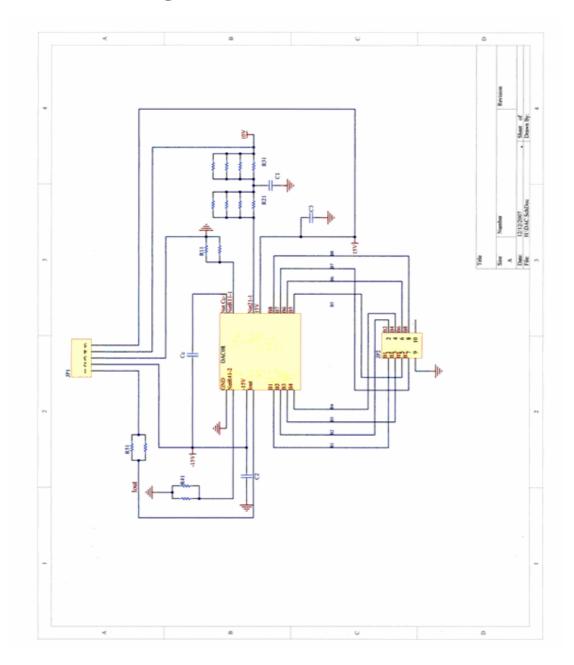

| A  | Circu                          | it diagrams                                              | 109 |  |  |

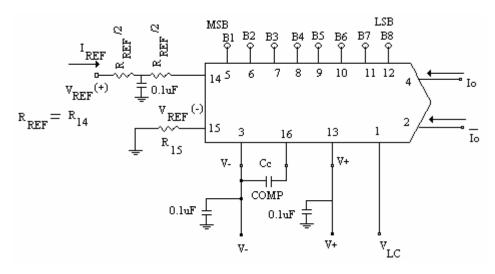

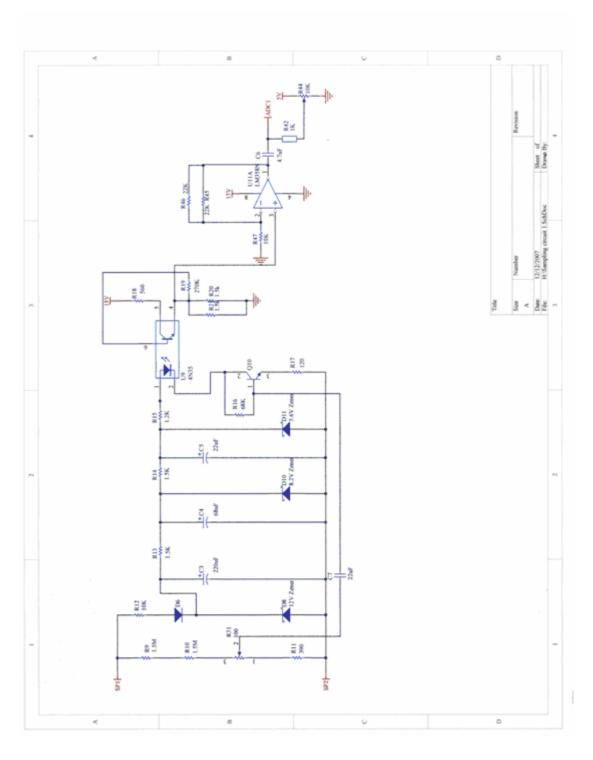

|    | <b>A.</b> 1                    | Circuit diagram of DAC circuit.                          | 109 |  |  |

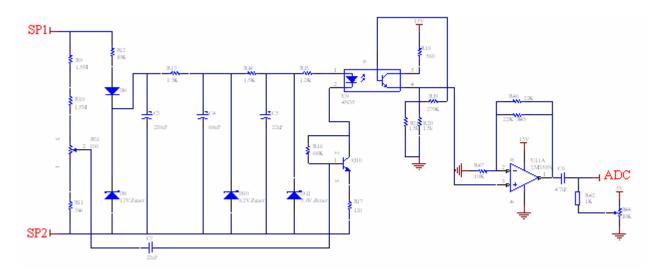

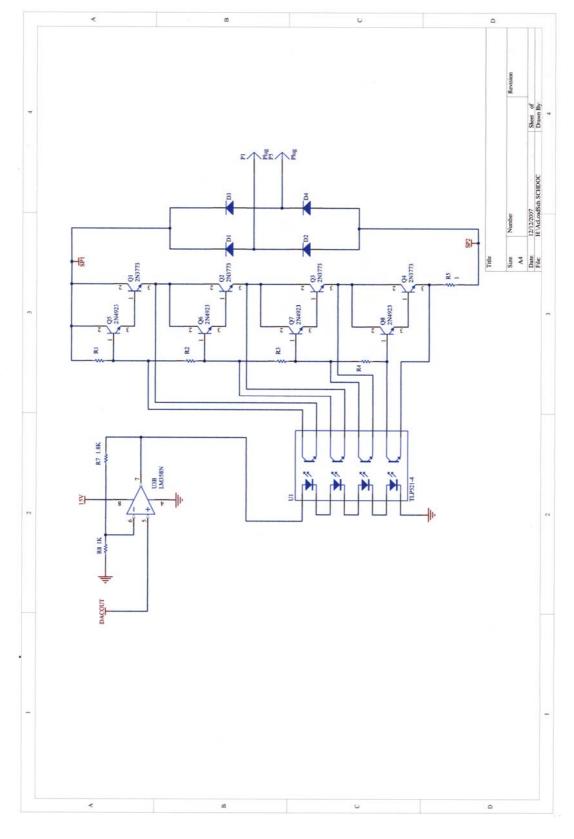

|    | A.2                            | Circuit diagram of Voltage sampling circuit.             | 110 |  |  |

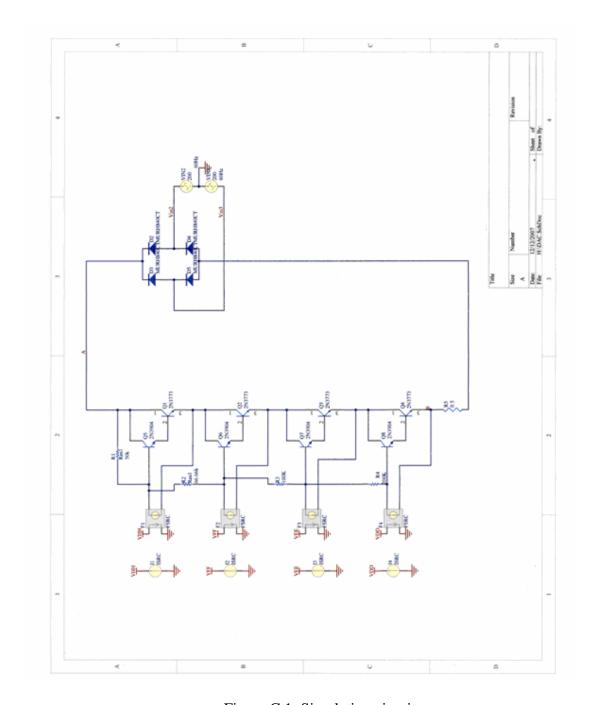

|    | A.3                            | Circuit diagram of the power stage.                      | 111 |  |  |

| Ap | pendi                          | ix B                                                     |     |  |  |

| В  | Phot                           | ograph of Circuits and test bench                        | 113 |  |  |

| Ap | pendi                          | ix C                                                     |     |  |  |

| C  | Simu                           | lation Circuit                                           | 117 |  |  |

|    | C.1                            | Simulation Circuit                                       | 118 |  |  |

|    | C.2                            | Simulation Models of Components                          | 119 |  |  |

|    |                                | C.2.1 Model of bipolar junction 2N3773 power transistor  | 119 |  |  |

|    |                                | C.2.2 Model of bipolar junction 2N3904 power transistor  | 120 |  |  |

|    |                                | C.2.3 Model of Rectifier diode BYT08P                    | 120 |  |  |

| Ap | pendi                          | ix D                                                     |     |  |  |

| D  | Sampl                          | e of simulation data in Excel                            | 121 |  |  |

# **List Of Tables**

| 1.1: Different AC and DC loads                          | 4  |

|---------------------------------------------------------|----|

| 7.1: Required m and C value at constant voltage of 100V | 91 |

| 7.2: Required m and C value at constant voltage of 150V | 91 |

| 7.3: Required m and C value at constant voltage of 100V | 92 |

# **List of Figures**

| 1.1 | Load transient recovery time                                                  | 6    |

|-----|-------------------------------------------------------------------------------|------|

| 1.2 | Load effect                                                                   | 6    |

| 1.3 | Typical Operating Characteristics of Three Types of Current                   |      |

|     | Limiting Power Supplies.                                                      | 7    |

| 1.4 | Voltage and current wave forms of a linear load                               | 12   |

| 1.5 | Voltage and current wave forms of an AC Electronic load                       | 12   |

| 1.6 | Complete block diagram of the AC Electronic load design                       | 16   |

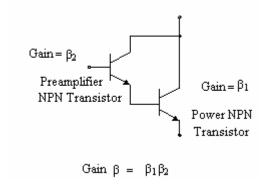

| 2.1 | Darlington pair                                                               | 22   |

| 2.2 | Current flow in an npn transistor biased to operate in the active mode        | 22   |

| 2.3 | Profiles of minority carrier concentrations in the base and the emitter of an |      |

|     | npn transistor operating in the active mode                                   | 23   |

| 2.4 | Output Characteristics of a power bipolar transistor                          | 25   |

| 2.5 | Transistor array                                                              | 26   |

| 2.6 | Basic blocks of sampling Circuit                                              | 29   |

| 3.1 | Basic Circuit blocks of the AC electronic load                                | 32   |

| 3.2 | Practical rectified output at bridge points of the array                      | 32   |

| 3.3 | Concept for variable resistance                                               | 33   |

| 3.4 | Base current diversion using an opto coupler                                  | 35   |

| 3.5 | Series connected configuration of transistor array                            | 36   |

| 3.6 | Use of Darlington pair                                                        | 40   |

| 3.7 | $I_{C}$ versus $V_{BE}$ of power transistor configured as a Darlington pair   | 40   |

| 3.8 | Transistor array                                                              | 42   |

| 3.9 | Current transfer ratio Vs forward current                                     | . 43 |

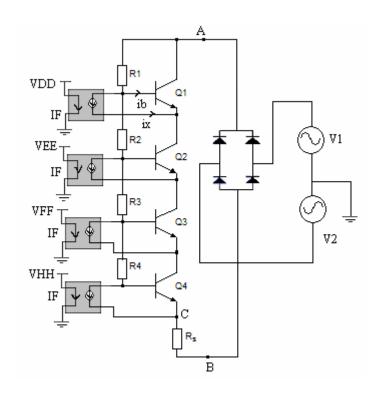

| 4.1 | Transistor array                                                              | . 46 |

| 4.2 | Simplified circuit used in Spice simulation.                                  | 46   |

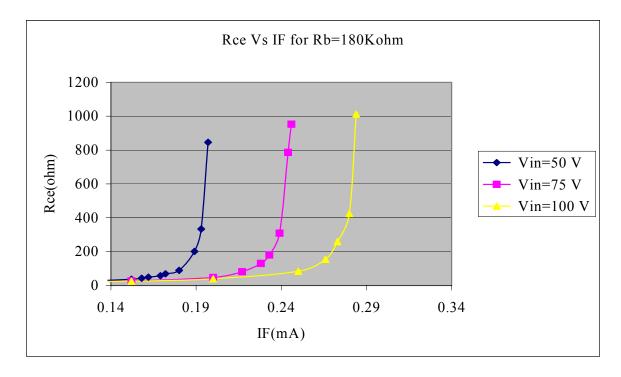

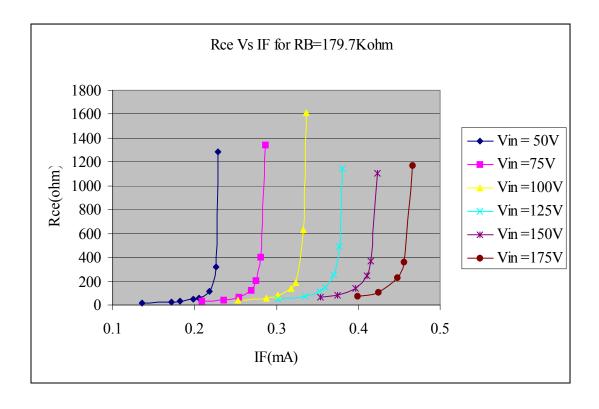

| 4.3  | Variation of resistance with diode current when $R_B$ =180K $\Omega$       | 47 |

|------|----------------------------------------------------------------------------|----|

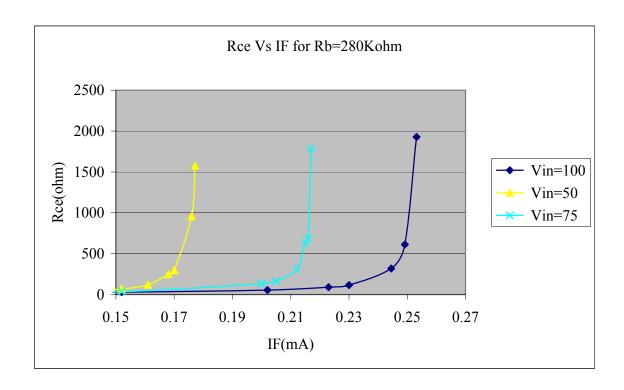

| 4.4  | Variation of resistance with diode current when $R_B = 280 \text{K}\Omega$ | 47 |

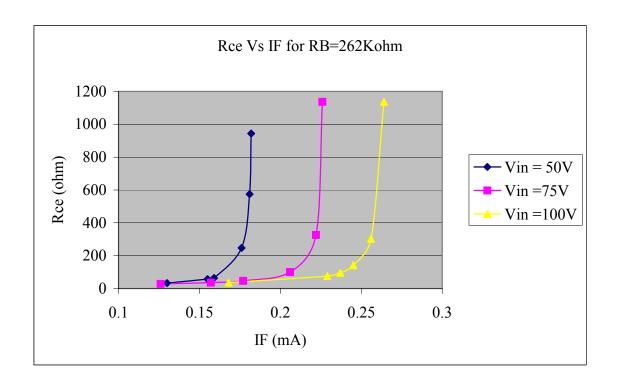

| 4.5  | Variation of resistance with diode current when $R_B = 262 \text{K}\Omega$ | 48 |

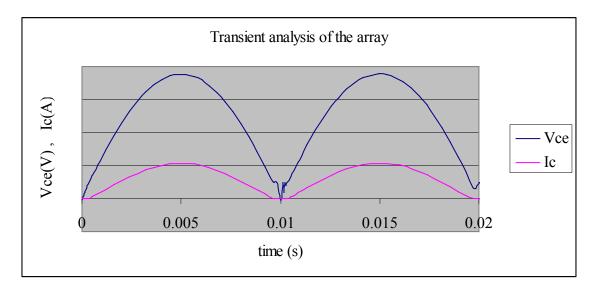

| 4.6  | AC behavior showing the bridge output of the array using transient         |    |

|      | analysis of PSpice simulation.                                             | 49 |

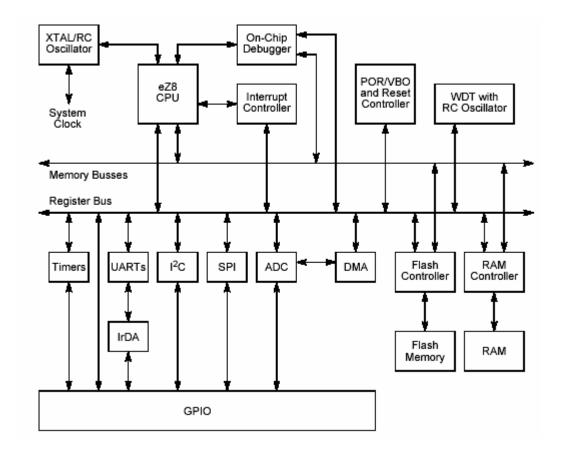

| 5.1  | Z8 Encore! 64K Series block diagram.                                       | 52 |

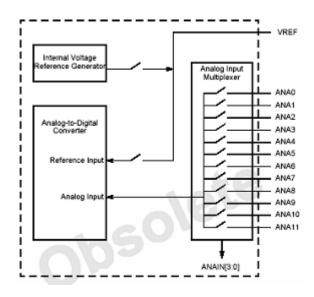

| 5.2  | Analog to Digital Converter Block Diagram                                  | 53 |

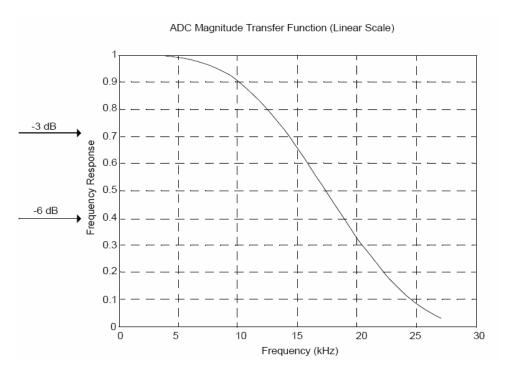

| 5.3  | Analog to Digital Converter frequency response                             | 55 |

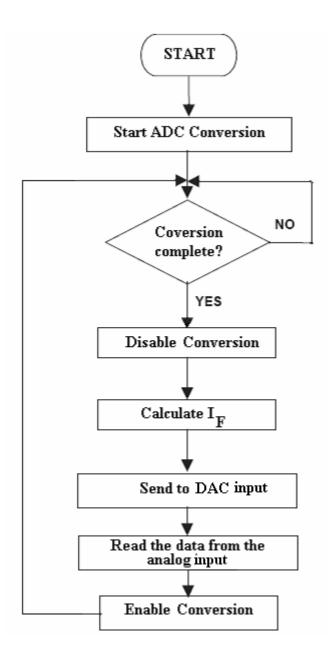

| 5.4  | ADC flow chart                                                             | 57 |

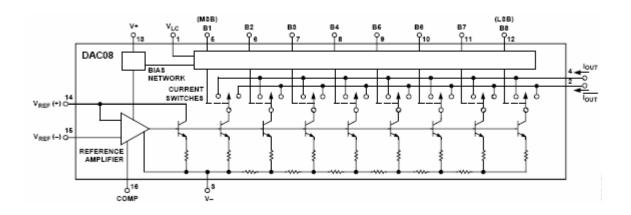

| 5.5  | Functional block diagram of DAC08                                          | 58 |

| 5.6  | DAC 08 Circuit configuration                                               | 58 |

| 5.7  | Basic Unipolar operation output currents of the DAC08                      | 59 |

| 5.8  | Analog to digital conversion subsystem                                     | 60 |

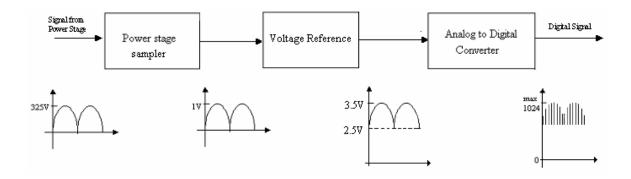

| 5.9  | The conversion process of the signal                                       | 60 |

| 5.10 | Actual circuit diagram of voltage sampler                                  | 61 |

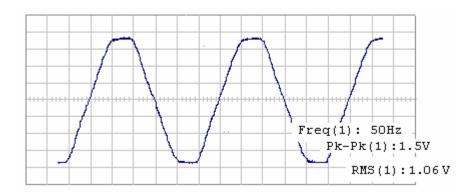

| 5.11 | Output waveform of the voltage sampler                                     | 62 |

| 6.1  | Maximum rating of Fast recovery rectifier diodes                           | 64 |

| 6.2  | Forward voltage Vs forward current (maximum values)                        | 64 |

| 6.3  | Maximum ratings of power transistor of 2N3773                              | 65 |

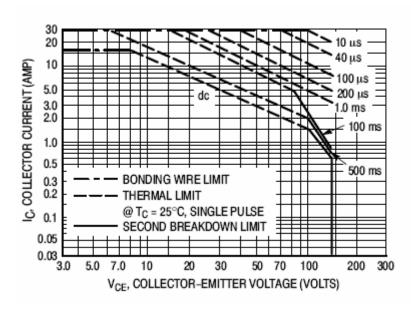

| 6.4  | Forward biased safe operating area of power transistor 2N3773.[25]         | 66 |

| 6.5  | Maximum ratings of 2N4923                                                  | 67 |

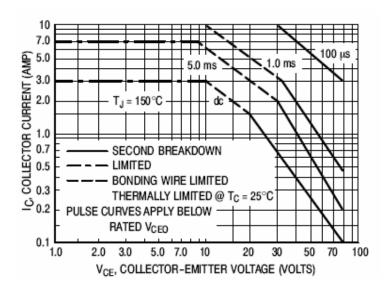

| 6.6  | Forward biased safe operating area of medium power transistor 2N4923       | 67 |

| 6.7  | Maximum ratings of TLP521-4                                                | 68 |

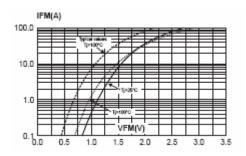

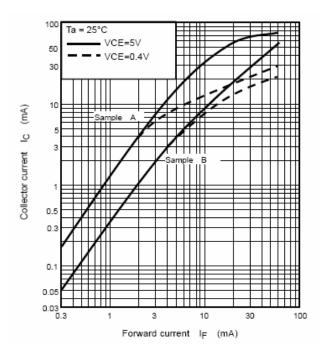

| 6.8  | Forward current $I_F$ Vs collector current $I_C$                           | 69 |

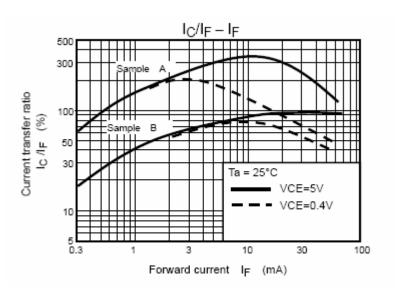

| 6.9  | Variation of current transfer ratio                                        | 69 |

| 6.10 | Initial Stage of the AC electronic load                                    | 72 |

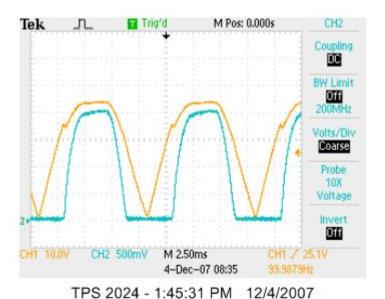

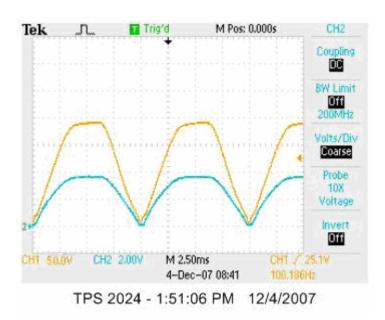

| 6.11 | Oscilloscope captures of voltage across the array and collector current    | 73 |

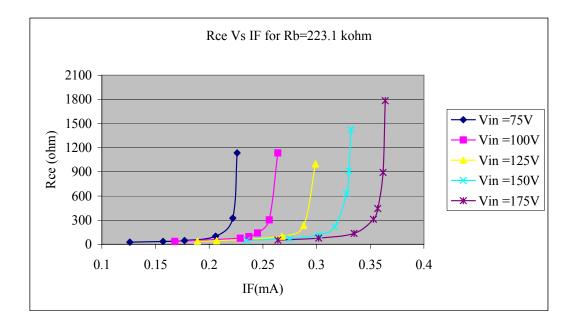

| 6.12 | Variation of the resistance of the array with the diode current of         |    |

|      | Optoisolator when $R_B = 220K\Omega$ .                                     | 74 |

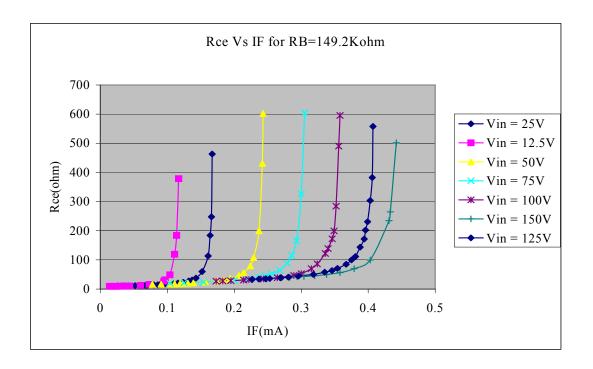

| 6.13 | Variation of the resistance of the array with the diode current of         |    |

|      | Optoisolator when $R_B = 150 \text{K}\Omega$ .                             | 75 |

| 6.14 | Variation of the resistance of the array with the diode current of         |    |

|      | Optoisolator $R_B = 180 K\Omega$ .                                         | 75 |

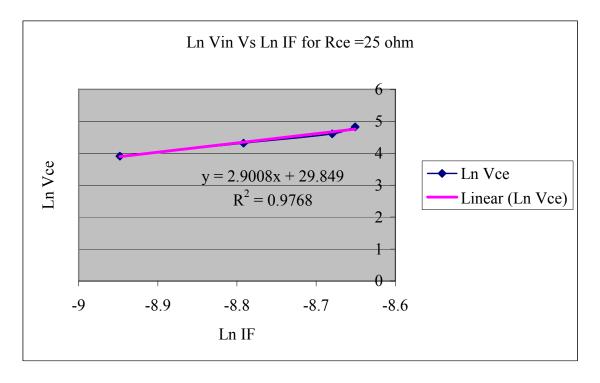

| 6.15 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 25$ ohm                             | 78 |

|------|------------------------------------------------------------------------|----|

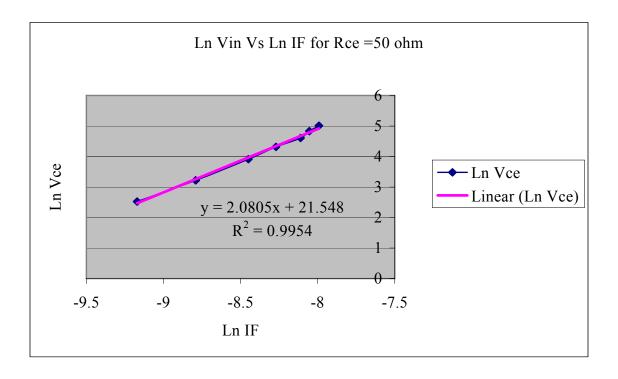

| 6.16 | Ln V <sub>in</sub> Vs Ln I <sub>F</sub> for <i>Rce</i> =50 ohm         | 79 |

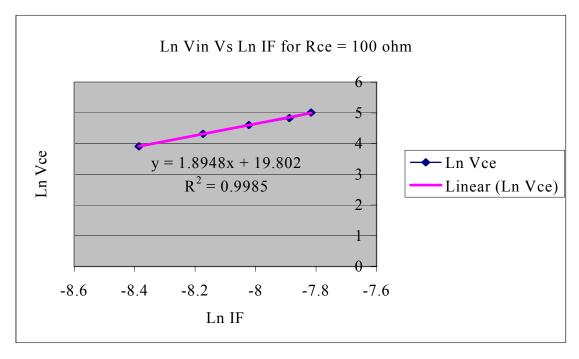

| 6.17 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 100$ ohm                            | 79 |

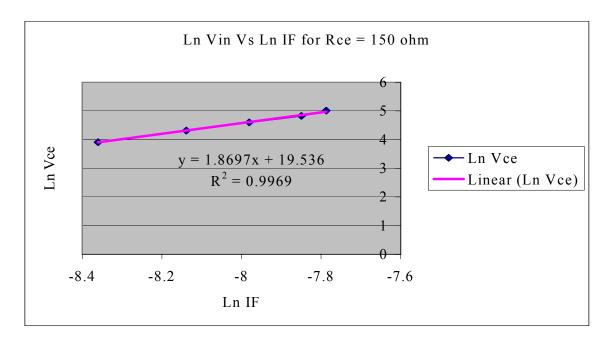

| 6.18 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 150$ ohm                            | 80 |

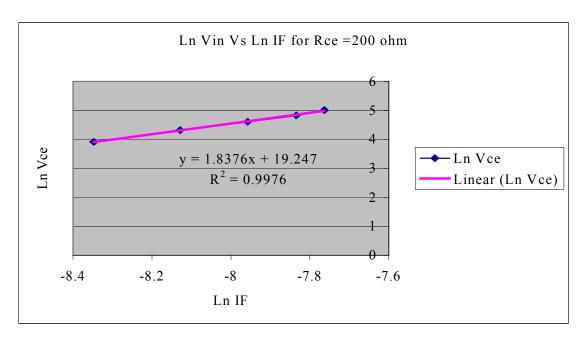

| 6.19 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 200$ ohm                            | 80 |

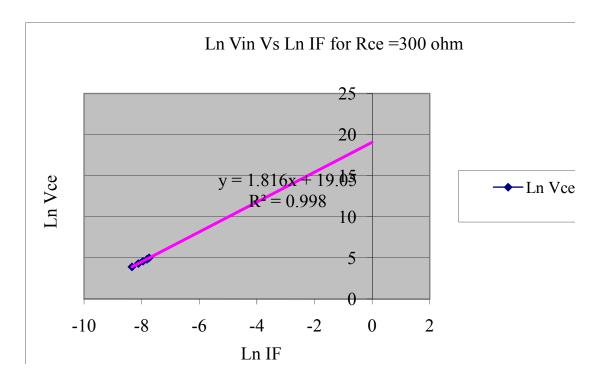

| 6.20 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 300$ ohm                            | 81 |

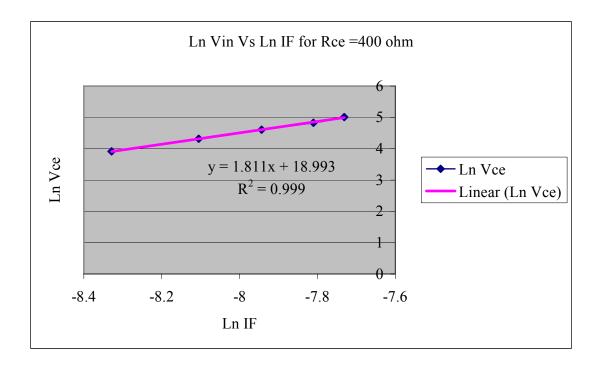

| 6.21 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce$ =400 ohm                             | 81 |

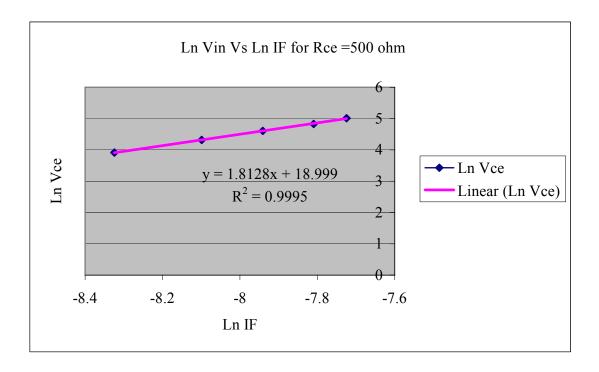

| 6.22 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 500$ ohm                            | 82 |

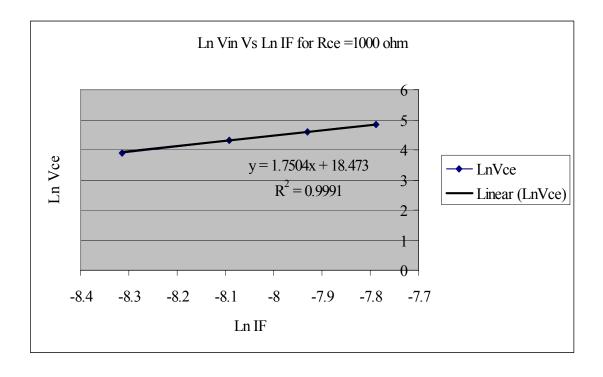

| 6.23 | Ln $V_{in}$ Vs Ln $I_F$ for $Rce = 1000$ ohm                           | 82 |

| 6.24 | Ln V <sub>in</sub> Vs Ln I <sub>F</sub> for <i>Rce</i>                 | 84 |

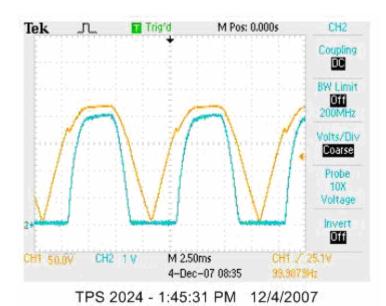

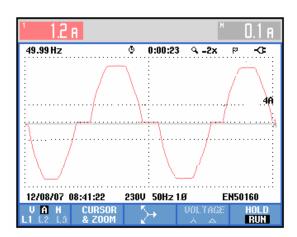

| 7.1  | Voltage and current at bridge points without controller                | 92 |

| 7.2  | Voltage and current at bridge points with controller                   | 92 |

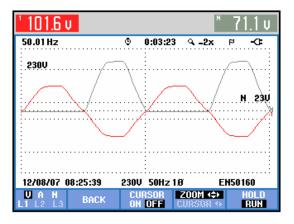

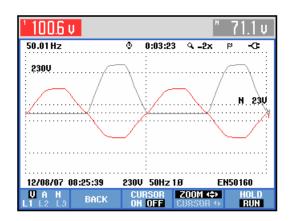

| 7.3  | Voltage waveform of the load with the digital control                  | 93 |

| 7.4  | Voltage waveform of the load without the digital control               | 93 |

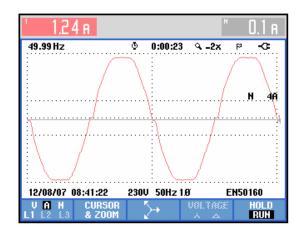

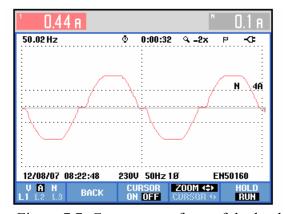

| 7.5  | Current waveform of the load with the digital control when             |    |

|      | resistance is $75\Omega$ .                                             | 93 |

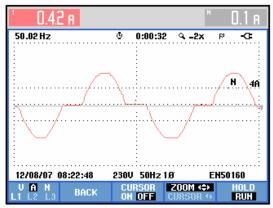

| 7.6  | Current waveform of the load without the digital control when          |    |

|      | resistance is $75\Omega$ .                                             | 93 |

| 7.7  | Current waveform of the load with the digital control when             |    |

|      | resistance is $200\Omega$ .                                            | 94 |

| 7.8  | Current waveform of the load without the digital control when          |    |

|      | resistance is $200\Omega$ .                                            | 94 |

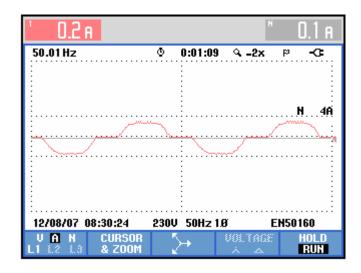

| 7.9  | Current waveform of the load with the digital control when             |    |

|      | resistance is $500\Omega$ .                                            | 94 |

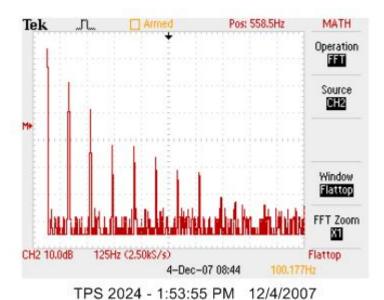

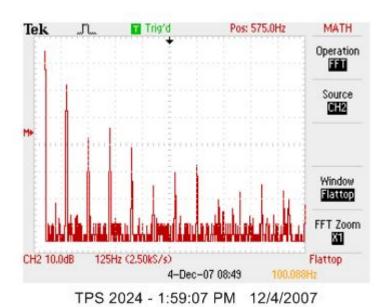

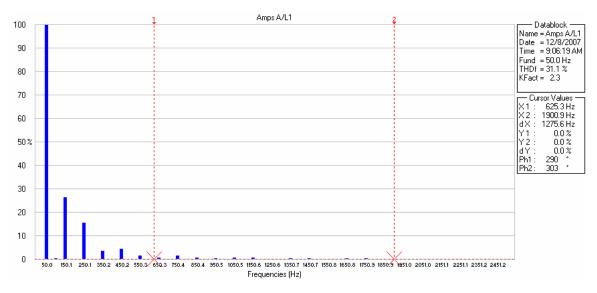

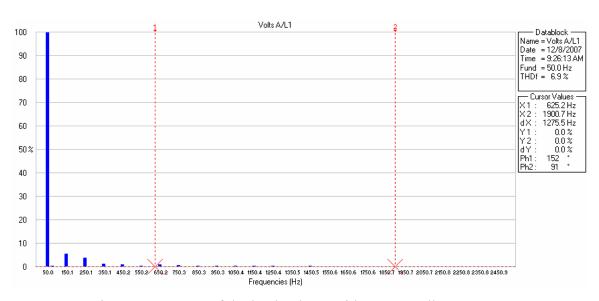

| 7.10 | Fast Fourier transform of the load current with the digital control    | 95 |

| 7.11 | Fast Fourier transform of the load current without the digital control | 95 |

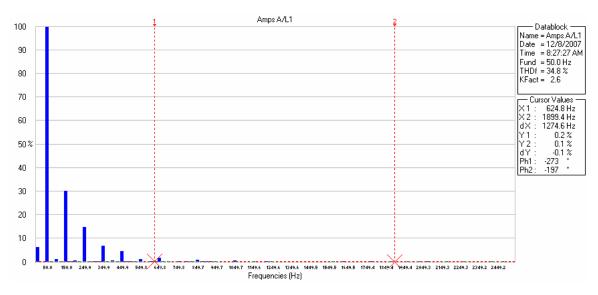

| 7.12 | THD of the load current with controller at 0.2A                        | 96 |

| 7.13 | THD of the load current without controller at 0.2A                     | 96 |

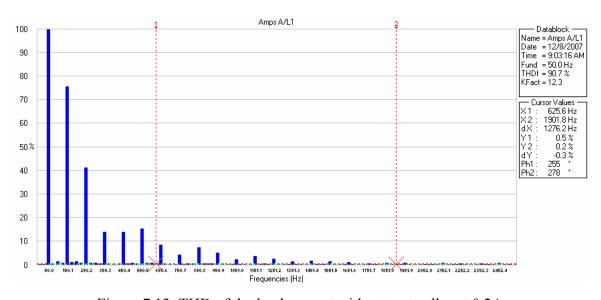

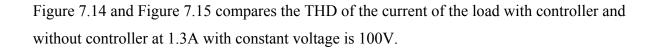

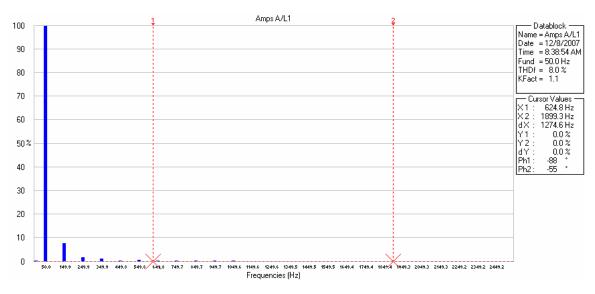

| 7.14 | THD of the load current with controller at 1.3A                        | 97 |

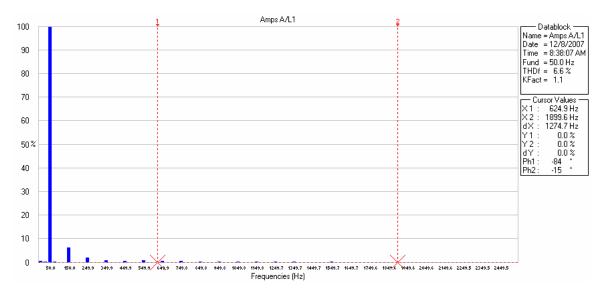

| 7.15 | THD of the load current without controller at 1.3A                     | 97 |

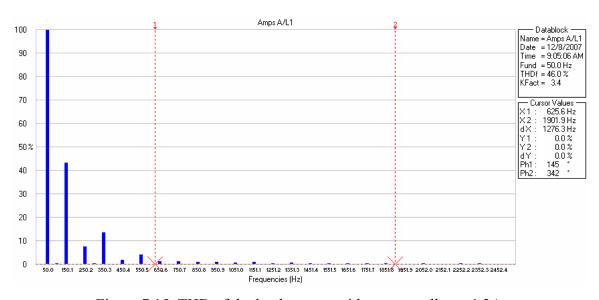

| 7.16 | THD of the load current with controller at 1.5A.                       | 98 |

| 7.17 | THD of the load current without controller at 1.5A             | 98   |

|------|----------------------------------------------------------------|------|

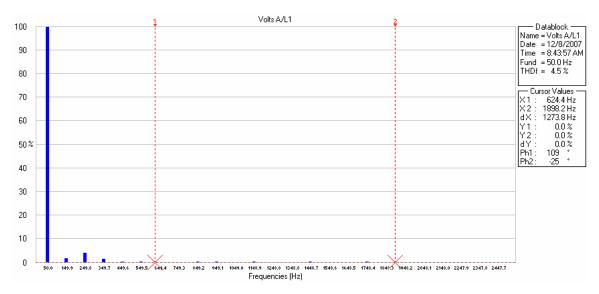

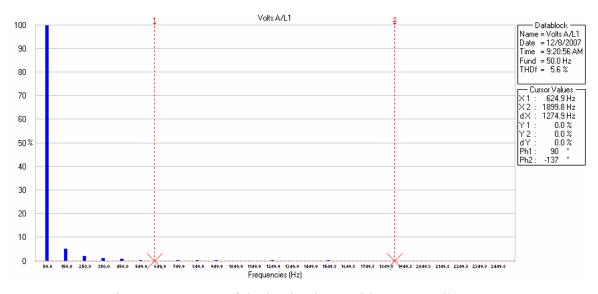

| 7.18 | THD of the load voltage with controller at 50V                 | 99   |

| 7.19 | THD of the load voltage without controller at 50V              | 99   |

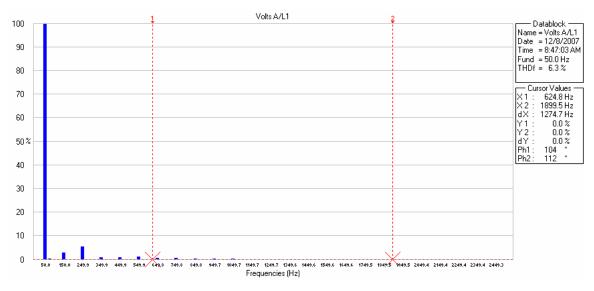

| 7.20 | THD of the load voltage with controller at 125V                | .100 |

| 7.21 | THD of the load voltage without controller at 125V             | 100  |

| 7.22 | THD Vs Load current at constant voltages                       | 101  |

| 7.23 | THD Vs Load voltage at constant current                        | 102  |

| A.1  | DAC circuit.                                                   | 109  |

| A.2  | Sampling Circuit.                                              | 110  |

| A.3  | AC Load circuit power stage.                                   | 111  |

| B.1  | Photograph of Zilog Z8Encore! Microprocessor development board | 113  |

| B.2  | Photograph of Transistor array.                                | 114  |

| B.3  | Photograph of the test bench.                                  | 115  |

| C.1  | Simulation circuit.                                            | 118  |

# Chapter 1

# Introduction

### 1.1 Background

With the development of technology related to power electronics and power conversion systems, testing methods for design verification and product function require sophisticated electronic equipment. The different power supply architectures and output combinations also dictate the need for versatile test instruments that can accommodate a broad range of specifications. As a result, one testing requirement that has been growing in importance is the method of loading a power supply under test. The need for a higher degree of load control due to test sophistication, such as the need for computer programmability, has increased the demand for programmable electronic loads.

### 1.2 Electronic Loads

Electronic load is a combination of circuits designed to provide a variable load at the outputs of a power supply, usually capable of dynamic loading and frequently programmable. An electronic load offers a broad range of operating modes, providing versatile loading configurations needed for characterizing and verifying power supply design specifications.

Loads can be resistive, inductive or capacitive. Real load behavior is typically more complex. They are in different emulation modes of operation and these loads can be controlled by microcontrollers. DC Electronic loads can be constant voltage (CV), constant current (CC), constant resistance (CR), dynamic and also short circuit type. AC electronic load can be constant mode and rectified mode. Constant mode includes constant current (CC), constant resistance (CR) and constant power. Rectified load mode includes crest factor (CF), power factor (PF) and short circuit load.

Among these different loads CC mode has the highest performance and dynamic loads are very important in testing Uninterrupted Power Supply (UPS) systems. Dynamic loads are more expensive than the other loads [1]. CR mode is only mode of AC loads that can be used to test discontinuous square wave or quasi-square wave units under test.

Following table explains the basic types of loads used in industry for testing power supplies [2].

| Description                                                                                                                                                                                                                                                                                                                                                                                                                              | Applications                                                                 | Circuit model               | Characteristics           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|---------------------------|

| Constant current mode (CC mode): AC/DC  Current will sink accordance with the programmed value regardless of the input voltage. Load regulation is the power supply's ability to provide a stable output voltage under load variations. It is specified as a percentage deviation from normal output at a fixed input voltage and is calculated using the following formula $\% LR = \frac{V_{o(max)} - V_{o(min)}}{V_{o(normal)}} x100$ | Used to test voltage sources and load regulation of AC and DC power supplies | Voltage Load Source CC Mode | Programmed Load Current V |

| Constant Voltage (CV) mode: DC only  Electronic loads will sink in enough current (if available) to control the source voltage to the programmed value.                                                                                                                                                                                            | Used to test current source. It is frequently used to test current limit characteristic of power supplies. It can also be used for testing battery chargers where CV mode load can emulate a battery's terminal voltage. |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Constant Resistance (CR) mode: AC/DC  Electronics loads will sink a current linearly proportional to the input in accordance with the programmed resistance                                                                                                                                                                                        | Used to test either voltage or current sources, and is normally used in testing power source start up and current limit.                                                                                                 | Current CR Mode  CR Mode  CR Mode  Voltage Source  CR Mode | I Programmed Load Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dynamic load: DC only  Dynamic load operation causes electronic loads to periodically switch between two load levels. A power T pply's regulation and transient response can be evaluated by monitoring its output voltage under varying combination of load High/ Low current levels, High/ Low current level duration, and Rise/ Fall slew rate. | Used to test the transient response of a power supply. Most commonly used loads are dynamic.                                                                                                                             | Voltage Dynamic Mode                                       | High level duration Theorem and the second duration durat |

| Crest Factor load (CF): AC only  Crest factor is the ratio of the peak value to the rms value of a load current waveform. This term is often used to specify the maximum peak amplitude the AC power supply or UPS can source (relative to its maximum rms rating) without di $Crest \ Factor = \frac{I_{peak}}{I_{rms}}$ | Most power-input circuitry (without power factor correction) consists of a rectifier diode and capacitor filter circuit, which generates a pulse AC line current. CF loads are used to simulate this current waveform | Load                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Power Factor Load: AC only Power factor is the ratio of average power value to the product of $V_{rms}$ and $I_{rms}$ . $P.F = \frac{P_{av}}{V_{rms} \ x \ I_{rms}}$                                                                                                                                                      | These are the first active AC loads to simulate inductive and capacitive load by programming the power factor from 0 to unity                                                                                         |                                                                         |  |

| Short Circuit Load: AC/DC An AC/DC power supply's output terminals having very low resistance. A power supply's protection circuit should be activated to limit the currant output when this condition exists (Short circuit).                                                                                            | Used to simulate the short circuit conditions.                                                                                                                                                                        | DC Electronic Load  AC Electronic Load  AC Source  AC Source  AC Source |  |

Table 1: Different AC and DC loads

## 1.3 Testing of Power Supplies

Power supplies are used in a wide variety of products and test systems. As a result, the tests performed to determine operating specifications could differ from manufacturer to manufacturer or from end user to end-user. For instance, the tests performed in R&D environment are primarily for power supply design verification. These tests require high performance test equipment and a high degree of manual control for bench use. In contrast, power supply testing in production environments primarily focus on overall function based on the specifications determined during the products design phase. Automation is often essential due to large volume testing, which requires high-test throughput and test repeatability. Power supply test instruments must then be computer programmable. For both test environments, measurement synchronization is necessary to perform some tests properly and to obtain valid data. Proper selection of test gear will provide the best combination of measurement sophistication and test set programmability.

There are certain instruments that are essential to all tests, regardless of the implementation. They are electronic loads, digital oscilloscopes, digital multimeters, true rms Voltmeters, Watt meters, and ac power sources. Electronic loads can facilitate power supply testing in several ways. They are typically programmable. This capability enables finer control over loading values during testing. Electronic loads are usually designed with transistors, which provide increased reliability and easy programmability.

#### 1.3.1 Testing of DC power supplies

DC power supply testing includes tests of,

• Load transient recovery time

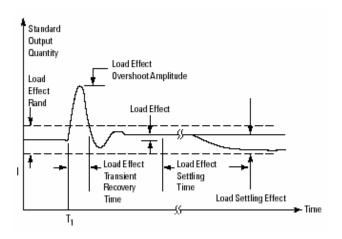

This is the time required for the output voltage of a power supply to settle within a predefined settling band following a load current induced transients as shown in the Figure 1.1.

Figure 1.1: Load transient recovery time [3]

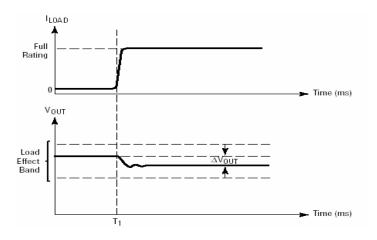

#### • Load effect (load regulation)

Load effect or load regulation defines the ability of a power supply under test to remain within specified output limits for a predetermined load change as shown in the Figure 1.2.

Figure 1.2: Load effect

#### • Current limit characterization

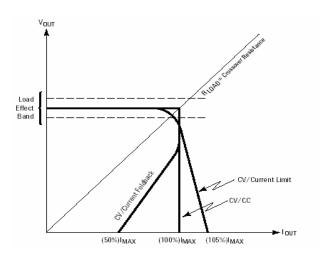

Current limit measurement demonstrates the degree to which a constant voltage power supply limits its maximum output current to a preset value. Figure 1.3 shows typical operating characteristics of three types of current limiting power supplies [3].

Figure 1.3:Typical Operating Characteristics of Three Types of Current Limiting Power Supplies

#### • Periodic and random deviation (PARD)

PARD is the periodic and random deviation of the DC output voltage from its average value, over a specified bandwidth and with all other parameters constant [3]. This represents the noise and similar random deviation at the output of a power supply.

#### Efficiency

Efficiency of a power supply is simply the ratio of total output power to its total input power.

#### startup delay

Startup delay of a power supply is the amount of time between the application of ac input and the time at which the outputs are within their regulation specifications.

In order to effectively carryout these tests maximum ratings of voltage, current and power capability of the loads should be higher than those of the power supply to be tested. For dynamic tests, loads are required to change their outputs at fast slew rate and therefore electronic loads are preferred. In testing the load transient response, it is necessary to produce fast changes in load current in the range of  $10A/\mu s$  to  $100A/\mu s$  and the easiest way of doing it is the use of an electronic load, which employs solid state switching [4].

#### 1.3.2 Testing of AC power systems

Systems such as automatic voltage regulators, power conditioners, and UPS systems require loads which can act as variable AC loads, which are capable of polarity reversal across the load. A test of UPS includes functional load testing, checking the protection settings and calibration of the unit [5]. Loads can be three phase or single phase. The work in the thesis is on single phase loads.

Functional load testing of an AC-AC converters can be divided into different operations. They are

#### Steady state load test

Under a steady-state test, checking of all input and output conditions at 0%, 50%, and 100% and testing of the following parameters: input voltage, output voltage, input current, output current, output frequency, input current balance for a three phase input, and output voltage regulation load is done. The analysis will reveal if input currents match across all phases of a module as well as determine if all modules equally share the load.

#### Harmonic analysis

Monitoring of the input and output of the AC-AC converters for harmonic content during the steady-state load test. Observing the harmonic content at 0%, 50%, and 100% load allows to determine the effectiveness of the input and output filters.

#### • Filter integrity

The filter integrity tests indicate the failure of inductors and capacitors in the filters in AC-AC converters. Performing a relative phase current balance is a simple means of checking filter integrity.

#### Transient response load test

The transient response test simulates the performance of the AC-AC converters with large instantaneous swings in load.

#### Module fault test

Module fault test is performed to verify that the multi module system continues to maintain the critical load in the event of a module failure. The system should continue to maintain the load without significant deviation of voltage or frequency as verified by a recording oscillograph.

#### • Battery rundown test

Battery rundown test detects the condition of the battery system and is simply done by measuring temperature, voltage, and current under load conditions.

These kind of testing are very expensive and variable loads are required to perform the tests. The best kinds of loads suitable for testing are electronic AC loads that can give constant load mode and rectified load mode [6].

Compared to a DC load, during load testing of an AC output systems, an AC load may require a good linearity property of the impedance at different instantaneous voltages of the AC cycle. If the load is not perfectly linear, the load current will create harmonics of the 50Hz or 60Hz AC line frequency. Therefore Total Harmonic Distortion (THD) measurement of AC output systems become an important issue.

Total Harmonic Distortion (THD) is essentially a measure of deviation from a perfect sinusoidal wave. THD is the ratio, expressed as a percentage, of the rms value of an AC signal after the fundamental component is removed to the rms value of the fundamental component. THD of current can be defined as;

$$THD = \frac{\sqrt{I_2^2 + I_3^3 + I_4^4 \dots + I_n^n}}{I_1^1}$$

Linearity of a load can be determined by the THD of the load current. IEE Std-519 applicable harmonic limits, IEEE Recommended practices and requirements of harmonic control in electrical power systems specify the harmonic limits for utilities and consumers [5].

In an AC output system, the output voltage waveform may not be purely sinusoidal. In testing these, a load with sufficient linearity may be required.

A load with a high THD requires more energy to sustain than a load with low THD. The wasted energy dissipates as heat. That makes the load inefficient. To test UPSs etc. with high THD it is necessary to select loads with low THD to avoid the unnecessary heating of the UUT.

Selection of an electronic load for a particular test requires an analysis of performance specifications and product features. Input specifications include power, voltage, current and frequency. Measurement type, efficiency and emulation mode are other considerations while selecting a load.

### 1.4 Requirements

Development of an AC load with high voltage and high current capability and with very low THD and fast switching capability to test AC-AC converters is the aim of this research.

As discussed in section 1.3 an AC electronic load need to be developed to work under 230V/50Hz or 110V/60Hz.Generally the maximum voltage across the load will be  $230\sqrt{2}V$  for 230V/50Hz system. Also they should have high power capability for testing of power conditioning systems such as UPS/Automatic Voltage Regulator /Power Conditioners etc.. The maximum ratings of the load should be higher than that of the unit under test.

In addition AC electronic loads need to meet the following requirements:

- Linearity

- Reliability

- Economy

- Stability

- Reproducibility

#### 1.4.1 Linearity

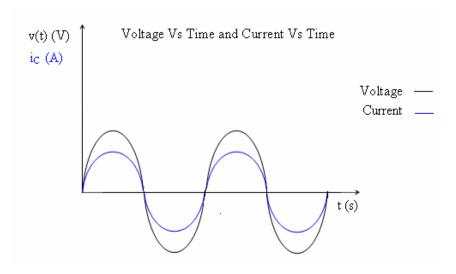

Linearity of a system is the property that the output quantity of the system is proportional to the input quantity. Linearity of a load is a characteristic that makes the current curve a perfect replica of the voltage curve as shown in Figure 1.4 giving the current and voltage very low THD.

The objective of a DC electronic load is to have a variable resistance. Unlike in AC cases there is no instantaneous change in the output voltage and usually the output load current can only be changed by varying the impedance of the transistor. Therefore they are easy to design.

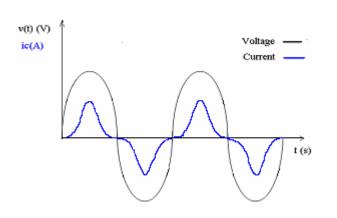

AC loads containing high-speed electronic switches, such as diodes, thyristors, or transistors could make the load non-linear because of their non-linear characteristics. In a transistor circuit large signal changes of ac voltage across the collector and the emitter make the device to operate in its saturation region, active region and cutoff region within a complete cycle, making it a non-linear device.

In this research, to implement an AC load, bipolar junction power transistors are used. The characteristics of the power BJTs are discussed in Section 1.5 and Section 2.1.1 in Chapter 2. Non linear behaviour of an AC electronic load is as shown in the Figure 1.5 highlighting the possibility of non linear currents drawn by the load. In this project linearity is to be achieved using electrically isolated digitally control circuitry.

Figure 1.4: Voltage and current wave forms of a linear load

Figure 1.5: Voltage and current wave forms of an AC Electronic load

#### 1.4.2 Reliability

The reliability of a device is related to the component count and the reliability of each component. Component reliability is a statistical function commonly expressed as the Mean Time Between the failures (MTBF) [7]. For a system comprising n non-redundant components, the system MTBF is expressed as

$$\frac{1}{\text{MTBF}} = \sum_{i=0}^{n} \frac{1}{\text{MTBF}_{n}}$$

Even when individual components are highly reliable, the MTBF for a large system could still be unacceptably short. For example, if the MTBF of one class of a component is 100,000 hours (about 11.5 years) and if there are 50 such components in the system, then the MTBF for that system is only 2,000 hours (83 days). The MTBF for *m* redundant components is MTBF<sup>m</sup> and judicious duplication of key components can be employed to increase the reliability of any system. Thus, two systems of components in redundant configuration each with a MTBF of 2,000 hours will have combined MTBF in excess of 450 years. This increase in reliability is only achievable if the system is designed so that transfer of function to the redundant set of components is time wise seamless and the failed components can be immediately replaced without interrupting the operation of the systems.

### **1.4.3 Economy**

Clearly, the smaller the component count is to achieve the required functionality, the longer is the MTBF and the lower is the overall system cost.

#### 1.4.4 Stability

The stability of a system is measured in terms of its ability to withstand disturbances of a given relative magnitude and the time required to attain normal functioning following a disturbance. The magnitude of a disturbance can be expressed in terms of the full load of the system. Clearly, a desirable property of a system is the ability to withstand significant disturbances and different kind of non-linear loads.

#### 1.4.5 Reproducibility

The reproducibility of a system describes how closely the properties of its output approach the design requirements. This can be measured in terms appropriate to the output waveform. For DC this would be voltage and tolerance limits. For AC it would be in terms of Root Mean Square (RMS) value.

# 1.5 Research Objectives/ Specifications

The aim of this research is to implement a 230V/50Hz high power capable AC electronic load. A single BJT may not withstand the voltage level and power in a 230V AC load. Therefore series connected transistor array was proposed to share the voltage and power equally [8]. The design concept of the array is discussed in Chapter 3.

Objectives in developing high power capable variable AC impedance are given below.

- Equal power dissipation and voltage distribution across the individual transistors with reasonable device temperatures.

- 230V/50Hz line voltage capability

- 5A RMS current

- Low harmonic distortion of current waveform according to the IEE Std-519

- Digitally controllable

- Linear

- Fast transient response

# 1.6 System Overview

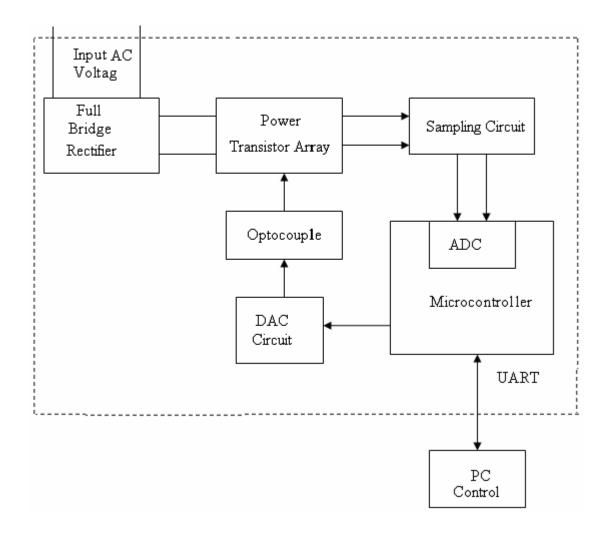

The AC electronic load consists of three major parts.

- The power transistor array

- Sampling circuit

- Digital control circuit

Basic concept of AC impedance control is achieved by base current diversion principle. BJT array is inserted between diode bridge points to achieve AC operational capability.

A combination of a high power transistor and a high voltage low power transistor are combined in a Darlington configuration to achieve higher gain. More details of complete circuits will be discussed in Chapter 2 and Chapter 3.

The complete block diagram of the system is shown in the figure 1.6 Set of opto isolators are used in the design to maintain the electrical isolation between the low voltage control circuitry and the high voltage power stage.

Figure 1.6: Complete block diagram of the AC Electronic load design

### 1.7 Thesis Outline

In this Chapter background, different loads, testing methods, requirements and objectives of the research were discussed. In addition the overall system overview is briefly reviewed.

In Chapter 2 the existing design techniques are examined and some related topics such as power transistor options, electrical isolation, sampling circuits are briefly discussed.

In Chapter 3 a theoretical overview of the design approach of power stage, advantages of the design, assumptions made and their effects are discussed.

Chapter 4 describes about the simulation carried out and its results.

In Chapter 5 the approach to digital control of the transistor array using microcontroller development system is discussed. In addition details of voltage sampler and digital to analog converter system are described.

Implementation aspects such as the selection of components, heat sink calculations and approach to measurements are discussed in Chapter 6.

Chapter 7 shows the performance of digitally controlled AC electronic load performance.

Chapter 8 summarizes the conclusions and its implications for future developments.

# Chapter 2

# **Background and Related Work**

### 2.1 Background work and literature survey

A literature survey carried out during the early stages of the thesis work indicated that a series connected BJT array can be used as the main control element of automatic voltage regulators [9]. In this case of the BJT array an approach to equally sharing the voltage and power among multiple transistors were discussed [10 - 13]. Based on the above work it was decided to use a similar technique for developing the AC electronic load, where multiple power BJTs were to share the dissipation.

# 2.2 Power Transistor options for electronic loads

Power transistors are able to handle voltages from few volts to several kilovolts and currents from few milliamperes to few hundred amperes. The operation of all power semiconductors is limited by a series of ratings which define the operating boundaries of the device. Among the commercially available power semiconductor devices usable options are the bipolar junction transistors (BJT), MOSFETs and IGBTs.

#### 2.2.1 Bipolar junction Transistors

BJT is essentially a current operated device where the device pushed to conducting stage by controlling the current into the base junction. When a BJT is turned on, a forward voltage drop is developed across the device collector and emitter terminals giving rise to power loss and thus heat loss. BJTs have very high current carrying capabilities and therefore they are used in low to high power applications.[14]

Low current gain, complex drive circuitry, relatively low switching characteristics which limits the maximum operating frequency to low kHz range and negative temperature coefficient which leads to high increase in device temperature are some of the drawbacks of BJTs.

#### 2.2.2 Metal Oxide Field Effect Transistors (MOSFET)

Power MOSFETs differ from BJTs in operating principles, specifications and performance A power MOSFET has high input impedance and thus requires minimal gate current to turn on and off. This greatly simplifies the drive circuitry and reduces its cost. In addition they have very fast switching characteristics allowing them to operate into the MHz range [15] MOSFETs are merely resistors while switched on and give rise to power and heat loss in the device. They have positive temperature coefficient which stop thermal runaway.

The relatively low breakdown voltages limit the use of MOSFETs in high voltage applications. High on resistance especially at high breakdown voltages limits their current carrying capabilities.

#### **2.2.3** Insulated Gate Bipolar Transistors (IGBT)

IGBT is a combination of a power MOSFET and a BJT having superior characteristics. Similar to MOSFETs they are voltage controlled devices. Their high input impedance makes the minimal gate drive requirements and low cost drive circuitry. Switching speed is comparable to MOSFETs and forward voltage drop and current densities are similar to BJTs thus low conduction losses. Their breakdown voltage is much higher than that of MOSFETs. These high performance along with high current capability make the IGBTs, a choice in high power and high voltage applications.

Possibility of uncontrollable latch-up under overstress conditions (high dv/dt or di/dt), lower switching speed and higher switching losses Compared to MOSFETs are some drawbacks of IGBTs.

#### 2.2.4 Selection of the device option for the AC electronic load

In this research BJTs are selected from these super devices in order to have current controllability and high current capability.

# 2.3 Use of Darlington pair

It is well known that Bipolar junction transistors have low current gain at typical operating current levels and they require continuous high base current for allowing significant current to flow from collector to emitter. This is discussed in this Section 2.3.1. Therefore in order to have a high current gain with low base current the single transistors in the circuit shown in Figure 2.5 are replaced using Darlington pairs.

Darlington Transistor comprises of a medium power BJT connected to a power BJT as shown in the Figure 2.1. This provides a high current gain approximately equal to the product of the current gains of the two transistors. Darlington transistor has better transistor parameters than the single transistor but almost twice the base to emitter voltage [16]. Darlington pair is treated as a single compound transistor for analytical purposes.

Figure 2.1 Darlington pair

#### 2.3.1 Large signal models of BJT in the forward active region

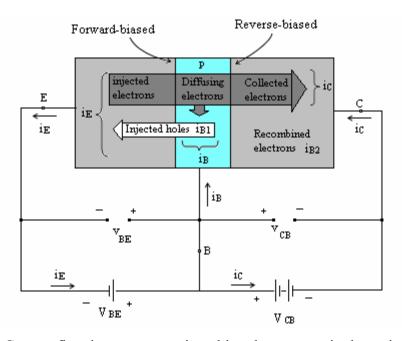

In a transistor control signal, a base current can be used to cause the current in the collector to change from zero to a large value. In bipolar junction transistor current is conducted by both electron and holes. For the analysis only diffusion current components are considered and drift currents due to thermally generated minority carriers are usually very small and are neglected.

Figure 2.2 Current flow in an npn transistor biased to operate in the active mode [16]

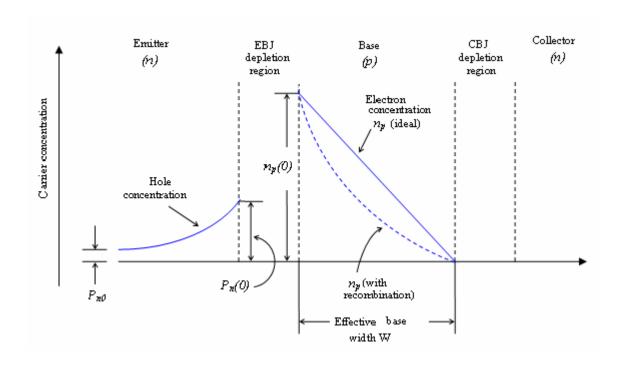

Figure 2.3 Profiles of minority carrier concentrations in the base and the emitter of an npn transistor operating in the active mode [16]

The electron concentration will be highest [denoted by  $n_p(0)$ ] at the emitter and lowest (zero) at the collector. For a forward bias p-n junction the concentration  $n_p(0)$ ,

$$n_p(0) = n_{p0} e^{v_{BE}/V_T}$$

....(2.1)

where  $n_{p0}$  is the thermal equilibrium value of the electron concentration in the base region,  $v_{BE}$  is the forward base-emitter bias voltage and  $V_T$  is the thermal voltage, which is equal to approximately 25mV at room temperature.

The tapered minority carrier concentration profile as shown in Figure 2.3 causes the electrons injected into the base to diffuse through the base region towards the collector. This electron diffusion current  $I_n$  is directly proportional to the slope of the straight line concentration profile,

$$I_n = A_E q D_n \left( \frac{dn_p(x)}{dx} \right)$$

$$I_n = A_E q D_n \left( -\frac{n_p(0)}{W} \right) \dots (2.2)$$

where  $A_E$  is the cross-sectional area of the base emitter junction, q is the magnitude of the electron charge,  $D_n$  is the electron diffusivity in the base, and W is the effective width of the base.[16]

The collector current  $i_C = I_n$

Then from equation (1) and (2),

$$i_C = I_S e^{v_{BE}/V_T}$$

....(2.3)

$$I_S = A_E q D_n n_{p0} / W$$

....(2.4)

where  $I_S$  is called saturation current or current scale function.

Also

$$n_{p0} = n_i^2 / N_A$$

where  $n_i$  is the intrinsic carrier density and  $N_A$  is the doping concentration.

Then

$$I_S = \frac{A_E q D_n n_i^2}{N_A W}$$

....(2.5)

Thermal voltage

$$V_T = kT/q....(2.6)$$

where k is the Boltsman constant and T is the absolute temperature [16].

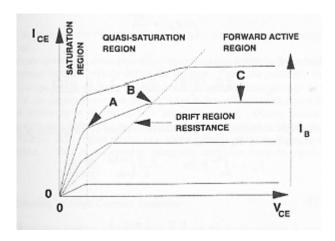

Figure 2.4 shows the output characteristics of a power bipolar transistor showing the saturation and quasi-saturation regions of operation. The current gain of the transistor is decreasing when proceeding from the forward active region through the quasi-saturation region into saturation region. This is because of the additional recombination current that must be supplied by the base electrode for sustaining carriers that are injected in to the collector drift region.

Figure 2.4: Output Characteristics of a power bipolar transistor

In a circuit if a transistor is replaced by Darlington pair, the operating point of the circuit will remain unchanged for all the practical values of transistor parameters. [17-18]

The DC current gain ( $h_{FE}$ ) of the Darlington pair shown in the Figure 2.1 is given by,

$$h_{FE} = h_{FE1} * h_{FE2} + h_{FE1} + h_{FE2}$$

More application details of the Darlington pair are discussed in Chapter 3.

### 2.4 Need for a series connected array

When a transistor is used in 230V AC applications the instantaneous peak values often vary up to approximately  $330\sqrt{2}$  V for the range of input AC RMS voltages from 160V to 260V [14]. A single BJT may not withstand this voltage level and power. Therefore a series connected transistor array was used to share the voltage and power equally [8]. Figure 2.5 shows the basic transistor array configuration used in this research.

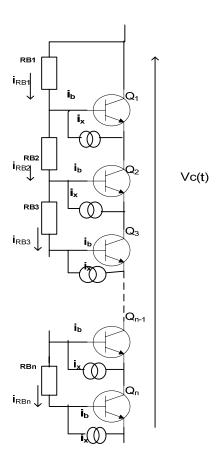

Figure 2.5: Transistor array

If all the transistors are to dissipate equal power, the base currents and collector current need to be equal. If the transistor gains are large and identical, and if each transistor has nearly identical collector currents it can be shown that,

$$R_{B1}(i_B + i_x) n + R_{B1}(i_B + i_x) (n-1) + R_{B1}(i_B + i_x) (n-2) + \dots + R_{B1}(i_B + i_x) = v_C(t) - v_{BE}$$

If

$$R_{B_1} = \frac{R_B}{n}$$

;  $R_{B_2} = \frac{R_B}{n-1}$ ;  $R_{B_3} = \frac{R_B}{n-2}$ .....;  $R_{B_n} = R_B$

Resistance across the array is given by,

$$R_{CE} = \frac{v_{BE}}{\beta i_B} + \frac{R_B}{\beta} \left( 1 + \frac{i_x}{i_B} \right)$$

Chapter 3 provides the details 0f the derivations.

#### 2.5 Electrical Isolation

Isolation electrically separates the low voltage control circuitry from the high voltage power stage. Isolation offers many benefits including,

- protection for expensive equipment, the user and data

- improved noise immunity

- ground loop removal

- increasing common-mode rejection

Isolation requires signal to be transmitted across the isolation barrier without any direct contact. There are several methods available such as optical, capacitive, inductive .etc.

#### 2.5.1 Optical isolation:

An optoisolator combines a photoconductor or a phototransistor with a high quality, long life light source in an encapsulated package that is light tight. The combination of various photosensors and light sources are available in a wide variety of packages. Typical optocouplers consists of a GaAs infrared-emitting diode and a silicon phototransistor mounted in a single package.

When forward current ( $I_F$ ) is passed through the GaAs diode, it emits infra red radiation peaking at about 900nm wavelength. This radiant energy is transmitted through an optical coupling medium and falls on the surface of the NPN phototransistor

The voltage level output by the phototransistor is directly related to the amount of light detected from the emitter. If the output transistor is biased in the active region, the current transfer relationship for the optocoupler can be represented as;

$$I_C = K \left(\frac{I_F}{I_{F'}}\right)^p \dots (2.7)$$

where  $I_C$  is the collector current,  $I_F$  is the input LED current,  $I_{F'}$  is the current at which K is measured, K is the collector current when  $I_F = I_{F'}$  and p is the slope of  $I_C$  Vs  $I_F$  on logarithmic coordinates [31].

The exponent p varies with  $I_F$ , but over some limit range of  $\Delta I_F$ , p can be regarded as a constant. The current transfer relationship for an optoisolator will be linear only if p equals to one. For typical optocouplers p varies from approximately 2 at input currents less than 5mA to approximately 1 at input currents greater than 16mA. Reasonable linearity can be obtained by using a single optocoupler.

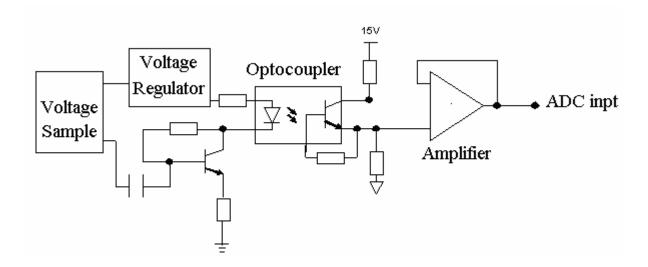

## 2.6 Sampling Circuit:

Voltage and current across the transistor array determines the effective AC resistance of the electronic load and they should be monitored for controlling purpose to achieve a linear resistance. For safety requirements high voltage samples should not be directly fed to the low voltage controlling circuits, directly. The sampling circuit has been designed to scale down the high voltage sample to a voltage level that can be fed to the control circuit.

Sampling circuit comprises with several stages such as voltage regulator, opto isolator, and amplifier. The basic diagram is shown in the Figure 2.6. The complete circuit diagram and operation will be described in the chapter 5

Figure 2.6 Basic blocks of sampling Circuit

## Chapter 3

# Power Stage –A Theoretical overview of design approach

## 3.1 Overview of the System

Developing a variable impedance with fast transient response using power transistors and conversion of the 230V/50Hz-supply input to a rectified output are the two main objectives of the power stage.

Power stage circuits includes a full bridge rectifier, bipolar junction transistor array and the associated circuits designed to achieve a uniform voltage and power distribution across each transistor.

In this research, a large signal circuit design approach was used to achieve the capability to share the power dissipation equally despite the wide variation of the instantaneous voltage over the AC cycle.

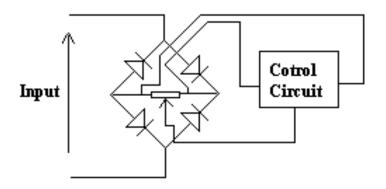

## 3.2 Rectification

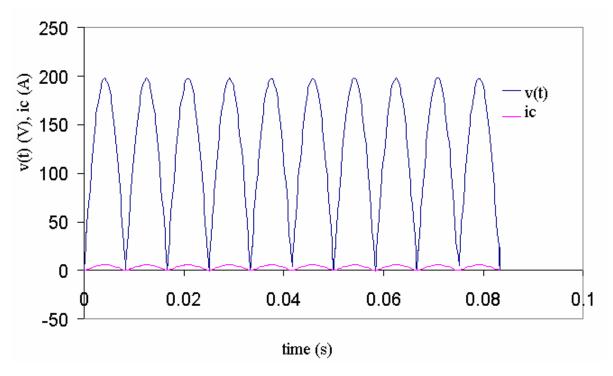

As a transistor is incapable of handling negative voltage, rectification is required. The rectification has been done using four rectifier diodes and the power transistor array is connected at the bridge points as shown in Figure 3.1 to achieve ac operational capability. Figure 3.2 shows the rectified output of current and voltage of transistor array.

Figure 3.1: Basic Circuit blocks of the AC electronic load

Figure 3.2: Practical rectified output at bridge points of the array

## 3.3 Transistor Array Design

A conceptual approach for changing the effective collector-emitter resistance of a BJT over a wide range is shown in Figure 3.3 with a transistor across a diode bridge to achieve AC capability. Large input voltage makes the voltage drop across diodes negligible compared to instantaneous voltages.

#### **3.3.1** Concept

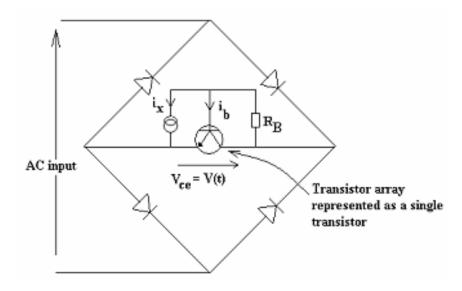

Figure 3.3 Simplified concept for variable resistance [20]

For a simplified case of a single transistor shown in Figure 3.3, impedance control is achieved by diverting a part of the base current using low voltage control circuit[20].

According to the Figure 3.3

When the transistor in active mode,

$$v(t) = v_{BE} + R_B(i_B + I_x)$$

....(3.1)

where v(t) - instantaneous collector-emitter voltage,

$v_{BE}$  - base-emitter voltage,

*i*<sub>B</sub> - instantaneous base current,

$i_x$  amount of base current diverted by control inputs

$R_B$  - resistance between the collector and base.

Also

$$v_t = i_C R_{CE}$$

....(3.2)

and

$$i_C = \beta i_B \dots (3.3)$$

Then from equation (3.1), (3.2) and (3.3) it can be proved

$$R_{CE} = \frac{v_{BE}}{\beta i_{R}} + \frac{R_{B}}{\beta} \left( 1 + \frac{i_{x}}{i_{R}} \right) \dots (3.4)$$

From the equation (3.4) it is evident that  $R_{CE}$  can be controlled by either varying  $R_B$  or the ratio  $\frac{i_x}{i_B}$  which is defined as the base current diversion ratio (BCDR). If  $R_B$  is sufficiently large enough compared to base emitter resistance  $\frac{v_{BE}}{\beta i_B}$  can be neglected.

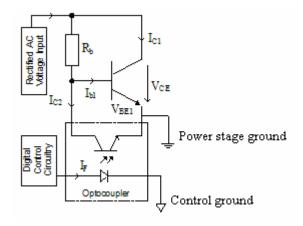

Figure 3.4 Base current diversion using an opto coupler

In the practical implementation when Darlington pairs are used for the transistor as shown in Figure 3.4, the low base emitter voltage permits the concept of controlling the BCDR using optoisolators, maintaining the necessary electrical isolation between transistor array and the control circuitry.

## 3.3.2 Application of the concept to multiple transistors in a series connected array

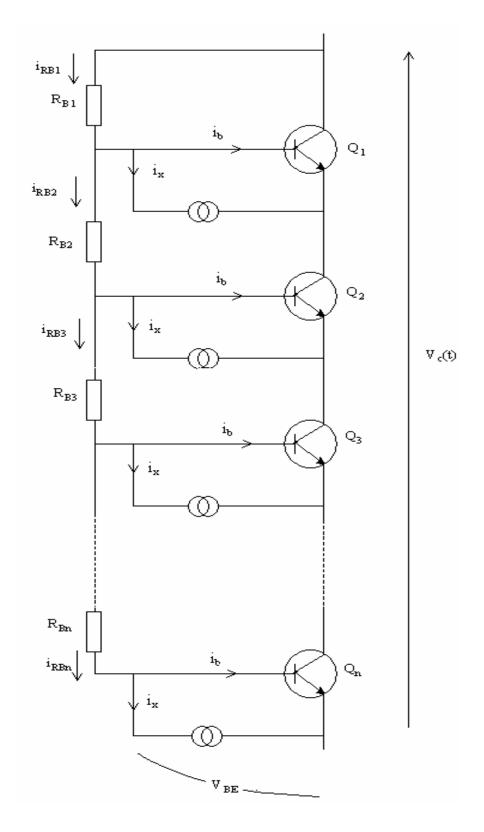

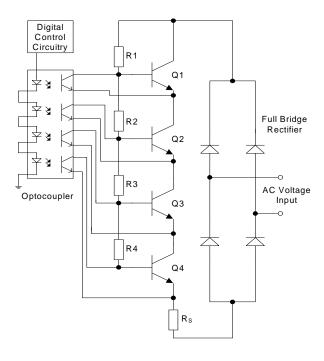

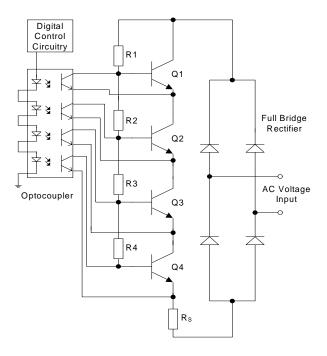

Series connected transistor configuration is a very important criteria for voltage and power sharing across the elements of the array and therefore is designed as shown in the Figure 3.5 in order to control a few hundreds of watts. It has also achieved equal power dissipation and uniform voltage distribution among the transistors.

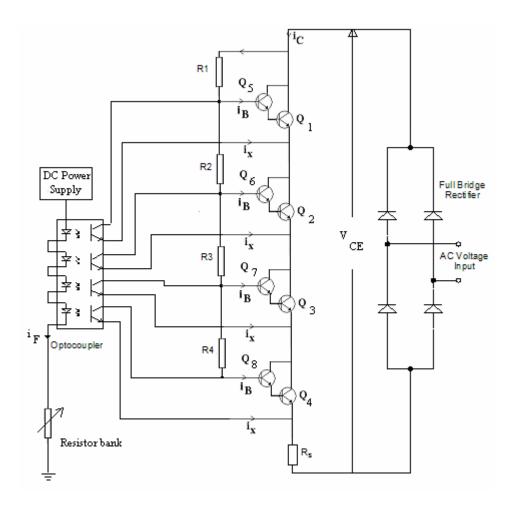

Figure 3.5 Series connected configuration of transistor array

As voltage distribution among the transistors is uniform, according to the Figure 3.5 the voltage across the m<sup>th</sup> transistor  $v_{CEm}$  is equal to  $\frac{v_c(t)}{n}$ , where  $v_C(t)$  is the instantaneous voltage across the array and n is the number of transistors.

For equal power dissipation, the base current and collector current of transistors need to be equal.

Therefore

$$i_{B1} = i_{B2} = i_{B3} = \dots = i_{Bn} = i_{B}$$

and  $i_{C1} = i_{C2} = i_{C3} = \dots = i_{Cn} = i_{C}$

If the transistor gains are large and identical, and if each transistor has nearly identical collector currents,

$$i_{C1} = \beta i_{B1}, \quad i_{C2} = \beta i_{B2}, \quad i_{C3} = \beta i_{B3}, \dots, i_{Cn} = \beta i_{Bn}, (= \beta i_{B})$$

and

$$i_{RB1} R_{B1} + i_{RB2} R_{B2} + i_{RB3} R_{B3} + \dots i_{RBn} R_{Bn} + v_{BE} = v_C(t) \dots (3.6)$$

where  $R_{B1}$  to  $R_{Bn}$  are the resistors connected between the collector and the base of each transistor.

$$R_{B1}(i_B + i_x) n + R_{B1}(i_B + i_x) (n-1) + R_{B1}(i_B + i_x) (n-2) + \dots + R_{B1}(i_B + i_x) = v_C(t) - v_{BE} + \dots$$

(3.7)

If

Equation (3.7) reduces to,

$$v_C(t) - v_{BE} = n R_B (i_B + i_x)$$

$$v_C(t) - v_{BE} = n i_B R_B (1 + \frac{i_x}{i_B})...(3.9)$$

Dividing by  $i_C$

$$\frac{v_C(t)}{i_C} = \frac{n i_B R_B}{i_C} (1 + \frac{i_x}{i_B}) + \frac{v_{BE}}{i_C}...(3.10)$$

Substituting  $i_C = \beta i_B$  and  $v_C(t) = R_{CE} i_C$  in equation (3.10)

$$R_{CE} = \frac{n R_B}{\beta} (1 + \frac{i_x}{i_B}) + \frac{v_{BE}}{\beta i_B} ....(3.11)$$

In practice  $v_{BE}$  is small compared to  $v_C(t)$ , and the equation (3.11) is approximated to,

$$R_{CE} \approx \frac{n R_B}{\beta} (1 + \frac{i_x}{i_B})....(3.12)$$

Also  $i_c = I_S e^{v_{BE}/V_T}$ ,  $i_B = i_C/\beta$  and  $V_T = kT/q$

Then

$$i_B = I_S e^{qv_{BE}/kT}/\beta$$

....(3.13)

and from equation (2.7) in Chapter 2,

$$I_C = K \left(\frac{I_F}{I_{F^+}}\right)^p$$

the equation (3.12) has become to,

$$R_{CE} \approx \frac{n R_B}{\beta} [1 + \beta \frac{K \left(\frac{I_F}{I_{F'}}\right)^p}{I_S e^{qv_{BE}/kT}}]....(3.14)$$

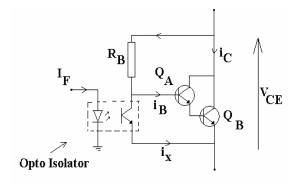

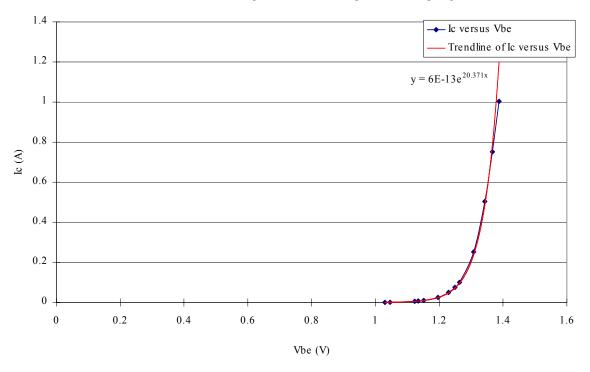

In the array of Darilington pair as shown in the Figure 3.6 the term  $I_S e^{qv_{BE}/kT}$  in equation (3.13) can be replaced by the equivalent relationship for the Darlington pair [17-18]. For the specific case in the prototype, by plotting the collector current of the Darlington pair ( $I_C$ ) versus the compound base emitter voltage ( $V_{BE}$ ) and using a mathematical fit as shown in Figure 3.7,an approximate relationship can be as follows.

$$I_C = 6 \times 10^{-13} e^{20.4V_{BE}}$$

Figure 3.6: Use of Darlington pair

Ic versus Vbe of power transistor configured as Darlington pair

Figure 3.7: I<sub>C</sub> versus V<sub>BE</sub> of power transistor configured as a Darlington pair [20]

This depicts a reasonable mathematical fit for the transfer characteristics representing the equivalent of the term  $I_S e^{qv_{BE}/kT}$  in equation (3.14). According to the Figure 3.7 it was evident that the  $R_{CE}$  value could be varied only if the effective  $V_{BE}$  for the Darlington pair was higher than 1.0V approximately.

The voltage drop  $V_{BE}$  is greater than 1.0V when the BCDR is low. Under high BCDR values i.e. diverting nearly the total base current, the effective resistance of the array is not controlled by the transistors except for the leakage effect.

If leakage effects are neglected at high BCDR values with the condition in equation (3.8), the effective maximum resistance of the array reaches the value given by the series combination of the resistors  $R_{B1}$  to  $R_{Bn}$  where

$$R_{CE \max} = R_B + \frac{R_B}{2} + \frac{R_B}{3} + \frac{R_B}{4} + \frac{R_B}{n}$$

(3.15)

At the other extreme, when the current through the input diodes of the optoisolator is zero, which is the case of minimum BCDR, the effective resistance of the array, from the equation (3.12), reduces to  $nR_B/\beta$ . Within these two theoretical limits the effective resistance of the array  $R_{CE}$ , can be controlled by varying the current through the emitter diodes of the optoisolator.

In this research four-element transistor array, as shown in the Figure 3.8, was used. In this case the range of the effective resistance is approximately  $4R_B/\beta$  to  $2.1R_B$  neglecting leakage currents of transistors. Due to the nonlinear behavior of the transistors including the dependence of  $\beta$  on the collector current [20], the effective resistance is a nonlinear function.

Figure 3.8: Transistor array

## 3.4 Controllability advantages of the proposed Technique

According to the equation 3.12 in the section 3.4.2, the array resistance  $R_{ce}$  can be controlled by both  $R_B$  and  $i_x$ . Resistance  $R_B$  operates at high voltage and low current. The current  $i_x$  is a low current due to the low voltage appearing across the base emitter junction of the transistor at all the time. Therefore  $i_x$  is easier to control than  $R_B$ .

## 3.5 Assumptions and their effects

Approximate analysis in this Chapter is carried out assuming the following.

1. Transistor gain  $\beta$  is constant over the entire range of instantaneous voltages occurring on an AC cycle (i.e for 230V AC 0- 230 $\sqrt{2}$ )

- 2. All transistors in the array are identical which is not the case in practical circumstances and that makes the power sharing and voltage sharing unequal.

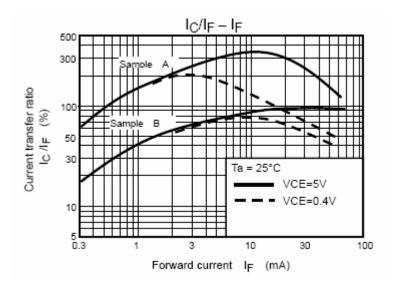

- 3. Variable *p* of the optoisolator current transfer function is considered as a constant but it is variable within in a small range with the diode forward current I<sub>F</sub>. Figure 3.9 shows the nonlinearity of the current transfer ratio of a typical optoisolator such as TLP521-5[22].

Figure 3.9: Current transfer ratio Vs forward current

4. Leakage currents occurring in the transistor (I<sub>CBO</sub>) are neglected but at very high impedance requirements of a load this becomes the significant parameter.

## 3.6 Theoretical approach to correcting the non linear nature of the transistor array

- As shown in Figures 6.13, 6.14, 6.15 in Section 6.4.1 in Chapter 6 transistor array is non-linear and depending on  $V_{CE}$ .

- To correct this problem curve fitting technique was used as detailed in Chapter 6.

## Chapter 4

## **Spice Simulation**

#### 4.1 Simulation Circuits