THE UNIVERSITY OF WAIKATO Research Commons Te Whare Wänanga o Waikato

#### http://waikato.researchgateway.ac.nz/

#### Research Commons at the University of Waikato

#### **Copyright Statement:**

The digital copy of this thesis is protected by the Copyright Act 1994 (New Zealand).

The thesis may be consulted by you, provided you comply with the provisions of the Act and the following conditions of use:

- Any use you make of these documents or images must be for research or private study purposes only, and you may not make them available to any other person.

- Authors control the copyright of their thesis. You will recognise the author's right to be identified as the author of the thesis, and due acknowledgement will be made to the author where appropriate.

- You will obtain the author's permission before publishing any material from the thesis.

# The Design of a CD Transport for Audio Applications

A thesis

submitted in partial fulfilment of the requirements for the Degree of Masters of Engineering in Physics and Electronic Engineering at the University of Waikato

By

## **Carl Dennis Benton**

Te Whare Wananga o Waikato

2006

## ABSTRACT

The project to design a CD transport (CD player) in conjunction with Perreaux Industries came about from the need for a source component in their Silhouette series of products. This project describes the design a high quality CD player, at a low price, to compliment Perreaux's Silhouette series.

A CD drive is selected over a proprietary optical pickup due to the former's low cost and the standardisation of the interface. The control circuitry includes a micro controller and discrete logic to provide the correct data and clock signals to the SPDIF transmitter and DAC circuits. These two circuits provided a high quality analogue output, and facilitate an upgrade path by connecting the SPDIF output to an external DAC.

After three board iterations, a final production ready revision was achieved. The design includes a high quality toroidal transformer, low jitter crystal oscillator, and a very high quality SPDIF pulse transformer output. The design also allows a remote input to control the player, and an optional digital cable via an RJ45 connector to provide synchronisation with a future design of the SXD2 DAC module, or to transmit SPDIF to a remote location.

The specifications of the final design were higher than expectations. The digital output boasts equal or superior performance to competitive products in the same price range, with the analogue output attaining exceptionally high performance.

## **ACKNOWLEDGEMENTS**

There are several parties whom I wish to thank for the opportunity to work on such a quality and educational project. Firstly, my supervisor Dale Carnegie, who has been a mentor to me at the University of Waikato for several years throughout the course of my degree, and who set up both my second work placement and this masters project with Perreaux Industries Ltd. Also despite Dale's relocation to Wellington, he remained my supervisor and worked hard to give me a great deal of attention. I hope Dale and his family enjoy their new life in the capital.

I would also like to thank Martin Van Rooyen, the Managing Director at Perreaux Industries Ltd, for the opportunity to work on the project. Also Clinton Jenson (Design Engineer) for working with me during my time at Perreaux. I wish both of them the best for the future.

I would also like to thank my partner (fiancé at the time of writing this report) Christy Brett for her support and understanding during the time I was working in Dunedin with Perreaux. For the duration of the project Christy remained in Hamilton also working on a master's project, and despite having over 1200 km between us for 8 months, we finished on a high note when we got engaged. I would also like to thank Christy for helping proof read the thesis, and for simply being there. Christy, I love you.

#### DEDICATION

I would like to dedicate this thesis to both my parents for the excellent job they have done over the past 23 years. My Mother is the most understanding woman I know and has always shown an interest in my passion, electronics. My Father introduced me to kit-set construction, which was most likely to stop me from dismantling my electronic toys. However, it is what started the ball rolling, and my Father has always encouraged me to use my full potential.

# **TABLE OF CONTENTS**

| ABSTRACT                         | iii  |

|----------------------------------|------|

| ACKNOWLEDGEMENTS                 | v    |

| TABLE OF CONTENTS                | vii  |

| LIST OF TABLES                   | xi   |

| LIST OF FIGURES                  | xiii |

| 1 INTRODUCTION                   | 1    |

| 1.1 Scope                        | 1    |

| 1.2 Company Overview             | 1    |

| 1.3 The Silhouette Series        | 2    |

| 1.4 Project Requirements         |      |

| 1.5 Thesis Structure             | 4    |

| 2 BACKGROUND                     | 7    |

| 2.1 Competitive Products         | 7    |

| 2.1.1 Cyrus Audio CD 6s          | 7    |

| 2.1.2 Marantz CD5400             | 8    |

| 2.1.3 Cambridge Audio Azur 640C  | 8    |

| 2.1.4 NAD C521BEE                | 9    |

| 2.1.5 Arcam Diva CD73            | 9    |

| 2.1.6 Denon DCD-685              |      |

| 2.1.7 Rotel RCD-1072             |      |

| 2.1.8 Summary                    | 11   |

| 2.2 A NOTE ON HI-FI              |      |

| 2.3 Design Constraints           |      |

| 2.3.1 Costs                      | 12   |

| 2.3.2 Component sourcing         | 13   |

| 2.3.3 System Clock               | 13   |

| 2.4 THE OPTICAL MECHANISM        | 13   |

| 2.5 OTHER BACKGROUND INFORMATION | 14   |

| 2.5.1 The Compact Disc           | 14   |

| 2.5.2 Stream Is Accurate         | 15   |

| 2.5.3 Jitter                                 |    |

|----------------------------------------------|----|

| 2.5.4 Digital Audio Transmission             |    |

| 3 HARDWARE DESCRIPTION                       |    |

| 3.1 Overview                                 |    |

| 3.2 THE ATAPI INTERFACE                      |    |

| 3.3 THE CONTROLLER                           |    |

| 3.4 DIGITAL OUTPUT                           |    |

| 3.4.1 SPDIF Chip                             |    |

| 3.4.2 Output Circuit                         |    |

| 3.5 ANALOGUE OUTPUT                          |    |

| 3.5.1 Digital to Analogue Converter          |    |

| 3.5.2 Output Filter                          |    |

| 3.5.3 Analogue Power Supply                  |    |

| 3.6 INTER CIRCUIT DIGITAL AUDIO TRANSMISSION |    |

| 3.6.1 Serial Formats                         |    |

| 3.6.2 Parallel to Serial Conversion          |    |

| 3.7 CLOCK GENERATION                         |    |

| 3.8 MASTER CLOCK                             |    |

| 3.9 User Interface                           |    |

| 3.10 POWER SUPPLY                            |    |

| 3.10.1 Circuit Overview                      |    |

| 3.10.2 Transformer Rating                    |    |

| 3.10.3 Voltage Regulators                    |    |

| 3.10.4 Filtering                             |    |

| 3.11 Remote Input                            |    |

| 3.12 RJ45 Connector                          |    |

| 3.13 PCB LAYOUT                              |    |

| 3.14 Interconnects                           |    |

| 3.15 DIMENSIONS                              |    |

| 3.16 FRONT PANEL                             |    |

| 4 FIRMWARE DESCRIPTION                       |    |

| 4.1 Overview                                 | 47 |

| 4.1.1 Restrictions                           |    |

| 4.1.2 Interrupt Structure         | . 48 |

|-----------------------------------|------|

| 4.1.3 Nested Interrupts           | . 49 |

| 4.1.4 Code Definitions            | . 50 |

| 4.2 ATAPI INTERFACE               | . 50 |

| 4.2.1 Register Access             | . 51 |

| 4.2.2 Packet Commands             | . 53 |

| 4.3 System Configuration          | . 55 |

| 4.4 Key Processing                | . 56 |

| 4.4.1 Play Key                    | . 57 |

| 4.4.2 Stop Key                    | . 58 |

| 4.4.3 Skip Keys                   | . 58 |

| 4.4.4 Scan Keys                   | . 60 |

| 4.4.5 Eject Key                   | . 62 |

| 4.5 READING THE TABLE OF CONTENTS | . 62 |

| 4.6 AUDIO PLAYBACK                | . 64 |

| 4.6.1 Audio Buffer                | . 65 |

| 4.6.2 Data Setup                  | . 67 |

| 4.6.3 Timing Restrictions         | . 68 |

| 4.6.4 Actual Timing               | . 70 |

| 4.6.5 Current Audio Position      | . 71 |

| 4.6.6 Emphasis Control            | . 72 |

| 4.7 User Interface                | . 73 |

| 4.8 Remote Input                  | . 75 |

| 4.9 The LED                       | . 77 |

| 5 FINAL DESIGN PERFORMANCE        | . 79 |

| 5.1 Physical Construction         | . 79 |

| 5.2 SXCD OPERATION                | . 82 |

| 5.2.1 CD formats                  | . 83 |

| 5.3 METHOD OF MEASUREMENT         | . 85 |

| 5.4 ANALOGUE OUTPUT               | . 88 |

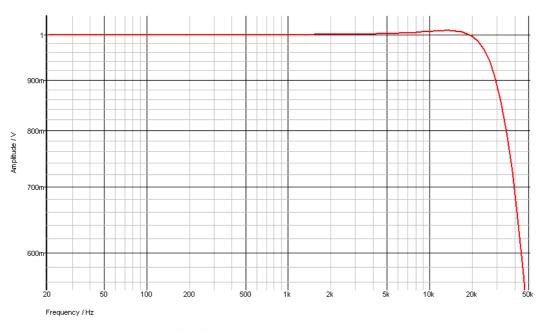

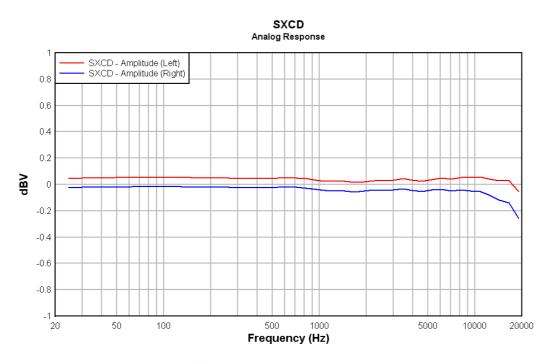

| 5.4.1 Frequency Response          | . 88 |

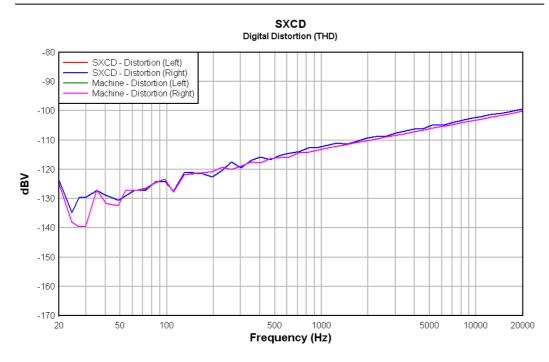

| 5.4.2 Total Harmonic Distortion   | . 89 |

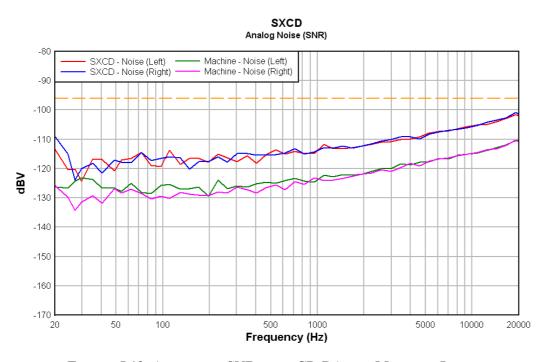

| 5.4.3 Signal to Noise Ratio       | . 90 |

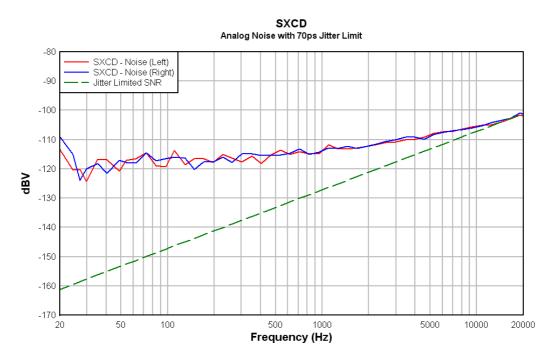

| 5.4.4 Master Clock Jitter         | . 91 |

|                                   |      |

| 5.5 DIGITAL OUTPUT                                                                                                                                                                                                                                      | 93                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 5.5.1 Total Harmonic Distortion                                                                                                                                                                                                                         | 93                                                                        |

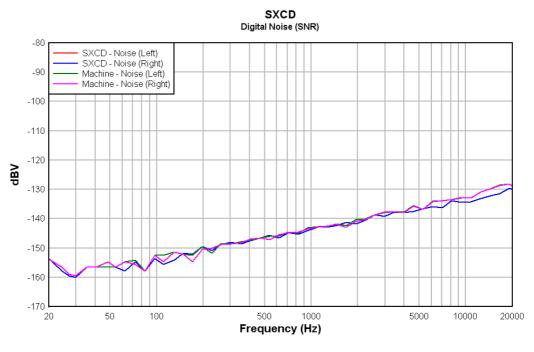

| 5.5.2 Signal to Noise Ratio                                                                                                                                                                                                                             | 94                                                                        |

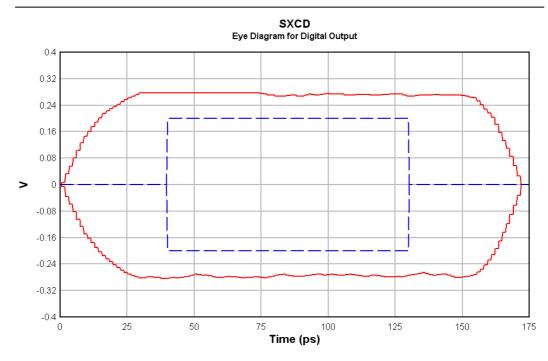

| 5.5.3 Digital Signal Quality                                                                                                                                                                                                                            | 95                                                                        |

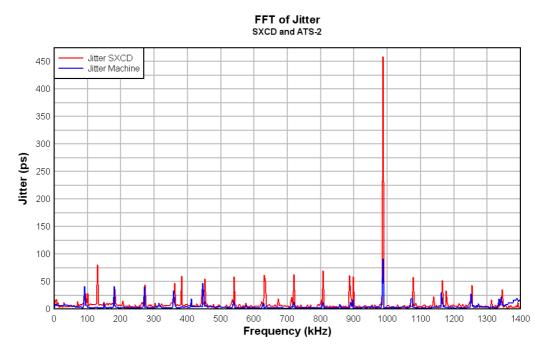

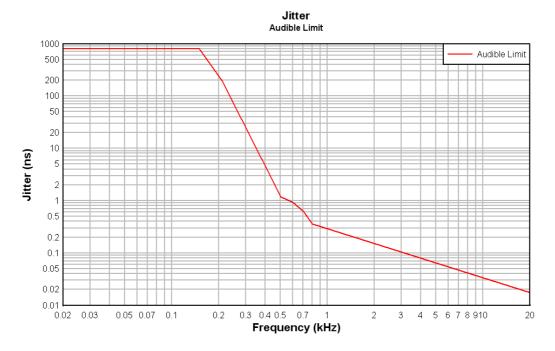

| 5.5.4 Digital Signal Jitter                                                                                                                                                                                                                             | 96                                                                        |

| 6 CONCLUSION                                                                                                                                                                                                                                            | 101                                                                       |

| 6.1 Review                                                                                                                                                                                                                                              | 101                                                                       |

| 6.2 Analysis of Results                                                                                                                                                                                                                                 | 101                                                                       |

| 6.2.1 Signal to Noise Ratio                                                                                                                                                                                                                             | 102                                                                       |

| 6.2.2 Total Harmonic Distortion                                                                                                                                                                                                                         | 102                                                                       |

|                                                                                                                                                                                                                                                         | 103                                                                       |

| 6.2.3 Other Digital Parameters                                                                                                                                                                                                                          |                                                                           |

| <ul><li>6.2.3 Other Digital Parameters</li><li>6.3 CIRCUIT OPERATION</li></ul>                                                                                                                                                                          | 104                                                                       |

|                                                                                                                                                                                                                                                         |                                                                           |

| 6.3 CIRCUIT OPERATION                                                                                                                                                                                                                                   | 105                                                                       |

| 6.3 CIRCUIT OPERATION                                                                                                                                                                                                                                   | 105<br>106                                                                |

| <ul><li>6.3 CIRCUIT OPERATION</li><li>6.4 FUTURE IMPROVEMENTS</li><li>6.5 SUMMARY</li></ul>                                                                                                                                                             | 105<br>106<br>. <b> 109</b>                                               |

| <ul> <li>6.3 CIRCUIT OPERATION</li></ul>                                                                                                                                                                                                                | 105<br>106<br>109<br>113                                                  |

| <ul> <li>6.3 CIRCUIT OPERATION</li> <li>6.4 FUTURE IMPROVEMENTS</li> <li>6.5 SUMMARY</li> <li>7 REFERENCES</li> <li>8 ACRONYMS</li> </ul>                                                                                                               | 105<br>106<br>109<br>113<br>117                                           |

| <ul> <li>6.3 CIRCUIT OPERATION</li> <li>6.4 FUTURE IMPROVEMENTS</li> <li>6.5 SUMMARY</li> <li>7 REFERENCES</li> <li>8 ACRONYMS</li> <li>9 APPENDICES</li> </ul>                                                                                         | 105<br>106<br>109<br>113<br>117<br>117                                    |

| <ul> <li>6.3 CIRCUIT OPERATION</li> <li>6.4 FUTURE IMPROVEMENTS</li> <li>6.5 SUMMARY</li> <li>7 REFERENCES</li> <li>8 ACRONYMS</li> <li>9 APPENDICES</li> <li>9.1 APPENDIX A - PHILIPS L1210 QUOTATION:</li> </ul>                                      | 105<br>106<br>109<br>113<br>117<br>117<br>119                             |

| <ul> <li>6.3 CIRCUIT OPERATION</li> <li>6.4 FUTURE IMPROVEMENTS</li> <li>6.5 SUMMARY</li> <li>7 REFERENCES</li> <li>8 ACRONYMS</li> <li>9 APPENDICES</li> <li>9.1 APPENDIX A - PHILIPS L1210 QUOTATION:</li> <li>9.2 APPENDIX B - SCHEMATICS</li> </ul> | 105<br>106<br>109<br>113<br>117<br>117<br>119<br>119                      |

| <ul> <li>6.3 CIRCUIT OPERATION</li></ul>                                                                                                                                                                                                                | 105<br>106<br>109<br>113<br>113<br>117<br>117<br>119<br>120               |

| <ul> <li>6.3 CIRCUIT OPERATION</li></ul>                                                                                                                                                                                                                | 105<br>106<br>109<br>113<br>113<br>117<br>117<br>119<br>120<br>121        |

| <ul> <li>6.3 CIRCUIT OPERATION</li></ul>                                                                                                                                                                                                                | 105<br>106<br>109<br>113<br>113<br>117<br>117<br>119<br>120<br>121<br>123 |

# LIST OF TABLES

| TABLE 3.1: SUMMARY OF CONTROLLER PIN CONNECTIONS                          | 21 |

|---------------------------------------------------------------------------|----|

| TABLE 3.2: SUMMARY OF REQUIRED CLOCK SIGNALS                              | 32 |

| TABLE 3.3: CD DRIVE CURRENT REQUIREMENTS                                  | 38 |

| TABLE 4.1: LIST OF INTERRUPTS                                             | 49 |

| TABLE 4.2: COMMAND BLOCK REGISTER LIST                                    | 51 |

| TABLE 4.3: PACKET COMMANDS USED BY THE CONTROLLER                         | 54 |

| TABLE 4.4: LEAD IN AREA (TOC), SUB CHANNEL Q FORMATS                      | 63 |

| TABLE 4.5: LEAD IN AREA (TOC) POINT VALUE DESCRIPTIONS                    | 63 |

| TABLE 4.6: LED STATUS SUMMARY                                             | 77 |

| TABLE 5.1: TOC FOR EXAMPLE MIXED MODE CD                                  | 84 |

| TABLE 5.2: TrackInfo Array Contents                                       | 84 |

| TABLE 5.3: LeadoutTrack Array Contents                                    | 84 |

| TABLE 5.4: EXTRACT FROM COLDPLAY X&Y CD TOC                               | 85 |

| TABLE 6.1: COMPARISON FOR THE CD PLAYERS DISCUSSED IN SECTION 2.1       1 | 04 |

# **LIST OF FIGURES**

| FIGURE 1.1: PERREAUX R2001 INTEGRATED AMPLIFIER               | 1  |

|---------------------------------------------------------------|----|

| FIGURE 1.2: THE SILHOUETTE SERIES SX251                       | 2  |

| FIGURE 2.1: CYRUS AUDIO CD6 CD PLAYER                         | 7  |

| FIGURE 2.2: MARANTZ CD5400 CD PLAYER                          | 8  |

| FIGURE 2.3: CAMBRIDGE AUDIO AZUR 640C CD PLAYER               | 9  |

| FIGURE 2.4: NAD C521BEE CD PLAYER                             | 9  |

| FIGURE 2.5: ARCAM DIVA CD73 CD PLAYER                         | 10 |

| FIGURE 2.6: DENON DCD-685 CD PLAYER                           | 10 |

| FIGURE 2.7: ROTEL RCD-1072 CD PLAYER                          | 11 |

| FIGURE 2.8: A JITTERED CLOCK COMPARED WITH AN IDEAL CLOCK     | 16 |

| FIGURE 2.9: THE COMPONENTS OF JITTER                          | 17 |

| FIGURE 3.1: SYSTEM BLOCK DIAGRAM                              | 19 |

| FIGURE 3.2: THE CONTROLLER                                    | 21 |

| FIGURE 3.3: SPDIF OUTPUT CIRCUIT                              | 23 |

| FIGURE 3.4: THEVENIN EQUIVALENT SPDIF OUTPUT                  | 23 |

| FIGURE 3.5: SIMULATED SPDIF SIGNAL (LOADED AND UNLOADED)      | 24 |

| FIGURE 3.6: DAC MFB FILTER                                    | 26 |

| FIGURE 3.7: FILTER RESPONSE TO A STEP INPUT                   | 27 |

| FIGURE 3.8: BUTTERWORTH, BESSEL AND CHEBYSHEV RESPONSE CURVES | 27 |

| FIGURE 3.9: SIMULATED FREQUENCY RESPONSE                      | 28 |

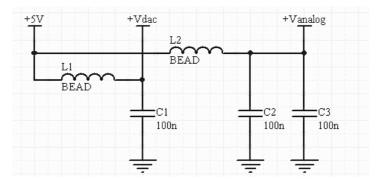

| FIGURE 3.10: ANALOGUE POWER SUPPLY                            | 29 |

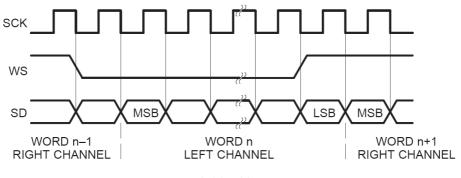

| FIGURE 3.11: I2S FORMAT                                       | 30 |

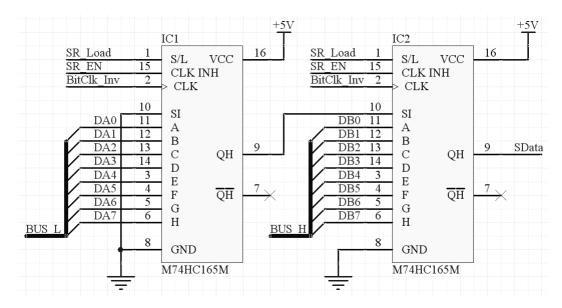

| FIGURE 3.12: SERIAL DATA GENERATION CIRCUIT                   | 31 |

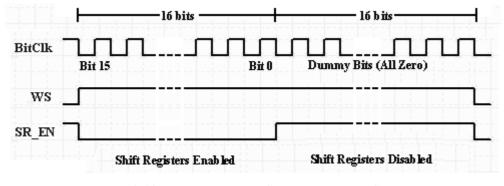

| FIGURE 3.13: TIMING OF THE SHIFT REGISTER SIGNALS             | 32 |

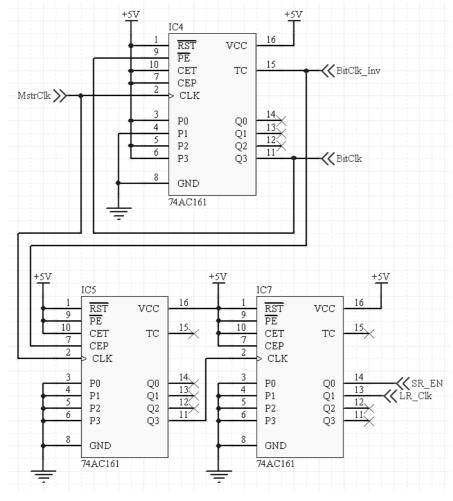

| FIGURE 3.14: CLOCK GENERATION CIRCUIT                         | 33 |

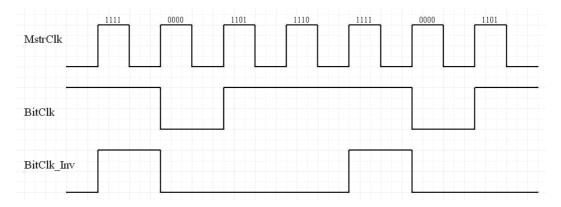

| FIGURE 3.15: BITCLK AND BITCLK_INV PHASE RELATIONSHIP         | 34 |

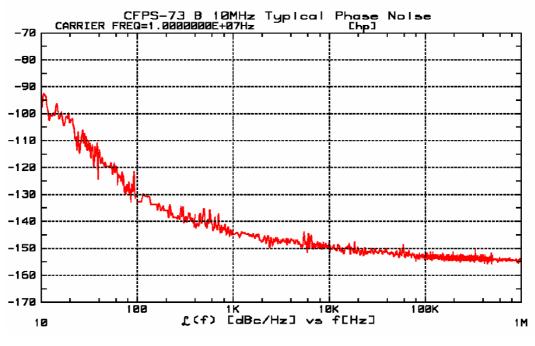

| FIGURE 3.16: PHASE NOISE FOR A 10 MHz CFPS-73                 | 35 |

| FIGURE 3.17: IMAGE OF USER INTERFACE BUTTONS                  | 36 |

| FIGURE 3.18: USER INTERFACE CIRCUIT                           | 36 |

| FIGURE 3.19: POWER SUPPLY CIRCUIT                             | 37 |

| FIGURE 3.20: POWER SUPPLY REGULATOR HEATSINKS                 | 40 |

| FIGURE 3.21: LOCAL L-C FILTERS                                | 40 |

| FIGURE 3.22: A SIMPLE MODULATED SIGNAL                        | 41 |

|---------------------------------------------------------------|----|

| FIGURE 3.23: REMOTE INPUT CIRCUIT                             | 41 |

| FIGURE 3.24: SIMULATED REMOTE IN FOR 5 V AND 12 V SIGNALS     | 42 |

| FIGURE 3.25: RJ45 CONNECTOR CIRCUIT                           | 43 |

| FIGURE 3.26: PCB CIRCUIT OVERLAY                              | 44 |

| FIGURE 3.27: MAIN SUB-CIRCUITS ON THE PCB                     | 44 |

| FIGURE 4.1: FIRMWARE OVERVIEW STATE DIAGRAM                   | 47 |

| FIGURE 4.2: REGISTER READ AND REGISTER WRITE FUNCTIONS        | 52 |

| FIGURE 4.3: ROUTINES TO WAIT FOR A GIVEN STATUS BIT           | 52 |

| FIGURE 4.4: READ WORD FUNCTION                                | 53 |

| FIGURE 4.5: SENDPACKETCOMMAND FUNCTION                        | 54 |

| FIGURE 4.6: PLAY KEY PROCESSING FLOW DIAGRAM                  | 58 |

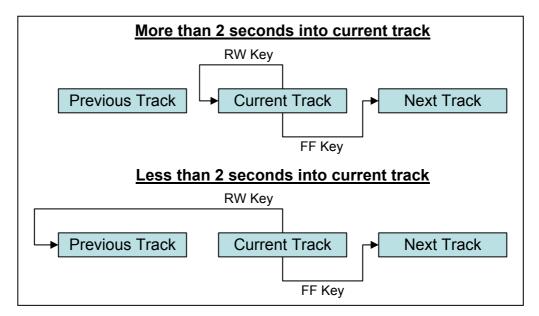

| FIGURE 4.7: FF AND RW KEY FUNCTIONALITY DURING AUDIO PLAYBACK | 59 |

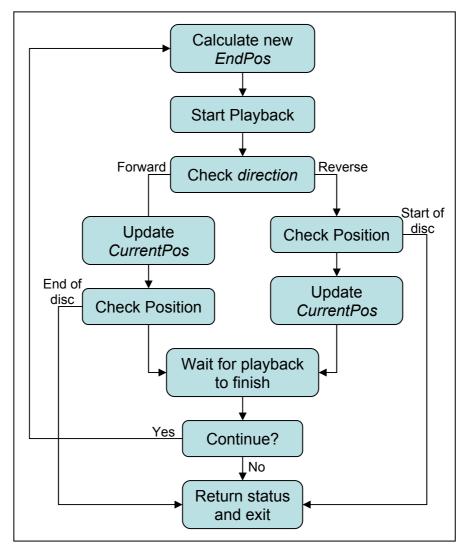

| FIGURE 4.8: SCAN FUNCTION FLOW DIAGRAM                        | 61 |

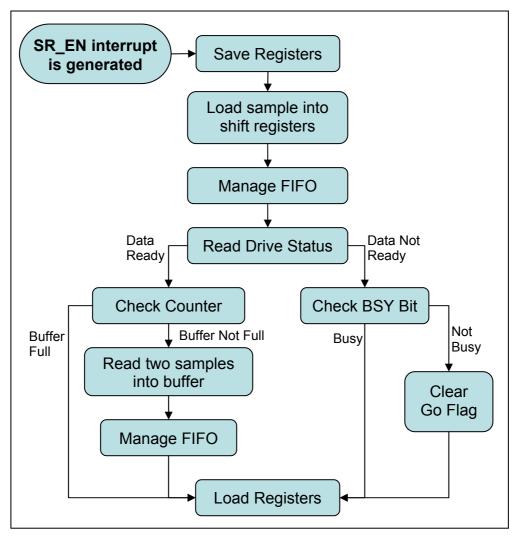

| FIGURE 4.9: PLAY OPERATION STATE DIAGRAM                      | 65 |

| FIGURE 4.10: BUFFER OVERVIEW                                  | 66 |

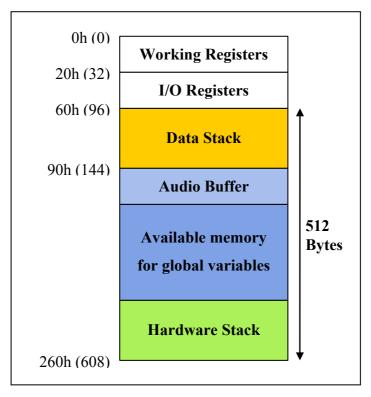

| FIGURE 4.11: CONTROLLER MEMORY ORGANISATION                   | 66 |

| FIGURE 4.12: LOAD SAMPLE CODE IN ASSEMBLY LANGUAGE            | 69 |

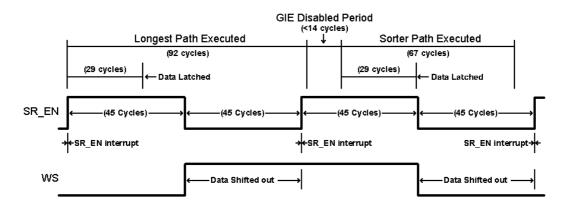

| FIGURE 4.13: SR_EN INTERRUPT WORST CASE TIMING                | 70 |

| FIGURE 4.14: UPDATE EMPHASIS FUNCTION                         | 72 |

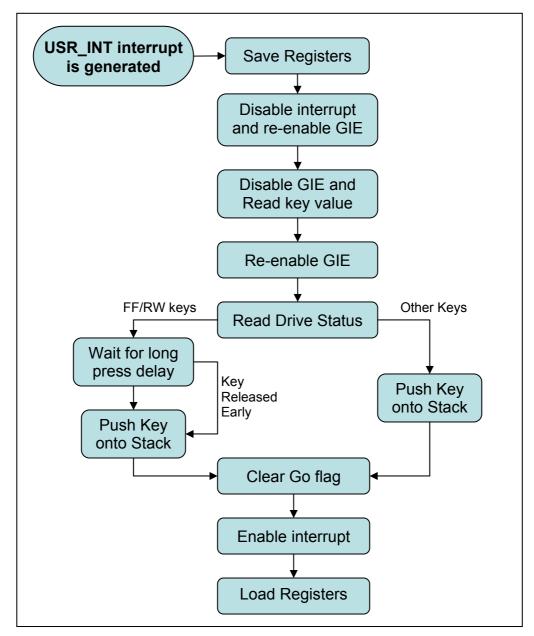

| FIGURE 4.15: USER INTERFACE INTERRUPT ROUTINE STATE DIAGRAM   | 73 |

| FIGURE 4.16: PUSH KEY AND POP KEY FUNCTIONS                   | 75 |

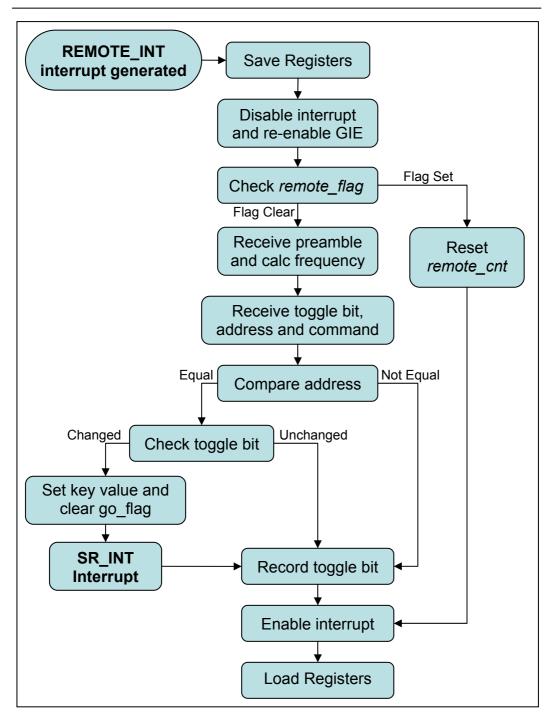

| FIGURE 4.17: REMOTE INPUT INTERRUPT ROUTINE STATE DIAGRAM     | 76 |

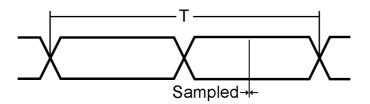

| FIGURE 4.18: SAMPLE LOCATION FOR REMOTE INPUT                 | 77 |

| FIGURE 5.1: PROTOTYPE RUNNING WITH TEMPORARY INTERFACE        | 79 |

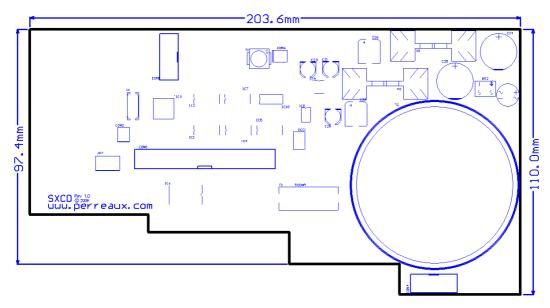

| FIGURE 5.2: PCB OUTLINE AND CRITICAL DIMENSIONS               | 80 |

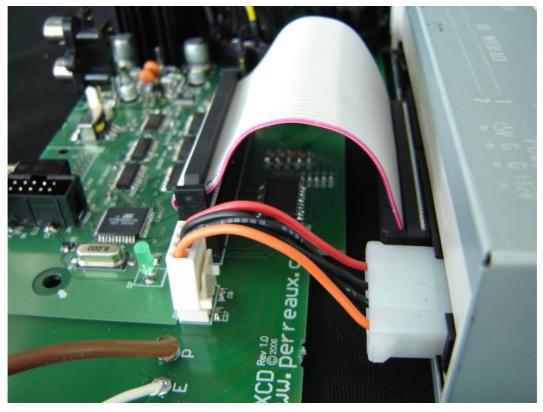

| FIGURE 5.3: CD DRIVE INTERCONNECTS                            | 81 |

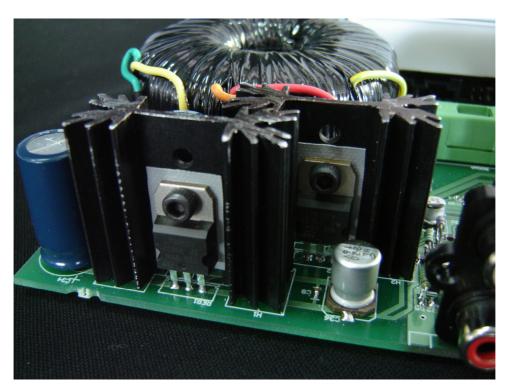

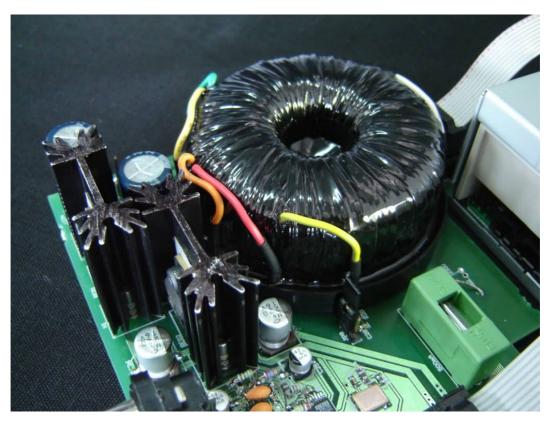

| FIGURE 5.4: COMPLETED POWER SUPPLY                            | 81 |

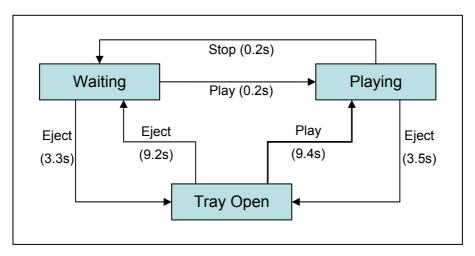

| FIGURE 5.5: SXCD MAIN OPERATION STATE DIAGRAM                 | 82 |

| FIGURE 5.6: SXCD STANDBY STATE DIAGRAM                        | 82 |

| FIGURE 5.7: THE SXCD UNDERGOING TESTS                         | 86 |

| FIGURE 5.8: TYPICAL ATS-2 TEST SETUP                          | 87 |

| FIGURE 5.9: SXCD ATS-2 TEST SETUP                             | 87 |

| FIGURE 5.10: ANALOGUE FREQUENCY RESPONSE                      | 88 |

| FIGURE 5.11: ANALOGUE TOTAL HARMONIC DISTORTION                 | 89 |

|-----------------------------------------------------------------|----|

| FIGURE 5.12: ANALOGUE SNR WITH CD-DA AND MACHINE LIMITS         | 90 |

| FIGURE 5.13: ANALOGUE SNR WITH 70 PS JITTER LIMIT               | 92 |

| FIGURE 5.14: DIGITAL TOTAL HARMONIC DISTORTION                  | 94 |

| FIGURE 5.15: DIGITAL SIGNAL TO NOISE RATIO                      | 95 |

| FIGURE 5.16: EYE DIAGRAM FOR THE DIGITAL OUTPUT SIGNAL          | 96 |

| FIGURE 5.17: FFT OF DIGITAL SIGNAL JITTER, HIGH BANDWIDTH       | 97 |

| FIGURE 5.18: MAXIMUM INAUDIBLE JITTER AMPLITUDES                | 98 |

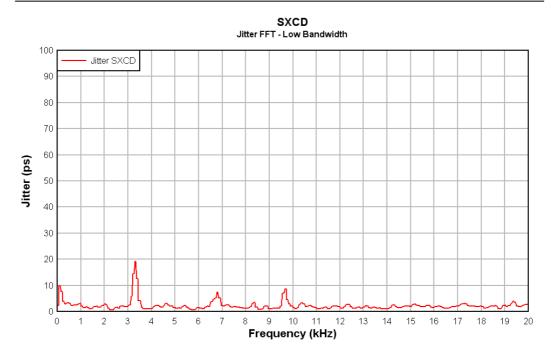

| FIGURE 5.19: FFT OF DIGITAL SIGNAL JITTER, LOW BANDWIDTH        | 99 |

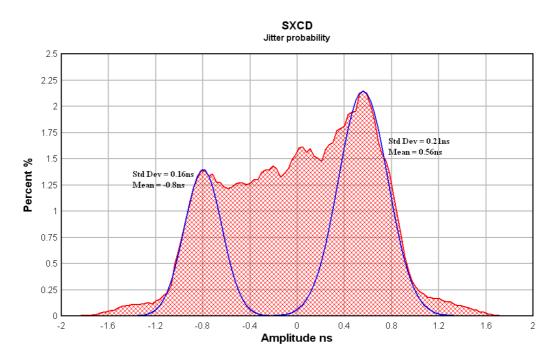

| FIGURE 5.20: PROBABILITY CURVE FOR THE DIGITAL SIGNAL JITTER    | 99 |

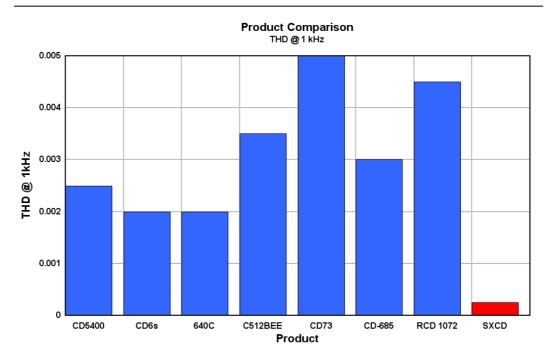

| FIGURE 6.1: A COMPARISON OF COMPETITIVE PRODUCTS ANALOGUE THD 1 | 03 |

| FIGURE 6.2: COMPLETED PROTOTYPE FROM REAR 1                     | 05 |

# The Design of a CD Transport for Audio Applications

A thesis

submitted in partial fulfilment of the requirements for the Degree of Masters of Engineering in Physics and Electronic Engineering at the University of Waikato By

# **Carl Dennis Benton**

THE UNIVERSITY OF WAIKATO Te Whare Wananga o Waikato

## 2006

## ABSTRACT

The project to design a CD transport (CD player) in conjunction with Perreaux Industries came about from the need for a source component in their Silhouette series of products. This project describes the design a high quality CD player, at a low price, to compliment Perreaux's Silhouette series.

A CD drive is selected over a proprietary optical pickup due to the former's low cost and the standardisation of the interface. The control circuitry includes a micro controller and discrete logic to provide the correct data and clock signals to the SPDIF transmitter and DAC circuits. These two circuits provided a high quality analogue output, and facilitate an upgrade path by connecting the SPDIF output to an external DAC.

After three board iterations, a final production ready revision was achieved. The design includes a high quality toroidal transformer, low jitter crystal oscillator, and a very high quality SPDIF pulse transformer output. The design also allows a remote input to control the player, and an optional digital cable via an RJ45 connector to provide synchronisation with a future design of the SXD2 DAC module, or to transmit SPDIF to a remote location.

The specifications of the final design were higher than expectations. The digital output boasts equal or superior performance to competitive products in the same price range, with the analogue output attaining exceptionally high performance.

## ACKNOWLEDGEMENTS

There are several parties whom I wish to thank for the opportunity to work on such a quality and educational project. Firstly, my supervisor Dale Carnegie, who has been a mentor to me at the University of Waikato for several years throughout the course of my degree, and who set up both my second work placement and this masters project with Perreaux Industries Ltd. Also despite Dale's relocation to Wellington, he remained my supervisor and worked hard to give me a great deal of attention. I hope Dale and his family enjoy their new life in the capital.

I would also like to thank Martin Van Rooyen, the Managing Director at Perreaux Industries Ltd, for the opportunity to work on the project. Also Clinton Jenson (Design Engineer) for working with me during my time at Perreaux. I wish both of them the best for the future.

I would also like to thank my partner (fiancé at the time of writing this report) Christy Brett for her support and understanding during the time I was working in Dunedin with Perreaux. For the duration of the project Christy remained in Hamilton also working on a master's project, and despite having over 1200 km between us for 8 months, we finished on a high note when we got engaged. I would also like to thank Christy for helping proof read the thesis, and for simply being there. Christy, I love you.

#### DEDICATION

I would like to dedicate this thesis to both my parents for the excellent job they have done over the past 23 years. My Mother is the most understanding woman I know and has always shown an interest in my passion, electronics. My Father introduced me to kit-set construction, which was most likely to stop me from dismantling my electronic toys. However, it is what started the ball rolling, and my Father has always encouraged me to use my full potential.

# **TABLE OF CONTENTS**

| ABSTRACT                         | iii  |

|----------------------------------|------|

| ACKNOWLEDGEMENTS                 | v    |

| TABLE OF CONTENTS                | vii  |

| LIST OF TABLES                   | xi   |

| LIST OF FIGURES                  | xiii |

| 1 INTRODUCTION                   | 1    |

| 1.1 Scope                        | 1    |

| 1.2 Company Overview             | 1    |

| 1.3 The Silhouette Series        | 2    |

| 1.4 Project Requirements         |      |

| 1.5 Thesis Structure             |      |

| 2 BACKGROUND                     | 7    |

| 2.1 Competitive Products         | 7    |

| 2.1.1 Cyrus Audio CD 6s          |      |

| 2.1.2 Marantz CD5400             |      |

| 2.1.3 Cambridge Audio Azur 640C  |      |

| 2.1.4 NAD C521BEE                | 9    |

| 2.1.5 Arcam Diva CD73            | 9    |

| 2.1.6 Denon DCD-685              |      |

| 2.1.7 Rotel RCD-1072             |      |

| 2.1.8 Summary                    |      |

| 2.2 A NOTE ON HI-FI              |      |

| 2.3 DESIGN CONSTRAINTS           |      |

| 2.3.1 Costs                      |      |

| 2.3.2 Component sourcing         |      |

| 2.3.3 System Clock               |      |

| 2.4 THE OPTICAL MECHANISM        |      |

| 2.5 OTHER BACKGROUND INFORMATION |      |

| 2.5.1 The Compact Disc           |      |

| 2.5.2 Stream Is Accurate         |      |

| 2.5.3 Jitter                                 | 16 |

|----------------------------------------------|----|

| 2.5.4 Digital Audio Transmission             | 17 |

| 3 HARDWARE DESCRIPTION                       |    |

| 3.1 OVERVIEW                                 | 19 |

| 3.2 THE ATAPI INTERFACE                      |    |

| 3.3 THE CONTROLLER                           |    |

| 3.4 DIGITAL OUTPUT                           |    |

| 3.4.1 SPDIF Chip                             |    |

| 3.4.2 Output Circuit                         |    |

| 3.5 ANALOGUE OUTPUT                          |    |

| 3.5.1 Digital to Analogue Converter          |    |

| 3.5.2 Output Filter                          |    |

| 3.5.3 Analogue Power Supply                  |    |

| 3.6 INTER CIRCUIT DIGITAL AUDIO TRANSMISSION |    |

| 3.6.1 Serial Formats                         |    |

| 3.6.2 Parallel to Serial Conversion          |    |

| 3.7 CLOCK GENERATION                         |    |

| 3.8 MASTER CLOCK                             |    |

| 3.9 User Interface                           |    |

| 3.10 POWER SUPPLY                            |    |

| 3.10.1 Circuit Overview                      |    |

| 3.10.2 Transformer Rating                    |    |

| 3.10.3 Voltage Regulators                    |    |

| 3.10.4 Filtering                             |    |

| 3.11 Remote Input                            | 41 |

| 3.12 RJ45 Connector                          |    |

| 3.13 PCB LAYOUT                              |    |

| 3.14 Interconnects                           |    |

| 3.15 DIMENSIONS                              |    |

| 3.16 FRONT PANEL                             | 46 |

| 4 FIRMWARE DESCRIPTION                       |    |

| 4.1 Overview                                 | 47 |

| 4.1.1 Restrictions                           |    |

| 4.1.2 Interrupt Structure         | 48 |

|-----------------------------------|----|

| 4.1.3 Nested Interrupts           | 49 |

| 4.1.4 Code Definitions            | 50 |

| 4.2 ATAPI INTERFACE               | 50 |

| 4.2.1 Register Access             | 51 |

| 4.2.2 Packet Commands             | 53 |

| 4.3 System Configuration          | 55 |

| 4.4 Key Processing                | 56 |

| 4.4.1 Play Key                    | 57 |

| 4.4.2 Stop Key                    | 58 |

| 4.4.3 Skip Keys                   | 58 |

| 4.4.4 Scan Keys                   | 60 |

| 4.4.5 Eject Key                   | 62 |

| 4.5 READING THE TABLE OF CONTENTS | 62 |

| 4.6 AUDIO PLAYBACK                | 64 |

| 4.6.1 Audio Buffer                | 65 |

| 4.6.2 Data Setup                  | 67 |

| 4.6.3 Timing Restrictions         | 68 |

| 4.6.4 Actual Timing               | 70 |

| 4.6.5 Current Audio Position      | 71 |

| 4.6.6 Emphasis Control            | 72 |

| 4.7 User Interface                | 73 |

| 4.8 Remote Input                  | 75 |

| 4.9 The LED                       | 77 |

| 5 FINAL DESIGN PERFORMANCE        | 79 |

| 5.1 Physical Construction         | 79 |

| 5.2 SXCD OPERATION                | 82 |

| 5.2.1 CD formats                  | 83 |

| 5.3 METHOD OF MEASUREMENT         | 85 |

| 5.4 ANALOGUE OUTPUT               | 88 |

| 5.4.1 Frequency Response          | 88 |

| 5.4.2 Total Harmonic Distortion   | 89 |

| 5.4.3 Signal to Noise Ratio       | 90 |

| 5.4.4 Master Clock Jitter         | 91 |

|                                   |    |

| 5.5 DIGITAL OUTPUT                        |  |

|-------------------------------------------|--|

| 5.5.1 Total Harmonic Distortion           |  |

| 5.5.2 Signal to Noise Ratio               |  |

| 5.5.3 Digital Signal Quality              |  |

| 5.5.4 Digital Signal Jitter               |  |

| 6 CONCLUSION                              |  |

| 6.1 Review                                |  |

| 6.2 ANALYSIS OF RESULTS                   |  |

| 6.2.1 Signal to Noise Ratio               |  |

| 6.2.2 Total Harmonic Distortion           |  |

| 6.2.3 Other Digital Parameters            |  |

| 6.3 CIRCUIT OPERATION                     |  |

| 6.4 FUTURE IMPROVEMENTS                   |  |

| 6.5 SUMMARY                               |  |

| 7 REFERENCES                              |  |

| 8 ACRONYMS                                |  |

| 9 APPENDICES                              |  |

| 9.1 APPENDIX A - PHILIPS L1210 QUOTATION: |  |

| 9.2 Appendix B - Schematics               |  |

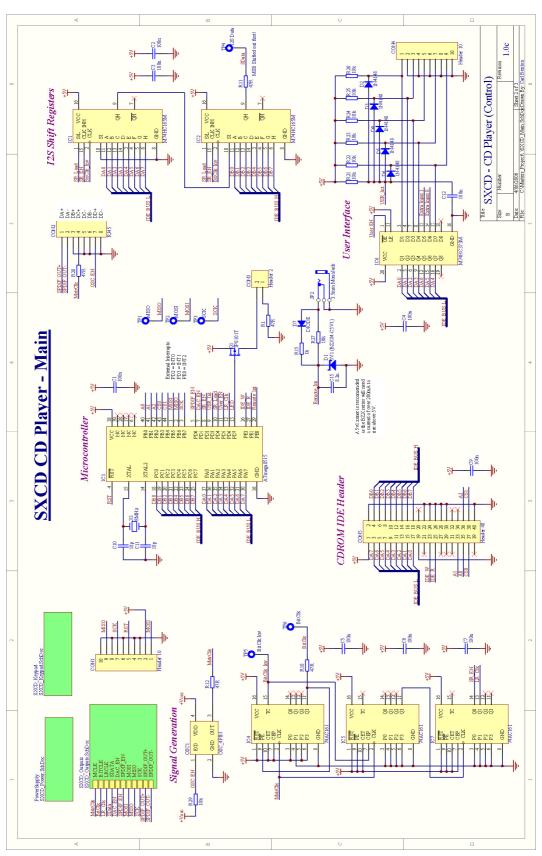

| 9.2.1 Main Schematic                      |  |

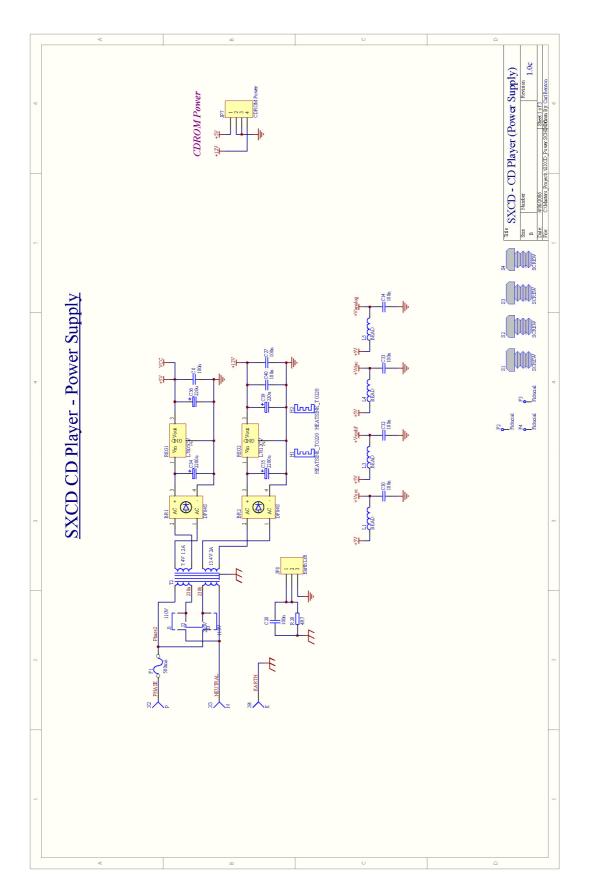

| 9.2.2 Power Supply                        |  |

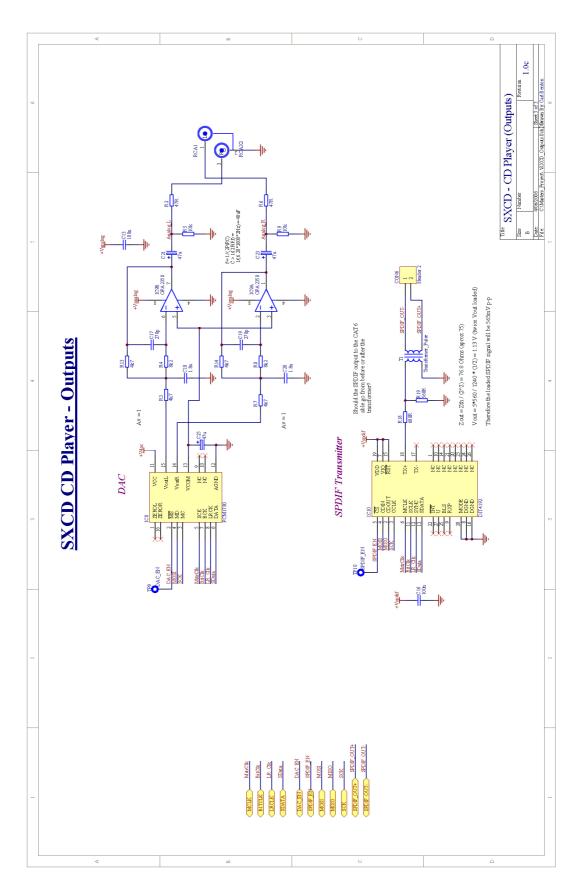

| 9.2.3 Outputs                             |  |

| 9.3 Appendix C – PCB Layout               |  |

| 9.4 APPENDIX D – LETTER OF RECOMMENDATION |  |

| 9.5 Appendix E – Project CD Contents      |  |

# LIST OF TABLES

| TABLE 3.1: SUMMARY OF CONTROLLER PIN CONNECTIONS                  | 21  |

|-------------------------------------------------------------------|-----|

| TABLE 3.2: SUMMARY OF REQUIRED CLOCK SIGNALS                      | 32  |

| TABLE 3.3: CD DRIVE CURRENT REQUIREMENTS                          | 38  |

| TABLE 4.1: LIST OF INTERRUPTS                                     | 49  |

| TABLE 4.2: COMMAND BLOCK REGISTER LIST                            | 51  |

| TABLE 4.3: PACKET COMMANDS USED BY THE CONTROLLER                 | 54  |

| TABLE 4.4: LEAD IN AREA (TOC), SUB CHANNEL Q FORMATS              | 63  |

| TABLE 4.5: LEAD IN AREA (TOC) POINT VALUE DESCRIPTIONS            | 63  |

| TABLE 4.6: LED STATUS SUMMARY                                     | 77  |

| TABLE 5.1: TOC FOR EXAMPLE MIXED MODE CD                          | 84  |

| TABLE 5.2: TrackInfo Array Contents                               | 84  |

| TABLE 5.3: LeadoutTrack Array Contents                            | 84  |

| TABLE 5.4: EXTRACT FROM COLDPLAY X&Y CD TOC                       | 85  |

| TABLE 6.1: COMPARISON FOR THE CD PLAYERS DISCUSSED IN SECTION 2.1 | 104 |

# **LIST OF FIGURES**

| FIGURE 1.1: PERREAUX R2001 INTEGRATED AMPLIFIER               | 1    |

|---------------------------------------------------------------|------|

| FIGURE 1.2: THE SILHOUETTE SERIES SX251                       | 2    |

| FIGURE 2.1: CYRUS AUDIO CD6 CD PLAYER                         | 7    |

| FIGURE 2.2: MARANTZ CD5400 CD PLAYER                          | 8    |

| FIGURE 2.3: CAMBRIDGE AUDIO AZUR 640C CD PLAYER               | 9    |

| FIGURE 2.4: NAD C521BEE CD PLAYER                             | 9    |

| FIGURE 2.5: ARCAM DIVA CD73 CD PLAYER                         | . 10 |

| FIGURE 2.6: DENON DCD-685 CD PLAYER                           | . 10 |

| FIGURE 2.7: ROTEL RCD-1072 CD PLAYER                          | . 11 |

| FIGURE 2.8: A JITTERED CLOCK COMPARED WITH AN IDEAL CLOCK     | . 16 |

| FIGURE 2.9: THE COMPONENTS OF JITTER                          | . 17 |

| FIGURE 3.1: SYSTEM BLOCK DIAGRAM                              | . 19 |

| FIGURE 3.2: THE CONTROLLER                                    | . 21 |

| FIGURE 3.3: SPDIF OUTPUT CIRCUIT                              | . 23 |

| FIGURE 3.4: THEVENIN EQUIVALENT SPDIF OUTPUT                  | . 23 |

| FIGURE 3.5: SIMULATED SPDIF SIGNAL (LOADED AND UNLOADED)      | . 24 |

| FIGURE 3.6: DAC MFB FILTER                                    | . 26 |

| FIGURE 3.7: FILTER RESPONSE TO A STEP INPUT                   | . 27 |

| FIGURE 3.8: BUTTERWORTH, BESSEL AND CHEBYSHEV RESPONSE CURVES | . 27 |

| FIGURE 3.9: SIMULATED FREQUENCY RESPONSE                      | . 28 |

| FIGURE 3.10: ANALOGUE POWER SUPPLY                            | . 29 |

| FIGURE 3.11: I2S FORMAT                                       | . 30 |

| FIGURE 3.12: SERIAL DATA GENERATION CIRCUIT                   | . 31 |

| FIGURE 3.13: TIMING OF THE SHIFT REGISTER SIGNALS             | . 32 |

| FIGURE 3.14: CLOCK GENERATION CIRCUIT                         | . 33 |

| FIGURE 3.15: BITCLK AND BITCLK_INV PHASE RELATIONSHIP         | . 34 |

| FIGURE 3.16: PHASE NOISE FOR A 10 MHz CFPS-73                 | . 35 |

| FIGURE 3.17: IMAGE OF USER INTERFACE BUTTONS                  | . 36 |

| FIGURE 3.18: USER INTERFACE CIRCUIT                           | . 36 |

| FIGURE 3.19: POWER SUPPLY CIRCUIT                             | . 37 |

| FIGURE 3.20: POWER SUPPLY REGULATOR HEATSINKS                 | . 40 |

| FIGURE 3.21: LOCAL L-C FILTERS                                | . 40 |

| FIGURE 3.22: A SIMPLE MODULATED SIGNAL                        | 41 |

|---------------------------------------------------------------|----|

| FIGURE 3.23: REMOTE INPUT CIRCUIT                             | 41 |

| FIGURE 3.24: SIMULATED REMOTE IN FOR 5 V AND 12 V SIGNALS     | 42 |

| FIGURE 3.25: RJ45 CONNECTOR CIRCUIT                           | 43 |

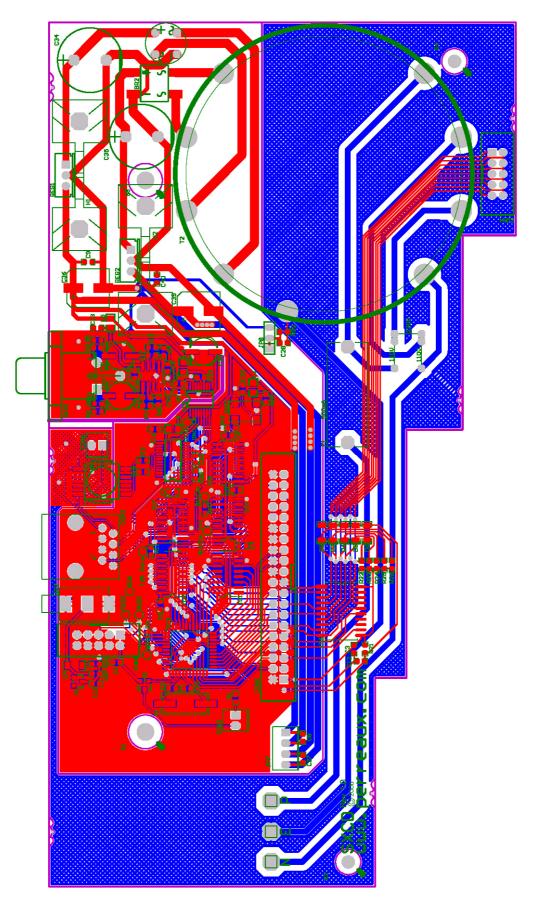

| FIGURE 3.26: PCB CIRCUIT OVERLAY                              | 44 |

| FIGURE 3.27: MAIN SUB-CIRCUITS ON THE PCB                     | 44 |

| FIGURE 4.1: FIRMWARE OVERVIEW STATE DIAGRAM                   | 47 |

| FIGURE 4.2: REGISTER READ AND REGISTER WRITE FUNCTIONS        | 52 |

| FIGURE 4.3: ROUTINES TO WAIT FOR A GIVEN STATUS BIT           | 52 |

| FIGURE 4.4: READ WORD FUNCTION                                | 53 |

| FIGURE 4.5: SENDPACKETCOMMAND FUNCTION                        | 54 |

| FIGURE 4.6: PLAY KEY PROCESSING FLOW DIAGRAM                  | 58 |

| FIGURE 4.7: FF AND RW KEY FUNCTIONALITY DURING AUDIO PLAYBACK | 59 |

| FIGURE 4.8: SCAN FUNCTION FLOW DIAGRAM                        | 61 |

| FIGURE 4.9: PLAY OPERATION STATE DIAGRAM                      | 65 |

| FIGURE 4.10: BUFFER OVERVIEW                                  | 66 |

| FIGURE 4.11: CONTROLLER MEMORY ORGANISATION                   | 66 |

| FIGURE 4.12: LOAD SAMPLE CODE IN ASSEMBLY LANGUAGE            | 69 |

| FIGURE 4.13: SR_EN INTERRUPT WORST CASE TIMING                | 70 |

| FIGURE 4.14: UPDATE EMPHASIS FUNCTION                         | 72 |

| FIGURE 4.15: USER INTERFACE INTERRUPT ROUTINE STATE DIAGRAM   | 73 |

| FIGURE 4.16: PUSH KEY AND POP KEY FUNCTIONS                   | 75 |

| FIGURE 4.17: REMOTE INPUT INTERRUPT ROUTINE STATE DIAGRAM     | 76 |

| FIGURE 4.18: SAMPLE LOCATION FOR REMOTE INPUT                 | 77 |

| FIGURE 5.1: PROTOTYPE RUNNING WITH TEMPORARY INTERFACE        | 79 |

| FIGURE 5.2: PCB OUTLINE AND CRITICAL DIMENSIONS               | 80 |

| FIGURE 5.3: CD DRIVE INTERCONNECTS                            | 81 |

| FIGURE 5.4: COMPLETED POWER SUPPLY                            | 81 |

| FIGURE 5.5: SXCD MAIN OPERATION STATE DIAGRAM                 | 82 |

| FIGURE 5.6: SXCD STANDBY STATE DIAGRAM                        | 82 |

| FIGURE 5.7: THE SXCD UNDERGOING TESTS                         | 86 |

| FIGURE 5.8: TYPICAL ATS-2 TEST SETUP                          | 87 |

| FIGURE 5.9: SXCD ATS-2 TEST SETUP                             | 87 |

| FIGURE 5.10: ANALOGUE FREQUENCY RESPONSE                      | 88 |

| FIGURE 5.11: ANALOGUE TOTAL HARMONIC DISTORTION               | 89  |

|---------------------------------------------------------------|-----|

| FIGURE 5.12: ANALOGUE SNR WITH CD-DA AND MACHINE LIMITS       | 90  |

| FIGURE 5.13: ANALOGUE SNR WITH 70 PS JITTER LIMIT             | 92  |

| FIGURE 5.14: DIGITAL TOTAL HARMONIC DISTORTION                | 94  |

| FIGURE 5.15: DIGITAL SIGNAL TO NOISE RATIO                    | 95  |

| FIGURE 5.16: EYE DIAGRAM FOR THE DIGITAL OUTPUT SIGNAL        | 96  |

| FIGURE 5.17: FFT OF DIGITAL SIGNAL JITTER, HIGH BANDWIDTH     | 97  |

| FIGURE 5.18: MAXIMUM INAUDIBLE JITTER AMPLITUDES              | 98  |

| FIGURE 5.19: FFT OF DIGITAL SIGNAL JITTER, LOW BANDWIDTH      | 99  |

| FIGURE 5.20: PROBABILITY CURVE FOR THE DIGITAL SIGNAL JITTER  | 99  |

| FIGURE 6.1: A COMPARISON OF COMPETITIVE PRODUCTS ANALOGUE THD | 103 |

| FIGURE 6.2: COMPLETED PROTOTYPE FROM REAR                     | 105 |

## **1** INTRODUCTION

### **1.1 SCOPE**

The project is developed in conjunction with Perreaux Industries Limited [1], a high-fidelity audio company, who design and produce leading edge audio products. The newest edition to Perreaux's product range is the Silhouette series, a range of products targeted at consumers looking in the lower price ranges, or for smaller units. The goal of this project is to design a high quality CD player (the SXCD) for the Silhouette series. Because the series does not currently include a CD player, this project will complete the series and offer a complete system solution to the customer.

### **1.2 COMPANY OVERVIEW**

Perreaux is a manufacturer of hi-fi audio amplifiers, preamplifiers, CD players and other hi-fi audio equipment. A fine example of a Perreaux product is the R200i 200 W integrated amplifier shown in Figure 1.1.

FIGURE 1.1: PERREAUX R2001 INTEGRATED AMPLIFIER

The company originated in Nelson in 1974 where it quickly gained a reputation for building highly reliable and well constructed amplifiers. In 1976 Perreaux built the first NZ made large PA system which was capable of outputting 900 W RMS. The company expanded, moving to MOSFET technology in 1979 and entering the export market in the early 1980's. The first preamplifier (the SM2) was introduced in 1983, and by 1985 Perreaux was exporting by the container load (mainly to the USA) and at its peak was producing over 20 units a day. In 1991 the factory was relocated to Auckland where the company embarked in further research, releasing a number of new products including the Silhouette range of entry-level products. Perreaux moved to Dunedin in 2005 and continues to invest in research and design, increasing the quality and range of their products. To this day the mission of Perreaux is the perfect re-creation of a musical event.

## **1.3 THE SILHOUETTE SERIES**

The Silhouette series of products [2] has been designed to be a range of high quality, yet affordable, modules to either complement an existing system, or to be a starting point for a new hi-fi enthusiast. Currently the series includes a headphone amplifier (SXH2), a line stage buffer (SXL2), a 25 W stereo integrated amplifier (SX25i) shown in Figure 1.2, and a digital to analogue converter (DAC) with both USB connectivity (SXD2).

FIGURE 1.2: THE SILHOUETTE SERIES SX25I

A 60 W mono-block amplifier is currently being designed, which originates from the design of the SX25i, and is intended to provide a higher power solution for customers wishing to run larger speakers. To provide volume control functionality with the mono-block amplifiers, a passive preamplifier is also being developed. Both of these products will be released shortly.

The goal of the SXCD CD Player is to complete the system, allowing users to match it with an SX25i for a simple system, upgrade it with the SXD2, or expand it with the mono-blocks or line stage buffer for improved performance in sound. When the SXCD is made available, many system configurations would be possible to suit a large array of situations ranging from a computer based office setup to a small lounge stereo system.

## **1.4 PROJECT REQUIREMENTS**

The requirements for the SXCD project were set out by Perreaux as a list of features that must be implemented on the design. The list is as follows:

- A high quality (0.001 % THD or less) SPDIF output for connectivity to the SXD2 or alternative DAC module.

- A moderate quality (0.003 % THD or less) analogue output for stand alone operation.

- A simple method to load a CD into the device.

- A simple user interface on the front and a remote input connection on the back.

- Fit into the current Silhouette series look, feel, and (preferably) size.

The target price for the SXCD is in the range of \$800-\$1200, and it is envisioned that it will compete with products in the market that are priced below \$2000. Perreaux have taken a minimalist approach with the Silhouette series, creating products that are simple to use and are physically (and visually) free from clutter. To continue this theme (and due to size and cost constraints) it is decided that no display will be used on the front panel.

All the current Silhouette products are the same size, being 45 mm high, 210 mm wide and 150 mm deep with the same base front panel design. It is important that the SXCD continues this trend with the same front panel dimensions.

The aesthetic aspects of the final product do have an effect on this project since the dimensions are constrained and hence component selection and placement must conform to these limitations. However, the aesthetic aspects themselves (such as chassis and front panel design) are not part of the project requirements as they are handled by other designers within Perreaux.

## **1.5 THESIS STRUCTURE**

Chapter One, **Introduction**, gives an overview of the project, while introducing Perreaux Industries Ltd and the Silhouette series. The project requirements are outlined as provided by Perreaux, and an outline of the thesis structure is given.

Chapter Two, **Background**, provides information on various competitive products that are currently in the target market of the SXCD. These products are considered in terms of both their technical performance and operation, and are summarised to obtain an idea on what is desirable in the current market. The inspiration behind using a CD drive instead of a proprietary optical pickup is discussed and also information on technologies that are directly related to the SXCD project are described such as the compact disc, clock jitter and the SPDIF digital audio format.

Chapter Three, **Hardware Description**, gives a detailed description of the hardware aspects involved in designing the project. The circuit design can be divided into separate functions or sub-circuits. The chapter is broken down into sections, where each section focuses on one of these sub-circuits.

Chapter Four, **Firmware Description**, details the operation of the firmware which is programmed into the microcontroller. The chapter describes how the controller functions, along with the limitations and problems encountered throughout the project and how these were overcome. Each aspect of the firmware is described at an operational level and, where relevant, code fragments are provided.

Chapter Five, **Final Design Performance**, presents the results obtained from the final revision of the SXCD. The operation of the CD player in terms of its response speed is measured, and the measurement equipment available at Perreaux is used to obtain the performance results for both the analogue and digital outputs.

Chapter Six, **Conclusion**, summarises the SXCD's specifications and compares them with the products which were outlined in Chapter Two. The final performance of the project is discussed reflecting on the initial requirements set at the beginning of the project. Future improvements are considered and the project as a whole is summarised and the thesis concludes with a comment from the managing director of Perreaux Industries Ltd.

# **2** BACKGROUND

## **2.1 COMPETITIVE PRODUCTS**

As part of any new product design process, one must investigate the range of competitive products currently on the market to gain an idea on how a new product must perform in order to be successful. Details from several competitive products that fall into the lower price range (of below \$2000) are given below where the products are compared in both their specifications and overall performance.

#### 2.1.1 CYRUS AUDIO CD 6s

The Cyrus Audio CD 6 CD Player [3], as shown in Figure 2.1, retails for around NZ\$2200. Although it is a bit more expensive than the target price range, it provides some competition due to its compact size and simplistic nature. The design includes quality components and eight regulated power supplies. The chassis is built with metal components on all six sides to create an electrical faraday cage and protect internal circuitry from stray interference. Cyrus also acknowledges the need for an accurate clock and therefore includes a remote re-clocking circuit at the DAC stage.

FIGURE 2.1: CYRUS AUDIO CD6 CD PLAYER

The CD 6 boasts specifications of 0.002 % Total Harmonic Distortion (THD) at 1 kHz, a Signal to Noise ratio (SNR) of -110 dB, and clock jitter of less than 100 ps. The unit includes an SPDIF optical output, a custom LCD display, a

24-bit current output DAC and a Cyrus system remote control, but does not support CDRW discs.

#### 2.1.2 MARANTZ CD5400

The Marantz CD5400 [4], shown in Figure 2.2, retails for around NZ\$599, and although it is an older product in the market it still gets reviews as late as 2005 [5]. For a CD player at such a low price it is popular due to its looks and sound quality. It offers numerous features such as CD-Text compatibility, both optical and coaxial digital outputs, a headphone output with volume control, and several different playback options. The specifications state a 0.0025 % THD (although the frequency is not given), a signal to noise ratio of -110 dB, and a frequency range of 20 Hz - 20 kHz (however the deviation is not stated).

FIGURE 2.2: MARANTZ CD5400 CD PLAYER

#### 2.1.3 CAMBRIDGE AUDIO AZUR 640C

The Cambridge Audio Azur series is relatively new as it was introduced in 2003. The product to compare is the 640C CD player [6] (shown in Figure 2.3), retails for around NZ\$899 and has been considered as the world's best budget CD player [6]. The chassis is completely made from metal, with a solid aluminium front panel that is matched with an aluminium faced remote control. On the 640C product page at Cambridge Audio's website, it boasts a completely separate power supply and upgraded audio filter and regulator stages, with the whole system housed on an acoustically damped chassis.

The analogue stage incorporates a WM8740 24-bit 192 kHz DAC from Wolfson. The frequency response has a 1 dB ripple across the audio band, the THD is reasonable at 0.002 % at 1 kHz, the SNR is -100 dB and the jitter is stated as

being below 260 ps. This overall performance has however been classed as one of the best for the product range that the Azur 640C sits in.

FIGURE 2.3: CAMBRIDGE AUDIO AZUR 640C CD PLAYER

## 2.1.4 NAD C521BEE

The NAD C521BEE [7] (shown in Figure 2.4) is another low cost CD player retailing at around NZ\$499 where the player has been designed to sit at the "sweet spot" in terms of price and performance. It is housed in a full unit size chassis and includes an EL backlit display, a remote control, a coaxial digital output and an analogue output. The design includes a digital output transformer, separate analogue and digital power supplies and high grade components, although only a 20-bit DAC is used. As far as the specifications go, the THD is 0.0035 % at 1 kHz, the SNR ratio is -108 dB, the frequency response of 5 Hz – 20 kHz deviates less than 0.5 dB, and NAD also mentions the CIRC error correction that is built into audio CD's.

FIGURE 2.4: NAD C521BEE CD PLAYER

## 2.1.5 ARCAM DIVA CD73

The CD73 is the entry-level Diva CD player from Arcam and retails for around NZ\$1499. It features an LED display, 20-track program memory and supports CD text and most CD-R and CD-RW discs. It also includes both optical and coaxial digital outputs as well as two pairs of line level analogue outputs, and comes with

a custom designed remote control. Internally it utilises the WM8740 24-bit Sigma Delta DAC chip from Wolfson Electronics and a carefully designed master clock to provide low jitter (although a jitter figure is not provided). Arcam states figures for THD of 0.005 % and a SNR of -112 dB.

FIGURE 2.5: ARCAM DIVA CD73 CD PLAYER

## 2.1.6 DENON DCD-685

The DCD-685 from Denon is shown in Figure 2.6 and retails for around NZ\$699. It features an LED display with dimmer function, pitch control, a remote control, headphone output and an optical digital output. It supports CD-R and CD-RW discs and includes one of the PCM1702 20-bit 2-DAC chips from Burr-Brown on each audio channel. The specifications state an SNR of -110 dB and a THD of 0.003 % at 1 kHz. It also states a frequency response of 20 Hz to 20 kHz, however no deviation figure is stated.

FIGURE 2.6: DENON DCD-685 CD PLAYER

## 2.1.7 ROTEL RCD-1072

The RCD-1072 from Rotel retails for around NZ\$1495. The front of the unit is silver aluminium (with black handles at each side) and has a centre mounted CD tray. It features an LED display and a selection of buttons for various features

such as random, repeat and track programming. It also includes a remote control, a 12 V trigger, and both analogue and digital coaxial outputs.

FIGURE 2.7: ROTEL RCD-1072 CD PLAYER

The analog output uses an 18-bit equivalent sigma delta DAC, which is stated as the PCM-1732 from Burr-Brown. However, details on this part cannot be found on the manufacturer website. The specifications include a frequency response of 20 Hz to 20 kHz within a deviation of 0.5 dB, a SNR of -100 dB, and THD of 0.0045 % at 1 kHz.

#### 2.1.8 SUMMARY

Looking at these products it is apparent that in the Hi-Fi market, it is important to produce a product that not only sounds good, but is also aesthetically pleasing. Unfortunately, comparing each of the products on how well they sound is not easy, so the construction and specifications become the primary focus. Many of these products include a display to show track and time information. A remote control is commonly included, and an optical output is not necessary. Several different types of DAC chips are used in these products, ranging from a 20-bit 2-DAC high precision DAC, to a 24-bit Sigma Delta DAC configuration.

Some of the products include re-clocking circuitry to reduce jitter at the internal DAC stage; however it would be better to minimise the jitter at the clock source instead. A jitter figure of less than a few hundred picoseconds seems to be accepted as high quality. To gain an advantage in this area, a value of less than 100 ps would be desirable.

It is also apparent that many of the products do not provide all the specifications. Usually the reason for doing so is because the specifications are either not so good, or are not obtainable with the company's available resources. The products state similar specifications with an average of 0.003 % THD at 1 kHz and a SNR of around -107 dB. Only four stated a deviation in frequency response, with the average being 0.6 dB. It is important to provide all the relevant specifications, especially when stating that a large amount of work has been invested in a particular design area. Making such statements without backing them up with the facts can have a negative effect if the buyer is somewhat technically inclined.

# 2.2 A NOTE ON HI-FI

It is important to note at this stage that as an electronic engineer, a product's performance is typically determined by its specifications. However, in the Hi-Fi realm, it is not this simple, and can be somewhat reversed with better "performance" gained from a product with lower "specifications". This is because the term performance is synonymous to a customer's tastes and a reviewer's preferences in audio sound. A reviewer typically uses words such as "open", "warm", "clean", "grainy" and "momentum" to describe the sound of a product, yet it is very hard to connect such words to a product's specifications. For a CD player proving perfect specifications such as zero distortion (THD) and jitter, infinite dynamic range and a perfectly flat frequency response etc., one would *expect* it to sound the most natural and unimpaired. Therefore, this is what is aimed for in the design of the SXCD.

# **2.3 DESIGN CONSTRAINTS**

### **2.3.1 COSTS**

Because this project is to be an entry level product in the Silhouette range, component costs need be kept to a minimum without compromising the performance of the design. This however, is not difficult and through careful component selection and circuit design both the component count and costs can be minimised.

#### **2.3.2 COMPONENT SOURCING**

When designing a product for a small company with a relatively low turnover one must be aware of higher production costs due to lower buying power and restrictions from a supplier's minimum order quantity. In this situation, costs can be reduced by both reusing components from existing products and including fewer component types in more areas of the design. This is one of the main issues that is dealt with in this project, and largely influences the component selection.

#### **2.3.3 System Clock**

The system clock in a CD player is the most critical component in order to minimise timing errors such as jitter and frequency stability. A poor clock can compromise the performance of the whole system, and must be chosen carefully.

## **2.4 THE OPTICAL MECHANISM**

There are three possible solutions for the optical pickup. The first is to use a mechanism solution which does not include the control circuitry for the CD mechanism, the second is the use of a pre-assembled module with simple control and data interface, while the third is to use an existing computer CD drive and interface it to provide the necessary functionality.

A raw CD mechanism contains only the basic mechanical and optical components involved in reading the data from a CD, and requires the controller circuitry and motor drivers to be included into the design. This approach is only a viable solution if the designer is willing to design the control circuit themselves, and is not an option for this project due to limited design time, budget, and the adopted "why re-invent the wheel" approach.

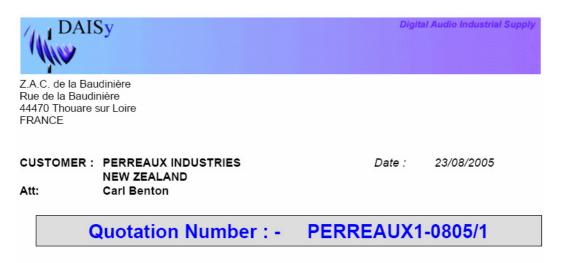

The majority of CD players available today use a CD mechanism module designed for audio applications. Such a module consists of the CD mechanism and the control circuitry in one unit where the control circuitry handles the low level control of the motors and laser and communicates through a simple interface such as the DSA interface used in the Philips L1210 module from Daisy Laser [8].

Although this solution is definitely viable in terms of the mechanical and electrical complexity of the design, the cost and production aspects are not so favourable. Daisy quoted a price of US\$43.85 for 240+ pieces for this L1210 module, and given the project's budget and the fact that these modules tend to change on occasion, this is not an ideal option.

It is therefore decided that the project will be designed around an ordinary computer CD drive such as a CDROM drive or CD Writer. These are well established optical devices used in computer applications for extracting both data and digital audio from CD media. Since the CD drive is a widely used device and is mass produced, they can be obtained for very little cost compared to the mechanisms available. They are also constructed according to the physical dimensions stated in the ATA specification and all use a well established ATAPI interface (see Section 3.2) which is an industry standard and will remain unchanged long into the future. This makes them an extremely attractive solution for a tight budgeted, low volume product. There are other advantages to using a CD drive over a mechanism module, such as a potentially higher quality of audio and versatility of CD formats as they are compatible with all forms of CD's including CDROM, CDR and CDRW. Therefore, any disc that a computer with a CD drive can read is compatible.

# **2.5 OTHER BACKGROUND INFORMATION**

#### **2.5.1 THE COMPACT DISC**

All data on a compact disc (CD) are stored in a single spiral track of pits representing logic ones and zeros. These pits are approximately  $0.5 \,\mu\text{m}$  wide and the pitch between adjacent spirals is  $1.6 \,\mu\text{m}$ . The spiral runs from the centre, to the outside of the disc, with a length of around 5 km over its 20,000 revolutions. The data are extracted using a laser to generate an 'eye pattern' and the reflected beam is then read by the optical pick up (OPU) and decoded using a CD decoder to create a stream of binary information.

Data errors are decoded and corrected using a well known Cross-Interleaved Reed-Solomon Code (CIRC) algorithm contained in the information, thus ensuring a reliable data stream. This CIRC information is added to the data when the disc is created. Other information is also included in the bit stream such as position and data type. All this information is stored in a sub-channel byte on each frame, where each bit is assigned to each of the eight sub-channels, designated P, Q, R, S, T, U, V, and W. Spanning over a total of 192 frames, each of these subchannels make up a 24 byte field. The only sub-channel of use here is the Q subchannel (called Sub-Q) as it contains information such as the Minute Seconds Frame (MSF) address (see below), the track index and the control field.

A CD containing digital audio (CD-DA), contains data at a sampled rate of 44.1 kHz using 16 bits per sample, corresponding to a data rate of 176.4 kB/s. All data are stored in frames of 2352 bytes in size, where on an audio disc this is entirely CDDA data, corresponding to a rate of 75 frames per second. Each frame is made up of 98 small frames, each containing 24 bytes of data, and for each of these small frames, 588 bits are stored on the CD (the extra bits contain the CIRC and sub-channel information). Therefore a 70 minute, 700 MB, audio CD will actually hold 2.1 GB of information.

When accessing a CD there are two different address formats to use. The Logical Block Address (LBA) format defines the addressing mode of the drive by the linear mapping of the sectors from 0 to n. An LBA address is 4-bytes long which can represent a total of over 4294 million sectors. The second is the MSF format which is expressed as a sector count relative to either the beginning of the CD (absolute) or the beginning of the current track (relative). The format is made up of 3 fields, an F field unit is one frame (also called a sector), an S field unit is one second and is 75 F field units, and an M field unit is one minute and is 60 S field units. An absolute MSF address corresponds to a location on the CD as M minutes, S seconds, and F frames from the start of the CD, and can be as high as 99 minutes, 59 seconds, and 74 frames.

#### **2.5.2 STREAM IS ACCURATE**

The structure of the data on a CD is arranged in blocks of 2352 bytes of information where for data CD's this block contains 2048 bytes of user data. The rest of the sector is used for a synchronisation field, sector address tag and an

auxiliary field. In the case of a CD-DA disc however, the entire 2352 bytes of the sector contains audio data and therefore there is no header information. For this reason, if streaming of the data is interrupted and must restart where it was stopped there will be an error in where the drive starts streaming again. This error could be as much as one second due to the uncertainty of the address. If the drive supports the CD-DA Stream-Is-Accurate capability then it contains the necessary circuitry to overcome this error and therefore there will only be a delay due to rotational latency. Fortunately, all modern drives include this functionality and therefore this should not be a problem in the SXCD design.

#### **2.5.3 JITTER**

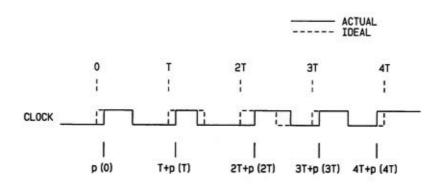

In a digital system, data transmission is robust and information is generally sent and received without any loss of data. The problem of jitter only arises in the ADC or DAC stages where each sample must be converted at a specific time. Jitter is the time variation in the sample clock used in an ADC or DAC and causes samples to be converted at a time other than the ideal. In a typical CD player, jitter is present in both the master clock driving the on-board DAC stage, and the digital output signal. Figure 2.8 shows this jitter on five successive edges where 'p' is the individual time variation of the actual clock signal from the ideal.

FIGURE 2.8: A JITTERED CLOCK COMPARED WITH AN IDEAL CLOCK.

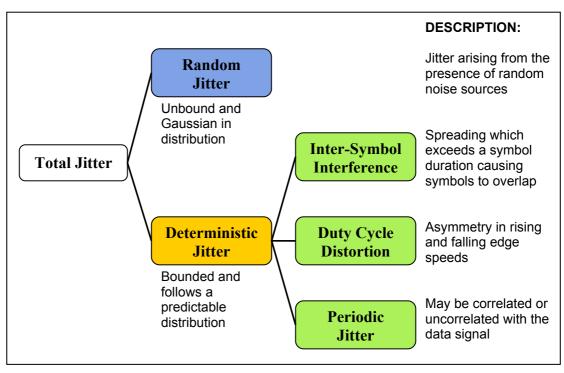

Total jitter comprises two main types: deterministic jitter and random jitter as shown in Figure 2.9. Random jitter is independent of frequency and is characterised by a Gaussian distribution. It is caused by many noise sources such as thermal noise, power supply noise or noise caused by semiconductor process anomalies.

FIGURE 2.9: THE COMPONENTS OF JITTER

Deterministic jitter is bounded in amplitude and is not analysed statistically. It can be broken down into three types: periodic jitter, duty cycle distortion, and inter-symbol interference. Periodic jitter has a signature that repeats at a fixed frequency, and can be caused by sources such as EMI radiation from power supplies, AC power lines and RF signal sources. Duty cycle distortion is the result of asymmetries in clock cycles, and can be caused by differences in rise and fall times and threshold variations of a device. Inter-symbol interference is the variation of each bit width, and can be caused by improper termination or bandwidth limitations. Duty cycle distortion and inter-symbol interference are types of data dependant jitter, where the timing errors are dependant on the data pattern itself.

## **2.5.4 DIGITAL AUDIO TRANSMISSION**

In the high-end audio market, the SPDIF format is used to transmit digital audio between hi-fi audio components. SPDIF is an acronym for Sony Philips Digital Interface and is the consumer version of the AES3 interface [9] used in professional equipment. SPDIF is commonly transmitted over a coaxial cable with either BNC or RCA interconnects, but sometimes an optical connection is used, and although it has become the standard interface in the hi-fi industry, it is far from ideal. The SPDIF format transmits both the digital data and the clock over a single wire using bi-phase mark encoding, and is susceptible to timing errors such as jitter that corrupt the digital to analogue conversion stage. In a typical system, the DAC circuitry will regenerate a clock signal based on the data stream received and is therefore running as a slave to the CD player. A system that removes jitter much more effectively is called master mode [10], where the master clock is directly driving the DAC stage with the CD player running as a slave to the DAC. In this situation, the timing errors between the CD player and DAC are completely eliminated, although this requires a clock signal to be transmitted separately.

# **3 HARDWARE DESCRIPTION**

## **3.1 OVERVIEW**

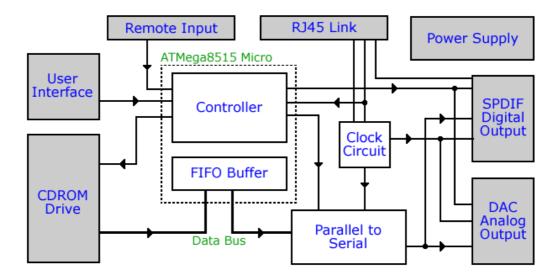

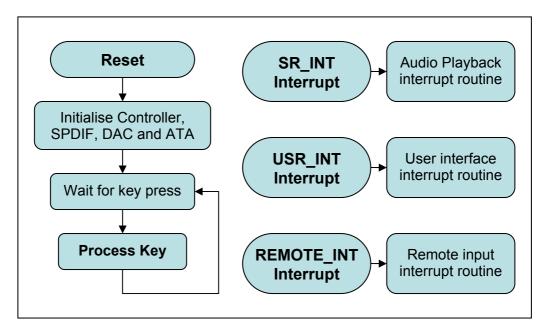

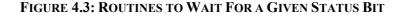

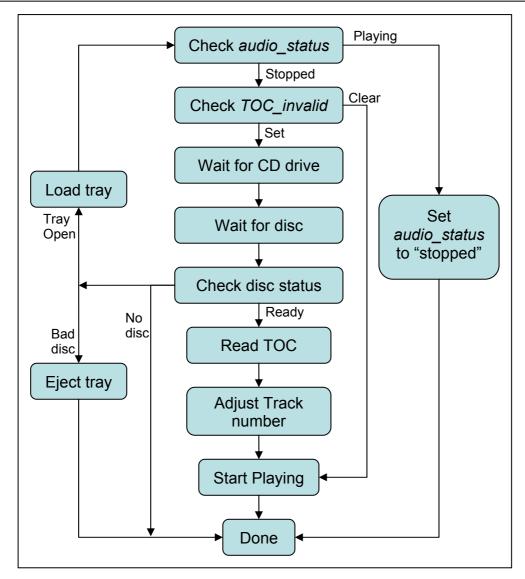

The complete system can be broken down into sub-circuits, where each sub-circuit deals with a separate function, and is synchronised to a master clock. Each sub-circuit in the system, along with their corresponding connections, is shown in the block diagram in Figure 3.1. At the heart of the system is the controller, an ATmega8515 microcontroller, which runs the firmware responsible for operating the system. There are two output circuits, one being the SPDIF output based around a digital audio transmitter chip, and the other an analogue output based around a DAC chip. Both of these are driven by a serial data transmission generated by the clock and parallel to serial circuitry. The user interface, CD drive and remote input are directly interfaced to the controller, and an RJ45 Link is available to either receive a master clock, or transmit a SPDIF signal when the need for this functionality arises. Each sub-circuit, along with other hardware aspects of the design, are described in detail in the following sections.

FIGURE 3.1: SYSTEM BLOCK DIAGRAM

# **3.2 THE ATAPI INTERFACE**

The AT Attachment (ATA) interface has been developed for over 10 years and was originally only designed to work with hard disc drives for storage. As the use of multimedia expanded and CD drives became widely used, there was a need for an enhanced protocol, and so the ATA Packet Interface (ATAPI) was developed. This ATAPI protocol consists of a Packet Command feature set and is used to provide extra commands that are not included in the ATA specification to interface removable media drives such as CD/DVD drives, tape drives and ZIP drives. Physically the ATA interface consists of a 16-bit data bus, a 5-bit address bus, a read line and a write line. Other signals are available on the interface such as a Reset line, Interrupt, DMA Acknowledge, DMA Request, IO Ready and Cable Select but are not required, nor connected to the controller in this project. The operation of the ATAPI interface is discussed in detail in Section 4.2.

## **3.3 THE CONTROLLER**

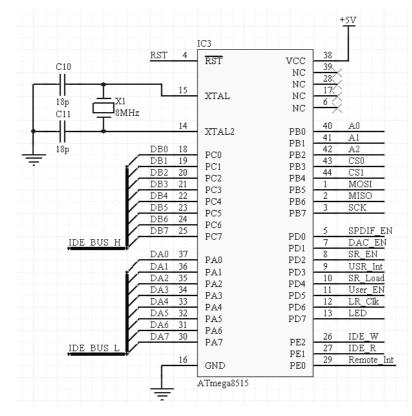

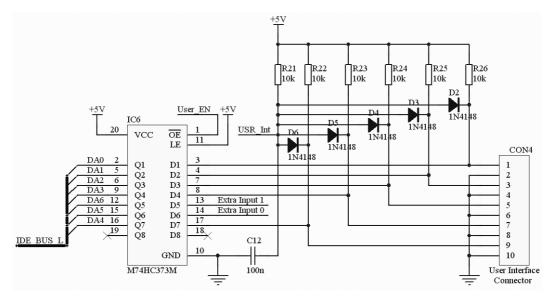

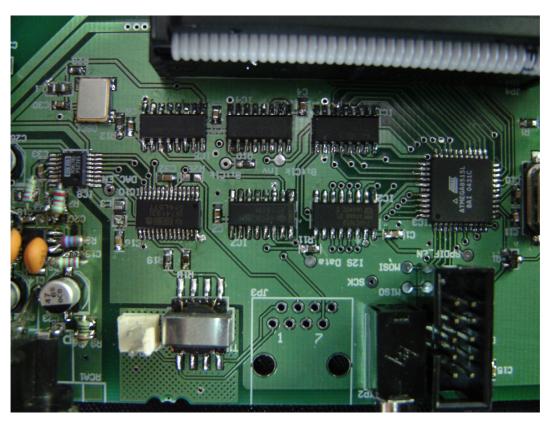

The ATmega8515L [11] microcontroller from Atmel was chosen simply because Perreaux currently uses Atmel parts, and the ATmega8515L is already a stocked component. The ATmega8515L is an 8-bit microcontroller based on the AVR enhanced RISC architecture and is the low power version of the ATmega8515. It features 8 Kbytes of Flash, 512 Kbytes of EEPROM, 512 bytes of SRAM, 35 general purpose I/O lines, 32 general purpose working registers and many other features such as counters, USART, SPI interface and interrupts. Instructions are executed in a single clock cycle resulting in a throughput of 1 MIPS per MHz. Running at the maximum speed of 8 MHz gives an instruction execution time of 125 ns. Of the 35 general purpose I/O lines, 16 are used for the data bus, 7 to control the ATA interface, 5 for the SPI port, 3 for the serial data generation, 2 for the user interface, 1 for the remote input, and 1 for driving the LED. These connections are shown on the schematic diagram of the controller in Figure 3.2 and are summarised in Table 3.1.

FIGURE 3.2: THE CONTROLLER

| Function:              | Number of Pins: | Pin Numbers:  |  |

|------------------------|-----------------|---------------|--|

| Data Bus               | 16              | 18-25, 30-37  |  |

| ATA Control Lines      | 7               | 26, 27, 40-44 |  |

| SPI Port               | 5               | 1-3, 5, 7     |  |

| Serial Data Generation | 3               | 8, 10, 12     |  |

| User Interface         | 2               | 9, 11         |  |

| Remote Input           | 1               | 29            |  |

| LED                    | 1               | 13            |  |

**TABLE 3.1: SUMMARY OF CONTROLLER PIN CONNECTIONS**

The three external interrupts are located on pins PD2, PD3 and PE0 (pins 8, 9 and 29 respectively) and are connected in this particular order deliberately to provide the correct interrupt structure. This is because the ATmega8515 interrupt priorities are fixed, with the INT0 (PD2) the highest and INT2 (PE0) the lowest, resulting in a *SR\_EN* interrupt having the highest priority, and a remote input interrupt having the lowest. More details on the interrupt structure are provided in section 0. The ATA address lines (pins 40-44) must be connected to port B because they need to be written to in the same manner as a complete data bus. This is possible because the upper three bits are used for the SPI port and are not affected by write operations to the pins themselves. The remaining pins are connected simply to reduce routing complexity on the final circuit board.

# **3.4 DIGITAL OUTPUT**

A digital output is required to provide high quality audio transmission for connecting to a high quality external DAC module such as the Perreaux SXD2. Because the SPDIF format has become an industry standard, it must be used in order for the digital output to be compatible with the various external DAC modules currently on the market. There are many digital audio transmitter chips available that transmit SPDIF and accept a range of serial digital audio interfaces, which helps to simplify the design.

### **3.4.1 SPDIF CHIP**

A few digital audio transmitter chips were investigated including the AK4103 from AKM, the CS8406 from Cirrus Logic and the DIT4192 from Texas Instruments. Each chip provides a different package size and range of features such as the range of master clock and bit clock frequencies the chip will accept, however all of them provide the functionality required by the system. The DIT4192 [12] from Texas Instruments was therefore chosen primarily for its good pricing and availability.

The DIT4192 is designed for both professional and consumer operation, and contains a single differential line driver output. It also runs from a single supply voltage of 5 V and is available in a TSSOP-28 package. Although the chip can be used with sampling frequencies up to 192 kHz, it is fixed at 44.1 kHz in the SXCD system due to the CD-DA format. The chip is configured for software operation, where it is connected directly to the controller via an SPI interface. This provides flexibility for future upgrades and control over the transmitted user data.

#### **3.4.2 OUTPUT CIRCUIT**

In order to provide isolation and short circuit protection to the SPDIF output circuitry, an output transformer is included. The transformer must be a high quality pulse transformer for digital transmission to keep jitter and signal distortion to a minimum. There are a few manufacturers who provide such pulse transformers, yet the SC982 from Scientific Conversion [13] is chosen for their good reputation (also note [14]) and optimised design for SPDIF applications between 32 and 192 kHz. The SC982 has a turns ratio of 1:2, which can be used in reverse to halve the signal voltage. It also has a very low leakage inductance, and is available in a surface mount package.

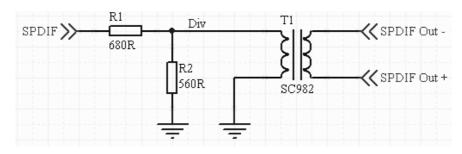

FIGURE 3.3: SPDIF OUTPUT CIRCUIT

There are two requirements of the output circuit: first it must meet the SPDIF specification [15] for an output voltage of 400 mV – 600 mV p-p, and second it must be matched to the required line impedance of a 75  $\Omega$  cable. To satisfy both these requirements from a supply voltage of 5 V and a 2:1 transformer ratio, a voltage divider is included to produce the final output circuit shown in Figure 3.3, which is a common unbalanced SPDIF configuration [16].

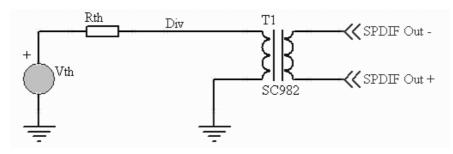

FIGURE 3.4: THEVENIN EQUIVALENT SPDIF OUTPUT

In this configuration a Thevenin equivalent circuit exists on the primary side of the transformer, as shown in Figure 3.4, where the Thevenin resistance ( $R_{th}$ ) is given by the parallel combination of R1 and R2, and the Thevenin voltage is given by the voltage divider created by R1 and R2. It shows that if  $R_{th}$  is matched to the transformer primary impedance when the secondary is under load, the

voltage present at the transformer will be half the unloaded voltage, and that  $V_{th}$  is the same as the SPDIF signal voltage of 5 V.

$$R_{th} = Z_P = Z_S \left(\frac{N_P}{N_S}\right)^2$$

Equation 3-1

$$V_{out} = \frac{N_s}{N_P} V_{th} \frac{R_2}{R_1 + R_2}$$

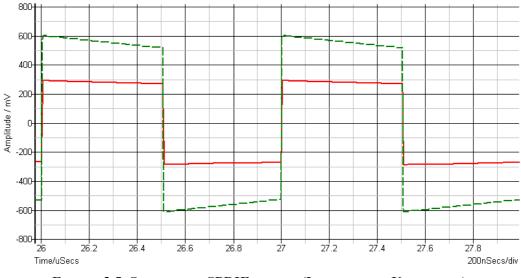

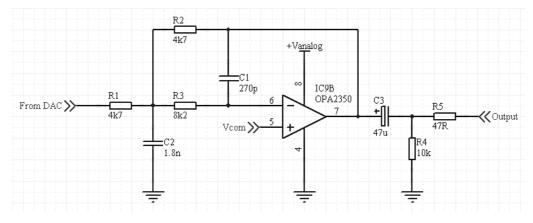

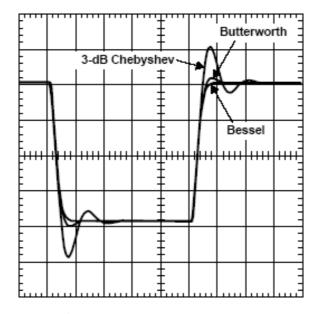

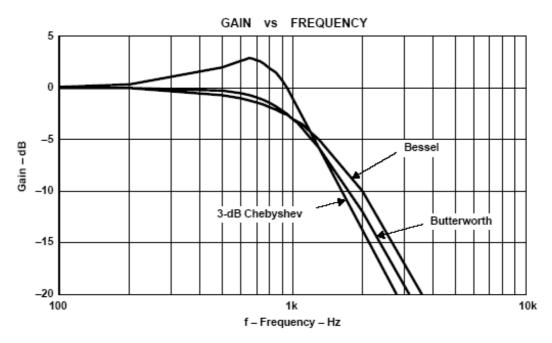

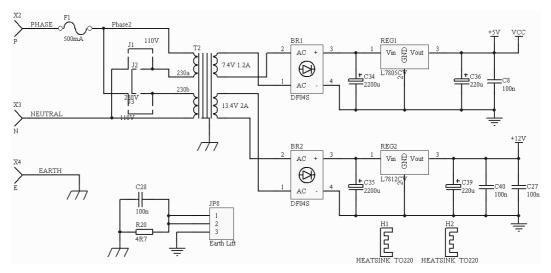

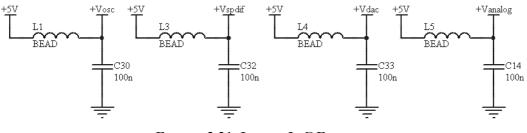

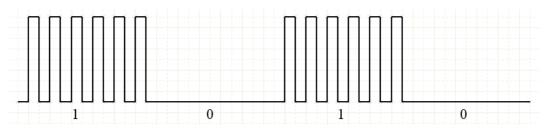

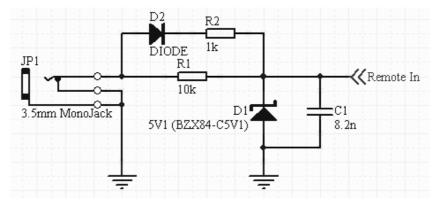

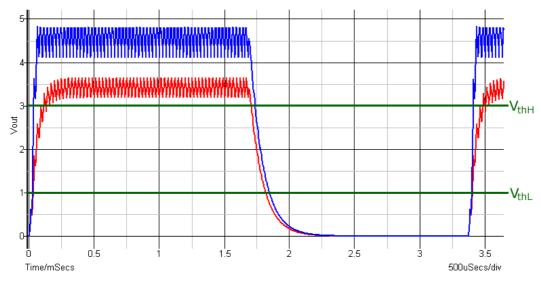

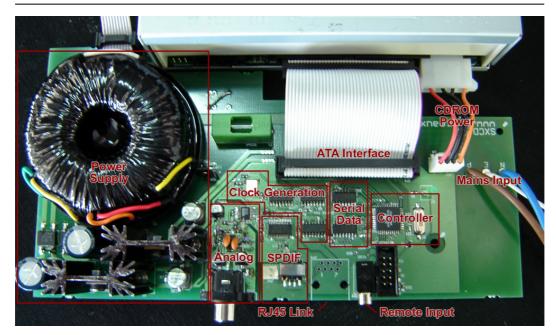

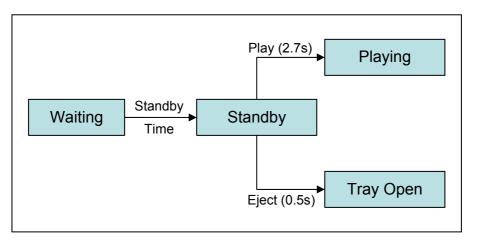

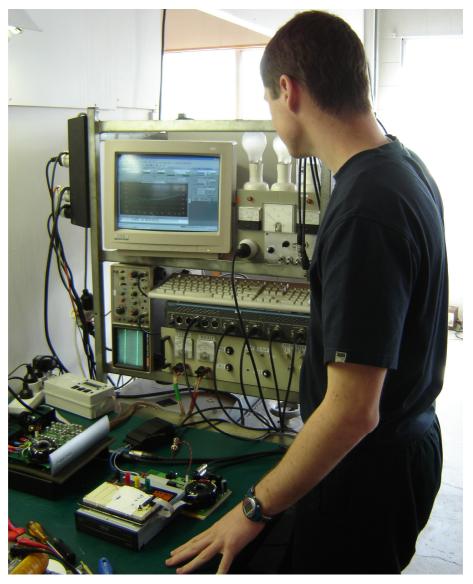

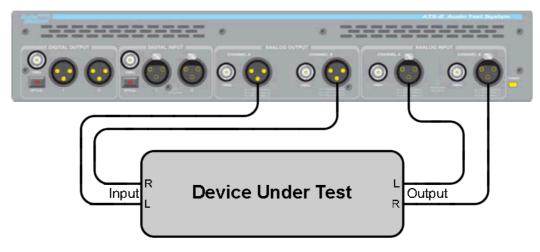

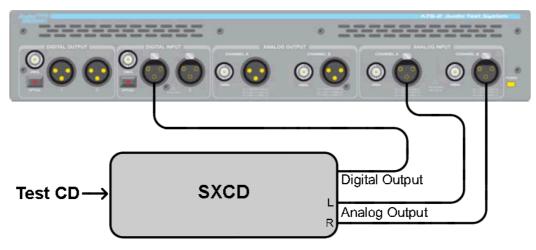

Equation 3-2