#### NAGAOKA UNIVERSITY OF TECHNOLOGY

#### **Research on Pulsed Power Generation Based on Inductive Energy Storage (IES)**

A Dissertation

By

Yu Liang

Department of < Extreme Energy-Density Research Institute >

Submitted in partial fulfillment of the requirements

for the degree of

Doctor of Engineering, < Energy and Environment Science>

2017/29/12

Accepted by the Graduate School

Date,

Dean of the Graduate School

The undersigned have examined the thesis entitled 'Research on Pulsed Power Generation Based on Inductive Energy Storage (IES)' presented by YU LIANG, a candidate for the degree of Doctor of Engineering (Energy and Environment Science) and hereby certify that it is worthy of acceptance.

2018/29/1

Weihua.J

Date

Advisors name

2018/29/1

Date

Taichi Sugai

committee member name

#### ABSTRACT

Pulse power technology is an effective means to produce extreme physical conditions. These conditions include high current strong electric field, ultra high voltage strong electric field and gas discharge plasma. These features enable pulse power to produce some special effects and thus bring unique applications. These applications can greatly improve the human ability to transform nature and improve the well-being of human life. While, with people demand more and more of their quality of life, pulsed power technology has extended its applications from traditional fusion and defense fields to many industrial areas, such as food processing, water treatment, laser pumping, and even cell manipulation [1]. At the same time, reliable and durable pulsed power sources are being developed in order to meet the requirements of industrial applications. This technical trend has pushed forward the evolution of not only the components but also the circuit methods of pulsed power generation. Pulsed power generation starts from energy storage. Although the capacitive energy storage (CES) has been the dominating method so far, it has been long since people realized that inductive energy storage (IES) could be more efficient and compact[2]-[4]. In this article, we study the circuit topology of the IES pulse generator. This study is divided into five parts. The first part is the introduction, which mainly summarizes the progress of the development of the pulse power source circuit, and finds that the current research and application of the IES topology are not much. The second part, the pure inductor energy storage circuit is studied. Its advantages and shortcomings of IES are deeply recognized. In the third part, several new circuits proposed, there are called IES pulse forming line adders. The experimental results show that they can output nanosecond square wave pulse and more efficient with the load matching easily. In the fourth part, in order to improve the energy density of the device, the IES Blumlein line is studied. Then, on this basis, a compact IES Blumlein line adder is developed.

**Key Words** Pulsed power systems, pulse generation, inductive energy storage, transmission lines, semiconductor switches.

#### ACKNOWLEDGMENTS

This thesis is completed under the guidance of my professor Jiang Weihua. In the author's three year postgraduate student career, every achievement has been inseparable from the enlightenment, education, encouragement and guidance of my professor. My professor's open research vision, profound and profound professional knowledge, and strict and realistic attitude to learning are all examples of my life. Tutor of life style and amiable and easy of approach of the educational spirit of tireless in teaching others let me bathed in spring. Although it has lasted for three years, it has been given to me for life. My professor provided me with very excellent research environment and relaxed research atmosphere, and provided many opportunities for learning and contacting outside activities, which I grew up. In the process of studying for a degree of resistance whenever I was in the course of scientific research, professor Jiang always encourage in time, and I should have little success pleased with oneself, the teacher will let me from the river. At the end of this paper, I would like to bow to the teacher deeply, because no words can express my feelings to my professor.

Thanks to the visiting associate professorr Tokuchi Akira, your selfless spirit of cooperation and innovation nonconformist to climb the peak of science academic attitude gives me great help in the process of scientific research. Thank you for the warm helps from the laboratory's assistant professor Sugai Taichi .Thanks to the doctor and master who have graduated in our laboratory, and with their help, I went through my life in Japan. For example, Dr. raze helped me financially, and the Master Hangai give me some help to arrange accommodation, medical insurance, and admission procedures in Japan.

Thanks to the Chinese students in our lab, we have made beneficial discussions in scientific research, and supported each other in our lives. We are like a family. I will always remember this wonderful time.

Thanks to Professor Liu Kefu of Fudan University and Professor Wang Xinxin of Tsinghua University, China, the useful advice provided in the author's research work.

Thanks to Nagaoka University of Technology for my education and training with three years. I was much more quiet and relaxed when I was in this "snow country" University. The learning experience in Japan will be a valuable asset in my life! Thank you for the convenience provided by the staff of the international department. I also thank the Japanese government for a series of scholarships that allow me to put my heart into academic research and not to worry about the high cost of living in Japan.

Finally, I want to thank my lovely wife. We face all the difficulties in our life together and give me the support and understanding when I am busy with research and research. I would like to dedicate this article to all the teachers, relatives and friends who have been concerned, supported and helped me.

# TABLE OF CONTENTS

## Chapter

| ACKNOWLEDGMENTSvTABLE OF CONTENTSviiLIST OF TABLESixLIST OF FIGURESxCHAPTER I: INTRODUCTION11.1 An overview of pulse power technology11.1.1 History and present situation1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                             |

| LIST OF FIGURES                                                                                                                                                            |

| CHAPTER I: INTRODUCTION                                                                                                                                                    |

| 1.1 An overview of pulse power technology       1         1.1.1 History and present situation       1                                                                      |

| 1.1.1 History and present situation1                                                                                                                                       |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

| 1.1.2 Definition, system composition, and implementation                                                                                                                   |

| 1.1.3 The development of nanosecond compact solid state pulse power technology11                                                                                           |

| 1.2 Research purpose and significance                                                                                                                                      |

| 1.3 Research methods and main works                                                                                                                                        |

| 1.3.1 Research methods 17                                                                                                                                                  |

| 1.3.2 Main works 17                                                                                                                                                        |

| CHAPTER II: SIMPLE INDUCTIVE ENERGY STORAGE (IES) PULSE POWER                                                                                                              |

| SOURCE AND ITS VLOTAGE ADDING EXPERIMENT 19                                                                                                                                |

| 2.1 The simple IES circuit principle base on semiconductor switch                                                                                                          |

| 2.1.1 Comparison of CES and IES                                                                                                                                            |

| 2.1.2 Operation principle of IES pulse source                                                                                                                              |

| 2.1.3 Charging process of IES circuit based on semiconductor switch                                                                                                        |

| 2.1.4 Discharge process of IES circuit based on semiconductor switch                                                                                                       |

| 2.2 A simple IES circuit experiment based on MOSFET switch                                                                                                                 |

| 2.3 Voltage adder experiment using simple IES circuit based on MOSET27                                                                                                     |

| 2.4 Summary and discussion                                                                                                                                                 |

| CHAPTER III: VOLTAHE ADDING OF IES PLUSE FORMING LINES [19][20] 32                                                                                                         |

| 3.1 Basic principle of IES pulse forming line (PFL) circuits                                                                                                               |

| 3.1.1 Symmetry geometric topology principle applied to IES circuit                                                                                                         |

| 3.1.2 Traditional CES-PFL and Type A IES-PFL                                                                                                                               |

| 3.1.3 Derived CES-PFL and Type B IES-PFL 40                                                                                                                                |

| 3.2 Experiment with IES pulse forming lines                                                                                                                                |

| 3.2.1 Experiment plan                                                                                                                                                      |

| 3.2.2 Experimental results and discussions                                                                                                                                 |

| 3.4 Voltage Adding                                                                                                                                                         |

| 3.4.1 Isolation mode of IES pulse forming lines                                                                                                                            |

| 3.4.2 Experimental results and discussion of voltage adding                                                                                                                |

| 3.5 Summary and discussions                                                                                                                                                |

| CHAPTER IV: PULSED VOLTAGE ADDER BASED ON INDUCTIVE BLUMLEIN                                                                                                               |

| LINES[20][22]                                                                                                                                                              |

| 4.1 Inductive Blumlein line                                                                                                                                                |

| 4.1.1 Basic principle                                                                                                                                                      |

| 4.1.2 Principle experiment                                                                                                                                                 |

|                                                                               | 61 |

|-------------------------------------------------------------------------------|----|

| MOSFET                                                                        | 01 |

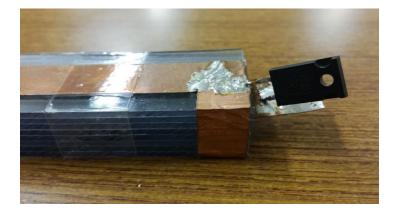

| 4.2.1 Solid-state stripline                                                   | 62 |

| 4.2.2 Function generator                                                      | 63 |

| 4.2.3 Silicon carbide MOSFET switch module                                    |    |

| 4.2.4 Experimental results of single module discharge using IES Blumlein line | 67 |

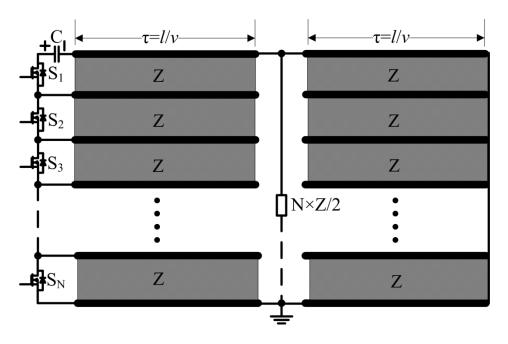

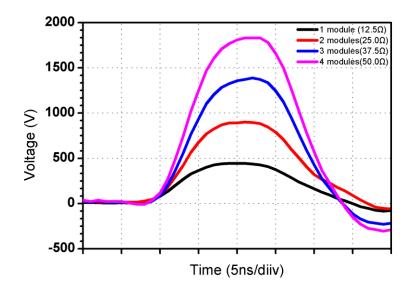

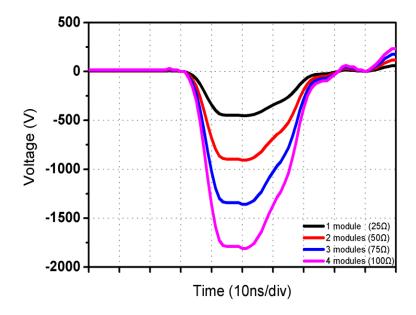

| 4.3 Inductive Blumlein line voltage adder                                     | 69 |

| 4.4 Summary and discussion                                                    | 73 |

| CHAPTER V: CONCLUSION                                                         | 75 |

| 5.1 The main research work and achievements                                   | 75 |

| 5.2 Main problems and work prospect                                           | 76 |

| REFERENCES                                                                    | 77 |

| Appendix I FPGA control program                                               | 81 |

| Appendix II Publication of papers                                             |    |

## LIST OF TABLES

| Page                                                                               |

|------------------------------------------------------------------------------------|

| ble 1: International high power pulse device[2][3][7]                              |

| ble 2 Some components used in the experiment of simple IES base on MOSFET 25       |

| ble 3 Symmetric relation table between the CES and IES                             |

| ble 4 Main components used in the experiments with IES pulse forming lines         |

| ble 5 Characteristic parameter table of Bumlein line and Inductive Bumlein line 59 |

| ble 6 Main components used in the inductive Blumlein line discharge experiments 60 |

| ble 7 Tansmission line parameters using solid state strip line                     |

| ble 8 Design parameters of function generator                                      |

| ble 9 Major components of the switch and driver                                    |

## LIST OF FIGURES

| Figure Page                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

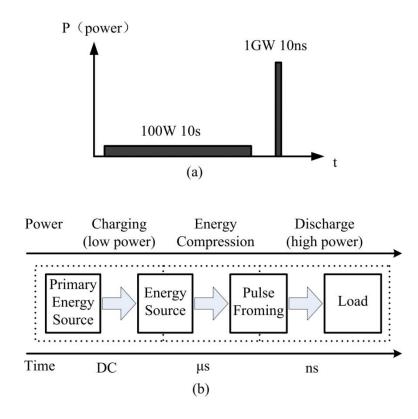

| Figure 1: A schematic diagram of definition and system composition.(a) Definition (b) system composition                                                                           |

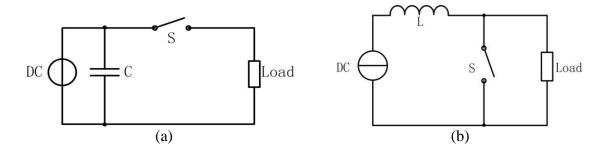

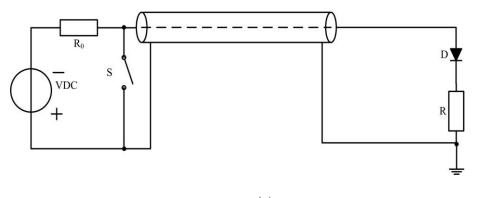

| Figure 2: Capacitive energy storage and inductive energy storage.(a) CES (b) IES 10                                                                                                |

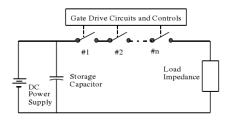

| Figure 3 Semiconductor switch series circuit. (a) Nanosecond solid-state pulse power source based on switch series. (b) 6.5 kV series IGBTs.(c) 5 kV/50 ns series SiC JFETs        |

| Figure 4 45kV Magnetic compress circuit (a) The circuit principle diagram (b) Output waveforms                                                                                     |

| Figure 5 30kV solid state LTD (a) The circuit principle diagram (b) Output waveforms 14                                                                                            |

| Figure 6 4kV bipolar Marx(a) The circuit principle diagram (b) Output waveforms 14                                                                                                 |

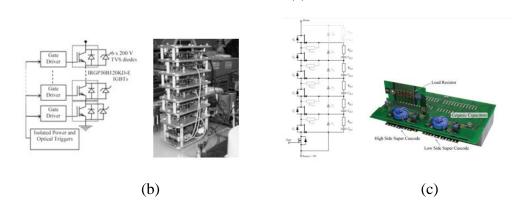

| Figure 7 Blumlein line module adder(a) The Physical diagram (b) Output waveforms 15                                                                                                |

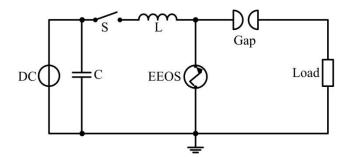

| Figure 8 Traditional IES circuit principle diagram                                                                                                                                 |

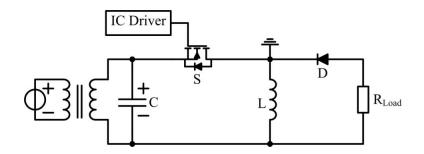

| Figure 9 Schematic diagram of a simple IES circuit based on MOSFET switch                                                                                                          |

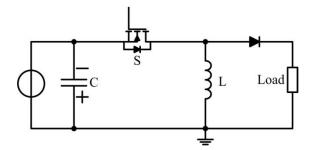

| Figure 10 Charging equivalent circuit model of IES based on semiconductor switch 22                                                                                                |

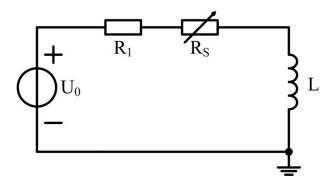

| Figure 11 Equivalent circuit diagram of discharge process using IES based on semiconductor switch (a) The switch is not completely turn off (b)The switch is completely turned off |

| Figure 12 Schematic diagram of experimental circuit using IES based on MOSFET 24                                                                                                   |

| Figure 13 Charge current and output voltage waveform using simple IES based on MOSFET with 500Ω load                                                                               |

| Figure 14 output voltage using simple IES based on MOSFET with different loads (a)<br>Peak voltages (b) Voltage waveforms                                                          |

| Figure 15 Voltage adder using simple IES circuit based on MOSFET. (a) The circuit principle diagram (b) Physical diagram                                                           |

| Figure 16 Output voltage waveforms of the voltage adder using simple IES circuit based on MOSFET                                                                                   |

| Figure 17 A schematic diagram of the coupling effect between inductors                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 18 Symmetric geometric graphs of CES and IES                                                                                                                             |

| Figure 19 Typical electric pulse compress (EPC) from magnetic pulse compress (MPC) by symmetric principle                                                                       |

| Figure 20 XRAM circuit[21] and Marx circuit                                                                                                                                     |

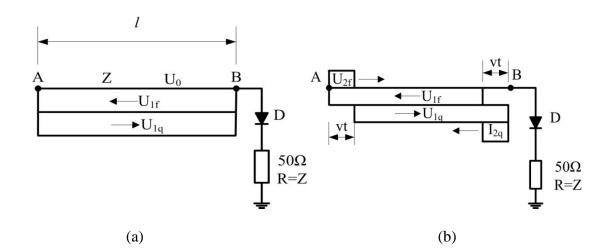

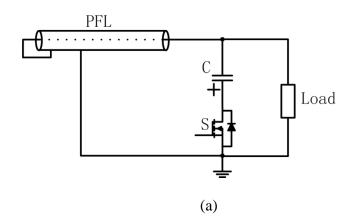

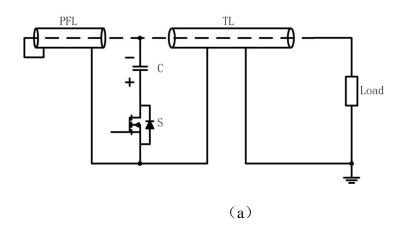

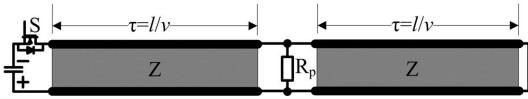

| Figure 21 The schematic diagram of the traditional CES pulse forming line and the type A IES pulse forming line (a) Traditional CES pulse line (b)Type A IES pulse forming line |

| Figure 22 Equivalent circuit model of transmission line                                                                                                                         |

| Figure 23 Circuit schematic diagram of derived CES pulse forming line and type B IES pulse forming line (a) Derived CES pulse forming line (b) Type B IES pulse forming line    |

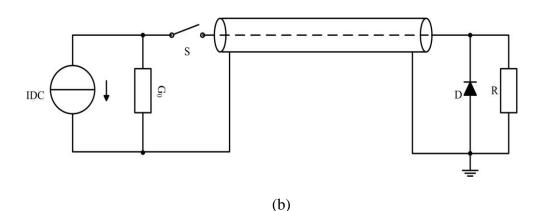

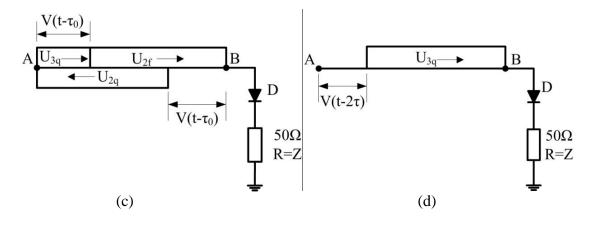

| Figure 24 Wave propagation analysis of the Derived CES pulse forming line (a) t=0 (b) $0 \le t \le \tau_0$ (c) $\tau_0 \le t \le 2\tau_0$ (d) $2\tau_0 \le t \le 3\tau_0$       |

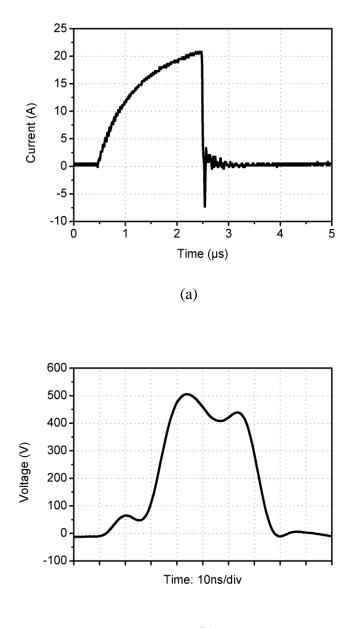

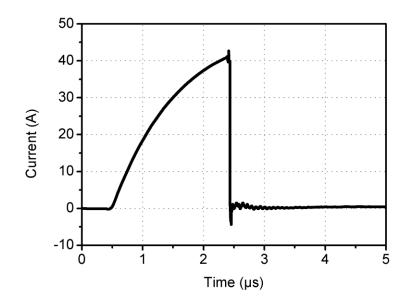

| Figure 25 Circuit diagrams of two examples of pulse forming lines using inductive energy storage (IES-PFL) (a) Type A (b) Type B                                                |

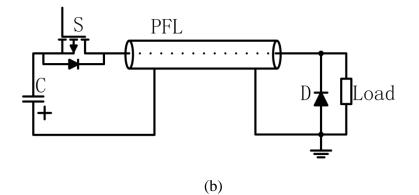

| Figure 26 Waveforms of PFL current and load voltage (Type A). (a) Charging current (b) load vltage                                                                              |

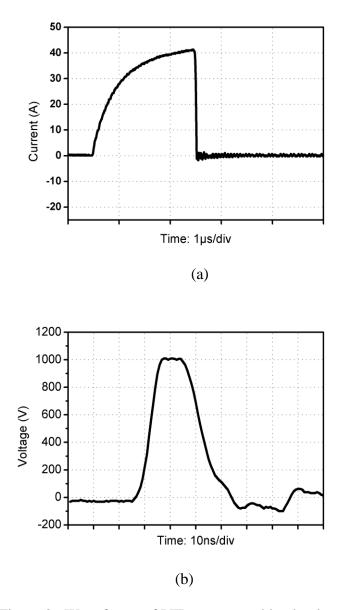

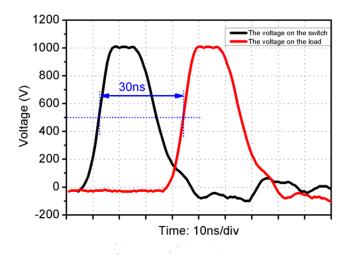

| Figure 27 Waveforms of PFL current and load voltage (Type B) (a) Charging current (b) load vltage                                                                               |

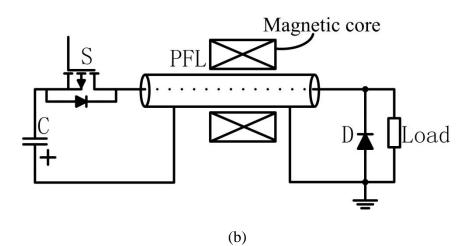

| Figure 28 Schematic diagram of isolation for IES pulse forming lines (a) Time isolation for Type A IES-PFL (b) Magnetic core isolation for Type B IES-PFL                       |

| Figure 29 Experimental results of time isolation for Type A CES-PFL                                                                                                             |

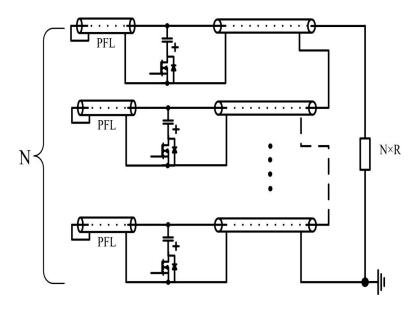

| Figure 30 Circuits for voltage adding based on IES-PFLs. (a) Type A and (b) Type B. 51                                                                                          |

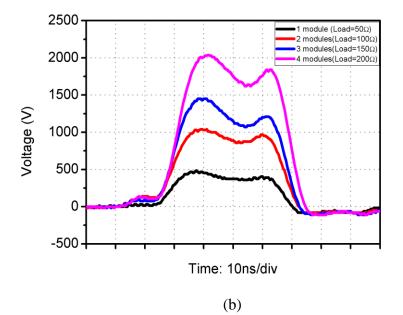

| Figure 31 Waveforms of output voltage obtained with the circuits shown in Figure 30a Type A and Figure 30b Type B.(a) Figure 30a Type A (b) Figure 30b Type B                   |

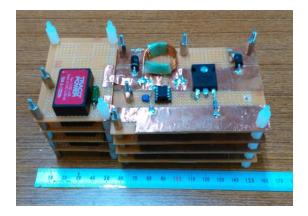

| Figure 32 The physical diagram with 4 modules adding (a) Figure 30a Type A (b) Figure 30b Type B                                                                                |

| Figure 33 The circuit principle diagram of Blumein line and inductive Blumein line circuit (a) Blumein line (b) Inductive Blumein line                                          |

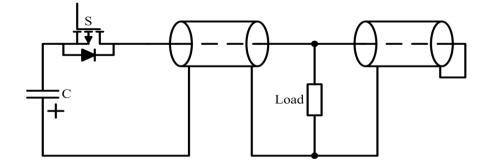

| Figure 34 Experimental circuit diagram of inductive Blumlein line                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 35 Experimental results of inductive Blumlein line circuit discharge                                                                                                           |

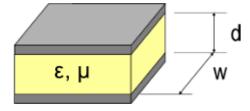

| Figure 36 A schematic diagram of the geometric structure of a strip line                                                                                                              |

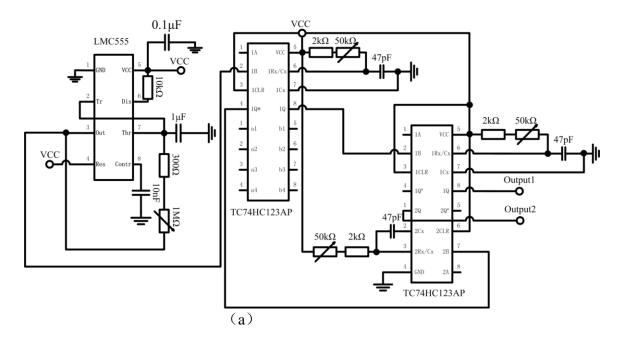

| Figure 37 Circuit schematic and physical diagram of a function generator (a) Circuit schematic diagram (b) physical diagram                                                           |

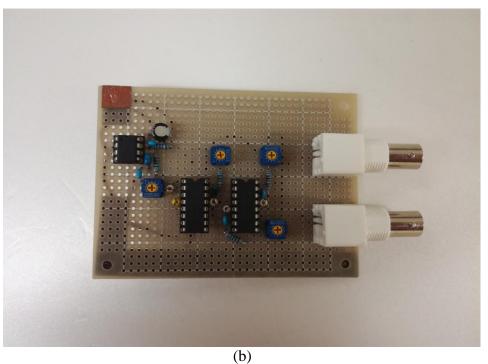

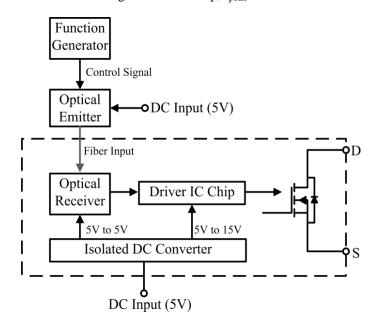

| Figure 38 Circuit diagram for the control of MOSFET                                                                                                                                   |

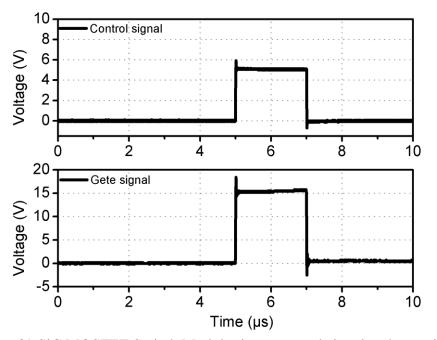

| Figure 39 SiC MOSFET Switch Modular input control signal and gate signal test waveform                                                                                                |

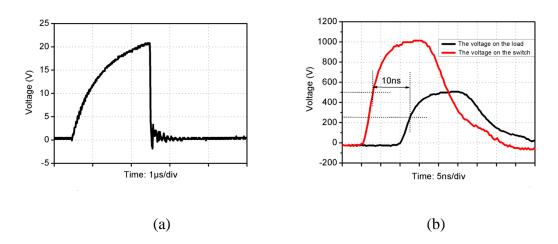

| Figure 40 Schematic diagram of single module circuit using IES Blumlein line                                                                                                          |

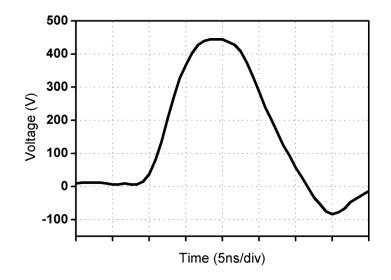

| Figure 41 The waveform of MOSFET current, obtained with capacitor charging                                                                                                            |

| Figure 42 The waveform of output voltage, obtained on the 12.5 $\Omega$ load                                                                                                          |

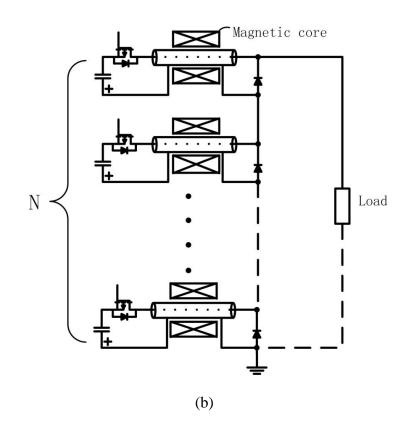

| Figure 43 Circuit diagram of voltage adder using inductive Blumlein lines                                                                                                             |

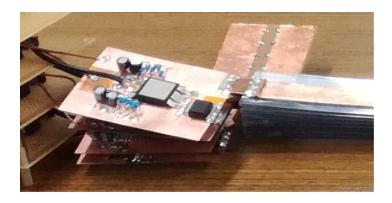

| Figure 44 Photograph of a voltage adder using inductive Blumlein line using 4 modules.<br>(a) Overall diagram of the device (b) Switch connection diagram (c) Load connection diagram |

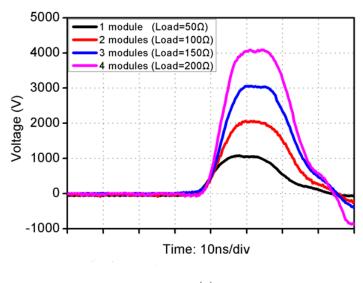

| Figure 45 The waveforms of output voltage obtained with different numbers of                                                                                                          |

| Figure 46 Circuit diagram of voltage adder using IES-PFL with single line                                                                                                             |

| Figure 47 The waveforms of output voltage obtained with different numbers of                                                                                                          |

#### **CHAPTER I: INTRODUCTION**

#### 1.1 An overview of pulse power technology

#### **1.1.1 History and present situation**

Pulse power technology is a new science and technology in the past 60 years. If only from the literal meaning, it is difficult to understand its connotation Because there are many ways to generate electric pulse square wave, such as the control method in power electronic power supply, PWM modulation is a typical electric pulse square wave, and for example, a variety of square wave generators in the field of electronic communications, it is obvious that the two case of appeal does not belong to the category of pulse power. It is clear that two cases of appeal are not in the category of pulse power. In fact, in the history of the birth and development of the so-called pulse power technology, its power is often high power. Therefore, the long term "pulse power technology" is actually "high power pulse technology". A large number of researchers also call it "strong relativistic particle beam" or "high power particle accelerator" according to their load and application place [2].

The concept of relativistic electron beam in the early medieval twentieth Century by Alfonso et al (Alfven), and in 1938, the United States Kingdon and Tanis first published a paper on the microsecond pulse power generated by high-voltage pulse X ray. After a year, the former Soviet Union successfully produced a Marx generator that simulated lightning shock waves in the field of high power rate pulses in 1939. However, the internationally recognized pulse power technology's theoretical formation and practical application owe to the J.C, Martin [2][3] and his team of the British Atomic Energy Research Center (AWE) in the 60s of last century. Therefore, at the 1981 International Conference on pulsed power, J.C. Martin won the special contribution award in the field of pulsed power ("Erwin Marx" award), in recognition of his special contribution to pulse power technology in the last century.

It can be said that in twentieth Century 60 to 80s, pulse power technology developed rapidly. At that time, the development of the pulse power is the arms race that the United States and the Soviet Union extended to the cold war. At this time, the Americans will take the lead in pulsed power technology produced by pulsed X ray for simulation of nuclear explosions, built a large pulse device Hermes II in the 1967 United States Sandia National Laboratory (1TW). In late 70s, due to the inertial confinement fusion scheme is proposed and advocated by the US star wars, various countries have produced their own "high power scientific device", such as: Angara 5 device and LIU-10M, which were built by the former Soviet Union's Institute of Atomic Energy and the Institute of Experimental Physics, respectively. France's Thalie and AIRIX. But, Japan and Germany's political and historical reasons, the pulsed power technology will not be applied to the military, so their device used for nuclear fusion research, there are some the representative devices. For instance, the researchers at Osaka University in Japan make the Raiden-IV. The ETIGO-series [2] were built by the Nagaoka University of Technology. And in Germany, nuclear technology research center do the KAKTUS device. China is also an important force that cannot be ignored in building large-scale pulsed power devices. From the early 1960s, the research team with Mr. Wang Ganchang as the core began to explore the new flash pulse X ray photography based on pulsed power technology, and built the first large device flash -I in China in 1979. In 80s, China's pulse power business has also been developing rapidly. In 1990, the scientific research team led by Dr. Qiu Aici in Northwest Institute of nuclear physics developed the low impedance accelerator flash-II in China. Table I enumerates some of the international pulse power devices. From the data in the Table I, the United States is the leader of the world's major scientific devices. From the nuclear arsenal National Laboratory (Sandia National Laboratory -SNL, Laurence Livermore National Laboratory, -LLNL) to the company (physical international company -PI, Maxwell) has the ability to develop high power pulse device. It is not difficult to find some interesting phenomena from Table 1. Some large pulse power devices seem to be related to geopolitics and national strength. Let's take note of three interesting points of time, 1965, 1991, and 2000, respectively. 1945-1965 was a period between the end of World War II and the beginning of the cold war. The center of this time science is western society. At this time, the British have a solid foundation, and the Americans are beginning to develop rapidly. In the 1965-1991 years, the United States and the Soviet Union began the "hegemony of the two camps", the so-called period of the cold war. Obviously, the Western leader is already the United States, when the American large power pulse device is completely surpassing any country in the West. Notable Soviet Union has developed a series of devices during this period, and some of the technical routes are different from those in the US, especially in inductive energy storage and short pulse. Unfortunately, after the disintegration of the Soviet Union in 1991, the development of these technologies was slowed. As we turn our eyes back to East Asia, Japan's large pulse power devices are internationally advanced in 1980s and 90s. This seems to be related to the high wealth created by the rapid economic development of Japan from 1961 to 1992. And China has almost nothing to build throughout the 1980s,

in the large pulse power devices. To know this period of time, China's "reform and opening up" has just started and ended the ten years of social turmoil. But after 21 Century, the world is only China and the United States that can build more than 5MA large pulse power devices. Does it mean that the era of G2 is coming?

Looking at the devices in Table 1 from another perspective, some countries in the world are obviously less interested in large pulse power devices, entering the 21st century. The development of peace is the theme of the world, and developing large pulsed power devices for military and nuclear fusion applications has not been as important as before. But in recent ten years, the application of high power nanosecond short pulses in industry has been paid much attention by many scholars all over the world. In the field of biomedicine, the research team in the United States Old Dominion University shows that the strong nanosecond electric field can induce biological effects of some cells. On the one hand, a strong nanosecond electric field can cause the death of cells in the cells of human cells [5][6]. On the other hand, changing the duration of the nanosecond pulse and the number of pulses can cause coagulation of the platelets [5][6]. These means that nanosecond pulse technique brings new ways to cancer treatment and homeostasis. In environmental protection, In the field of environmental protection, the Kumamoto University study suggests that less than tens of nanoseconds can form high frequency pulse discharge can be applied to flue gas denitrification [1].Research at the Nagaoka University of Technology shows that a mixed discharge of nanosecond gas and liquid, produced by strong oxidizing substances, can be used to treat industrial waste water [8].In the automobile industry, the ignition of nanosecond discharge can overcome the limitation of the traditional ignition mode and reduce the fuel consumption and reduce

the emission of polluted gas[8]. The promise of these attractive application prospects is the development of compact, all solid state, high frequency, and short pulse generator[1][9].

| Name       | Countries and                  | Main technical parameters (technical      | Time          |

|------------|--------------------------------|-------------------------------------------|---------------|

|            | organizations                  | route)                                    |               |

| Mini B     | U.K.Atomic Weapons<br>Research | 2.2 MV, 50 kA, ( High impedance)          | 1964          |

|            | Establishment(AWE)             |                                           |               |

| SWARF-II   | U.K.AWE                        | 10 MV,100 kA (High impedance)             | 1986          |

| Magpie     | U.K.AWE                        | 1.5MA (Multiple devices parallel)         | ?             |

| Hermes-II  | USA SNL                        | 10-12MV,0.17MA,80ns (High impedance)      | 1968          |

| Hermes-III | USA SNL                        | 20MV,0.8MA,40ns (Induction voltage adder) | 1989          |

| PBFA-I     | USA SNL                        | 1.9MV,4.5MA,40ns (36 branches parallel)   | 1980          |

| PBFA-II    | USA SNL                        | 4MV,10MA,40ns (72 branches parallel)      | 1985          |

| PBFA-Z/ZR  | USA SNL                        | 2.5MV,20-26MA,40ns (36 branches parallel) | 1996-<br>2010 |

Table 1: International high power pulse device[2][3][7]

| Gambl-I    | USA Naval Research<br>Laboratory (NRL) | 0.75MV,0.5MA,50ns (Low impedance)            | 1968 |

|------------|----------------------------------------|----------------------------------------------|------|

| Gambl-II   | USA NRL                                | 0.9MV,1.3MA,50ns (Low impedance)             | 1970 |

| Mercury    | USA NRL                                | 6MV, 0.36MA,50ns (Induction voltage adder)   | 2004 |

| ETA        | USA LLNL                               | 4.5MV,10kA,50ns (Induction voltage adder)    | 1979 |

| ATA        | USA LLNL                               | 50MV,10kA,70ns (Induction voltage adder)     | 1984 |

| Blackjack5 | USA Maxwell                            | 3MV,3.5MA,50ns (Low impedance)               | 1978 |

| Pithon     | USA PI                                 | 2MV, 3.5MA,50ns (Low impedance)              | 1975 |

| DECADE     | USA PI                                 | 1.5MV,17MA,50ns(Multiple devices parallel)   | 1983 |

| Thalie     | France                                 | 10-15MV, 0.2MA,70ns (High impedance)         | 1974 |

| AGLAE-II   | France                                 | 0.7MV,1.7MA,35ns (Low impedance)             | 1981 |

| AIRIX      | France                                 | 16-20MV,3.5MA,60ns (Induction voltage adder) | 2000 |

| ИГУР       | Former Soviet Union and<br>Russia      | 6MV,80kA,20-150ns (IES)                      | 1978 |

| Эмир       | Former Soviet Union and<br>Russia          | 7.5MV,0.2MA,20-200ns (IES)                         | 1990 |

|------------|--------------------------------------------|----------------------------------------------------|------|

| ТОНҮС-ІІ   | Former Soviet Union and<br>Russia          | 1MV,1MA,60ns (Low impedance)                       | 1979 |

| Angara-5-1 | Former Soviet Union and<br>Russia          | 3MV,3-5MA,90ns (8 branches parallel)               | 1989 |

| Liu-10     | Former Soviet Union and<br>Russia          | 14MV,50kA,20ns (Induction voltage adder)           | 1977 |

| Liu-10M    | Former Soviet Union and<br>Russia          | 25MV,50kA,20ns(Induction voltage adder)            | 1983 |

| Liu-30     | Former Soviet Union and<br>Russia          | 40MV,0.1MA,20ns                                    | 1989 |

| Reiden-IV  | Japan, Osaka University                    | 1.4MV,1.4MA,50ns (Low impedance)                   | 1978 |

| ETIGO-II   | Japan, Nagaoka University<br>of Technology | 3MV,0.46MA,50ns (Low impedance)                    | 1986 |

| ETIGO-III  | Japan, Nagaoka Univ.Tech.                  | 8MV,5kA,30ns (Induction voltage adder)             | 1996 |

| ETIGO-IV   | Japan, Nagaoka Univ.Tech.                  | 0.5MV, 13kA,200ns,1HZ (Magnetic pulse compression) | 2000 |

| Flash-I         | People's Republic of China<br>(P.R.C), China Academy of<br>Engineering Physics<br>(CAEP) | 8MV,0.1MA,80ns (High impedance)                                        | 1979 |

|-----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|

| Flash-II        | P.R.C., (Northwest Institute of nuclear technology)                                      | 0.9MV,0.9MA,70ns (Low impedance)                                       | 1990 |

| LIA-10          | P.R.C.,CAEP                                                                              | 12MV,3.5kA,70ns (Induction voltage adder)                              | 1993 |

| ShenLong-I      | P.R.C.,CAEP                                                                              | 20MV,3.5kA,70ns (Induction voltage adder)                              | 2003 |

| ShenLong-<br>II | P.R.C.,CAEP                                                                              | 3MV,>2kA,2MHZ (Induction voltage adder<br>and transmission line delay) | 2015 |

| PTS-I           | P.R.C.,CAEP                                                                              | 3MJ,8-10MA (24 branches parallel)                                      | 2013 |

#### 1.1.2 Definition, system composition, and implementation

Pulse power technology, in a broad sense, is a science and technology aimed at obtaining short-time high power electrical pulses. It has the feature that the stored energy is loaded in a single or repeated form in the form of a short electric pulse. The traditional pulse power is often required to reach the following electrical parameters: The power is generally above 1GW, and the maximum is in the order of 10<sup>14</sup>W, the voltage range from10kV to 50MV, the current from1kA to 10MA, the di/dt from 1kA/µs to100kA/ns,

and du/dt from  $1kV/\mu s$  to 100kV/ns. Due to the rise of industrial applications, the traditional electrical parameters are difficult to cover fast pulse and short pulse generator.

Therefore, a new definition method has been put forward by some scholars. This method synthesizes the characteristic parameters of electric pulse, and the specific method is as follow.  $P_{max}$ ,  $V_{max}$ ,  $I_{max}$  and  $t_r$  represent short pulse power capacity, voltage peak value, current peak value and rise time of electric pulse. Then the pulse power technology can be quantitatively expressed as equation 1-1.  $K_{pr}$  is the rate of increase of electrical power, in other words, the rate of providing pulse power.

$$K_{\rm pr} = \frac{P_{\rm max}}{t_{\rm r}} = \frac{V_{\rm max}I_{\rm max}}{t_{\rm r}} > 10^{13} \,\rm W/s$$

[1-1]

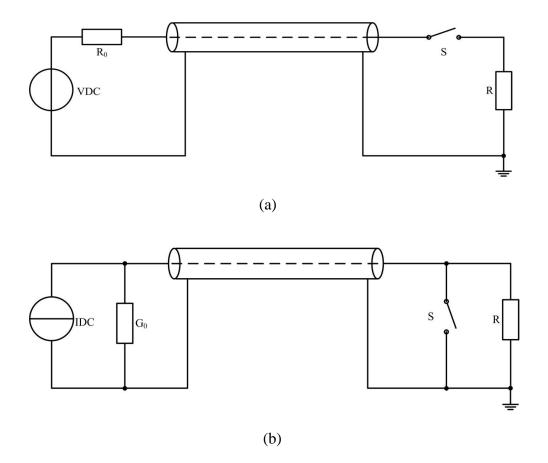

If the physical meaning of equation 1-1 is represented by a graph, it is shown as shown in Figure 1 (a). As shown in Figure 1 (a), if a high power output is to be achieved, an effective method is the energy compression.

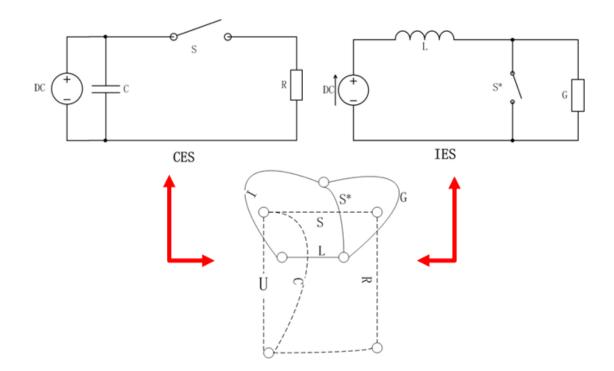

The typical pulse power system is shown in Figure 1 (b). It is composed by a primary charging power, an energy storage unit, a pulse forming network, a switch, and a load. Primary charging power is the power source of the whole system. DC power is usually used. The energy storage unit has two forms, the electric field energy storage and the magnetic field energy storage. Their equivalent circuits are shown in Figure 2. For electric field energy storage, a capacitor C is used to store energy. When the switch S is

Figure 1: A schematic diagram of definition and system composition.(a) Definition (b) system composition

Figure 2: Capacitive energy storage and inductive energy storage.(a) CES (b) IES

opened, the capacitor C will be charged by the constant voltage source. When the voltage on the capacitor C is charged to the switch S is closed, and the capacitor will be discharged to the load. As the load and energy storage element are parallel, the output voltage is equal to the charge voltage. If the closing time of the switch S is far shorter than the opening time of the switch, the output current is far higher than the charging current, according to the energy conservation law. Therefore, the circuit in Figure 2 (a) can be used to obtain the current amplification. While, the magnetic field energy storage is shown by using an inductor as a energy storage element, in Figure 2 (b). So magnetic field energy storage is also called inductive energy storage (IES) circuit. For the IES circuit, the primary DC charging power supply is a constant current source in the ideal case. When the switch S is closed, the inductor L is charged by the current source. When the current in the inductor reaches the preset current, the switch S is opened, and the inductor discharge to the load. Because the inductor L is connected in series with the load, the output current is equal to the charge current in the ideal case. If opening time of the switch S is far shorter than the closing time, the output voltage will be higher than the charge voltage, according to the conservation of energy law.

# 1.1.3 The development of nanosecond compact solid state pulse power technology

From the previous description, it is not difficult to find that industrial applications require pulse power sources to have the following characteristics. First, it can output short, fast and rectangular pulse. Secondly, the size of the device smaller is the better when the output power is satisfied. Once more, the pulsed power source should have the ability with high reliability and high repetition. Finally, it should have low cost and high efficiency. The development of all solid state pulse power sources is an effective way to achieve the above requirements. The primary problem that hinders the development of all solid state pulse power technology is the limited power capacity of the switches [9].

In recent ten years, scholars from all over the world have invested a lot of enthusiasm in developing all solid state pulse power technology, not only in energy storage components

and switches, but also in the innovation of circuit methods. First of all, it is easy to think of the switch series, based on the circuit making generator in Figure 2 (a). For example, USA scholars use IGBTs in series make a generator with a voltage 6.5kV [10]. This circuit has a simple structure. However, multiple switches have to divide the voltage evenly during the operation, and the potential of the switch on the high voltage side is floating. If one of the switches is broken, it will cause the overall overvoltage of the system and eventually cause the system to collapse. The schematic diagram of the switch component is shown in Figure 3(b). In order to solve the problem of floating voltage, the German scholars have developed the switch in series. The SiC-JFETs is used in series to make a generator with a voltage 5kV and a pulse width 50ns, as shown in Figure 3(c) [11]. But, it cannot solve the problem of system stability, because of single switch breakdown.

(a)

Figure 3 Semiconductor switch series circuit. (a) Nanosecond solid-state pulse power source based on switch series. (b) 6.5 kV series IGBTs.(c) 5 kV/50 ns series SiC JFETs[10][11]

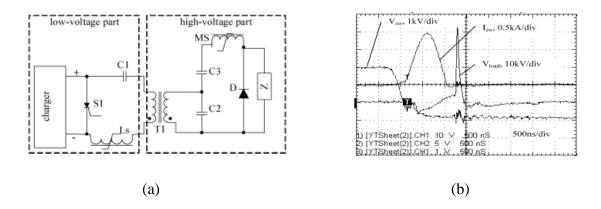

Secondly, the invention of magnetic switch effectively solves the problem of insufficient switching power capacity. For example, the Israeli research team developed a 45kV nanosecond generator using magnetic compression and fast recovery diodes, as shown in Figure 4 [12]. Although the circuit is easy to obtain high power output, the output waveform is not ideal, not an ideal rectangular wave, as seen in Figure 4 (b). Furthermore, when the circuit is designed, the circuit parameters are fixed, and all the output parameters are difficult to adjust.

Figure 4 45kV Magnetic compress circuit (a) The circuit principle diagram (b) Output waveforms[12]

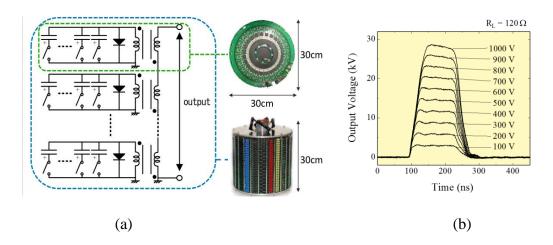

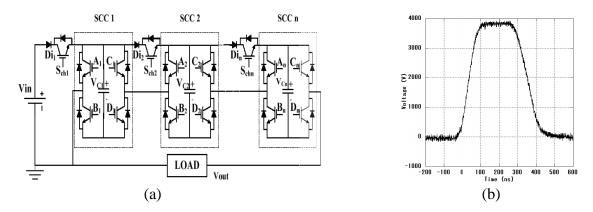

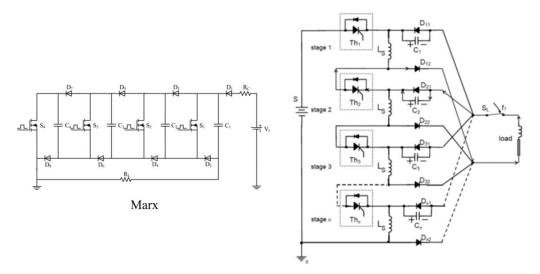

Because of the obvious shortcomings of these circuits, recently, pulsed power system design method has shifted rapidly toward modular concept. Instead of designing and building a pulsed power machine from the beginning, it is more desirable to construct a pulsed power system from pre-manufactured modules. Most of the recently reported solid-state MARX-type or LTD-type generators are developed based on this concept. Modular concept relies on the feasibility of voltage adding and power adding. As a result, the system no longer requires a "main" switch that must be able to handle the total output voltage and output power of the whole system. Therefore, the significance of the pulsed power system modularity is not only on lowering the system cost but also, more importantly, on the extension of the operation parameters far beyond the limit of a single device. With this in mind, the research team at the Nagaoka University of Technology developed the 30kV solid state LTD[13], as shown in Figure 5. And the research team at the Kumamoto University developed 4kV bipolar Marx[14] for gas discharge, as shown in Figure 6. And researchers from Chongqing University in China have developed the Blumlein line module adder [15] for cancer treatment, as shown in Figure 7.

Figure 5 30kV solid state LTD (a) The circuit principle diagram (b) Output waveforms[13]

Figure 6 4kV bipolar Marx(a) The circuit principle diagram (b) Output waveforms[14]

Figure 7 Blumlein line module adder(a) The Physical diagram (b) Output waveforms[15]

It has been long since people realized that inductive energy storage (IES) could be more efficient and compact [16].But the development of the high voltage nanosecond generator based on the inductive energy storage is very slow. Only circuits based on semiconductor opening switch (SOS) and drift step recovery diode (DRSD) are reported [17].Although Russian scholars exploit these special switches to develop a 1MV 50ns pulse generator [17]. However, the purchase channels of these switches are difficult, so the cost is high. The efficiency of the device is less than 60%, and the output waveform is not an ideal rectangular wave [17].

#### 1.2 Research purpose and significance

IES is an important development direction of pulse power technology. The energy storage density of IES is several tens times higher than the CES. Under the condition of a certain volume of the pulse power source, the IES can output a higher energy than the CES. It is easier to miniaturize the system when the output energy is required. The obstacle that has hampered IES has been the lack of suitable opening switches, because high-voltage, high-speed, and high-efficiency opening switch has not been developed yet.

The pulse source using magnetic pulse compression and special switch has no advantages in efficiency, waveform and cost. The new circuit method used IES should be put forward to develop the nanosecond compact solid state pulse power technology. It should have the following features. Fist, it can output the rectangle wave, which has improved the unsatisfactory waveform of the traditional IES circuit. Next in importance, it can output less than 50 nanosecond pulse width pulses to meet the demand for industrial applications for short pulses. Once more, its voltage is superimposed to meet the high electric field applications. In the end, it should be efficient and low cost relative to traditional inductive energy storage circuits. Some successful experiences should be used for reference. On the one hand, the development of the MOSFET switch has been able to turn off less than 10 nanoseconds, but less power capacity limits its application. On the other hand, the application of modular concept in capacitive energy storage has greatly promoted the popularization of CES. The new inductive energy storage circuit in this paper will introduce these useful concepts and create a new circuit method to enrich the compact nanosecond solid state pulse source.

This research has great significance, not only to guide the future design of nanosecond pulse source, but also promoting the development of nanosecond high repetition rate pulsed power technology. As well as compact, ideal rectangular wave, high voltage ratio and high stability pulse power source have important practical significance for environmental protection, health care, or food industry. It will also bring considerable social and economic benefits.

#### 1.3 Research methods and main works

#### 1.3.1 Research methods

#### 1. Theoretical analysis

According to the theoretical analysis, the circuit principle is studied by the method of circuit analysis for the IES pulse power source. The internal relations of CES and IES are discussed by a symmetric analysis method.

#### 2. Experimental study

Based on the theoretical research and computer simulation design, a variety of prototype platform of inductive energy storage pulse power source is set up, and the correctness of the theoretical analysis is verified.

#### 1.3.2 Main works

On the basis of in-depth analysis and study of traditional IES pulse power source, the paper fully recognizes the characteristics and defects of the inductive energy storage circuit. Several new inductive energy storage circuits are proposed by using the dual principle to change the traditional pulse forming line (PFL). Experiments show that these circuits can output rectangular waves, which are better than the output waveform of traditional inductive power source power source. These circuits are easier to achieve load matching and achieve higher efficiency. After the introduction of the concept of modularization, the pulse adding is realized. These circuits can be called IES-pulse forming line (IES-PFL) adder and Inductive Blumlein Line adder.

The main structure of the thesis is as follows:

- In the first chapter, the history of pulse power technology is combed, and then the nanosecond all solid state high frequency pulse power technology is investigated. On the basis of this, the purpose and significance of this study are expounded. Finally, the main work of the paper is briefly introduced.

- In the second chapter, the theoretical knowledge of IES, the charging and discharging process, the energy efficiency, the discharge waveform, and power adding of the traditional IES are elaborated and analyzed. Then, we show its advantages and disadvantages through experiments, and make a summary and analysis. At the same time, some simple power adder experiments are presented, which makes us realize the necessity of improvement.

- In the third chapter, the relationship between the IES and the CES is studied by using the dual principle. Since then, some new circuit topologies are proposed, which can be called IES-pulse forming line (IES-PFL) adder and Inductive Blumlein Line adder. The feasibility of these circuits is verified by simulation and experiment.

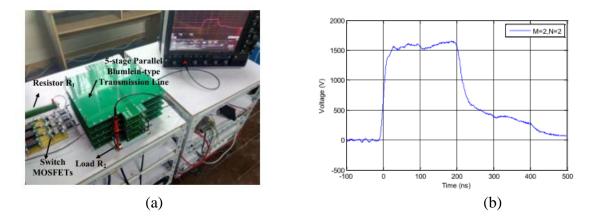

- In the fourth chapter, the core purpose is compactness, short pulse and bipolar output. A compact Inductive Blumlein Line adder is proposed. Here, the strip-line is designed as the transmission line, and the silicon carbide MOSFET is used as an opening switch. In the case with the 4 module, a short pulse is obtained, with 15 ns 2kV. And this new type of circuit can get the negative voltage output only by the geometric folding.

- The fifth chapter is a conclusion and prospect.

### CHAPTER II: SIMPLE INDUCTIVE ENERGY STORAGE (IES) PULSE POWER SOURCE AND ITS VLOTAGE ADDING EXPERIMENT

# 2.1 The simple IES circuit principle base on semiconductor switch

#### 2.1.1 Comparison of CES and IES

Before explaining the basic principle of the inductive energy storage pulse power source, it is better to understand the difference between the capacitive energy storage and the inductive energy storage.

Capacitive energy storage refers to the storage of energy in an electrostatic field after the capacitor is charged. For example, a flat plate capacitor, its energy density  $\omega_{\rm C}$  is as follow:

$$\omega_{c} = \frac{\frac{1}{2}CU^{2}}{V} = \frac{\frac{1}{2}\varepsilon\frac{S}{d}E^{2}d^{2}}{Sd} = \frac{1}{2}\varepsilon E^{2}$$

[2-1]

The symbols in the equation represent the following: C-Capacitance, U-Voltage between plates, V-Capacitor volume, ε-Dielectric constant, S-plat area, d-Distance between plates, E- Electric field strength between plates

The inductive energy storage is to store the energy in a magnetic field produced by the current in the inductance coil. For example, a spiral inductor its energy density  $\omega_L$  is as follow:

$$\omega_{L} = \frac{\frac{1}{2}LI^{2}}{V} = \frac{\frac{1}{2}\mu n^{2}V\left(\frac{B}{\mu n}\right)^{2}}{V} = \frac{1}{2}\frac{B^{2}}{\mu} = \frac{1}{2}\mu H^{2}$$

[2-2]

The symbols in the equation represent the following: L- Inductance, I-Current in the inductor, V-Inductor volume,  $\mu$ -Magnetic permeability, n-Turn number of coil, B-, Magnetic induction intensity, H- Magnetic field intensity.

It is known from equation 2-1 and 2-2 that the capacitance density ( $\epsilon E^2/2$ ) is obviously limited by the electric field intensity of the medium, and it is easy to break, when the the medium is charged with high voltage for a long time. Therefore, the long charging time of CES is also limited to the increase of its energy storage density. However, the density of inductive energy ( $B^2/2\mu$ ) is only related to the magnetic induction intensity B, and the high electric field only appears at the output terminal. Therefore, the electric field intensity has almost no limitation on the inductive energy storage, and its energy storage density is almost limited by the electromagnetic force. Therefore, under reasonable numerical conditions, it is known that the density of the IES is several times the CES. It has been shown that the cost of IES is only 10% of CES for energy storage above 5MJ [2].

#### 2.1.2 Operation principle of IES pulse source

The operating principle circuit of the traditional IES pulse source is shown in Figure 8. The basic operation process is as follows: When the primary energy storage unit of C is charged to the working voltage, the switch S is closed. The inductance L can be charged by the capacitor C. When the current reaches the maximum value, the switch EEOS opened, at this time, the current in the circuit is suddenly cut off, causing a high voltage on the inductor L. The high voltage is applied to the sharpening switch Gap, and when the voltage is higher than the breakdown voltage of the sharpening switch, the switch Gap is closed. Then, the voltage is applied to the load, and driving the load to work.

Figure 8 Circuit principle diagram of traditional IES

In the traditional circuit, the electric exploding wire is used as the main opening switch. The advantage of this switch is that its power capacity is large, and it can withstand high voltage after opened. The disadvantage is that the switch speed is slow and it cannot be closed, so some auxiliary switches are needed. As shown in Figure 8, in order to output a nanosecond pulse, it is necessary to sharpening switch Gap and control switch S.

The MOSFET switch is used to replace the electric exploding wire as the main opening switch, and the inductive energy storage circuit can be simplified, as shown in Figure 9. The switching speed of the MOSFET can be less than 10ns, so a short nanosecond pulse can be get without using sharpening switch Gap. The MOSFET, as a fully controlled switch, can perfect all the functions of the closing switch S and the opening switch EEOS, without considering the power capacity of the switch. The operating principle of the circuit is as follows. When the MOSFET switch is closed, the constant voltage source composed by capacitor and voltage source charges the inductance L, and the current in the inductor rising. Because the diode reverses bias, there is not voltage on the load.

When the current reaches a predetermined value, the MOSFET switch is opened, and the current in the inductor flows through the diode to the load.

Figure 9 Schematic diagram of a simple IES circuit based on MOSFET switch

### 2.1.3 Charging process of IES circuit based on semiconductor switch

If the capacitor is large enough and the closing time of the MOSFET switch is not long, the voltage on the capacitor is basically unchanged at this time. Therefore, the inductor charging process can be equivalent to the first order circuit as shown in Figure 10. The meaning of the symbol in the Figure 10 is as follows:  $U_0$ -charging voltage,  $R_1$ -Line resistance (including resistance of wire and inductance coil),  $R_S$ -The on resistance of the semiconductor switch MOSFET, L-Inductance.

Figure 10 Charging equivalent circuit model of IES based on semiconductor switch

According to the principle of circuit analysis, it is assumed that the charging current is I, and the state of the circuit can be expressed in the following equation [2-3]. The charging

current can be obtained by the equation [2-3].  $I = \frac{U_0}{R_1 + R_s} (1 - e^{-\frac{R_1 + R_s}{L}t})$

$$U_0 = I(R_1 + R_s) + L\frac{dI}{dt}$$

[2-3]

From the calculation formula, the low circuit resistance is often needed to obtain high charge current. When the line resistance is low enough, the voltage on line resistance in equation [2-3] can be ignored. At this time, the rising rate of charging current is basically constant ( $U_0/L$ ).

#### 2.1.4 Discharge process of IES circuit based on semiconductor switch

After the MOSFET is disconnected, the energy storage inductor is discharged to the load. This process can be divided into two stages, as shown in Figure 11. This process is as follows. When the current of the energy storage inductor L is I, the MOSFET switch begins to open and it changes from a low resistance to the high resistance. This change obviously takes some time. During this period of time, the discharge process is shown in Figure 11 (a), and the energy storage inductor L discharges to the switch and the load. Then, the switch is completely off. At this time, because the leakage current of the switch is very small, it can be considered that the energy storage inductor L only discharges to the load, as shown in the Figure.11 (b). Because of the energy loss on the switch discharge, the current I\* is smaller than the charging current I. The whole discharge time

is proportional to opening time of the switch and the time constant  $(L/R_{load})$  of the inductor L discharge.

Figure 11 Equivalent circuit diagram of discharge process using IES based on semiconductor switch (a) The switch is not completely turn off (b)The switch is completely turned off

#### 2.2 A simple IES circuit experiment based on MOSFET switch

The experimental design of a simple inductive energy storage circuit based on MOSFET switch is designed to verify the theoretical discussion, and to further understand the advantages and disadvantages of the IES circuit. In order to extend the application to high voltage in the future, the opt-coupler isolation is used, and the power supply is isolated from the transformer, which is shown in Figure 12.

Figure 12 Schematic diagram of experimental circuit using IES based on MOSFET

The experimental design is as follows. The trigger control signal is the digital signal generator (GD535), and it can produce the control signal with 2 microseconds to control

the switch on. The charge uses a DC isolation converter, which converts the voltage from 5V into 12V to charge a  $47\mu$ F capacitor C. Part of the components used in the experiment are shown in Table 2.

| Table 2 Some components used in the experiment of simple ins base on WOSTET |                    |            |                           |  |  |

|-----------------------------------------------------------------------------|--------------------|------------|---------------------------|--|--|

| Components                                                                  | Manufacturer       | Model      | Main parameters           |  |  |

| MOSFET                                                                      | STMicroelectronics | STW23N85K5 | V <sub>DSS</sub> =850V    |  |  |

|                                                                             |                    |            | I <sub>D25</sub> =19A(DC) |  |  |

|                                                                             |                    |            | t <sub>f</sub> =8ns       |  |  |

| Driver Chip                                                                 | Microchip          | TC4429     | $V_{max}=20V$             |  |  |

|                                                                             |                    |            | I <sub>peak</sub> =6A     |  |  |

| Isolated DC-DC                                                              | TRACOPOWER         | NMJ0515SAC | V <sub>OUT</sub> =12V     |  |  |

| converter                                                                   |                    |            | V <sub>IN</sub> =5V       |  |  |

|                                                                             |                    |            | P <sub>OUT</sub> =10W     |  |  |

|                                                                             |                    |            | Isolated                  |  |  |

|                                                                             |                    |            | Voltage=5kV               |  |  |

| Opto-coupler                                                                | Avago Tech.        | HCPL-0601  | Isolated                  |  |  |

|                                                                             |                    |            | du/dt=15kV/µs             |  |  |

|                                                                             |                    |            | High speed:10MBd          |  |  |

| Murata                                                                      | Chemicon           | Murata RCE | 50V,10 μF                 |  |  |

| Diode                                                                       | STMicroelectronics | STTH310    | V <sub>rev</sub> =1kV     |  |  |

|                                                                             |                    |            | $I_{max}=3A(DC)$          |  |  |

| Inductor                                                                    | /                  | /          | 1µH                       |  |  |

Table 2 Some components used in the experiment of simple IES base on MOSFET

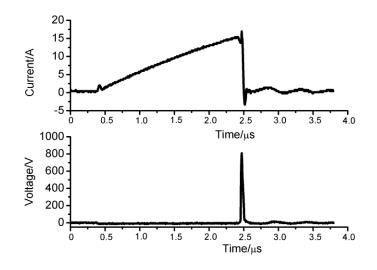

According to the circuit shown in Figure 12, and the use of components in Table 2 to build a laboratory platform, the control switch is turned off after  $2\mu$ s. When the load is 500 ohm pure resistance, the output voltage waveform and charging current waveform are shown in Figure 13.

From the experimental results, the advantage of inductive energy storage is voltage amplification. As the experiment did, when charge current is nearly 16A, the output of about 800V was obtained at a load 500 ohms, and the charge voltage was only 12V. The increase of the charge current is Linear on the inductance with  $1\mu$ H is basically matching the theoretical deduction. According to Ohm's law, the peak output current is about 1.6A,

and it is less than 16A of the charging current. This phenomenon, as described in the previous theory, the current in the inductor partially discharges to the switch with the process of the switch opened.

Figure 13 Charge current and output voltage waveform using simple IES based on MOSFET with  $500\Omega$  load

Figure 14 Output voltage using simple IES based on MOSFET with different loads (a) Peak voltages (b) Voltage waveforms

The relationship between the peak output voltages and the different loads can be obtained by maintaining the constant charging current and changing the load resistance, as shown in Figure 14. As we can see from Figure 14 (a), the output voltage increases with the increase of load, but the nonlinearity increases. Compare the output voltage waveforms of different loads in Figure 14 (b). When the load is 200 ohms, the voltage fall part is close to the exponential waveform longer than 500 ohms, and the rise time of voltage is basically the same as the rise time of 500 ohms. This phenomenon indicates that the inductor discharge is divided into two parts, the first part is the phase of the output voltage rising, and its time is completely determined by the switch off speed. The latter part is the voltage drop stage, and its time is related to the time constant of the inductance discharge, and the lower the load resistance the longer the longer. This is matching with the inference in 2.1.4.

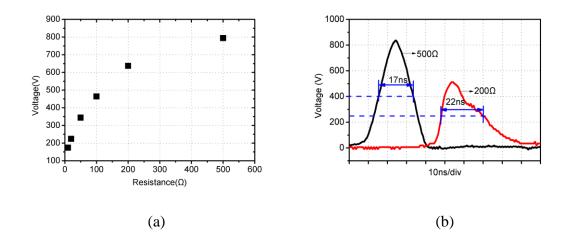

# 2.3 Voltage adder experiment using simple IES circuit based on MOSET

In order to obtain higher voltage output and short pulse, it is obviously impossible to increase the load resistance only. There are two reasons. On one hand, the peak voltage of switch is limited, for example, the peak voltage of MOSFET used in experiment is 850V, while the output voltage with 500 ohms is 800V, which is close to the limit value of switch. In order to obtain higher voltage output and short pulse, it is obviously impossible to increase the load resistance only. There are two reasons. On one hand, the peak voltage of switch is limited, for example, the peak voltage of MOSFET used in experiment is 850V, while the output voltage with 500 ohms is 800V, which is close to the limit of switch is limited, for example, the peak voltage of MOSFET used in experiment is 850V, while the output voltage with 500 ohms is 800V, which is close to the limit of switch. On the other hand, from the results in Figure 14 (a), the increase rate of the voltage load is slowing down with the increase of load.

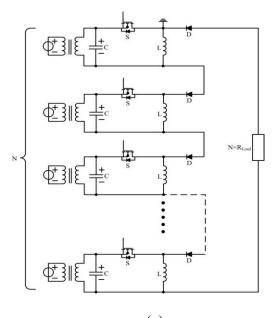

In order to obtain higher output voltage, the basic concept of Marx circuit is used for reference, and the inductor is connected in series in series. At the same time, the resistance of the load is increased with the inductor increasing, which ensures the discharge time constant as  $L/R_{load}$ . The schematic diagram and the physical diagram of the experimental circuit are shown in Figure 15.

(b)

Figure 15 Voltage adder using simple IES circuit based on MOSFET. (a) The circuit principle diagram (b) Physical diagram

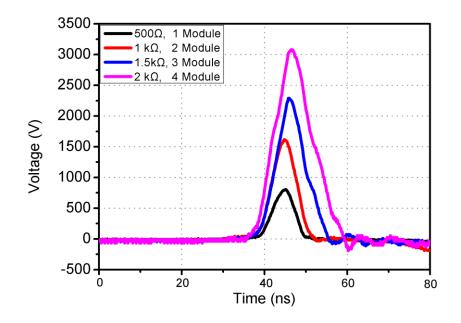

In the experiment, we select 4 modules to stack in series, and the circuit of each module is the same as that used in the 2.2. The load resistance in the experiment increases from 500 ohms to 2000 ohms. The load resistance in the experiment increases from 500 ohms to 2 thousand ohms.

Figure 16 Output voltage waveforms of the voltage adder using simple IES circuit based on MOSFET.

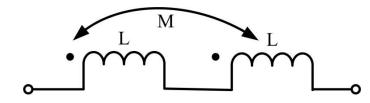

From the results of Figure 16, the increase of the output voltage can be obtained by connecting the modules of the IES circuit in series connection. However, the peak value of the voltage is not multiplied by the number of modules. And the width of the pulse has a tendency to widen with the number of modules increasing, especially in the part of the voltage fall. Obviously, these shortcomings are caused by the simple using pure inductors. In the series, we wanted the total inductance to be multiplied with the number of modules. However, it must be noted that in the process of inductor series, several important details are ignored. First, in the process of series, the inductance of the loop is increasing. This

will lead to the tail of the voltage during the discharge process. What is more serious is the process of inductance in series, if the coupling between inductors as shown in Figure 17, the total value will lead to mutual inductance deviation from ideal multiplier. It is assumed that the inductance of the inductor is L, the coupling inductance is M, and the inductance in series is the same as that in Figure 17. The sum of the two inductors at this time is not 2L but 2 (L+M). Obviously, the total amount of the inductor deviates from the ideal value, so the time constant of the series of two modules is not L/R<sub>load</sub>, but (L+M)/ $R_{load}$ . This causes the width of the discharge pulse to long.

Figure 17 A schematic diagram of the coupling effect between inductors

## 2.4 Summary and discussion

In this chapter, the basic knowledge of inductive energy storage is introduced, and the working principle of the traditional inductive energy storage pulse power source is discussed in detail. On the basis of the study of traditional inductive energy storage pulse power technology, a simple inductive energy storage circuit based on MOSFET switch is designed. The advantages and defects of the inductive energy storage circuit with MOSFET are fully demonstrated by theoretical analysis and experimental analysis. Because of the limited power capacity of MOSFET, it is difficult to meet the application of high pressure in the future. Therefore, in the light of the traditional Marx circuit, we propose a voltage adder based on a simple inductive energy storage circuit. The

characteristics of the voltage adder are studied by experiments. The research work in this chapter can be summed up as the following.

- Through the experiment, we find that the simple inductive energy storage circuit uses MOSFET as an opening switch, which can simplify the traditional inductive energy storage circuit.

- Using MOSFET switches and inductive energy storage, we can get nanosecond short pulses, and get voltage gain easily. As we did in experiments, we can amplify the voltage of 12V to 800V.

- The disadvantage of inductive energy storage is that the load matching is difficult, and it is difficult to get a standard rectangular pulse.

- Although the accumulation of the module can further improve the voltage, the peak output voltage is not an ideal increase, and the pulse width is widened with the increase of the number of modules. It is obvious that the coupling between inductors cannot be ignored.

# CHAPTER III: VOLTAHE ADDING OF IES PLUSE FORMING LINES [19][20]

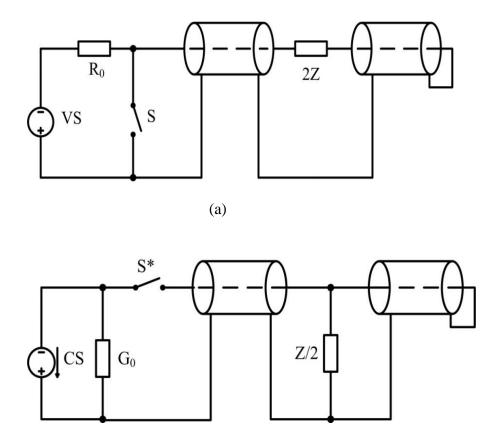

In the chapter II, a simple inductive energy storage circuit is discussed. Its advantage is that the voltage gain can be obtained, but the output waveform is not ideal. In order to improve the output waveform, some new pulse forming circuits are discussed in this chapter. Both methods use inductive energy storage (IES) instead of traditional capacitive energy storage (CES), which means that the PFLs are charged by current instead of voltage. One of the methods (Type A) used an additional transmission-line-transformer (TLT) to achieve the output voltage adding from multiple PFLs, while the other method (Type B) combined the functions of PFL and TLT into one set of transmission lines... Both methods have advantages and disadvantages over each other and both methods are believed to have certain significance in pulsed power generation.

# 3.1 Basic principle of IES pulse forming line (PFL) circuits

### 3.1.1 Symmetry geometric topology principle applied to IES circuit

The new circuit is not created by imagination, so the IES pulse forming line circuits are inspired by the traditional CES pulse forming lines and symmetry principle. From the analysis of the second chapter, we have already known that the energy storage density of a capacitor is  $\epsilon E^2/2$ , and it is  $\mu H^2/2$  with the IES. In other words, their mathematical expression of the energy storage density is same, if physical meaning is ignored. The propagation of electromagnetic waves should follow the Maxwell equation group [], as shown in [3-1]. It is not difficult to find that the electric field and the magnetic field are symmetric in the mathematical form from the equation group.

$$\begin{cases}

\nabla \cdot E = 0 \\

\nabla \times E = -\mu \frac{\partial H}{\partial t} \\

\nabla \cdot H = 0 \\

\nabla \times H = \varepsilon \frac{\partial E}{\partial t}

\end{cases}$$

[3-1]

The essence of the pulse power source circuit is the storage and propagation of the electromagnetic energy. Therefore, we have reason to suspect that there is some symmetry in the geometric topology of the CES circuit and the IES circuit. It is not difficult to find that the node voltage equations of the CES circuit, as shown in Figure 2(a), which has the same mathematical form as the loop current equations of the IES circuit, as shown in Figure 18.

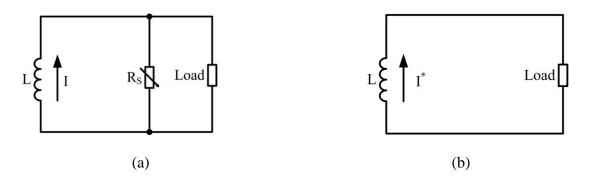

Figure 18 Symmetric geometric graphs of CES and IES

The components and branches in the CES circuit are expressed in the dotted line, and the voltage nodes in the circuit are expressed in the hollow circle, which is the dotted line diagram shown in Figure 18. Each loop in the dashed graph corresponds to a hollow circle, and the circles are connected by solid lines. As shown in Figure 18, a solid line diagram is obtained. This solid line diagram is the IES circuit corresponded from the CES. This corresponding relationship can be summed up as shown in Table 3.

| Table 3 S | ymmetric re | lation table | between the | CES and IES |

|-----------|-------------|--------------|-------------|-------------|

|           |             |              |             |             |

| CES                   | IES                   |

|-----------------------|-----------------------|

| node                  | loop                  |

| series and parallel   | parallel and series   |

| capacitance (C)       | inductance (L)        |

| charge (q)            | magnetic linkage (ψ)  |

| impedance (Z)         | admittance (Y)        |

| voltage charging      | current charging      |

| current amplification | voltage amplification |

| switch (off-on)       | switch (on-off)       |

| open circuit          | short circuit         |

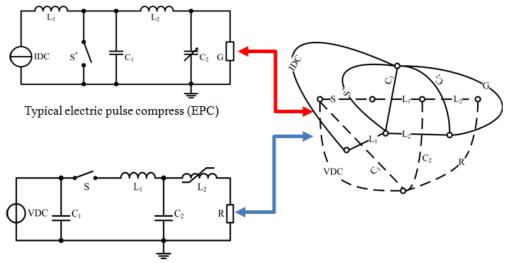

This kind of relationship and method can be extended to other derivative circuits. As in Figure 19, if this method be applied to the magnetic pulse compression circuit (MPC), as everyone knows, the new IES circuit called electric pulse compression circuit (EPC) can be obtained. If the symmetric law is applied to the Marx circuit, the new IES circuit called XRAM circuit [21] can be obtained..

Typical magnetic pulse compress (MPC)

Figure 19 Typical electric pulse compress (EPC) from magnetic pulse compress (MPC) by symmetric principle

Figure 20 XRAM circuit[21] and Marx circuit

XRAM

Figure 12 shows a typical Marx, and a XRAM circuit. It is well known that the Marx circuit topology is essentially "capacitor parallel charging and series discharge." Its functions are low voltage input and high voltage output. Using the symmetry law in Table 3, there is a new IES circuit whose topology is "series charging and parallel discharge", from the Marx, and its functions are low current input and high current output. The circuit topology and its characteristics derived from the symmetry law are confirmed in the paper [21].

## 3.1.2 Traditional CES-PFL and Type A IES-PFL

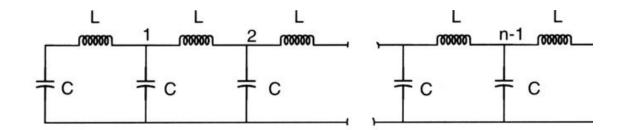

In the chapter II, from discussion and experiment, we find that it is difficult to obtain a rectangular pulse, only using pure inductor, with the simple IES circuit. However, it is easier to obtain the rectangular pulse with the simple CES circuit, using pure capacitor. The main reason is that, in a CES circuit, the switch can be opened to cut the pulse tail, so that a rectangular wave can be obtained. While, in the IES circuit, when the switch is opened, the pulse is output, as well as, the switch loses control of the pulse. This means that the inductor is fully discharged, pulse tail forming an exponential wave. In the past, we can use a simple method to get the rectangular pulse, without the switch being opened to eliminate the tail of the pulse. The specific circuit is shown in Figure 21(a). A rectangular wave can be obtained by discharging a matching load with a fully charged transmission line. This circuit is called capacitance energy storage pulse forming line. Using the principle of symmetry, a new pulse forming circuit is obtained. It can be called Type A IES forming line. The energy storage element of the pulse forming line is the inductor inside the transmission line, and the control switch is an opening switch.

Figure 21 The schematic diagram of the traditional CES pulse forming line and the type A IES pulse forming line (a) Traditional CES pulse line (b)Type A IES pulse forming line