#### REFERENCE ONLY

| UNIVERSITY OF LONDON THESIS                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Degree Pho Year 7005 Name of Author Gondon, T. G. W                                                                                                                                                                                                                                                                                   |

| COPYRIGHT  This is a thesis accepted for a Higher Degree of the University of London. It is an unpublished typescript and the copyright is held by the author. All persons consulting the thesis must read and abide by the Copyright Declaration below.                                                                              |

| COPYRIGHT DECLARATION I recognise that the copyright of the above-described thesis rests with the author and that no quotation from it or information derived from it may be published without the prior written consent of the author.                                                                                               |

| LOANS Theses may not be lent to individuals, but the Senate House Library may lend a copy to approved libraries within the United Kingdom, for consultation solely on the premises of those libraries. Application should be made to: Inter-Library Loans, Senate House Library, Senate House, Malet Street, London WC1E 7HU.         |

| REPRODUCTION  University of London theses may not be reproduced without explicit written permission from the Senate House Library. Enquiries should be addressed to the Theses Section of the Library. Regulations concerning reproduction vary according to the date of acceptance of the thesis and are listed below as guidelines. |

| A. Before 1962. Permission granted only upon the prior written consent of the author. (The Senate House Library will provide addresses where possible).                                                                                                                                                                               |

| B. 1962 - 1974. In many cases the author has agreed to permit copying upon completion of a Copyright Declaration.                                                                                                                                                                                                                     |

| C. 1975 - 1988. Most theses may be copied upon completion of a Copyright Declaration.                                                                                                                                                                                                                                                 |

| D. 1989 onwards. Most theses may be copied.                                                                                                                                                                                                                                                                                           |

| This thesis comes within category D.                                                                                                                                                                                                                                                                                                  |

| This copy has been deposited in the Library of UCC                                                                                                                                                                                                                                                                                    |

This copy has been deposited in the Senate House Library, Senate House, Malet Street, London WC1E 7HU.

# **Exploiting Development to Enhance the Scalability of Hardware Evolution**

# Submitted to the University of London for the degree of Doctor of Philosophy

Timothy Glennie Wilson Gordon

Department of Computer Science University College London July 2005 UMI Number: U592084

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U592084

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

## **Abstract**

Evolutionary algorithms do not scale well to the large, complex circuit design problems typical of the real world. Although techniques based on traditional design decomposition have been proposed to enhance hardware evolution's scalability, they often rely on traditional domain knowledge that may not be appropriate for evolutionary search and might limit evolution's opportunity to innovate.

It has been proposed that reliance on such knowledge can be avoided by introducing a model of biological development to the evolutionary algorithm, but this approach has not yet achieved its potential. Prior demonstrations of how development can enhance scalability used toy problems that are not indicative of evolving hardware. Prior attempts to apply development to hardware evolution have rarely been successful and have never explored its effect on scalability in detail.

This thesis demonstrates that development can enhance scalability in hardware evolution, primarily through a statistical comparison of hardware evolution's performance with and without development using circuit design problems of various sizes. This is reinforced by proposing and demonstrating three key mechanisms that development uses to enhance scalability: the creation of modules, the reuse of modules, and the discovery of design abstractions.

The thesis includes several minor contributions: hardware is evolved using a common reconfigurable architecture at a lower level of abstraction than reported elsewhere. It is shown that this can allow evolution to exploit the architecture more efficiently and perhaps search more effectively.

Also the benefits of several features of developmental models are explored through the biases they impose on the evolutionary search. Features that are explored include the type of environmental context development uses and the constraints on symmetry and information transmission they impose, genetic operators that may improve the robustness of gene networks, and how development is mapped to hardware. Also performance is compared against contemporary developmental models.

## **Acknowledgements**

I would like to thank the following people:

My supervisor, Peter Rounce for all his encouragement and advice, for proof reading, and for his help in funding both the hardware that my work relied on and my conference trips around the world.

My other supervisor, Peter Bentley for fostering my interest in development, adopting me as a student, showing me how to write, convincing me I had something to write about and pestering me into finishing this thesis. Peter's support has been invaluable.

Bill Langdon for our many constructive discussions about the field and my work, and Julian Miller for his useful comments.

Scott McMillan at Xilinx for his help debugging and patching the early versions of JBits.

Daniel Roggen for supplying the patterns for the Norwegian flag problem.

Mike Brent for providing access to and support for the VLSI consortium tools, and Denis Timm and the rest of the Systems Group for the use of their equipment, from crocodile clips to oscilloscopes.

Matt Trotter, David Corney, Rob Burbidge and the other members of nUCLEAR and Primal, for helping me understand Machine Learning and Evolutionary Computation and for their friendship. Dirk Weirich for showing me how a Ph.D. should be done.

My parents, without whose support and encouragement this work would never have been started, let alone finished.

Finally I would like to thank my girlfriend Lianne King for so much: listening to my reasoning, double checking my algebra, sitting through endless practice talks, helping format and proof read this document, and putting up with a lot of boring weekends. You are a star!

# **Contents**

| A | bstract2                                          |

|---|---------------------------------------------------|

| A | cknowledgements3                                  |

| C | ontents4                                          |

| L | ist of Figures9                                   |

| L | ist of Tables12                                   |

| 1 | Introduction14                                    |

|   | 1.1 Scalability                                   |

|   | 1.2 Hardware Evolution                            |

|   | 1.2.1 An Example of Hardware Evolution17          |

|   | 1.2.2 Abstraction in Hardware Evolution           |

|   | 1.3 Development                                   |

|   | 1.3.1 Differential Gene Activation                |

|   | 1.3.2 Gene Regulatory Networks21                  |

|   | 1.3.3 Intercellular Communication                 |

|   | 1.3.4 Problems Suited to Development              |

|   | 1.4 Motivation and Hypothesis                     |

|   | 1.5 Outline                                       |

| 2 | Literature Review27                               |

|   | 2.1 Hardware Evolution                            |

|   | 2.1.1 Applications of Hardware Evolution          |

|   | 2.1.2 Concepts for Classifying Hardware Evolution |

|   | 2.1.3 Research on Innovation                      |

|   | 2.1.4 Research on Generalisation                  |

|   | 2.1.5 Research on Performance and Evolvability60  |

|   | 2.2 Development                                   |

|   | 2.2.1 Applications of Developmental Models        |

|   | 2.2.2 Biological Background                       |

|   | 2.2.3 Benefits of Development74                   |

|   | 2.2.4 Computational Models of Development                         | 78  |

|---|-------------------------------------------------------------------|-----|

|   | 2.2.5 Development and Hardware                                    | 96  |

|   | 2.3 Summary                                                       | 104 |

| 3 | A Platform for Scalable, Innovative Hardware Evolution            | 106 |

|   | 3.1 Design Criteria for the Hardware Evolution Platform           | 106 |

|   | 3.1.1 Features for Innovation                                     | 106 |

|   | 3.1.2 Features for Evolvability                                   | 107 |

|   | 3.1.3 Features for Scalability                                    | 108 |

|   | 3.1.4 Features for Flexibility                                    | 108 |

|   | 3.1.5 Device Class Selection                                      | 109 |

|   | 3.1.6 Criteria for Intrinsic Hardware Evolution                   | 110 |

|   | 3.2 Platform Design                                               | 112 |

|   | 3.2.1 The Virtex Architecture                                     | 112 |

|   | 3.2.2 Platform Description                                        | 114 |

|   | 3.3 Platform Validation                                           | 116 |

|   | 3.3.1 The Adder problem                                           | 116 |

|   | 3.3.2 Validation of the Genetic Algorithm                         | 117 |

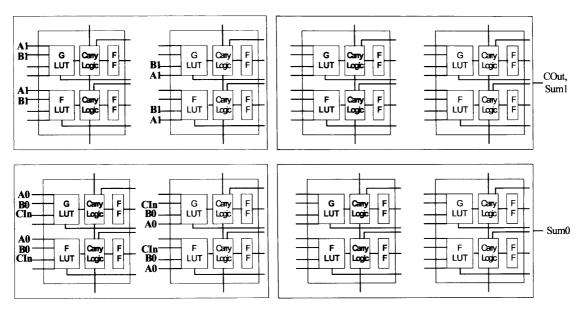

|   | 3.3.3 A Demonstration of Low Abstraction Evolution using Virtex   | 120 |

|   | 3.4 Summary                                                       | 125 |

| 4 | Modularity and Abstraction in Developmental Hardware Evolution    | 126 |

|   | 4.1 Design Criteria for a Developmental Hardware Evolution System | 126 |

|   | 4.1.1 General criteria                                            | 127 |

|   | 4.1.2 Criteria for Hardware Evolution                             | 128 |

|   | 4.2 An Exploratory Developmental System                           | 129 |

|   | 4.2.1 Context, Regulation and Communication                       | 129 |

|   | 4.2.2 Mapping Development to Hardware                             | 133 |

|   | 4.3 Scalability and Modules                                       | 138 |

|   | 4.4 Abstraction in Action                                         | 139 |

|   | 4.4.1 Parameter Selection                                         | 140 |

|   | 4.4.2 Evolution of Adders                                         | 140 |

|   | 4.5 Analysis                                                      | 142 |

|   | 4.5.1 Modules in Development                                      | 144 |

|   | 4.6 Summary                                                       | 146 |

| Development of Optimal Adder Designs                      | 147                   |

|-----------------------------------------------------------|-----------------------|

| 5.1 Pattern Formation                                     | 149                   |

| 5.1.1 Measuring Performance using Target Patterns         | 149                   |

| 5.1.2 Assessing Pattern Formation                         | 151                   |

| 5.1.3 Improving Intercellular Communication               | 155                   |

| 5.1.4 The Totalistic Developmental System                 | 156                   |

| 5.1.5 A Diffusion-like Model of Protein Concentrations    | 160                   |

| 5.1.6 Outer Totalistic Development                        | 162                   |

| 5.2 Exploring the Formation of Robust Regulatory Networks | 166                   |

| 5.2.1 Experiment 4A: Rule Duplication                     | 167                   |

| 5.2.2 Experiment 4B: Random Rule Insertion                | 168                   |

| 5.3 Mapping Regulatory Networks to Circuit Designs        | 169                   |

| 5.3.1 Exploring Protein to Logic Mappings                 | 170                   |

| 5.3.2 Exploring Logic and Routing                         | 181                   |

| 5.4 Summary of the Final Developmental Model              | 182                   |

| 5.4.1 The Protein Layer                                   | 182                   |

| 5.4.2 The Virtual FPGA                                    | 185                   |

| 5.4.2 The Architecture Layer                              | 186                   |

| 5.5 Summary                                               | 188                   |

| Scalability                                               | 191                   |

| 6.1 Evolving Patterns on Large Arrays                     | 193                   |

| 6.1.1 Experimental Setup                                  | 193                   |

| 6.1.2 Initial Considerations                              | 194                   |

| 6.1.3 Evolving Translational Patterns with Small Motifs   | 196                   |

| 6.1.4 Evolving Patterns with Large Motifs                 | 201                   |

| 6.1.5 Evolving Non-Uniform Patterns                       | 206                   |

| 6.1.6 Comparison with Roggen and Federici                 | 207                   |

| 6.1.7 Comparison with Miller                              | 210                   |

| 6.1.8 Universal Initial Conditions                        | 212                   |

| 6.1.9 Summary and Guidelines for Suitable Problems        | 213                   |

| 6.2 Scalability and the n-bit Adder with Carry Problem    | 214                   |

| 6.2.1 Experimental Setup                                  | 214                   |

| 6.2.2 Results and Analysis                                | 215                   |

| 6.2.3 Circuit Analysis                                    | 220                   |

| 6.3 Scalability and the Even n-bit Parity Problem         | 228                   |

|                                                           | 5.1 Pattern Formation |

|        | 6.3.1 Problem Description                                                                                       | 228        |

|--------|-----------------------------------------------------------------------------------------------------------------|------------|

|        | 6.3.2 Experimental Setup                                                                                        | 229        |

|        | 6.3.3 Results and Analysis                                                                                      | 230        |

|        | 6.3.4 Circuit Analysis                                                                                          | 232        |

|        | 6.4 Summary                                                                                                     | 236        |

| 7      | Conclusions and Further Work                                                                                    | 238        |

|        | 7.1 Thesis Précis                                                                                               | 238        |

|        | 7.2 Major Contributions                                                                                         | 238        |

|        | 7.3 Minor Contributions                                                                                         | 241        |

|        | 7.4 Further Work                                                                                                | 245        |

|        | 7.4.1 Short-term Issues                                                                                         | 245        |

|        | 7.4.2 Long-Term Issues                                                                                          | 250        |

|        | 7.5 Summary                                                                                                     | 251        |

| R      | eferences                                                                                                       | 252        |

|        | ppendix A: Intrinsic Device Survey  ppendix B: Design Space for the Direct Intrinsic Evolution of Two Bit Adder | 273        |

| w      | ith Carry Circuits                                                                                              | 276        |

|        | B.1 Design Space                                                                                                | 276        |

|        | B.2 Chromosome Structure                                                                                        | 276        |

| A      | ppendix C: Architecture and Virtual Protein Mappings for the Exploratory                                        |            |

| D      |                                                                                                                 | 279        |

|        | evelopmental System                                                                                             |            |

|        | C.1 Virtual Architecture Mapping                                                                                |            |

|        |                                                                                                                 | 279        |

| A      | C.1 Virtual Architecture Mapping                                                                                | 279        |

|        | C.1 Virtual Architecture Mapping  C.2 Developmental Rule Postcondition Key                                      | 279<br>281 |

| E      | C.1 Virtual Architecture Mapping  C.2 Developmental Rule Postcondition Key                                      | 279<br>281 |

| E<br>A | C.1 Virtual Architecture Mapping  C.2 Developmental Rule Postcondition Key                                      | 279281283  |

| Appendix D3: Protein map showing the development of a solution from        |  |

|----------------------------------------------------------------------------|--|

| Experiment 7C                                                              |  |

| Appendix D4: Protein map showing the development of a solution from        |  |

| Experiment 8A(2)292                                                        |  |

| Appendix D5: Protein map showing the development of a solution from        |  |

| Experiment 8A(3)295                                                        |  |

| Appendix D6: Protein map showing the best solution found to the 7x7 cheque |  |

| problem298                                                                 |  |

| Appendix E1: List of Publications301                                       |  |

| Appendix E2: CEC Best Student Paper Award302                               |  |

# **List of Figures**

| Figure 1.2.1: An example of hardware evolution.                                        | 18  |

|----------------------------------------------------------------------------------------|-----|

| Figure 1.3.1: An example GRN with 5 regulatory genes (1-5) and their products          |     |

| (A-D)                                                                                  | 21  |

| Figure 1.3.2: Three Drosophila heads, (a) wild type, (b) with the antp mutation and    |     |

| (c) with both pb and antp mutations.                                                   | 22  |

| Figure 2.1.1: The elements of hardware evolution.                                      | 27  |

| Figure 2.1.2: The interrelationships between hardware design and synthesis, and        |     |

| Evolutionary Computation                                                               | 28  |

| Figure 2.1.3: The hardware abstraction space defined by constraint.                    | 38  |

| Figure 2.1.4: Common levels of abstraction applied to hardware evolution research      | 40  |

| Figure 2.2.1: DNA transcription.                                                       | 72  |

| Figure 3.2.1: A simplified representation of the Virtex architecture.                  | 114 |

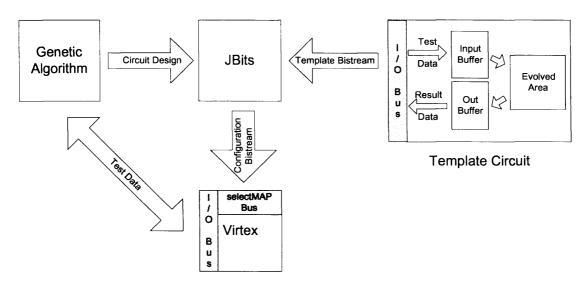

| Figure 3.2.2: The hardware evolution platform.                                         | 115 |

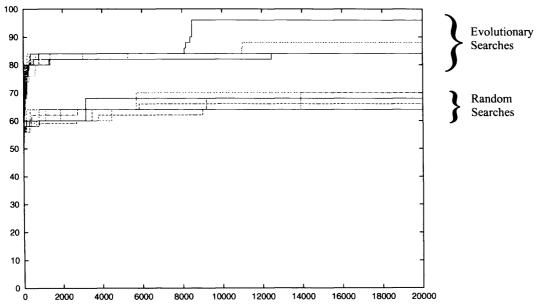

| Figure 3.3.1: Best fitness against generations of an evolved two bit adder, on a 3x3   |     |

| array along with ten random searches of the same length.                               | 119 |

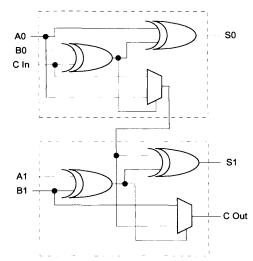

| Figure 3.3.2: Example of an adder evolved on a 3x3 array.                              | 120 |

| Figure 3.3.3: Inputs and outputs to the evolved area.                                  | 123 |

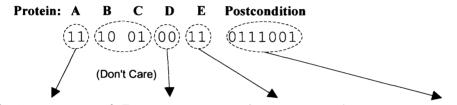

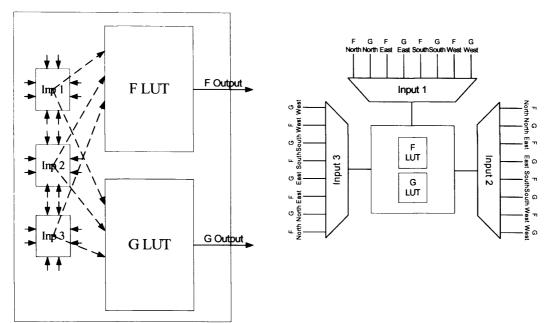

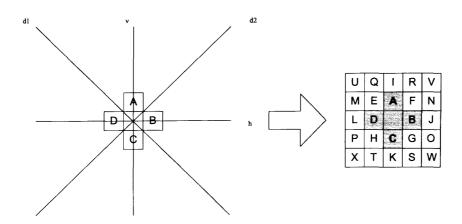

| Figure 4.2.1: The Developmental Rule of the Exploratory System                         | 131 |

| Figure 4.2.2: A developmental timestep highlighting the protein interaction model      |     |

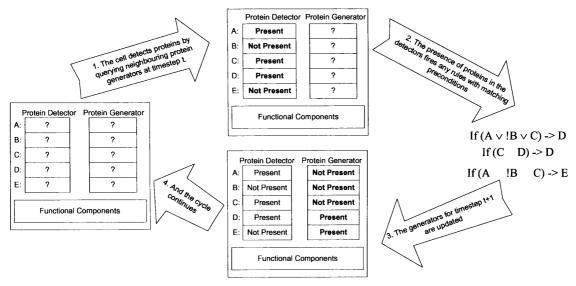

| within a cell                                                                          | 132 |

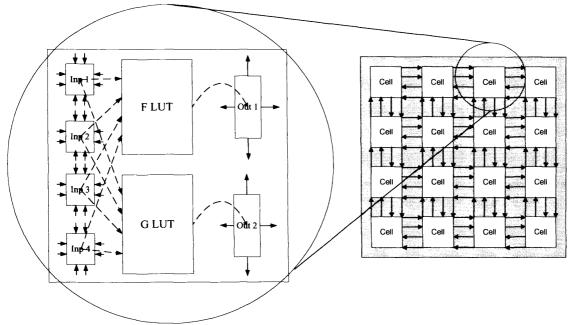

| Figure 4.2.3: The virtual FPGA architecture. Each CLB contains 2 LUTs that share       |     |

| the 4 CLB inputs.                                                                      | 134 |

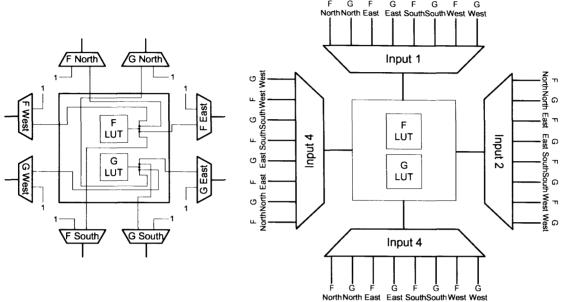

| Figure 4.2.4(a): The outputs of the virtual CLB. Each LUT can drive a signal north,    |     |

| south east and west. When not driven, an output line is pulled high.                   | 135 |

| Figure 4.2.4(b): The inputs of the virtual CLB.                                        | 135 |

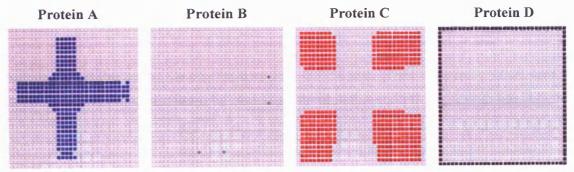

| Figure 4.5.1: A solution to the two bit adder problem found by the developmental       |     |

| system.                                                                                | 145 |

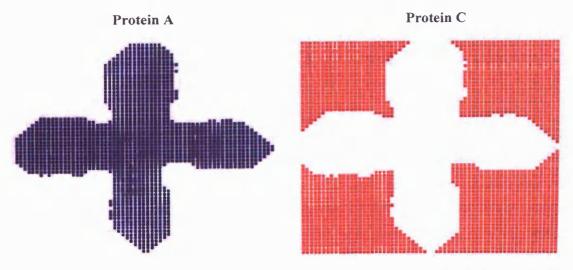

| Figure 5.1.1: The hand-designed adder circuit and a pattern of proteins that           |     |

| distinguishes cells using different logic.                                             | 150 |

| Figure 5.1.2: The totalistic developmental rule.                                       | 157 |

| Figure 5.1.3: The Outer Totalistic developmental rule                                  | 163 |

| Figure 5.3.1(a): A hand-designed adder based on a new virtual architecture with        |     |

| fixed routing.                                                                         | 171 |

| Figure 5.3.1(b): A pattern of proteins that distinguishes cells using different logic. | 171 |

| Figure 5.3.1(c): The adder of 5.3.1(a) with additional probe points used in           |     |

|---------------------------------------------------------------------------------------|-----|

| Experiment 5E.                                                                        | 171 |

| Figure 5.3.2: A graph of the number of generations required to evolve all functions   |     |

| of a three bit LUT.                                                                   | 174 |

| Figure 5.3.4: A hand-designed adder using a propagate-generate structure with         |     |

| fixed feedforward routing, and a pattern of proteins that distinguishes cells         |     |

| configured with different logic.                                                      | 179 |

| Figure 5.3.5(a): The three input virtual CLB.                                         | 182 |

| Figure 5.3.5(b): Inputs sources for the three input virtual CLB.                      | 182 |

| Figure 5.4.1: The contents of a cell in the protein layer.                            | 183 |

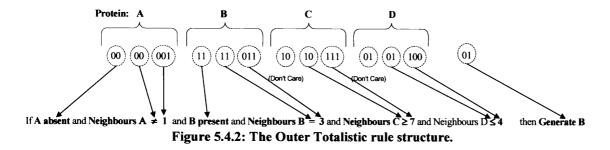

| Figure 5.4.2: The Outer Totalistic rule structure.                                    | 184 |

| Figure 5.4.3: The protein generation process.                                         | 185 |

| Figure 5.4.4: The Virtual Architecture. Only inputs and LUT logic are                 |     |

| reconfigurable.                                                                       | 186 |

| Figure 5.4.5: The contents of a cell in the architecture layer.                       | 187 |

| Figure 5.4.6(a): Counters are updated during an architecture mapping cycle            | 188 |

| Figure 5.4.6(b): A CLB configuration is derived at the end of development             | 188 |

| Figure 6.1.1(a): The maximum number of unique contexts available with simple          |     |

| initial conditions                                                                    | 199 |

| Figure 6.1.1(b): An increased number of unique contexts following the                 |     |

| introduction of symmetry-breaking initial conditions                                  | 199 |

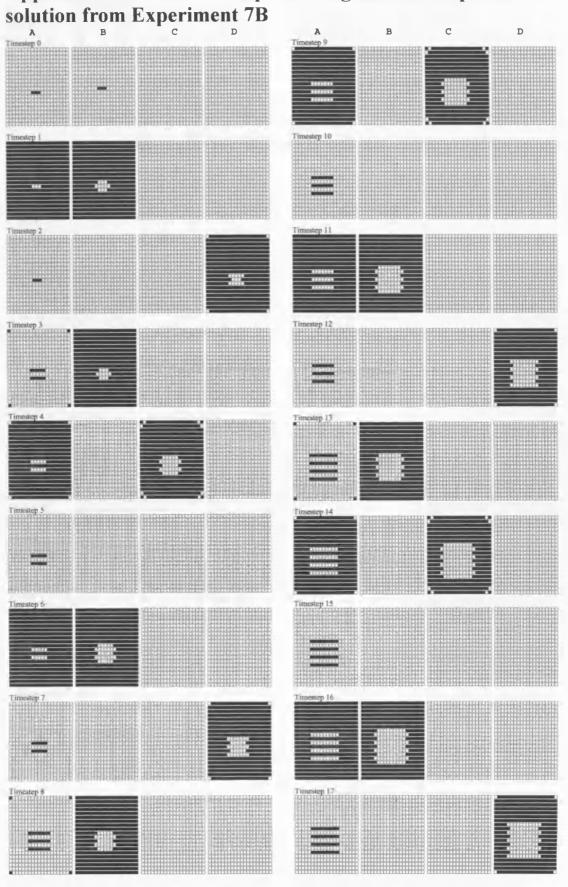

| Figure 6.1.2: The growth strategy used by all optimal solutions to Experiment 7B      | 199 |

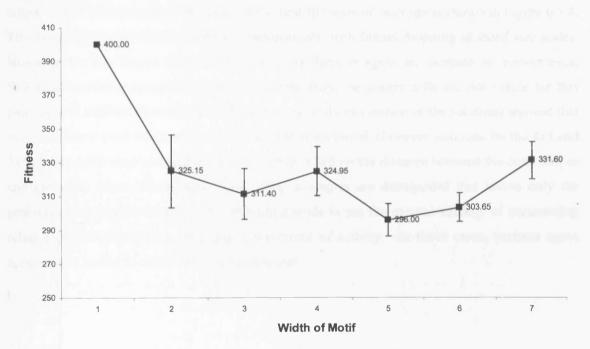

| Figure 6.1.3: A plot of mean fitness against motif width for 20 runs of the evolution |     |

| of a pattern with a chequed motif                                                     | 204 |

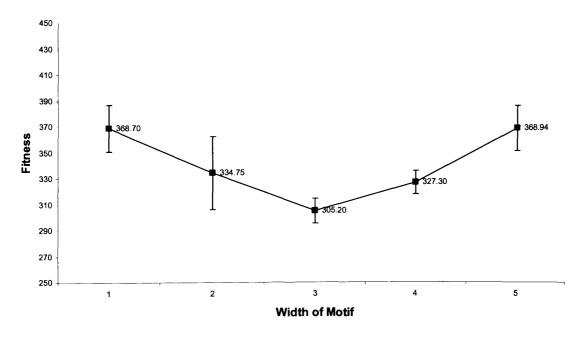

| Figure 6.1.4: A plot of mean fitness against motif width for 20 runs of the evolution |     |

| of a pattern with a striped motif.                                                    | 205 |

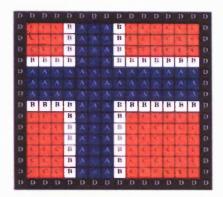

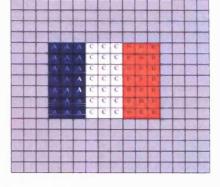

| Figure 6.1.5(a): A pattern based on the Norwegian flag.                               | 207 |

| Figure 6.1.5(b): A pattern based on the French flag.                                  | 207 |

| Figure 6.1.6: Protein map for the best evolved 16x16 Norwegian flag                   | 208 |

| Figure 6.1.7: Protein map for the best evolved 32x32 Norwegian flag                   | 208 |

| Figure 6.1.8: Protein map for the best evolved 64x64 Norwegian flag                   | 208 |

| Figure 6.1.9: A set of universal initial conditions that break all symmetry and       |     |

| permit the maximum number of unique contexts.                                         | 212 |

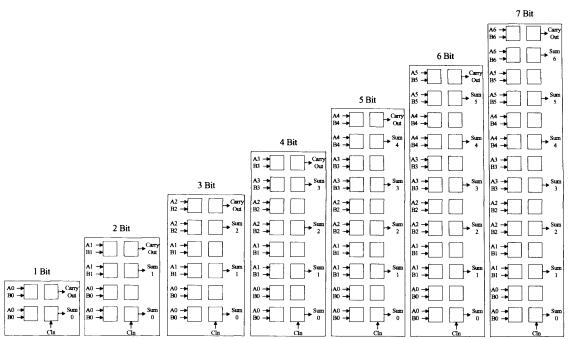

| Figure 6.2.1: Diagram of evolved array areas, input points and output points for the  |     |

| adder scalability experiments                                                         | 215 |

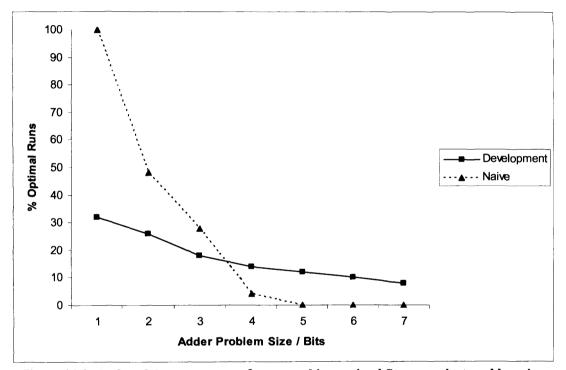

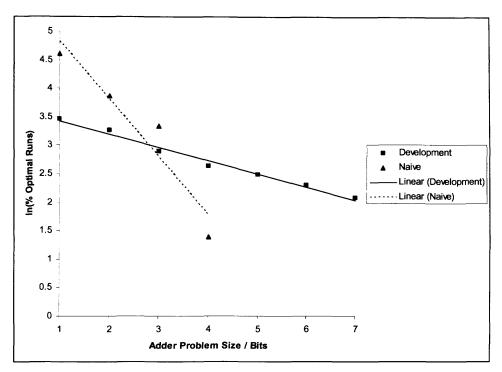

| Figure 6.2.2: A plot of the percentage of runs reaching optimal fitness against       |     |

| nrohlem size                                                                          | 216 |

| Figure 6.2.3: A plot of the percentage of runs reaching optimal fitness, linearised                         |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| by applying a logarithmic function, against problem size.                                                   | 217 |

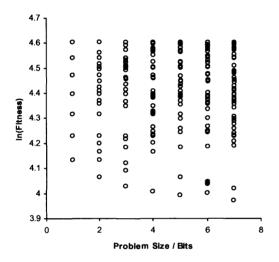

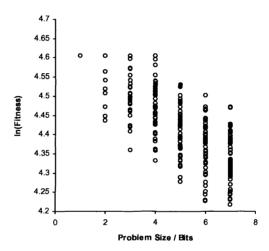

| Figure 6.2.4(a): A plot of fitness normalised to 100 and linearised by applying a                           |     |

| logarithmic function, against problem size for the developmental system, for all 50                         |     |

| runs                                                                                                        | 218 |

| Figure 6.2.4(b): A plot of fitness normalised to 100 and linearised by applying a                           |     |

| logarithmic function, against problem size for the naïve system, for all 50 runs                            | 218 |

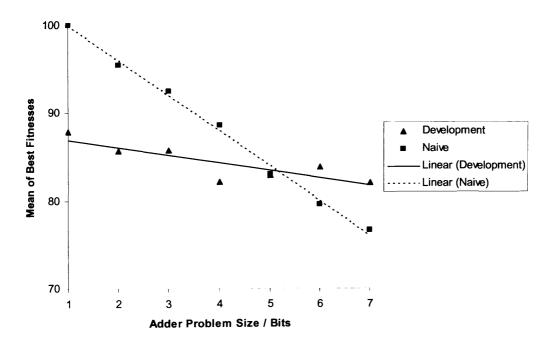

| Figure 6.2.5: A plot of the mean of the best fitnesses for each problem size against                        |     |

| problem size.                                                                                               | 219 |

| Figure 6.2.6: A plot of the difference between $Dev_{\overline{f}best}$ and $Nv_{\overline{f}best}$ against |     |

| problem size                                                                                                | 220 |

| Figure 6.2.7: An evolved optimal two bit adder with carry                                                   | 221 |

| Figure 6.2.8(a): The first optimal seven bit adder with carry evolved                                       | 225 |

| Figure 6.2.8(b): A diagram of the adder in Figure 6.2.8(a) highlighting the level of                        |     |

| design reuse                                                                                                | 225 |

| Figure 6.2.9(a): The second optimal seven bit adder with carry evolved                                      | 226 |

| Figure 6.2.9(b): A diagram of the adder in Figure 6.2.9(a) highlighting the level of                        |     |

| design reuse                                                                                                | 226 |

| Figure 6.2.10: A plot of the mean of the best fitnesses against problem size for                            |     |

| incremental and non-incremental evolution.                                                                  | 227 |

| Figure 6.3.1: The evolved array areas, input points and output points for the two bit                       |     |

| to seven bit parity scalability experiments.                                                                | 230 |

| Figure 6.3.2: Plot of the percentage of optimal solutions found for the                                     |     |

| developmental and naïve system on the even n-bit parity problem.                                            | 232 |

| Figure 6.3.3(a): The first 8 bit parity circuit evolved with development, showing                           |     |

| inputs, K-Maps of LUT configurations and the logical outputs of each LUT in the                             |     |

| context of its inputs.                                                                                      | 233 |

| Figure 6.3.3(b): Distinct CLB types of the same circuit.                                                    | 233 |

| Figure 6.3.4: A plot of the percentage of optimal solutions using development for                           |     |

| both problems, linearised by application of a logicarithmic function, against                               |     |

| problem size measured in CLBs.                                                                              | 234 |

| Figure 6.3.5(a): An optimal evolved solution to the eight bit parity problem, with                          |     |

| two distinct CLB types P and Q.                                                                             | 235 |

| Figure 6.3.5(b): The optimal 12 bit solution generated when the same rule set is                            |     |

| applied to the larger array.                                                                                | 235 |

# **List of Tables**

| 1 able 2.2.1: Processes used by some models of development                             | 83  |

|----------------------------------------------------------------------------------------|-----|

| Table 3.3.1: The cell function lookup table.                                           | 118 |

| Table 3.3.2: Results from ten runs of Miller's extrinsic adder problem across a        |     |

| range of array sizes                                                                   | 119 |

| Table 3.3.3: Results from ten runs of intrinsic two bit adder evolution                | 124 |

| Table 4.4.1: Equivalent naïve representation for the adder problem.                    | 141 |

| Table 4.4.2: Parameters for the evolutionary experiments                               | 141 |

| Table 4.4.3: Five runs of evolution and five random searches, both with and            |     |

| without development                                                                    | 142 |

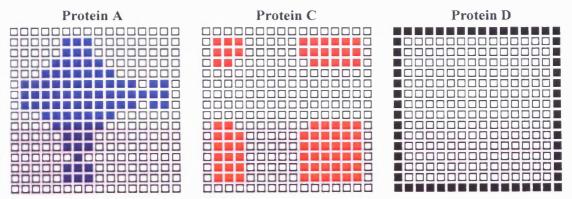

| Table 5.1.1: Results of evolving target patterns of proteins A-E on 2x5 and 3x5 cell   |     |

| arrays with the exploratory system.                                                    | 152 |

| Table 5.1.2: Results from the evolution of target patterns on 2x5 and 3x5 arrays       |     |

| with the initial model of development.                                                 | 153 |

| Table 5.1.3: An example rule set that generates a travelling wavefront with the new    |     |

| model                                                                                  | 156 |

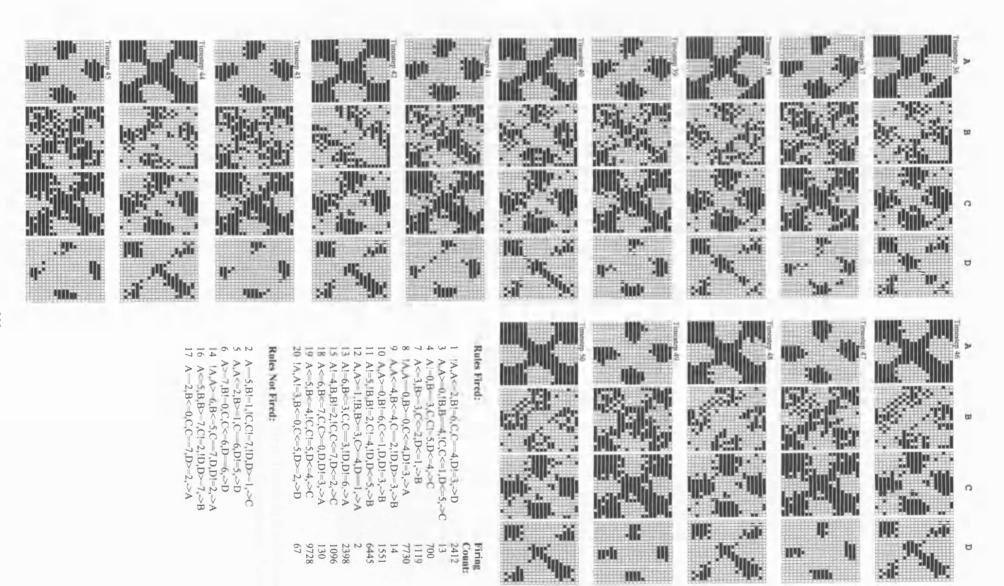

| Table 5.1.4: Initial protein concentrations, target protein patterns and best patterns |     |

| evolved with the totalistic system. The lower right hand side of the table shows a     |     |

| key to protein concentrations.                                                         | 158 |

| Table 5.1.5: Results from the evolution of patterns on a 3x5 cell array using the      |     |

| totalistic model                                                                       | 159 |

| Table 5.1.6: Initial conditions and target patterns for Experiments 3A and 3B          | 164 |

| Table 5.1.7: Results of evolving target patterns on and 3x5 cell arrays with the       |     |

| totalistic system                                                                      | 164 |

| Table 5.1.8: Results from evolution of the adder target pattern with various number    |     |

| of rules using the outer totalistic system.                                            | 166 |

| Table 5.2.1: Results of experiments involving rule duplication and removal             | 168 |

| Table 5.3.2: Results of experiments pattern-circuit mapping models with altered        |     |

| biases                                                                                 | 175 |

| Figure 5.3.3: The structural proteins introduced to (a) remove bias towards any        |     |

| logic function and (b) to provide bias towards logic that routes signals               | 176 |

| Table 5.3.1: Results of experiments exploring the original pattern to circuit          |     |

| mapping model                                                                          | 172 |

| Table 5.3.3: Results of experiments with a new problem representation and test         |     |

| nattern                                                                                | 180 |

| Table 6.1.1: Initial protein concentrations and target protein patterns for the      |     |

|--------------------------------------------------------------------------------------|-----|

| evolution of chequed and striped patterns on a 20x20 array                           | 198 |

| Table 6.1.2: Results from the evolution of patterns across large arrays.             | 199 |

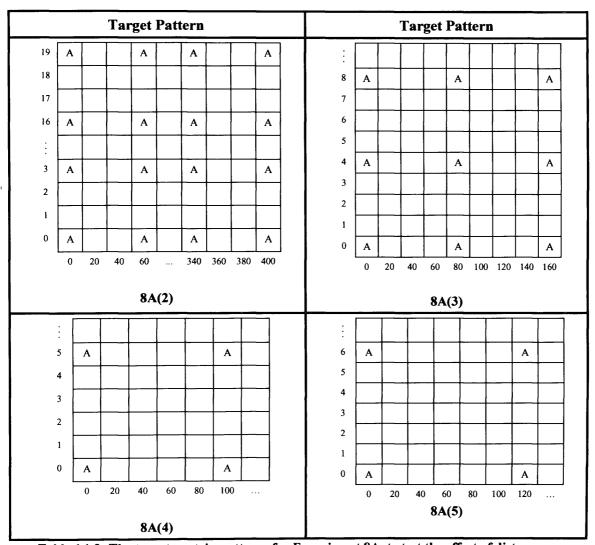

| Table 6.1.3: The target protein patterns for Experiment 8A, to test the effect of    |     |

| distance on information transmission.                                                | 202 |

| Table 6.1.4: Results of Experiment 8A, testing the effect of distance on information |     |

| transmission.                                                                        | 203 |

| Table 6.1.5: Comparison between the current system and approximate results for       |     |

| both the Morphogenetic and Embryonic systems presented in (Roggen and Federici,      |     |

| 2004)                                                                                | 208 |

| Table 6.1.6: Comparison between the Outer Totalistic model and Miller's CGP          |     |

| system used in (Miller, 2004) with zero and two proteins.                            | 211 |

| Table 6.2.1: Parameters for the evolutionary experiments                             | 214 |

| Table 6.2.2: Equivalent naïve representation for the adder problem.                  | 215 |

| Table 6.2.3: Results of the adder scalability experiments                            | 216 |

| Table 6.3.1: Equivalent naïve representation for the adder problem.                  | 230 |

| Table 6.3.2: Results of the even parity scalability experiments. Fitness values are  |     |

| normalised to 100.                                                                   | 231 |

| Table A1: Commercial digital devices.                                                | 274 |

| Table A2: Commercial analogue devices.                                               | 274 |

| Table A3: Research-specific devices.                                                 | 275 |

| Table B1: Details of the input genes for one CLB                                     | 277 |

| Table B2: Details of the CLB internal genes for one CLB                              | 278 |

| Table B3: Details of the output-MUX-to-Single-PIP genes for one CLB                  | 278 |

| Table C1: Output multiplexer-to-single lines used to carry signals from the F-       |     |

| LUTs.                                                                                | 279 |

| Table C2: Output multiplexer-to-single lines used to carry signals from the G-       |     |

| LUTs.                                                                                | 279 |

| Table C3: The routes used to map the Virtual Architecture inter-CLB routing to       |     |

| Virtex                                                                               | 280 |

| Table C4: Protein and Input rule postconditions, and their effect during             |     |

| development                                                                          | 281 |

| Table C5: Logic and output postconditions, and their effect during development       | 282 |

### 1 Introduction

In the hundred years since John Ambrose Fleming invented the diode at University College London and gave birth to the field, electronics has become a well established engineering discipline. The resulting reservoir of knowledge has allowed the commercial semiconductor industry to grow at a remarkable rate in the intervening years, both in volume and device complexity with the now-famous Moore's Law holding true for forty years (Moore, 1965). The advent of ever cheaper, more efficient and more powerful electronics has changed society to the point where reliance on electronics for many daily tasks is now common. However there are still many niches where even cheaper, more efficient and more powerful hardware would be useful and it is the desire to exploit these niches that drives industry growth. In recent years improvements in hardware have for the most part been achieved by technology scaling: improving hardware fabrication processes rather than moving to fundamentally new circuit medium technologies or circuit designs. Yet it is becoming increasingly difficult to sustain the current rate of scaling using today's technologies without resorting to expensive tricks (McFarland, 1997; Borkar, 2000; Kahng, 2004).

This means that in the medium term the requirement for innovative circuit designs is likely to grow as it becomes necessary to squeeze more and more out of current circuit medium technologies. The long-term solution is likely to lie in the development of new technologies. But even when they do eventually become feasible commercially, they are likely at best to require design features that current circuit design methodologies were not conceived to provide, such as fault tolerance, and might require a complete rewriting of the design rules. Hence in the long term there is also a significant requirement for innovative circuit designs and design methodologies, and the cost of developing these in man-hours of research and design is likely to be considerable.

Over the past decade a new field applying evolutionary techniques to hardware design and synthesis has emerged. These techniques may be able provide a new option: evolution can be used to design and synthesise innovative circuits automatically, or at least aid in their design and synthesis by revealing innovative design concepts that traditional designers can learn from.

#### 1.1 Scalability

An interesting feature of hardware evolution that is potentially useful for tackling the issues outlined above is its ability to discover circuits without relying on all the constraints that human designers require to simplify the design process. It has been shown that by relaxing such constraints evolution can discover innovative circuits more efficient than any conventional designs (Thompson and Layzell, 1999). So it may seem surprising that there are few examples of evolutionary methods being applied to real-world circuit design problems. This can be attributed to a number of issues including the limited robustness of, and difficulty in interpreting evolved solutions. But the most conspicuous issue is scalability: larger, more complex problems typical of those faced by real-world designers tend to be difficult for evolution to solve. Schema theorem suggests that evolution inherently designs solutions by combining small, weakly interacting components incrementally (Goldberg, 1989). It is often unclear how the parameters of a design problem can be presented to evolution so that such components emerge, and it rapidly becomes more difficult to do so as problem size increases and the fraction of potential solutions sampled by the algorithm at any one time diminishes (Thierens, 1999). The issue of scalability is likely to be most prevalent when evolution juggles huge numbers of tiny components as it does when designing a large circuit when traditional constraints have been relaxed. It is here that evolution is most in need of a helping hand and it is here that there is the greatest opportunity to discover innovative circuit designs

Many researchers have explored solving large problems with evolution by designing more complex components for evolution to operate on. Such an approach is usually dubbed Function Level Evolution (Higuchi et al., 1997; Zhao-Shuguang and Yang-Wanhai, 2002). This does not solve the scalability problem, but merely moves it somewhere else: a human expert is now required to design modules suitable for evolution (a tricky task in itself), and crucially the opportunity for innovative design within and between the modules is lost.

The conventional engineering approach to a solving large problem is to break it up into modules that interact with each other in a limited manner. For instance the software designer's tenet is that code should be arranged into modules with "low coupling" and "high cohesion" (Sommerville, 1992). The abstractions used by conventional circuit designers serve the same purpose. Perhaps because of the parallel between the weakly interacting components required by schema theorem and the modules that result from traditional design decomposition, some hardware evolution researchers have suggested using similar methods of decomposition to create a series of problems each of which is small enough for evolution to tackle (Torresen, 2002a; Shanthi et al., 2004). However decomposing a problem into strict sub-problems using traditional methods removes any opportunity for evolution to find innovative ways to partition

the problem itself. Furthermore there is no guarantee that the sub-problems that traditional designers find useful will be useful to evolution.

This thesis will argue that a better solution is for evolution to design its own modules from the ground up, thereby removing the need for a human designer, providing opportunity for innovation at all levels of abstraction, and allowing evolution to discover modules that are genuinely useful for evolutionary design rather than those presumed to be useful by a human designer.

Attempts at automatic modularisation in evolutionary design are not new. Methods such as Automatically Defined Functions (Koza, 1994) and Adaptive Representation through Learning (Rosca, 1995) have been used for many years in genetic programming, a branch of Evolutionary Computation. Although these have proved useful in many respects, the most impressive examples of evolutionary scalability, design innovation and automatic modularisation are still confined to biological evolution: the size and complexity of biological organisms ranges over many orders of magnitude, and for hundreds of millions of years evolution has managed to consistently generate new, innovative designs. Most large biological organisms are clearly highly modular: the body plans of most animals are made up of distinct tissues and organs. They also exhibit hierarchical modularity: insects have compound eyes and vertebrates segmented spines. These subcomponents are in turn composed of many cells.

The process that allows evolution to generate intricate, innovative organisms across such a wide range of sizes is *development*, the process by which egg becomes adult. This thesis will show that by applying a model of development to hardware evolution, evolution is able to discover large circuits without relying on the traditional abstractions that might limit innovation but would be necessary using a conventional evolutionary algorithm, and that there is potential benefit in allowing evolution to do so.

This thesis does not solve the scalability problem. It merely demonstrates a step towards that goal, highlighting mechanisms inherent to development that can enhance scalability, in particular for hardware evolution without the aid of the usual complement of traditional design constraints. In doing so, several models of biological development that have been tailored for both implementation in hardware and for the design of hardware are presented.

#### 1.2 Hardware Evolution

Evolutionary Computation is the field of solving problems using learning algorithms inspired by biological evolution. These algorithms are collectively known as *evolutionary algorithms*. They

model the principles of selection, variation and inheritance that are the basis of the theory of Darwinian evolution, and have been applied to a huge spectrum of problems from classic optimisation (Langdon, 1997) to the creation of original music (Biles, 1994). Typically they work on a population of prospective solutions in parallel. Each member of the population is evaluated according to a problem-specific *fitness function* that tests how well each solution performs a required task, and assigns it a *fitness* score. A *selection* operator then chooses solutions with higher fitness probabilistically from the population to form the basis of a new generation of solutions. These solutions are then varied. Most commonly this is achieved by randomly altering each solution to model *mutation*. Another common operation called *crossover* recombines two solutions in some way to model sexual reproduction. The process is then iterated for a number of generations until a stopping condition is met. Typical stopping conditions are the discovery of a solution with a given fitness, or the completion of a predefined number of generations.

This thesis concerns the application of evolutionary algorithms to the automatic design and synthesis of electronic circuits, a field that has been coined evolutionary electronics, evolvable hardware and hardware evolution amongst others. Throughout this thesis the field will be referred to as hardware evolution, and will be explored in more detail as the work presented here is set in context in Chapter 2. In order to familiarise the reader with how circuits might be evolved, an example of the hardware evolution is now presented using the evolutionary algorithm used throughout this thesis.

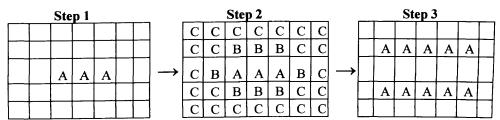

#### 1.2.1 An Example of Hardware Evolution

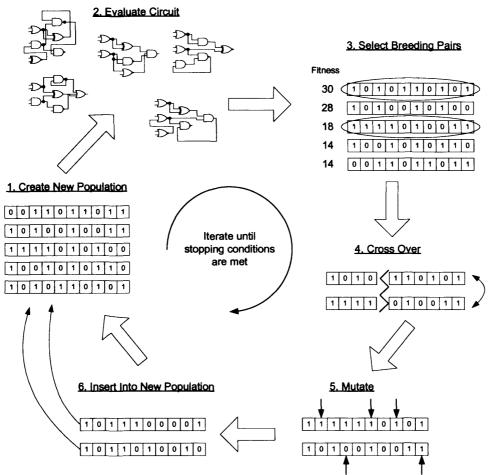

The class of evolutionary algorithm used in this thesis is a genetic algorithm (Goldberg, 1989). Most commonly these operate on a fixed size population of fixed length binary strings called chromosomes, where each bit can referenced by a unique index called a locus. Each chromosome encodes a set of parameters that describe a collection of electronic components and their interconnections, thus each set of parameter values represents an electronic circuit. The set of all possible combinations of parameter values defines the search space of the algorithm, and the circuits that they represent define the solution space of the algorithm. Traditionally every parameter set in the search space encodes a unique circuit description in the solution space. When referring to a chromosome / circuit pair, biological terminology is often used: the chromosome is often called the genotype and the circuit it represents is called the phenotype.

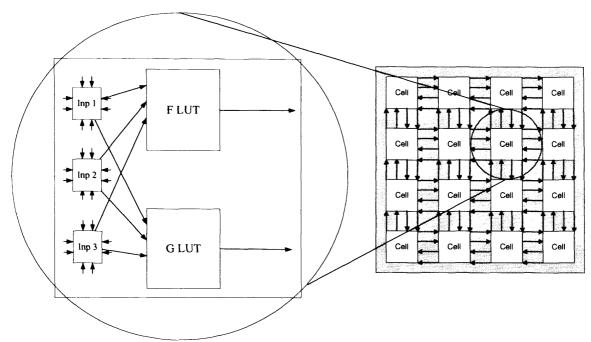

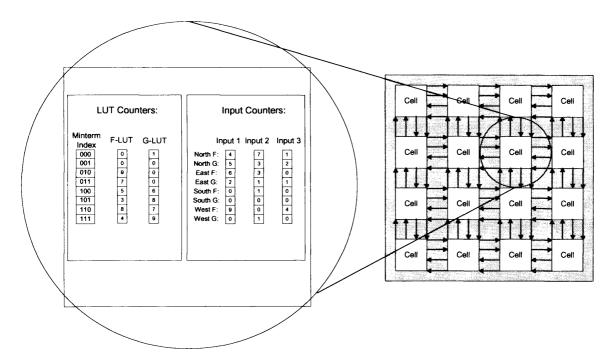

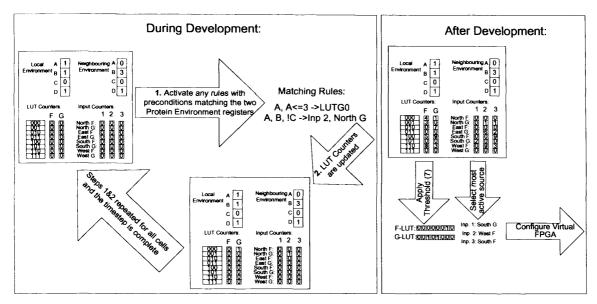

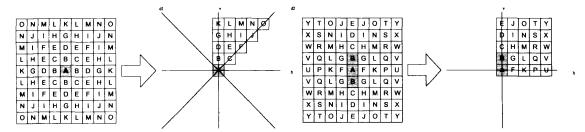

An example of hardware evolution is shown in Figure 1.2.1. The algorithm begins by initialising the bits of each chromosome with random values. The chromosomes are then

evaluated in turn by creating a circuit based on the parameter values, either as a simulated model of the circuit or as a concrete circuit embodied in reconfigurable hardware, an example of which is introduced in the next section. The circuit's fitness for performing the target task is then measured by passing it a set of test inputs and evaluating the circuit's output. The selection operator then populates the next generation of chromosomes probabilistically such that chromosomes with high fitness are more likely to be selected.

Figure 1.2.1: An example of hardware evolution.

There are many methods to achieve this, and the approach used in this thesis is called two-member tournament selection (Goldberg, 1989): the operator selects two individuals at random and compares their fitness. Only the individual with the highest fitness is inserted into the next generation. If they have equal fitness the individual to be inserted is chosen at random. Once the new population has been selected it is varied using one-point crossover and point mutation operators (Goldberg, 1989), again two common variation operators of many that have been reported. One point crossover recombines two chromosomes by choosing a locus at random along the chromosome and swapping every bit beyond this point between the strings. It is applied stochastically according to a fixed probability. Point mutation independently inverts each bit in the chromosome according to a fixed probability. Another crossover operator used occasionally in this thesis is uniform crossover. Here each bit in a chromosome is swapped

independently, according to a fixed probability. The crossover and mutation operators are applied to all members of the new population. Finally some copies of the best member of the original population are copied into the new population unchanged, a strategy called *elitism* (Goldberg, 1989). The new population is now complete and the algorithm then iterates the steps of evaluation, selection and variation until the stopping conditions are met.

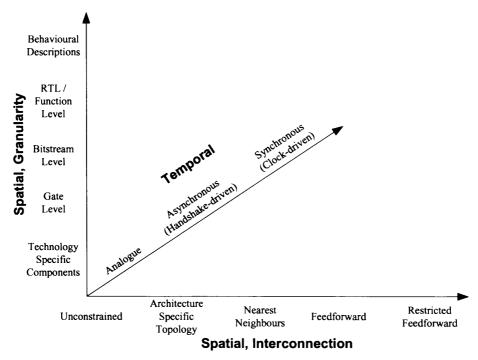

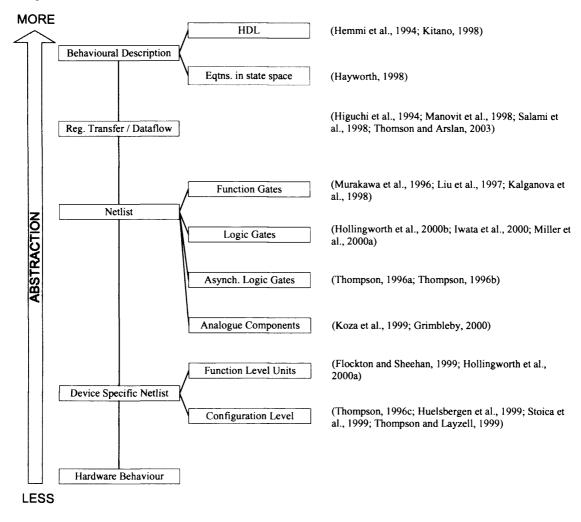

#### 1.2.2 Abstraction in Hardware Evolution

Details of the types of circuit that can be evolved and how these are represented by the parameters that make up the genotype have so far been omitted from this discussion. Typically each parameter describes the behaviour of a single component of the circuit or an interconnection between two components. Circuits have been evolved using an array of component and interconnection types that represent the entire spectrum of circuit design abstractions, from high level behavioural descriptions (Hemmi et al., 1996; Araujo et al., 2003) through networks of logic gates (Kajitani et al., 1998) (Miller et al., 1997) to networks of transistors (Stoica et al., 2002) or other analogue components (Zebulum et al., 1998).

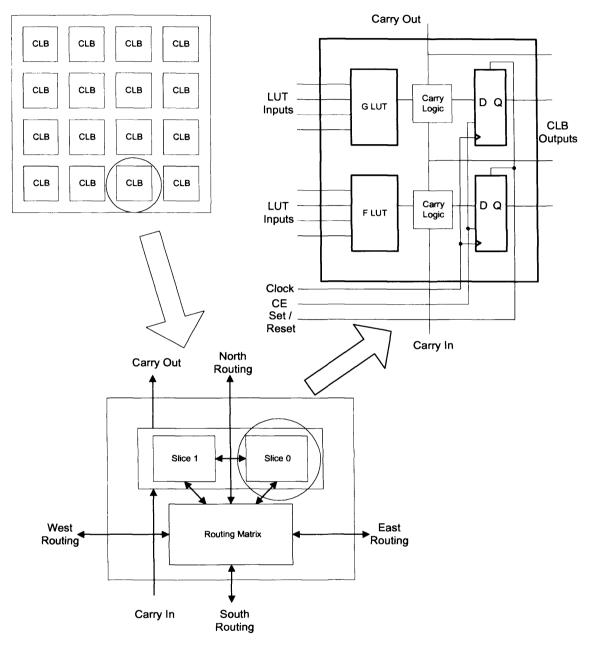

One of the most interesting abstractions was used by Thompson (Thompson, 1996a), who evolved configurations for a Field Programmable Gate Array (FPGA). FPGAs are integrated circuits that consist of arrays of identical electronic components and wires interconnecting them. The behaviour of each component or interconnection can be altered by passing configuration data to the device. By passing the FPGA a configuration bitstream that describes several components and their interconnections, a circuit design can be realised in hardware. FPGAs are available commercially at low cost. They are one of several classes of reconfigurable devices that are useful for evolutionary work as they allow circuits to be created and evaluated in real hardware (termed *intrinsic* evolution). This avoids the need for a simulation of the circuit behaviour (termed *extrinsic* evolution), which can be computationally expensive.

Each bit in Thompson's chromosomes directly represented a bit in the configuration bitstream of the FPGA, with almost every bit for a small section of the chip included in the chromosome. This meant that evolution was free to explore almost all possible configurations hence almost all possible behaviours that the evolved area of the chip could manifest. It might be said that he evolved the section of the chip at the lowest possible level of configurability, or using the lowest possible design abstraction, for that FPGA. The majority of the solution space was made up of circuits that would never be considered by conventional digital circuit designers as they break some of the basic rules of circuit design. The best circuit found by evolution was one of these circuits, with much more efficient design than conventional techniques would yield. It could not have been discovered if evolution had explored the design space using a conventional design

abstraction, thus demonstrating that permitting evolution to work at low levels of abstraction increases the opportunity to discover innovative circuits.

The area of the chip that Thompson evolved was very small by conventional design standards, certainly too small to perform computations of the order required by most real-world problems. Even so the search space that resulted from allowing evolution to directly manipulate the FPGA at its lowest level of configurability was vast by evolutionary terms. It has already been discussed that generally evolution is not able to search very large spaces effectively because it cannot sample enough of the space to direct it to good solutions. This scalability problem has been recognised by many hardware evolution researchers as an issue that is critical to the field (Torresen, 2000b; Vassilev and Miller, 2000c; Haddow et al., 2001; Gordon and Bentley, 2002; Koza et al., 2003; Shanthi et al., 2004). The only reports of evolving circuit designs significantly larger than Thompson's intrinsic demonstration have been achieved by strictly limiting evolution's search to more conventional areas of solution space through abstraction, for example (Hemmi et al., 1996; Thomson and Arslan, 2003). However with this kind of approach, any solutions to large circuit design problems that rely on behaviours beyond the scope of conventional circuit design are also beyond the scope of evolutionary design. If evolution is to be allowed the opportunity to innovate at low design abstractions, another approach is needed.

#### 1.3 Development

Nature does not appear to suffer from the scalability problem. It has managed to evolve large organisms without losing the ability to design complex, intricate features such as neural networks or immune systems. Many students of biology, for instance (Wagner and Altenberg, 1996; Kirschner and Gerhart, 1998; Wolpert et al., 2002; Schlosser, 2004), believe that the key to nature's ability to learn and manipulate complex adaptations is the process of development.

The term *development* describes the process that transforms a single-celled embryo into a complex adult organism (Wolpert et al., 2002). In this thesis it is used as a metaphor for the transformation of genotype to phenotype. The entire process is by no means completely understood. It encapsulates a huge array of interactions between genes, their products and the environment, from microscopic to macroscopic, some of seemingly minor importance, some ubiquitous to all stages of development. One mechanism that has a hand in all stages of development is differential gene activation: the genes that are active in a given cell at a given time can differ from those active in another.

•

#### 1.3.1 Differential Gene Activation

Differential gene activation is on the whole self-regulated. The products of gene activation are proteins, and many of these play a role in gene activation itself. Such proteins are called *transcription factors* and control gene activation by interacting directly with the gene itself. The rate at which a particular protein is generated is dependent on the rate at which the gene that describes it is transcribed, hence the rate at which the gene's transcription factors are generated. As a transcription factor is simply a gene product, the rate at which it is generated relies on the rate at which other transcription factors are generated, and so on. The specificity of transcription factors varies, some affecting a single gene while others may be involved in the regulation of a number of genes.

#### 1.3.2 Gene Regulatory Networks

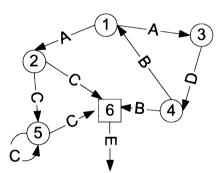

The relationship between regulatory genes and their transcription factors can be modelled as a directed graph, where the nodes represent genes and the edges represent their products. If a gene product is a transcription factor, it is represented by edges connecting its parent gene to the genes it regulates. This type of network is known as a Gene Regulatory Network (GRN) (Kauffman, 1969), an example of which is shown in Figure 1.3.1.

Figure 1.3.1: An example GRN with 5 regulatory genes (1-5) and their products (A-D). This network activates Gene 6, which generates a structural protein labelled E.

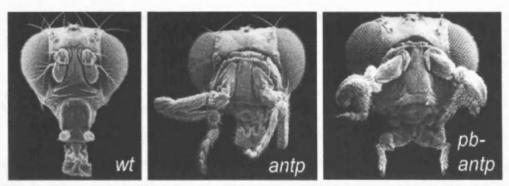

The GRN model has been used by developmental biologists to explain the observation of homeotic genes. A homeotic gene is one which when mutated transforms one complex phenotypic feature into another (Slack, 1991). Two examples are shown in Figure 1.3.2. The left-hand picture shows a normal, or "wild type" Drosophila head. The centre picture shows a head of a Drosophila with a single mutation that has resulted in the transformation of antennae into legs. The right-hand picture shows the head of a Drosophila with two mutations where in addition to the homeotic transformation of the antennae also exhibits legs in place of the proboscis. It has been shown that many homeotic genes are master control genes (Lewis, 1992) that when expressed activate a GRN, causing a cascade of activity in the network of genes that eventually leads to the formation of a complex structure.

Figure 1.3.2: Three Drosophila heads, (a) wild type, (b) with the *antp* mutation and (c) with both *pb* and *antp* mutations. Micrographs courtesy of F. Rudolph Turner & Flybase (Drysdale et al., 2005).

The existence of homeotic genes in nature demonstrate that GRNs provide evolution a mechanism for encoding *modules* that perform complex functions through the activation of a single gene. Furthermore evolution is free to augment a GRN that encodes such a module with feedback loops, allowing the module to be *re-used* in an iterative or recursive manner.

Once evolution has discovered a useful module encoded as a GRN it can vary either the GRN or the expression of the master control gene to move directly between areas of search space that were previously separated by large distances, avoiding the potentially less fruitful space in between. Hence a GRN can be thought of as a mechanism for effectively transforming or abstracting the design space so that evolution is presented with a more tractable landscape, a smaller landscape, or perhaps both. Crucially evolution will have discovered any modules it uses in this way whilst working at a lower level of abstraction. There it will have been able to identify and exploit potentially useful innovations and incorporate them into the module.

There is nothing preventing evolution from incorporating the control genes for one GRN within another GRN, thus development is capable of building hierarchies of modules, unlike methods such as Function Level Evolution. Furthermore such modules are discovered in a manner quite different from the top-down design process common to traditional engineering. Instead they are created by combining components incrementally using evolution rather than domain knowledge to guide the search, unlike some methods that have been suggested for providing modularity in hardware evolution. In addition evolution is not constrained to use a design abstraction encapsulated by a module. Rather it is merely *biased* towards searching the space using the new design abstraction. It is still free to modify, or even disregard the module should it prove fruitful to do so.

The notion that the regulatory processes described by GRNs can be used to encapsulate useful design features within *modules* and provide a mechanism for their *reuse*, thus presenting a *design abstraction* is central to the argument made in this thesis as to how development can

enhance the scalability of hardware evolution, and central to the models of development used in this thesis to demonstrate scalability.

#### 1.3.3 Intercellular Communication

The GRN model can explain how development can control and iterate the generation of a complex feature, but it cannot explain how development can ensure the positioning of a complex feature at a particular site in a large organism or iterate the generation of a feature over many specific sites within an organism. To do so development must communicate information that activates a GRN across space. The most common developmental communication mechanisms in large, multicellular organisms rely on the process of induction. Here a cell encodes regulatory information as a chemical signal, which is transmitted to nearby cells. A variety of inductive signal types have been identified (Slack, 1991), which pass information over various localities and at various rates. A thorough exploration of detailed biochemical models are of interest to developmental and molecular biologists, and artificial life researchers amongst others. The developmental models used in this thesis model intercellular communication and in particular the process of induction, in addition to the regulatory processes embodied by GRNs. However to maintain clarity the experiments and analysis in this thesis have been limited to focus on the engineering problem at hand. Hence the communication models abstract any biochemical details of both cells and induction. Only features that either aid the implementation of developmental models in hardware or aid the generation of circuit designs are modelled. The same is true of the models of regulation.

#### 1.3.4 Problems Suited to Development

Not all circuit design problems might benefit from a developmental approach. An ideal problem would be one where an optimal circuit description is easily partitioned into a number of repeated modules, each contributing independently to the circuit's fitness. It should be possible to represent each unique module in a compact form similar to a GRN, and iterate the module across space using some form of intercellular communication, thus generate the final circuit design. Hence problems where solutions can take the form of large modular repetitive circuits that can be represented by a simple developmental process are the ideal target for development. Note that such circuits are not necessarily complex in the sense of information theory. In fact it is circuit designs that appear complex as they cannot be represented succinctly using conventional circuit components but can be described succinctly using some other representation that are of most interest.

#### 1.4 Motivation and Hypothesis

The motivation for this work is two-fold. First it aims to show that the introduction of a developmental genotype-phenotype map can allow evolution to design larger electronic circuits automatically, leaving open the possibility that one day the size and complexity of evolved circuits might rival those generated by conventional design techniques. The second aim of this work is to show that circuits can be evolved using development without preventing evolution from exploring innovative and evolvable design features found only at the lowest design abstractions. In achieving these aims, several features of biological development that are of benefit to the evolution of such circuits are identified. This work does not attempt to model biological development accurately, but merely to model it at a level of detail necessary to achieve the engineering goal of generating the circuits described above.

From the above background the hypothesis of this work can now be plainly stated:

# The scalability of hardware evolution can be enhanced by exploiting a model of biological development.

Where: scalability is defined as the ability to solve a series of problems of increasing size where the larger problems can be decomposed into modules of the smaller problems

And: performance is measured as the expectation that evolution will provide fully compliant solutions to the problems.

In section 1.3 it was explained that one mechanism though which development could enhance scalability relies on three properties: abstraction, modularity and reuse. This thesis aims to support the hypothesis by highlighting these properties through the following three objectives:

- 1. *Abstraction:* show that a developmental model for hardware evolution can discover and encode biases towards design abstractions that might benefit hardware evolution (Chapter 4 and Chapter 6),

- 2. *Modularity:* show that evolution can encapsulate such design abstractions in useful developmental modules (Chapter 4 and Chapter 6), and

- 3. *Reuse:* show that evolution can re-use such modules to solve larger hardware evolution problems (Chapter 5 and Chapter 6).

This thesis aims to demonstrate the hypothesis itself through a series of experiments presented in Chapter 6 that compare the evolution of useful electronic circuits using a developmental mapping and a traditional 1:1 gene to component mapping.

In the course of demonstrating the hypothesis, the thesis also aims to achieve the following minor objectives:

- 4. Demonstrate hardware evolution of the Virtex architecture (Xilinx Inc., 2001) at a level of abstraction that imposes the fewest design constraints that has been reported in the literature.

- 5. Show that such an approach allows more efficient use of the resources provided by the Virtex architecture than previously reported work, and may provide a more evolvable search space than those constrained to combinational circuits.

- 6. Show that the choice of context is important to the ability of induction-based models of development to evolve hardware.

- 7. Show that a dynamic representation can increase the evolvability of rule-based developmental systems.

- 8. Show that it is possible to characterise the learning biases introduced by a developmental process to the extent that classes of problem that might and might not be suitable targets for a developmental approach can be identified.

- 9. Show that the model of development used for the scalability experiments in this thesis performs well in comparison with similar models introduced by other researchers.

- 10. Show that providing a bias towards traditional problem decomposition, as proposed by other approaches to scalability can actually harm scalability.

During the course of the scalability experiments large evolved circuits will be presented, including adders that are larger than any that have previously been presented using evolution alone (i.e. without relying on additional traditional problem decomposition techniques) and parity generators of similar size to the largest found in the literature.

Even so these circuits are not of a size that can challenge traditional design methodologies. Furthermore for hardware evolution to supplant conventional designers additional questions such as how to ensure that the behaviour of a large evolved circuit generalises to unseen conditions and can be easily verified must also be answered. Unfortunately there are no immediate answers to such questions. However there is still value in enhancing the scalability of hardware evolution as it might allow the reach of the technique to be extended, to a point where it can tackle a set of moderately sized yet difficult problems where traditional design fares poorly, and evolution's ability to innovate is most needed. At that point hardware evolution might find a niche alongside traditional design.

#### 1.5 Outline

The rest of the thesis is structured as follows. Chapter 2 reviews the fields of hardware evolution and developmental evolution in order to set the rest of the work presented here in context. Chapter 3 introduces an intrinsic circuit evolution platform that was developed to explore the hypothesis stated in Section 1.4, and presents experiments used to validate the platform. The final validation experiment is also used to demonstrate objectives 4 and 5. Chapter 4 presents an exploratory developmental hardware evolution system, along with analysis of circuits evolved with it that demonstrates objectives 1 and 2. Chapter 5 introduces a revised developmental hardware evolution system that incorporates a number of enhancements, and demonstrates objective 6. It also explores the concept of evolvability and presents experiments that demonstrate objective 7. Chapter 6 focuses on the evolution of large phenotypes. It begins by exploring the inductive biases inherent in the revised model of development, leading to a set of guidelines that demonstrate objective 8. This is followed by a comparison with similar models used by other researchers across a number of benchmark problems, the results of which demonstrate objective 9. The crux of the thesis follows: the primary hypothesis of the thesis is clearly demonstrated through a series of experiments that show scalability is enhanced when a developmental model is used in place of a traditional 1:1 genotype-phenotype map. Analysis of some of the large evolved circuits confirms objective 3. Chapter 6 also demonstrates objective 10 by repeating the adder scalability experiments but with an additional bias towards traditional problem decomposition. Chapter 7 reviews the objectives laid out here, introduces ideas for further work and presents conclusions.

### 2 Literature Review

This chapter reviews the two fields of research directly related to the work of this thesis. In Section 2.1 the field of hardware evolution is reviewed. Particular emphasis is given to the scalability issue, the motivation for this thesis. Section 2.2 reviews the use of genotype-phenotype mappings that model development in Evolutionary Computation, focusing on their benefits to scalability and their use in hardware evolution.

#### 2.1 Hardware Evolution

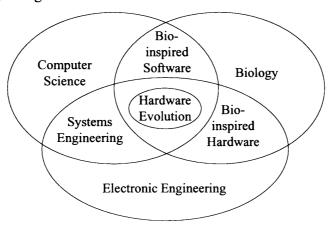

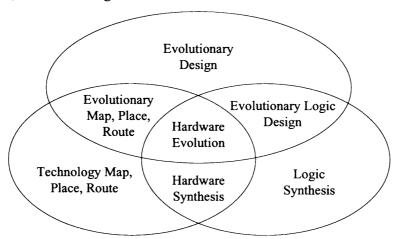

Hardware evolution is the application of evolutionary algorithms to the automatic design and synthesis of electronic circuits. The field draws inspiration from several other fields, as shown in Figure 2.1.1. For many years computer scientists have modelled their learning algorithms on self-organising processes observed in nature. Perhaps the most well known example is the artificial neural network (ANN) (Widrow and Hoff, 1960; Rumelhart et al., 1988). Others include the collective decision-making of ant colonies (Dorigo et al., 1991), the adaptive ability of immune systems (Dasgupta, 1996), the growth of self-similar structures in plants (Lindenmayer, 1968), and Darwinian evolution (Goldberg, 1989). Collectively, work on such algorithms is known as bio-inspired software, which is shown at the intersection of Computer Science and Biology in Figure 2.1.1.

Figure 2.1.1: The elements of hardware evolution.

Nature has also inspired algorithms used in Electronic Engineering. For instance simulated annealing algorithms are used in many circuit partitioning, placement and routing algorithms (Sechen, 1988; Gerez, 1999). (These are inspired by the physical phenomenon of annealing as metals cool.) Interest in using ideas from nature has grown in recent years to the extent that the field of bio-inspired hardware is now firmly established in its own right, as shown at the intersection of Electronic Engineering and Biology in Figure 2.1.1. This field uses many of the

ideas adopted from nature by software developers, and some new ones, not only to improve features such as fault tolerance and reconfigurability but also for automatic circuit design. The field of hardware evolution is shown at the intersection of Computer Science, Biology and Electronic Engineering in Figure 2.1.1. The first half of this chapter reviews work in this area.

Hardware evolution encompasses the application of evolutionary algorithms to both analogue and digital circuit design and synthesis. However as digital methodologies are generally more structured than analogue methodologies it is possible to clarify the relationships between traditional digital hardware synthesis, Evolutionary Computation and hardware evolution in a little more detail, as shown in Figure 2.1.2.

Figure 2.1.2: The interrelationships between hardware design and synthesis, and Evolutionary Computation.

Traditional digital hardware synthesis is a combination of two processes. First a human-designed circuit specification is mapped to a logical representation, normally a list of components and their interconnections or *netlist*, through the process of logic synthesis. This is represented as the lower right-hand set in Figure 2.1.2. The netlist then undergoes further combinatorially complex optimisation processes in order to place and route the circuit to the target technology. This area is represented as the lower left-hand set in Figure 2.1.2. Many modern EDA<sup>1</sup> tools apply intelligent techniques to these optimisation algorithms, and there is much research into use of evolution for these purposes (Göckel et al., 1997; Mazumder and Rudnick, 1999). Hence the set representing evolutionary design intersects with that of technology mapping, placement and routing in Figure 2.1.2 to yield evolutionary mapping, placement and routing. However circuit design, along with some optimisation decisions during the synthesis process is still in the domain of the human designer. It is only recently that significant interest has developed in implementing evolutionary techniques higher up the digital design flow for circuit design, a move that can allow evolution to generate creative designs that

\_

<sup>&</sup>lt;sup>1</sup> Electronic Design Automation

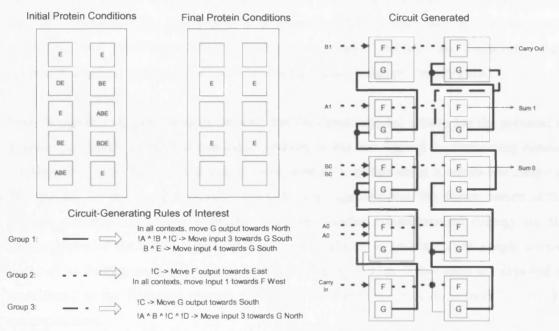

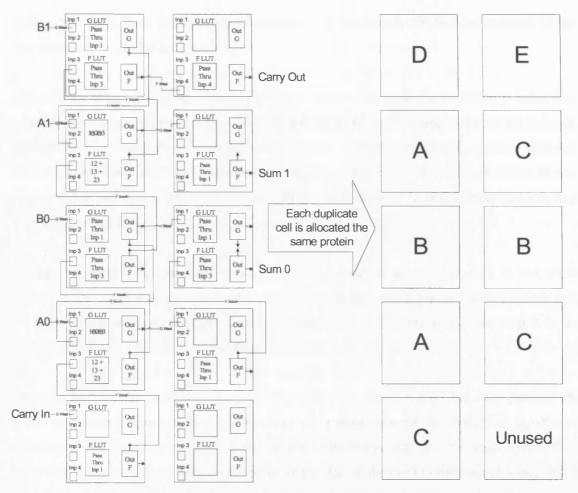

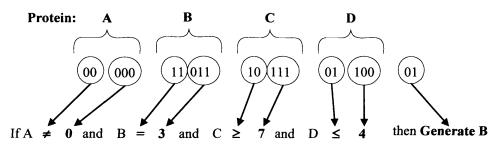

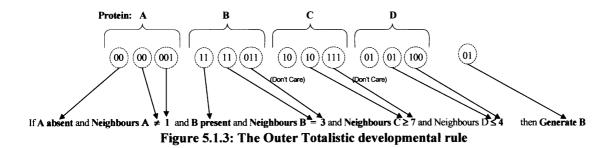

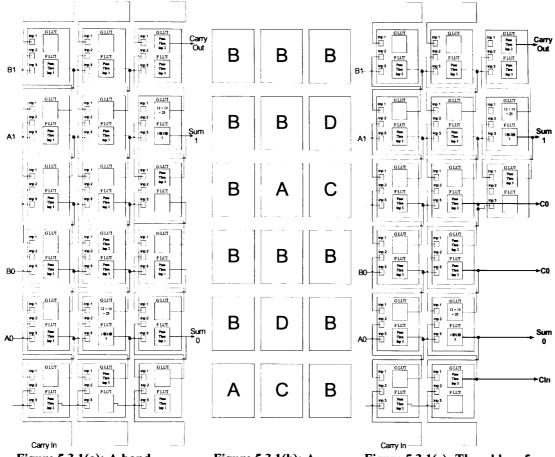

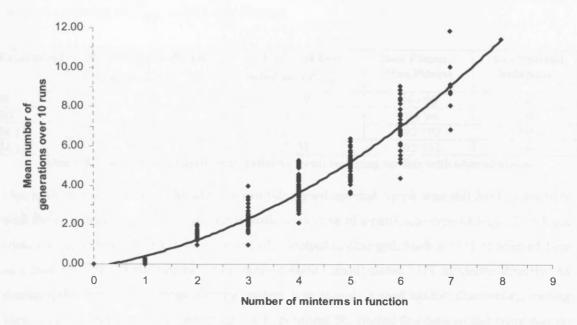

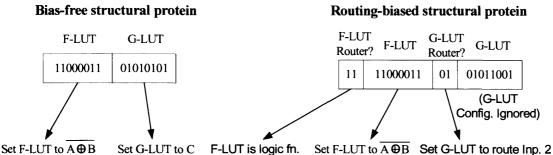

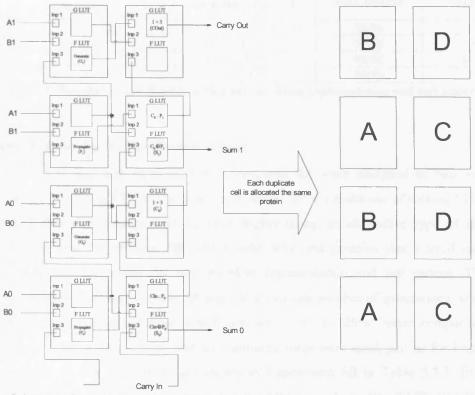

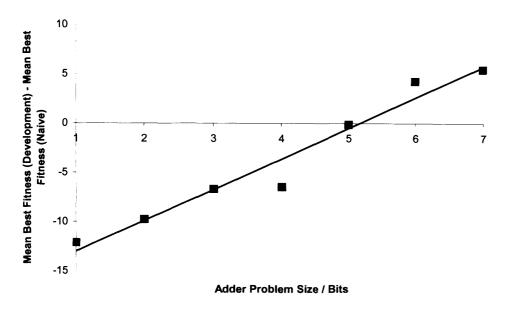

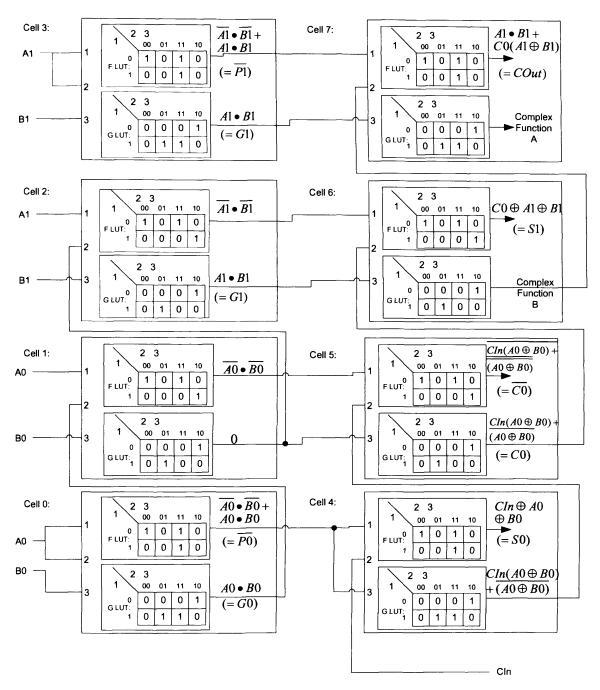

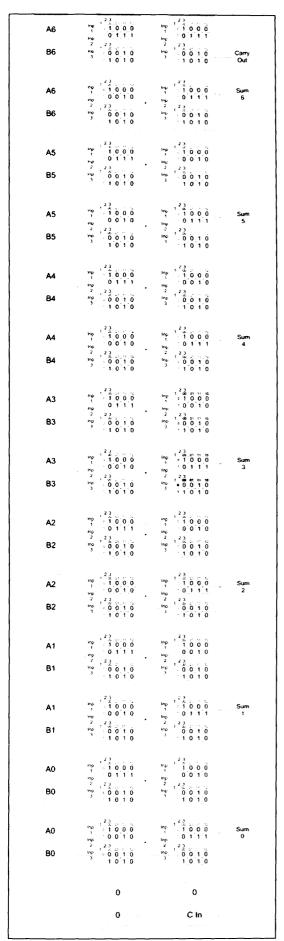

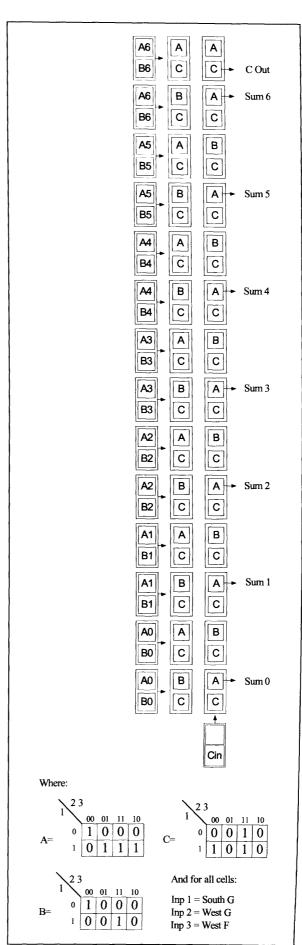

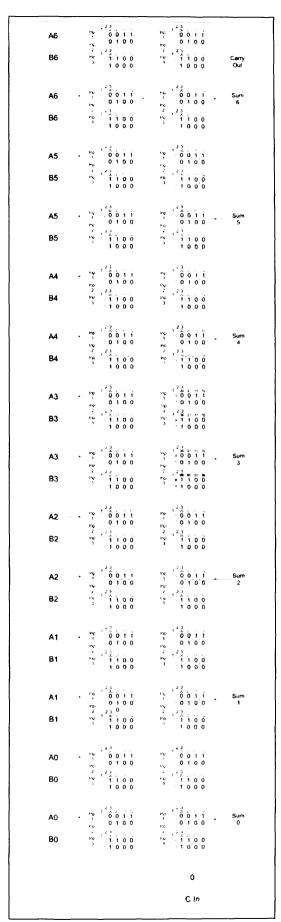

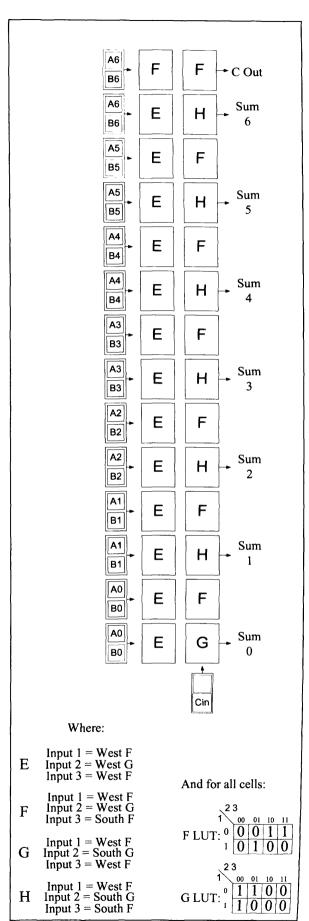

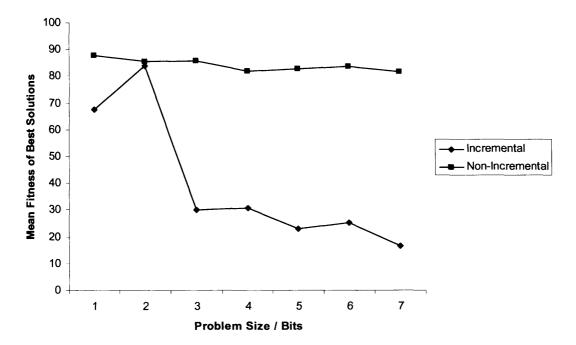

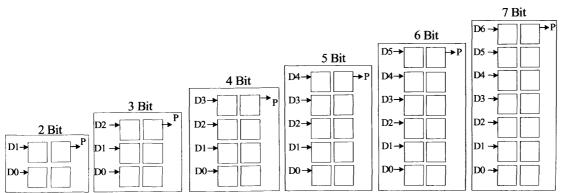

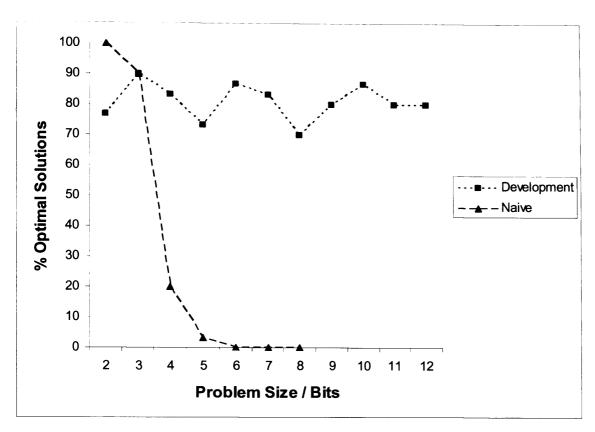

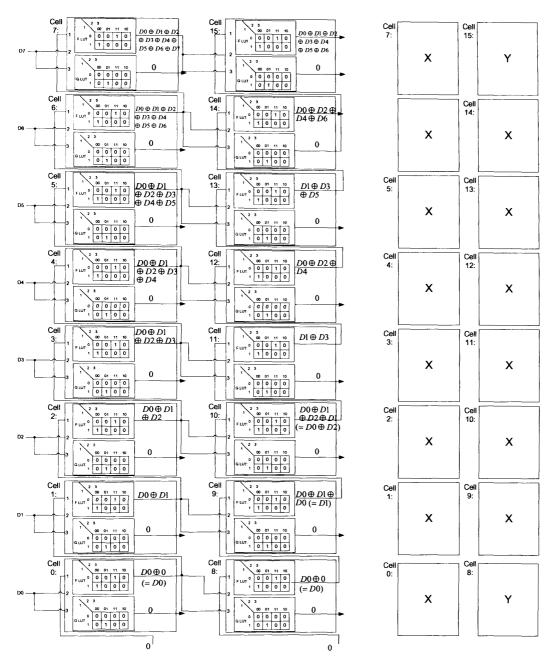

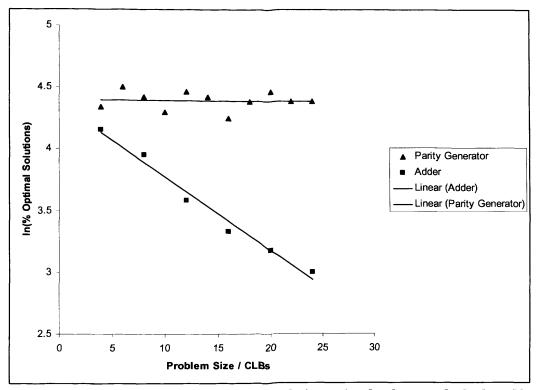

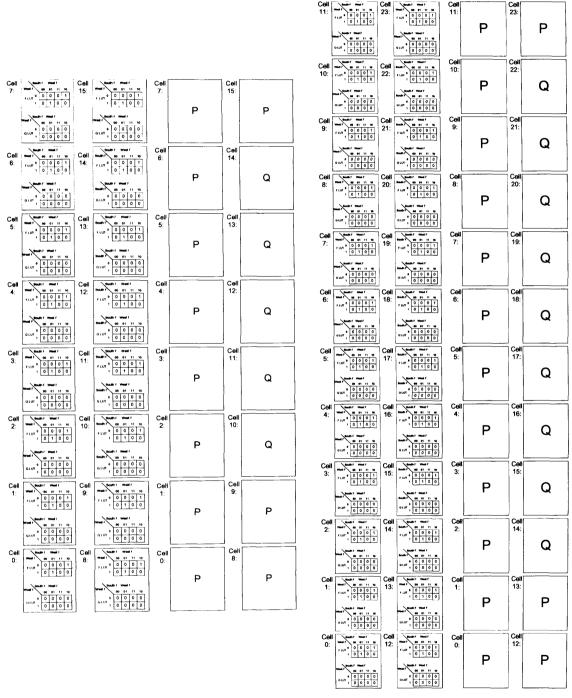

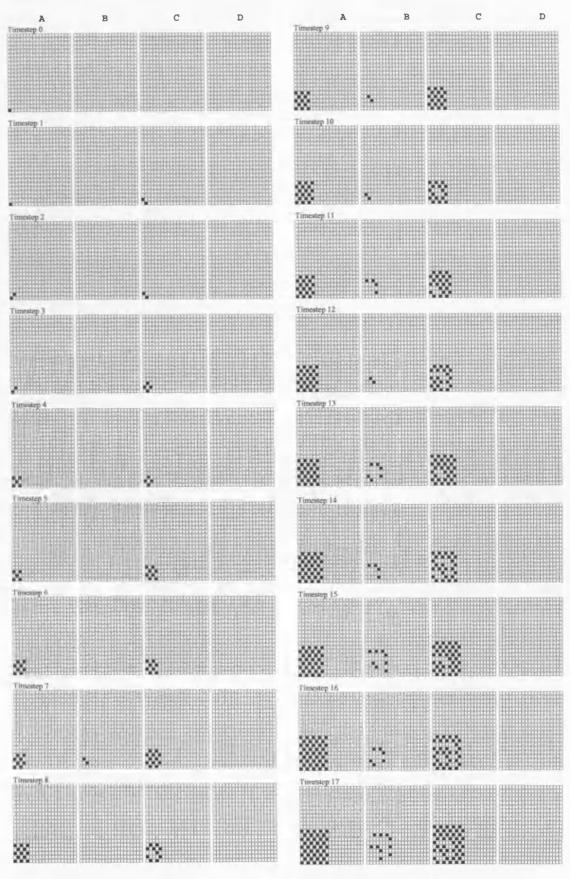

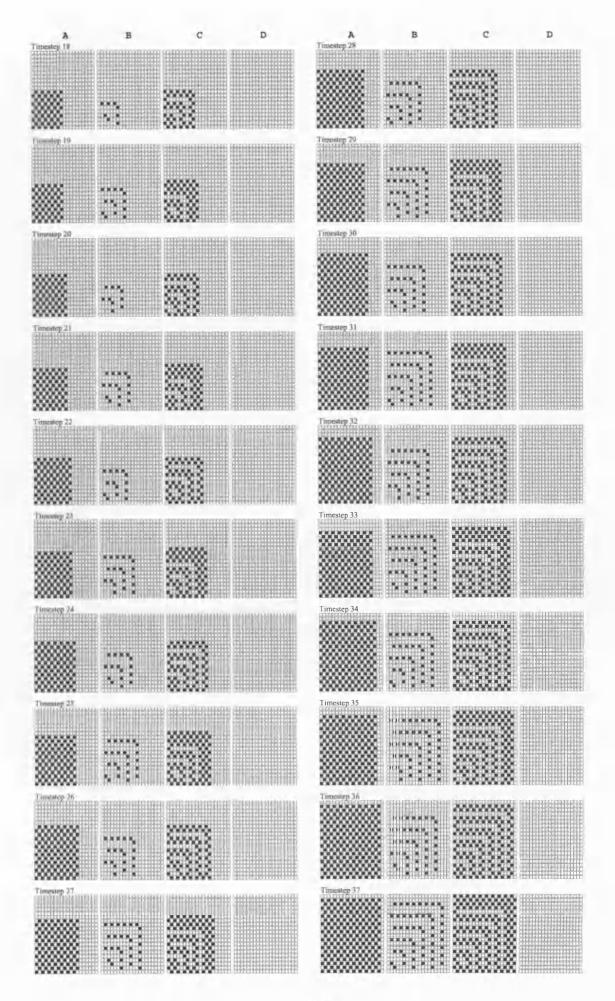

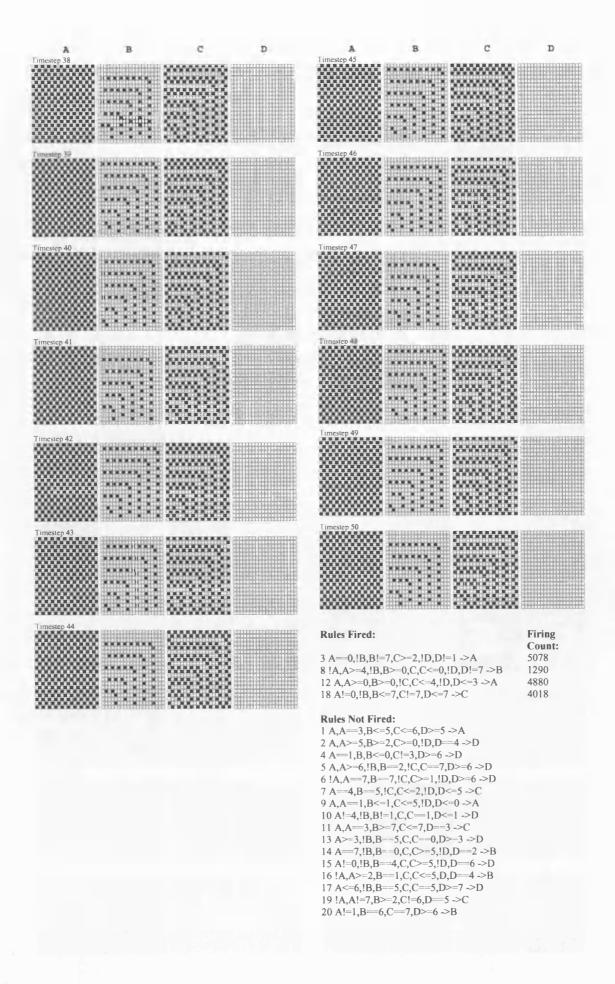

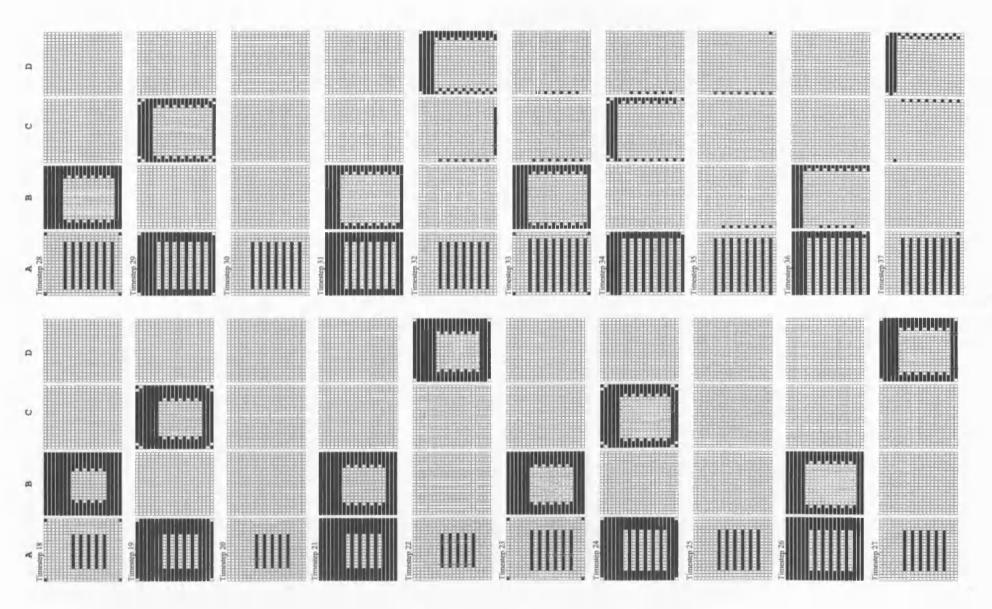

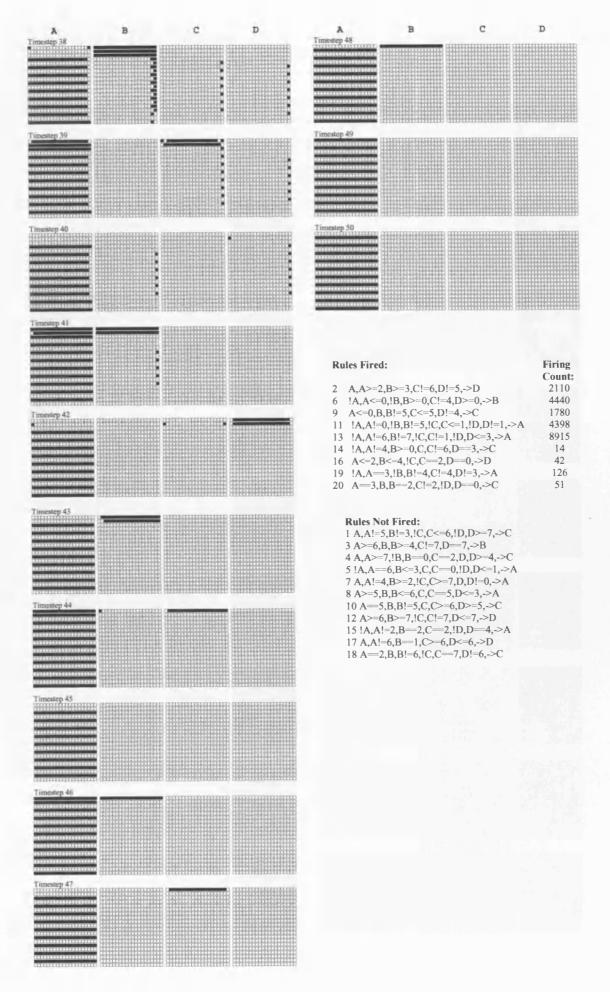

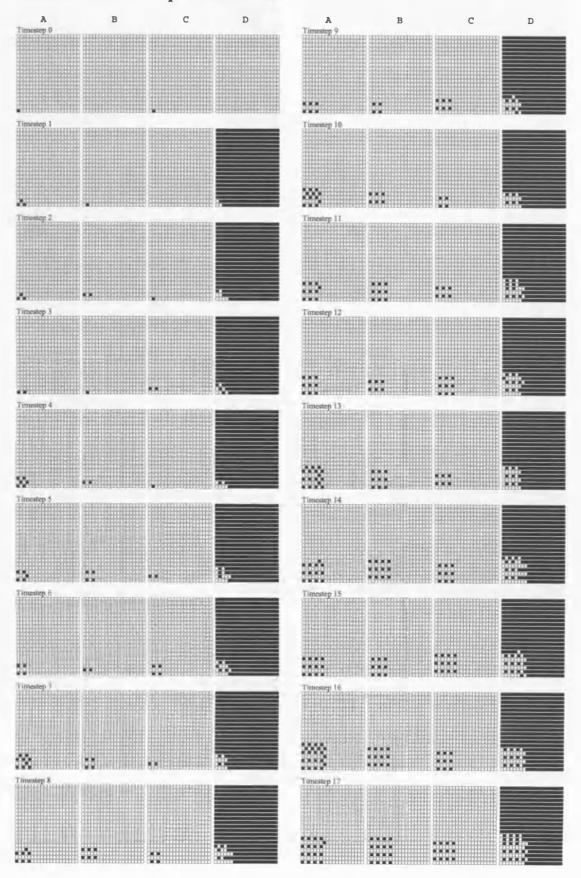

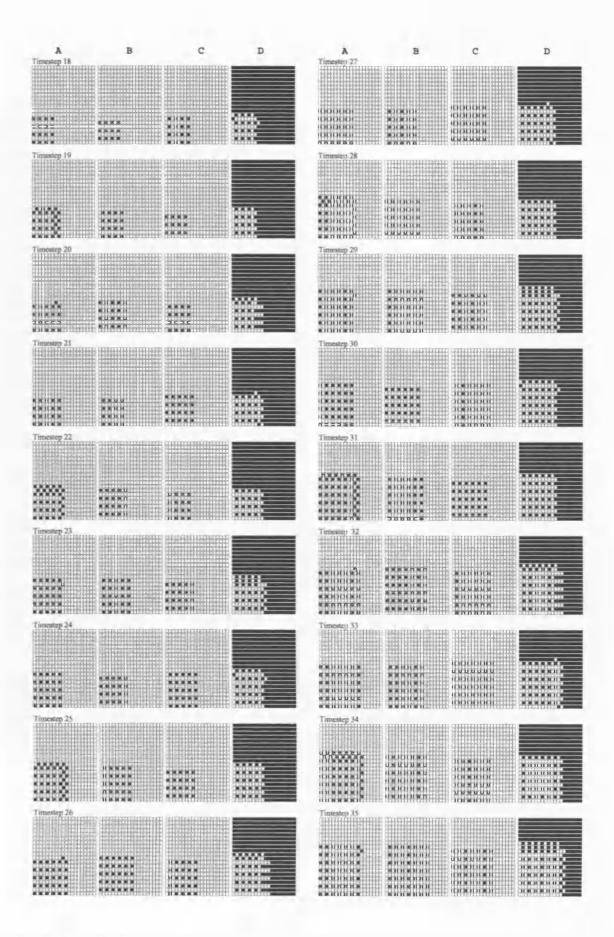

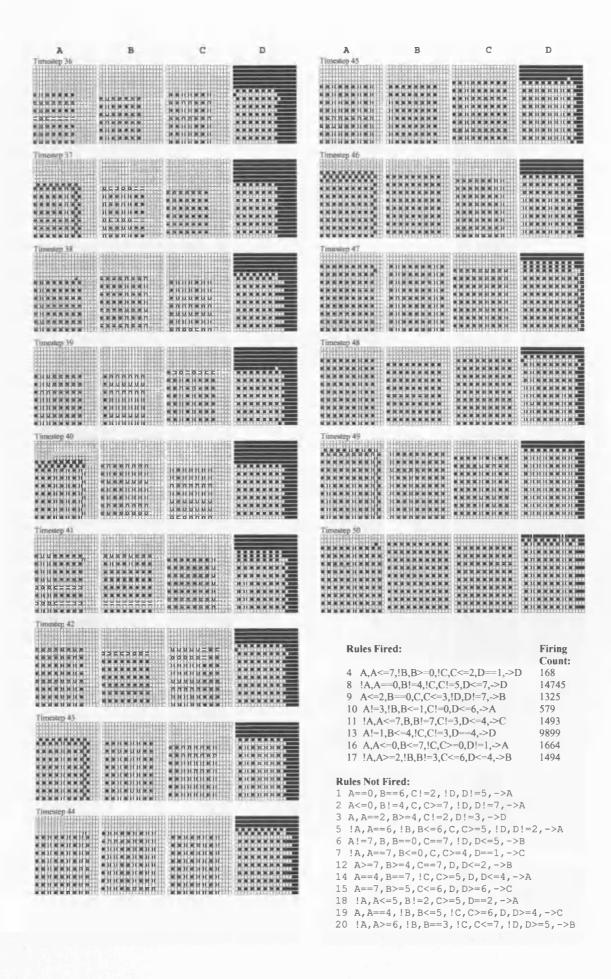

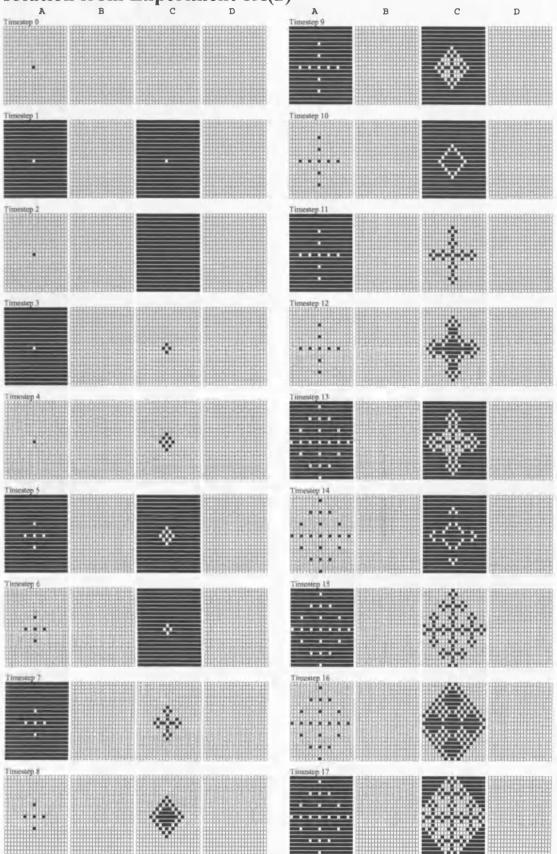

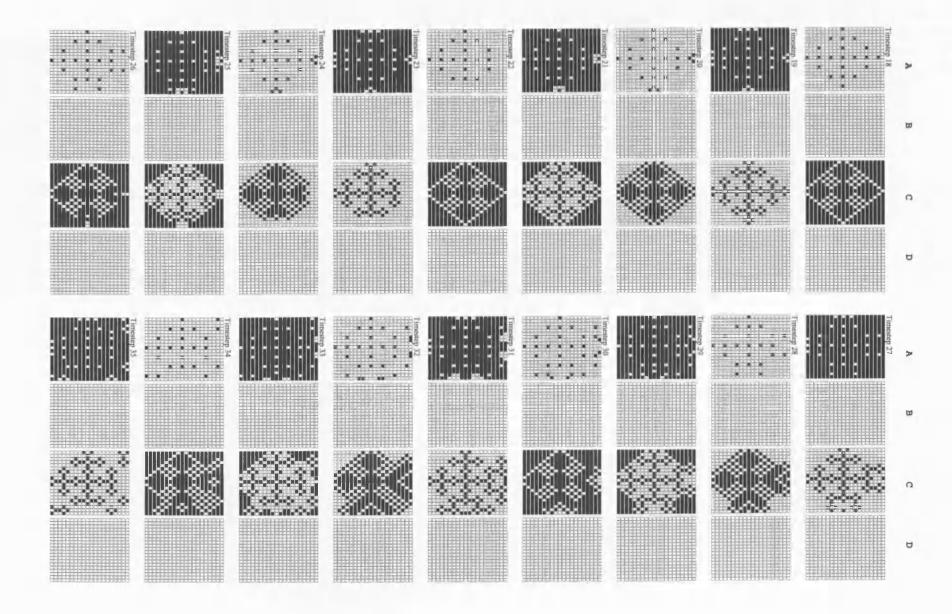

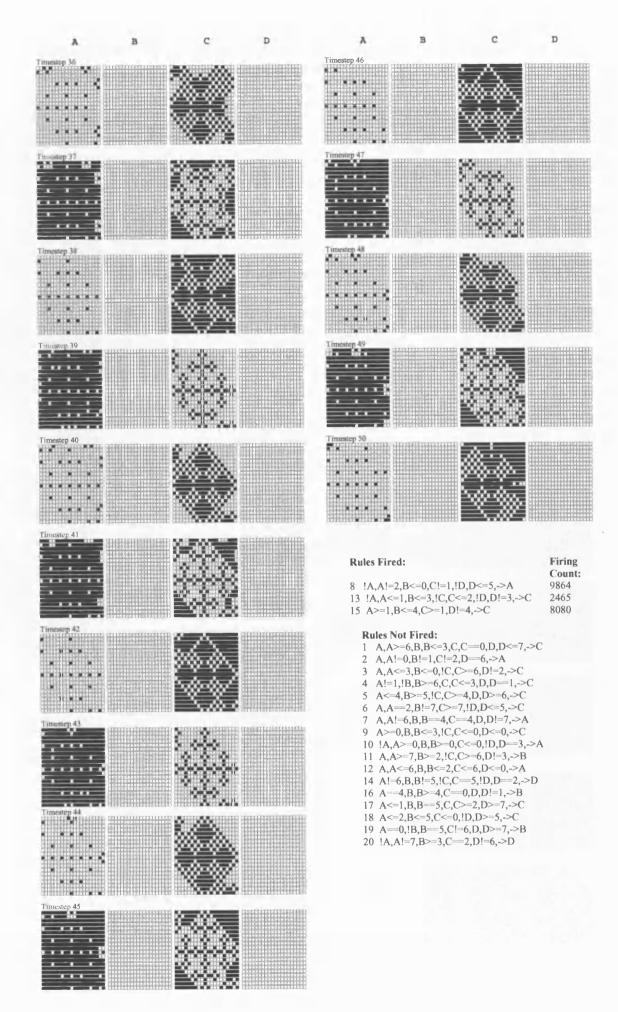

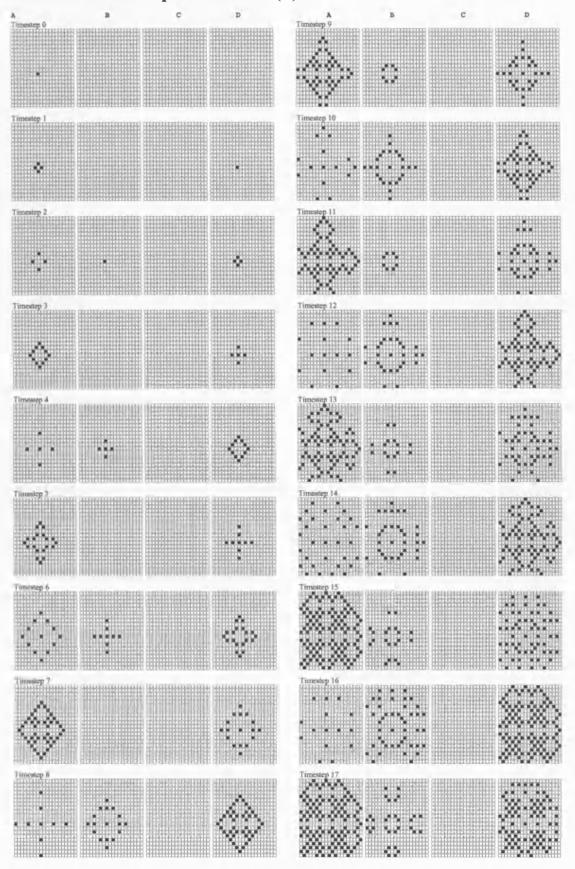

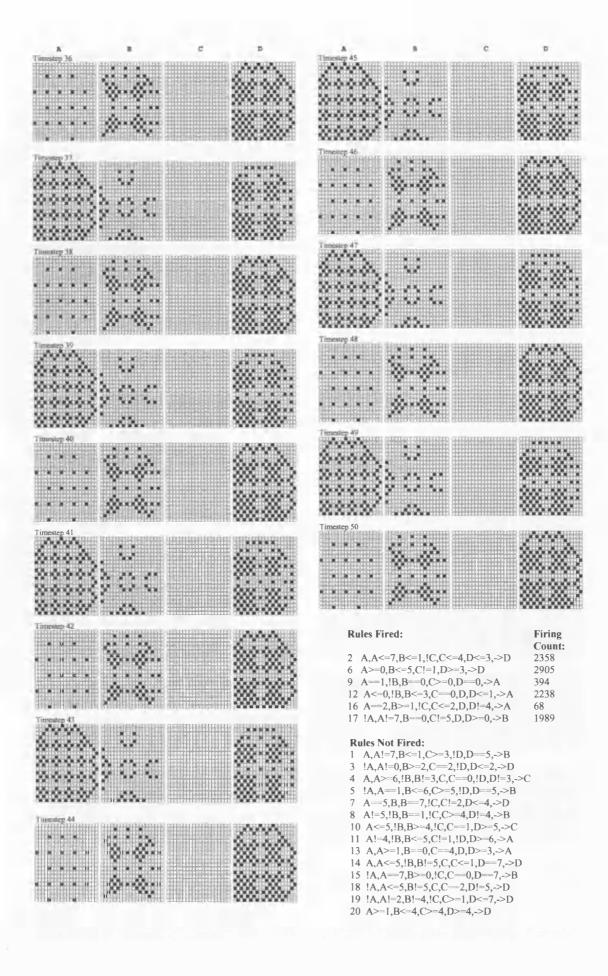

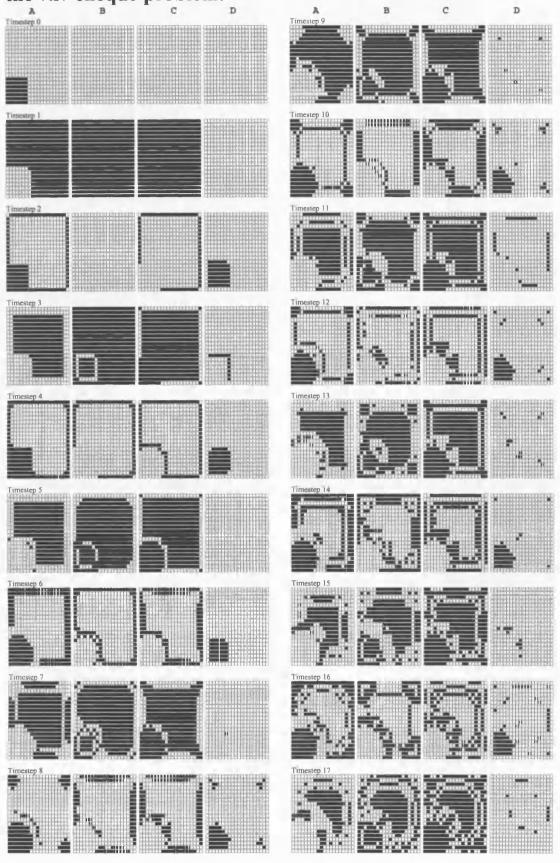

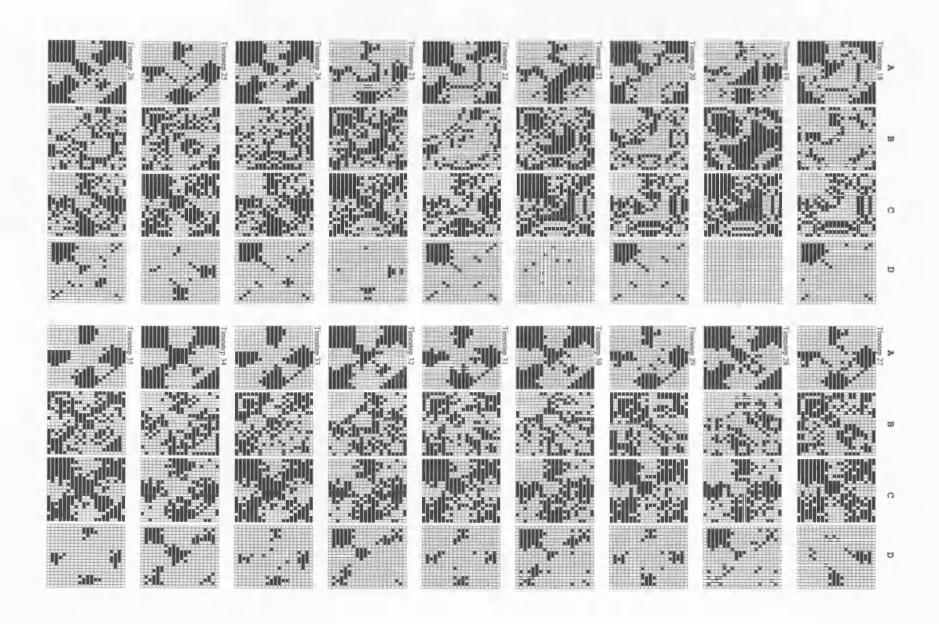

can rival or improve on human ones. Most commonly evolution has been used to design logic, as represented by the intersection of the areas of evolutionary design and logic synthesis in Figure 2.1.2. Some of the work in this intersection falls into the field of hardware evolution. However much work at the logical level is carried out in the spirit of evolving programs or other forms of logic, so is beyond the scope of this thesis.