21

**Bulletin of Electrical Engineering and Informatics** Vol. 7, No. 1, March 2018, pp. 21~27 ISSN: 2302-9285, DOI: 10.11591/eei.v7i1.750

# Qualitative Analysis of Darlington Feedback Amplifier at 45nm Technology

### Rashmi Singh\*, Rajesh Mehra

Department of Electronics and communication, National Institute of Technical Teachers Training and Research, Chandigarh, City-Chandigarh, India

| Article Info | ABSTRACT |

|--------------|----------|

#### Article history:

Received Nov 14, 2017 Revised Jan 15, 2018 Accepted Jan 29, 2018

#### Keywords:

45nm technology Bandwidth enhancement Broadband Darlington Amplifier Circuit design Circuit simulation Slew rate

## The transistors of

The transistors are the key element of present communication system having high data rate. Some applications need high gain by using very low frequency, and then transistors are used. Amplifier is the key element in many applications of present high data rate communication system such as low noise amplifier (LNA), broadband amplifier, distributed and power amplifier. The Darlington pair amplifier is analyzed for high frequency performance and related effect of bandwidth. Broadband feedback Darlington pair amplifier is designed with enhanced gain, bandwidth and slew rate. This paper presents the comparison of single stage and three stage feedback Darlington feedback amplifier with reference to gain, bandwidth and slew rate. This paper is simulated on cadence analog design environment at GPDK 45nm technology. This paper shows that increase in gain, bandwidth and slew rate of three stage Darlington feedback amplifier can show better stability over the single stage Darlington feedback amplifier.

> Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

Rashmi Singh, Department of Electronics and communication. National institute of Technical Teachers Training and Research, Chandigarh City-Chandigarh, India, Email: Contecter.rashmi@gmail.com

### 1. INTRODUCTION

At the global level, wideband amplifier has become a standard building block for radio frequency, macrowave applications, high speed communications, imaging systems and wide band instrumentations [1]-[10]. Currently, a number of circuits are in place to implement the wideband amplifier such as distributed amplifier, multi-stage amplifier, cascode amplifier, feedback amplifier [11]-[15]. The key advantages are that after multi decade its bandwidth performance up to macrowave frequencies, it can be realized in a small chip without the use of distributed or reactive matching techniques, and it is simple to use with few external components [16]-[20]. Darlington pair amplifier has been described as the amplifier, where two transistors are kept inside a single packet and equipped with high gain and input impedance [1]-[8]. In this amplifier, however, collectors are common, but the emitter terminal of first transistor has been coupled to the base terminal of the second transistor. Configuration means that the second transistor amplifies the signal which is already amplified by first transistor [3], [4], [6]. Darlington Pair amplifier is used for amplification of small signal which is used in various communication circuits. If we need large current gain and more stability in any application Darlington pair amplifier is the best option [4], [6]. The voltage required to switch on a Darlington amplifier is just double compared to single transistor, because there are two base emitter junction. Bipolar transistors have low frequency current gain, to enhance this feature of bipolar transistors, Darlington pair amplifier is invented. After that, Darlington amplifier is used mainly in broadband amplifier.

In future world, some portable devices like software radio, mobile etc. will need to cover a very range of frequency from 800 MHz up to 2.6 GHz. The bandwidth requirement has been converted into

narrower frequency band. Hence, large bandwidth requirement proposes the appreciable use of multiple bands in future. Thus it is necessary to develop amplifiers with large bandwidth, more gain and enhances slew rate to fulfill the requirements of portable devices like mobile handsets. In case of Darlington amplifier, use of feedback circuit leads to the less stability of circuit.

In this paper, authors compare the single stage and three stage feedback Darlington amplifier with reference gain, bandwidth and slew rate by simulating on GPDK 45nm technology cadence analog design environment. In this study, authors highlight the better stability of Darlington amplifier using feedback circuit.

### 2. RESEARCH METHOD

## 2.1. Single Stage Darlington Amplifier

A single transistor is used as the trans-conductance stage in broadband amplifier when it is in common source configuration [1]-[7], [9], [12]. To achieve broad bandwidth performance almost equal to microwave frequencies, there is significant demand of Darlington pair amplifier in broadband amplifiers. To enhance the features of Darlington pair amplifier, many circuits are designed like cascade amplifier, mirror doubler, active balluns etc.[8] As compared to single stage emitter follower, Darlington pair amplifier shows the characteristics of high input resistance and low output resistance. Many circuits are widely used in many applications like distributed amplifier, feedback amplifier, multistage amplifier [1]-[6], [9], [12].

As compared to single transistor, the Darlington pair amplifier have wideband highly linear feature in recent application. The cutoff frequency of a Darlington pair amplifier is just double as compared to single transistor with output impedance low and input impedance high [1]-[6], [9], [12]. Present Darlington pair amplifier has disadvantages when operated at a large bandwidth and under large signal. It has been found that the bias current can increase or decrease with related to change in input power due to operation of transistor under a large signal. When transistors are under large signal conditions, it has been suggested that even number of order products can be generated within transistor. The DC bias condition related to power level is varied by DC component which is included in even order products [11]. This disadvantage is removed in Darlington pair amplifier, which results in unacceptable big changes in the bias current. Figure 1 shows the basic circuit of single stage Darlington pair amplifier.

Figure 1. Basic circuit of single stage Darlington amplifier

$\beta D = \beta Q1. \beta Q2$

where  $:\beta D=$ current gain of whole unit

- $\beta$ Q1=current gain of first transistor

- βQ2=current gain of second transistor

#### 2.2. Multistage Darlington Amplifier

It has been observed that a single transistor is not sufficient for many applications. So that, a multistage amplifier is designed in which 2, 3, 4, etc. transistors are joined together. Different transistors are configured in such a way that next transistor will amplify the signal which is already amplified by the first transistor. In next, third transistor will amplify the signal which is already amplified by the second transistor [1]-[6], [12].

In multistage amplifier overall gain may be defined as the product in the form of gain generated from the individual amplifier.

$Gain (A) = A1 * A2 \dots An$ (2)

$$Gain in dB (A)=A1 + A2 \dots An$$

(3)

(1)

(5)

A is the overall gain of the multistage Darlington amplifier. Figure 2 shows multistage Darlington amplifier

Figure 2. Multistage Darlington amplifier

#### 2.3. Slew Rate

The slew rate may be defined as the rate of change of output. It may also be defined as the changes in the output voltage over unit time. But there is a disadvantage with slew rate with respect to its ability to increase the amplifier non-linearity effects [13], [17], [18], At ideal condition, the output of the amplifier cannot be able to change instantly to the input voltage. Then the output of the amplifier is said to be slew rate limited and known as slewing [14].

It is expressed as volts/seconds and the formula is presented as below:

$$SR > 2\pi fV pk \tag{4}$$

where :f=operating frequency

Vpk=peak voltage

Additionally, small variation of voltage according to time is expressed as slew rate.

SR=max ([dvout(t)/dt])

Slew rate has been used to calculate some parameters of amplifiers like amplitude and maximum input frequency, which helps to get enhanced output of amplifiers and possibly not the distorted one [14].

The pair amplifier has disadvantage that it produces worst frequency response when amplifier is operated at higher frequency, although pair amplifier is used in applications of high speed just because of compact chip size and broadband performance of pair amplifier [15].

The Because of the slew rate of amplifier in the single stage and directly related to bias current source, there is a report that power dissipation of the circuit can be increased [14]. The main objective of the present study focused on to increase the slew rate having low input power. At the same time, other parameters of the amplifier will be remaining constant. The main factor which is responsible for slew rate in amplifier is its internal architecture. Amplifiers are unable to lead nonlinear operation because of limited bandwidth and linear phenomenon [15]. An amplifier is connected in unity gain configuration. In case of limitation is found on its dynamic performance as the finite amplifier bandwidth, then output would be expected from the follower.

Below is the equation of unity gain Amplifier and its transfer function.

$$Vo/Vt = 1/1 + s/Wt$$

(4)

Here, it shows the low pass STC response referenced over a time constant 1/Wt.

Hence, in the next step, the step response is presented as.

$$Vo(t) = V(1 - e - wt)$$

(5)

Positive slew rate and negative slew rate have different value due to different arrangement of circuits of amplifier. Different arrangement of the pair amplifier has different slewing conditions [16]. For pull up and pull down amplifier should have outputs which are compliments with each other. I.e. the configuration does not have same at two sides.

Modern instrumentation, high data rate communication system and wireless sensor network etc., are the current applications of pair amplifier. For wireless sensor network, we need that as soon as the output of amplifier changes from one level to other. In the above applications, the speed of amplifier should be high i.e. the rate of change from one level to other should be high [1]-[6], [16]-[19]. So, amplifier should have high slew rate. This statement inspires the designers to develop unique architecture which enhance amplifier slew rate. By increasing the slew rate of Darlington Amplifier, speed of Darlington amplifier also increases. Speed is first requirement of today's high data rate communication system.

#### 2.4. Circuit Diagram

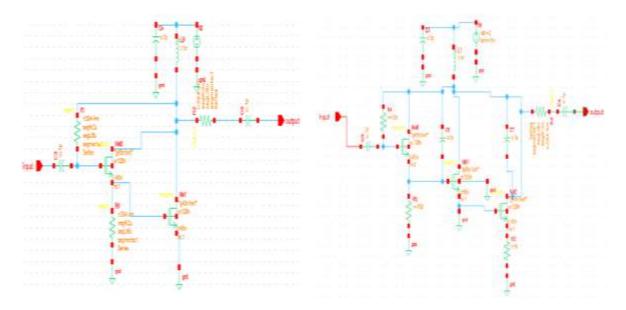

As presented in Figure 3, the schematic diagram shows that two NPN transistors are arranged in such a way that emitter terminal of first transistor is coupled with base terminal of second transistor and collectors are common. Resistors and capacitors used in schematic are shown to have distinct parameters. One capacitor is used as load capacitor which is used to calculate the slew rate of the circuit. It is a single stage Darlington pair feedback amplifier.

To improve the bandwidth, a feedback resistance is used Rf (12 k $\Omega$ ) and another resistance Rbias (150  $\Omega$ ) is used to maintain the value so that Ibias=Ie2. The circuit is biased with a supply voltage of 2 volt [13]. In this paper, the value of feedback resistance is increased to Rf (19 k $\Omega$ ) and biased resistance is decreased up to Rbias (132  $\Omega$ ). Hence, parameters indicate that the slew rate of circuit can be enhanced. Figure 4 shows three stage Darlington pair feedback amplifier amplifier.

Figure 3. This diagram illustrates the flow diagram of the two stage Darlington pair feedback amplifier

Figure 4. This diagram shows the layout of the three stage Darlington pair feedback amplifier amplifier

In the present paper, used value of feedback resistance is Rf (13 k $\Omega$ ) and biasing resistance is Rbias (156  $\Omega$ ) and based on these two parameters, the bandwidth of Darlington feedback amplifier is significantly enhanced. To achieve additional increase in bandwidth, author have added some parasitic capacitances (C6 and C7).

## 3. RESULTS AND ANALYSIS

Gain, bandwidth and noise and linearity of circuit also depend upon size and bias of the transistors. If no constraint exists on the noise and linearity of the amplifier and only the gain and bandwidth should satisfy a set of given conditions, the two transistors should be biased at a current density that maximizes their Transconductance. Thus small width can be chosen for first transistor [1]-[10]. This improves the bandwidth and lowers the power consumption of the amplifier [1]. The width of other transistors is determined from ratio of width of the transistors. If number of stages is increased in amplifier, gain is increased but complexity of the circuit is increased which lower down the speed of the circuit.

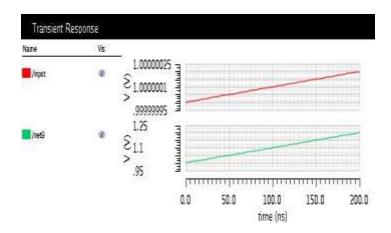

As a part of analysis of gain, bandwidth and slew rate of Darlington feedback amplifier, a simulated graph showing transient response of single stage Darlington feedback amplifier is generated based upon the

step of simulation and running of referred circuit model on Cadence analog and digital system design tools of GPDK 45nm technology. As shown in Figure 5, response graph indicate that the output voltage is in amplified form as compared to the input voltage.

Figure 5. This graph shows the results of the transient response of schematic presented in Figure 3

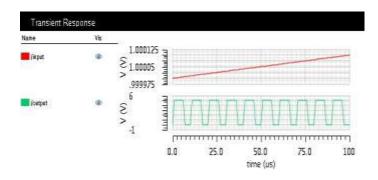

This transient response graph is obtained from schematic diagram of three stage Darlington feedback amplifier on cadence analog and digital system design tools of GPDK 45nm technology. As shown in Figure 6, the transient response signal is indicated to be more amplified in comparison to response signal in Figure 4. It means that if we increase the number of stages in Darlington feedback amplifier, the gain is enhanced especially in case of three stage amplifier.

Figure 6. This diagram depicts the transient response graph of three stage Darlington feedback amplifier, which is obtained from the circuit diagram presented in Figure 4.

In an earlier paper [13], there is a report on increase in 30% resistive biased Darlington Amplifier with reference to constant input power at 16 dBm, supply current of 14 mA at 1.8 GHz and supply current of 14.6 mA at 900 MHz. In present case, we found up to 32% enhancement for resistive biased Darlington Feedback Amplifier. If we increase the stages in Darlington amplifier to enhance the gain, then maintenance of gain flatness is very difficult [1]. Further, to maintain the linearization of the circuit, the supply voltage and size of the transistors should be high enough [1]. In this work, especially in three stage Darlington amplifier, the supply voltage is 1.8 volt and the size of transistors (W1/W2=1) and (W2/W3=1), which means that all three transistors have same width and responsible for the improvement of slew rate of three stage Darlington amplifier circuit. Additionally, there is possibility of increase in the speed of used Darlington amplifier circuit.

In this paper, various important parameters of respective single stage and two stage amplifiers are calculated based on simulation results and the outcomes as listed in Table 1 to establish the rapid comparison specifically qualitatively Figure 6, Figure 7 and Table 1. At present, data obtained in this paper suggest that gain of three stage can be achieved up to three times compared to single stage Darlington pair feedback

amplifier. Bandwidth is also calculated in single stage and three stage Darlington amplifier, (single stage 0.7-28.4 dB, three stage 1.6-26.8 dB). Slew rate is also increased in case of three stage Darlington amplifier Figure 6, Figure 7 and Table 1. In this paper, authors compared data with an earlier reported broadband Darlington amplifier that showed a gain of 13.2 dB and bandwidth of 25.3 GHz by using HEMT-HBT configuration [2]. By comparison, our data support the existing notion that by increasing stage of Darlington feedback amplifier, there is an increase in gain of amplifiers as appeared in the present work. Another work on Darlington feedback amplifier [5] also reported on the gain of 14.5 dB and bandwidth of 12.3 GHz on three stage using 500nm pHEMT configuration, which is comparable to proposed circuit and found gain of 18.1 dB and bandwidth of 1.6-26.8 GHz. In this work three stage Darlington feedback amplifier has high slew rate due to which speed is also increased and also improves the stability of the system. This work shows 15% improvement in slew rate of three stage Darlington feedback amplifier. Taken together, by comparing earlier reported papers [1], [2], [5], our proposed circuit can be useful in enhancing gain, bandwidth and slew rate for better stability of Darlington feedback amplifier (Table 1).

Table 1. This table shows the values of referred single stage and three stage Darlington feedback amplifier model. These values are calculated by using calculator on cadence analog and digital system design tools of GPDK 45nm technology.

| Ampiner Model |      |           |             |             |              |  |

|---------------|------|-----------|-------------|-------------|--------------|--|

| Ref           | GAIN | BANDWIDTH | SLEW RATE   | PROCESS     | Stage of     |  |

|               | (dB) | (GHz)     | $(\mu V/S)$ |             | amplifier    |  |

| [1]           | 6    | 0.8-32.7  | 991         | 250nm pHEMT | Single       |  |

| [1]           | 17.8 | 1.5-29.5  | 1019        | 250nm pHEMT | Three        |  |

| [5]           | 14.5 | 12.3      | -           | 500nm pHEMT | Three        |  |

| [2]           | 13.2 | 25.3      | -           | HEMT-HBT    | Two stage    |  |

| This work     | 6.8  | 0.7-28.6  | 1007        | 45nm GPDK   | Single stage |  |

| This work     | 18.1 | 1.6-26.8  | 1171        | 45nm GPDK   | Three stage  |  |

Table 1. This Table Shows the Values of Referred Single Stage and Three Stage Darlington Feedback

#### 4. CONCLUSION

Based on the comparative analysis of data, authors conclude that the gain of three stage Darlington feedback amplifier can be possible up to three times compared to single stage Darlington feedback amplifier. In this paper, analysis between single stage and three stage Darlington feedback amplifier, slew rate is appreciably increased. However, in future work slew rate may be further increased by applying a slew rate booster circuit in above proposed Darlington feedback amplifier. By increasing the slew rate of Darlington amplifier, there is an opportunity to increase the speed of the amplifier by changing the value of load capacitor. Therefore, by using above approach, the performance of Darlington feedback amplifier can be enhanced for use mobile applications and other portable devices.

#### REFERENCES

- [1] Gholamreza Nikandish, Ali medi, "Design and Analysis of Broadband Darlington Amplifiers with bandwidth Enhancement in GaAs pHEMT technology", *IEEE Transactions on microwave Theory and Technique*, Vol.62, No.8, pp.1705-1715, August 2014.

- [2] Shou-hsien Weng, Hong-Yeh Chang, Chau-Ching Chiong, Yu-Chi Wang, "Gain-Bandwidth Analysis of Broadband Darlington amplifiers in HBT-HEMT process", *IEEE Transaction on Microwave Theory and Techniques*, Vol.60, No.11, pp. 3458-3472, November 2012.

- [3] Michael A. Oakley, Uppili S. Raghunathan, Brian R. Wier, Partha Sarathi Chakraborty, John D. Cressler, "Large-Signal Reliability Analysis of SiGe HBT Cascode Driver Amplifiers", *IEEE Transaction on Electron Devices*, Vol.62, No.5, pp. 1383-1389, May 2015.

- [4] Rashmi Singh, Rajesh Mehra, "Analysis of Darlington pair amplifier at 90nm technology", International Conference on Electrical, Electronics, and Optimization Techniques, pp. 3637-3641, 2016.

- [5] Kevin W.Kobayashi, "Linearized Darlington Cascode amplifier employing GaAs pHEMT and GaN HEMT technologies", *IEEE Journal of solid-state circuits*, Vol.42, No.10, pp.2116-2122, October 2007.

- [6] Kuei-Cheng Lin, Hwann-Kaeo Chiou, Kuan-Hsiu Chien, Tsung-Yu Yang, Po-Chang Wu, Chun-Lin Ko, Ying-Zong Juang, "A 4.2-mW 6-dB Gain 5-65-GHz Gate-pumped Down- conversion Mixer using Darlington cell for 60-GHz CMOS Receiver", *IEEE Transaction on Microwave Theory and Techniques*, Vol.61, No.4, pp.1516-1522, April 2013.

- [7] Kuan-Hsiu Chien, Jian-Ying Chen, Hwann-Kaeo Chiou, "Designs of K-band divide-by-2 and divide-by-3 injection-locked frequency divider with Darlington Topology", *IEEE Transaction on Microwave Theory and Techniques*, Vol.63, No.8, pp.2877-2888, September 2015.

- [8] Pin-Cheng Huang, Kun-you Lin, Huei Wang, "A 4-17 GHz Darlington Cascode Broadband medium power amplifier in 0.18-μm CMOS Technology", *IEEE Microwave and Wireless Components Letters*, Vol.20, No.1, pp. 43-45, January 2010.

- [9] H.-K. Chiou, I- S. Chen and W.-C Chen, "High gain V- band active integrated antenna transmitter using Darlington pair VCO in 0.13µm CMOS process" *Electronics Letters*, Vol.46, No. 5, pp.321-322, March 2010.

- [10] Devasis Haldar, Shagun Panwar, Vipul Kumar, Ayush Goswami, Sakshi Dhawan "Circuits for Optical Based Line of Sight Voice Communication" *Bulletin of Electrical Engineering and Informatics (BEEI)*. ISSN: 2302-9285. Vol. 6, No. 1, March 2017, pp.

- [11] Asif Ahmed. Feedback Linearization of RF Power Amplifier for TETRA Standard", Bulletin of Electrical Engineering and Informatics (BEEI). Vol. 3, No. 3, September 2014, pp. 161-172

- [12] Hai-Tao Zhang; Qing Wang; Zhiyong Chen; Fei-Long Wei. Dynamics and Feedback Control of Electrospinning Processes. *IEEE Transactions on Control Systems Technology*. Year: 2017, Volume: 25, Issue: 2. Pages: 611 - 618

- [13] J.- S. Paek, B. Park and S. Hong, "CMOS LNA with Darlington pair for UWB system", *Electronics Letters*, Vol. 42, No. 16, pp.913-914, August 2006.

- [14] T.K. Lee, W.S. Chan and Y.M. Siu, "Darlington feedback amplifier with good bias stability under large signal conditions", *Electronics Letters*, Vol.40, No.20, pp.1271-1272, September 2004.

- [15] Chatham Saigon, Andreas Demosthenes, Xiao Liu, Outer A. Serein, "A compact Rail-to-rail class-AB CMOS buffer with slew-rate enhancement", *IEEE Transaction On Circuits And Systems*, Vol.59, No.8, PP.486-490, August 2012.

- [16] Abhishek Pandey, Subhas Chakraborty, Vijay Nat, "slew rate enhancing technique in Darlington pair based CMOS OP-AMP", ARPN Journal of Engineering and Applied Sciences, Vol. 10, No.9, pp.- 3970-3973, May 2015.

- [17] Inyong Kwon; Taehoon Kang; Byron T. Wells; Lawrence J. D'Aries; Mark D. Hammig. A High-Gain 1.75-GHz Dual-Inductor Transimpedance Amplifier With Gate Noise Suppression for Fast Radiation Detection. *IEEE Transactions on Circuits and Systems II: Express Briefs*. Year: 2016, Volume: 63, Issue: 4.

- [18] Roger Yubtzuan Chen; Zong-Yi Yang CMOS Transimpedance Amplifier for Gigabit-per-Second Optical Wireless Communications. *IEEE Transactions on Circuits and Systems II: Express Briefs*. Year: 2016, Volume: 63, Issue: 5. Pages: 418 – 422.

- [19] Abhishek Pandey, Subhra Chakraborty, Vijay Nath, "A Darlington Pair Transistor Based Operational Amplifier", Global Conference on Communication Technologies, pp.273-276, 2015.

- [20] Tran Van Hoi, Ngo Thi Lanh, Nguyen Xuan Truong, Nguyen Huu Duc, Bach Gia Duong. et al., "Design of a Front-End for Satellite Receiver", *International Journal of Electrical and Computer Engineering (IJECE)*. Vol. 6, No. 5, October 2016, pp. 2282~2290.