Bulletin of Electrical Engineering and Informatics ISSN: 2302-9285 Vol. 5, No. 2, June 2016, pp. 213~218, DOI: 10.11591/eei.v5i2.531

213

## Selection of Gate Dielectrics for ZnO Based Thin-Film Transistors

#### Vaibhav Garg\*<sup>1</sup>, Navneet Gupta<sup>2</sup>

Department of Electrical and Electronics Engineering, Birla Institute of Technology and Science Pilani–Rajasthan, India, 333031 \*Corresponding author, e-mail: vaibhavgarg1995@gmail.com<sup>1</sup>, ngupta@pilani.bits-pilani.ac.in<sup>2</sup>

#### Abstract

The bulk of semiconductor technology has been based on silicon till today. But silicon has its own limitations. It is not transparent to visible light and hence it cannot be used in certain applications. ZnO is a material which is transparent to visible light. In this paper, we compare the electrical performance of ZnO Thin film Transistors using different gate insulators. Certain performance indices and material indices were considered as the selection criteria for electrical performance. A methodology known as Ashby's approach was adopted to find out the best gate insulators and based on this methodology various charts were plotted to compare different properties of competing materials. This work concludes that  $Y_2O_3$  is the best insulator followed by  $ZrO_2$  and HfO<sub>2</sub>.

Keywords: ZnO, TFTs, Ashby and dielectrics

#### 1. Introduction

There has been a rapid advancement in semiconductor technology in recent years. Most of the semiconductor technology has been based on silicon. Most of the transistors are made of silicon but silicon is not a transparent material to visible light. It has been found out that transparent materials have the potential to improve the performance of the electronics currently used in LCD display screens. ZnO being a wide band gap (3.4 eV) semiconductor is transparent to visible light and can be used for transparent electronics. ZnO based Thin Film Transistors are being realized [1]. Also the current scenario involves large number of transistors installed on a single chip. The numbers of transistors on a single chip are increasing in accordance with Moore's Law. Due to scaling, problems of leakage current arise in the device. The electrons tunnel through the gate insulator leading to leakage current. It is desirable to increase the capacitance of gate insulator to obtain better drain current. Thus scaling is limited by the leakage current and therefore to improve the capacitance it is necessary to look for materials which have high dielectric constant.

The current technology requires low voltage operation transistors with low power consumption. The gate dielectric affects the performance of the transistors significantly. Hence it is necessary to understand how the gate dielectric affects the electrical properties of the transistors. A study was conducted to find out which gate insulators have been used in ZnO Thin Film Transistors and how they affect the electrical performance of these transistors. Some of the materials that were studied included SiO<sub>2</sub>, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub> and BaSrTiO<sub>3</sub>.

Each material possess some good material properties to be used as gate insulators but at the same time it lacks on providing some performance parameters of the device. Therefore a proper methodology has to be followed to find out the gate insulators with best electrical performance in ZnO Thin Film Transistors. A well-established method of material selection is Ashby's Approach proposed by Ashby [2].

The paper is organized as follows: Section 2 explains the device structure of ZnO TFT, section 3 covers the criteria for electrical performance of the device, section 4 illustrates the various steps involved in Ashby's Approach, section 5 includes results and discussion, section 6 describes the final conclusion and section 7 gives an insight into future scope of work.

### 214 🔳

#### 2. Device Structure

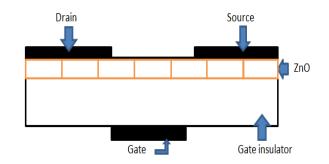

Figure 1 shows a schematic view of ZnO Thin Film Transistor in a bottom gate configuration. Transparent and conducting polycrystalline ZnO thin films can be deposited on glass substrate. These films are composed of nano-crystals with grain size ranging from 50 to 100 nm and, consequently, contain high density of grain boundaries (GBs). These GBs in general contain wide distribution of deep level traps.

Figure 1. Cross-sectional view of ZnO TFT

# 3. Criteria for Electrical Performance *Performance Indices:*

#### a) Drain Current

To obtain a higher drain current for a given gate to source voltage, the capacitance of the gate insulator has to be increased as indicated by the following equation:

$$I_{D} = \mu C_{ox}(W/L)[(V_{GS} - V_{T})V_{DS} - (1/2)V_{DS}^{2}]/2$$

(1)

where

$C_{ox} = \mathcal{E}_{ox} / t_{ox}$  is the capacitance per unit area

The value of  $t_{ox}$  cannot be decreased beyond a certain value due to leakage current. Hence we need a higher  $\mathcal{E}_{ox}$  to have higher drain current.

From (1) it is clear that higher mobility value ( $\mu$ ) enhances the drain current.

#### b) Leakage Current

To obtain better electrical performance it is necessary to have low leakage current. The equation for leakage current is given by (2).

J<sub>G</sub>=b×exp{-a×f×t<sub>ox,eq</sub>}[3]

(2)

where a is a constant, b is a pre-exponential factor and f is entirely dependent on the essential material properties of the gate dielectric like carrier effective mass in the dielectric, tunneling barrier height in eV and dielectric constant. Here f is directly proportional to dielectric constant of gate insulator. Hence to decrease leakage current density, f should be high or dielectric constant of gate insulator must be high.

The conduction band offset must also be high to decrease leakage current. (As the high energy barrier will decrease the density of electrons and holes crossing the barrier.)

#### c) Subthreshold Slope

Another performance index is the subthreshold slope S which refers to the increase required in gate voltage to increase the drain current (in saturation) by a decade.

Subthreshold slope

$$S=dV_G/d(logI_{DSAT})$$

(3)

where I<sub>DSAT</sub> refers to drain current in saturation mode. It is clear from the expression that to have better electrical performance, S should be lower. So subthreshold slope should be less.

#### d) Threshold Voltage

It is defined as the minimum voltage required to induce the channel in case of enhancement mode transistor. In case of depletion mode transistor it is defined as the negative voltage required to turn-off the device.

Threshold Voltage depends on a number of factors like gate insulator, temperature, channel doping and impurities at surface. So it is difficult to relate threshold voltage directly with gate insulator.

#### e) ION / IOFF Ratio

This ratio must be high as it signifies higher current when transistor is ON and lower leakage current when transistor is OFF.

#### Material Indices:

#### a) Dielectric constant

Dielectric Constant of gate insulator must be high as it reduces leakage current, increases drain current by increasing capacitance of insulator and also allows better scaling of transistor.

#### b) Mobility

Mobility must be high to have higher drain current.

#### c) Conduction Band Offset

It is required to have high conduction band offset to have lower leakage current.

#### 4. Ashby's Approach

This approach involves comparing simultaneously the competing properties of various materials and choosing the material with optimum performance under given constraints. The four steps involved in this approach are:

(i) Translation of design requirements

(ii) Screening using constraints

(iii) Ranking using objectives

(iv) Seek supporting information and compare with experimental results [3].

Here Ashby's Approach is used to find out the gate insulator with optimum electrical performance.

| Table 1. | <b>Franslation</b> | of Design | Requiremer | nts as | per Ashby | 's Approach |

|----------|--------------------|-----------|------------|--------|-----------|-------------|

|          |                    |           |            |        |           |             |

| Function       | Gate insulator                  |  |  |  |

|----------------|---------------------------------|--|--|--|

| Objective      | Maximize Dielectric Constant    |  |  |  |

|                | Maximize Conduction Band Offset |  |  |  |

|                | Minimize Subthreshold Slope     |  |  |  |

| Constraints    | High Band Gap                   |  |  |  |

|                | High Dielectric Constant        |  |  |  |

| Free Variables | Choice of Material              |  |  |  |

|                | Objective<br>Constraints        |  |  |  |

Screening is done by plotting various parameters for available gate insulators.

#### 5. Results and Discussion

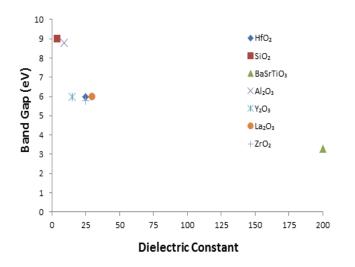

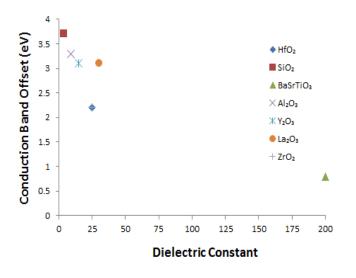

Based on the data obtained from [4], the interrelationship between material indices are plotted and shown in Figure 2 and Figure 3. So, Figure 2 shows the variation of band gap with dielectric constant and Figure 3 shows the variation of conduction band offset with dielectric constant.

Figure 2. Band Gap for materials with different dielectric constants

Figure 3. Conduction Band Offset for materials with different dielectric constants

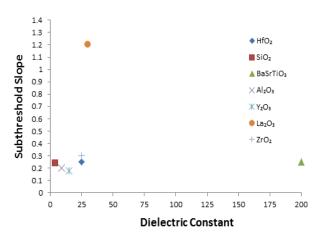

Figure 4. Subthreshold slope for materials with different dielectric constants

It can be observed from the plots that  $HfO_2$ ,  $Y_2O_3$ ,  $La_2O_3$  and  $ZrO_2$  have a high dielectric constants (15-30), a considerable band gap (5.8-6 eV) and conduction band offset (2.2-3.1 eV).  $Al_2O_3$  has a considerable conduction band offset but its dielectric constant (9) is low in comparison to others.  $SiO_2$  also has the same constraint of low dielectric constant (3.9).  $BaSrTiO_3$  has a high dielectric constant but the conduction band offset is very low (.8 eV) and thus there could be possibility of high leakage current. Hence we found that  $HfO_2$ ,  $Y_2O_3$ ,  $La_2O_3$  and  $ZrO_2$  are the possible candidates that satisfy the constraints of high dielectric constant and a considerable band gap and conduction band offset.

Figure 4 shows the relationship between subthreshold slope and and dielectric constant based on the data obtained in [5-11]. It can be observed that all the materials except La<sub>2</sub>O<sub>3</sub> have subthreshold slope lying in the range of .18-.23 V/decade. La<sub>2</sub>O<sub>3</sub> has a very high subthreshold slope of 1.2 V/decade and hence the electrical performance will be poorer in comparison to others.

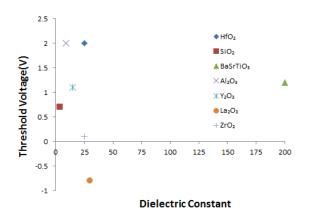

Figure 5. Threshold Voltage for materials with different dielectric constants

Figure 5 shows the relationship between threshold voltage and dielectric constant based on the data obtained in [5-11]. The values are highly scattered as threshold voltage depends on some other factors also. The negative value of threshold voltage of La<sub>2</sub>O<sub>3</sub> suggests that it acts as depletion type thin film transistor. HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have relatively high threshold voltages. Based on the above plots, it may be concluded that Y<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub> possess better performance indices as compared to others.

#### 6. Conclusion and Future Works

The key motivation for this study was to find out the gate insulators that provide best electrical performance in ZnO based Thin film Transistors. In this paper, certain performance indices and material indices were considered as the selection criteria for electrical performance. A methodology known as Ashby's Approach was adopted to find out the best gate insulators and based on this methodology various charts were plotted to compare different properties of competing materials. Using these charts, we conclude that we can arrange the gate insulators in the ranking given below:

A further study can be done to find out the best gate insulator. One of the performance indices that can be considered for further selection can be drain current given as follows:

$I_D = \mu_{eff}C_{ox} (W/L)[(V_{GS} - V_T) V_{DS} - (1/2) V_{DS}^2]/2$

<sup>1.</sup> Y<sub>2</sub>O<sub>3</sub>

<sup>2.</sup> ZrO<sub>2</sub>

<sup>3.</sup> HfO<sub>2</sub>

(4)

Drain current can be compared for these materials for similar device structure, geometry and doping profile. The deciding parameters will be  $\mu_{eff}$  and dielectric constant of the materials keeping all other parameters same.

$\mu_{eff}$  can be computed using (4).

$$\mu_{eff}=2\mu_{o}\Theta(V_{G}-V_{T})/(1+\Theta^{2}(V_{G}-V_{T})^{2})[12]$$

where  $\mu_0$  is low-field mobility and  $\Theta$  is mobility degradation factor.

Hence we can compute drain current for different materials and find out the best gate insulator.

#### References

- [1] Hossaina FM, Nishii J, Takajib S, Ohtomo A, Fukumura A. Modeling and simulation of polycrystalline ZnO thin-film transistors. *Journal of Applied Physics*. 2003; 94(12): 7768-7777.

- [2] Ashby MF. Materials selection in mechanical design. 2nd ed. Oxford (UK): Butterworth-Heinemann. 1999.

- [3] Gupta N & Aditya BN. Material selection methodology for gate dielectric material in metal-oxidesemiconductor devices. *Materials and Design*. 2012; 35: 696-700.

- [4] Robertson J & Falabretti B. Band offsets of high K gate oxides on high mobility semiconductors. *Materials Science and Engineering.* 2006; 135(3): 267-271.

- [5] Kim JK, Ahn BD, Lee CH, Jeon KA, Kang HS, Lee SY. Characteristics of transparent ZnO based thin-film transistors with amorphous HfO<sub>2</sub> gate insulators and Ga doped ZnO electrodes. *Thin Solid Films*. 2008; 516: 1529-1532.

- [6] Cramer G. Electrical Engineering, The Cooper Union for the Advancement of Science and Art. Fabrication and Comparison of ZnO Thin Film Transistors with Various Gate Insulators. *Electronics:* NNIN REU 2006 Research Accomplishments. 2006: 34-35.

- [7] Siddiqui J, Cagin E, Chen D, Phillips JD. ZnO thin-film transistors with polycrystalline (Ba, Sr) TiO<sub>3</sub> gate insulators. *Applied Physics Letter*. 2006; 88(212903).

- [8] Lan L, Peng J. High-Performance Indium–Gallium–Zinc Oxide Thin-Film Transistors Based on Anodic Aluminum Oxide. *Electron Devices (IEEE Transactions)*. 2011; 58(5).

- [9] Cho YJ, Shin JH, Bobade SM, Kim YB, Choi DK. Evaluation of Y<sub>2</sub>O<sub>3</sub> gate insulators for a-IGZO thin film transistors. *Thin Solid Films*. 2009; 517(14): 4115-4118.

- [10] Moon YK, Lee S, Park JW. Characteristics of ZnO-based TFT Using La<sub>2</sub>O<sub>3</sub> High-k Dielectrics. *Journal of the Korean Physical Society.* 2009; 55(5): 1906-1909.

- [11] Xifeng L, Enlong X, Jianhua Z. Low-Temperature Solution-Processed Zirconium Oxide Gate Insulators for Thin-Film Transistors. *IEEE Transactions on Electron Devices*. 2013; 60(10).

- [12] Cheralathan M, Chang SJ, Bawedin M, Bayraktoraglu B, Lee JH, Iniguez B, Cristoloveanu S. Mobility Models for ZnO TFTs. 8th International Caribbean Conference on Devices, Circuts and Systems (ICCDCS). 2012.