Bulletin of Electrical Engineering and Informatics Vol. 3, No. 4, December 2014, pp. 245~250 ISSN: 2089-3191

245

# A Comparision of Three Phase 27 Level Inverter Scheme under No Load and Multiple Load Conditions

## C. Kannan, C.K. Kishore\*

Department of Electrical and Electronics Engineering, Arunai Engineering College, Anna University, India \*Corresponding author, email: ckkusb@gmail.com

#### Abstract

Multilevel inverters have been used in the industrial as well as the drive applications. Here three phase system of the 27 level inverter scheme with and without loads have been presented by combining the three single phase inverters of various and asymmetrical voltage ranges. Here capacitors, batteries may be used for multiple dc sources in order to achieve high voltage output. It is shown that by implementing the single phase model in the three phase system the harmonic content is lowered even in the loaded conditions than compared to the single phase system. The proposed method can be validated and simulation is carried out with the help of MATLAB/Simulink software.

Keywords: Cascaded H-Bridge, Total Harmonic Distortion, Isolated DC sources

#### 1. Introduction

Major industrial applications have been implementing the concept of multilevel inverter. Several motor drives and utility applications require medium as well as high voltage and power at megawatt level [1-5]. Numerous multilevel converter topologies have been developed.

Power converters are an enabling technology for industrial processes powered by electric drive systems. They are potentially useful for a wide range of applications: transport, energy conversion, manufacturing, mining, and petrochemical, to name a few. Many of these processes have been continuously increasing their demand of power to reach higher production rates, cost reduction, and efficiency [1].

Three major multilevel converter structures have been applied in industrial application: cascaded H-bridges converter with separate dc sources, diode clamped, and flying capacitors [1, 2]. A multilevel converter achieves high power ratings and enables the use of renewable energy resources with good voltage output [6-8].

Multilevel inverter is a device capable of producing different Voltage Levels. Each capacitor voltage En is given by,

$$EN = \frac{Vdc}{m-1}$$

(1)

where 'm' denotes the number of levels [9].

The cascaded multilevel inverter consists of series connection of single phase full bridge inverter. The common function of multilevel inverter is to synthesize a desired voltage from several separate DC sources. Each inverter is able to generate three different output voltages,  $+V_{dc}$ , 0 and  $-V_{dc}$  i.e. positive, negative and zero voltages accordingly [10].

## 2. Proposed Method

The proposed topology is realized by cascading three conventional two-level inverters, fed from asymmetrical isolated dc voltage sources [6]. It improves the efficiency of the overall system. Here pulse width modulation scheme is used. This type of inverter system is flexible for generating different medium and high voltage levels for ASD applications. This feature enables

the proposed topology to be suitable for powering constant torque as well as variable torque type loads [3].

Proposed method of the MLI has three different input stages. The proposed inverter topology requires only 3 universal bridges instead of the 12 switches.

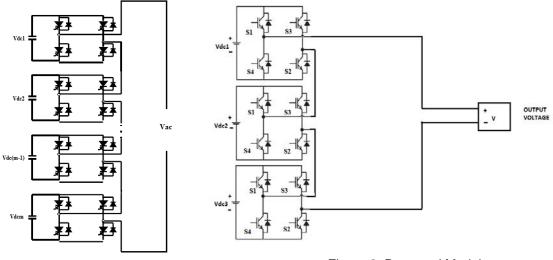

Figure 1. Conventional Multilevel Inverter

The topology of the proposed DC–AC cascaded H-bridge multilevel inverter is shown in Figure 2. The inverter uses a standard three-leg and an H bridge with its dc source in series with each phase leg. In the proposed method of the inverter, there are three input stages. All the modules are connected as new hybrid with each module having power switches [8]. The power switches may be IGBT, MOSFET or any other power devices. The switching is as S1=S3 and S2= S4 [9]. The number of levels in cascaded MLI is increased by connecting more number of modules [11]. The space vector modulation is used for the three phase system while the single phase system uses only the pulse width modulation system [7, 11].

Cascaded H-bridge cells are connected in series hence, the synthesized voltage waveform is the sum of all individual cell outputs [6, 5].

The new hybrid multilevel inverter consists of full bridge modules which have the relationship of  $1V_{dc}$ ,  $3V_{dc}$ ,  $9V_{dc}$ .... $3^{s-1}V_{dc}$  for dc link Voltage. The output waveform has 27 levels,  $\pm 1300V$ ,  $\pm 1200V$ ,  $\pm 1100V$ ,  $\pm 1000V$ ,  $\pm 900V$ ,  $\pm 800V$ ,  $\pm 700V$ ,  $\pm 600V$ ,  $\pm 500V$ ,  $\pm 400V$ ,  $\pm 300V$ ,  $\pm 200V$ ,  $\pm 100V$ , 0V.

The main advantage of this arrangement is the simplicity to cascade several H-bridge cells for improvement of the output voltage resolution with reduced number of components.

A different dc voltage ratio for H-bridge cells is proposed to achieve the maximum number of output voltage levels [6].

The output voltage of the inverter can be described as

$$V_{out} = V_{dc1} + V_{dc2} + V_{dc3}.$$

(2)

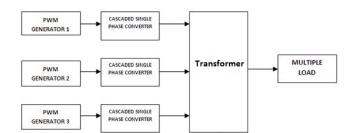

#### 3. Block Diagram

Here in this system the transformer as Figure 3 is used for connecting the multiple loads and to isolate the load from the source. However, some criteria have to be undertaken into account to achieve a stable converter operation. Supplying each cell with a unique dc voltage, can result in a high number of voltage levels [12].

Figure 2. Proposed Model

Figure 3. Block Diagram

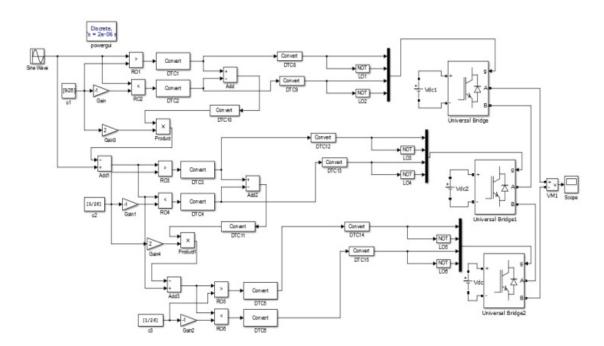

## 4. Simulation Results without Loads

The feasibility of the single-phase cascaded asymmetrical 27-level inverter can be verified using MATLAB-Simulink. It is possible to improve the spectral performance with an appropriate combination of voltage sources [4]. Thus through the simulation the circuit can be simulated according to the switching Table 1 given below.

Table 1. Comparision of Topologies

| Parameters                | Cascade              | Hybrid                      | Proposed                    |

|---------------------------|----------------------|-----------------------------|-----------------------------|

|                           | Topology             | Topology                    | Topology                    |

| No.of levels,             | 2(S)+1, 7 level      | 2 <sup>S+1</sup> – 1, 15    | 3 <sup>s</sup> ,27 levels   |

| S=3                       |                      | level                       | <b>.</b>                    |

| Input dc                  | $V_{dc}$ , $1V_{dc}$ | $2^{S-1}V_{dc}$ , $4V_{dc}$ | $3^{S-1}V_{dc}$ , $9V_{dc}$ |

| voltage (V <sub>dc)</sub> |                      |                             |                             |

The three input voltage sources is controlled at  $V_{dc1} = 100v$ ,  $V_{dc2} = 3V_{dc1}$ ,  $V_{dc3} = 9V_{dc1}$ . Corresponding lower inverter generates a fundamental output voltage of 1300V using three individual DC sources. Thus the logic used for the single phase is given below in Figure 4.

Figure 4. Simulink model of Single phase system

The basic principle of the suggested 27 level - inverter scheme is that the continuousoutput-voltage levels can be obtained by the addition or subtraction of the instantaneous voltages generated from different voltage levels. In the proposed multilevel inverter, this can be realized by an array of switching devices composing full-bridge inverter modules and proper mixing of each transformer terminal voltage [10].

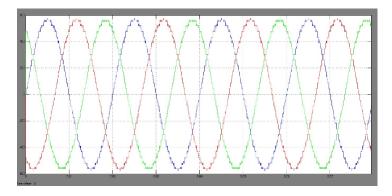

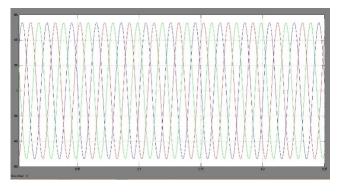

Figure 6. Three phase system without loads

In order to form the equation, fundamental component is given desired output value and all other harmonics are equated to zero. Thus the above given single phase system is converted into a block or subsystem to get the three phase systems given in the figure 6.

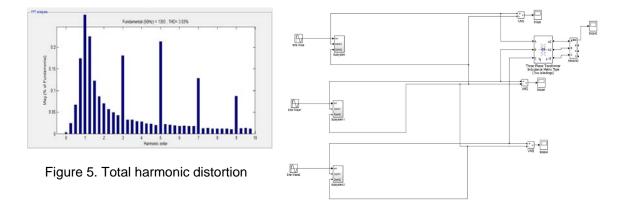

The equation which is derived for Total Harmonic Distortion of the output voltage of an inverter is used in order to reduce the harmonics that are produced in the inverter. The amount of Harmonic content is given by following formula.

$$\% THD = \sqrt{\left(\frac{1}{a_1^2} \sum_{n=5}^{\infty} (a_n^2)\right)} x_{100}$$

(3)

where  $n = 6i \pm 1$  (here i = 1, 2, 3....)

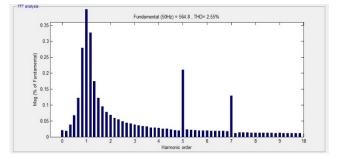

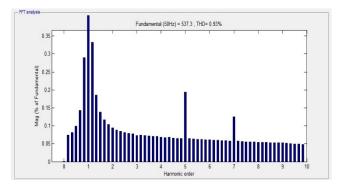

Thus the voltage and the total harmonic content of the three phase system is shown in the Figure 7 and Figure 8.

Figure 7. Voltage Waveform

Figure 8. Total Harmonic Distortion

Thus the total harmonic distortion of 2.5 percent is obtained under no load condition.

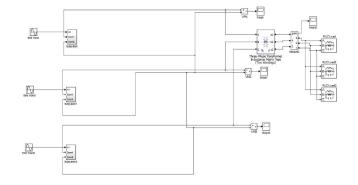

## 5. Proposed System with Multiple Loads

## 5.1. Load Parsmeters

| In Type of Load               | : Three phase Parallel RLC Load. |

|-------------------------------|----------------------------------|

| Line voltage                  | : 380 V <sub>rms</sub> .         |

| Frequency                     | : 50 Hz.                         |

| Reactive Power Q <sub>L</sub> | : 100 var.                       |

| Reactive Power Q <sub>c</sub> | : 100 var.                       |

| Loads L1                      | : 20 kW.                         |

| Loads L2                      | : 30 kW.                         |

| Loads L3                      | : 40 kW.                         |

|                               |                                  |

Figure 10. Output Voltage Waveform

Figure 11. THD Performance

Thus the three phase system with multiple loads is proved to be efficient as the total harmonic content is obtained less than 1 percent which is shown in the figure 11.

#### 6. Conclusion

Provide In this paper the simulation model has been designed by combining three asymmetrical dc sources to give 27 level single phase inverter output with a harmonic distortion of 3 percent and the output is verified using MATLAB / SIMULINK Software. THD can be reduced below 1 percent in the multiple load conditions in the three phase system compared to the harmonic content in the single phase system with harmonic content of 3 percent.

### References

- [1] J Rodriguez, JS Lai and FZ Peng. "Multilevel Inverters: Survey of Topologies, Controls, and Applications". *IEEE Transactions on Industrial Applications*. 2002; 49(4): 724-738.

- [2] JS Lai and FZ Peng. "Multilevel Converters-A new Breed of Power Converters". *IEEE Transactions on Industrial Applications*. 1996; 32: 509-517.

- [3] E Cengelci, SU Sulistijo, BO Woom, P Enjeti, R Teodorescu, and F Blaabjerg. "A New Medium Voltage PWM Inverter Topology for Adjustable Speed Drives". in Conf. Rec. IEEE-IAS Annu. Meeting, St. Louis, MO. 1998: 1416-1423.

- [4] MD Manjrekar, TA Lipo. "A Generalized Structure of Multilevel Power Converter". *IEEE Conference on Power Electronics, Drives, and Energy Systems, Australia.* 1998: 62-67.

- [5] Hossein Sepahvand, Student Member, IEEE, Jingsheng Liao, Member, IEEE, Mehdi Ferdowsi, Member, IEEE, and Keith A.Corzine, Senior Member, IEEE. "Capacitor Voltage Regulation in Single-DC-Source Cascaded H-Bridge Multilevel Converters Using Phase-Shift Modulation". *IEEE Trans. Ind. Electron.* 2013; 60(9): 3619-3626.

- [6] Alireza Nami, Student Member, IEEE, Firuz Zare, Senior Member, IEEE, Arindam Ghosh, Fellow, IEEE, and Frede Blaabjerg, Fellow, IEEE. "A Hybrid Cascade Converter Topology with Series-Connected Symmetrical and Asymmetrical Diode-Clamped H-Bridge Cells". *IEEE Trans. Power Electron.* 2011; 26(1): 51 - 65.

- [7] Anubrata Dey, Student Member, IEEE, PP Rajeevan, Rijil Ramchand, K.Mathew, and K. Gopakumar. "A Space-Vector-Based Hysteresis Current Controller for a General n-Level Inverter-Fed Drive with Nearly Constant Switching Frequency Control". *IEEE Trans. Ind. Electron.* 2013; 60(5): 1989-1998.

- [8] YS Lai and et al. "Topology for hybrid multi-level inverter". *IEEE Proc.Electr. Power Appl.* 2002; 149(6).

- [9] FS Kang, SJ Park, MH Lee, CU Kim. "An efficient multilevel synthesis approach and its application to a 27-level inverter". *IEEE Trans. Ind. Electron.* 2005; 52(6): 1600-1606.

- [10] MH Rashid. Power Electronics Handbook. Academic Press, 2001: 539-562.

- [11] V Gopi Latha, K Ratna Raju. "A DER Based Single-Phase Asymmetrical 27 Level Inverter Topology". International Journal of Modern Engineering Research. 2012; 2(5): 3220-3225.

- [12] K Corzine, Y Familiant, "A New Cascaded Multilevel H-Bridge Drive". *IEEE Transactions on Power Electronics*. 2002; 17(1): 125-131.