# TESIS DE LA UNIVERSIDAD DE ZARAGOZA

2019

150

#### Manuel Fernández Martínez

Towards a More Flexible, Sustainable, Efficient and Reliable Induction Cooking: A Power Semiconductor Device Perspective

Departamento

Ingeniería Electrónica y Comunicaciones

Director/es

Perpiñá Giribert, Xavier Jordà i Sanuy, Xavier

http://zaguan.unizar.es/collection/Tes

#### **Tesis Doctoral**

#### TOWARDS A MORE FLEXIBLE, SUSTAINABLE, EFFICIENT AND RELIABLE INDUCTION COOKING: A POWER SEMICONDUCTOR DEVICE PERSPECTIVE

#### **Autor**

#### Manuel Fernández Martínez

Director/es

Perpiñá Giribert, Xavier Jordà i Sanuy, Xavier

#### UNIVERSIDAD DE ZARAGOZA

Ingeniería Electrónica y Comunicaciones

2018

Repositorio de la Universidad de Zaragoza – Zaguan http://zaguan.unizar.es

# TOWARDS A MORE FLEXIBLE, SUSTAINABLE, EFFICIENT AND RELIABLE INDUCTION COOKING:

#### A Power Semiconductor Device Perspective

Thesis dissertation presented to obtain the qualification of Doctor of Philosophy from the Electronic Engineering Department of University of Zaragoza

#### **Author:**

Manuel Fernández Martínez

#### **Supervisors:**

PhD Xavier Perpiñà Giribet

PhD Francesc Xavier Jordà Sanuy

#### **Assigned Tutor:**

PhD Jesús Acero Acero

INSTITUTO DE MICROELECTRÓNICA DE BARCELONA CENTRO NACIONAL DE MICROELECTRÓNICA (IMB-CNM) CONSEJO SUPERIOR DE INVESTIGACIONES CIENTÍFICAS (CSIC)

#### **UNIVERSITY OF ZARAGOZA**

#### PUBLICATIONS COMPENDIUM

This thesis is presented as a compendium of articles published or accepted for its publication to obtain the Doctor of Philosophy degree in Electronics Engineering at the University of Zaragoza, following the agreement of 20<sup>th</sup> December 2013 of the Governing Council of the University of Zaragoza on the Regulation for Doctoral Theses.

The publications that are part of the thesis and which have been published in journals indexed in the Journal of Citation Reports are:

- [1] M. Fernández, X. Perpiñà, J. Rebollo, M. Vellvehi, D. Sánchez, T. Cabeza, S. Llorente, and X. Jordà, "Solid State Relay Solutions for Induction Cooking Applications based on Advanced Power Semiconductor Devices," *IEEE Transactions on Industrial Electronics*, doi: 10.1109/TIE.2018.2838093. (In press). (Impact Factor: 7.050) URL: <a href="https://ieeexplore.ieee.org/document/8365104/">https://ieeexplore.ieee.org/document/8365104/</a>

- [2] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, X. Jordà, and M. Tack, "P-GaN HEMTs Drain and Gate Current Analysis Under Short-Circuit," *IEEE Electron Device Letters*, vol. 38, no. 4, pp. 505-508, April 2017, doi: 10.1109/LED.2017.2665163.

(Impact Factor: 3.433) URL: <a href="https://ieeexplore.ieee.org/document/7845577/">https://ieeexplore.ieee.org/document/7845577/</a>

[3] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, M. Tack, and X. Jordà, "Short-Circuit Study in Medium-Voltage GaN Cascodes, p-GaN HEMTs, and GaN MISHEMTs," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 9012-9022, Nov. 2017, doi: 10.1109/TIE.2017.2719599.

(Impact Factor: 7.050) URL: https://ieeexplore.ieee.org/document/7956198/

The publications that are part of the thesis and which have been published in international conferences are:

[4] M. Fernández, X. Perpiñà, M. Vellvehi, X. Jordà, T. Cabeza, and S. Llorente, "Analysis of solid state relay solutions based on different semiconductor technologies," in *Proc. European Conference on Power Electronics and Applications* (EPE), Warsaw, Sept. 2017, pp. P.1-P.9, doi: 10.23919/EPE17ECCEEurope.2017.8099012.

URL: <a href="https://ieeexplore.ieee.org/document/8099012/">https://ieeexplore.ieee.org/document/8099012/</a>

[5] M. Fernández, X. Perpiñà, M. Vellvehi, D. Sánchez, X. Jordà, J. Millán, T. Cabeza and, S. Llorente, "Analysis of bidirectional switch solutions based on different power devices," in *Proc. Spanish Conference on Electron Devices* (CDE), Barcelona, Feb. 2017, pp. 1-4, doi: 10.1109/CDE.2017.7905220.

URL: <a href="https://ieeexplore.ieee.org/document/7905220/">https://ieeexplore.ieee.org/document/7905220/</a>

[6] M. Fernández, X. Perpiñà, M. Vellvehi, X. Jordà, J. Roig, F. Bauwens and M. Tack, "Short-circuit capability in p-GaN HEMTs and GaN MISHEMTs," in *Proc. International Symposium on Power Semiconductor Devices and ICs* (ISPSD), Sapporo, May 2017, pp. 455-458. doi: 10.23919/ISPSD.2017.7988916.

URL: https://ieeexplore.ieee.org/document/7988916/

The patents that are part of the thesis and which have been published are:

- [7] T. Cabeza, M. Fernández, X. Jordà, S. Llorente, I. Millán, X. Perpiñà, D. Sánchez, and

M. Vellvehi, "Dispositivo de aparato doméstico", Application number:

P201631613 (19.12.2016), Publication number: ES2673129 A1 (19.06.2018).

- [8] T. Cabeza, M. Fernández, X. Jordà, S. Llorente, I. Millán, X. Perpiñà, D. Sánchez, and

M. Vellvehi, "Haushaltsgerätevorrichtung", Application number:

DE201710222394 (11-12-2017), Priority number: ES20160031613 (19.12.2016).

The publications that are part of the thesis and are in writing process:

- [9] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, S. Llorente, and X. Jordà, "Feedback Oscillations in Super-Junction MOSFET-based Solid State Relays," *IEEE Transactions on Power Electronics* (In writing process).

- [10] M. Fernández, M. Vellvehi, X. Jordà, and Xavier Perpiñà, "Power Losses and Current Distribution Extraction in IGBTs under Resonant Load and ZVS Condition," *IEEE Transactions on Power Electronics*. (In writing process).

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all the Microelectronics Institute of Barcelona

First, both Xavier Jordà and Xavier Perpiñà. I have enjoyed very much working with you over the past 3 years. I am very thankful that I had the opportunity of developing this PhD thesis together. From this collaboration, it emerged a bridge among power electronics and power semiconductor devices which I had the wonderful fortune to cross. Moreover, thank you for letting me to be the visible face of our work at the many journals and international conferences where I have participated, and now, of this doctoral thesis, which would have been impossible to successfully conclude without your advice. In addition, I would like to thank José Rebollo for his teachings in semiconductor devices, the university lost an outstanding professor. Additionally, many thanks to Miquel Vellvehi for his technical support concerning the development and analysis of infrared Thermographies. Finally, I wish we had more time, José Millán.

The developed test setups would not have worked with first time success without the help of David and Fede. Thank you very much for your fellowship and excellent work. Furthermore, I would also like to thank those who were our partners and are my actual colleagues in BSH: Sergio Llorente and Tomás Cabeza.

As well, I wish to thank Viorel Banu for sharing his experiences with me. I learned a lot from your professional and life lessons. Also, many thanks for your advice concerning my future professional life. In this regard, I extend my thanks also to José Rebollo, Philippe Godignon, Alberto García, Xavier Perpiñà, Xavier Jordà and Miquel Vellvehi.

Of course, my stay at the IMB-CNM would not have been the same without my colleagues Pablo, Arnau, María, Víctor, Javi, Matthieu, Bernat, Raphaela, Íñigo, Mar and Eric. I wish to pay a special recognition to Alberto for everything he had taught me, for being such a good listener and for his willingness to help.

Dedicated to my beloved family; my parents and my brother. The perfect image of honesty.

#### **ABSTRACT**

This thesis is focused on addressing a more flexible, sustainable, efficient and reliable induction cooking approach from a power semiconductor device perspective. In this framework, this PhD thesis has identified the following activities to cover such demands:

- In view of the growing interest for an effective power multiplexing in Induction Heating (IH) applications, improved and efficient Solid State Relay (SSR) alternatives to electromechanical relays (EMRs) are deeply investigated. In this context, emerging Gallium Nitride (GaN) High-Electron-Mobility Transistors (GaN HEMTs) and Silicon Carbide (SiC) based devices are identified as potential candidates for the mentioned application, featuring several improved characteristics over EMRs. On the contrary, other solutions, which seemed to be very promising, resulted to suffer from anomalous behaviors; i.e. SJ MOSFETs, and are thoroughly analysed from electro-thermal physical simulations at the device level.

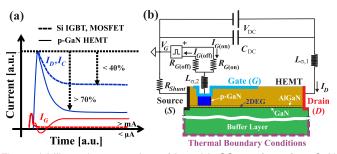

- Additionally, the SC capability of power semiconductor devices employed or with potential to be used in IH appliances is also analysed. On the one hand, conventional IGBTs SC behavior is evaluated under different test conditions so that to obtain the trade-off between ruggedness and a low power losses. Moreover, ruggedness and reliability of several normally-off 600-650 V GaN HEMTs are deeply investigated by experimentation and physics-based simulation.

- Finally, power losses calculation at die-level is performed for resonant power converters by means of using Infrared Lock-in Thermography (IR-LIT). This method assists to determine, at the die level, the power losses and current distribution in IGBTs used in resonant soft-switching power converters when functioning within or outside the Zero Voltage Switching (ZVS) condition. As a result, relevant information is obtained related to decreasing the power losses during commutation in the final application, and a thermal model is extracted for simulation purposes.

#### RESUMEN

Esta tesis tiene como objetivo fundamental la mejora de la flexibilidad, sostenibilidad, eficiencia y fiabilidad de las cocinas de inducción por medio de la utilización de dispositivos semiconductores de potencia:

- Dentro de este marco, existe una funcionalidad que presenta un amplio rango de mejora. Se trata de la función de multiplexación de potencia, la cual pretende resolverse de una manera más eficaz por medio de la sustitución de los comúnmente utilizados relés electromecánicos por dispositivos de estado sólido. De entre todas las posibles implementaciones, se ha identificado entre las más prometedoras a aquellas basadas en dispositivos de alta movilidad de electrones (HEMT) de Nitruro de Galio (GaN) y de aquellas basadas en Carburo de Silicio (SiC), pues presentan unas características muy superiores a los relés a los que se pretende sustituir. Por el contrario, otras soluciones que inicialmente parecían ser muy prometedoras, como los MOSFETs de Súper-Unión, han presentado una serie de comportamientos anómalos, que han sido estudiados minuciosamente por medio de simulaciones físicas a nivel de chip.

- Además, se analiza en distintas condiciones la capacidad en cortocircuito de dispositivos convencionalmente empleados en cocinas de inducción, como son los IGBTs, tratándose de encontrar el equilibrio entre un comportamiento robusto al tiempo que se mantienen bajas las pérdidas de potencia. Por otra parte, también se estudia la robustez y fiabilidad de varios GaN HEMT de 600-650 V tanto de forma experimental como por medio de simulaciones físicas.

- Finalmente se aborda el cálculo de las pérdidas de potencia en convertidores de potencia resonantes empleando técnicas de termografía infrarroja. Por medio de esta técnica no solo es posible medir de forma precisa las diferentes contribuciones de las pérdidas, sino que también es posible apreciar cómo se distribuye la corriente a nivel de chip cuando, por ejemplo, el componente opera en modo de conmutación dura. Como resultado, se obtiene información relevante relacionada con modos de fallo. Además, también ha sido aprovechar las caracterizaciones realizadas para obtener un modelo térmico de simulación.

#### **SUMMARY**

| 1:-+ -£ Al- | ala van dakta va                                                                 | 42   |

|-------------|----------------------------------------------------------------------------------|------|

| LIST OF AK  | obreviations                                                                     | 13   |

| Publicati   | ons Summary                                                                      | 15   |

| Chapter     | <ol> <li>Induction Cooking Systems General Overview and New Requireme</li> </ol> | nts  |

|             |                                                                                  |      |

| 1.1.        | Home Appliance Induction Cooking System Description                              | 19   |

| 1.2.        | Open Quests and Demands in Induction Cooking Systems: Flexibil                   | ity, |

| Sustainab   | ility, Efficiency and Reliability in Induction Cooking                           | 21   |

| 1.3.        | Flexibility in Induction Cooking                                                 | 23   |

| 1.3.        | 1 Limitations of Multiplexing Approach                                           | 23   |

| 1.3.        | 2 Power Multiplexing function for IH                                             | 24   |

| 1.3.        | 3 State-of-the-art in SSR                                                        | 26   |

| 1.4.        | Ruggedness and Reliability Studies of Power Semiconductor Devices                | 28   |

| 1.4.        | 1 Standard Reliability Tests at System Level                                     | 28   |

| 1.4.        | 2 Power Device Ruggedness against Overloading Stresses: SC Studies               | as   |

| a Test f    | or Overcurrent in IH                                                             | 29   |

| 1.4.        | Power Device Degradation due to Ageing: $T_j$ Monitoring                         | 30   |

| 1.5.        | Current Approaches for Efficiency Assessment in Induction Cook                   | ing  |

| Systems     | 33                                                                               |      |

| 1.5.        | 1 Power Losses Evaluation by Electrical Means                                    | 33   |

| 1.5.        | 2 Power Losses Evaluation by Calorimetry Means                                   | 34   |

| 1.6.        | Thesis Thematic Unit and Scope                                                   | 34   |

| Chapter     | 2: Thesis Objectives and Structure                                               | 36   |

| 2.1.        | Main Objectives                                                                  | 36   |

| 2.2.        | PhD Thesis structure:                                                            | 37   |

| Chanter     | 3. SSR RDS Implementations                                                       | 38   |

| 3.1               | L. (   | Objectives and PhD student's role                                          |

|-------------------|--------|----------------------------------------------------------------------------|

| 3.2               | 2. 9   | SSR Test Vehicles Design, Development and Characterization 39              |

| ;                 | 3.2.1  | Semiconductor Power Devices Selection for SSR                              |

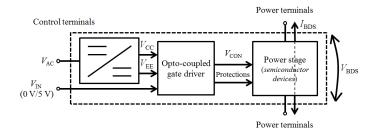

| :                 | 3.2.2  | SSR Test Vehicles Development                                              |

| 3.3               | 3. I   | Evaluation of Performances and Characteristics43                           |

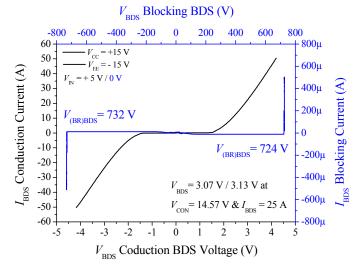

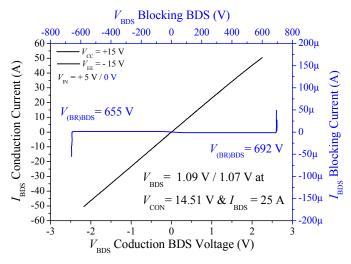

| :                 | 3.3.1  | Static Analyses and FOM Definition43                                       |

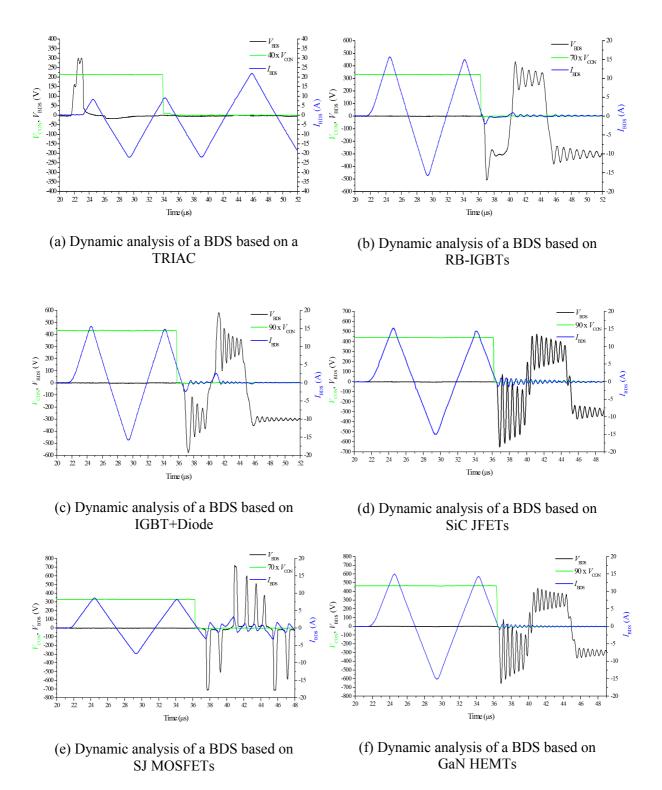

| :                 | 3.3.2  | Dynamic Analyses48                                                         |

| ;                 | 3.3.3  | Simulation of the Voltage Oscillations                                     |

| ;                 | 3.3.4  | SJ-based BDS Abnormal Behaviour                                            |

| 3.4               | 1. 1   | Functional Prototype and Final Application Test 54                         |

| 3.5               | 5. (   | Conclusions 55                                                             |

| Chap              | ter 4: | Ruggedness and Reliability Studies in Power Semiconductor Devices          |

| for IH            |        | 57                                                                         |

| 4.1               | L. (   | Objectives and PhD student's role57                                        |

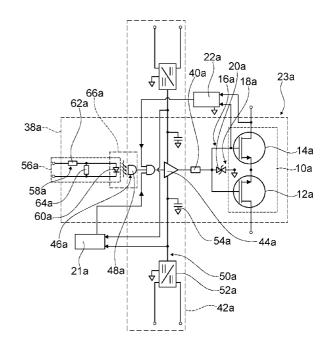

| 4.2               | 2. 9   | SC Test Platform Description58                                             |

| 4.3               | 3.     | Selected IGBTs, Test Conditions and Results59                              |

| 4.4               | 1. 9   | Selected GaN HEMTs, Tests Conditions, and Results63                        |

| 4.5               | 5. (   | Conclusions                                                                |

| Chap<br>Condition |        | $T_{\rm j}$ Extraction and Device Weak Spots Identification under Rea 67   |

| 5.1               | L. (   | Objectives and PhD Student's role 67                                       |

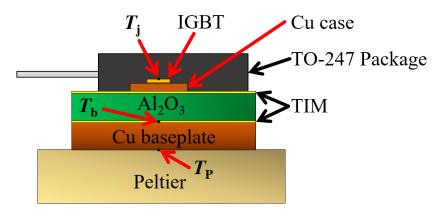

| 5.2               | 2.     | $T_{ m j}$ evaluation with an appropriate calculation of thermal losses 68 |

| !                 | 5.2.1  | Selected Devices                                                           |

| !                 | 5.2.2  | Test Setup Description I: Power Stage                                      |

| !                 | 5.2.3  | Test Setup Description II: Peltier Stage and IR Measurements 71            |

| !                 | 5.2.4  | CTM and Power Losses Extraction74                                          |

| 5.3.      | Conclusions                            | 76 |

|-----------|----------------------------------------|----|

| Chapter   | 6: General Conclusions and Future Work | 77 |

| 6.1.      | General Conclusions                    | 77 |

| 6.2.      | Future Work                            | 79 |

| Conclusi  | iones Generales                        | 82 |

| Reference | ces                                    | 86 |

| Publicati | ions                                   | 97 |

| Appendi   | ix                                     |    |

List of Abbreviations 13

#### LIST OF ABBREVIATIONS

**2DEG** Two-Dimensional Electron Gas

AUX Auxiliary switch

BDS Bidirectional Switch

BJT Bipolar Junction Transistor

CCD Charge-Coupled Device

**CMOS** Complementary Metal-Oxide-Semiconductor

CTM Compact Thermal Model

**DUT** Dual Flat No-lead Device Under Test

EMI Electro-Magnetic Interference

**EMR** Electromechanical Relay **FEM** Finite Element Methods

**FMT** Fluorescence Microthermography

FOM Figure Of Merit

FUL Fault Under Load

FWD Free Wheeling Diode

**GaN** Gallium Nitride

**HEMT** High-Electron-Mobility Transistor

**HSF** Hard Switch Fault

**IGBT** Insulated Gate Bipolar Transistor

IH Induction Heating

IR Infrared

JFET Junction Field-Effect Transistor

LCT Liquid Crystal Thermography

MDR Mercury Displacement Relays

Misro Floatro Mashanical Switcher

MEMS Micro-Electro-Mechanical Switches

MISHEMT Metal-Insulator-Semiconductor High-Electron-Mobility Transistor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

**NETD** Noise Equivalent Temperature Difference

PCB Printed Circuit Board

RB-IGBT Reverse-Blocking IGBT

RC-IGBT Reverse-Conduction IGBT

RFI Radio Frequency Interference

SAM Scanning Acoustic Microscope

SC Short-Circuit

SiC Silicon Carbide

SJ Super-Junction

SOA Safe Operating Area

SPDT Single-Pole, Double-Throw

SPICE Simulation Program with Integrated Circuits Emphasis

**SPST** Single-Pole, Single-Throw

14 List of Abbreviations

**SSR** Solid State Relay

TIM Thermal Interface Material

TRIAC Triode for Alternating Current

**TSEP** Thermo-Sensitive Electrical Parameter **TSEP** Thermo-Sensitive Electrical Parameter

**WBG** Wide-bandgap

**ZVS** Zero Voltage Switching

#### **PUBLICATIONS SUMMARY**

This work has been developed at the Instituto de Microelectrónica de Barcelona-Centro Nacional de Microelectrónica (IMB-CNM) of Consejo Superior de Investigaciones Científicas (CSIC), Bellaterra, Spain, under a partnership with BSH Electrodomésticos España.

It is focused on power semiconductor device solutions and die-level investigations for a more flexible, sustainable, efficient and reliable induction cooking. The development of these contents is distributed in three main sections: the first one concerns a deep analysis and implementation of multiple Solid-State Relay (SSR) solutions based on advanced power semiconductor devices. The second one is focused on the ruggedness and reliability for both currently used and future power semiconductor devices. Finally, the extraction of Insulated Gate Bipolar Transistors (IGBTs) junction temperature ( $T_i$ ) and the identification of their potential weak spots using innovative infrared (IR) techniques is evaluated in the last section.

The different approaches performed to each of the mentioned subjects have found academic recognition along the doctoral research period, and are summarized in this manuscript into a compendium of the following journal and conference publications, and a patent:

- 1. Development of compact SSR based on advanced power semiconductor devices:

- a. Journal Publication

- [1] M. Fernández, X. Perpiñà, J. Rebollo, M. Vellvehi, D. Sánchez, T. Cabeza, S. Llorente, and X. Jordà, "Solid State Relay Solutions for Induction Cooking Applications based on Advanced Power Semiconductor Devices," *IEEE Transactions on Industrial Electronics*. doi: 10.1109/TIE.2018.2838093. (In press).

URL: https://ieeexplore.ieee.org/document/8365104/

- Journal: IEEE Transactions on Industrial Electronics.

- Status: In press (available online).

- Impact Factor: 7.050.

#### Categories:

- Automation & Control Systems Q1 2/61.

- Engineering, Electrical & Electronic Q1 13/260.

- o Instruments & Instrumentation Q1 1/61.

#### b. Conference Publications

[2] M. Fernández, X. Perpiñà, M. Vellvehi, X. Jordà, T. Cabeza, and S. Llorente, "Analysis of solid state relay solutions based on different semiconductor technologies," in *Proc. European Conference on Power Electronics and Applications* (EPE), Warsaw, Sept. 2017, pp. P.1-P.9, doi: 10.23919/EPE17ECCEEurope.2017.8099012.

URL: <a href="https://ieeexplore.ieee.org/document/8099012/">https://ieeexplore.ieee.org/document/8099012/</a>

[3] M. Fernández, X. Perpiñà, M. Vellvehi, D. Sánchez, X. Jordà, J. Millán, T. Cabeza and, S. Llorente, "Analysis of bidirectional switch solutions based on different power devices," in *Proc. Spanish Conference on Electron Devices* (CDE), Barcelona, Feb. 2017, pp. 1-4, doi: 10.1109/CDE.2017.7905220.

URL: <a href="https://ieeexplore.ieee.org/document/7905220/">https://ieeexplore.ieee.org/document/7905220/</a>

#### c. In Writing Process

[4] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, S. Llorente, and X. Jordà, "Feedback Oscillations in Super-Junction MOSFET-based Solid State Relays," *IEEE Transactions on Power Electronics* (In writing process).

#### d. Patent

[5] T. Cabeza, M. Fernández, X. Jordà, S. Llorente, I. Millán, X. Perpiñà, D. Sánchez, and M. Vellvehi, "Dispositivo de aparato doméstico", Application number: P201631613 (19.12.2016), Publication number: ES2673129 A1 (19.06.2018).

- [6] T. Cabeza, M. Fernández, X. Jordà, S. Llorente, I. Millán, X. Perpiñà, D. Sánchez, and M. Vellvehi, "Haushaltsgerätevorrichtung", Application number: DE201710222394 (11-12-2017), Priority number: ES20160031613 (19.12.2016).

- 2. Ruggedness and reliability studies of several power semiconductor devices:

- a. Journal Publications

- [7] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, X. Jordà, and M. Tack, "P-GaN HEMTs Drain and Gate Current Analysis Under Short-Circuit," *IEEE Electron Device Letters*, vol. 38, no. 4, pp. 505-508, April 2017, doi: 10.1109/LED.2017.2665163.

URL: https://ieeexplore.ieee.org/document/7845577/

- Journal: IEEE Electron Device Letters.

- Impact Factor: 3.433.

- Categories:

- o Engineering, Electrical & Electronic Q1 53/260.

- [8] M. Fernández, X. Perpiñà, J. Roig, M. Vellvehi, F. Bauwens, M. Tack, and X. Jordà, "Short-Circuit Study in Medium-Voltage GaN Cascodes, p-GaN HEMTs, and GaN MISHEMTs," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 9012-9022, Nov. 2017, doi: 10.1109/TIE.2017.2719599.

URL: https://ieeexplore.ieee.org/document/7956198/

- Journal: IEEE Transactions on Industrial Electronics.

- Impact Factor: 7.050.

- Categories:

- Automation & Control Systems Q1 2/61.

- Engineering, Electrical & Electronic Q1 13/260.

- Instruments & Instrumentation Q1 1/61.

- b. Conference Publication

[9] M. Fernández, X. Perpiñà, M. Vellvehi, X. Jordà, J. Roig, F. Bauwens and M. Tack, "Short-circuit capability in p-GaN HEMTs and GaN MISHEMTs," in *Proc. International Symposium on Power* Semiconductor Devices and ICs (ISPSD), Sapporo, May 2017, pp. 455-458. doi: 10.23919/ISPSD.2017.7988916.

URL: <a href="https://ieeexplore.ieee.org/document/7988916/">https://ieeexplore.ieee.org/document/7988916/</a>

- 3. Junction temperature extraction and device weak spots identification under real conditions:

- a. In Writing Process

- [10] M. Fernández, M. Vellvehi, X. Jordà, and Xavier Perpiñà, "Power Losses and Current Distribution Extraction in IGBTs under Resonant Load and ZVS Condition," *IEEE Transactions on Power Electronics*. (In writing process).

## Chapter 1: INDUCTION COOKING SYSTEMS GENERAL OVERVIEW AND NEW REQUIREMENTS

#### 1.1. Home Appliance Induction Cooking System Description

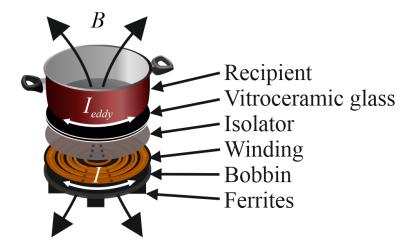

Induction cookers make use of the electromagnetic induction process (Faraday, 1831) to generate heat directly inside the base of electrically conducting cookware by means of Foucalt/eddy currents ( $I_{\rm eddy}$ ) combined with energy dissipation by the Joule effect and ferromagnetic hysteresis. Thanks to this process, the energy transfer efficiency is improved since any of the intermediate layers between the inductor and the recipient needs to be heated up. In order to reach the mentioned  $I_{\rm eddy}$  at the vessel, alternating electromagnetic fields (B) are generated at the power inductor, where high frequency currents (I) are involved. These layers are depicted in Fig. 1.1-1.

Fig. 1.1-1. Inductor-vessel system.

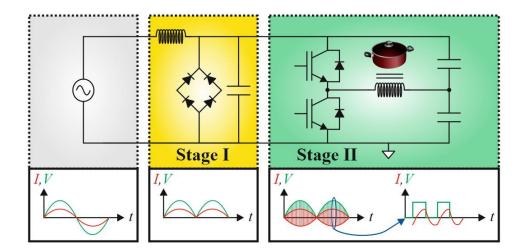

In this framework, the energy transfer from mains to the induction coils involves a two-stage power conversion which can be outlined as follows [11][12]:

- First, mains AC voltage is filtered and then rectified by a diode bridge.

- Resulting DC bus voltage ( $V_{BUS}$ ) is connected to resonant switching inverters to supply the high-frequency current to the power inductors.

The most commonly used circuit topologies for Induction Heating (IH) applications are the half-bridge, full-bridge and single switch inverter topologies [13]. From all of

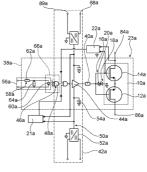

Fig. 1.1-2. Block diagram of an IH application, based on a half-bridge topology.

them, the half-bridge inverter is the most extended one, owing to its higher robustness and favourable balance among simplicity and performance above full-bridge and single switch based topologies [12][13]. However, despite their lower efficiency and most demanding requirements for the power switches, single-ended quasi-resonant topologies are also extensively used due to their lower complexity and subsequent costs [13]. Fig. 1.1-2 depicts the blocks diagram of the mentioned power stages, exemplified for a half-bridge power inverter.

Concerning their implementation, power inverters for IH are based on IGBTs as main semiconductor devices, which are positioned as cost-effective solutions due to their high-frequency and high-current capabilities, while ensuring sufficiently low power losses and an adequate thermal performance. Nowadays, IGBT trench field stop technology is widespread since it allows to reach some of the lowest power losses. However, the application of IGBTs to resonant inverters implies the integration of additional freewheeling diodes. In this sense, each manufacturer provides its own solution, where the IGBT can be either co-packaged together with an optimized diode or integrated monolithically with the diode (Reverse-Conducting IGBT (RC-IGBT)). The latter approach involves reduced costs for the manufacturers in terms of test, assembly [14] and a slightly reduced chip size for the same active area, as one of the edge regions is removed [15]; at the cost of worsened reverse recovery diode characteristics [16], which makes RC-IGBTs only suitable for soft-switching applications [17], i.e. induction cookers. Therefore, it becomes essential using snubber capacitances to reduce the

device turn-off switching losses. Moreover, operating under Zero Voltage Switching (ZVS) condition will also contribute to have reduced turn-on switching losses by commutating the IGBT during the diode conduction window.

## 1.2. Open Quests and Demands in Induction Cooking Systems: Flexibility, Sustainability, Efficiency and Reliability in Induction Cooking

One of the major concerns of IH appliances manufacturers is to improve the user experience by extending the flexibility of the cooking zones. Based on this concept, highend market segment products have evolved towards solutions without serigraphy, where the user may distribute the cookware of whatever size or shape all along the cooktop and at whatever position (two dimensions flexibility). This solution is conventionally realized from large number of inductors which can be connected and disconnected from several power inverters, and a high resolution pot detection system, which in combination with control techniques allows the implementation of different functions to increase the feeling of flexibility.

A different approach considers the division of the cooktop into different heating zones where varied size and shape cookware can be arranged with a lower resolution and one dimension flexibility. Usually, these zones are combined with ring or combi induction zones, constituting the value-added market segment together with conventional ring induction cooktops, where each cooking zone is assigned to a single inverter that can be enabled or disabled to the rectifying stage. Fig. 1.2-1 (a)-(b) illustrates an example of high-end and value-added oriented products, respectively.

Fig. 1.2-1. Cooktop flexibility examples oriented to (a) high-end and (b) value-added market segments (one dimension flexibility cooktop combined with ring cooking zones).

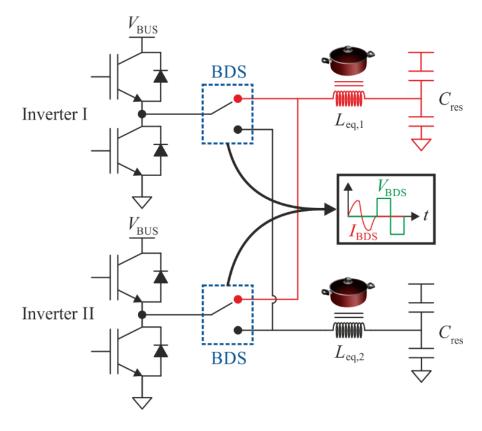

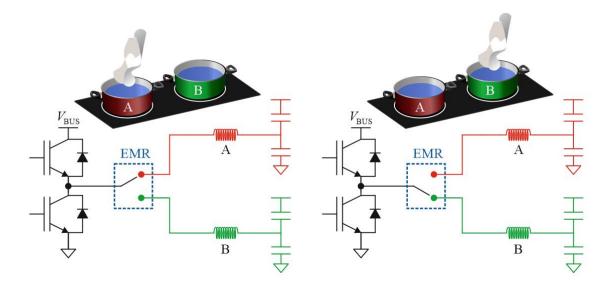

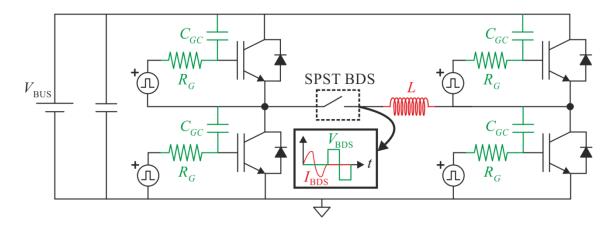

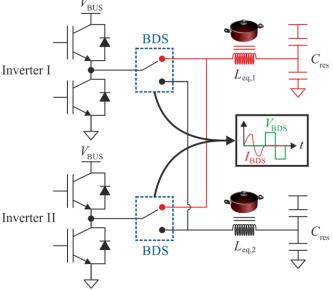

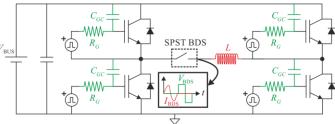

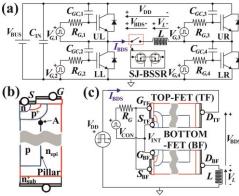

In addition, a more energy-efficient and low cost appliance can be attained from the power multiplexing of different loads [18][19]. A simplified schematic of this method is presented in Fig. 1.2-2. It is based on using several switches which permit a time-commutated connection (bidirectional current conduction flow,  $I_{BDS}$ ) and disconnection (bidirectional voltage blocking,  $V_{BDS}$ ) of the induction coils ( $L_{eq,1}$ ,  $L_{eq,2}$ , ...), in resonance with capacitor banks ( $C_{res}$ ), to any of the available power inverters. Also, they provide the inverters parallel operation, leading to a relevant cost reduction of the over-all system. Thereby, this platform constitutes the entry market segment.

Accordingly, one of the key elements for improving the flexibility and efficiency at all IH platforms is the electromechanical relay (EMR). However, it presents a set of drawbacks when it concerns to providing flexibility through the power multiplexing function. This constitutes an open demand that can be addressed from power semiconductor devices based designs.

Another concern of IH cooking systems is to reduce the power losses at the inverter, since it is one of the first elements to restrict the appliance performance. Currently, one solution to reduce the conduction losses of insulated gate semiconductor devices for power converters mainly consists of triggering them at gate voltages higher than the nominal ones, resulting in increased charge densities at the channel and lower on-state resistance [20]. However, increasing their gate control input voltages close to the maximum allowed may lead to reduced ruggedness and reliability and, the gate dielectric being the most affected part. In this sense, an adequate characterization of the semiconductor devices to fully exploit their potential will be beneficial for improving the efficiency, leading towards a higher sustainability for home appliances. In addition, a thorough evaluation of device power losses at die-level will provide useful information concerning the effect of different driving concepts, such as the operation outside ZVS condition or the use of capacitive snubbers. Furthermore, by extending this analysis to a die-level, it will also be possible to identify the devices weak spots, acting as a failure precursor.

Moreover, due to the higher complexity of modern appliances, under certain circumstances of varying origin, the power devices can be subjected to high voltage and current stress. Consequently, analysing their behaviour under such faulty conditions

Fig. 1.2-2. Simplified schematic of an IH system using the power multiplexing function. Figure extracted from [1].

becomes crucial to determine their ruggedness and reliability. Every year a certain percentage of total production of induction cooktops is scrapped, which adds to those ending their useful life. These facts provoke a significant environmental impact. In this sense, home appliances industrial manufacturers aim at reducing their failure rate and extending their products lifetime above 10 years, always taking into account that these appliances must provide uniform performances for a domestic use (limited hours per day). In this field, the contribution of power semiconductor devices is linked to an improved ruggedness.

#### 1.3. Flexibility in Induction Cooking

#### 1.3.1 Limitations of Multiplexing Approach

One of the main benefits of EMRs is a very low on-state resistance, in the range of 5-10 m $\Omega$ . In addition, the EMR producers invest large amounts on developing the manufacturing technology for fabricating these components into high volumes,

constituting the most widespread and lowest cost solution for the commutation of power sub-circuit blocks.

However, their application to power multiplexing evidences a set of limitations which are summarized below:

- They present moving parts, which are susceptible to wear and be affected by vibration or physical shock, with a consequent short service life.

- In addition, they present electric arcs during commutation, with a resulting risk of terminals welding.

- They are commonly packaged using plastic cases, which will not provide enough protection (hermeticity) against external pollutants.

- They produce acoustical noise when contacts are switched.

- They present large electromagnetic interferences.

- High inrush current and input power consumption.

- Very slow response (in the order of ms), thereby limiting the multiplexing rate.

- Large size and weight.

#### 1.3.2 Power Multiplexing function for IH

For the specific case of IH appliances, some of the above-mentioned limitations remain unacceptable. Therefore, an EMR-based power multiplexing function involves additional restrictions.

The inverter power devices specification for the studied application usually considers voltage and current ratings of 600-650 V and 30-40 A at 100 °C. However, conventionally used EMR might consider AC voltage and current ratings of 300-400 V and 16-30 A at 100 °C as it is established by the automotive industry. Depending on the IH platform and operating modes, many elements can be responsible for the application of a power regulation caused by overtemperature: the inductors, the inverter power devices (usually IGBTs) or even the EMR. In the scenario of a power multiplexing platform, the EMR is the receiver of the highest thermal loads. Unfortunately, the higher sizes for the next current steps leads to a trade-off against a solution based on two parallelized EMR, together with the consequent costs increase. Therefore, the EMR current rating constrains the maximum supplied power, which would require a multiple

Fig. 1.3-1. Water boiling effect.

inverters parallelization.

Consequently, arcing under such current/voltage conditions need to be avoided to prevent the terminals welding. This can be achieved by turning-off the inverter prior to the EMR commutation for a specified transition time, which unfortunately highlights a significant dispersion. Once the EMR has been detected to have finished its movement, the inverter is, again, switched on. Moreover, the inverters deactivations/activations have to be performed by ramping the inverters frequency to prevent the high magnetic field from inducing additional noise at the recipient.

A direct consequence of such a low multiplexing rate occurs when a single EMR is time-multiplexed for liquid boiling at multiple loads for recipients with a low thermal inertia and for which a high sum power is selected. As a result, water boiling can intermittently stop and might give a misleading impression of a performance loss event (Fig. 1.3-1), unless multiplexing of different inverters with no involved EMR commutation is possible. Also, increasing the multiplexing rate will reduce the EMR service time. Furthermore, the EMR acoustical noise under multiplexing conditions is quite high. In this context, efforts are being made in the industry to reduce this nuisance for the final user [21].

Since most of these drawbacks can be downsized or removed by power semiconductor devices based SSR design, one of the research targets of this PhD is investigating possible replacing solutions based on them.

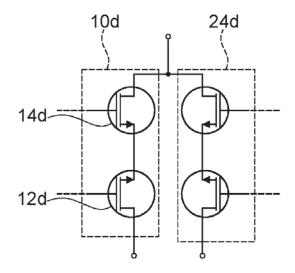

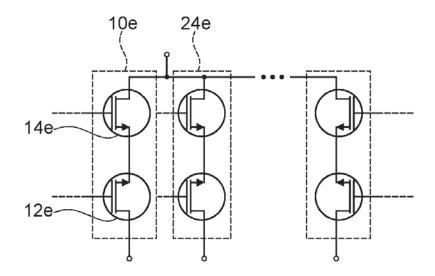

For the specific case of the power multiplexing function, this method can be implemented using SPDT (Single-Pole, Double-Throw) bidirectional switches (BDS), as shown by Fig. 1.2-2. However, this work focuses on analyzing different static implementations of the Single-Pole, Single-Throw (SPST) BDS switching function as the main step for SPDT implementation, so that all results stemming from this study can be extended to the mentioned SPDT relay.

#### 1.3.3 State-of-the-art in SSR

First, an exhaustive research resulted into a complete state-of-the-art where any existing and emerging technological options to implement the mentioned relay or power multiplexer function in the framework of the IH applications was identified. The main objective of this analysis is to get data from each technology and make a quantitative comparative study, so that a set of potential possible alternatives to EMRs are selected for deeper study. Besides the EMRs, five technological families are identified:

- 1) Dry reed relays: these relays can commutate faster than EMRs with a lower input power consumption. In addition, they highlight a longer service life. However, they present a higher contact resistance and due to their smaller contacts, they are limited to low currents, in the range of 2-3 A [22].

- 2) Mercury Displacement Relays (MDR): which can be categorized as a type of reed relays [23]. MDRs combine the absence of mobile contacts, as a relevant advantage over EMRs, and the lack of heatsinks, as a relevant advantage over SSRs [24]. However, they are not suitable for a high-frequency operation and became obsolete due to the mercury toxicity.

- 3) Micro-Electro-Mechanical Switches (MEMS): whose main switch element is a freestanding mechanical cantilever. This technology is conventionally used for low power; however, the parallel connection of multiple MEMS arrays has been demonstrated to resist more than 300 V, with low on-state resistances, in the range of 100 m $\Omega$ , and with a fast arc-free switching speed, in the  $\mu$ s range [25]. Unfortunately, this solution presents a very low current-carrying capability, around 5 A, and very high-voltage driving requirements, around 80 V. This technology is

presently under development and therefore it is expected a future improvement of its performance.

- 4) Standard SSR solutions: which make use of power semiconductor devices for realizing the BDS function. This type of switches is industrially available with both control and power stages integrated into single parts. Concerning their output stages, they are conventionally Thyristor or Triode for Alternating Current (TRIAC) based for AC loads and Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) based for AC/DC loads [26]. Notwithstanding, the first ones are only spread for AC applications at mains frequency, in the range of 0 to 1.5 kV. As a consequence, they are not suitable for the high-frequency operating currents involved in the studied framework. Alternatively, SSR solutions based on new power semiconductor device technologies will be deeply evaluated in the next chapters.

- 5) Specific hybrid solutions, based on different combinations of semiconductor power devices or even with EMR, i.e. an EMR parallelized with a TRIAC based SSR, where a control circuit first switches on the SSR, so that to handle the load inrush current, and then the EMR, at no load, to handle the corresponding load current [24].

All technological options have been categorized in view of their conduction and switching power losses, switching speeds, driving needs, isolation, input power consumptions, controllability, service life, typical failure state, size, weight, existence of arcs, magnetic interaction, noise and EMI, presence of mechanical/moving parts, environment (vibration, shock, altitude, position, interaction) and comparative costs.

From the characteristics of each technology, it is concluded that the only practical solution for the induction cooking application is based on the use of advanced SSRs, since any of the other technological families will find a technical advantage [1]. For that reason, this thesis performs, for the first time, an exhaustive comparison among the electric and electronic options available to implement the BDS function for EMR replacement based on power device assemblies, analyzing their pros and cons and including emerging technologies such as Wide-bandgap (WBG) power devices. In addition, a Figure Of Merit (FOM) is proposed to extend the comparison from specific

device references to the different device technologies. These topics are developed in Chapter 3.

### 1.4. Ruggedness and Reliability Studies of Power Semiconductor Devices

#### 1.4.1 Standard Reliability Tests at System Level

Short-Circuit (SC) protection is not usual at IH appliances, since the power inductors are electrically isolated for high temperatures and from the heated recipient. Therefore, the possibility of a complete inductor SC is reduced.

As a consequence, the performed endurance tests mainly consist of the development of accelerated aging tests.

However, since novel inverter topologies are becoming more complex, the risk for a SC event is increased. Some examples are:

- Welding of EMR contacts at multiplexed topologies.

- Erratic driving strategy, resulting either into too short dead times or high frequency modulation at no load.

In addition, despite it is not a SC event, the use of an Aluminum recipient for the same maximum load power than for a non-ferromagnetic recipient results into many times higher currents flowing through the inverter devices [27].

Also, similar unlikely failure modes may occur leading to a SC event as for any other industrial application, i.e. faulty gate control signals, defective collector-emitter or gate-emitter overvoltage protections, etc.

Each of the mentioned scenarios result into completely different SC current profiles and electric signatures which might not be possible to identify during aging tests. Therefore, a ruggedness failure analysis is proposed in the next section.

Moreover, apart from studying how a specific power device technology would reach destruction, it becomes also very important to identify precursor parameters which can reveal how the device might be degraded under certain operating conditions, in order

to have an estimation of its expected service life. In this sense, the use of junction temperature  $(T_i)$  monitoring as a lifetime indicator is also presented.

### 1.4.2 Power Device Ruggedness against Overloading Stresses: SC Studies as a Test for Overcurrent in IH

In general, electro-thermal overloading stresses result from abnormal working conditions or events, in which the device is set outside its Safe Operating Area (SOA). They can be categorized into overvoltage, overcurrent and overtemperature. Another abnormal event is that originated from an electrical SC during the regular operation of the device; where the switch withstands the whole  $V_{\rm BUS}$ , while conducts current. As a result, the power device can reach destruction [28][29]. This occurs within the die, starts from a local electro-thermal phenomenon (high temperature and current levels reached locally) at very short timescales (ns-us range). Sometimes, the origin of such catastrophic phenomena is unknown, is non-repetitive, and depends on the device layout or its inherent structure (weak spots) [30]. All such abnormal events (i.e., SC, overcurrent, or overvoltage) can come from dysfunctions on the driving process, [28][31][32] environmental conditions or load variations [33]; thus compromising the reliability of the power system. From a final user point of view, a first approach to face such abnormal events is the use of ruggedness tests to select the devices, which can overcome such stressful conditions. Jointly with endurance tests, this helps to enhance the converter reliability. Moreover, from the electrical failure signature, a more complex solution involving the driver circuit can be performed. The driver constantly surveils any failure indicator occurrence, prepared for actuating to avoid the power device destruction. Unfortunately, such ruggedness tests (also known as test at limit) have been designed by power devices manufacturers and not always are representative of the final application.

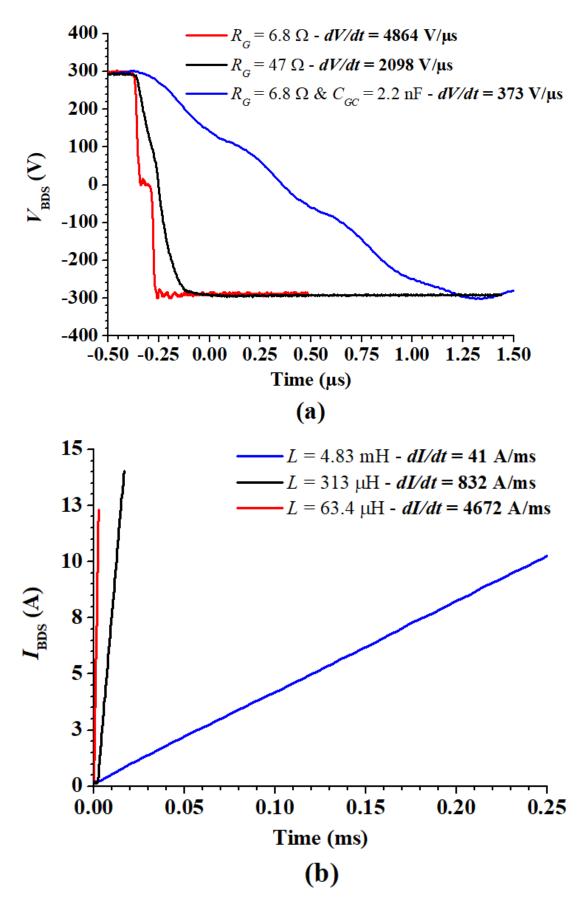

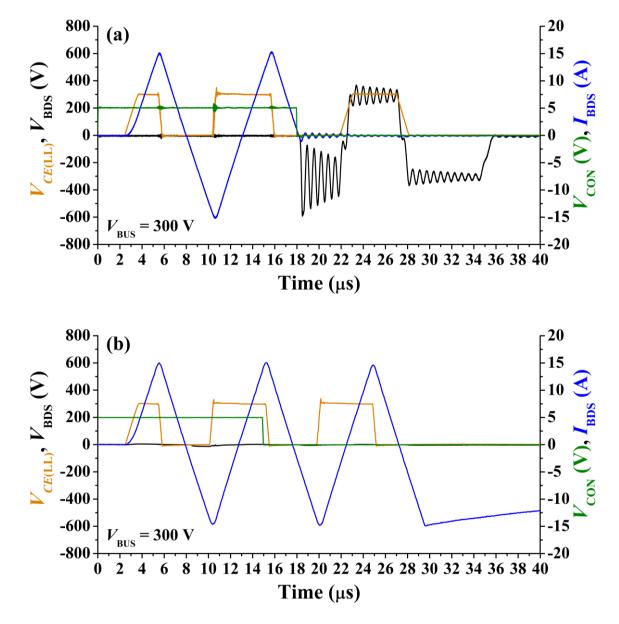

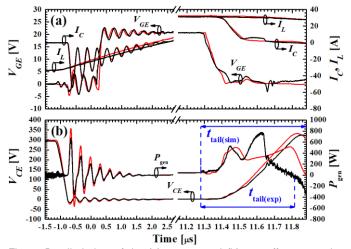

In the case of IH applications, SC test is some of the closer one to replicate the situation of an overcurrent event due to the snubber discharge when the maximum current is passing through the device, especially as a consequence of losing ZVS condition. In fact, X. Perpiñà et al. determined in [34] that a modified SC tests could be a good approach to replicate this and useful for the selection of more rugged power

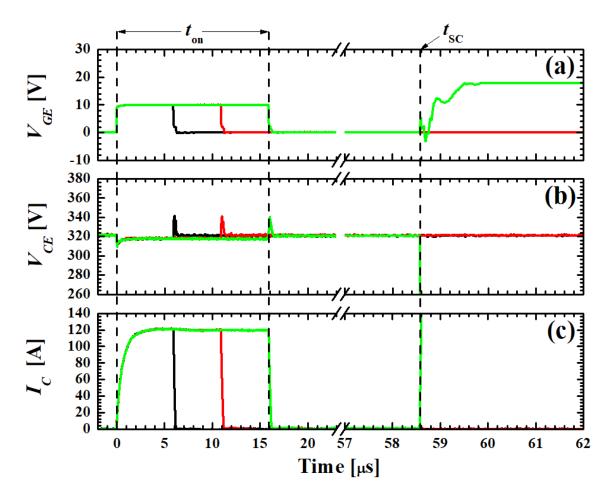

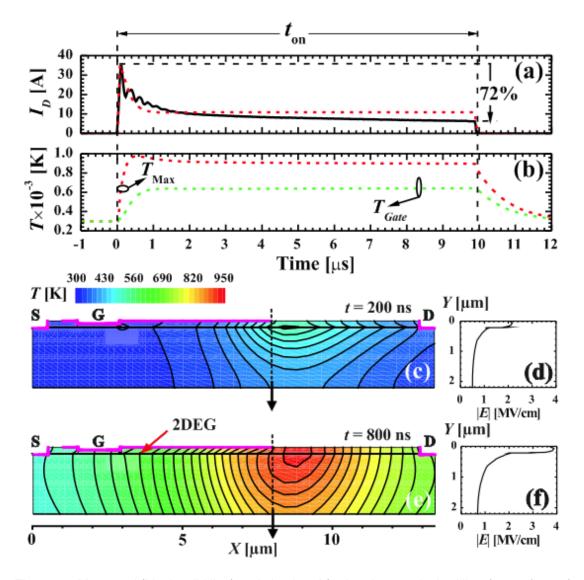

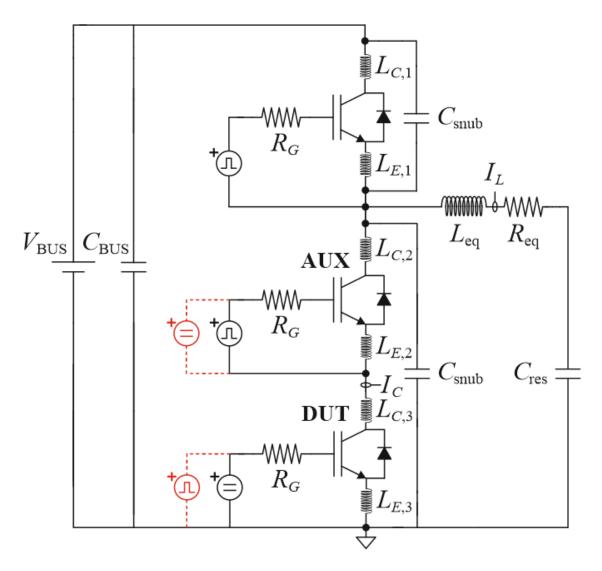

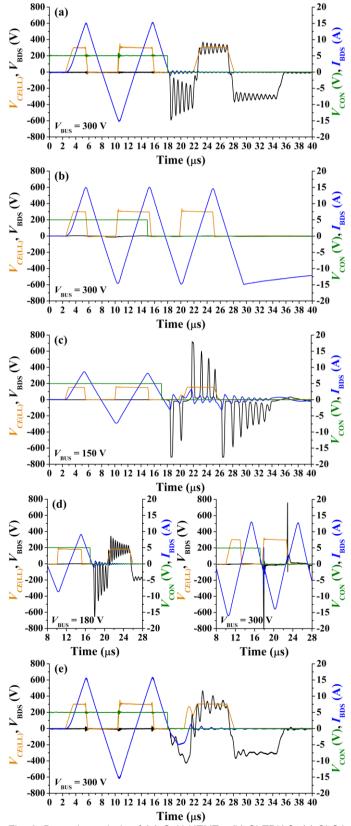

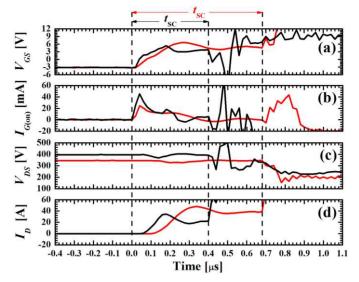

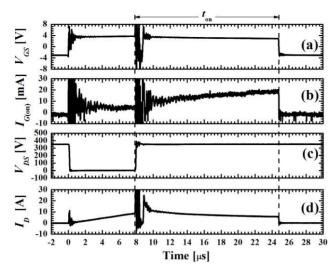

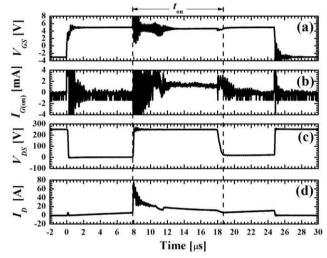

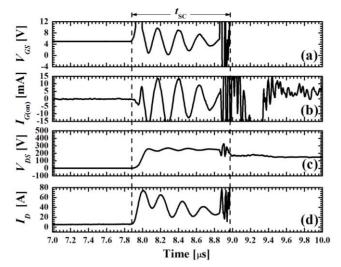

semiconductor devices. This work suggests that setting gate-emitter voltages ( $V_{GE}$ ) at 10 V under a SC condition reproduces the situation typical of an overcurrent event due to the snubber discharge when the maximum current is passing through the device as a consequence of losing ZVS. Moreover, it has already been demonstrated that the limits of Trench IGBT for medium voltage applications devices are mainly thermal under SC events [35][36]. This is supported by its thin drift region. This situation is going to worsen as IGBTs manufacturing trends target at thinner dies and smaller cell pitch [20]. This increases the power density generated within them under operating conditions. Traditionally, another purpose of SC tests is to evaluate if, for a given  $V_{\text{BUS}}$ , the SC withstand time ( $t_{\text{on}}$ ) is long enough so that the SC condition can be detected by a controller or driver, and safely interrupted by switching-off the tested device with no electrical damage for the power converter [37]. According to the available drivers, the fault detection time is conservatively estimated to be below 6 µs [38].

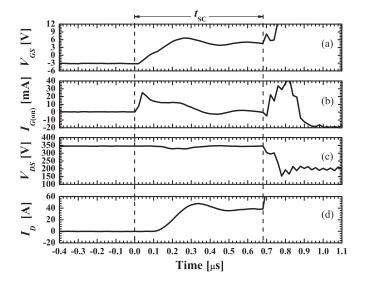

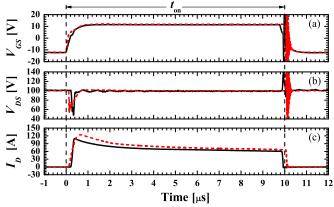

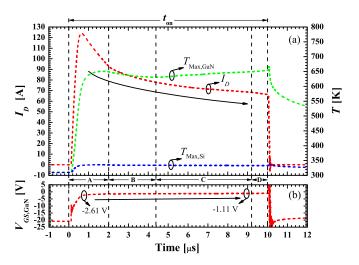

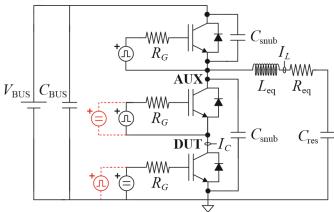

To provide more details in this sense, the aim of SC test is to reproduce a SC fault in the converter, which must be withstood by the device without destruction or degradation, and/or detected by its driver to turn it off safely. The Hard Switch Fault test (HSF, SC I) is the most commonly used by power device manufacturers [39], despite being less demanding for the device than Fault Under Load test (FUL, SC II). Under a SC I condition, the Device Under Test (DUT) is gated on into a faulty event, while under SC II, the device is on-state when SC fault occurs. Consequently, SC current flows through it while withstanding  $V_{\text{BUS}}$ , eventually giving rise to its destruction in a certain time to failure ( $t_{\text{SC}}$ ). For a given  $V_{\text{BUS}}$ , this test aims at evaluating whether the SC time duration is long enough to detect the SC condition with a controller or driver, and safely switch the device off without any converter electrical failure [40]. This situation can be envisaged more stressful in IH due to the devices gate control. As a consequence of the higher involved  $V_{GE}$ , the devices SC current is higher, and therefore  $t_{\text{SC}}$  is reduced. In this topic, passing SC I tests becomes essential prior to integrating the devices in the studied application.

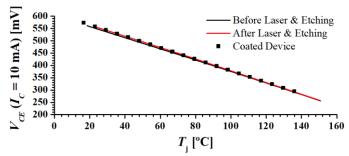

#### 1.4.3 Power Device Degradation due to Ageing: $T_i$ Monitoring

As Arrhenius law dictates, the material properties of the different parts of the power converter evolve and change along endurance tests according to their operation

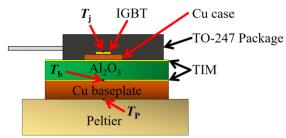

temperature. As a consequence, the power semiconductor devices performance can degrade. Thus, the role of temperature as an acceleration factor is critical in IH, as the cooktops are always mounted on top of ovens and their worst working scenario contemplates both under operation. This forces the switches to operate at temperatures near to their limit (150 °C) or higher enough to fasten their ageing. For this reason, investigation efforts in last years have been focused on reducing the power losses in power devices, as performed, e.g., with soft-switching strategies under ZVS condition. For all these reasons, temperature is a parameter susceptible of being monitored not only during its thermal design, but also in the final cooktop. Unfortunately, measuring  $T_j$  in power devices is not a common practice in such systems. Usually, this is estimated by means of circuit level simulations thanks to the electrothermal compact models of the device jointly with its dissipation system. Moreover, there is also a lack of commercial systems which allows locally monitoring  $T_j$  within commercially available power devices. Therefore, two clear needs have been identified:

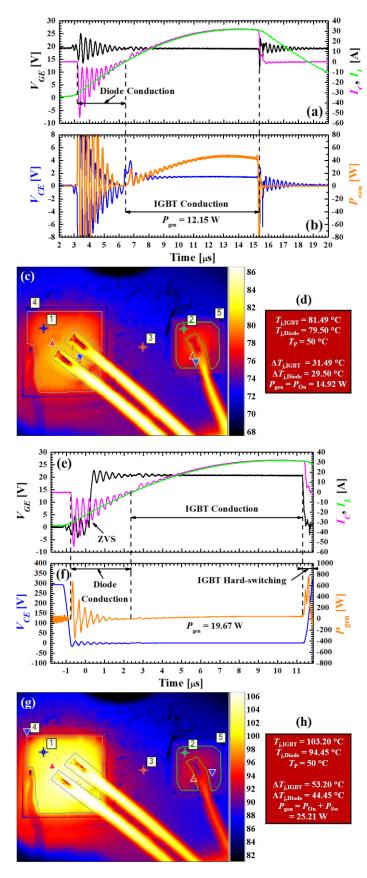

- The measurement of the average T<sub>j</sub> is crucial to maintaining the device operating temperature below a maximum value, aiding and assessing the thermal management design of the power converter. However, with a heat dissipation system, it is not possible to control local temperature rises due to electrothermal coupling.

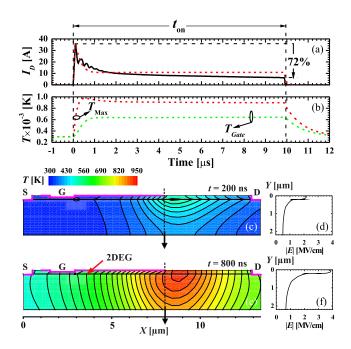

- Within the device itself, local temperature can reveal structural weak spots or current crowding problems, as current density extremely increases. This is linked with the local electro-thermal aspects stated in 1.4.2. Due to the local high dissipation in such processes, burnout failures or die cracking can induce the device failure, leaving some signatures interesting to be located for the die posterior analysis. In fact, to better withstand such high stress conditions, power devices are being designed with improved local electro-thermal behaviour, by performing accurate simulations. Nonetheless, the simulation of their thermal failure phenomena requires transient temperature-field data for verification and improvement of the model parameters used.

For a long time, thermometry in power devices has been based on the use of Thermo-Sensitive Electrical Parameters (TSEP) [41]. The most used TSEP in power electronics is the voltage drop of a PN junction forward biased by a low current level, since all power devices contain inherent PN junctions inside them. Apart from the voltage drop in the PN junction of a power diode, some examples are the voltage drop between collector-emitter terminals of a bipolar or IGBT in saturation regime. Other TSEP very used in MOS-controlled power devices is the threshold voltage. Despite the threshold voltage is less linear and sensitive than the forward biased PN junction; it allows an extraction of a maximum operation temperature much more precise and accurate depending on the operation regimes of the DUT, e.g., SC for IGBTs [42]. As major advantages of the TSEPs use, temperature measurements can be performed on fully packaged devices with little or no modification, directly measuring the temperature within the device. However, an average value of device temperature is obtained, because of the calibration experimental conditions [43][44]. This calibration is performed measuring the desired TSEP once the whole device is just heated and stabilized to a given steady-state temperature.

In contrast to this, other techniques have appeared to allow local monitoring at dielevel. Basically, they may be categorized in laser probing or surface thermal imaging techniques [45]. The former consists in using as a probe a laser beam, where the thermosensitive magnitudes are its power, propagation direction, or phase. Thus, according to the monitored beam characteristic, internal infrared (IR)-Laser Deflection (beam deflection) and interferometric (phase shift) thermometry are distinguished. However, sometimes they require an extra step for DUT conditioning before the measurement and their use is restricted in laboratory environments as integrating them in a real working scenario is very difficult. As for surface thermal imaging techniques, they determine the temperature distribution on the die top surface by means of a Charge-Coupled Device (CCD) camera. This process may be performed by either directly measuring the radiated heat flux with an IR camera (IR thermography) [46] or previously depositing a thermo-sensitive film on the inspected surface as Liquid Crystal Thermography (LCT) or Fluorescence Microthermography (FMT). As a result, an image containing the die surface thermal mapping is recorded with a camera. All these techniques are very useful for hot spot determination especially when lock-in strategies are used [47]. With this approach, the thermographic system signal-to-noise ratio is

extremely increased, while the spatial resolution of hot spots is improved by frequency modulation. This allows determining the locations where the failure or any current crowding occur.

# 1.5. Current Approaches for Efficiency Assessment in Induction Cooking Systems

#### 1.5.1 Power Losses Evaluation by Electrical Means

The electrical measurement [48]-[53] uses the product of voltage and current, which gives an electrical quantity equivalent to power. Power measurement can be performed by measuring the voltage drop across the device and the current flowing through it using electrical instruments. In DC and low-frequency AC circuits, it is common to measure power directly by using analog electronic equipment: voltmeters for voltage measurements and ammeters for current measurements, or a combined measurement using a wattmeter. However, for high-frequency signal and highly distorted signals, such as pulse width modulation, conventional meters are no longer suitable because of their limited bandwidth and dynamic frequency response. Digital instruments have gained popularity for obtaining the required resolution. This kind of digital meter takes simultaneous samplings of voltage and current waveforms, digitizes these values, and provides arithmetic multiplication and averaging using digital techniques to obtain a power measurement. An appealing advantage of the electrical methods is that they are easy to perform and to reproduce a measurement. It is suitable for steady state as well as transient measurements. However, high dI/dt and dV/dt introduce serious Radio Frequency Interference/Electro-Magnetic Interference (RFI/EMI) problems since digital instruments are very sensitive to noise. The accuracy of digital measurement is also affected by the delays introduced between probes, phase shifts between sampling channels of digitizer, sampling errors, and nonlinearities of analog-to-digital converter. No instrument known to man can accurately record the hard-switched output voltage waveforms when dV/dt is very high [54].

To date, the most common methods of determining power loss have been the conventional input-output procedure by taking the difference between the measured

input and output power. From the basic definition of losses, this is a natural choice. There is always considerable error associated with the subtraction of two nearly equal numbers for high-efficiency system, whichever method is used to measure input and output power.

#### 1.5.2 Power Losses Evaluation by Calorimetry Means

In theory, higher accuracy is possible by measuring loss directly. Since the total power losses dissipate as heat, the effect caused by the heat can be measured to determine the losses. This can be achieved by calorimetric methods. Consequently, calorimetric method based on direct loss measurement provides a more accurate measurement technique. Calorimetric methods have been widely used in power electronics to measure the power losses of magnetic components [55]-[59], capacitors [60], switching semiconductors [61][62], power converters [63], and electrical machines [63]-[72]. Consequently, the calorimetric principle is the most promising of the methods available for accurate power loss measurements [72][73]. This method has the advantage of being able to measure the power losses under normal operating conditions and being independent of electrical quantities of the device under test. The disadvantages are that it is usually limited to steady state and that measurement procedure is time consuming.

# 1.6. Thesis Thematic Unit and Scope

Current trends in induction cooking propose to design the new cooktops for being more flexible, sustainable, efficient and reliable. In this way, new products with a lower cost, longer lifetime and more rational use of energy could be commercially available. In this regard, power semiconductor devices emerge as promising pillars to achieve such targets. However, a long pathway of technological exploration is still required. This thesis faces some of such topics from semiconductor power device point of view, either proposing new applications or starting new ways to better study them at die-level. Bearing in mind several semiconductor technologies, this PhD work proposes several solutions in the following fields: SSR, power losses calculation in resonant power converters and ruggedness study on semiconductor devices employed or with potential to be used in induction cooking appliances.

With regards to SSR, a suitable replacing technology for the EMR is investigated in the framework of induction cooking appliances, mainly intended to provide flexibility through the power multiplexing function. Existing and emerging technological options are studied and the most promising identified solutions are completely developed, bringing them closer to the practical application scenario from fully functional prototypes.

Moreover, ruggedness tests are performed to much better study the suitability of new power device references in induction cookers: SC tests at high  $V_{GE}$  values (up to 20 V), to explore if they have such capability and exploit this to improve the induction cooker reliability. In this last point, the suitability of medium voltage Gallium Nitride (GaN) High-Electron-Mobility Transistor (HEMT) devices for induction cooking appliances is also considered in terms of their SC capability.

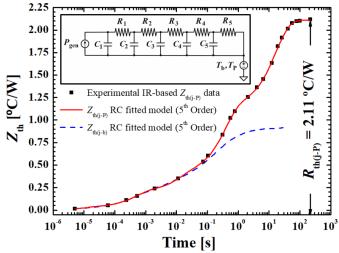

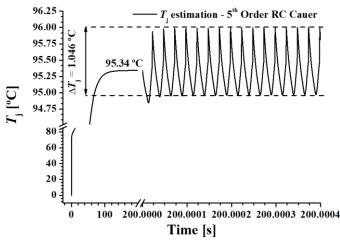

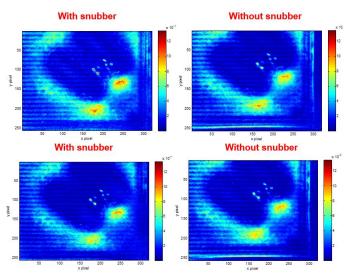

Finally, in relation to efficiency and reliability aspects in induction cooking, several working scenarios are considered. Firstly, the working  $T_j$  evolution of the IGBT semiconductor devices used in induction cooking appliances is unknown and is a completely new topic to be investigated. It will be interesting having a procedure to accurately evaluate the power losses in devices (power dissipation model), as well as a predictive thermal model of the used components, accounting for all effects involved from the device to external boundary conditions. Therefore, establishing a losses evaluation procedure, jointly with a validation protocol by means of an IR camera, could aid to a more accurate modelling. Secondly, the power dissipated due to switching losses (thermal cycles with higher frequency and lower temperature swing) are analysed if higher time resolution can be achieved by alternative post-processing approaches of IR thermal maps. This helps to determine the effects of IGBT recombination processes after turn-off in such a modelling to further understand the IGBT behaviour and decrease its losses under soft-switching conditions.

# **Chapter 2: THESIS OBJECTIVES AND STRUCTURE**

#### 2.1. Main Objectives

The main objectives of this PhD Thesis are:

- An improvement of IH appliances by increasing their flexibility, sustainability, efficiency and reliability levels, based on power semiconductor devices. This goal is achieved from:

- Studying the implementation of SSR based on advanced power semiconductor devices to improve the performance reached by EMR. Different technological solutions are evaluated and a specifically designed dynamic test circuit is developed.

- Robustness analysis of the power semiconductor devices used in IH appliances. Studying the robustness of emerging power devices to be used for IH. Using the SC tests as a ruggedness evaluation tool in line with the standards used by the power semiconductor devices manufacturers. To this end, an already available test platform is optimized to perform those measurements.

- Extraction of  $T_j$  distribution of the power semiconductor devices as a means of evaluation of the devices power losses and weak spots identification under real condition. For this purpose, a specific measurement test platform needs to be designed and implemented. It is worth to point out that under ZVS conditions and the presence of a snubber capacitor, the measurements of the total electrical power losses become more complex and further approximations are required. These facts help to improve the design for reliability at system level by allowing the validation of the suitability of electrical models for its simulation. Moreover, local analyses of the temperature distribution are used for the extraction of the devices current distribution, which provides useful information to identify the device weak spots which might originate the component destruction.

Establishing criteria/protocols for power semiconductor devices selection representative of IH appliances requirements, in order to mitigate future reliability problems.

#### 2.2. PhD Thesis structure:

To cover the outlined goals, this thesis is organized in the next chapters as follows. Chapter 3 addresses the SSR BDS implementations. First, the objectives and PhD student's role is described. Then, the implementation of the studied BDS into test vehicles, together with its characterization, is addressed in section 3.2. Moreover, section 3.3 is focused on their performances and characteristics, which are evaluated from static and dynamic analysis. In addition, a simulation approach is also developed so as to fully understand the devices oscillatory phenomena at the blocking instant (Simulation Program with Integrated Circuits Emphasis (SPICE) simulation) and the identified abnormal behaviours using Finite Element Methods (FEM) based simulations. Besides, it is addressed the implementation of a functional prototype and its final evaluation at an IH appliance. Finally, this chapter ends with the main conclusions.

In Chapter 4, ruggedness and reliability studies in power semiconductor devices in the framework of induction cooking are addressed. First, the objectives and PhD student's role is described. Then, the used test platform for performing SC tests in IGBTs and GaN HEMTs is described, together with a brief description of the studied devices characteristics. Afterwards, the results of the SC tests are discussed. Finally, the chapter ends with the conclusions.

Chapter 5 addresses  $T_j$  extraction and device weak spots identification under real operating conditions. This chapter starts with the objectives and PhD student's role. Then, the selected devices and the used test setups are described. Moreover, the extraction of the devices Compact Thermal Model (CTM) is addressed. Furthermore, this chapter describes the development of a simulation thermal model based on the obtained CTM. Finally, the conclusions are discussed.

Chapter 6 concludes this PhD Thesis with an outline of the general conclusions and a proposal of future works.

# **Chapter 3: SSR BDS IMPLEMENTATIONS**

#### 3.1. Objectives and PhD student's role

As it has been already stated, one of the objectives of the present research was the analysis of innovative options for replacing the EMR as a key component for enhancing the flexibility of future induction cooking systems. In this sense, SSR solutions based on advanced power semiconductor devices have been experimentally analysed by the PhD student in the context found in IH converters for home appliances. Emerging Silicon Carbide (SiC) and GaN WBG based implementations are compared to the most performant Silicon (Si) based devices (i.e.: TRIACs, Si IGBT+diode, RC-IGBTs, Reverse-Blocking IGBTs (RB-IGBTs), Si Super-Junction (SJ) MOSFETs, SiC Junction Field-Effect Transistors (JFETs), SiC MOSFETs, GaN HEMTs, GaN Cascodes etc.). Up to 20 test vehicles have been implemented with these devices and assessed with specifically designed test platforms and set-ups, providing for the first time an exhaustive evaluation and comparison among SSRs developed with all the commercially available power semiconductor devices. The results obtained from the tests have been presented in national and international conferences in order to promote a fruitful exchange with other researchers and to detect any possible alternatives of interest to be included in the study. In particular, in [3] the electrical characterization approach taken for the SSR test vehicles evaluation was presented, as well as the results obtained from the first prototypes developed with the anti-series connection of devices (Si IGBT+diode, RC-IGBT, SJ-MOSFET, SiC MOSFET, SiC JFET and GaN HEMT). In [2] the experimental results concerning single chip solutions (Si TRIACs) and anti-parallel combination of RB-IGBTs were also presented. Finally, the complete study adding the last device references appeared in the market (SiC Bipolar Junction Transistors (BJTs), SiC cascodes and GaN cascodes) was published in [1]. In this paper, original concepts for SSR electrical characterization from the static (definition of a new FOM) and dynamic (new test platform concept) point of view were presented, as well as the validation of one of the most promising solutions (GaN HEMT based SSR) in a real induction cooker. Using this GaN-based SSR prototype, special attention to the thermal management issues was also addressed. The most tangible conclusion derived from the present PhD objective

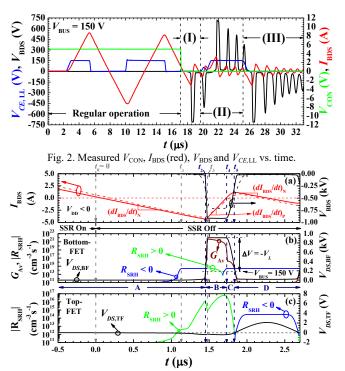

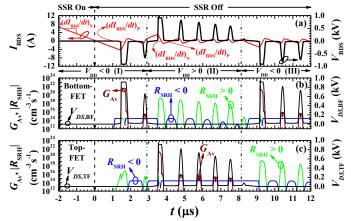

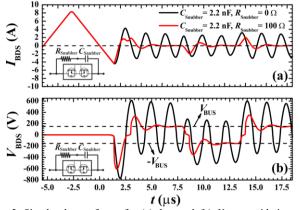

(analysis of new SSR concepts) has been a patent application claiming for a SSR solution based on GaN HEMTs [5][6]. The benefits and potential of such innovation is directly derived from the exhaustive study performed by the PhD, which is described in the mentioned references. Another significant conclusion obtained in this work was the identification of abnormal failure mechanisms detected for the first time in RC-IGBTs and SJ MOSFETs [4]. The explanation of these unexpected results required an in-depth analysis of the device structure and operation, and justify in fact the research effort devoted on each new SSR solution analysed. The next sections summarize the main results concerning the development and characterization of the proposed SSR solutions.

## 3.2. SSR Test Vehicles Design, Development and Characterization

#### 3.2.1 Semiconductor Power Devices Selection for SSR

The requirement of power semiconductor devices to IH appliances comes almost from its very beginning [74], imposed by the commutation of the high-frequency currents for the power inverters: 20-40 kHz. Nowadays, the upper limits have been extended up to 80-100 kHz and are limited by the switching losses of the involved power semiconductor devices, conventionally Si IGBTs.

Concerning the power multiplexing function, the requirement of a soft-stop/start function of the power inverter is removed when SSR solutions are employed, except for the TRIAC. In contrast, a zero-crossing current detection circuit is required. Moreover, the EMRs are commutated at very low switching frequencies. Consequently, it exists a clear predominance of the conduction power losses, well above the switching power losses, when SSR-based implementations are considered. Therefore, despite the mentioned drawbacks of EMRs, their application is preferred because of their lower onstate power losses, compactness and reduced costs. However, recent improvements on Si-based devices and the excellent properties of emerging WBG-based devices open up the possibility for SSRs with comparable efficiencies and improved switching characteristics, when compared to EMRs. Moreover, in so far as the need for higher EMR current rating grows, the cost of SSR BDS will be more competitive.

The studied framework involves 600-1200 V and 20-70 A for the power devices included in this work, so as to extend the coverage of the analysis to the biggest possible number of power semiconductor devices families. For simplicity, all the developed implementations are based on commercially available devices.

#### 3.2.1.1 Si Devices Technologies

From Si-based device technologies, Si TRIACs and Si SJ MOSFETs were initially identified as some of the most promising solutions to replace the EMR.

Concerning the Si TRIAC, the main advantage of this device above the rest of the studied semiconductor devices is that it implements a BDS just by itself. Unfortunately, at the same time it is the only one that conceptually fails at switching off the involved high-frequency AC currents, due to highly exceeding the devices turn-off maximum rate of current change. Therefore, a solution based on Si TRIACs would imply the need for deactivating the power inverter prior to the device commutation, as it happens for EMRs. In addition, despite these devices highlight some of the highest current densities [1], the device power losses are high when compared to EMR due to the intrinsic voltage drop of its PN junctions, which will involve the need for additional dissipation heatsinks. Notwithstanding, a solution based on Si TRIACs will allow a higher multiplexing rates (with the above-mentioned restrictions) and therefore improve the application performance by eliminating the irregular water boiling issues and completely removing the acoustical noise.

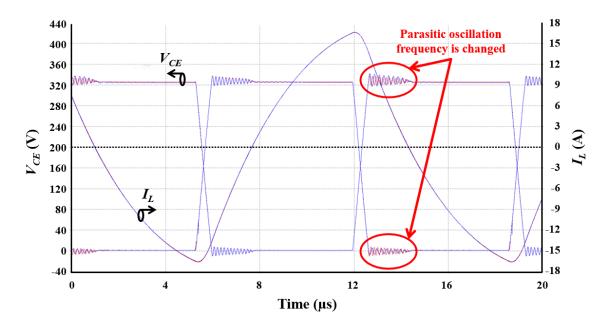

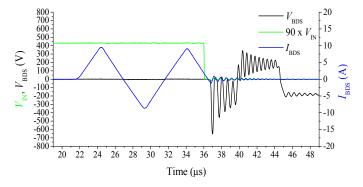

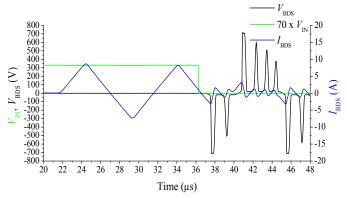

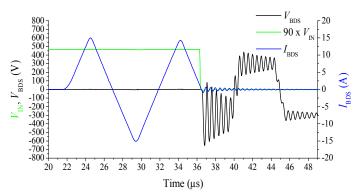

With regards to Si MOSFETs, the development of SJ technology in 1997 was capable of breaking the called "limit of Silicon", which had been established during 1980s. This limit fixed the lowest possible on-state resistances for specified breakdown voltages. SJ technology gave rise to a power device with one of the lowest on-state resistances: featuring <20 m $\Omega$  at 650 V. Though, a BDS solution based on these devices revealed an abnormal oscillatory phenomenon when turned-off, as it has been demonstrated for the first time by experiments and physics-based simulations. It is addressed in [4].

Other Si-based technologies are interesting for SSR implementation, in particular RC-IGBTs and RB-IGBTs. Nevertheless, such bipolar power devices show an unavoidable off-

set voltage drop (higher than that of TRIACs) responsible for relatively high conduction power losses [1][75][76].

Given that the most performing Si-based BDS alternatives to EMR in terms of the conduction power losses highlight several limitations, and that Si-based technologies have already reached a significant degree of maturity, the focus is placed at innovative WBG-based power semiconductor devices, with the expectations of higher performances and projected costs drop in the medium/short-terms.

#### 3.2.1.2 WBG Devices Technologies

WGB semiconductor devices highlight superior switching and thermal characteristics compared to its Si counterparts, enabling a reduction of the passive elements. Therefore, power devices technologies based on those materials are emerging as potential candidates for those applications in which Si devices present a limited operation [77].

Among WBG materials, GaN and SiC materials are the most promising ones. While GaN HEMTs highlight lower on-state resistances than SiC, the latter provides higher breakdown voltages. In this sense, there is a crossing point around 600-1000 V from which the balance is shifted in favour of SiC [78]. Concerning GaN devices, they can be grown in both Si and GaN substrates, but Si substrates provide substantial costs decrease and takes advantage of keeping the same semiconductor devices manufacturing lines used for nowadays Si-based devices.

Natively, GaN HEMTs are normally-on switches, which result critical for appliances with fail-safe requirements. In response to this, GaN cascodes and Enhancement-mode HEMTs (EHEMTS) have appeared as a normally-off solution [79][80]. In this scenario, p-GaN HEMTs and Metal-Insulator-Semiconductor HEMTs (MISHEMTs) are consolidating as the most promising commercially available EHEMTs. An implementation of a SSR BDS based on GaN MISHEMTs is addressed in this chapter, where this solution highlights the lowest on-state resistance and the highest integration characteristics, from the possibility of implementing the BDS monolithically.

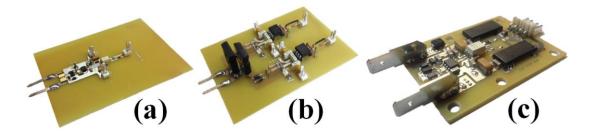

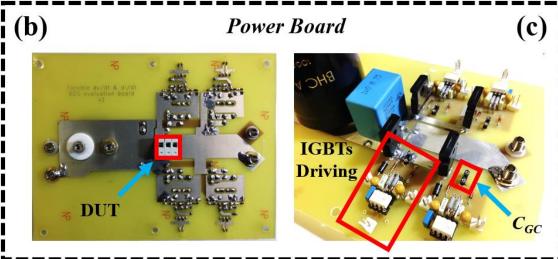

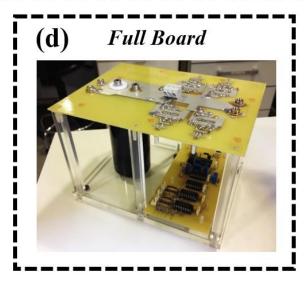

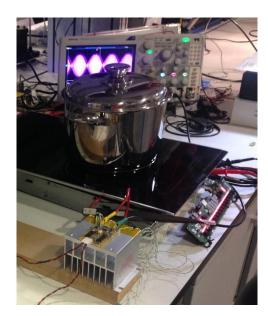

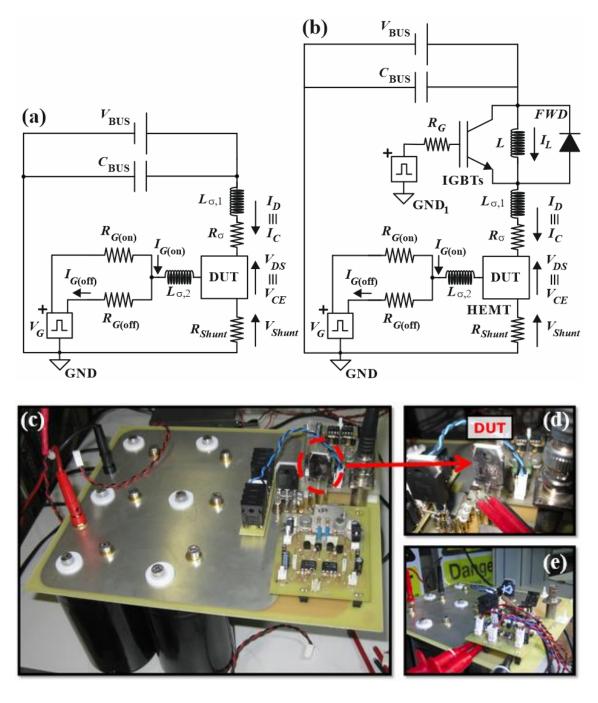

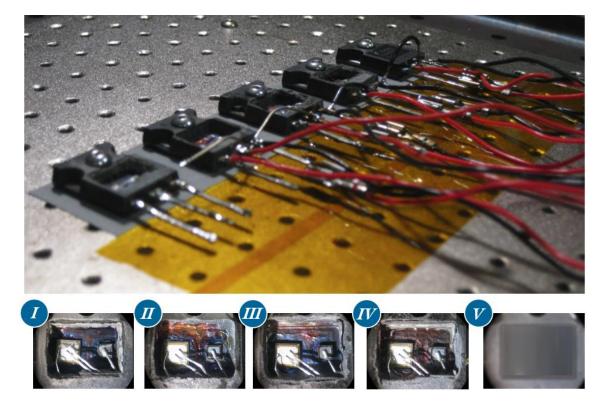

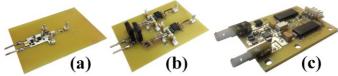

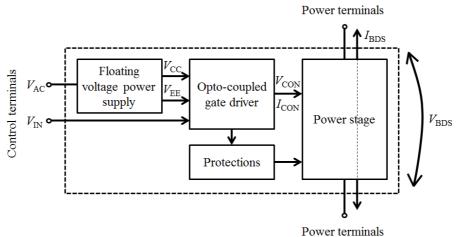

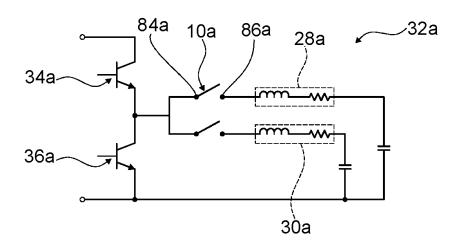

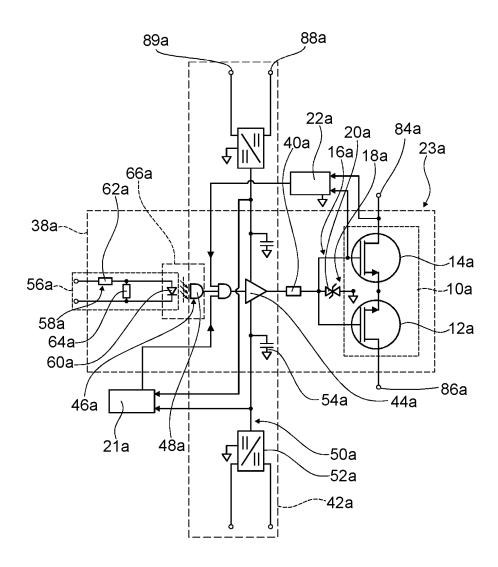

Fig. 3.2-1. Test vehicles for implementing a BDS from (a) GaN HEMTs and (b) RB-IGBTs; and (c) GaN HEMT SSR functional prototype. Figure extracted from [1].

#### 3.2.2 SSR Test Vehicles Development

The driving conditions and control complexity of each solution is used to implement a set of different test vehicles based on the different power devices. A total of twenty implementations have been developed and evaluated, from which thirteen are based on different device technologies and semiconductor structures. Their operation is conditioned by the number of required power devices, the way they are arranged in the BDS and their driving requirements: voltage/current control, operating modes (normally-on/normally-off), etc. Therefore, particular driving circuitry is designed for each solution.

An example of some of them is shown in Fig. 3.2-1 (a)-(b).

On the one hand, the complexity of the control system is subjected to analysis in view of the following characteristics:

- Number of combined devices and their interconnection scheme.

- Switching characteristics.

- Operating modes.

- Number of required power supplies.

- Number and type of the required drivers.

- Control signals.

In addition, the power losses of the control system are also evaluated, with the following data collected for each solution:

- Input power losses (related to control signal) for each type of driver.

- Voltage between terminals for each power source present in the control stage of the BDS in both states:

- On-state (BDS in conduction)

- Off-state (BDS in open circuit)

- Average current consumption for each power source under the aforementioned conditions.

From this information, on-state and off-state power losses are calculated, together with an average power consumption for comparison purposes.

Finally, the cost for each implementation is calculated, based on the quotations provided by the biggest electronic devices suppliers, including the isolation and driving requirements, power sources and passive elements.

Publication [1] provides a qualitative analysis of the obtained results concerning the control stage characteristics. This topic can be critical concerning the production of SSRs at industrial level, where the cost of every part is critical for obtaining a reasonable commercial success. The performed analysis shows the main trends concerning the control stage characteristics and issues, although in this work the power stage analysis is focused more in detail.

#### 3.3. Evaluation of Performances and Characteristics

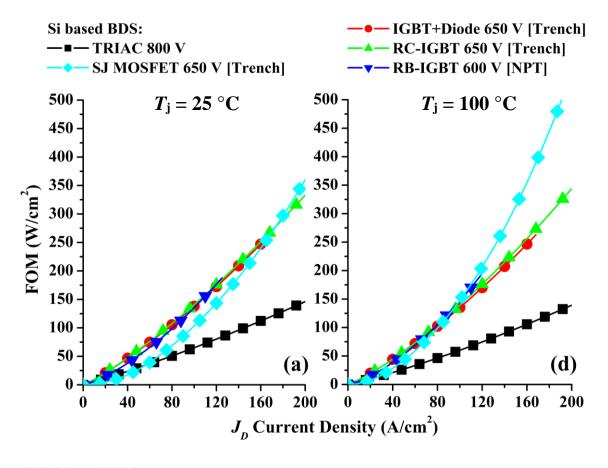

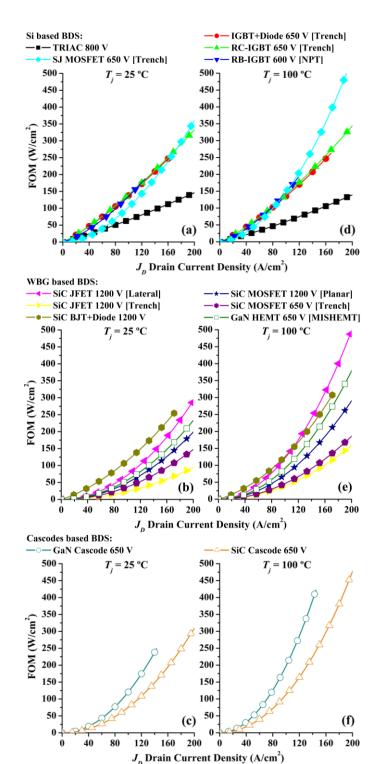

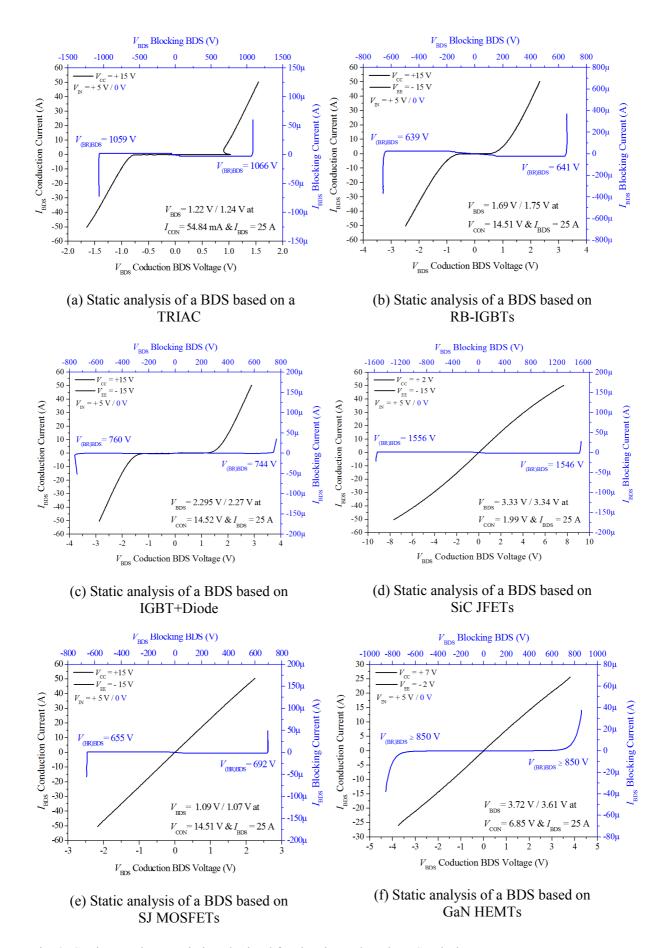

#### 3.3.1 Static Analyses and FOM Definition

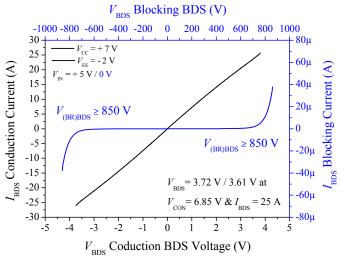

In the studied framework, the BDSs are commutated at very low switching frequencies. Therefore, it exists a clear predominance of the conduction power losses above the switching power losses. For this reason, the static *I-V* curves for each BDS test vehicle are extracted in forward and blocking modes, using standard curve tracers (TEK 371A).

The characterization data provides the basic set of parameters to compare the considered devices among and to understand their behaviour under operation. However, a static analysis based on those measurements allows only a comparison between specific device references. This analysis can be enhanced from the extraction of the devices active areas and expressing the static characteristics in terms of current density. However, those areas cannot be precisely differed from the whole chip size.

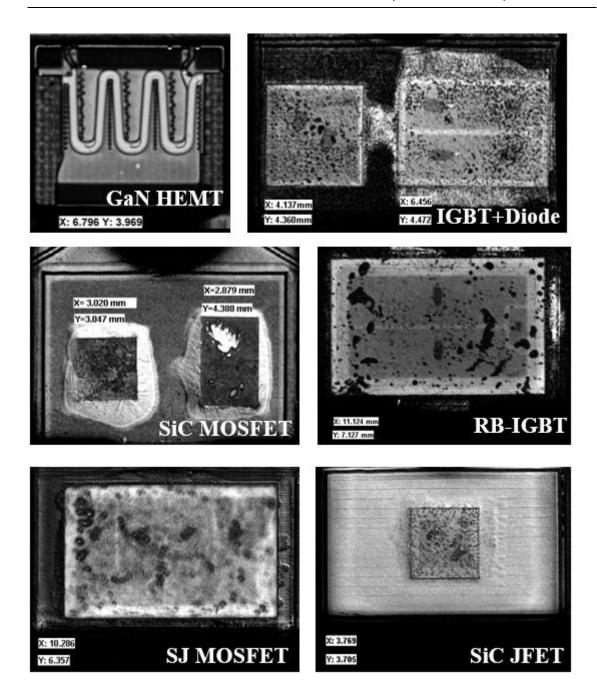

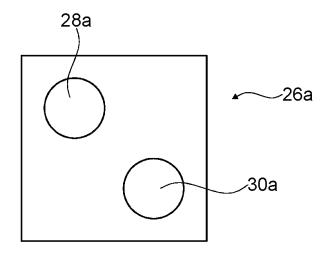

Fig. 3.3-1. Bare die areas of several power semiconductor devices.

Therefore, using a Scanning Acoustic Microscope (SAM) Sonoscan GEN-5 the devices bare die areas are measured (Fig. 3.3-1) and the static current densities ( $J_D$ ) are obtained.

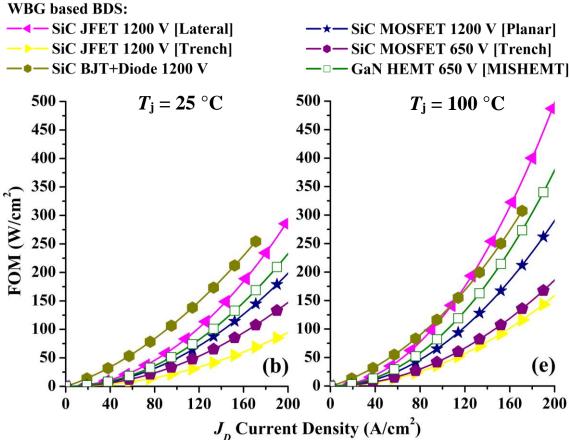

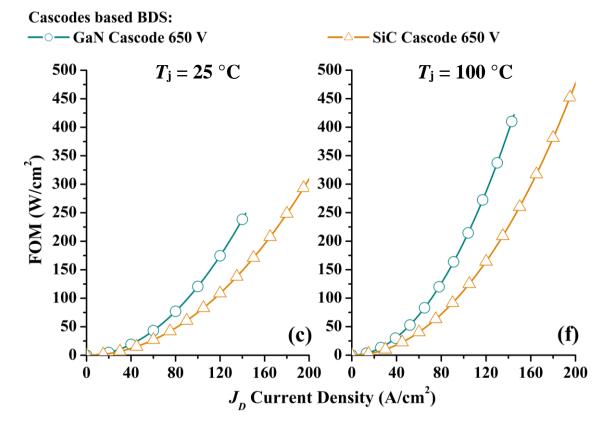

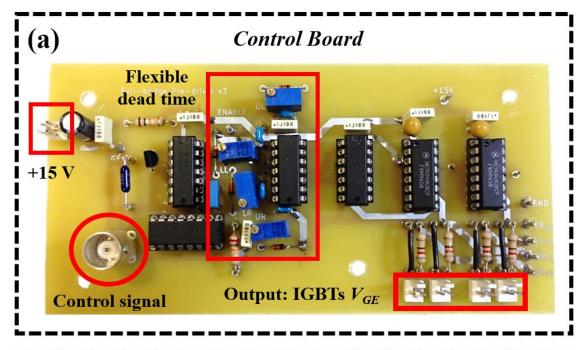

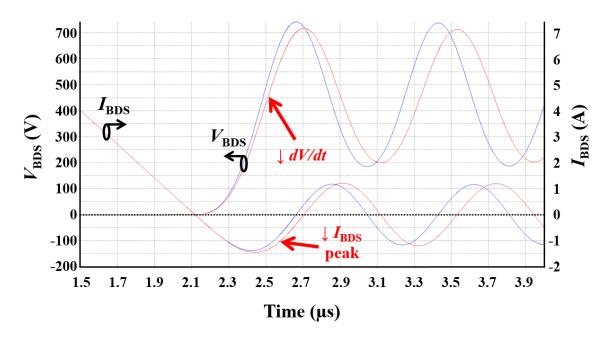

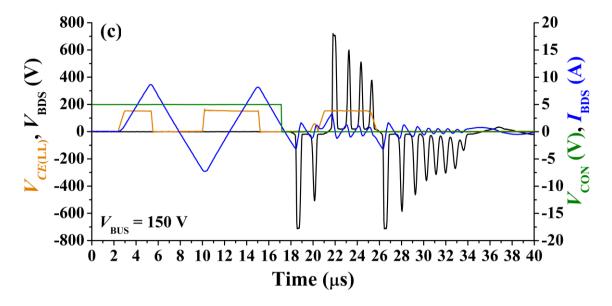

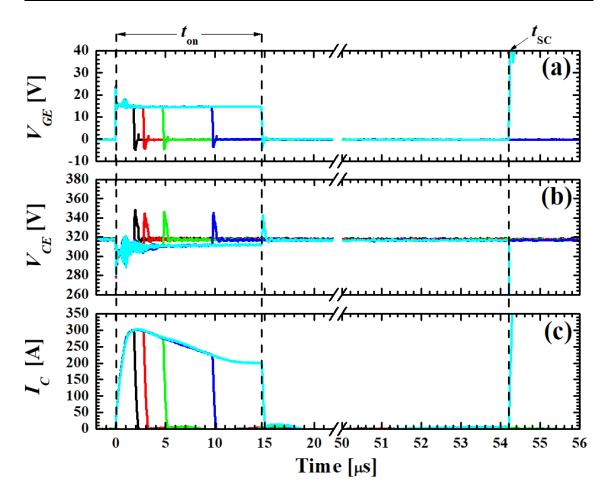

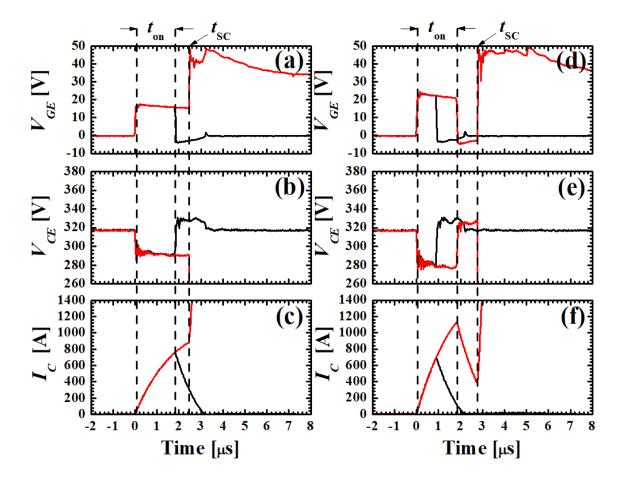

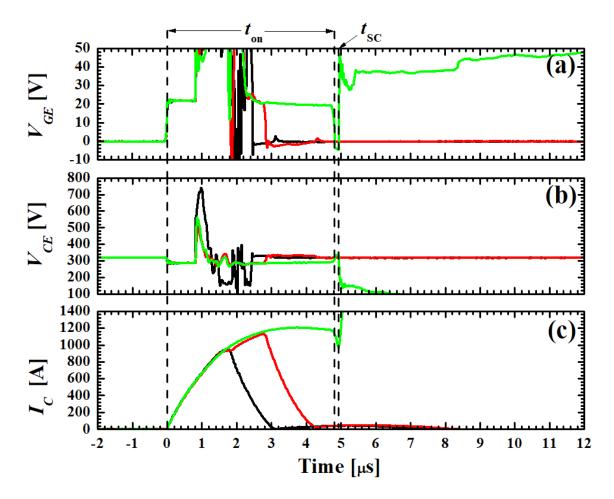

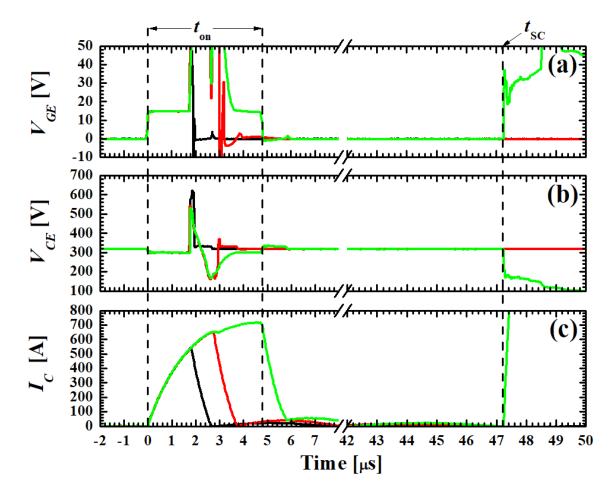

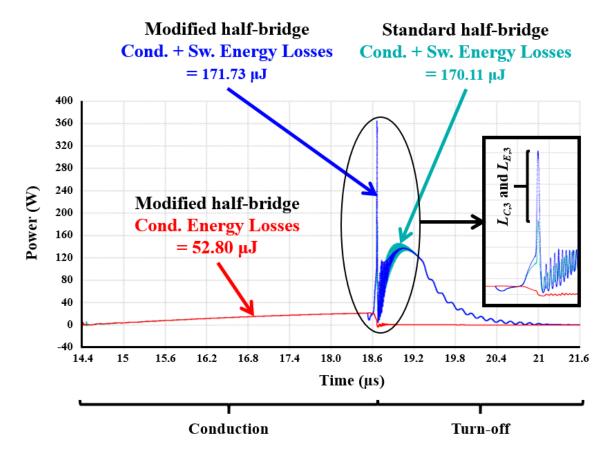

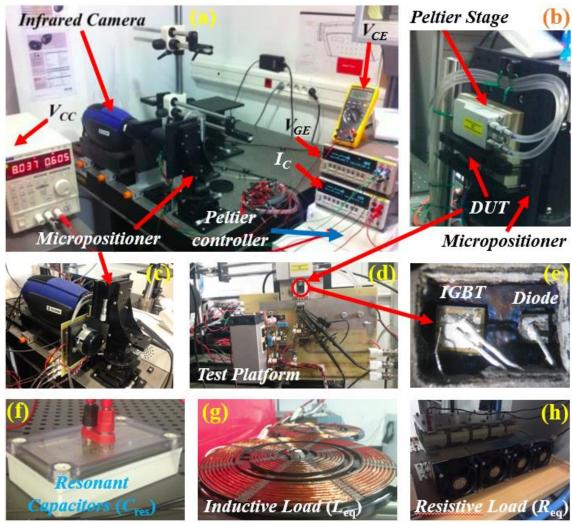

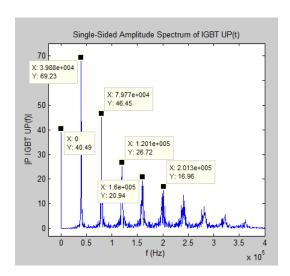

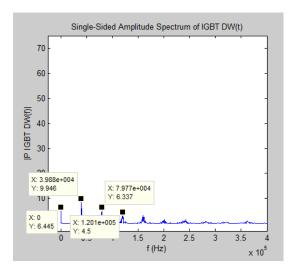

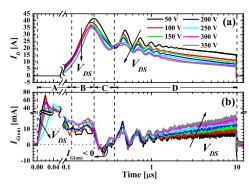

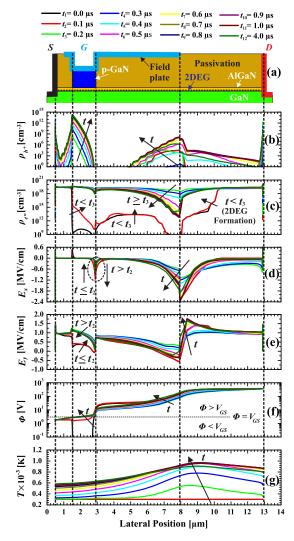

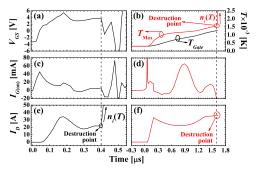

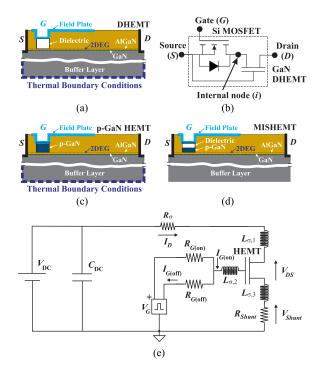

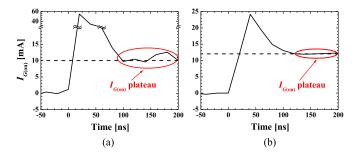

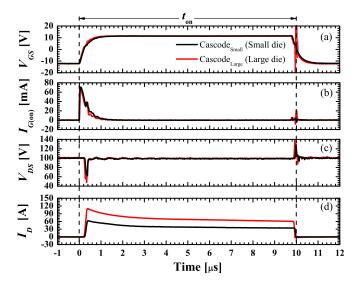

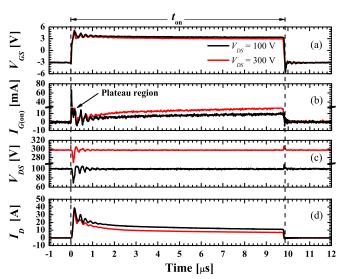

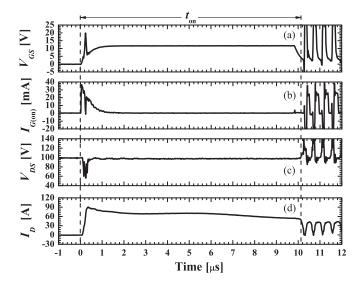

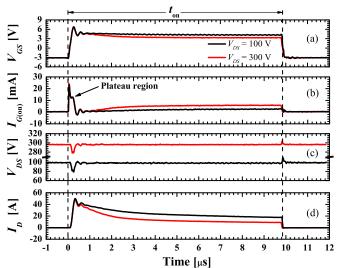

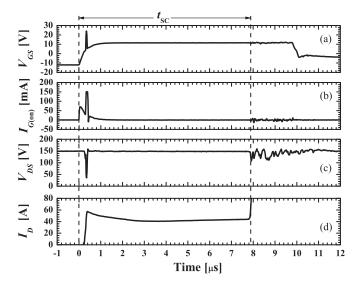

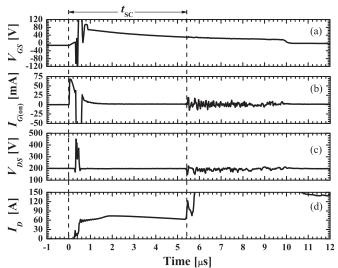

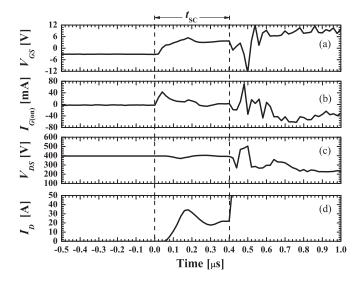

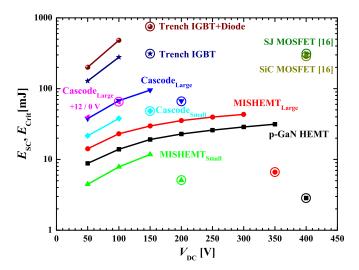

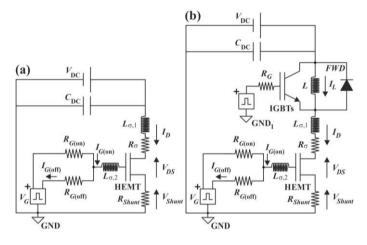

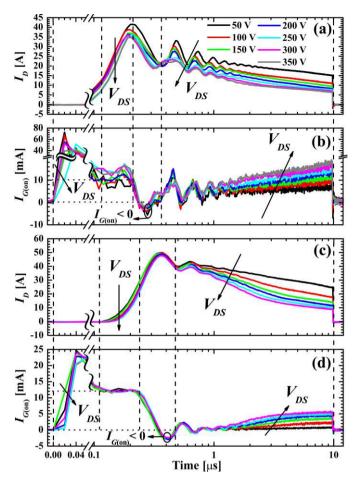

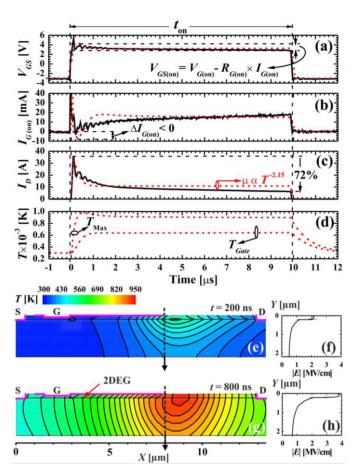

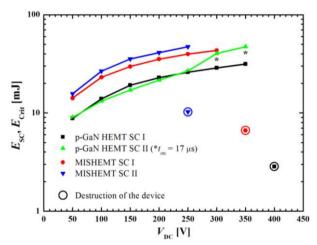

As a result,  $J_D$ - $V_{BDS}$  curves are calculated for each solution, so that the static analysis can be extended from specific references to device technologies. In this calculation, the bare die areas are totalled when more than one device is simultaneously conducting current (i.e. GaN or SiC cascodes).