Available online at www.sciencedirect.com

### **ScienceDirect**

Procedia Engineering 168 (2016) 1291 - 1295

# **Procedia Engineering**

www.elsevier.com/locate/procedia

30th Eurosensors Conference, EUROSENSORS 2016

## Synchronous OEIC integrating receiver for ORGA applications

Carlos Sánchez-Azqueta<sup>a,b,\*</sup>, Bernhard Goll<sup>a</sup>, Santiago Celma<sup>b</sup>, Horst Zimmermann<sup>a</sup>

<sup>a</sup>Institute of Electrodynamics, Microwave and Circuit Engineering, Vienna University of Technology Gußhausstraße 25/234, Vienna 1040, Austria <sup>b</sup>Group of Electronic Design, Aragón Institute of Engineering Research, Universidad de Zaragoza C/Pedro Cerbuna 12, Zaragoza 50009, Spain

#### Abstract

This work presents a monolithically integrated synchronous optical receiver fabricated in a standard 0.35 µm CMOS process. The receiver consists of a regenerative latch acting as a sense amplifier; two highly effective, low-capacitance pin photodiodes connected to its output nodes (one of them blocked to the light); and an adjustable reference current to compensate the dynamic offset created by the asymmetries between the parasitic capacitances of the photodiodes. For  $\lambda = 635$  nm, a sensitivity of -25.8 dBm, -26.0 dBm, and -28.4dBm is obtained, respectively, for 400 Mbit/s, 350 Mbit/s, and 250 Mbit/s (BER = 10<sup>-9</sup>). The power consumption is 670 µW, which translates to an energy efficiency of 1.7 pJ/bit at 400 Mbit/s. © 2016 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license

(http://creativecommons.org/licenses/by-nc-nd/4.0/). Peer-review under responsibility of the organizing committee of the 30th Eurosensors Conference

Keywords: Integrated optoelectronics; integrated pin photodiodes; integrating receivers.

#### 1. Introduction

High-speed reconfigurable circuits have attracted great interest because their operation can be modified in order to avoid idle activity, allowing a re-use of the hardware components and thus optimizing performance. Although field programmable gate arrays (FPGAs) are the most commonly used reconfigurable system, their reconfiguration cycles of typically several milliseconds make them unsuitable for the speeds demanded in today's applications, which range up to several hundreds of megahertz [1], [2]. Higher reconfiguration speeds can be achieved by multicontext FPGAs, DAP/DNA or DRP circuits, but at a very low gate density [3].

<sup>\*</sup> Corresponding author. Tel.: +34-876-553547. E-mail address: csanaz@unizar.es

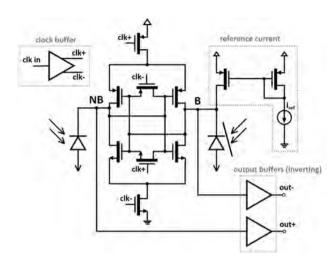

Fig. 1. Circuit diagram of the OEIC. One clock phase resets and the other one activates the latch. A DC current into the blocked PD node compensates asymmetries in the parasitic capacitances of the blocked and non-blocked PDs.

Another alternative are optically reconfigurable gate arrays (ORGAs) in combination with holographic memories, which can achieve near Gbit/s speeds without compromising gate density. To operate, ORGAs require optical receivers with high sensitivity, low power consumption and large integration density. Because of this, implementations based on conventional optical detectors with a transimpedance amplifier (TIA) are not possible because of their high power and large die area. For instance, in [4] a TIA with post amplifiers in 0.35  $\mu$ m high-voltage CMOS needed 55 mW and a core area, excluding the PD, of 79 300  $\mu$ m² to achieve a digital output.

As an alternative to TIA-based optical receivers, this paper proposes the use of the integrating optical receiver, whose digital operation achieves a drastic reduction of the power consumption while at the same time allows being downscaled to shorter technologies for faster operation. Recently reported implementations achieve Gbit/s with energy efficiencies of 0.9 pJ/bit [5], where a multi-quantum well (MQW) *pin* PD was flip-chip bonded to a CMOS chip, and 4.5 pJ/bit [6], which used an electro-absorption modulator at 1550 nm. The main disadvantage of integrating optical receivers is low sensitivity. For instance, [5] reports –16.5 dBm at 1 Gbit/s, and [6] –19.4 dBm at 1.2 Gbit/s. This happens because the voltage generated across the PD capacitance is inversely proportional to the capacitance itself; for this reason, the sensitivity of integrating optical receivers can be improved by their monolithic integration with the PD in an optoelectronic integrated circuit (OEIC). In this respect, current standard silicon CMOS and BiCMOS technologies allow small-area *pin* PDs with a capacitance under 100 fF, responsivity higher than 0.5 AW<sup>-1</sup> and –3 dB cut-off frequency above 1 GHz [7].

In this work, a monolithic integrating optical receiver is implemented in a 0.35  $\mu$ m CMOS process that allows the integration of a highly efficient 50  $\mu$ m *pin* PD featuring 50 fF capacitance. The circuit is fed at only 2.5 V and it achieves 400 Mbit/s operation with a bit error ratio (BER) better than 10<sup>-9</sup>. The regenerative latch achieves an energy efficiency of 1.7 pJ/bit and, along with the output buffer (excluding the PDs), occupies 50  $\mu$ m × 30  $\mu$ m.

#### 2. Integrating optical receiver OEIC

The architecture of the OEIC is shown in Fig. 1. A regenerating latch driven by a synchronization clock operates in two phases: when the clock is high, i.e., clk+ is in a logic 1, the latch is reset to a metastable state characterized by  $V_B = V_{NB} \approx V_{dd}/2$ ; in turn, when the clock is low, the operation as a latch is enabled. Two monolithically integrated pin PDs are connected to the outputs, one of them receiving the light input and the other one blocked by a metal layer. Ideally, if no external stimuli act after the reset, the metastable state is kept for the half clock period when the latch is enabled; however, in a practical implementation there are asymmetries breaking the metastable state that

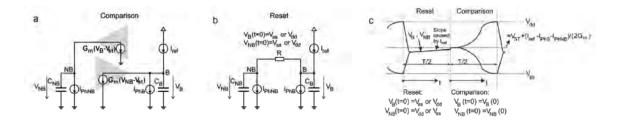

Fig. 2. Model for the latch (a) in the comparison phase and (b) during reset. (c) Main transients of the latch during reset and comparison.

need to be compensated for reliable operation. In particular, there is a significant increase of roughly 40 % in the parasitic capacitance of the blocked PD over the non-blocked PD caused by the metal layer above.

The asymmetry between the parasitic capacitance  $C_{NB}$  at node NB (non-blocked PD) and  $C_B$  at node B (blocked PD) causes a dynamic offset for the latch that has been analysed in [8]. Figs. 2a and 2b show, respectively, the circuits equivalent to Fig. 1 for comparison (clk+ = 1) and reset (clk+ = 0), where  $I_{PhNB}$ ,  $I_{PhB}$  are the PD photocurrents compared during the comparison phase,  $G_m$  the transconductance and  $V_{st}$  the switching threshold of one of the two latch inverters, which are assumed equal for simplicity.  $I_{PhB}$  is usually very small due to light blocking and can be considered as dark current and current caused by stray light to the active area. A DC current  $I_{ref} < 1 \mu A$  is fed to node B to minimize dynamic offset. Fig. 2c shows a sketch of the transients in the latch.

The condition of a metastable state for equal PD currents ( $I_{PhNB} = I_{PhB} = I_{Ph}$ ) in the comparison phase is that the exponential growing term of  $V_B - V_{NB}$  is zero. Under the condition that  $V_{st} > V_0$  in the comparison phase, the dynamic offset can be adjusted with a positive current  $I_{ref}$  into node B, taking care that for most process tolerances this condition is valid so that no negative  $I_{ref}$  is needed, which is controlled during the design of the latch. Another advantage is that the initial voltage  $V_0$  of the comparison phase is controlled during the reset phase with  $I_{ref}$ .

#### 3. Measured results

An edge-emitting laser source with  $\lambda=635$  nm and extinction ratio ER = 10 and a vertical cavity surface-emitting laser (VCSEL) with  $\lambda=675$  nm and ER = 5.5 have been used to generate the light input data stream, whose average power is controlled by an optical attenuator before reaching the OEIC through a multi-mode fibre with a core diameter of 62.5  $\mu$ m. The output from the OEIC is sensed on-wafer by an active probe with 0.1 pF parallel 10 M $\Omega$  input impedance and 1:20 attenuation. The average power of the modulated light signal is obtained directly measuring the current through the OEIC substrate, which can be done because the anode of the integrated *pin* PD is formed by the p+ substrate and all transistors are isolated by deep n-wells or n-wells, taking into account the PD sensitivity, which is 0.51 AW<sup>-1</sup> for 635 nm and 0.53 AW<sup>-1</sup> for 675 nm.

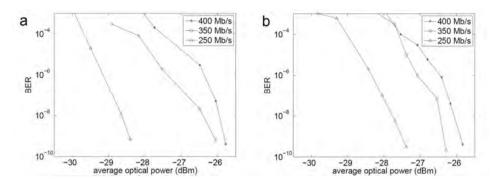

Fig. 3 shows the eye diagrams at BER =  $10^{-9}$  and Fig. 4 the sensitivity measurements carried out on the OEIC. The sensitivities at 400 Mbit/s, 350 Mbit/s, and 250 Mbit/s are, respectively, -25.8 dBm, -26.0 dBm and -28.4 dBm for 635 nm (Fig. 4a), and -25.8 dBm, -26.3 dBm and -27.4 dBm for 675 nm (Fig. 4b), all corrected for ER =  $\infty$  and obtained for a  $2^{31}$ -1 PRBS at BER =  $10^{-9}$ . Finally, the power consumption of the OEIC is 4.75 mW, of which only 670  $\mu$ W are consumed by the latch; at 400 Mbit/s, this translates to an energy efficiency of 1.7 pJ/bit.

#### 4. Comparison and conclusion

This work presents a synchronous OEIC integrating receiver in an OPTO ASIC 0.35  $\mu$ m CMOS technology with integrated *pin* PDs and dynamic offset compensation. The prototype shows a sensitivity of -25.8 dBm, -26.0 dBm and -28.4 dBm at 400 Mbit/s, 350 Mbit/s and 250 Mbit/s (BER =  $10^{-9}$ ), and a power consumption of only 670  $\mu$ W.

Although the digital nature of integrating receivers makes the maximum speed dependent on technology, the OEIC shows a clear improvement in terms of sensitivity, which is 6.6 dB better than in [6], which operated at 1 Gbit/s in 250 nm CMOS, and 9.5 dB better than in [5], which operates at 1.2 Gbit/s in 90 nm CMOS. [9] used 0.7

Fig. 3. Eye diagram of the output signal of the OEIC at (a) 400 Mbit/s, average optical power -25.8 dBm, (b) 350 Mbit/s, average optical power -26.0 dBm, and (c) 250 Mbit/s, average optical power -28.4 dBm.  $2^{31}$ -1 PRBS, BER =  $10^{-9}$ ,  $\lambda = 635$  nm, ER = 10.

Fig. 4. Measured sensitivity of the OEIC at 400 Mbit/s, 350 Mbit/s and 250 Mbit/s for (a)  $\lambda = 635$  nm, ER = 10 and (b)  $\lambda = 675$  nm, ER = 5.5.  $2^{31}$ -1 PRBS. The shown BER curves are corrected to ER =  $\infty$ .

$\mu m$  CMOS and reported 14 dB worse sensitivity at 180 Mbit/s. Finally, [10] achieves a remarkable -29.0 dBm sensitivity in 0.35  $\mu m$  CMOS, but at only 5 Mbit/s whereas our OEIC remains only 0.6 dB below in sensitivity but for a bit rate 50 times larger at 250 Mbit/s. This good sensitivity is achieved without compromising the low power and small area features of integrating optical receivers. In this sense, its energy efficiency is 1.7 pJ/bit and its area is 50  $\mu m \times 30 \mu m$ , in contrast to the hundreds of  $\mu m$  per side of TIA-based receivers, making it appropriate for applications featuring massively parallel receivers such as ORGAs.

#### Acknowledgements

This work was supported by the Spanish Ministry for Science and Innovation (MICINN) under a José Castillejo Mobility Scholarship to C. Sánchez-Azqueta, and by Grants TEC2011-23211 and TEC2014-52840-R.

#### References

- [1] M. Watanabe, R. Fujime, and F. Kobayashi, A dynamic differential reconfiguration circuit for optically differential reconfigurable gate arrays, in 49th IEEE International Midwest Symposium on Circuits and Systems. MWSCAS'06, vol. 2, pp. 94–98, Aug 2006.

- [2] B. Kim and J. Lee, 2-d non-isolated pixel 6/8 modulation code, IEEE Transactions on Magnetics, vol. 50, pp. 1-4, July 2014.

- [3] D. Seto and M. Watanabe, A dynamic optically reconfigurable gate array: Perfect emulation, IEEE Journal of Quantum Electronics, vol. 44, pp. 493–500, May 2008.

- [4] P. Brandl, R. Enne, T. Jukic, and H. Zimmermann, Monolithically integrated optical receiver with large-area avalanche photodiode in high voltage CMOS technology, Electronics Letters, vol. 50, pp. 1541–1543, October 2014.

- [5] A. Emami-Neyestanak, S. Palermo, H.-C. Lee, and M. Horowitz, CMOS transceiver with baud rate clock recovery for optical interconnects, in Digest of Technical Papers. 2004 Symposium on VLSI Circuits, pp. 410–413, June 2004.

- [6] J. Roth, S. Palermo, N. Helman, D. Bour, D. Miller, and M. Horowitz, An optical interconnect transceiver at 1550 nm using low-voltage electroabsorption modulators directly integrated to CMOS, Journal of Lightwave Technology, vol. 25, pp. 3739–3747, Dec 2007.

- [7] P. Brandl and H. Zimmermann, 3 Gbit/s optical receiver IC with high sensitivity and large integrated pin photodiode, Electronics Letters, vol. 49, pp. 552–554, April 2013.

- [8] A. Nikoozadeh and B. Murmann, An analysis of latch comparator offset due to load capacitor mismatch, IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, pp. 1398–1402, Dec 2006.

- [9] K. Ayadi, M. Kuijk, P. Heremans, G. Bickel, G. Borghs, and R. Vounckx, A monolithic optoelectronic receiver in standard 0.7-μm CMOS operating at 180 MHz and 176-fJ light input energy, IEEE Photonics Technology Letters, vol. 9, pp. 88–90, Jan 1997.

- [10] T. Schaffer and P. Mitkas, Smart photodetector array for page-oriented optical memory in 0.35-μm CMOS, IEEE Photonics Technology Letters, vol. 10, pp. 866–868, June 1998.