Proyecto de Fin de Carrera Ingeniería Informática Curso 2013/2014

# Caracterización de instrucciones en aplicaciones de cloud

Alba Pedro Zapater

Director: Dr. Víctor VIÑALS YÚFERA

Departamento de Informática e Ingeniería de Sistemas Escuela de Ingeniería y Arquitectura Universidad de Zaragoza

Septiembre 2014

## A grade cimientos

Sobre todo quiero agradecer a mi director, Víctor, todo lo que me ha enseñado, su paciencia, sus ánimos, su tiempo, su buen humor y toda la ayuda que me ha proporcionado durante este año. Fue uno de mis mejores profesores en la carrera y sin duda ha sido el mejor director que podría haber tenido. También le doy las gracias a Clemente Rodríguez y a Pablo Ibáñez por el tiempo que me han dedicado y por la gran ayuda que ha sido lo que me han enseñado. Además, darle las gracias a Marta Ortín por estar siempre dispuesta a resolverme dudas y su rapidez para contestarme a los emails.

También a mis compañeros de carrera que me han sorprendido con grandes dosis de solidaridad y ayuda mutua frente a la competencia que mueve nuestro mundo . En especial a Álvaro, Cintia, David y Juan, que han estado siempre para los buenos y los malos momentos y que sin su apoyo y amistad no hubiera sido posible llegar hasta aquí.

Para terminar, quiero agradecerles a mis padres por todo lo que me han dado, sin pedir nada a cambio, tan solo verme feliz. Y a todas las personas que siempre han creído en mi, y de una forma u otra han hecho posible que yo esté ahora escribiendo las últimas lineas de mi proyecto de fin de carrera.

#### Resumen

Las tendencias de mercado indican que el negocio de los procesadores para grandes centros de datos va a seguir creciendo, impulsado por la economía de la virtualización y la gran penetración empresarial y social de las aplicaciones que residen en las nubes (cloud computing). Para diseñar un procesador de futuro adaptado a este mercado es necesario experimentar con una carga de trabajo apropiada. Por ello, en este proyecto nos hemos centrado en caracterizar el comportamiento de la cache de instrucciones para un sistema de cuatro procesadores, usando el conjunto de aplicaciones Cloudsuite 2.0 del laboratorio de investigación Parsa, representativo del cloud computing.

Hemos usado la plataforma de simulación Simics, un simulador de sistema completo, trabajando con las cinco aplicaciones de Cloudsuite que están acompañadas de checkpoints públicos. Además, se ha contribuido con un tutorial de Simics, acompañado de material práctico, para facilitar y agilizar la fase de formación de otros proyectos que también utilicen esta plataforma.

Para realizar los experimentos deseados se han programado dos módulos de Simics de jerarquía de memoria basados en el módulo g-cache, que implementan dos algoritmos eficientes y específicos para registrar tasas de fallos y huellas de memoria. Un algoritmo obtiene resultados para múltiples caches en una sola simulación y el otro está especializado en caches completamente asociativas.

A partir de estos experimentos hemos analizado los benchmarks en cuanto a su tasa de fallos, en función de su tamaño y de su asociatividad, sugiriendo configuraciones prácticas de tamaño y asociatividad para cada aplicación. También se ha examinado la huella de memoria de instrucciones a lo largo del tiempo, concluyendo que todas las aplicaciones tardan muchos segundos en entrar en régimen estacionario y que la aparición de varias fases complica la selección de ventanas de simulación. Y finalmente, se ha calculado el ancho de banda de instrucciones agregado para los cuatro procesadores simulados, concluyendo que la presión sobre el siguiente nivel puede ser bastante grande, y sugiriendo configuraciones de ese segundo nivel con capacidad para absorber las demandas del primero.

# Contenidos

| Αę  | gradecimientos                                                                                                                                                                                                                          | V           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Re  | esumen V                                                                                                                                                                                                                                | I           |

| Co  | ontenidos                                                                                                                                                                                                                               | X           |

| Lis | sta de Figuras x                                                                                                                                                                                                                        | Ι]          |

| Lis | sta de Tablas xi                                                                                                                                                                                                                        | V           |

| 1.  | Introducción  1.1. Contexto del Proyecto                                                                                                                                                                                                | 1<br>3<br>3 |

| 2.  | Estado del Arte en simulación y cargas de trabajo  2.1. Plataformas y estrategias de simulación                                                                                                                                         | 5<br>5      |

| 3.  | CloudSuite 3.1. Características de los Benchmarks                                                                                                                                                                                       |             |

| 4.  | 4.1. Métricas Utilizadas       1         4.2. Modelo de las 3C       1         4.2.1. Algoritmos de una sola pasada       1         4.3. Módulo G-Cache       1         4.3.1. Módulos en Simics       1         4.3.2. G-cache       1 |             |

| 5.  | 5.1. Mpki por Core                                                                                                                                                                                                                      | 22          |

<u>Contenidos</u> X

|    |      | 5.1.4.  | Classification (Figura 5.4)                                               | 23        |

|----|------|---------|---------------------------------------------------------------------------|-----------|

|    |      | 5.1.5.  | Cloudstone (Figura 5.5)                                                   | 23        |

|    |      | 5.1.6.  | Conclusiones                                                              | 25        |

|    | 5.2. | Huella  | de Memoria                                                                | 25        |

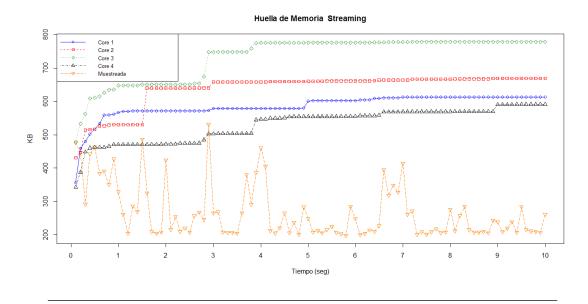

|    |      | 5.2.1.  | Streaming (Figura 5.7)                                                    | 27        |

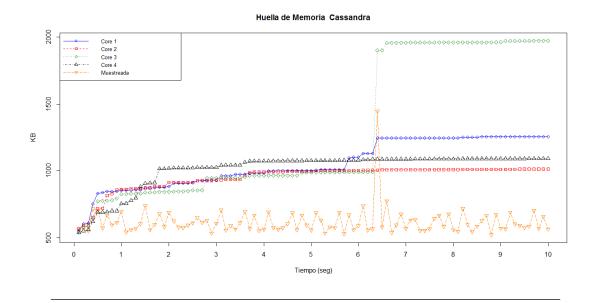

|    |      | 5.2.2.  | Cassandra (Figura 5.8)                                                    | 28        |

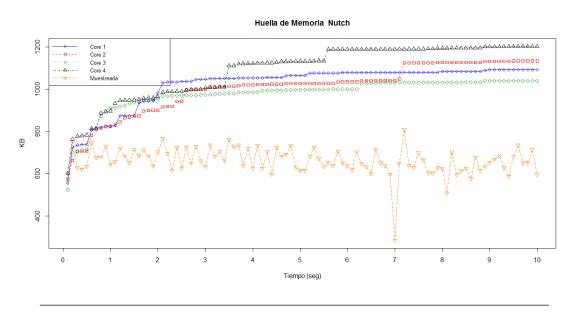

|    |      | 5.2.3.  | Nutch (Figura 5.9)                                                        | 29        |

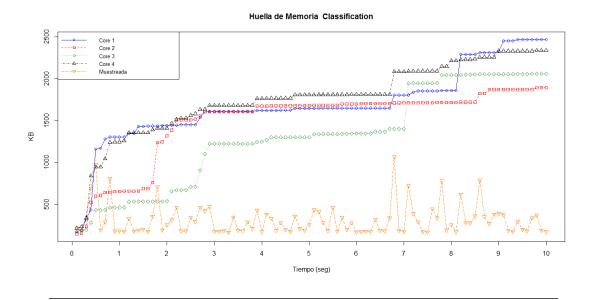

|    |      | 5.2.4.  | Classification (Figura 5.10)                                              | 29        |

|    |      | 5.2.5.  | Cloudstone (Figura 5.11)                                                  | 29        |

|    |      | 5.2.6.  | Conclusiones                                                              | 30        |

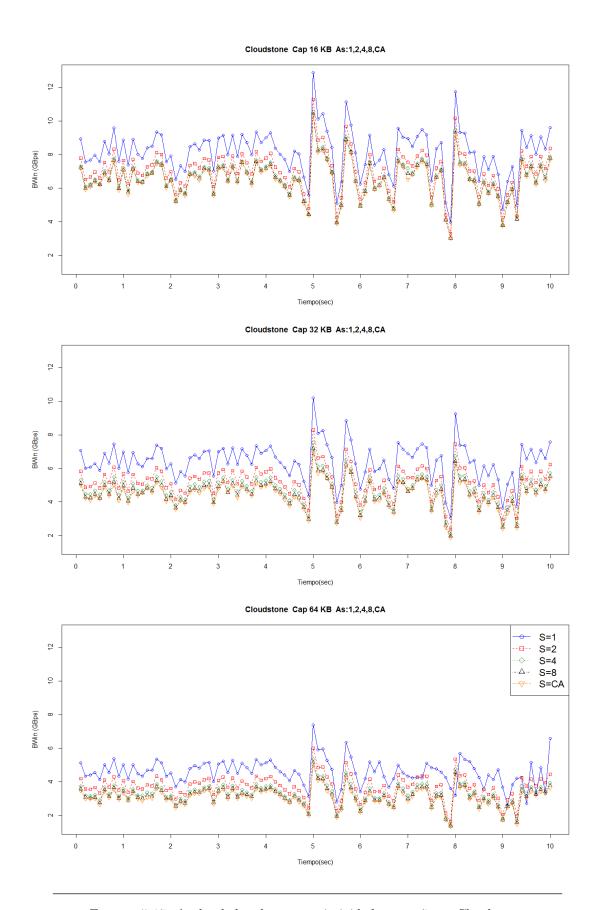

|    | 5.3. | Ancho   | de Banda de instrucciones                                                 | 31        |

|    |      | 5.3.1.  | Streaming (Figura 5.13)                                                   | 32        |

|    |      | 5.3.2.  | Cassandra (Figura 5.14)                                                   | 32        |

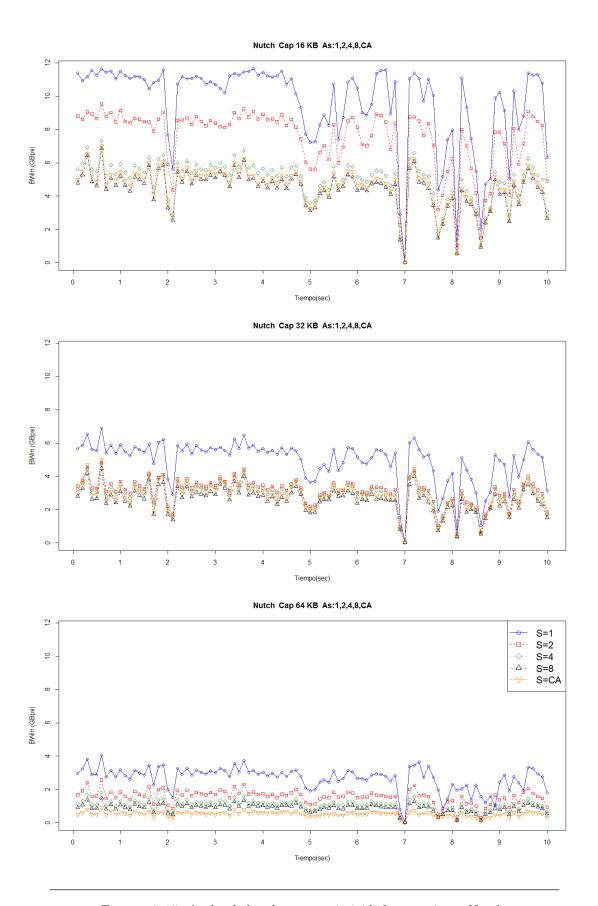

|    |      | 5.3.3.  | Nutch (Figura 5.15)                                                       | 35        |

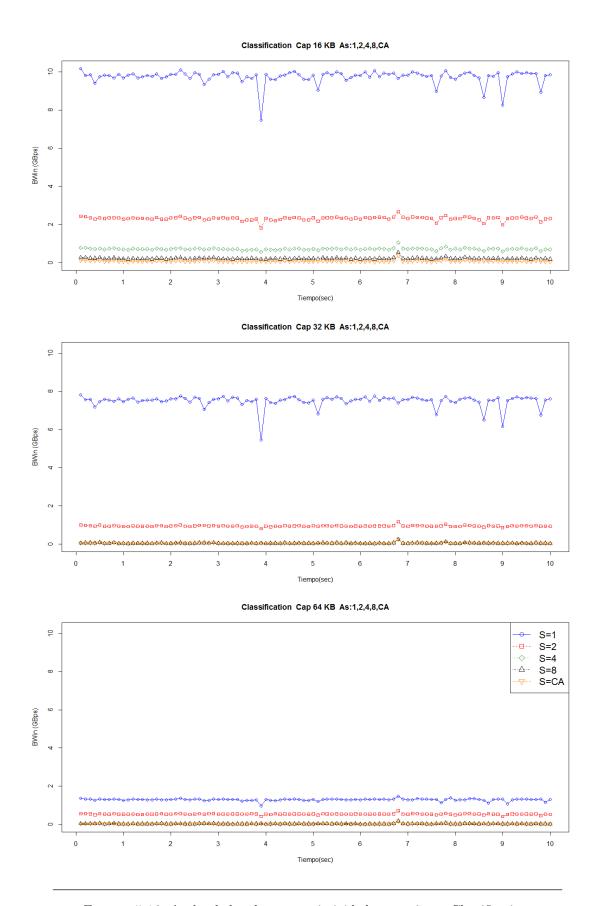

|    |      | 5.3.4.  | Classification (Figura 5.16)                                              | 35        |

|    |      | 5.3.5.  | Cloudstone (Figura 5.17)                                                  | 35        |

|    |      | 5.3.6.  | Conclusiones                                                              | 35        |

|    | 5.4. | Compa   | ración con otras cargas de trabajo                                        | 40        |

|    |      | 5.4.1.  | Conclusiones                                                              | 41        |

|    |      |         |                                                                           |           |

| 6. |      |         | nes y lineas abiertas                                                     | 44        |

|    |      |         | siones técnicas                                                           |           |

|    |      |         | abiertas                                                                  |           |

|    | 6.3. | Conclu  | siones personales                                                         | 46        |

|    |      |         |                                                                           |           |

|    |      | ъ       | W 1175                                                                    |           |

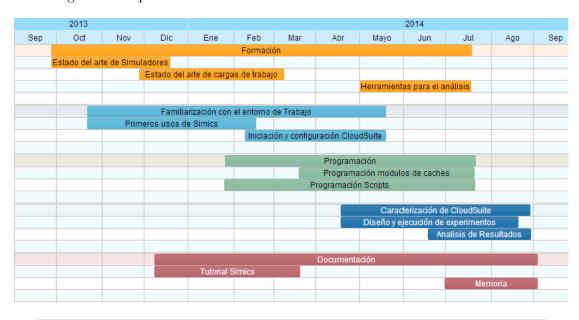

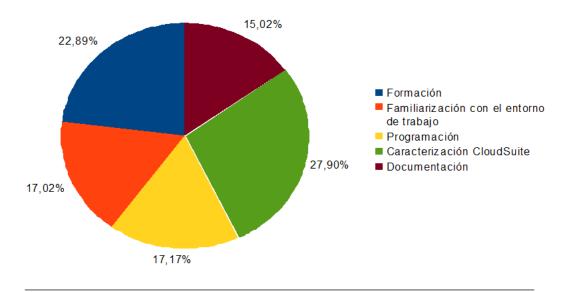

| Α. |      |         | esarrollo del Proyecto                                                    | 47        |

|    |      |         | n del tiempo                                                              |           |

|    |      |         | zo invertido                                                              |           |

|    |      |         | ción horas CPU                                                            |           |

|    | A.4. | Proble  | mas encontrados                                                           | 49        |

| в. | Pro  | ductivi | dad en Simics                                                             | 51        |

|    |      |         |                                                                           |           |

| С. |      |         | -Cache                                                                    | <b>58</b> |

|    |      |         | bre G-cache                                                               | 58        |

|    | C.2. | Algorit |                                                                           | 61        |

|    |      |         | Algoritmo para múltiples caches (algoritmo MC)                            | 61        |

|    |      | C.2.2.  | Algoritmo para cache completamente asociativa (algoritmo $\mathbf{CCA}$ ) | 63        |

| D. | Sim  | ulacion | nes CloudSuite                                                            | 66        |

| _• |      |         | ATPS                                                                      | 66        |

|    |      | Condo   |                                                                           | 67        |

|    |      |         |                                                                           | 67        |

|    |      | _       | Shell Scripts                                                             | 68        |

|    |      |         | Simics Scripts                                                            |           |

|    |      |         |                                                                           |           |

| Contenidos   | X |

|--------------|---|

| 701000100000 | A |

Bibliografía 72

# Índice de figuras

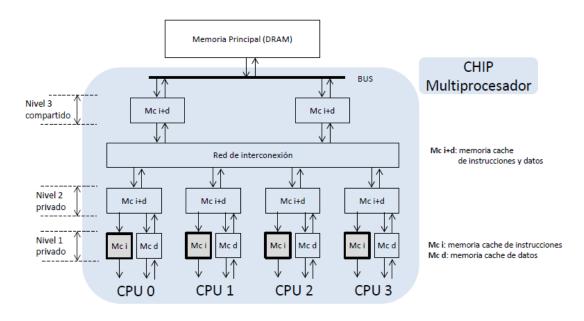

| 1.1.         | Ejemplo de chip multiprocesador contemporáneo                                                                                                                          | 2                               |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.1.         | Esquema de la aplicación Web Frontend                                                                                                                                  | 9                               |

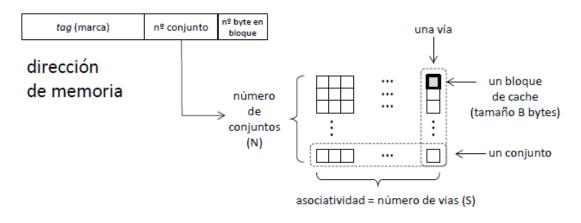

| 4.1.         | Memoria cache genérica de tamaño NxSxB bytes                                                                                                                           | 12                              |

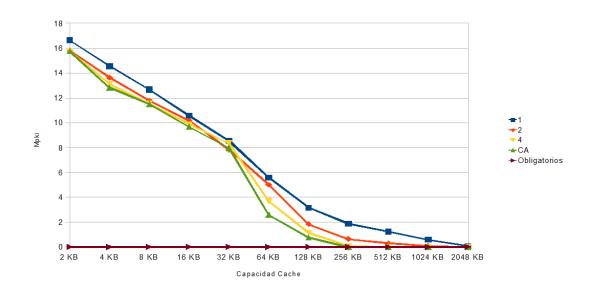

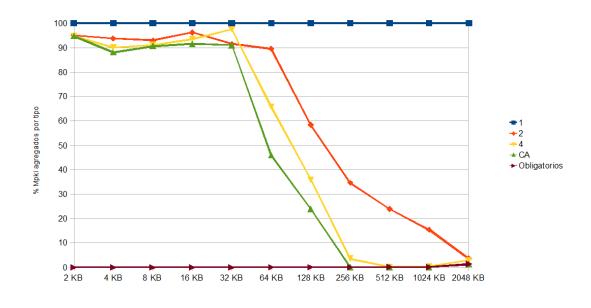

| 4.2.<br>4.3. | Ejemplo modelo de las 3C. Streaming, un procesador, 4,5 segundos Ejemplo modelo de las 3C con porcentajes agregados. Aplicación Media                                  | 14                              |

| 1 1          | Streaming, un procesador, 4,5 segundos de ejecución                                                                                                                    | <ul><li>14</li><li>15</li></ul> |

| 4.4.<br>4.5. | Sistema de cuatro procesadores simulado                                                                                                                                | 16                              |

| 4.5.<br>4.6. | Aciertos y fallos para una cache LRU con asociatividad 1                                                                                                               | 16                              |

| 4.0.<br>4.7. | Aciertos y fallos para una cache LRU con asociatividad 3                                                                                                               | 17                              |

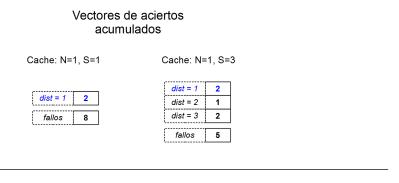

| 4.8.         | Vector de aciertos acumulados para S=1 y S=3                                                                                                                           | 17                              |

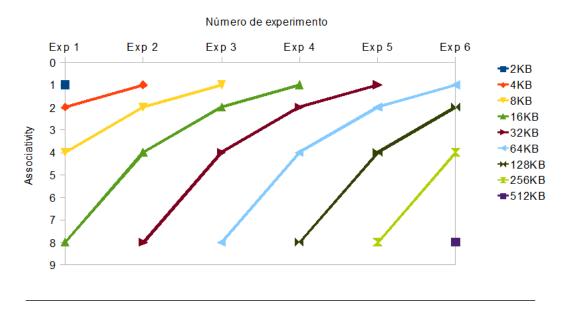

| 4.9.         | Experimentos lanzados con algoritmo de varias asociatividades                                                                                                          | 20                              |

| 1.0.         | Experimentos tanzados con argorrino de varias asociatividades                                                                                                          | 20                              |

| 5.1.         | Streaming: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B                                                             | 22                              |

| 5.2.         | Cassandra: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B                                                             | 23                              |

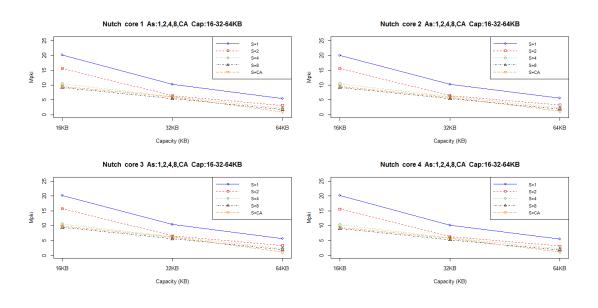

| 5.3.         | Nutch: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B                                                                 | 24                              |

| 5.4.         | Classification: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B                                                        | 24                              |

| 5.5.         | Cloudstone: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B                                                            | 26                              |

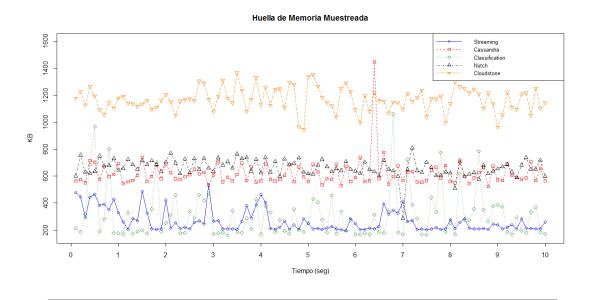

| 5.6.         | Huella de recarga de todas las aplicaciones de Cloudsuite. Cien muestras de $100 \text{ ms}$ . Tamaño en KB $(2^{10}) \dots \dots \dots \dots \dots \dots \dots \dots$ | 27                              |

| 5.7.         | Huellas acumuladas y de recarga de Streaming                                                                                                                           | 28                              |

| 5.8.         | Huellas acumuladas y de recarga de Cassandra                                                                                                                           | 28                              |

| 5.9.         | Huellas acumuladas y de recarga de Nutch                                                                                                                               | 29                              |

|              | Huellas acumuladas y de recarga de Classification                                                                                                                      | 30                              |

|              | Huellas acumuladas y de recarga de Cloudstone.                                                                                                                         | 30                              |

|              | Sistema simulado para calcular Bwin, el ancho de banda de instrucciones.                                                                                               | 31                              |

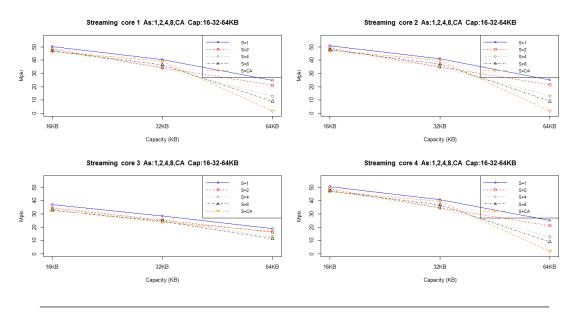

|              | Ancho de banda por asociatividad y tamaño en Streaming                                                                                                                 | 33                              |

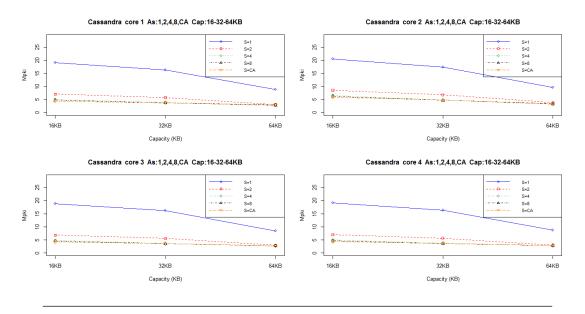

| 5.14.        | Ancho de banda por asociatividad y tamaño en Cassandra                                                                                                                 | 34                              |

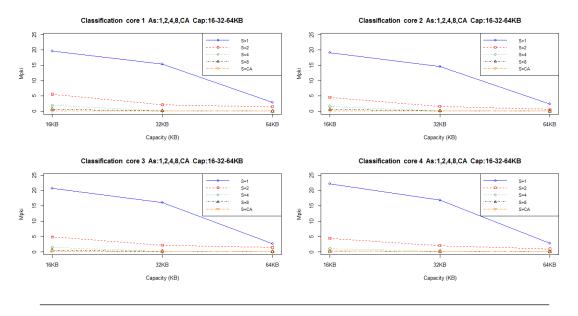

| 5.15.        | Ancho de banda por asociatividad y tamaño en Nutch                                                                                                                     | 36                              |

| 5.16.        | Ancho de banda por asociatividad y tamaño en Classification                                                                                                            | 37                              |

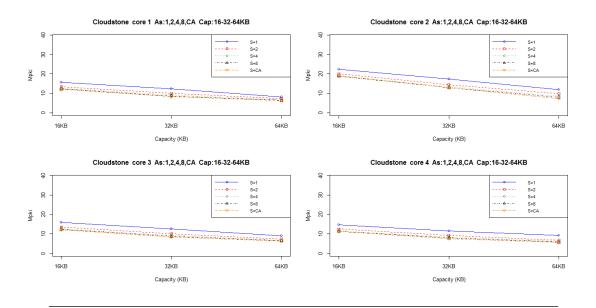

| 5.17.        | Ancho de banda por asociatividad y tamaño en Cloudstone                                                                                                                | 38                              |

Índice de Figuras XIII

| 5.18. Dos propuestas para mejorar el suministro de instruccion | es desde el si-   |    |

|----------------------------------------------------------------|-------------------|----|

| guiente nivel                                                  |                   | 39 |

| 5.19. Comparación MPKI benchmarks                              |                   | 42 |

| A.1. Diagrama de Gantt del proyecto                            |                   | 47 |

| A.2. Distribución del tiempo invertido en el proyecto          |                   | 49 |

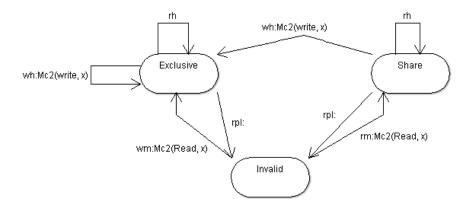

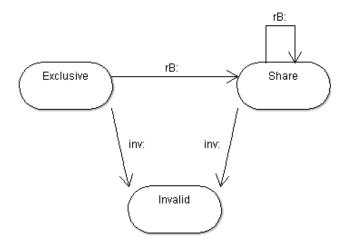

| C.1. Jerarquía de caches                                       |                   | 59 |

| C.2. Ejemplo Sistema de Caches multiprocesador con MESI        |                   | 59 |

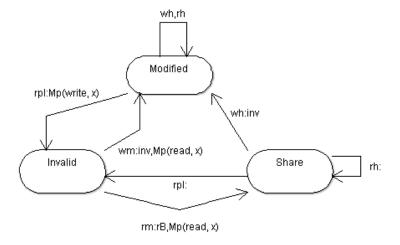

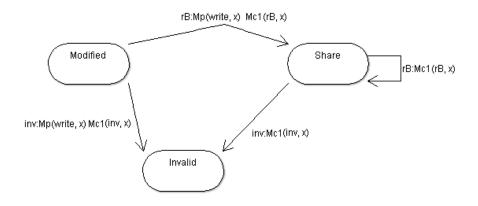

| C.3. Diagrama de Estados Cache Copy-Back Nivel 2 debido a e    | eventos internos. | 60 |

| C.4. Diagrama de Estados Cache Copy-Back Nivel 2 debido a e    | eventos externos. | 60 |

| C.5. Diagrama de Estados Cache Write-Through Nivel 1 debido    | a eventos in-     |    |

| ternos                                                         |                   | 60 |

| C.6. Diagrama de Estados Cache Write-Through Nivel 1 debido    | a eventos ex-     |    |

| ternos                                                         |                   | 61 |

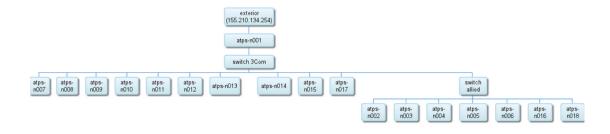

| D.1. Red de conexiones atps                                    |                   | 67 |

| D.2. Jerarquía de cache configurada con el script              |                   | 71 |

# Índice de tablas

| 3.1. | Aplicaciones CloudSuite 2.0 simuladas                                                | 8  |

|------|--------------------------------------------------------------------------------------|----|

| A.1. | Horas dedicadas a cada tarea del Proyecto                                            | 50 |

| C.1. | Relación de tamaño, asociatividad y aciertos para una ejecución con el algoritmo MC. | 63 |

# Capítulo 1

## Introducción

Las tendencias de mercado indican que el negocio de los procesadores para grandes centros de datos va a seguir creciendo, impulsado por la economía de la virtualización y la gran penetración empresarial y social de las aplicaciones que residen en las nubes (cloud computing).

Para diseñar un procesador de futuro adaptado a este mercado es necesario experimentar con una carga de trabajo apropiada, pero en la actualidad apenas existen programas de prueba (benchmarks) de esta clase. Una excepción es la denominada CloudSuite 2.0, un conjunto de aplicaciones cliente/servidor seleccionadas recientemente por el laboratorio de investigación Parsa de la EPFL en Suiza. Estas aplicaciones están pensadas para escalar en un centro de datos de forma horizontal (scale-out, es decir, con capacidad para aumentar el rendimiento a medida que se añaden mas computadores independientes) y se caracterizan por su paralelismo explícito y por manejar conjuntos de datos de tamaño muy considerable. Las aplicaciones seleccionadas pretenden ser representativas del futuro del cloud computing: Data Analytics, Data Caching, Data Serving, Graph Analytics, Media Streaming, SW Testing, Web Search y Web Serving [EPF].

La experimentación preliminar con estos programas de prueba, publicada en los congresos de arquitectura de computadores, ha revelado un uso intensivo y muy poco eficiente de la jerarquía de cache de instrucciones en chip [FAK<sup>+</sup>12]. Parece que no solo los conjuntos de datos son muy grandes, sino también el código que los manipula.

Una memoria cache es una memoria RAM estática (SRAM), pequeña y rápida que contiene un subconjunto de las direcciones referenciadas por el procesador. Su funcionamiento es automático, transparente al programador, y se basa en explotar la localidad temporal y espacial del acceso a memoria durante la ejecución de los programas. En los chips actuales de altas prestaciones las memorias cache ocupan una parte sustancial del

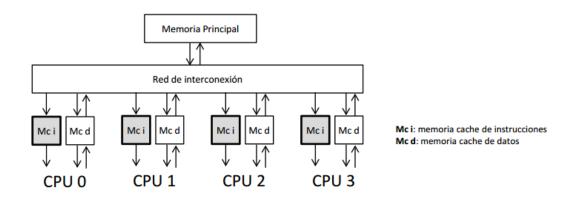

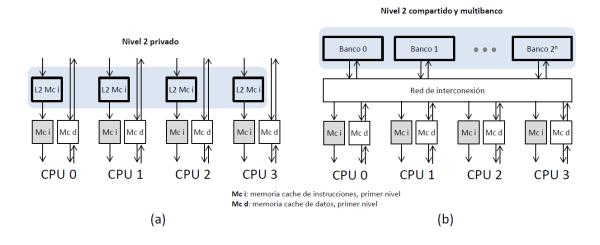

silicio, ya que la velocidad en la ejecución de los programas depende en gran medida del rendimiento de las caches. Las memorias cache dentro del chip se organizan como una jerarquía multinivel, ver figura 1.1. El primer nivel de memoria cache está separado en datos e instrucciones para cada procesador; el resto de niveles, hasta dos más, suelen contener de forma mezclada datos e instrucciones. Un buen diseño de la jerarquía de memoria cache permite acceder poco a la memoria principal RAM dinámica (DRAM) situada fuera del chip, contribuyendo de forma crítica a la ejecución eficiente de los programas.

FIGURA 1.1: Ejemplo de chip multiprocesador contemporáneo, con cuatro procesadores y tres niveles de memoria cache en chip (SRAM): los dos primeros privados de cada procesador, y el tercero compartido

En este proyecto nos planteamos una caracterización por simulación del comportamiento de las instrucciones en CloudSuite 2.0. Seguiremos una metodología de experimentación basada en Simics, un hipervisor de tipo 2 con capacidad de emulación de sistema completo: máquinas cliente y servidor con sus periféricos, sistemas operativos huésped (Oracle Solaris 11) y procesadores SPARC v9. Simics no está pensado para desplegar máquinas virtuales orientadas a la consolidación de servidores, sino al desarrollo y prueba de nuevos sistemas hardware y software. Esta orientación permite en nuestro caso configurar un sistema multiprocesador, capturar la secuencia de direcciones de instrucciones e inyectarla a un simulador de memoria cache. Si bien este tipo de simulación de sistema completo (aplicación y sistema operativo) es realmente lenta, la precisión de las conclusiones experimentales es muy elevada.

[Los resultados han sido...]

#### 1.1. Contexto del Proyecto

Este Proyecto Fin de Carrera se ha realizado con el soporte del grupo de investigación en Arquitectura de Computadores de la Universidad de Zaragoza (gaZ) y ha sido financiado en parte por el proyecto TIN2010-21291-C02-01 (Gobierno de España y Unión Europea) y por la dotación anual recibida como grupo consolidado de investigación en Aragón (ref. T48). Además, durante el curso 2013/2014 he disfrutado de una Beca de Colaboración del Ministerio de Educación destinada a la iniciación a la investigación.

#### 1.2. Objetivos

El objetivo de este Proyecto Fin de Carrera es analizar el comportamiento de las instrucciones en CloudSuite 2.0. Para ello se han realizado las siguientes tareas:

- Instalación y despliegue en cluster de los checkpoints necesarios para la simulación con Simics. Un checkpoint es un registro del estado de los procesadores, memorias y dispositivos de E/S en un instante dado.

- 2. Programación de un módulo muy ligero de simulación de cache de instrucciones, que reduce la sobrecarga de las herramientas convencionales de simulación de jerarquía de memoria (p.e. Multifacet GEMS Simulator de la U. de Wisconsin)

- 3. Análisis de tasas de fallos y de huella de memoria de instrucciones a lo largo de tiempos de ejecución significativos.

- 4. Conclusiones sobre comportamiento temporal a través de una simulación muestreada y sobre la efectividad de una jerarquía multinivel de instrucciones.

Tras llevar a cabo estas tareas se han alcanzado todos los objetivos inicialmente planteados. El valor añadido en este proyecto se concentra principalmente en los capítulos de resultados y conclusiones, dónde se analizan los resultados obtenidos por simulación.

#### 1.3. Organización de la Memoria

El resto del presente documento está organizado del siguiente modo: en el capítulo 2 se introduce el estado del arte en simulación y cargas de trabajo; en el capítulo 3 se explica con mayor detalle la suite Cloudsuite; el capítulo 4 explica la metodología utilizada para llevar a cabo los experimentos; en el capítulo 5 se presenta un resumen de los resultados

del proyecto y en el capítulo 6 se recogen las conclusiones y las posibles lineas abiertas. Se incluyen como anexos:

- A. Gestión del proyecto. Incluye la planificación del tiempo durante el proyecto y el esfuerzo invertido en el mismo.

- B. Productividad en Simics. Se adjunta un tutorial de Simics que sirva de documentación para futuros proyectos.

- C. Módulo G-cache. Se amplia la información sobre el módulo de g-cache y los módulos programados para el proyecto.

- D. Simulaciones Cloudsuite. Se presenta dónde y cómo se han llevado a acabo las simulaciones de la CloudSuite.

## Capítulo 2

# Estado del Arte en simulación y cargas de trabajo

La simulación es una herramienta fundamental para diseñar nuevo hardware o mejorar el rendimiento de los programas. En este capítulo describimos brevemente la plataforma Simics y el papel de los programas de prueba en la simulación de nuevas jerarquías de memoria.

#### 2.1. Plataformas y estrategias de simulación

Simics de la empresa Virtutech (simplemente Simics a partir de ahora) es un simulador de sistema completo que podemos configurar para modelar multiprocesadores, sistemas empotrados, routers de telecomunicaciones, clusters o redes de esos elementos [MCE<sup>+</sup>02]. Es capaz de ejecutar sistemas operativos sin necesidad de que sean adaptados y simular aplicaciones realistas ofreciendo resultados precisos. Se trata de un hipervisor comercial de tipo 2, puede ejecutarse sobre múltiples procesadores y sistemas operativos, y el código no es libre. En la comunidad de experimentación en arquitectura de computadores, Simics suele utilizarse conjuntamente con el entorno GEMS (General Execution-Driven Multiprocessor Simulator) [MSB<sup>+</sup>05], que fue creado en la Universidad de Wisconsin y proporciona módulos para el estudio de prestaciones en sistemas multiprocesador de memoria compartida con jerarquías complejas y coherentes de memorias cache. El componente principal de GEMS se llama Ruby, que simula las memorias cache, el protocolo de coherencia y la red de interconexión. Simics actúa como un simulador funcional, es decir, simplemente se ocupa de ejecutar las instrucciones, y se comunica con el módulo Ruby de GEMS, que se encarga de gestionar los accesos a memoria, temporizándolos de forma adecuada.

Un problema muy importante en la simulación de multiprocesadores es el bajo rendimiento del simulador, y esto es especialmente cierto en Simics, que como ya hemos dicho es una máquina virtual de sistema completo. Según el detalle temporal (precisión) de la simulación, las aplicaciones se ejecutan entre 100 y 1000 veces más lentas que en la máquina real. En nuestro caso estamos interesados en muy largas simulaciones de fallo-s/aciertos, sólo para la cache de instrucciones y no nos importa el detalle temporal. Por ello hemos escogido una solución de menos sobrecarga, aunque conllevará la necesidad de un mayor esfuerzo de programación. La solución escogida ha sido el módulo g-cache (que explicaremos en el apartado 4.3), cuyo código fuente acompaña a la distribución estándar de Simics.

#### 2.2. Cargas de Trabajo

Se llama benchmark al programa de prueba que sirve para evaluar el rendimiento de un computador completo o de uno de sus subsistemas. [Bon07]. Un conjunto de benchmarks se denomina suite. Históricamente los programas de prueba han evolucionado en complejidad, desde los primeros programas sintéticos, pasando por pequeñas rutinas intensivas en cálculo o memoria, hasta los programas reales de la actualidad, representativos de un campo informático determinado.

La selección de la carga de trabajo tiene una gran importancia, puesto que queremos obtener conclusiones que sirvan para el diseño de los computadores del futuro. Veamos algunas suites actuales:

- PARSEC 2.1: suite compilada por la universidad de Princeton (Princeton Application Repository for Shared-Memory Computers, 2009-10). Está compuesta por trece aplicaciones paralelas de memoria compartida (multithreaded applications). Ofrece aplicaciones paralelas típicas, por ejemplo de High-Performance Computing (HPC), pero también incluye otro tipo de aplicaciones paralelas emergentes (p.e. escritorio y servicio WEB). Recoge distintas dominios de aplicación, como visión por computador, codificación de vídeo, análisis financiero, visualización de experimentos físicos y proceso de imagenes.[BKSL08]

- SPEC CPU2006: suite compilada por la cooperativa SPEC en 2006 (Standard Performance Evaluation Corporation). Está pensada para medir el rendimiento del procesador, la jerarquía de memoria o el compilador, puesto que no tiene apenas operaciones de entrada/salida. Contiene dos suites de benchmarks, una intensiva en cálculo entero (12 programas no paralelos) y otra en coma flotante (19 programas no paralelos). [CPU06]

- SPECweb 2009: también de la cooperativa SPEC, busca evaluar el rendimiento de servidores WEB. Sus cargas de trabajo están pensadas para multiprocesadores de memoria compartida e incluyen aplicaciones de banca, comercio electrónico o soporte Web.[web09]

- TPC-C: aplicación patrocinada por la cooperativa Transaction Processing Council desde 1992. En la actualidad está en su versión cinco, y simula un entorno completo de usuarios realizando transacciones en directo (online) hacia una base de datos. Aunque no se limita a ninguna actividad en particular modela una empresa que debe gestionar, vender y/o distribuir un producto o servicio. [TC]

Los anteriores benchmarks son un buen resumen de aplicaciones que se están ejecutando en los computadores actuales. Sin embargo, unos nuevo tipo de aplicación está emergiendo con fuerza en los últimos años: los servicios de la nube (cloud computing). Esta plataforma está dominando el suministro de servicios escalables online. Estos servicios se caracterizan por unos enormes working-sets, un alto grado de paralelismo y restricciones de tiempo real no estricto. Todo esto hace que estas aplicaciones denominadas scale-out tengan un comportamiento distinto a las aplicaciones tradicionales ya conocidas y que se recogen en los benchmarks anteriores. Por ello, para estimular la investigación en el área de los centros de datos y la nube y ya que apenas existen benchmarks de esta clase, el laboratorio de investigación Parsa de la EPFL en Suiza ha creado CloudSuite, un benchmark basado en servicios online del mundo real [FAK+12]. Esta es la carga de trabajo que hemos seleccionado para nuestro proyecto, por lo que explicamos sus características con más detalle en el capítulo siguiente.

# Capítulo 3

# CloudSuite

Como ya hemos introducido en el capítulo anterior, la carga de trabajo que usamos en este trabajo es Cloudsuite 2.0, un conjunto de aplicaciones cliente/servidor del grupo de investigación Parsa de la EPFL en Suiza. Estas aplicaciones están pensadas para escalar en un centro de datos de forma horizontal ( scale-out: a más servidores físicos, más rendimiento) y se caracterizan por su paralelismo explícito y por manejar conjuntos de datos de tamaño muy considerable. Aunque en su web podemos encontrar disponibles 8 aplicaciones para ejecutar en nativo [EPF], nosotros hemos trabajado solo con 5, aquellas acompañadas de checkpoints públicos para la simulación en Simics. En la tabla 3.1 podemos ver las aplicaciones con una breve descripción:

| Aplicación | Descripción                                                              |  |

|------------|--------------------------------------------------------------------------|--|

| Data       | Esta aplicación se basa en el paradigma map-reduce, que ha emergido      |  |

| Analytics  | como una aproximación muy popular para los análisis de datos a gran      |  |

|            | escala. Se lanzan peticiones al cluster de procesadores que se simulan,  |  |

|            | que en primer lugar filtran y transforman la información (map) y después |  |

|            | unen los resultados (reduce).                                            |  |

| Data       | Aplicación de almacenamiento y servicio de datos basada en NoSQL         |  |

| Serving    | (Not only SQL). Ha sido diseñada explícitamente para soportar aplica-    |  |

|            | ciones web como Facebook, Google Earth y Google Finance, proporcio-      |  |

|            | nando almacenamiento escalable, con capacidad de adaptar rápidamente     |  |

|            | el esquema de almacenamiento.                                            |  |

| Media      | Los servicios en streaming, tipo Youtube, usan enormes clusters de ser-  |  |

| Streaming  | vidores que gradualmente empaquetan y transmiten ficheros multimedia     |  |

|            | cuyo tamaño puede ir desde los megabytes hasta los gigabytes.            |  |

| Web        | Las aplicaciones que dan servicio al alojamiento de páginas web se ca-   |  |

| Frontend   | racterizan por su gran tolerancia a fallos y su escalabilidad dinámica.  |  |

| Web        | Aplicación basada en un motor de búsqueda, similar a Google, capaz de    |  |

| Search     | indexar terabytes de datos recogidos dinámicamente de fuentes online.    |  |

Tabla 3.1: Aplicaciones CloudSuite 2.0 simuladas.

#### 3.1. Características de los Benchmarks

Todas estas aplicaciones tienen unas características similares [FAK<sup>+</sup>12]:

- Operan con grandes conjuntos de datos que se reparten entre un gran número de máquinas, típicamente en fragmentos residentes en las memorias principales de los servidores.

- Sirven grandes cantidades de peticiones completamente independientes que no comparten ningún estado.

- Están diseñadas específicamente para una infraestructura de servidores típica de la nube, donde las conexiones y las máquinas no son del todo fiables.

- Usan conectividad entre máquinas solo para las tareas más importantes de coordinación y administración.

En algunas aplicaciones de esta suite llegamos a simular hasta tres computadores completos conectados por red, como es el caso de Web Frontend, cuyo esquema está representado en la figura 3.1. Este benchmark consiste en tres componentes principales: el servidor web, la base de datos y un cliente, cada una es ejecutada en una máquina distinta y emulan los accesos del mundo real al servidor web. Todo este sistema simulado nos permite estudiar las instrucciones del servicio crítico: el servidor web que se ejecuta en una máquina multiprocesador, de cuatro procesadores en nuestro caso.

FIGURA 3.1: Esquema Aplicación Web Frontend.

#### 3.2. Cloudsuite en Simics

Como ya se ha apuntado, únicamente se disponen de forma pública los checkpoints para Simics de las cinco aplicaciones de la tabla 3.1. Los checkpoints permiten empezar una simulación en un punto de interés, sin necesidad de configurar todo de nuevo, arrancar la máquina, y saltar la fase de inicialización. Un checkpoint almacena el contenido de los registros de los procesadores, de las MMUs, la imagen de la memoria principal, los contenidos de los discos y el estado de los periféricos (consola, conexiones de red, etc.). En nuestro caso un checkpoint consiste en varios ficheros que contienen la configuración del sistema simulado (máquinas para los clientes, para la base de datos y para el servidor bajo análisis) en un estado estacionario de la ejecución, saltando la fase de inicialización del sistema que queremos analizar. Para desplegar los checkpoints en ATPS, nuestro cluster de experimentación, ha sido necesario configurar las rutas que referencian a los diferentes ficheros de un checkpoint: datos de entrada de la aplicación simulada, configuración hardware de las máquinas, e imagen del estado hardware en el punto de inicio de la simulación.

# Capítulo 4

# Metodología

Este capítulo recoge la metodología utilizada durante el proyecto. Se presentan las métricas seleccionadas, las herramientas que se han elegido para obtenerlas y cómo se han usado.

#### 4.1. Métricas Utilizadas

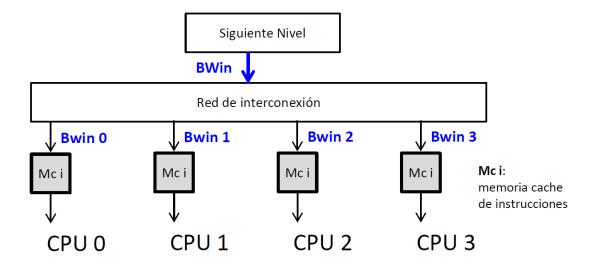

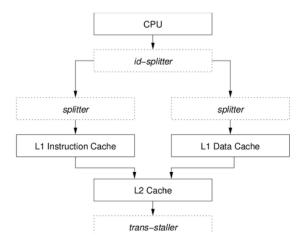

Estamos interesados en estudiar el rendimiento de la cache de instrucciones, en un sistema multiprocesador de memoria compartida, centrándonos en la máquina que ejecuta el servicio crítico en las cinco aplicaciones seleccionadas de CloudSuite 2.0. El sistema de interés es el representado en la figura 4.4.

Como se verá en el capítulo siguiente, para analizar el comportamiento durante un tiempo significativo, hemos optado por obtener estadísticas de forma periódica. El conjunto de métricas que obtenemos en cada muestra temporal, para cada procesador, forma una traza temporal que almacenamos para manipulaciones posteriores. De esta forma, podremos estudiar la variación en el tiempo o calcular un agregado, según la escala temporal que nos interese considerar.

A continuación describimos las métricas y modelos que vamos a usar para analizar el cómo se referencian las instrucciones y obtener, si es posible, conclusiones de diseño.

■ Mpki : Número medio de fallos de la cache de instrucciones por cada mil instrucciones ejecutadas (*Misses per kilo instruction*), en este trabajo nos centramos de la cache de instrucciones de primer nivel. Recordemos que cada vez que se produce un fallo, entra el bloque de cache requerido, de 64 bytes.

- **BWin**: Ancho de banda de instrucciones (*Instruction Bandwidth*) entrante desde el siguiente nivel. Se agrega para las cuatro caches. Es el cociente entre el número de bytes de instrucciones entrante a las caches y el tiempo de ejecución.

- Huella de memoria de instrucciones: (*Instruction Footprint*) Tamaño del programa referenciado durante la ejecución, en número de bytes. Se trata de contar instrucciones *diferentes*. Por ejemplo, un bucle de diez instrucciones que se repite 1000 veces supone una huella de 40 bytes (10 instr. x 4 bytes/instr.)

#### 4.2. Modelo de las 3C

El "modelo de las 3C" (compulsory, capacity, and conflict) es uno de los más usados y conocidos para el estudio de los fallos en las memorias caches [HS89]. Para entender el modelo, en la figura 4.1 se presenta una memoria cache genérica, con los parámetros de diseño a tener en consideración.

FIGURA 4.1: Memoria cache genérica de tamaño NxSxB bytes. Se escogen  $log_2N$  bits de la dirección para indexar conjunto. En caso de fallo, si el conjunto correspondiente está lleno, se reemplaza al bloque menos recientemente usado (LRU).

El modelo se basa en tres tipos de fallos:

- Obligatorios (Compulsory): Son los producidos por la primera referencia de un bloque en memoria. Este número no se ve afectado por la asociatividad o el tamaño de la memoria cache. Estos fallos corresponderían a los fallos que tendría una cache completamente asociativa (un solo conjunto) de tamaño infinito, y contabilizan el número total de bloques que se cargan desde el siguiente nivel.

- De Capacidad (Capacity): Son aquellos fallos que se dan en una cache completamente asociativa con política de reemplazo LRU (least recently used), menos los fallos obligatorios. Estos fallos aparecen por referenciar mayor cantidad de bloques

que los que caben en la memoria, por lo tanto estos fallos dependen del tamaño de la cache.

■ **De Conflicto (Conflict)**: Son los fallos totales de la cache *menos* los de capacidad y los obligatorios. Son dependientes de la asociatividad, ya que corresponden aquellos fallos que se dan por tener que alojar bloques en el mismo conjunto.

Para representar este modelo se obtienen los fallos para distintos tamaños de cache con distintas asociatividades, incluyendo siempre la completamente asociativa y la correspondencia directa (o asociatividad 1).

En las gráficas 4.2 y 4.3 vemos un ejemplo de las dos representaciones habituales del modelo para la cache de instrucciones de la aplicación Media Streaming con un único procesador, los primeros 4'5 segundos de ejecución y con 32B de tamaño de bloque. Ambas gráficas muestran fallos en función de la capacidad, desde 2 hasta 2048 KB en el eje X. El eje Y representa tasa de fallos en mpki o porcentaje relativo de cada tipo de fallos, respectivamente. En la primera gráfica se observa como las tasas de fallos disminuyen desde los 15-17 mpki para 2KB, hasta una cifra inapreciable para 2 MB. Para 64 KB, por ejemplo, podemos ver cual es la penalización por disminuir asociatividad: pasamos progresivamente de los 2,57 mpki en completamente asociativo, hasta los 5,6 mpki de correspondencia directa. En la gráfica 4.3 vemos los porcentajes relativos; para la cache de 64 KB los fallos obligatorios suponen una porcentaje no apreciable, mientras que al disminuir la asociatividad (desde completamente asociativo hasta S=1, pasando por S=4 y 2), los fallos suponen el 46 %, 65,9 %, 89,5 % y 100 %, respectivamente. Dicho de otra forma, manteniendo el tamaño fijo a 64 KB, si cambiamos la organización de la cache y pasamos de S=1 (N = 1024 conjuntos) a S=2 (N = 512 conjuntos), los fallos bajan aproximadamente un 10%.

La gráfica 4.2 ilustra una anomalía que no suele aparecer en caches de datos y a veces se observa en caches de instrucciones. Vemos que en la cache de 32KB hay más fallos para asociatividad 4 que para asociatividad 2. En principio la intuición dice que a mayor asociatividad, menos fallos de conflicto, y menos fallos totales (por cierto, a mayor asociatividad una cache requiere mas energía por acceso y resulta en un mayor tiempo de acierto). Sin embargo, en el punto reseñado no es así, ¿porqué?. Consideremos un ejemplo extremo: dos caches de T bloques, una de correspondencia directa (S=1) y otra completamente asociativa (N=1). Supongamos un bucle de instrucciones cuyo tamaño supera en un bloque al tamaño de la cache, es decir, T+1 bloques. En régimen permanente la cache de correspondencia directa se carga con T-1 bloques que no se mueven, pero hay un conjunto al que van a parar dos bloques en cada iteración; el resultado es una tasa de fallos muy baja: 2 fallos cada Tx16 referencias (64 Bytes = 16 instrucciones). En

cambio, en la cache completamente asociativa, debido al algoritmo de reemplazo LRU, el régimen permanente resulta en T fallos cada Tx16 referencias, ya que las últimas referencias sobrescriben a las primeras, las primeras a las segundas y así sucesivamente

FIGURA 4.2: Ejemplo modelo de las 3C con mpki. Aplicación Media Streaming, un procesador, 4,5 segundos de ejecución.

FIGURA 4.3: Ejemplo modelo de las 3C con porcentajes agregados. Aplicación Media Streaming, un procesador, 4,5 segundos de ejecución.

En nuestro proyecto hemos simulado un sistema de cuatro procesadores tal como se puede ver en la figura 4.4. Para caracterizar caches en sistemas multiprocesador puede usarse el modelo ampliado de las 4C [CGS99]. La cuarta fuente de fallos (coherence) proviene de las invalidaciones necesarias para mantener la coherencia, sin embargo este tipo de fallos no aparece en el flujo de instrucciones, que no están sometidas a escrituras compartidas.

FIGURA 4.4: Sistema de cuatro procesadores simulado. Las memorias cache de instrucciones han sido modeladas en detalle.

#### 4.2.1. Algoritmos de una sola pasada

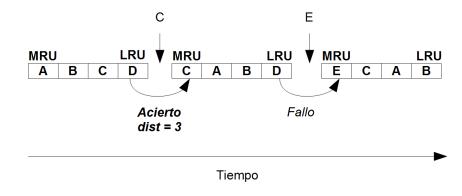

Para construir las gráficas 4.2 y 4.3 podemos ejecutar una simulación por cada tamaño de cache y por cada asociatividad. Sin embargo este procedimiento requiere mucho tiempo de simulación. Alternativamente, podemos usar un algoritmo "de una sola pasada" que nos permite en una sola simulación obtener los fallos para distintas asociatividades y tamaños de cache [MGST70]. Estos algoritmos son factibles para políticas de reemplazo de tipo pila, para los cuales aumentar la asociatividad manteniendo el número de conjuntos siempre resulta en una tasa de aciertos mayor. La política de reemplazo LRU (Least Recently Used) cumple esta condición. LRU precisa una pila ordenada en cada conjunto. En la cima de la pila está el bloque mas recientemente utilizado (MRU, Most Recently Used), y en el fondo el menos recientemente utilizado (el LRU), es decir el bloque que será víctima en caso de reemplazo. En la figura 4.5 se ilustran los casos de acierto y fallo a un conjunto cualquiera. Se puede ver el estado original de la pila LRU del conjunto, y su nuevo estado al llegar una referencia al bloque C. Cómo ya está en el conjunto se produce un acierto a distancia 3 en la pila y este bloque pasa a ser el MRU. La siguiente referencia que llega es al bloque E, que no está en la cache, por lo tanto se

produce un fallo. El bloque víctima, el que se expulsa, será el LRU, es decir el bloque D. Y el bloque E queda en la cima de la pila, es decir la posición MRU.

FIGURA 4.5: Pila de bloques en orden LRU en un conjunto cualquiera. Acierto en el bloque C seguido de fallo del bloque E.

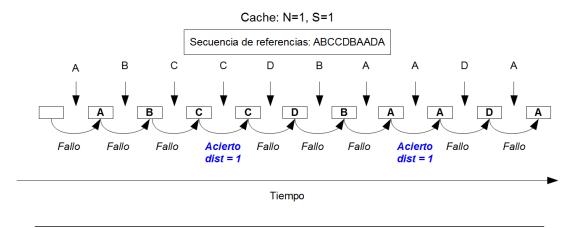

Analizando la pila ordenada de bloques de un conjunto cualquiera, vemos que el acierto a distancia 1 de la cima (la propia cima) se produce si un bloque vuelve a referenciarse inmediatamente. El acierto a distancia 2 se produce si entre dos referencias al mismo bloque se referencia uno distinto. Aplicando este razonamiento de forma sucesiva se puede demostrar que, manteniendo fijo el número de conjuntos, una cache de asociatividad S experimenta los mismos o mas aciertos que una cache de asociatividad S-1, ya existe una relación de inclusión entre los contenidos de la cache de asociatividad S y la cache de asociatividad S-1. Esta relación es más fácil de apreciar a través de un ejemplo, para ello vamos a ayudarnos de las figuras 4.6 y 4.7. En ambas el tiempo transcurre de izquierda a derecha. Entre estado y estado aparece en la parte superior cual es el bloque referenciado y en la parte inferior si se produce acierto o fallo. En el caso de acierto se apunta también a que distancia de la cima de la pila LRU se ha producido.

FIGURA 4.6: Aciertos y fallos para una cache LRU con asociatividad 1

FIGURA 4.7: Aciertos y fallos para una cache LRU con asociatividad 3

En la primera figura, la 4.6, se representa una cache de un solo bloque, y de un solo conjunto, así que si inmediatamente no se referencia al mismo bloque, se produce un fallo. En el caso de que se produzca un acierto este siempre es a distancia 1, ya que la pila LRU del conjunto solo tiene un elemento. En el vector de la izquierda de la figura 4.8 podemos ver el resumen de los aciertos y fallos totales de la secuencia de referencias utilizada (ABCCDBAADA).

Figura 4.8: Vector de aciertos acumulados para S=1 y S=3

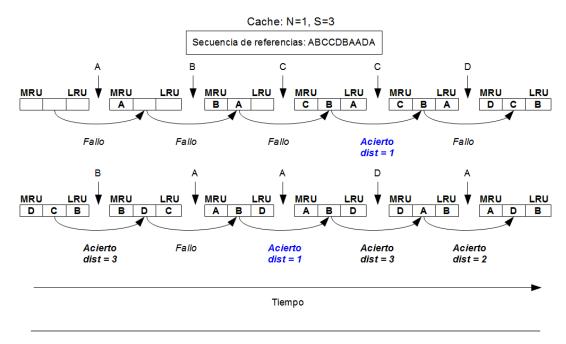

Sin embargo la secuencia de estados en la figura 4.7 se complica, ya que corresponde a una cache de un solo conjunto, pero de asociatividad 3. Ahora aparecen aciertos a distancias 1, 2 y 3. Aquí se aprecia lo que explicábamos anteriormente, por ejemplo, el último acierto se da a distancia 2 porque entre la última referencia al bloque A y la anterior referencia solo se ha referenciado al bloque D. O en el penúltimo acierto, que se da a distancia 3 porque entre la última vez que se referencia a D y la anterior sólo se han

referenciado dos bloques: el A y el B. En el vector de la derecha de la figura 4.8 recogemos el número total de fallos y de aciertos, estos últimos clasificados por distancias.

Gracias a las figuras y a las tablas ahora podemos ver mejor porque los aciertos de asociatividad 1 de una cache están incluidos en los aciertos de una cache con el mismo número de conjuntos pero mayor asociatividad. Los aciertos a distancia 1 del vector S=3 en 4.8 son los correspondientes a los aciertos de la cache de asociatividad 1 de la figura 4.6 para esa secuencia de referencias a bloques.Y llegamos a la conclusión de que no es necesario representar una cache de asociatividad 2 con 2 bloques, y un solo conjunto, para saber su número de aciertos ya que la cache de asociatividad 2 incluirá los de la 1 (2 aciertos) más los de distancia 2 del vector S=3 en 4.7 de la cache de asociatividad 3. Es decir, para la cache de un conjunto y asociatividad 2 el número de aciertos será 3, y por lo tanto el número de fallos 7, ya que en total hay 10 referencias a bloques.

Asumiendo reemplazo LRU, ¿cómo concretar estas ideas en un algoritmo?. Una forma es gestionar un *vector de aciertos* que contabiliza cuantos aciertos se dan en cada distancia. El algoritmo en detalle puede consultarse en el anexo C.2.1.

Con este algoritmo podemos obtener, por ejemplo, a partir de la simulación de una cache de 16KB de asociatividad 4, los aciertos (y por lo tanto también los fallos) de una cache 8KB con asociatividad 2, y de una cache de 4KB con asociatividad 1.

#### 4.3. Módulo G-Cache

#### 4.3.1. Módulos en Simics

Un módulo en Simics es un código ejecutable que se carga dinámicamente en la máquina virtual. Para tener un uso práctico debe interactuar con Simics, con otros módulos o con el usuario. Simics proporciona una API (application programming interface) para que los módulos puedan utilizar diversas funciones. La API soporta los conceptos de clase, objeto, interfaz y evento. Los módulos pueden programarse en DML (Device Modeling Language), Python o C/C++.

En este proyecto hemos trabajado modificando un módulo ya definido por Simics, g-cache, que se explica a continuación.

#### 4.3.2. G-cache

Simics es una máquina virtual con capacidad de ejecución funcional de sistema completo, tanto de aplicaciones como de sistema operativo. Por tanto no modela las cuestiones de

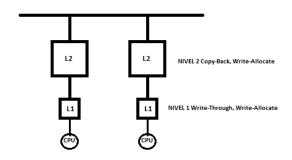

implementación transparentes al lenguaje máquina, como la jerarquía de caches. Sin embargo, incorpora a modo de ejemplo el módulo g-cache que permite modelar una jerarquía multinivel de caches para multiprocesador. G-cache trata las transacciones de memoria de forma simple: todas las operaciones necesarias (copy-back de bloques sucios de datos, fetch de instrucciones, etc.) se ejecutan en orden de programa y una sola vez. La cache devuelve la suma de los ciclos de parada para cada operación. Hemos modificado este modulo para programar de forma eficiente nuestras caches de instrucciones. Las dos versiones programadas tienen la siguiente funcionalidad:

- Algoritmo para múltiples caches (algoritmo MC): Se aplica la idea del apartado 4.2.1 para recoger en una simulación única los fallos de varias asociatividades y tamaños.

- Algoritmo para caches completamente asociativas (algoritmo CCA): Ya que las caches completamente asociativas solo tienen un conjunto, los algoritmos tradicionales de reemplazo LRU es muy costoso de simular para caches grandes, por tener que recorrer toda la lista LRU una o varias veces cada vez que se produce un fallo. La mejora original que proponemos es utilizar una cache de correspondencia directa auxiliar, que permite capturar una gran parte de los aciertos, evitando tener que buscar el bloque en la cache simulada. Hemos medido una mejora media en velocidad de un 90,52 % gracias a esta mejora.

En el Anexo C se describen en detalle los dos algoritmos.

#### 4.4. Experimentos

En este trabajo hemos lanzado 6 experimentos con el algoritmo MC, y 5 experimentos con el algoritmo CCA, por cada aplicación. La gráfica 4.9 muestra los seis primeros experimentos y a qué cache (asociatividad y tamaño) corresponden los resultados obtenidos, cuatro caches distintas por cada experimento. Así que con seis ejecuciones hemos obtenido los datos de 24 caches distintas, suponiendo una muy importante mejora.

El algoritmo CCA se ha ejecutado para las caches de 16KB, 32KB y 64KB, para las que ya disponemos resultados desde asociatividad 1 a 8, pudiendo así completar el modelo de las 3Cs.

El cuarto experimento con este algoritmo corresponde a la simulación de una cache de 2048KB. Esta cache que al ser lo suficientemente grande nos permite contabilizar los fallos obligatorios.

FIGURA 4.9: Experimentos lanzados con algoritmo MC.

Cada uno de los experimentos anteriores supone 10 segundos (tiempo en máquina real) de cada aplicación, recogiendo muestras cada 100ms, es decir se obtienen 100 muestras por cada experimento y aplicación. Antes de cada muestra las caches y sus estadísticas se inicializan.

Por último, el quinto experimento con el algoritmo CCA corresponde a la obtención de los fallos obligatorios a lo largo de los 10 segundos (tiempo en máquina real) sin inicializar las caches ni las estadísticas y recogiendo los datos cada  $100 \mathrm{ms}$ . El experimento se ha lanzado con un tamaño de  $2048 \mathrm{KB}$  para todas las aplicaciones excepto para Classification y Cloudstone que ha sido de  $4096 \mathrm{KB}$  y  $8192 \mathrm{KB}$ , respectivamente.

# Capítulo 5

## Resumen de Resultados

En este capitulo se recogen los resultados de los experimentos realizados, siguiendo las métricas presentadas en el apartado 4.1.

Los resultados se estructuran en tres apartados; el primero muestra las tasas de fallos promediadas para todos los cores en toda la duración de las aplicaciones; el segundo presenta la huella de memoria, estudiando su evolución temporal en intervalos de 100ms; el tercer apartado presenta el ancho de banda agregado que debe suministrar el siguiente nivel, también analizando intervalos de 100 ms. Al final de cada apartado se ofrecen unas conclusiones de comportamiento y, en su caso, de diseño.

#### 5.1. Mpki por Core

Las gráficas presentadas en esta sección (5.1 - 5.5) resumen el comportamiento de las caches de instrucciones en cuanto a su tasa de fallos expresada en mpki, en función de su tamaño y de su asociatividad, para un tamaño de bloque de 64 bytes. Para cada tamaño de cache y para cada core hemos calculado la media aritmética de todas las muestras temporales<sup>1</sup>.

En estas gráficas observaremos la importancia relativa del tamaño y la asociatividad en la tasa de fallos, así como la posible diferencia de comportamiento entre cores.

<sup>&</sup>lt;sup>1</sup>Estos datos, junto con los del siguiente apartado, permiten descomponer los fallos según el modelo de las 3Cs. No se ha hecho así porque la anomalía de asociatividad aparece, y entonces la representación pierde utilidad.

### 5.1.1. Streaming (Figura 5.1)

Destaca la diferencia de comportamiento entre cores: el core 3 es menos sensible a la asociatividad y al tamaño (rango total 35-20 mpki), mientras que los cores 1,2 y 4 tienen comportamientos casi idénticos, presentando unas tasas altas para 16KB (45-50 mpki) y mucha sensibilidad a la asociatividad para 64 KB.

En los dos grupos de cores aparece la anomalía de asociatividad. Para el core 3, en 64 KB solo la correspondencia directa es peor que completamente asociativo. Para el resto de cores ocurre algo muy parecido, pero para 32 KB.

Resaltemos esto: la mejor elección de asociatividad se invierte por completo, según el tamaño y el core considerados, lo cual no es nada bueno desde el punto de vista de diseño. Escoger una asociatividad 4-8 para todos los cores y tamaños, podría ser un buen compromiso de diseño.

En definitiva, estamos frente a una aplicación cuya búsqueda de instrucciones puede convertirse en el cuello de botella del procesador si el tamaño de cache es insuficiente o la asociatividad no es la apropiada.

FIGURA 5.1: Streaming: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B.

#### 5.1.2. Cassandra (Figura 5.2)

En esta aplicación basta con descartar diseños de correspondencia directa para obtener un muy buen rendimiento (4-5 mpki), independientemente del tamaño y del core considerado. En cuanto a comportamiento de cache, parece que esta aplicación paralela

usa el mismo código en los cuatro procesadores. No se observa ninguna anomalía de asociatividad, y la sensibilidad de los fallos al tamaño de cache es reducida.

FIGURA 5.2: Cassandra: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B.

### 5.1.3. Nutch (Figura 5.3)

Buen aprovechamiento de la capacidad y de la asociatividad: al aumentar tamaño de 16KB a 64 KB, nos movemos desde la franja 20-10 mpki a 5-1 mpki, para asociatividades entre 1 y CA, respectivamente. Todos los cores parecen ejecutar el mismo código.

#### 5.1.4. Classification (Figura 5.4)

Podemos apreciar una gran diferencia entre asociatividad 1 y el resto. Independientemente del tamaño, a partir de asociatividad 4-8, la tasa de fallos es inapreciable. Todos los cores parecen ejecutar el mismo código.

#### 5.1.5. Cloudstone (Figura 5.5)

El core 2 presenta una tasa de fallos (20-15 mpki) superior al resto (15-20 mpki), que se comportan de forma similar. Independientemente de la asociatividad, todos los cores experimentan el mismo descenso de mpki al doblar el tamaño, un 21 % aproximadamente. A partir de asociatividad 4 apenas se aprecia mejora.

FIGURA 5.3: Nutch: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B.

FIGURA 5.4: Classification: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B.

#### 5.1.6. Conclusiones

En base al estudio de las tasas medias de fallos por core, podemos extraer la siguientes conclusiones para el conjunto de todas las aplicaciones:

- Dos aplicaciones, Streaming y Cloudstone, no facilitan un diseño homogéneo de la cache de instrucciones, ya que un core se desmarca del comportamiento de los otros tres. Escoger descuidadamente una configuración de tamaño y asociatividad puede resultar en unas tasas de fallos excesivas para unos y en un diseño sobredimensionado para otros. La existencia de anomalías de asociatividad complica aún mas la decisión de diseño.

- El rango de tasa de fallos observado es grande, destacando Streaming, que puede llegar a los 50 mpki. Le sigue Cloudstone, presentando entre 20 y 10 mpki. A continuación, Nutch puede llegar a fallar bastante con pequeños tamaños (20-10 mpki), pero con suficiente capacidad y asociatividad apenas falla (5-1 mpki). Finalmente, Cassandra y Classification, con una asociatividad suficiente, apenas fallan (<4 mpki).

- A la vista de los experimentos realizados podemos derivar algunas pautas de diseño para la cache de instrucciones de primer nivel con tamaño de bloque 64 Bytes: Si el tiempo y la energía de acceso no quedan comprometidas<sup>2</sup>, el diseño mas razonable es un tamaño de 64 KB con asociatividad 4-8.

- La opción de 32 KB es mas barata y rápida. Salvo para Streaming sería muy apropiada. Una asociatividad 4 sería suficiente.

- En caso de optar por 16 KB, la mitad de las aplicaciones funcionarían bien por debajo de su potencial (Streaming, Nutch y Cloudstone). En esta caso, una asociatividad 4 también sería suficiente.

#### 5.2. Huella de Memoria

La huella de memoria es el número total de bloques diferentes que un programa visita cuando se ejecuta. En nuestro caso nos interesa la huella de instrucciones, medida con una granularidad de 64 bytes, el tamaño de bloque de cache que vamos a utilizar en

<sup>&</sup>lt;sup>2</sup> Tanto el tiempo como la energía de un acceso de cache crecen más o menos linealmente con el tamaño y de forma marginal con la asociatividad. Un diseño comercial no sólo considera la tasa de fallos, sino el tiempo medio de acceso y el posible impacto sobre el tiempo de acceso del procesador [HP06]

FIGURA 5.5: Cloudstone: mpki de la cache de instrucciones en cada core vs. tamaño y asociatividad. Tamaño de bloque 64B.

todo este capítulo. Por tanto la huella de instrucciones es equivalente al tamaño *efectivo* del código que se ha ejecutado en cada aplicación.

Para observar la evolución temporal, hemos medido en primer lugar la huella de recarga en intervalos de 100 ms. Para cada core, la huella de recarga mide el número de bloques diferentes que se visitan en cada intervalo. Esta medida se ha realizado mediante una cache completamente asociativa lo suficientemente grande para que no haya fallos de conflicto ni de capacidad, solo fallos obligatorios, que son los correspondientes al número de bloques diferentes referenciados. Al principio de cada intervalo se vacía la cache. Puesto que cada cache tiene su propia dinámica, hemos optado por representar únicamente la mayor de las cuatro huellas de recarga<sup>3</sup>.

En las figuras también se presentan los resultados para cada core de la *huella acumulada*, que se ha calculado sin perder memoria cada 100 ms. Por tanto la huella acumulada al final de los 10 s representa el número total de bloques de instrucciones visitado por cada core.

Hay que prestar especial atención en las figuras ya que no todas están escaladas igual y no todos los ejes verticales comienzan en el valor cero.

En este apartado nos interesa verificar si las aplicaciones están en régimen estacionario, como afirman los creadores de los checkpoints. En tal caso, podríamos buscar fases de ejecución que nos permitan simular en una ventana de tiempo mas reducida. Por otra

<sup>&</sup>lt;sup>3</sup>En el capítulo de conclusiones y líneas abiertas (Capítulo 6) se comenta un interesante trabajo futuro relacionado con las posibles similitudes o diferencias entre las huellas de recarga de los cuatro procesadores.

parte, también nos interesa descubrir si existe relación, o no, entre la huellas (acumulada o de recarga) y las tasas de fallos presentadas en el apartado anterior.

FIGURA 5.6: Huella de recarga de todas las aplicaciones de Cloudsuite. Cien intervalos de 100 ms. Tamaño en KB  $(2^{10})$

En la figura 5.6 podemos ver la huella de recarga en KB (2<sup>10</sup> bytes) para cada una de las cinco aplicaciones. Podemos observar que Cloudstone es la que más código toca, al contrario que Streaming y Classification que presentan huellas incluso 7 veces menores. Sin embargo, estas dos aplicaciones, sobre todo Classification, presentan una variabilidad relativa muy grande en su recarga. Nutch y Cassandra tocan una cantidad de código parecida, del orden de los 600-700 KB, mostrando bastante estabilidad en la cantidad de código que se recarga.

A continuación presentamos los resultados desagregados por aplicación.

### 5.2.1. Streaming (Figura 5.7)

La huella acumulada en los 10 segundos de simulación se mueve en un rango de entre  $800 \rm KB$  para el core 3 y casi  $600 \rm KB$  para el core 4. La recarga en cada muestra varía entre  $200 \rm KB$  y más de  $500 \rm KB$ .

Al principio de la ejecución los 4 cores cargan el código y después se pueden destacar los cambios de fase del core 2 y 3, que cargan unos 100 KB de código sobre el segundo 1,5 y el segundo 3, respectivamente. Estos cambios de fase corresponden a picos máximos en la huella de recarga.

FIGURA 5.7: Huellas acumuladas y de recarga de de Streaming.

## 5.2.2. Cassandra (Figura 5.8)

Mientras que los cores 1,2 y 4 consumen entre 900 KB y 1200 KB de instrucciones a lo largo de los 10 segundos, el core 3 alcanza los 2000 KB. Hay varios cambios de fase en los cores, por ejemplo cerca del segundo 6 aparece una carga de unos 100KB de instrucciones en el core 1. Sin embargo, el que más destaca es el del core 3 en el segundo 6,4, que es de unos 900 KB. Esto coincide con el pico en la huella de recarga, que es unos 900 KB mayor que la media, media que se mantiene constante a lo largo del tiempo en unos valores de 500-700KB.

${\it Figura}$ 5.8: Huellas acumuladas y de recarga de Cassandra.

#### 5.2.3. Nutch (Figura 5.9)

El número de bloques referenciados en total en los 10 segundos de simulación se mueve en un rango de entre 1200KB para el core 4 y 1000 KB para el core 3. Y la huella de recarga oscila entre 600 KB y 800 KB, destacando un punto muy bajo de unos 200KB.

FIGURA 5.9: Huellas acumuladas y de recarga de Nutch.

#### 5.2.4. Classification (Figura 5.10)

La huella acumulada en los 10 segundos de simulación se mueve en un rango de entre 2500KB para el core 1 y 1800KB para el core 2. Aunque las huellas de recarga son relativamente bajas, moviéndose en su mayoría por debajo de los 500KB, existen picos significativos que corresponden con los cambios de fase de las huellas acumuladas.

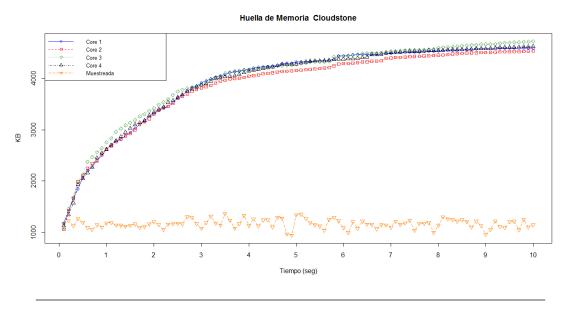

#### 5.2.5. Cloudstone (Figura 5.11)

Alcanzamos una huella acumulada superior a los 4000KB, mucho más alto que en el resto de las aplicaciones. Observamos que los 4 cores tienen un comportamiento prácticamente idéntico, trazando una función de aspecto logarítmico. Al principio se cargan grandes tamaños, del orden de 100KB, y al final casi no se cargan nuevos bloques de instrucciones. No hay cambios de fase claros ya que la carga es progresiva, y esto se puede apreciar en la huella de recarga, ya que varia poco y no tienen ningún pico significativo.

FIGURA 5.10: Huellas acumuladas y de recarga de Classification.

FIGURA 5.11: Huellas acumuladas y de recarga de Cloudstone.

#### 5.2.6. Conclusiones

■ Los creadores de los checkpoints afirman que el punto de inicio de ejecución corresponde a un régimen estacionario. Sin embargo todas las aplicaciones no estabilizan sus huellas hasta bien entrada la ejecución. En concreto, a partir del segundo 4 para Streaming, 6,4 para Cassandra, 7,2 para Nutch, 7 para Cloudstone y 9 para Classification. Sin embargo sería necesario simular unos 10 segundos más para ver si realmente se ha llegado a un comportamiento estable en cuanto a huella acumulada y recarga.

- Cuando hablamos de un cambio de fase, nos referimos a que recargamos del orden de 100 o más KB de instrucciones. Estos cambios de fase, que se dan en todas las aplicaciones excepto en Cloudstone, complican escoger una ventana de tiempo representativa.

- No existe correlación entre las huellas de memoria y las tasas de fallos observadas en el apartado anterior. Por ejemplo, Streaming no destaca ni por el tamaño final de la huella ni por sus valores de recarga, pero es la aplicación que mas falla: se visita poco código, pero con poca localidad. Por el contrario, a veces se visita mucho código, pero con gran localidad. En este grupo caen Cassandra y Cloudstone. Cassandra falla realmente poco, aunque su huellas acumuladas y de recarga son de las mayores de la suite. Cloudstone es con diferencia la que tiene huellas acumuladas y de recarga mas grandes. Sin embargo, sus tasas de fallos son medias.

## 5.3. Ancho de Banda de instrucciones

Como ya hemos indicado en el apartado 4.1, la métrica BWin es el ancho de banda de instrucciones que entra desde el siguiente nivel, agregado para las cuatro caches. La figura 5.12 recuerda el sistema simulado y resalta la agregación de los tráficos entrantes a las cuatro caches de instrucciones.

FIGURA 5.12: Sistema simulado para calcular Bwin, el ancho de banda de instrucciones.

La siguiente formula concreta como se calcula dicho ancho de banda a partir de las tasas de fallos en mpki, asumiendo un procesador de 2 GHz que ejecuta a un ritmo de un ciclo

por instrucción:

$$BWin(GBps) = \sum_{K=1}^{4} mpki_{core\ K} \times \frac{64B}{1000\ instrucciones \times 1 \frac{ciclo}{instrucción} \times 0, 5 \frac{ns}{ciclo}} = \sum_{K=1}^{4} mpki_{core\ K} \times 0, 128 \times \frac{10^{9}}{2^{30}} GBps$$

$$(5.1)$$

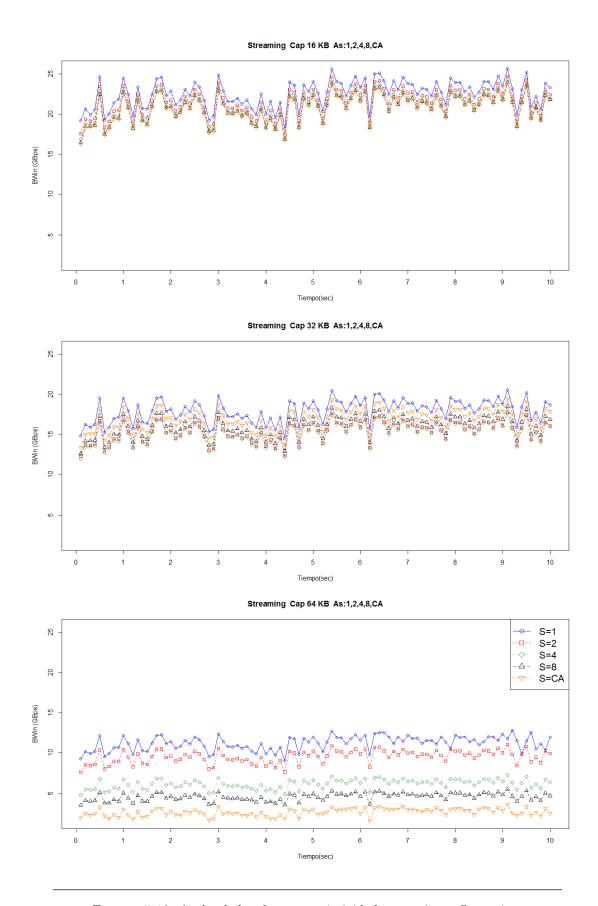

Vamos a presentar en tres gráficas la evolución temporal de BWin para cada tamaño de cache (16KB, 32KB, 64KB); en cada gráfica se detalla el comportamiento para cada asociatividad.

#### 5.3.1. Streaming (Figura 5.13)

En concordancia con sus elevadas tasas de fallos, Streaming es la aplicación que puede presionar más al siguiente nivel, presentando picos de hasta 25 GBps para la cache mas sencilla (16 KB, S=1). Al igual que en todo el resto de aplicaciones, si consideramos la evolución temporal como una señal, podemos ver como el aumento de tamaño y asociatividad actúa como un filtro paso bajo con gran reducción de la componente continua. En este caso, al pasar de 16 KB con S=1 a 64 KB con S=2, BWin se reduce, en media, en un orden de magnitud.

Al aumentar el tamaño de cache, el BWin es más sensible a la asociatividad: para 16 KB apenas se nota la diferencia entre asociatividades, mientras que para 64 KB cada vez que doblamos la asociatividad, el BWin desciende apreciablemente. Hay que resaltar que el resto de aplicaciones van a presentar justo el comportamiento contrario: a mayor tamaño, menor impacto de la asociatividad.

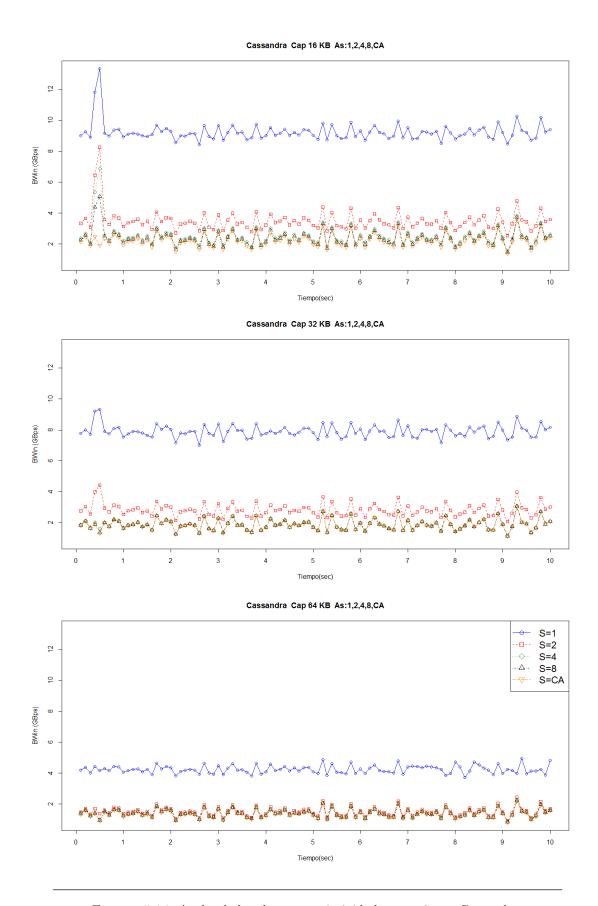

#### 5.3.2. Cassandra (Figura 5.14)

Hay que destacar la gran diferencia entre correspondencia directa y el resto de asociatividades, aunque ésta disminuye bastante al aumentar el tamaño de la cache. También observamos que a partir de una asociatividad mínima (S > 2), apenas hay diferencias de ancho de banda.

La influencia del tamaño de la cache sobre el filtrado de ruido y la disminución de la componente continua sigue el patrón general.

FIGURA 5.13: Ancho de banda por asociatividad y tamaño en Streaming.

FIGURA 5.14: Ancho de banda por asociatividad y tamaño en Cassandra.

### 5.3.3. Nutch (Figura 5.15)

Destaca la gran variabilidad temporal del ancho de banda, sobre todo para 16KB y 32KB. Al aumentar el tamaño de la cache el rango del ancho de banda se reduce apreciablemente, aunque el escalado es variable (e.g. en media, el cociente entre BWin para S=1 y para CA, es del orden de 2, 1,7 y 6, para las caches de 16, 32 y 64 KB, respectivamente).

La influencia del tamaño de la cache sobre el filtrado de ruido y la disminución de la componente continua sigue el patrón general.

#### 5.3.4. Classification (Figura 5.16)

Salvo con una cache de correspondencia directa, esta aplicación es la que menos presiona al siguiente nivel de memoria. Observamos una gran diferencia entre asociatividad 1 y el resto de asociatividades. Además, al aumentar el tamaño de la cache, la sensibilidad a la asociatividad es menor.

La influencia del tamaño de la cache sobre el filtrado de ruido y la disminución de la componente continua sigue el patrón general.

#### 5.3.5. Cloudstone (Figura 5.17)

Junto con la aplicación Nutch, Cloudstone destaca por gran variabilidad temporal. Pero en este caso, apenas es apreciable el filtrado paso bajo que se observa en el resto de aplicaciones al aumentar el tamaño de cache. Observamos que la diferencia absoluta entre las distintas asociatividades es casi constante, independientemente del tamaño de la cache.

#### 5.3.6. Conclusiones

Con tan solo cuatro procesadores las aplicaciones estudiadas pueden ejercer una presión notable sobre el siguiente nivel de memoria cache. Si asumimos que la recarga de instrucciones se produce regularmente, sin ráfagas (lo cual no suele ser cierto), podemos calcular a partir de BWin el número medio de ciclos entre las transacciones de 64 B, mediante la siguiente formula (procesadores de 2GHz):

$$\frac{119,2}{BWin(GBps)} \cdot \frac{ciclos}{transaccion} \tag{5.2}$$

Esto significa que un ancho de banda de 10 GBps, observado en mas de una aplicación y configuración, supone en media un acceso cada 12 ciclos, aproximadamente.

${\it Figura}$ 5.15: Ancho de banda por asociatividad y tamaño en Nutch.

FIGURA 5.16: Ancho de banda por asociatividad y tamaño en Classification.

FIGURA 5.17: Ancho de banda por asociatividad y tamaño en Cloudstone.

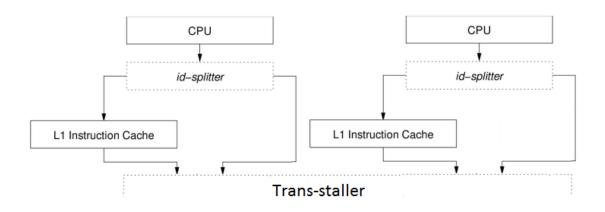

En la actualidad, las latencias de las caches de segundo nivel están en ese orden de magnitud, lo cual hace pensar en la necesidad de un diseño específico. Una posibilidad sería un siguiente nivel de memoria cache de instrucciones *privado* para cada core, que disminuiría el tráfico por cuatro, ver figura 5.18(a). Otra posibilidad sería un siguiente nivel multibanco para datos e instrucciones, que permita el servicio simultáneo del tráfico de datos (que no ha sido considerado en este trabajo) y soporte la presencia de ráfagas de fallos, cuya serialización también comprometería las prestaciones, ver figura 5.18(b).

FIGURA 5.18: Dos propuestas para mejorar el suministro de instrucciones desde el siguiente nivel.(a)Segundo nivel de cache de instrucciones privado para cada core.(b)Segundo nivel de cache compartido (datos + instrucciones) y multibanco.

- Una buena forma de entender como afecta el aumento de tamaño y asociatividad consiste en observar la evolución temporal del ancho de banda como si fuera una señal, y considerar a la cache como un filtro paso bajo, que de acuerdo a su tamaño y asociatividad, reduce progresivamente el nivel de la componente continua y su frecuencia de corte. Esta es una hipótesis interesante, que debería ser contrastada de forma rigurosa, pero que excede del alcance de este trabajo.

- Desde el punto de vista de muestreo, es decir, de la posibilidad de extraer conclusiones válidas observando únicamente una parte pequeña de toda la evolución temporal, podemos dividir las aplicaciones en dos grupos. El primero está formado por Nutch y Cloudstone; su variabilidad es grande y no parece que pueda escogerse un trozo pequeño representativo. El segundo está formado por Streaming, Cassandra y Classification; en estos casos, no parecen verse fases claras, pareciendo cualquier tramo similar y susceptible de ser representativo. Por supuesto estas reflexiones valen únicamente para experimentos encaminados a probar el siguiente nivel, cargándolo con un tráfico representativo.

## 5.4. Comparación con otras cargas de trabajo

Según los creadores de Cloudsuite una de sus principales características es que sus benchmarks ejercen una fuerte presión contra la cache de instrucciones [FAK+12]. Para contrastar esta afirmación vamos a comparar las tasas de fallos que hemos obtenido experimentalmente con los suyos y con otras fuentes disponibles. A continuación presentamos un resumen de los trabajos que hemos consultado:

- Evaluating associativity in CPU caches. Este es el trabajo en el que Hill y Smith proponen el modelo de las 3Cs [HS89]. Además, en él realizan un estudio para arquitecturas maduras de 32 bits, mediante simulaciones hechas con 28 trazas de computadores IBM 370 (sistema operativo MVS) y DEC VAX-11 (sistemas operativos VMS y ULTRIX). Los datos que reproducimos corresponden a unos promedios ajustados que sus autores denominan "design target miss ratios", pensados para caracterizar de forma tabular el comportamiento "medio" de una cache y no tener que simular. En la figura 5.19 están recogidos los mpki para caches de instrucciones de tamaño 16KB y 32KB y asociatividades desde 1 a 8, con tamaño de bloque 64B.

- Filtering Directory Lookups in CMPs. En esta tesis Ana Bosque recoge la tasa de fallos para las aplicaciones de la suite SPLASH2, una suite usada para estudios científicos de máquinas paralelas con memoria compartida [LVIB11]. Las simulaciones se realizaron con SIMICS, con binarios compilados para SPARC v9 en Solaris 8, y corresponden a una cache de instrucciones de primer nivel de 16 KB, con tamaño de bloque 32B y asociatividad 8. En la figura 5.19 se reproducen las tasas de fallos obtenidas para toda la sección paralela de cada benchmark.

- Memory System Behavior of Java-Based Middleware. En este trabajo, Karlsson, Moore, Hagersten y Wood usan dos benchmarcks: SPECjbb y ECperf [KMHW03]. Las simulaciones se realizaron con SIMICS, con binarios compilados para SPARC v9 en Solaris 8. SPECjbb está diseñado para medir la habilidad de un sistema para ejecutar aplicaciones Java en el lado del servidor. Esta aplicación conecta a los clientes con la base de datos a través de la lógica de negocio, pero para hacer el benchmark más portable y fácil de usar, no usan una base de datos comercial, almacenando directamente las tablas en memoria como objetos de tipo árbol de Java. ECperf está diseñado para comprobar el rendimiento y la escalabilidad de un sistema de 3 niveles (cliente, servidor y base de datos), modelando un negocio online. Los benchmarks se simulan para distintos tamaños de cache, con asociatividad 4 y tamaño de bloque 64B.