Jorge Albericio Latorre

Improving the SLLC Efficiency by exploiting reuse locality and adjusting prefetch

Departamento

Informática e Ingeniería de Sistemas

Director/es

Ibáñez Marín, Pablo Enrique Llaberia Griñó, José María http://zaguan.unizar.es/collection/Tesis

# **Tesis Doctoral**

# IMPROVING THE SLLC EFFICIENCY BY EXPLOITING REUSE LOCALITY AND ADJUSTING PREFETCH

**Autor**

Jorge Albericio Latorre

Director/es

Ibáñez Marín, Pablo Enrique Llaberia Griñó, José María

#### UNIVERSIDAD DE ZARAGOZA

Informática e Ingeniería de Sistemas

2013

# Improving the SLLC efficiency by exploiting reuse locality and adjusting prefetch

$\begin{tabular}{ll} Author: \\ Jorge Albericio Latorre \\ \end{tabular}$

Supervisors: Dr. Pablo Ibáñez Marín Dr. José María Llabería Griñó

DISSERTATION

Submitted in partial fulfillment of the requirements

for the degree of Doctor of Philosophy

in the Universidad de Zaragoza

Grupo de Arquitectura de Computadores Dpto. de Informática e Ingeniería de Sistemas Instituto de Investigación en Ingeniería de Aragón Universidad de Zaragoza

Marzo 2013

Chip-Multiprocessors (CMP) are nowadays commonplace from embedded to supercomputer markets. Due to the existing gap, between cpu and main memory speeds, a hierarchy of cache memories is included in the chip with the aim of reducing the average memory access latency.

Commercial CMPs include a hierarchy with two or three levels of cache memories, where the Last-level cache (LLC) is usually shared among all the cores in the system and comprises several megabytes of storage that fill up to a half of the total chip die area. Moreover, the LLC hit ratio critically affects performance since being the last storage inside the chip, any miss at the LLC provokes an expensive off-chip access to the main memory, penalizing the average memory access latency.

The whole CMP efficiency passes through the SLLC efficiency. This thesis makes contributions comprising the SLLC efficiency on two different directions: 1) its performance and 2) its hardware storage.

1) In order to improve SLLC performance, two aspects are tackled during this thesis: hardware prefetching effectivity and replacement policy. The contribution to optimize hardware prefetching is a low-cost controller, called ABS, that relies on a hill-climbing approach to infer the optimal combination of prefetching aggressiveness associated to the different cores of the CMP. This controller achieves better results than state of the art with a lower cost. Regarding to the replacement policy, this thesis proposes to base the SLLC replacement algorithm on a property called *reuse locality* that will be stated during this dissertation. Two new replacement policies are proposed. As it will be shown during the evaluation, our algorithms achieve better performance than the state of the art with a lower hardware complexity.

2) In order to reduce SLLC hardware storage, this thesis proposes a SLLC design called *reuse cache*. This design relies on the reuse locality property to only store data that has shown reuse. The tag array is used to detect reuse and maintain coherence. The experimental evaluation will show that this contribution allows drastic reductions of

the SLLC hardware storage cost while maintaining the overall system performance.

Los chips multiprocesador (CMP) están presentes en la actualidad en todos los segmentos de mercado, desde los teléfonos móviles hasta los superordenadores. Debido a la gran diferencia que existe entre la velocidad del procesador y la de la memoria principal, los CMPs en la actualidad están provistos de una jerarquía de memorias cache que tiene dos o tres niveles.

Cada fallo en el último nivel de esa jerarquía (SLLC) provoca un acceso a la memoria principal que se encuentra fuera del chip. Además la memoria principal está hecha de chips de DRAM. Ambos factores incrementan su latencia de acceso, latencia que se suma a cada uno de los accesos que falla en la SLLC, penalizando a la vez la latencia media de acceso a memoria. Por lo tanto, la tasa de aciertos de la SLLC es un factor crítico para lograr una latencia media de acceso a memoria óptima. Esta tesis fija su atención en la eficiencia de la SLLC y concretamente, en la eficiencia de la prebúsqueda y la explotación de la localidad de reúso.

Para mejorar la eficiencia de la prebúsqueda se propone un controlador de bajo coste llamado ABS capaz de ajustar la agresividad de la prebúsqueda asociada a cada uno de los núcleos de un CMP pero con el ánimo de mejorar el rendimiento general del sistema. El controlador funciona de manera aislada en cada uno de los bancos de la SLLC y recoge métricas locales. Para optimizar el rendimiento global del sistema busca la combinación óptima de valores de la agresividad de prebúsqueda. Para inferir cuál es esa combinación óptima usa una estrategia de búsqueda hill-climbing.

En esta tesis se caracteriza la propiedad de localidad de reúso y se realizan contribuciones que tienen por finalidad última una mayor explotación de dicha propiedad. En concreto, se proponen dos algoritmos de reemplazo capaces de explotar la localidad de reúso, *Leastrecently reused (LRR)* y *Not-recently reused (NRR)*. Estos algoritmos son modificaciones de otros dos muy bien conocidos: *Least-recently used (LRU)* y *Not-recently used (NRU)*. Diseñados para explotar la localidad temporal, mientras que los propuestos en esta tesis explotan la localidad de reúso. Las modificaciones propuestas no suponen ninguna sobrecarga hardware respecto a los algoritmos base y al mismo tiempo

muestran ser capaces de incrementar el rendimiento de la SLLC de manera consistente.

Además se propone un diseño para la SLLC llamado *Reuse Cache*. En este diseño solamente se almacenan en el array de datos aquellos bloques que hayan mostrado reúso. El array de etiquetas se usa para detectar reúso y mantener la coherencia. Esta estructura permite reducir el tamaño del array de datos de manera drástica. Como ejemplo, una Reuse Cache con un array de etiquetas equivalente al de una cache convencional de 4MB y un array de datos de 1MB, tiene el mismo rendimiento medio que una cache convencional de 8MB, pero con un ahorro de almacenamiento de en torno al 84%.

# CONTENTS

| I   |            | LIMINARIES                                    | 1        |

|-----|------------|-----------------------------------------------|----------|

| 1   |            | RODUCTION  Contact and background             | 3        |

|     | 1.1        | Context and background                        |          |

|     | 1.2<br>1.3 | Problem                                       | 10       |

|     | 1.3        | Contributions                                 | 11<br>12 |

| 0   |            | Thesis organization                           |          |

| 2   |            | ATED WORK                                     | 15       |

|     | 2.1        | Prefetch engines for multiprocessor systems   | 16       |

|     | 2.2        | Mechanisms to adjust prefetch aggressiveness  | 16       |

|     | 2.3        | Reuse locality                                | 17       |

| _   | 2.4        | How to decouple the SLLC tag and data arrays? | 22       |

| 3   |            | ERIMENTAL FRAMEWORK                           | 25       |

|     | 3.1        | Introduction                                  | 26       |

|     | 3.2        | Baseline system                               | 26       |

|     | 3.3        | Simulator                                     | 27       |

|     | 3.4        | Workloads and performance evaluation          | 28       |

| II  | ADJ        | USTING PREFETCHING AGGRESSIVENESS             | 33       |

| 4   | ABS        | PREFETCHING                                   | 35       |

|     | 4.1        | Introduction                                  | 36       |

|     | 4.2        | Motivation                                    | 38       |

|     | 4.3        | Background and related work                   | 39       |

|     | 4.4        | The ABS controller                            | 41       |

|     | 4.5        | Prefetching framework                         | 47       |

|     | 4.6        | Methodology                                   | 49       |

|     | 4.7        | Results                                       | 55       |

|     | 4.8        | Concluding remarks                            | 66       |

| III | ΕX         | PLOITING REUSE LOCALITY                       | 69       |

| 5   | REU        | SE LOCALITY                                   | 71       |

|     | 5.1        | Introduction                                  | 72       |

|     | 5.2        | Motivation                                    | 75       |

|     | 5.3        | Re-reference interval prediction (RRIP)       | 77       |

|     | 5.4        | Reused-based replacement                      | 79       |

|     | 5.5        | Evaluation                                    | 83       |

|     | 5.6        | Concluding remarks                            | 93       |

| 6   | REU        | SE CACHE                                      | 95       |

|     | 6.1        | Introduction                                  | 96       |

#### viii CONTENTS

|    | 6.2   | Motivation             | 98  |

|----|-------|------------------------|-----|

|    | 6.3   | The Reuse Cache Design | 100 |

|    | 6.4   | Evaluation             | 107 |

|    | 6.5   | Concluding remarks     | 117 |

| IV | COI   | NCLUSION               | 119 |

| 7  | CON   | CLUSIONS               | 121 |

|    | 7.1   | Conclusions            | 122 |

|    | 7.2   | Publications           | 123 |

|    | 7.3   | Future work            | 124 |

| Co | nclus | iones                  | 127 |

|    |       |                        |     |

| BI | BLIO  | GRAPHY                 | 129 |

## Part I

### **PRELIMINARIES**

In this first part of the thesis, material is provided which will be useful in next parts. Here we justify the presence of the memory hierarchy and present some organizational aspects and properties of the Shared last-level cache. We show previous works that are related with the work exposed on this dissertation, and describe the experimental methodology that has been followed in order to evaluate the contributions of this thesis.

1

#### INTRODUCTION

#### 1.1 CONTEXT AND BACKGROUND

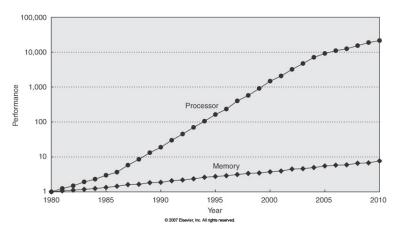

Chip-Multiprocessors (CMP) are nowadays commonplace from embedded to supercomputer markets. The cores of a CMP have to be constantly fed with data stored in the main memory, but processor memory requests frequency is much higher than memory access latency. This speed gap, called *memory wall*, has been increasing during the last thirty years (Figure 1.1). With the aim of downing the memory wall and getting closer to present the programmer unlimited and fast memory they would want, a hierarchy of cache memories brings profitable data closer to the cores. A cache memory bases its effectiveness on two behaviors that programs show when run in the computer; programs tend to use information (either data or instructions) that was recently used (temporal locality) and is close to other recently used data (spatial locality).

Given each core has to access to the cache nearly every cycle, each core has a first level of cache memories (L1) for data and instructions

Figure 1.1: The memory wall. This graph shows the evolution of processor and memory performance from 1990 to 2010. The difference between both has always continuously increased. (Note the logarithmic scale)

that are designed small and fast. It is infrequent that more than one core shares the same L1. Misses in the first level will provoke requests to the following level in the hierarchy. Provided that there still exists a big difference between access latencies to L1 and main memory, additional intermediate levels of cache memories are usually installed to mitigate that latency gap. Cache memories are bigger and slower as we move away from the core. Nowadays, commercial processors usually have two or three levels of cache [20]. The aim is to minimize the average access latency with the smallest possible cost. The Lastlevel cache (LLC) represents a critical component of this hierarchy of caches. Since it is the last storage inside the chip, an LLC miss would provoke an access to the next component, main memory. To access to main memory supposes to exit from the chip, to pass trough the memory controller and to access to the DRAM chips; and all these steps are expensive in latency. Therefore, small improvements in the LLC hit ratio will lead to big improvements in the system performance.

Next, we discuss some aspects about the LLC.

#### 1.1.1 Last-level cache organization

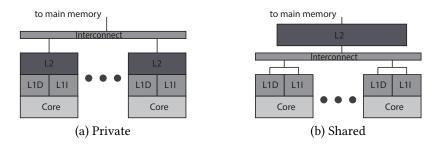

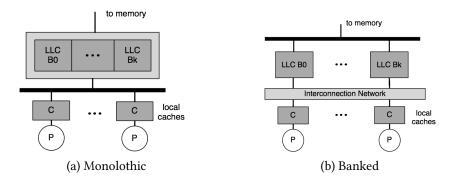

The Last-level cache (LLC) can be designed as a collection of private caches (Figure 1.2a) or as a space which is shared among all the cores (Figure 1.2b). Following we will briefly show the pros and cons of both designs.

PRIVATE In a private organization of the Last-level cache, each core has a storage for its own use (Figure 1.2a). The total size of the LLC is equally divided among all the cores in the system. As the size of each LLC is smaller than in a shared design, their average access latency is also shorter. Given only one core accesses each LLC, interference effects between cores are not found.

On the other hand, shared data is replicated in the LLC of each sharer of that cache line, reducing the total effective available space. Moreover, applications running in the CMP may require very different cache sizes; as in this design each core has associated a fixed LLC size, the LLC can not be adapted to the requirements of each application. In addition, a mechanism to maintain coherence in this organization will suffer higher latencies than the same mechanism in a shared design.

Figure 1.2: Last-level cache organizations

SHARED In a shared organization of the Last-level cache (SLLC), all the cores share the complete LLC available storage (Figure 1.2b). The size of the SLLC is bigger than in the private design, so the access latency is also larger. Given the LLC storage is shared among all the cores, the activity of the applications running in the system may harm each other.

On the other hand, only one copy of the data used by more than one core is stored in the SLLC, maximizing the effective SLLC available storage. In addition, a SLLC can suffice at the same time the requirements of two very different applications.

SLLC are internally split in banks which are accessed through one port. This organization provides at the same time layout flexibility and increased access bandwidth.

This thesis follows the general trend in both industry and academy, choosing a shared design (SLLC) as the LLC organization where contributions are proposed and evaluated.

#### 1.1.2 Inclusivity

A hierarchy of cache memories (L1-L2) is said to be **inclusive** when the L2 stores the contents of all the L1s. In other words, the L2 contents are always a superset of the L1 caches contents [3]. In order to maintain this property, two actions have to be consistently performed:

- 1. When a cache line is inserted in some L1, it must be also inserted in the L2 if it is not present.

- 2. When a L2 line is evicted, invalidation messages are sent to all the L1 copies, if any.

An inclusive hierarchy simplifies coherence maintenance [42]. As the SLLC knows about the contents of the cache levels closer to the processor, a mechanism to maintain the coherence installed at this level is able to take decisions without sending look-up messages to the local caches. Many commercial CMPs present an inclusive hierarchy [20].

A hierarchy of cache memories (L1-L2) is said to be **exclusive** when the contents of the L2 and the L1s are always disjoint sets. Meaning that when a cache line is inserted in some L1, it must be removed from the L2 if it is present. In this type of hierarchy, two basic schemes can be considered to maintain the system coherent. This information can be present at the SLLC as an updated copy of the L1s tags, or be obtained by sending look-up messages to the L1s every time some situation requires it.

When neither inclusion nor exclusion are enforced, the hierarchy is said to be **non-inclusive/non-exclusive**. There exist a broad range of options to define this intermediate scheme [69, 53].

This thesis considers an inclusive SLLC organization as the baseline design where contributions are proposed and evaluated.

#### 1.1.3 Hardware Data Prefetching

Hardware prefetching is a technique that tries to load into the cache, contents the processor will use in the future. The decision on what to prefetch has relayed on plenty of prediction schemes, from simple to very sophisticated ones. All of those schemes revolve around a property programs show, called *spatial locality*. This property says that a program will reference in the future, memory addresses that are close to memory addresses it referenced recently in the past. In other words, programs are kind of predictable in their stream of references accessing to memory. The hardware prefetcher installed at some cache level observes the stream of references arriving to that cache with the intention of generating prefetches that bring data into the cache which will be referenced in the near future.

A basic type of prefetcher trying to exploit spatial locality is the *stride* prefetcher. This prefetcher calculates the difference between the addresses of the cache lines referenced by two consecutive misses and it generates a prefetch request based on such difference, e.g. misses are observed over the cache lines corresponding to the ad-

dresses A and A+m, thus the stride prefetcher will generate a request for the address A+2m. The basic case of stride is when m is equal to 1, a prefetcher considering always this kind of pattern is called *sequential prefetcher*. A parameter associated to the prefetcher is its *aggressiveness*. The aggressiveness of a prefetcher defines how much (*degree*), and also, depending on the type of prefetcher, how far (*distance*) the prefetcher will follow its prediction in order to bring data to the cache. E.g. on the stride prefetcher, the degree defines how many cache lines will be brought into the cache per triggering event, for the example before, if we define degree as equal 3, consecutive misses to A and A+m will generate prefetches of A+2m, A+3m, and A+4m.

Aggressiveness of a prefetcher should adapt to application and memory system characteristics. Adaptive mechanisms to dynamically adjust the prefetching aggressiveness has been previously proposed and are presented in Section 2.2. If a CMP system with a SLLC is considered new tradeoffs, which are presented in the next Section, appear.

#### 1.1.4 Replacement Policy

When a miss is observed by the cache and there is no free cache entries, one cache line has to be selected as victim. The replacement policy decides which is the cache line that will be evicted to make place for another incoming. Three basic schemes of replacement traditionally considered are: 1) Random. 2) FIFO. 3) LRU.

RANDOM The random replacement policy, as its name indicates, randomly chooses a victim among the elements present in the set. Its implementations normally uses a pseudo-random periodical function. It does not need any additional storage.

FIRST-IN-FIRST-OUT The First-In-First-Out (FIFO) replacement policy orders the elements of a set following their arrival order. Only a pointer is needed to implement this policy, the pointer has to indicate the element entered the furthest in the past. The storage needed to implement this policy is log<sub>2</sub>(associativity) bits per set. The lifespan of a line in a *N-way* associative cache is exactly the time for the set to observe N misses. A spread variant of the FIFO policy is the CLOCK algorithm. It was originally proposed for the management of pages in a virtual memory

management system [12]. It has been used in caches or buffers with a high associativity. It uses one bit per cache line to record if the element has been referenced during its stay in the structure or not. When an element has to be evicted, the element entered the first one is selected as victim, if its bit is set, the bit will be reset and the next element will be considered as possible victim.

LEAST-RECENTLY USED The *least-recently used (LRU)* replacement algorithm is oriented to exploit a property called *temporal locality* that programs show when running. Temporal locality assumes that a recently used cache line will be used again in the near future. All the elements in a cache set conform a chain and are ordered following the use order; the most recently referenced elements are at the beginning of the chain, while the end of the chain is occupied by the least recently referenced element. On a miss, a cache line has to be chosen as victim, the last one is selected. Every cache line increases its position by one and the new line is inserted at the beginning of the chain. On a hit, the hit line is situated at the beginning of the chain while all the lines that were occupying positions over the hit line see decremented their position by one.

There is a plenty of options to implement the LRU policy, each one representing different tradeoffs in terms of storage cost and logic complexity. Sudarshan *et al.* made a review of different implementations in [60].

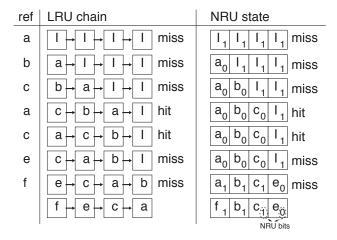

True LRU can be implemented with low cost when small associativities are considered, e.g. to implement LRU in a 4-way associative cache is 8 bits per set. But when higher associativities are considered (16- 32-, or 48-way associative caches), as the ones we can find in a SLLC, true LRU gives way to alternative policies that try to mimic LRU performance with a lower hardware cost. These policies are called pseudo-LRU policies. There is a broad variety of this kind of policies and what they have in common is the use of partial information to maintain an approximation to the LRU order inside the set. Normally, all of them try to avoid to evict the most-recently used element while they keep some kind of order among the rest of the elements of a set. An example of pseudo-LRU policy is Not-recently used (NRU) [43]. As Figure 1.3 shows, this policy employs one bit for each cache line (NRU-bit), the bit is zero when the line is inserted into the set. All the NRU-bits but the one corresponding

Figure 1.3: Example of LRU and NRU replacement policies

to the just inserted line will be reset in case of all the NRU-bits are equal to zero. When a victim has to be selected, the first cache line with the NRU-bit equal to one is evicted. The search of the line with NRU-bit equal to one can be started from the position indicated by a global pointer (Sun T2) or from the way 0 (intel i7).

In Figure 1.3, we can observe an example of the behavior of LRU and NRU replacement policies. Each line represents the state of the set before the reference that appears on the left column accesses the cache. For LRU, elements are ordered forming a chain, while for NRU each element is at its corresponding way and the NRU bit appears along the address. Next to state, for both algorithms, we can observe if a determined reference is a hit or a miss. Consecutive lines of the figure show consecutive states of the set; the second line of any pair shows the state of the set after the reference ("ref" on the figure) of the first line makes its access effective.

Section 2.3 presents recent research on replacement algorithms for the SLLC. These works have shown replacement policies for the SLLC should not be based on temporal locality and the next section will expose the problem.

#### 1.2 PROBLEM

Every SLLC miss provokes an access to the main memory. The main memory is out of the chip and made of DRAM memory chips, adding a long latency to every access that misses in the SLLC and penalizing the average memory access time. Thus, the SLLC hit ratio is a critical factor to achieve an optimal average memory hierarchy access latency. Technological innovations aside, two aspects that can be tackled to improve the SLLC hit ratio are the efficiency of both prefetching and replacement policy.

#### 1.2.1 Hardware Data Prefetching

Hardware prefetching tries to load data into the cache time ahead of the processor references it. This technique has been broadly shown as good to reduce the average access memory latency. Prefetching performs specially well in mono-processor memory hierarchies where only one stream of data flows from main memory to the caches closer to the core. However, when prefetching is used in the SLLC of a multicore system where different applications are running at the same time, prefetches associated to one core may interfere with the data placed into the cache by other core, evicting contents of other application and harming its performance. A control mechanism to regulate the prefetching aggressiveness associated to each core is desired. This mechanism should target the overall system performance. In section 2.2, we feature previous work on hardware data prefetching aggressiveness adjustment for mono- and multi-processor systems, and in Section 4.2 we explain in detail the aforementioned inter-core prefetching interference problem.

#### 1.2.2 Replacement policy

The replacement policy critically influences the cache memory hit ratio. In a CMP fitted with a hierarchy of cache memories, temporal locality is squeezed by the cache levels closer to the core. Thus, many of the lines inserted in the SLLC are single use, meaning that they will not experiment any hit during their lifespan at the SLLC. However, cache lines that experiment one hit in the SLLC are normally experimenting many hits. Therefore, to assume that the replacement

algorithm has to base its decisions on the temporal locality exploitation is no longer valid at the SLLC. On the contrary, this behavior indicates the SLLC replacement policy should be based on reuse instead of temporal locality. Section 5.2 goes over SLLC replacement problematics with more detail.

#### 1.3 CONTRIBUTIONS

These are the main contributions of this thesis:

#### 1.3.1 The ABS controller

A low-cost controller able to adjust the prefetching aggressiveness associated to each core in the CMP with the aim of improving the overall system performance. The controller runs stand-alone at each SLLC bank and gathers local metrics. Using a hill-climbing approach whose target function is the overall system performance, the ABS controller tries to infer the optimal combination of prefetching aggressiveness values for the applications that are running in the system.

#### 1.3.2 Reuse locality

Observing the stream of references accessing to the SLLC, we state a property called *Reuse locality* that says that i) Cache lines used more than one time will be highly likely used many times in the future. ii) Cache lines recently reused are more useful than lines reused before. We claim that SLLC access pattern shows reuse locality.

#### 1.3.3 Replacement algorithms to exploit the reuse locality

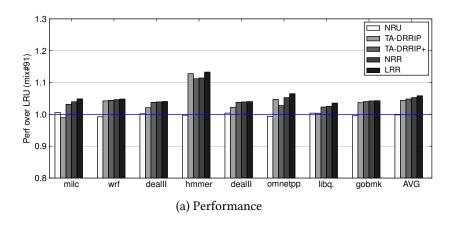

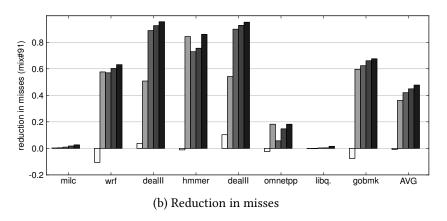

Two replacement algorithms able to exploit the reuse locality are proposed, *Least-recently reused (LRR)* and *Not-recently reused (NRR)*. These algorithms are modifications of two very well known algorithms based on the use, to be based on the reuse. The base algorithms are *Least-recently used (LRU)* and *Not-recently used (NRU)*, our transformations do not add any hardware to them. We will show that

these two new algorithms consistently improve the performance of their predecessors.

#### 1.3.4 Reuse cache

A novel design for the SLLC of a CMP is proposed. On this design tag and data arrays are decoupled. Only those cache lines that have shown reuse are stored in the data array. The tag array is used to detect reuse and maintain coherence. This scheme allows to drastically reduce the size of the data array. As an example, a reuse cache with a tag array equivalent to a conventional 4MB cache and a data array of 1MB achieves the same average performance that a conventional 8MB cache

#### 1.4 THESIS ORGANIZATION

This dissertation is organized in four parts. The first part contains Chapters 1, 2, and 3. These chapters introduce the topics of the dissertation, present background and previous works, and discuss the experimental framework followed during this thesis. Second part includes only Chapter 4 that explains our contribution to adjust prefetching aggressiveness. Third part comprises Chapters 5 and 6, which explains our contributions to improve the SLLC efficiency by the better exploitation of reuse locality. Finally, fourth part concludes this dissertation.

CHAPTER 2 presents previous works related with the contributions presented on this thesis. Related work includes research regarding the exploitation of reuse locality, works where decoupled structures are proposed or used, prefetch engines with the aim of improving CMP performance, and in mechanisms to adjust the prefetching aggressiveness in mono- and multi-processors.

CHAPTER 3 explains the experimental setup that has been used to evaluate our proposals. Including the simulator characteristics, the baseline system we consider, and the workloads whose behavior have been analyzed during this thesis.

- CHAPTER 4 presents the ABS controller and its evaluation. The evaluation includes the use of particular metrics that will be justified. A comparison with the state of the art is also presented.

- CHAPTER 5 states the reuse locality and presents two replacement policies that exploit such property. This chapter also shows the evaluation of our policies and their comparison with both base algorithms and state of art.

- CHAPTER 6 presents the reuse cache and its rationale and design are explained. That chapter also shows a broad evaluation from different design points and a comparison with the state of the art. The chapter finishes suggesting further improvements or future lines for the reuse cache.

- CHAPTER 7 concludes the dissertation summarizing the work done and discusses about possible future research lines.

#### RELATED WORK

#### SUMMARY

This chapter about the related work comprises four different sections. First two sections of this chapter are related with our contribution to control the prefetching aggressiveness in a CMP. Concretely, Section 2.1 summarizes previous works about prefetch engines, focusing only on research which targets multiprocessor systems. And Section 2.2 revises the previous work on adjustment of the prefetching aggressiveness in mono and multiprocessor systems. Section 2.3 is about the reuse locality and also about how different insertion and replacement schemes for the SLLC have tried to exploit such property, the material exposed on this section is related with three of the contributions of this thesis, namely, the reuse locality, the policies to exploit it and the reuse cache. Finally, Section 2.4 shows a variety of works that proposed alternative organizations for the cache memory related with our reuse cache.

#### 2.1 PREFETCH ENGINES FOR MULTIPROCESSOR SYSTEMS

The development of prefetching engines able to interpret memory access patterns has been a broadly studied field of research. In this section, we only focus on those proposals with the aim of improving the behavior of the memory hierarchy of multiprocessor systems.

Cantin et al. [6] and Wallin and Hagersten [63] aim to identify private memory regions not shared by the other processors, starting to prefetch only in these memory regions in order to avoid that shared data prefetching may hurt performance. Koppelman [29] uses the instruction history to compute an area around the demanded data, which can be prefetched. Somogyi et al. [56] predicts memory accesses that exhibit a repetitive layout (spatial streaming); it proposes a predictor that correlates the memory access patterns with instructions addresses. Wenisch et al. [64] proposes temporal streaming, which is based on the observation that recent sequences of shared data accesses often recur in the same precise order; therefore it proposes to move data to a sharer in advance of its demand. Somogyi et al. [57] leverages the ideas of the two previous works and proposes a predictor that exploits both temporal and spatial correlations. How to store meta-data off chip for an address-correlating prefetcher has been also evaluated [65]. The concern of that work is how to store the large amount of information that requires their prefetcher to get good results in commercial applications. In contrast, the ABS controller that is proposed in this dissertation is not proposing a new prefetch engine but a control system to set the aggressiveness of a prefetcher installed in the banked SLLC of a Chip Multiprocessor.

#### 2.2 MECHANISMS TO ADJUST PREFETCH AGGRESSIVENESS

In mono-processors, *Adaptive Data Cache Prefetcher (AC/DC)* divides the memory address space into zones of the same size called *Czones*, and it uses global history buffer to track and detect patterns in consecutive miss addresses within each Czone. It is also able to dynamically adjust the size of the Czones and the prefetcher degree. Ramos *et al.* introduce an adaptive policy that selects the best prefetching degree within a fixed set of values, by tracking the performance gradient and following a hill-climbing approach are able to approximate to the prefetcher configuration optimal value [49]. Srinath *et al.* proposed *Feedback directed prefetching (FDP)* [58]; a mechanism that incorpo-

rates dynamic feedback to increase the performance improvement provided by prefetching. The mechanism estimates prefetching accuracy, timeliness, and cache pollution and, depending on a predefined set of thresholds, it adjusts the aggressiveness of the data prefetcher dynamically. FDP also incorporates a mechanism to decide in which position of the LRU stack it inserts depending on the pollution the prefetcher is provoking.

Several works address the problem of adjusting prefetch aggressiveness in CC-NUMA multiprocessos having only private cache memories. Dahlgren *et al.* suggest to determine the prefetch aggressiveness at each private cache by counting the number of useful prefetches every given number of issued prefetches (an epoch) [14]; the prefetch aggressiveness is increased or decreased taking into account two usefulness thresholds. Tcheun *et al.* add a degree selector to a sequential prefetch scheme [61]; when the selector detects useful prefetches along a sequential sub-stream it increases the prefetch aggressiveness of the next sub-stream belonging to the same stream. As these works are not using a shared cache, the interference problems among cores that they found are only related with the available bandwidth when accessing to memory.

To our knowledge, only *Hierarchical Prefetcher Aggressiveness Control (HPAC)* Ebrahimi et al. [15] faced for the first time the problem of reducing the prefetch inter-core interference in a chip multiprocessor with a shared LLC. HPAC monitors several global indexes (prefetch accuracy, inter-core pollution, and memory controller activities) and compares them to a predefined set of thresholds. That comparisons are contrasted against a set of rules to finally adjust the prefetch aggressiveness of each core. In Chapter 4, we have included a deep discussion about HPAC characteristics, and also a comparison in terms of performance and resource consumption with respect to a system using ABS controllers.

#### 2.3 REUSE LOCALITY

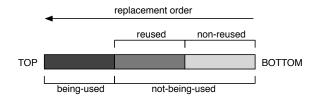

Reuse locality says that i) Cache lines used more than one time will be highly likely used many times in the future. ii) Cache lines recently reused are more useful than lines reused before. This property was first observed and exploited in cache memories for disks. Segmented LRU [24] tries to protect useful lines against harmful behaviors (i.e., a burst of single-use accesses) by dividing the classical LRU stack into

two different logical lists, the *referenced* and the *non-referenced* list. The boundary between the lists is fixed and victims are selected in order to preserve that limit.

Recent proposals have applied this idea to the replacement policy of non-inclusive SLLCs. Both dynamic segmentation [26] and dueling segmented LRU [17] consider these two logical LRU divisions and try to dynamically find an optimal configuration by using set dueling. The former uses a set dueling predictor and a decision tree to dynamically move the border between the reused and non-reused segments. Another level of set dueling chooses between dynamic segmentation and plain LRU. Whenever the size of the reused segment becomes the smallest (one line), bypass is switched on. In spite of the cache being bypassed, one of every thirty-two lines is stored in cache in order to prevent the working set from becoming stale.

Dueling segmented LRU adds random promotion and aging to the basic segmentation. Random promotion acts by randomly tagging some non-reused lines as being reused, while aging acts in the opposite way. The mechanism uses set dueling in order to dynamically choose between segmented and plain LRU. In addition, they suggest using adaptive bypass. Some shadow tags are required to evaluate the bypass benefit and switch it on or off accordingly.

Recently, *MRU-Tour* based algorithms also propose using reuse to divide the elements of a set into different groups and randomly evict elements with a number of MRU-Tours lower than a given value [62].

#### 2.3.1 Insertion policy

Several studies propose to change the insertion point in the recency stack of lines that reach the cache. Their goal is to avoid that thrash or scan workloads evict the useful cache lines.

The dynamic insertion policy (DIP) involves a hybrid cache replacement [47]. Under this scheme, LRU and Bimodal insertion Policy (BIP) are dynamically selected by using set-dueling. LRU always inserts the incoming lines in the MRU position of the recency stack. BIP inserts the majority of incoming lines in the LRU position and with a low probability in the MRU position.

Promotion/Insertion Pseudo-Partitioning (PIPP) allows each thread to insert their lines at a different point in the recency stack

Figure 2.1: Static re-reference interval prediction (SRRIP) replacement algorithm

[68]. It provides the benefits of cache partitioning, adaptive insertion and capacity stealing among threads. However, it requires a utility monitor with shadow tags to detect thread's behavior.

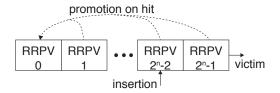

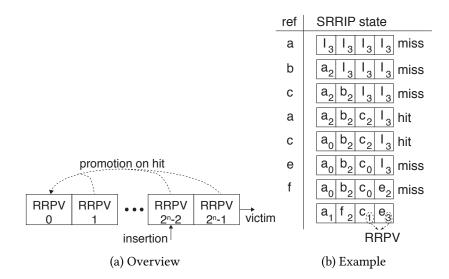

Although industry has widely adopted inclusive SLLC schemes in commercial processors, specific content management for this kind of cache organization has not received much attention from academia. An exception is Re-Reference Interval Prediction (RRIP), that has been proposed for an inclusive hierarchy [23].

RRIP involves a modified LRU that considers a chain of segments where all the cache lines in a segment are supposed to have the same *re-reference interval value (RRPV)* [23] (Figure 2.1). The mechanism is able to insert new lines into the segments corresponding to re-reference intervals either *intermediate* (segment with a RRPV equal to 2<sup>N</sup>-2) or *long* (segment with a RRPV equal to 2<sup>N</sup>-1), becoming in this way *scan*-resistant and *Thrash*-resistant. A more detailed explanation of this algorithm can be found in Section 5.3.

Recently, a plethora of proposals try to infer reuse properties of cache contents (present and incoming) by using predictors. Later on, these predictions are used to modify the insertion policy.

Signature-based hit predictor (SHip) improves RRIP with rereference interval prediction [67]. SHiP correlates re-reference behavior with memory region, program counter, and instruction sequence history. SHiP and other work, like ones proposed by Chaudhuri et al. [7], Li et al. [34], Seshadri et al. [51] are complementary to the reuse cache design. For instance, the predictors proposed in [51, 67] could be used to increase the performance of the reuse cache by predicting the reuse behavior of a cache line on a tag miss. The OBM mechanism proposed in [34] signals the first line to be reused between the incoming-victim line pair involved on a miss. Again this detection scheme could be used to improve the reuse cache, for instance on a tag array hit missing in the data array. Chaudhuri et al. [7] propose to track the reuse behavior within the private caches and utilize it to estimate reuse in the SLLC when the lines are evicted from private caches. Such a predictor could be used to change the fixed reuse prediction performed in the reuse cache whenever a line is evicted from private caches.

#### 2.3.2 Frequency-based replacement

Frequency-based replacement algorithms classify according to the number of times cache lines have been accessed, giving more priority to the more accessed ones. The *least frequently used (LFU)* approach relies on the access frequency of cache lines to attempt to avoid harmful patterns that may evict useful lines [33]. Although frequency-based replacement improves the performance of applications with frequent *scans*, it is not good if the workload exhibits temporal locality.

In a way, our SLLC replacement proposals are a very simple form of a frequency-based replacement since lines get classified in only two counts: either those accessed one time or more than one time during their stay in the SLLC. However, LRR and NRR also work correctly if the workload exhibits temporal locality because they use recency within each segment.

#### 2.3.3 Dead-block prediction

Dead-block prediction tries to identify dead lines by means of hardware predictors [27, 31, 36]. For instance, prediction relies on recording the instruction sequences performing the last touch of a given line, or counting the number of accesses performed on a line before it gets replaced. When a line experiences again some of those past behaviors, it is tagged as dead and becomes a replacement candidate. Dead-block prediction requires expensive hardware to predict and store metainformation. Khan et al. [27] introduce sampling dead block prediction, a technique aimed to reduce the storage of metainformation of the predictor. This mechanism samples program counters (PCs) to determine when a cache block is likely to be dead. Rather than learning from accesses and evictions from every set in the cache, a sampling predictor tracks a small number of sets using partial tags.

Lai et al. [31] proposed Block Predictors, predictors that accurately identify if a cache line is dead. The mechanism evicts those cache lines detected as dead and prefetchs data into them. Instead of using PCs to predict wether a cache line is dead, Liu et al. [36] predict dead blocks based on bursts of accesses to a cache block. A cache burst begins when a block becomes MRU and ends when it becomes non-MRU. The authors claim that cache bursts are more predictable than individual references because they hide the irregularity of individual references.

The underlying behavior of lines assumed in dead-block prediction and reuse-based replacement is the same: a big fraction of cache lines is dead at any moment. However, the opportunity that shows up is exploited in different ways.

Our mechanisms classify a priori all lines entering the SLLC as dead (since we realize most of them are indeed touched once). A line becomes alive once it is referenced a second time during its stay in the SLLC.

#### 2.3.4 Replacement on inclusive hierarchies

In inclusive hierarchies, the core caches absorb most of the temporal locality and the hot lines may lose positions in the LRU stack of the SLLC, up to the point of being evicted. A recent paper shows ways to solve this problem by identifying lines in the core caches and preventing their replacement in the SLLC [22]. Three ways are proposed: sending hints to the SLLC about the core accesses (*TLH*), identifying temporal locality by early invalidation of lines in the core caches (*ECI*), or querying the core caches about the presence of the victim lines (*QBS*).

We also address this problem by using the information present in the coherence directory, assuming non-silent eviction of clean blocks in the private caches. However, our main contribution is the design of two replacement algorithms that exploit reuse locality with the same hardware cost than those used in commercial processors.

#### 2.4 HOW TO DECOUPLE THE SLLC TAG AND DATA ARRAYS?

In recent years, there have been many innovations for improving the performance of the SLLC. In spite of this huge quantity of research, most of innovations only achieve to improve system performance within 5%. One of the contributions of this thesis, the reuse cache, targets the SLLC efficiency in a different way, proposing to downsize the SLLC data array while maintaining the average performance. In order to achieve that objective, our proposal relays on a decoupled tag and data arrays. Next we show works used similar types of decoupled designs.

Using pointer indirection appears as a natural solution when tag/data decoupling is required. Several authors have used this idea for different purposes. Regarding sectored caches, a common idea is to share a number of data subsectors among a set of tag sectors, instead of the conventional 1:1 mapping between a tag sector and its data subsectors. Seznec suggests decoupling to conciliate a low tag implementation cost with a low miss ratio [52], while the decoupling proposed by Rothman et al. aims to reduce cache space requirements [50].

Chishti et al. propose the NuRAPID cache, that decouples tag lookup and data placement in order to reduce the average access latency in dynamic non-uniform cache architectures [9].

Tag/data decoupling has also been proposed in the V-way cache by Qureshi et al. to achieve a high associativity and reduce the number of conflict misses in the non-inclusive last level cache of a single-processor system [48]. The V-way cache stores the same number of items in tag and data arrays and inserts into the cache all the data requested by the lower level caches. However, V-way relies on additional tag space to reduce conflicts in the set associative tag array. In the data array, V-way requires a global replacement policy based on use frequency. In contrast, the reuse cache objective is to reduce the cache size while keeping performance and inclusion benefits. It stores more tags than data lines and tries to only retain lines showing reuse. The additional tag space in the reuse cache allows to maintain inclusion and track reuse. Furthermore, its data array does not require a global replacement algorithm.

Two recent works are directly related with our reuse cache contribution [37, 69]. The cache organization relies in tag/data decoupling

to retain tags inclusion property and to use a selective allocation policy of lines in a cache miss.

NCID uses additional tags in order to maintain tag inclusion of the private caches, though the data lines of those private caches are not necessarily present in the data array. So, NCID allows SLLC data to be non-inclusive or exclusive while retaining the inclusion property on tags. Moreover, many NCID architectural options are presented and evaluated. One of them uses NCID to support a selective allocation policy to address transient data. Selective allocation allocates tag and data for a randomly chosen 5% of the lines and only tag for the remaining 95%. Set dueling is proposed to select between normal fill or selective fill policies.

Instead of random selection, the reuse cache data array selects lines with potential for reuse. In the reuse cache, tags without allocated data are indeed used to maintain inclusion, but also to detect reuse. Once a line experiences such a reuse it is written in the data array. Both, the replacement algorithms of tag and data arrays are designed with the objective of identifying and prioritizing reused lines. Set dueling is not needed.

Lodde et al. [37] use cache line state and coherence messages to classify lines as private or shared. Such information is used to selectively allocate only shared lines in the data array in order to reduce data array size. This organization requires to move tags within the tag array when the classification of a line changes. The information used by the selective allocation policy does not take reuse into account. Thus, transient private cache lines are put into the shared data array, increasing required data array size. Our proposal relies in reuse locality detection, independently of which private cache requests the line. Thus shared lines are implicitly allocated in the data array and private lines are only allocated if reuse locality is detected.

#### EXPERIMENTAL FRAMEWORK

#### SUMMARY

In order to evaluate each of the contributions of this thesis, the associated mechanisms were faithfully modeled and these models incorporated to a simulator. The simulator was then used to run a set of benchmarks and the results of that simulations were employed to infer the validity of the hypotheses. The experimental framework is explained on this chapter: baseline system, simulator, workloads, and metrics.

#### 3.1 INTRODUCTION

This chapter explains the experimental framework used during this thesis. Here it is shown the common part of this experimental framework, meaning that in the evaluation of some of our contributions the configuration of the considered system varied, workloads were built in an alternative way, or the metrics used to evaluate our proposals were different or enlarged. In such points, this document explains the corresponding changes.

The remaining of this chapter is organized as follows. Section 3.2 shows the baseline CMP system has been considered along this thesis. Section 3.3 presents the *Simics* full-system simulator and *ruby*, a plugin for Simics by the University of Wisconsin Madison which allowed us to model the memory hierarchy of our system. And finally Section 3.4 discusses about the types of workloads used in this thesis and the different metrics used to evaluate them.

#### 3.2 BASELINE SYSTEM

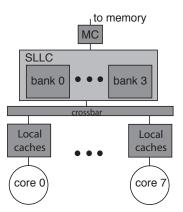

Figure 3.1 shows the CMP system we have used during this thesis. It comprises eight in-order SPARC V9 cores and a hierarchy of memory composed by three levels of cache. The first level is private to each core and it is composed by split instruction and data cache memories. The second level is private and unified (data and instructions). And last, the third level is shared among all the cores in the system. All the three cache levels are write-back write-allocate. Table 3.1 shows remarkable parameters of the considered hierarchy.

Figure 3.1: Baseline system overview

The third is the last level of our hierarchy of cache memories. We consider an 8 MB LLC, split in four banks which are shared among all the cores in the CMP. The banks are cache line interleaved to facilitate a homogeneous share of accesses, excepting on the ABS prefetching proposal, where they were interleaved using operating system page size to avoid inter-bank interference. The SLLC is accessible through a crossbar that connects the eight L2s to the four SLLC banks. Inclusion is enforced at the SLLC, meaning that a cache line is inserted at the SLLC when it is inserted into some L1 or L2, and when a cache line is evicted from the SLLC, it is also removed from any L1 or L2 that could have a copy.

An invalidation directory-based MOSI coherence protocol is implemented to maintain the private caches coherent. The directory is distributed among the SLLC banks, containing its information along with the tag of each cache line.

The memory system comprises 4GB of DDR3 DRAM per core which are accessed trough one memory channel. The memory runs at one quarter of the frequency of the processor.

#### 3.3 SIMULATOR

In order to perform experimental evaluations of our proposals, we used the *Simics* simulation platform [40]. Simics provides functional models of all the devices included in a system (i/o, network, hard disks, etc...), allowing full-system simulation of multi-processor systems. At the same time it is able to simulate a wide range of cpus

| Private L1 I/D     | 32 KB, 4-way LRU replacement, 64 B line size,<br>1-cycle access latency                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Private unified L2 | 256 KB, 8-way LRU replacement, 64 B line size,<br>7-cycle access latency                                                                              |

| Shared L3          | 8 MB inclusive (4 banks of 2 MB each), 64 B interleaving, 64 B line size. Each bank: 16-way, LRU replacement, 10-cycle access latency. 16 demand MSHR |

| DRAM               | 1 rank, 16 banks, 4 KB page size,<br>Double Data Rate (DDR3 1333Mhz).<br>92-cycle raw access latency                                                  |

| DRAM bus           | 667Mhz, 8 B wide bus, 4 DRAM cycles/line,<br>16 processor cycles/line                                                                                 |

Table 3.1: Baseline system configuration

at the instruction set level, e.g. ARM, SPARC, x86, MIPS, and Alpha. Simics run with hypervisor privileges, allowing to execute unmodified real operating systems; during this thesis, the evaluated systems were managed by the *Solaris 10.0* operating system.

To accurately simulate the memory hierarchy of a CMP model we used the *ruby* plugin from the *GEMS Multifacet toolset* [41], publicly available thanks to the University of Wisconsin. This plugin is loaded into the Simics simulator to capture all the memory access operations, modeling their latency with cycle accuracy. Ruby provides faithful models of all the memory hierarchy components from the cache controllers to the switches of the Network-on-chip interconnect. Buffering and blocking of components due to lack of resources are always considered.

During this thesis many of the components of ruby have been modified or enlarged to faithfully model each one of our proposals; including a model of the memory controller that implements the DRAM DDR3 protocol. During the implementation of our ABS controller this model was fundamental in order to accurately model the overhead that prefetching provoked on the memory hierarchy. The model reflected the status of every page of memory, queues, bus occupancy, and the scheduling policy, to observe how they were affecting each memory operation. Other modifications we included in GEMS are clarified and explained at the methodological part of each chapter of this dissertation.

## 3.4 WORKLOADS AND PERFORMANCE EVALUATION

In order to evaluate how our proposals affect the behavior of a wide range of CMP systems, two different types of workloads have been set up. A first group of workloads is composed by multiprogrammed workloads made of sequential applications from the *SPEC CPU 2006* suite of benchmarks. A second group of workloads is composed by parallel applications from the suites *PARSEC* [5] and *SPLASH-2* [66].

### 3.4.1 Multiprogrammed

In a multiprogrammed workload, as many sequential applications as cores the system has, are running at same time. This kind of workloads represents scenarios we can find from our desktop, where a web browser is running at the same time that a video player, to a server, where applications of very different nature run at the same time.

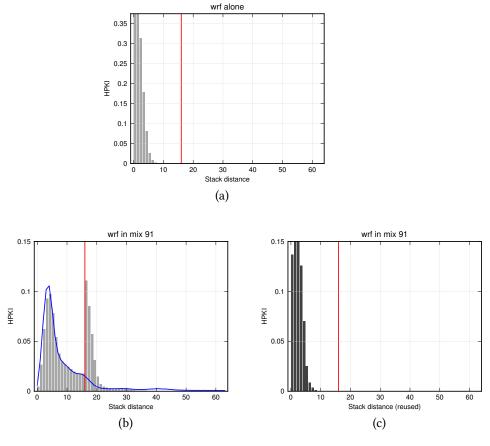

The employed multiprogrammed workloads are composed by applications from among all the 29 included in the SPEC CPU 2006 benchmark suite. Applications were firstly run until completion in a native machine. Their initialization phases where identified by using hardware counters. Groups of eight applications were randomly chosen to form workload mixes. Once in simics, the applications forming a workload mix were executed together, binding each application to a core in order to avoid migration effects. A number of instructions as long as the longest initialization phase of the applications composing the workload mix was fast-forwarded. At that point a checkpoint was taken. The average number of MPKI each application shows at the moment of taking the checkpoint at each cache level of the hierarchy is shown in Table 3.2, it is the average for all the mixes where each application appears.

In order to evaluate a microarchitectural proposal in a given work-load mix, its corresponding checkpoint is read from Simics. Then, the ruby module is loaded with the configuration which mimics the pro-

| Application | L1   | L2   | LLC  | Application | L1   | L2   | LLC  |

|-------------|------|------|------|-------------|------|------|------|

| perlbench   | 3.7  | 0.8  | 0.6  | povray      | 11.0 | 0.3  | 0.3  |

| bzip2       | 8.2  | 4.3  | 2.1  | calculix    | 13.8 | 3.7  | 1.5  |

| gcc         | 21.8 | 7.1  | 6.2  | hmmer       | 2.9  | 2.2  | 1.7  |

| bwaves      | 20.3 | 19.6 | 19.6 | sjeng       | 4.2  | 0.5  | 0.5  |

| gamess      | 75.3 | 46.2 | 28.6 | GemsFDTD    | 25.8 | 25.7 | 21.6 |

| mcf         | 22.9 | 22.2 | 18.1 | libquantum  | 36.6 | 36.6 | 36.6 |

| milc        | 21.6 | 21.6 | 21.5 | h264ref     | 3.5  | 0.7  | 0.6  |

| zeusmp      | 12.3 | 6.4  | 6.3  | tonto       | 4.88 | 0.86 | 0.52 |

| gromacs     | 8.71 | 5.91 | 5.91 | lbm         | 68.1 | 39.2 | 39.2 |

| cactusADM   | 13.9 | 1.4  | 0.7  | omnetpp     | 7.3  | 4.4  | 1.2  |

| leslie3d    | 29.5 | 18.1 | 17.7 | astar       | 6.9  | 0.9  | 0.7  |

| namd        | 1.4  | 0.2  | 0.1  | wrf         | 4.1  | 1.6  | 0.5  |

| gobmk       | 9.5  | 0.5  | 0.4  | sphinx3     | 13.8 | 8.0  | 6.3  |

| dealII      | 2.3  | 0.3  | 0.3  | xalancbmk   | 8.2  | 7.0  | 6.4  |

| soplex      | 6.7  | 5.8  | 4.8  |             |      |      |      |

Table 3.2: Average MPKI at each cache level

posal to study. The whole hierarchy is then warmed, normally during 300M cycles, after that, statistics are cleaned and performance accounting starts. The duration of the simulation is given in system cycles, during this thesis we have normally used 700M cycles long simulations.

The metric considered to evaluate the behavior of the different proposals when multiprogrammed workloads are employed is the geometric mean of the speedup of each application appearing in the workload mix. Given that duration of simulations is fixed and equal for all the proposals, what is employed in order to calculate speedups are the number of executed instructions. Equation 3.1 formally shows this metric.

Speedup =

$$\sqrt[n]{\prod_{i=1}^{n} \frac{I_i^A}{I_i^{base}}}$$

(3.1)

$IPC_i^A$ : Number of executed instructions of program i when run in system A  $IPC_i^{base}$ : Number of executed instructions of program i when run in baseline system

## 3.4.2 Parallel

The parallel applications evaluated in this thesis are five applications of *SPLASH-2* [66] and *PARSEC* [5] suites. The first one is a very well known benchmark suite of scientific parallel programs, while the second focuses on emerging workloads and was designed to be representative of next-generation shared-memory programs for chipmultiprocessors.

Table 3.3 gathers the applications we selected for our evaluation. They are those applications from both suites having more than 1 MPKI in a 8-MB SLLC. Each application spawns in its parallel phase as many threads as processors are in the system. We utilize *simmedium* input set for PARSEC applications and a 1026x1026 grid for *Ocean*. Performance statistics are only taken in the parallel phases.

Parallel applications should be run until completion when meaningful results are desired, or at least some work-oriented metric should be considered [1]. In our simulations we have observed that no

|      | canneal | facesim | ferret | vips | ocean |

|------|---------|---------|--------|------|-------|

| MPKI | 4.48    | 3.45    | 1.27   | 1.74 | 13.35 |

Table 3.3: MPKI of the selected parallel applications in the LLC of the baseline system

OS activity appeared when parallel applications were run and moreover the ratio of load of work among the different threads was practically constant between simulations, thus sampling seems to be a reasonable option to evaluate this type of applications. Thus, as only one application has been run until completion (OCEAN) and because of the huge simulation time would be needed to simulate them completely, the rest of the applications were evaluated using a technique similar to the one used for multiprogrammed workloads.

In order to evaluate a microarchitectural proposal in an application can not be run until completion, the corresponding checkpoint and ruby configurations are loaded and the whole hierarchy is warmed during 300M cycles. After that, statistics are reset and performance accounting is performed during 700M cycles.

Processor throughput is used as performance metric, meaning that given that duration is fixed and the same for all of our simulations, in order to compare different proposals, the total number of executed instructions is compared. Equation 3.2 formally shows this metric.

Speedup =

$$\frac{\sum_{i=1}^{n} I_{i}^{A}}{\sum_{i=1}^{n} I_{i}^{base}}$$

(3.2)

$IPC_i^A$ : Number of executed instructions of core i in system A  $IPC_i^{b\,as\,e}$ : Number of executed instructions of core i in baseline system

# Part II

# ADJUSTING PREFETCHING AGGRESSIVENESS

This second part of the thesis comprises only one chapter. Chapter 4 contains our contribution *Low-Cost Adaptive Controller for Prefetching in a Banked SLLC (ABS)*. The aim of this proposal is to increase the SLLC efficiency by adjusting the prefetching aggressiveness associated to each core of a CMP.

# ABS PREFETCHING

#### SUMMARY

On a multicore system fitted with a shared Last-Level Cache, prefetch induced by a core consumes common resources like shared cache space and main memory bandwidth. The uncontrolled use of the SLLC space by prefetching could lead to a paradoxical situation where this technique becomes harmful for the system performance. In order to avoid such situation prefetching aggressiveness should be controlled from an overall system performance standpoint. Given it is usual to find a broad spectrum of applications running at the same time in modern CMPs, it seems natural to adjust the prefetching aggressiveness associated to each core independently.

This chapter presents ABS, a low-cost controller that runs stand-alone at each LLC bank without requiring inter-bank communication. Following a hill-climbing approach, the mechanism is able to adapt the prefetching aggressiveness associated to each core in the system gathering only bank-local metrics.

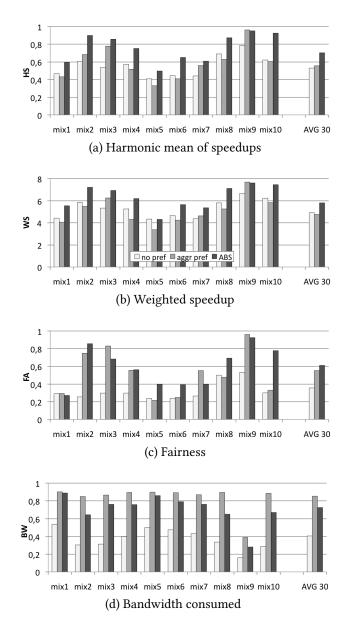

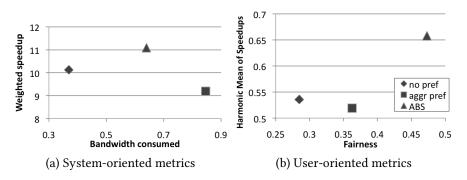

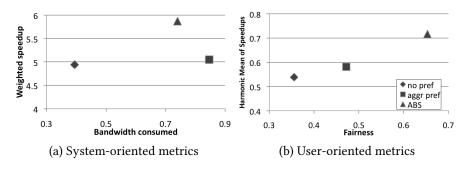

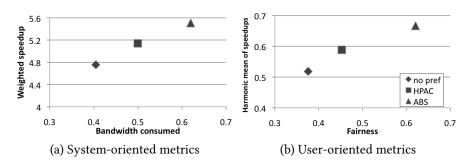

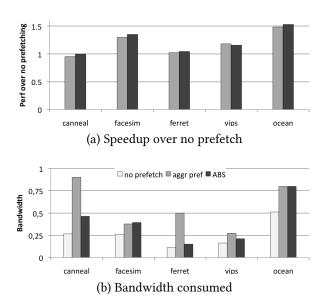

Using multiprogrammed SPEC2K6 workloads, our analysis shows that the mechanism improves both user-oriented metrics (Harmonic Mean of Speedups by 27% and Fairness by 11%) and system-oriented metrics (Weighted Speedup increases 22% and Memory Bandwidth Consumption decreases 14%) over an eight-core baseline system that uses aggressive sequential prefetch with a fixed degree. Similar conclusions can be drawn by varying the number of cores or the LLC size, when running parallel applications, or when other prefetch engines are controlled.

#### 4.1 INTRODUCTION

Hardware data prefetch is a very well known technique for hiding the long latencies involved in off-chip accesses. It tries to predict memory addresses in advance, requesting them to the next level, and loading the lines into the cache before the actual demands take place. Several commercial multicore processors implement some form of hardware data prefetch [11, 32].

Prefetches may be initiated in the first-level caches or directly from events occurring in the SLLC, but in the end the prefetches reach the SLLC and interfere with each other. That is, prefetches issued on behalf of one core may evict LLC lines previously allocated by other cores, either by a memory instruction or a prefetch request. In addition, the prefetch activity originated from a single core can reduce the overall available bandwidth, potentially increasing the latency seen by the demands or prefetches coming from the rest of cores.

Most prefetch proposals in multiprocessors deal with systems having only private caches [6, 14, 29, 57, 61], while prefetch for shared caches has received little attention [15].

Ebrahimi et al. [15] tackle for the first time the problem of reducing the prefetch inter-core interference in a chip multiprocessor with a shared LLC. They propose the *Hierarchical Prefetcher Aggressive-ness Control (HPAC)* mechanism, that monitors several global indexes (prefetch accuracy, inter-core pollution, and memory controller activities) to adjust the prefetch aggressiveness of each core. This assumes a centralized implementation of the LLC, internally organized in banks but with a single access port (see Figure 4.1a). Thus, the global aggressiveness control and associated hardware structures are also centralized.

Figure 4.1: Last Level Cache organizations

To the best of our knowledge, our contribution is the first work where prefetch is studied in a multicore system fitted with a *banked* shared LLC, see Figure 4.1b. We assume an LLC organized in independent cache banks with an access port each, and an interconnection network attaching cores to cache banks (a crossbar is assumed, but other topologies can be considered) [28, 30]. Each bank is internally sub-banked in order to provide a higher throughput. This kind of SLLC is already mainstream because independent banks add layout flexibility and increase access bandwidth. Commercial processors from AMD, Sun, Intel, or IBM are using this design [11, 28, 30, 32].

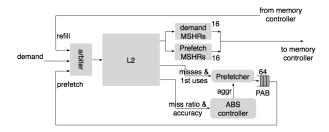

In this scenario, we introduce the *ABS controller*, an Adaptive controller for prefetch in a Banked Shared LLC. ABS controllers are installed in all the LLC banks which are already fitted with a prefetch engine. Each ABS controller runs autonomously and gather local statistics to set the prefetch aggressiveness for each core in the bank it controls in order to maximize the *overall* system performance using a hill-climbing approach. Therefore, a given core is allowed to prefetch with different aggressiveness on different banks of the LLC.

Isolation between banks is a key factor of our proposal, meaning that both the ABS controller and the prefetcher in a bank are not influenced by their peers at other banks. Bank isolation achieves two essential benefits, namely *i*) the prefetches generated from a given bank target itself, and it will always be possible to filter useless prefetches by looking up in the bank, thus saving memory bandwidth, and *ii*) communicating prefetchers or ABS controllers among banks is not required, removing the need for a dedicated interconnection network or extra traffic in the existing one. As discussed in Section 4.5.2, bank isolation can be achieved by selecting a proper address interleaving among banks or by adjusting the prefetch distance.

Our results show that an eight-core system with ABS controllers running multiprogrammed SPEC2K6 workloads improves in both user-oriented metrics and system-oriented metrics over a baseline system with a fixed degree sequential prefetch. The results are consistent when varying the number of cores or LLC sizes. ABS control can be applied to other prefetch engines as long as they are able to operate at different aggressiveness levels. Specifically, we introduce ABS-controlled sequential streams. A comparison with HPAC-controlled sequential streams, such as that proposed by Ebrahimi et al. [15], shows higher performance at a very small fraction of the cost. Furthermore, when running multithreaded workloads from *SPLASH-2*

[66] and *PARSEC* [5], the ABS controllers also reduce the execution time and the consumed bandwidth over the baseline system.

The remaining of the chapter is structured as follows. Section 4.2 describes the motivation behind the work. Section 4.3 gives some background and reviews related work. Section 4.4 introduces the ABS controller. Section 4.5 presents the prefetch framework. Section 4.6 shows the methodological differences respect to what was presented in Chapter 3. Section 4.7 shows the results when ABS controllers are evaluated in a variety of situations, and Section 4.8 discusses and summarizes the contribution.

#### 4.2 MOTIVATION

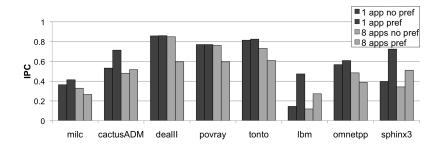

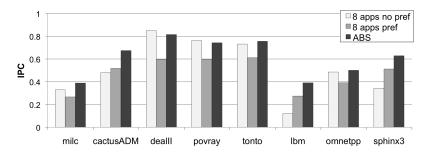

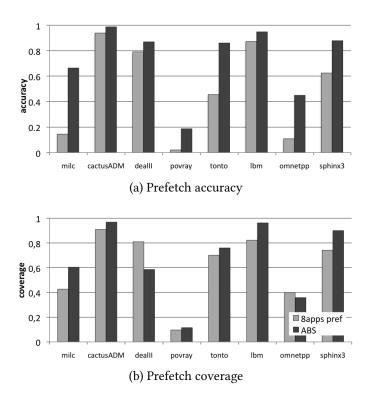

Figure 4.2 shows instructions per cycle (IPC) for eight SPEC2K6 applications running on a system with eight cores and a 4MB shared LLC. The simulation details are shown in Section 4.6. The figure shows four bars for each application. The first two bars represent programs running alone in the system, either without prefetch or with an aggressive (degree 16) sequential tagged prefetch (see Section 4.3). The last two bars represent the eight applications running together, either all without prefetch or all with the former aggressive prefetch turned on. When comparing the systems with prefetch (second and fourth bars), significant performance losses appear when resources are shared among cores. Note that prefetch involves virtually no performance loss in any application when running alone (first and second bars), while it causes losses in 5 out of 8 applications when running all together (third and fourth bars). Therefore, in order to boost the shared LLC performance by means of prefetch, a mechanism to control aggressiveness is called for. Such a mechanism should consider global metrics to realize when the prefetch activity of a core harms the overall system performance and it should be decreased in spite of the improvement achieved by that core.

As figure 4.2 highlights, the benefit obtained by an application due to prefetch can decrease or even turn into losses if prefetch is simultaneously active in all cores. Therefore, our goal is to design a mechanism that dynamically controls the prefetch aggressiveness of each core in order to maximize system performance.

The impact on system performance can be assessed using global indexes such as aggregated IPC or shared LLC miss ratio. Both are

Figure 4.2: IPC for eight SPEC2K6 applications (mix2) running on an 8-core system with a shared LLC

obtained by adding quantities that are distributed in the cores or the cache banks, respectively. So, a centralized design of the prefetch aggressiveness control requires sending information from the places where events are counted to the centralized control point. Alternatively, we propose to place an ABS controller in each LLC bank. The controller uses bank-local information (i.e. bank miss ratio) to improve bank performance. Improving the performance of every bank will thus improve the system performance.

#### 4.3 BACKGROUND AND RELATED WORK

This section provides with material will be useful in next sections. First, Section 4.3.1 explains the concept *prefetching aggressiveness* that will be used in next sections. And second, Section 4.3.2 presents the *Hierarchical Prefetcher Aggressiveness Control (HPAC)*, to the best of our knowledge, the only proposal in the literature with the aim of controlling the prefetching aggressiveness associated to each core in a CMP.

## 4.3.1 Prefetch aggressiveness

Prefetch aggressiveness is often defined in terms of degree and/or distance. Let us consider a stream of references a processor is going to demand  $(a_i, a_{i+1}, a_{i+2}, ...)$ , where address  $a_i$  has just been issued. A prefetcher can be designed to produce the next k addresses following  $a_i$   $(a_{i+1}, ... a_{i+k})$ , calling k the prefetch degree. Alternatively, or in addition, it can also be designed to produce a single address of a far reference  $(a_{i+d})$ , calling d the prefetch distance. As an example, we recall the sequential tagged prefetcher with degree k [14]. If reference

$a_i$  having the line address V is going to trigger a burst of prefetches ( $a_i$  misses or is the first use of a prefetched line), then the prefetcher will issue the following request burst (V+1,V+2,...,V+k). Another example of a prefetch engine using aggressiveness is the sequential streams as presented in [58]. In that work, aggressiveness was defined as a combination of distance and degree.

## 4.3.2 Hierarchical Prefetcher Aggressiveness Control (HPAC)

To our knowledge, only the Hierarchical Prefetcher Aggressiveness Control (HPAC) presented by Ebrahimi et al. [15] has faced the problem of adjusting prefetch aggressiveness on a shared LLC.

We notice four main differences between that work and the present one:

- 1. While HPAC resorts on computing the prefetching aggressiveness by means of a set of rules applied to several system variables (a kind of fuzzy controller), while ABS relies on a local search method (a variant of hill-climbing) to minimize a single system variable, the bank miss ratio.

- 2. HPAC was proposed for a centralized LLC with a single access port (see Figure 4.1a). We propose ABS for a cache organized in banks, each one with an access port (see Figure 4.1b).

- 3. HPAC throttles auto-regulated prefetch engines attached to each core. In the original paper, HPAC is evaluated using Feedback Directed Prefetching as the auto-regulated prefetch engine [58]. However, ABS controllers set directly the aggressiveness level of the local prefetchers.

- 4. HPAC uses four global metrics and FDP (as part of HPAC) uses three more local metrics. All these metrics are monitored and compared to ten thresholds (4 for HPAC + 6 for FDP). In contrast, ABS only samples two system variables and only considers one threshold.

A performance and complexity comparison between HPAC and ABS is presented in Section 4.7.4.

#### 4.4 THE ABS CONTROLLER

An *ABS controller* is an adaptive mechanism that sets dynamically the aggressiveness associated to each core on the prefetcher installed in a bank of a banked shared LLC. Every LLC bank has an ABS controller commanding the prefetcher of that bank. Thus the ABS controller of an LLC bank is able to associate different levels of prefetch aggressiveness to each core, and conversely ABS controllers in different banks can associate to the same core different levels of prefetch aggressiveness.

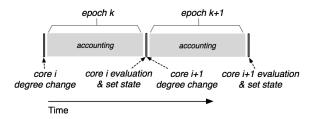

ABS control relies on a hill-climbing approach for finding the minimum of a function (the miss ratio of a bank<sup>1</sup>) that we assume to be dependent on a set of variables namely, the prefetching aggressiveness of each core in the bank. Time is divided into regular intervals called epochs. In each epoch, in order to establish a cause-effect relationship between change in aggressiveness and change in performance, the aggressiveness of only one core (the probed core) is varied. The point is that at each epoch, the observed change in the bank miss ratio is only due to a single aggressiveness change. At the end of the epoch an aggressiveness value is established for the currently probed core and this value remains unchanged until it is probed again. Furthermore, ABS controllers force the prefetch aggressiveness associated to a core to be decreased if its accuracy falls under a given threshold. The operation of ABS controllers involves two aspects: *i*) selection of the core to probe and temporal sampling, and ii) adaptive per-core aggressiveness control.

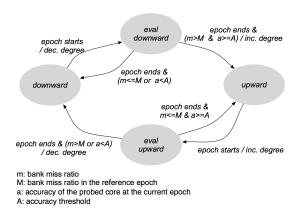

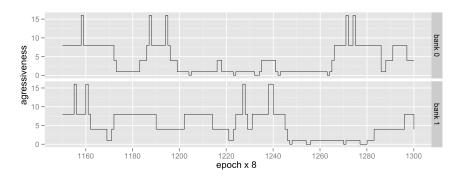

core selection and temporal sampling. At the beginning of each epoch a core is chosen in a round-robin fashion<sup>2</sup> and its current prefetch aggressiveness is changed. Then, at the end of the epoch, the effect of the change is evaluated by comparing the bank miss ratios observed during the current epoch and a reference epoch (Figure 4.3a). The change is undone if the current bank miss ratio is greater than the reference one. Otherwise, the change is confirmed and the current epoch is set as the new reference. So, the core se-

<sup>1</sup> Ratio of bank demand misses to demand requests coming from all cores. Other performance indexes were also tested as the target function, such as global miss ratio, MPKI, or IPC. Although results were similar, these other indexes were discarded because they are more expensive to compute in terms of communication and hardware cost.

<sup>2</sup> A random order was also tested achieving slightly worse results.

lection and temporal sampling guarantee that there is always only one prefetch aggressiveness change between reference and current epochs. That change corresponds to the probed core at each epoch.

At the end of an epoch, an aggressiveness value is established for the currently probed core and this remains unchanged until the core is probed again. Note that if an application remains in a stable phase the ABS controller reaches a steady state only broken by the glitches involved in testing sub-optimal configurations. Hill-climbing processes usually deals with functions that are not time-dependent. Thus, the process stops when no change can be found to improve the value reached. However, we know miss ratio is time-dependent because applications change their behavior over time. This has two important implications for the design of ABS.

- 1. Our algorithm never stops. The combination of aggressiveness able to minimize the miss ratio changes over time and ABS continually seeks that combination.

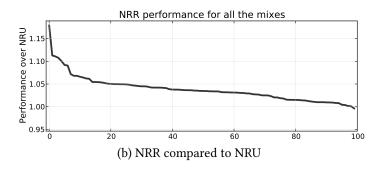

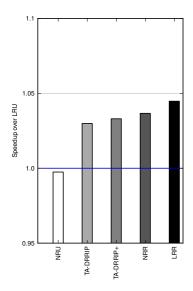

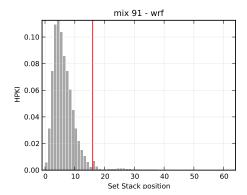

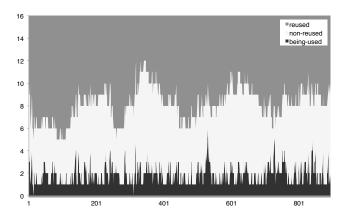

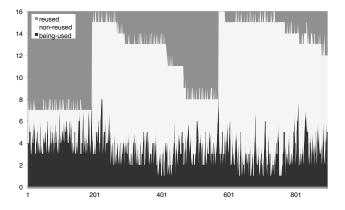

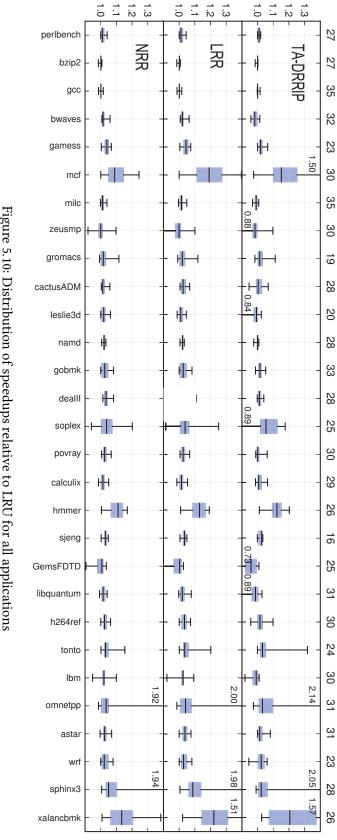

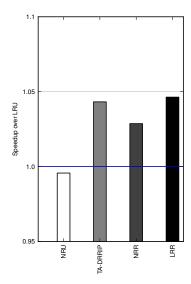

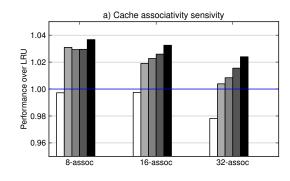

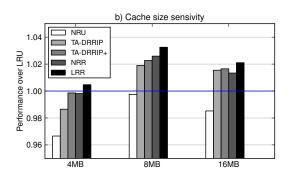

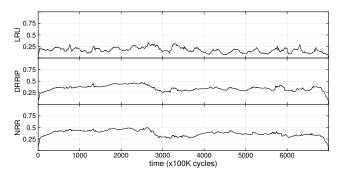

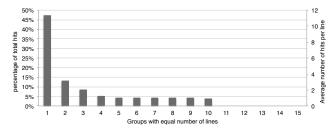

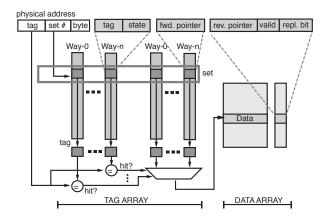

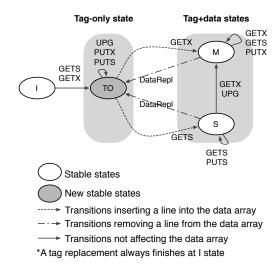

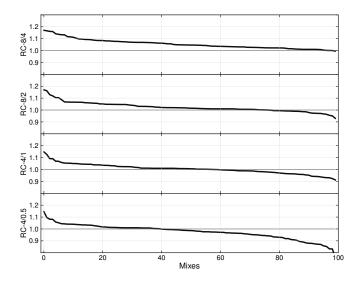

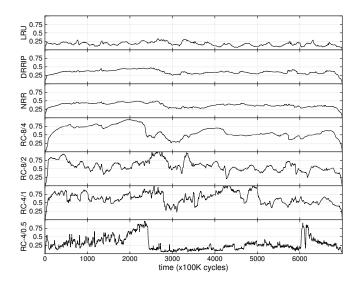

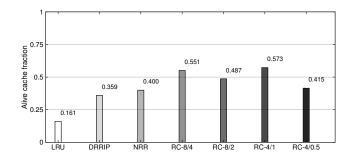

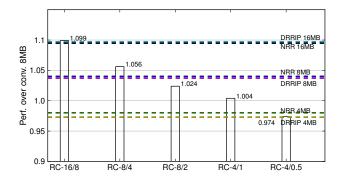

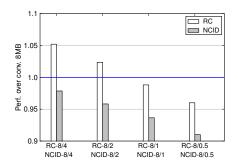

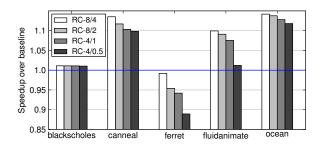

- 2. When the miss ratio reaches the global minimum in the corresponding program phase, ABS will set the current epoch as the reference epoch and the current miss ratio as the rate to beat. So, as a lower miss ratio will no longer appear, ABS will never change the control actions, and worse, a similar behavior may occur during long program phases after reaching a local minimum. In order to remedy this situation, the number of epochs elapsed without updating the reference epoch is counted. When this count is equal to the number of cores, the mechanism sets the last epoch as the new reference. Updating the reference epoch in this way ensures that a new value is taken after probing all cores without experiencing a miss ratio decrease.