## Modulated Nanowire Structures for Exploring New Nanoprocessor Architectures and Approaches to Biosensing

The Harvard community has made this article openly available. Please share how this access benefits you. Your story matters.

| Citation     | Choe, Hwan Sung. 2013. Modulated Nanowire Structures for<br>Exploring New Nanoprocessor Architectures and Approaches to<br>Biosensing. Doctoral dissertation, Harvard University.                                                                                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accessed     | April 17, 2018 4:09:07 PM EDT                                                                                                                                                                                                                                          |

| Citable Link | http://nrs.harvard.edu/urn-3:HUL.InstRepos:11158237                                                                                                                                                                                                                    |

| Terms of Use | This article was downloaded from Harvard University's DASH<br>repository, and is made available under the terms and conditions<br>applicable to Other Posted Material, as set forth at<br>http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-<br>use#LAA |

(Article begins on next page)

## Modulated Nanowire Structures for Exploring

## New Nanoprocessor Architectures and Approaches to Biosensing

A dissertation presented

by

### **Hwan Sung Choe**

to

The Department of Physics

in partial fulfillment of the requirements

for the degree of

### **Doctor of Philosophy**

in the subject of

### Physics

Harvard University Cambridge, Massachusetts April, 2013 © 2013 - Hwan Sung Choe

All rights reserved.

## Modulated Nanowire Structures for Exploring New Nanoprocessor Architectures and Approaches to Biosensing

#### Abstract

For the last decade, semiconducting nanowires synthesized by bottom-up methods have opened up new opportunities, stimulated innovative scientific research, and led to applications in materials science, electronics, optics, and biology at the nanoscale. Notably, nanowire building blocks with precise control of size, structure, morphology, and even composition in one, two, and three dimensions can successfully demonstrate high-performance electrical characteristics of field-effect transistors (FETs) and highly sensitive, selective, label-free, real-time biosensors in the fields of nanoelectronics and nano-biosensing, respectively. This thesis has focused on the design, synthesis, assembly, fabrication and electrical characterization of nanowire heterostructures for a proof-of-concept nanoprocessor and morphology-modulated kinked nanowire molecular nanosensor.

#### Nanoprocessor

Realization of a fully integrated complex circuit such as a nanoprocessor has remained difficult due to issues of assembly and electrical uniformity of nanowire devices. To surmount these obstacles, we have developed a multi-functional nanoprocessor architecture based on programmable non-volatile nanowire transistor arrays. Ge/Si core/shell NWs synthesized by chemical vapor deposition according to the vapor-liquid-solid mechanism are coupled with a rationally-designed dielectric shell stack based on a charge-trapping mechanism to realize nanowire field-effect transistors (NWFETs) with well-defined and programmable gate responses. Controlled integration of individual NWFETs yields reconfigurable charge-trapping NWFET arrays consisting of 496 functional device nodes, capable of complex logic functions such as full-adder with a maximal voltage gain of 10 and input/output (I/O) matching. Significantly, the same device arrays can be re-programmed to perform diverse functions including full-subtractor, multiplexer, demultiplexer and D-latch. These results represent a significant advance in both complexity and functionality of nanoelectronic circuits built by the bottom-up approach. Moreover, the architecture demonstrated here provides a general and scalable paradigm for a fully-integrated nanoprocessor with computing, memory and addressing capabilities.

#### Nano-biosensor

The realization of an electrochemical nano-biosensor that is functional in physiological environments seems unlikely to occur soon, due to the challenges posed by the short Debye length in a high ionic strength solution. Furthermore, development of such a nano-biosensor cannot keep pace with growing demands for a point-of-care or *in vivo* biosensor. To overcome these limitations of conventional electrochemical nano-biosensors, the concept of a kinked NWFET synthesized by rational modulation of morphology and dopant concentration is presented here. This chemical/biomolecular probe is considered and investigated here under physiological conditions. Heavily n-doped (n++)/intrinsic (i)/heavily n-doped (n++) silicon

semiconductor nanowire has been synthesized in a probe-like kinked structure, and modified to form an FET device. Based on models of the NWFET's sensitivity in solution and investigation of reliable surface functionalization to immobilize antibodies, the n-type kinked NWFET biosensor has successfully been demonstrated and verified for sensing cancer markers with Enzyme-Linked ImmunoSorbent Assay (ELISA) method in a microfluidic system at low ionic strength. Furthermore, theoretical analysis of a NWFET biosensor operating with high-frequency modulation predicts new opportunities to sense target proteins at high ionic strength, regardless of protein charge. These results imply that a kinked structural NWFET biosensor with high-frequency measurement will allow realization of a future 3D *in vivo* bioprobe for advanced pathology and proteomics in a single cell.

## Contents

| Acknowledgements           | X    |

|----------------------------|------|

| List of Figures and Tables | xiii |

| List of Publications       | xvii |

## CHAPTER 1 - Introduction

| 1.1           | Overview of nanotechnology and nanoscience                    | 2  |

|---------------|---------------------------------------------------------------|----|

| 1.2<br>hetero | Rational synthesis of semiconductor nanowires and ostructures | 5  |

| 1.3           | Semiconductor nanowire field-effect transistor (NWFET)        | 11 |

| 1.4           | Organization of thesis                                        | 16 |

| Bibliography  |                                                               | 18 |

1

## Part I Programmable multi-functional nanowire array circuit for nanoprocessor

| CHAPTER 2 - Design, synthesis, and characterization of non-volatileNWFET for nanoprocessor building block2 |              |                                                                  | 26 |

|------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------|----|

|                                                                                                            | 2.1          | NWFET for nanoelectronics                                        | 27 |

|                                                                                                            | 2.2<br>eleme | Physical design of charge-trapping NWFET as logic and memory nts | 28 |

|                                                                                                            | 2.3          | Fabrication of core/shell NWFET                                  | 35 |

|                                                                                                            | 2.4          | Fabrication and electrical characterization of CTNWFET device    | 42 |

|                                                                                                            | 2.5          | Conclusion                                                       | 46 |

|                                                                                                            | Biblic       | ography                                                          | 47 |

| CHAPTER 3 - Fully integrated configurable multi-functional CTNWFET crossbar array circuit |                                                                                                 | 50 |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----|

| 3.1<br>multi-                                                                             | Physical design of CTNWFET crossbar array for programmable functional complex circuit           | 50 |

| 3.2                                                                                       | Development of novel CTNWFET toward uniform performance                                         | 56 |

| 3.3                                                                                       | Fabrication of CTNWFET crossbar arrays for circuitry                                            | 59 |

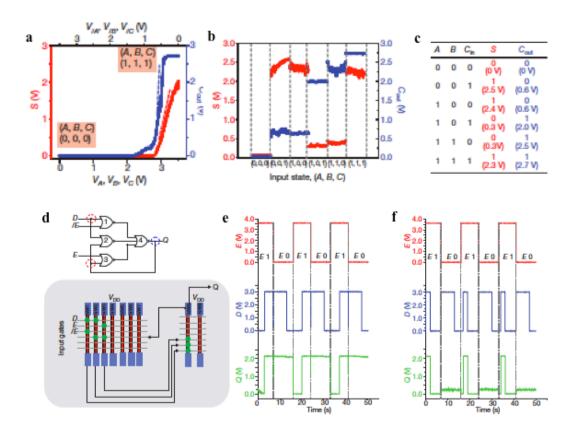

| 3.4<br>compl                                                                              | Demonstration of fully integrated programmable multi-functional ex circuit based on CTNWFET-CAs | 62 |

| 3.5<br>state-o                                                                            | Comparison between nanowire logic tiles and 32-nm of-the-art CMOS logic                         | 71 |

| 3.6                                                                                       | Conclusion                                                                                      | 76 |

| Biblio                                                                                    | graphy                                                                                          | 76 |

# Part II Looking into the NWFET biosensor: critical components and qualifying factors for sensing

| <b>CHAPTER 4</b> - Understanding NWFET biosensor and surface modification |                | 81                                                                 |     |

|---------------------------------------------------------------------------|----------------|--------------------------------------------------------------------|-----|

|                                                                           | 4.1<br>solutio | Theoretical sensitivity of NWFET biosensor in low ionic strength n | 83  |

|                                                                           | 4.2<br>probe   | Rational synthesis of kinked NWFET for a biochemical sensing       | 89  |

|                                                                           | 4.3            | Analysis of surface functionalizations on SiNW                     | 94  |

|                                                                           | 4.4<br>with E  | Analysis of antibody modifications on SiNWFET biosensor<br>LISA    | 103 |

|                                                                           | 4.5            | Conclusion                                                         | 110 |

|                                                                           | Biblio         | graphy                                                             | 111 |

| CHAPTER 5 - A novel kinked nanowire biosensor and opportunities for<br>biomolecular detection under physiological conditions |                                                                                                     |     |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|

| 5.1                                                                                                                          | Biosensing measurement system with microfluidics                                                    | 117 |

| 5.2<br>ionic                                                                                                                 | Biomolecular detection with a kinked NWFET biosensor in low strength solution                       | 122 |

| 5.3                                                                                                                          | Toward biomolecular detection at high ionic strength                                                | 126 |

| 5.4                                                                                                                          | Conclusion and prospects                                                                            | 134 |

| Bibli                                                                                                                        | ography                                                                                             | 134 |

|                                                                                                                              |                                                                                                     |     |

| Appendi                                                                                                                      | <b>x A:</b> Atomic layer deposition                                                                 | 137 |

|                                                                                                                              | <b>x B:</b> Multi-channel measurement system for programming and ization of nanowire logic circuits | 139 |

| Appendi                                                                                                                      | x C: Signal artifacts in biosensing by ionic strength changes                                       | 143 |

To my parents, wife, and daughters

## Acknowledgements

This dissertation is the result of far more than five years of study. Every single page also reflects my relationships with the many distinguished and inspiring people I have met since joining the Lieber research group. I cherish all their contributions to my development and achievements as a scholar and a scientist.

First and above all, I would like to thank my dissertation advisor Professor Charles M. Lieber for instilling in me what a good scientist is. As a mentor and a scientist, Charlie not only fired my passion, inspiration, and devotion to my research by sharing his vision with me, but constantly encouraged me toward future achievements. He exemplifies for me the virtues necessary to become a great scientist: insightfulness, eagerness, diligence, and creativity. Undoubtedly, his lessons and guidance have helped to correct my weak points and forced me to think more critically. So, thank you, Charlie. I am truly honored to be your student.

I would also like to thank my current committee members Professor Hongkun Park and Professor Adam Cohen and my previous committee member Professor Charles Marcus for their mentorship. Even though there was never enough time for personal conversations, your advice inspired passion and energy, and helped me onward in my graduate school life.

To Dr. Hao Yan and Dr. SungWoo Nam, I'm truly grateful for your cordial help and collaboration during the nanoprocessor project. When I joined the Lieber research group, Hao, then a senior graduate student, willingly gave his time to teach me semiconductor nanowire synthesis and device fabrication. SungWoo was a good friend as well as a good research partner in the nanoprocessor and graphene bioprobe projects. Whenever I encountered problems, a

Х

discussion with him would give me a new idea to address them. Our synergistic collaboration often enabled me to solve tough problems and create new breakthroughs. As a mentor and sounding board, he played an important role in the achievement of the novel programmable complex nanocircuit in this thesis.

I also want to thank my current collaborator Leon Xueliang Liu for his collaboration with me on the 3D *in-vivo* bioprobe project. He is a very smart person who quickly absorbs new information. His tendency to persist in asking questions and "probing" the unknown until he finds a solution has been a constant driving force toward progress. Furthermore, Leon is a great debating partner and friend, so in my work with him one plus one equals more than two. Our close collaboration has led to huge progress toward not only theoretical understanding but also reliable demonstration of the novel structural NWFET biosensor in this thesis.

I would like to thank my office mates Dr. Quan Qing, Dr. Thomas Kempa, Dr. Tzahi Cohen-Karni, Dr. James Cahoon, Dr. Wooyoung Shim, Bobby Day and Max Markin. They all acted at times as friends, mentors, listeners and helpers. Whether I felt happy, sad, or frustrated, they shared my joy, sorrow or frustration and lightened the load. I hope to keep in touch with you guys for the rest of my life.

I also want to thank all of my labmates. In particular, I'm grateful to Dr. Ping Xie, Dr. Xiaojie Duan, Dr. Qihua Xiong, Dr. Hong-Gyu Park, Dr. Won-Il Park, Dr. Yajie Dong, Dr. Bozhi Tian, Dr. Brian Timko, Dr. Xiaocheng Jiang, Zhe Jiang, Ruixuan Gao, Jia Liu, and Tian-Ming Fu for discussion and conversation about everything from scientific topics to private concerns. I very much appreciate all of them for creating a family within the Lieber group.

xi

I would like to thank Dr. Shamik Das and Dr. Jim Klemic of the MITRE Corporation. Shamik proposed practical and useful designs and functions based on nanowire crossbar array circuits. Jim has visited the group to discuss results and suggested measurements for improved device characterization.

I would like to thank our senior research associate Dr. Jinlin Huang. As an experienced scientist and born teacher, he tries to give me and everyone in the group inspiration and tough questions about physical principles. Always my discussions with him force me to think more deeply and strengthen my weak points. I also owe him a huge thank you for teaching me electronics and maintaining/managing our group's instruments.

I would like to thank the lab administrator Kathleen. She is my good listener as well as good mentor. Whenever I had trouble, she advised me and it always made it right.

Finally, my deepest gratitude goes to my family for their unflagging love and support throughout my life; my graduate student life, as well as this dissertation, would simply have been impossible without them. I am indebted to my father and mother, Ki-man Choi and Jung-ha Lee. Lastly, thank you to my lovely wife, Seon Ah Lee, and to my lovely daughters, Emily Eunji Choe and Grace Eunhye Choe. All of you are the reason why I am happy, why I can love, and why I can keep moving forward. Thank you very very much for being with me. I loved you too, in my past life, I love you in this life, and I will love you forever in my next life.

xii

## **List of Figures**

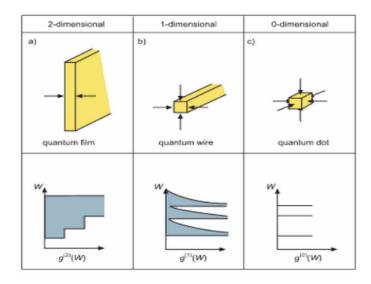

Figure 1-1 | Confined structure in 0D, 1D and 2D and corresponding densities of electron states (pg. 3)

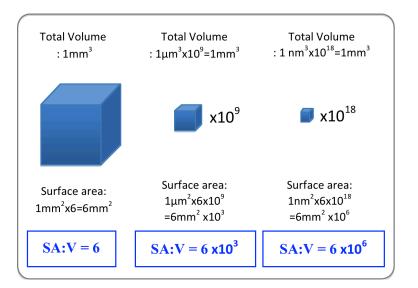

Figure 1-2 | Scheme demonstrating the effect of the increased surface area provided by nanostructured materials (pg. 5)

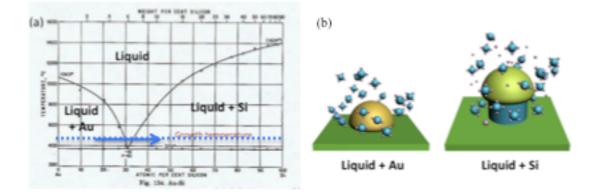

Figure 1-3 | VLS mechanism in phase diagram (pg. 7)

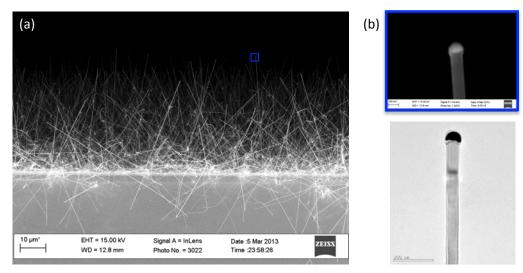

Figure 1-4 | P-type silicon nanowire synthesized by the VLS-CVD method (pg. 9)

Figure 1-5 | Synthesized i-Si/i-Ge core/shell nanowire with CVD-VLS mechanism (pg. 11)

- Figure 1-6 | FET structures (pg. 13)

- Figure 1-7 | Electrical characteristics of NWFET (pg. 16)

- Figure 2-1 | Charge-trapping mechanisms (pg. 30)

- Figure 2-2 | Physical and bandgap structure of simulated CTNWFET (pg. 31)

- Figure 2-3 | Simulation results of NWFET and CTNWFET (pg. 35)

- Figure 2-4 | SiNW transfer (pg. 36)

- Figure 2-5 | Nanowire registration with optical microscope (pg. 37)

- Figure 2-6 | Metal-semiconducting nanowire contacts at room temperature (pg. 40)

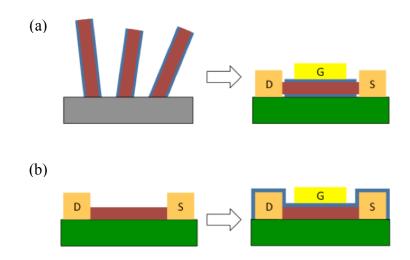

- Figure 2-7 | Two strategies for the fabrication of shells on NWFET (pg. 42)

Figure 2-8 | Electrical performance of CTNWFET (pg. 44)

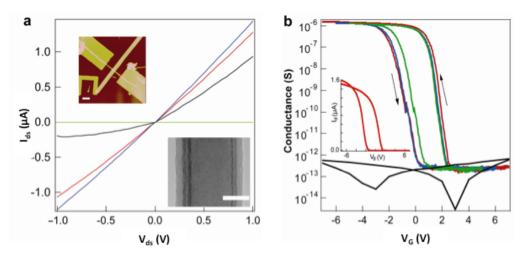

Figure 2-9 | Investigation of CTNWFET performance with four different multi-dielectric shell structures (pg. 46)

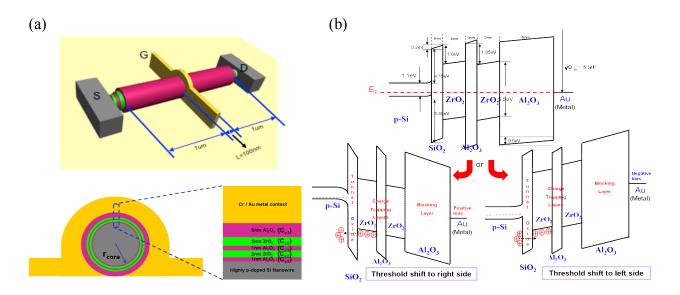

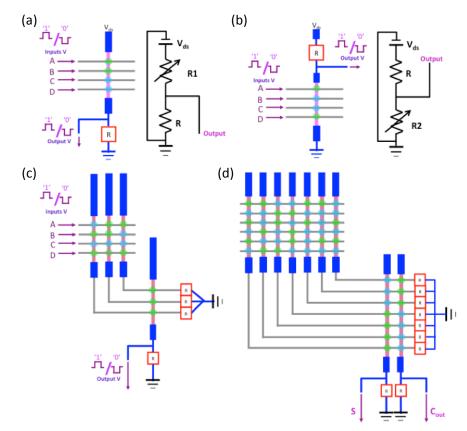

Figure 3-1 | Structure and basic operation of one node based on the programmable CTNWFET (p. 52)

Figure 3-2 | Schemes of  $n \times n$  CTNWFET crossbar array for NOR or OR logics gates (pg. 54)

Figure 3-3 | Nanoprocessor architecture based on the CTNWFET logic tile (pg. 55)

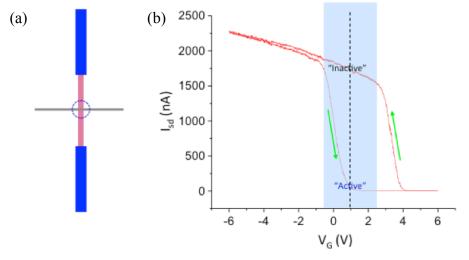

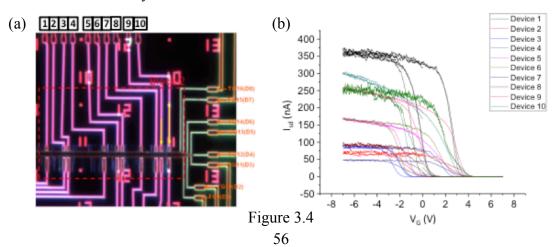

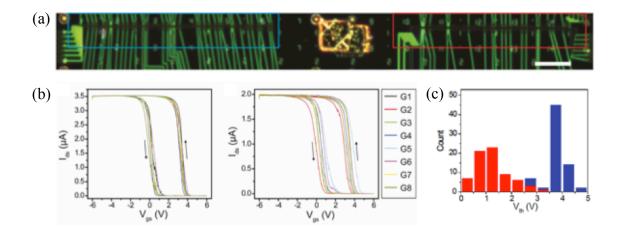

Figure 3-4 | Non-uniform performance of Si-based CTNWFETs (pg. 57)

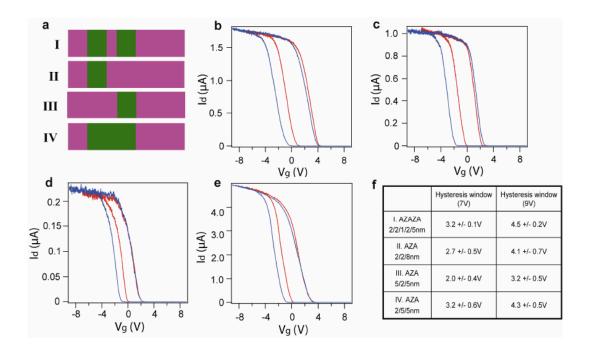

Figure 3-5 | Uniform performance of Ge/Si-based CTNWFET (pg. 58)

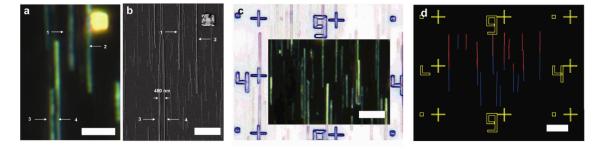

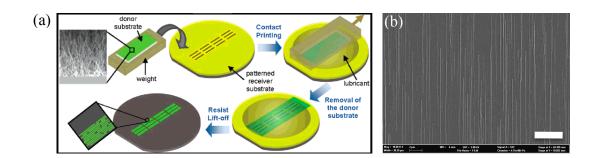

Figure 3-6 | Procedure and result of lubricant-assisted contact printing method for Ge/Si NWs (pg. 60)

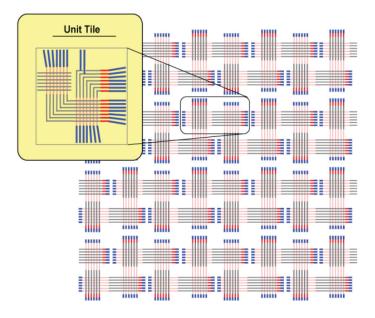

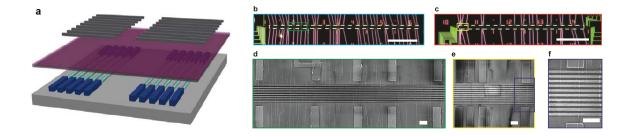

Figure 3-7 | Fabrication and structure of CTNWFET-CA tile (pg. 61)

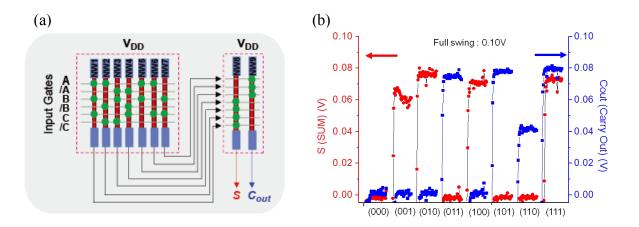

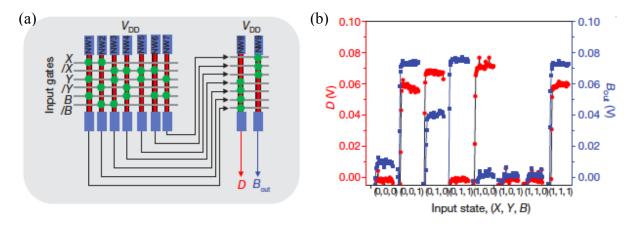

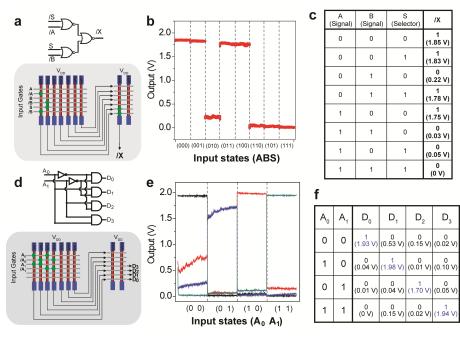

Figure 3-8 | Demonstration of a full-adder circuit (pg. 63)

Figure 3-9 | Demonstration of a full-subtractor circuit (pg. 65)

Figure 3-10 | Multiplexer and demultiplexer circuits implemented in CTNW logic tile architecture (pg. 67)

Figure 3-11 | Demonstration of a full-adder and D-latch based on input/output matching (pg. 70)

Figure 3-12 | Structure and characterization of a typical programmable CTNWFET in the unit tile (pg. 75)

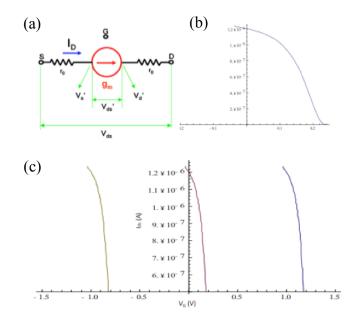

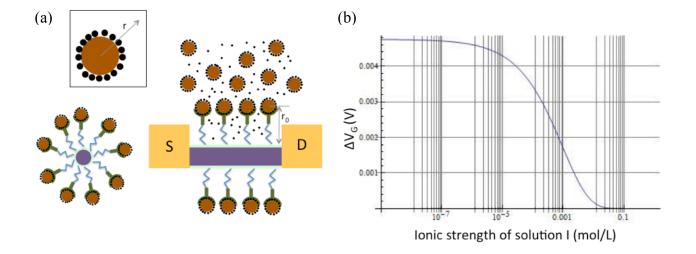

Figure 4-1 | Model and model result for NWFET sensitivity (pg. 88)

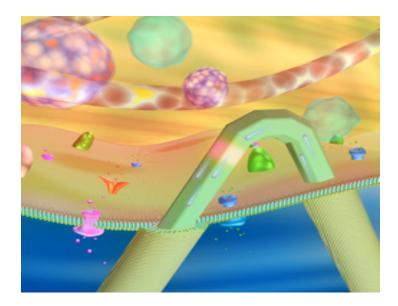

Figure 4-2 | Schematic of a concept of 3D biomolecule/chemical sensing probe for intracellular researches based on kinked NWFET (pg. 90)

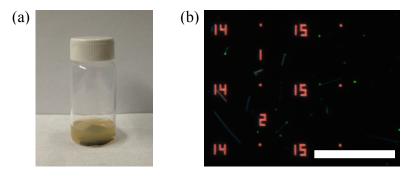

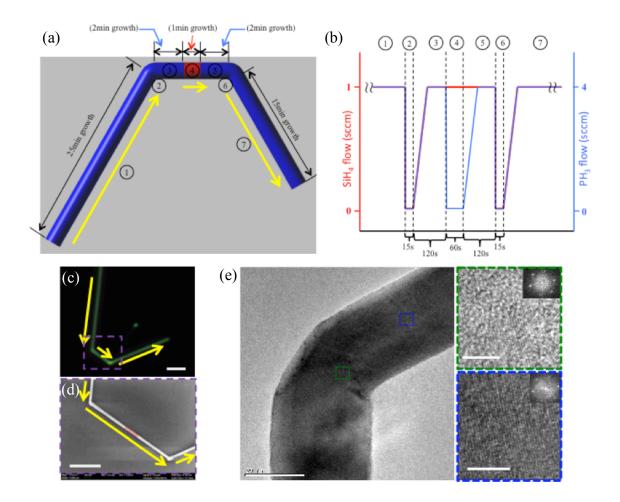

Figure 4-3 | Synthesis of n++/i/n++ kinked nanowire (pg. 92)

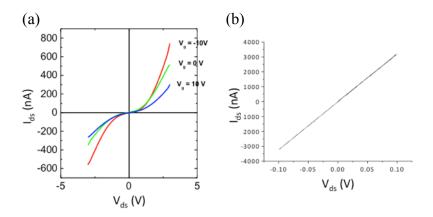

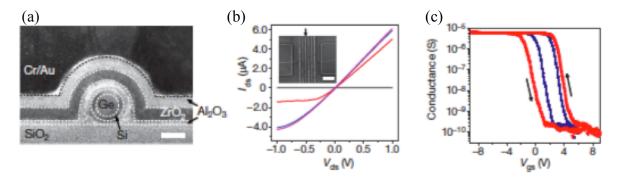

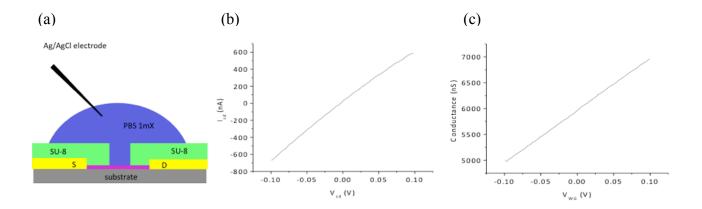

Figure 4-4 | Characteristics of n++/i/n++ kinked NWFET in solution (pg. 94)

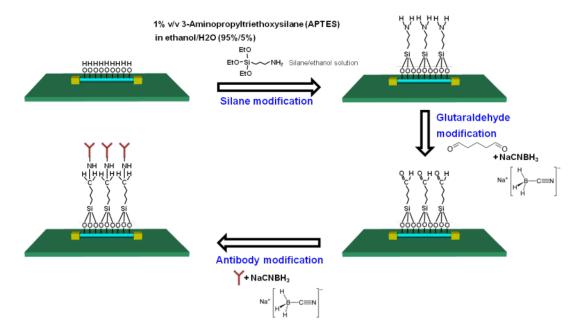

Figure 4-5 | Schematic of SiNW surface modification with APTES and GA to covalently attach antibodies (pg. 95)

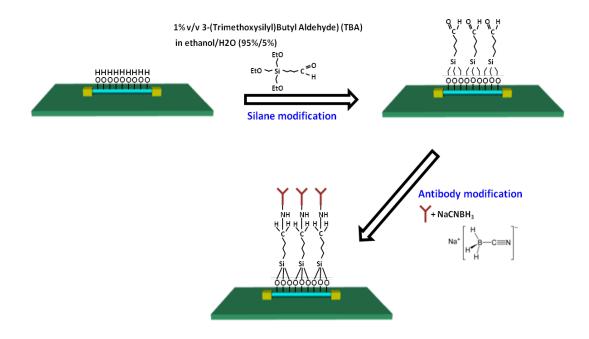

Figure 4-6 | Schematic of SiNW surface modification with TBA to covalently attach antibodies (pg. 96)

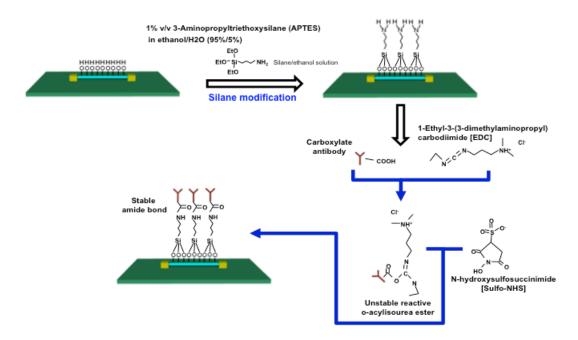

Figure 4-7 | Schematic of SiNW surface modification with APTES and EDC/NHS to covalently attach antibodies (pg. 97)

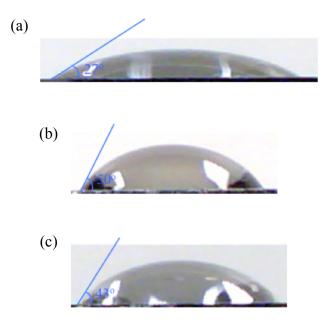

Figure 4-8 | Results of contact angle measurement after oxygen plasma treatment, APTES modification, and GA modification (pg. 99)

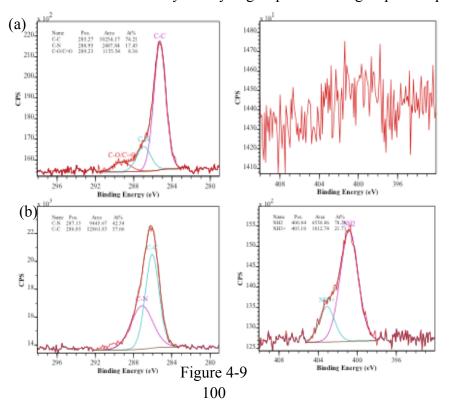

Figure 4-9 | High-resolution XPS spectra of various functionalized surfaces (pg. 101)

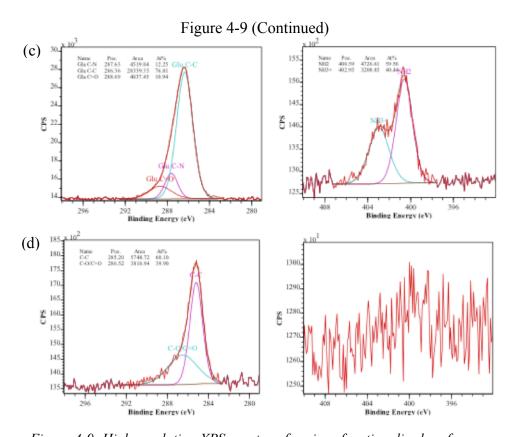

Figure 4-10 | Surface analysis with ATR-FTIR (pg. 102)

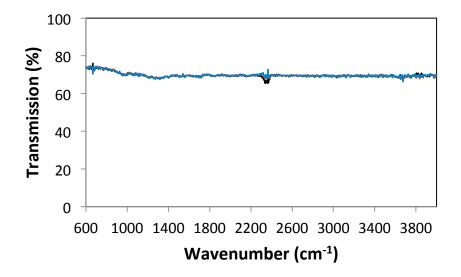

Figure 4-11 | Logarithmic pore size chart of molecular weight for nano- and micro- structures (pg. 105)

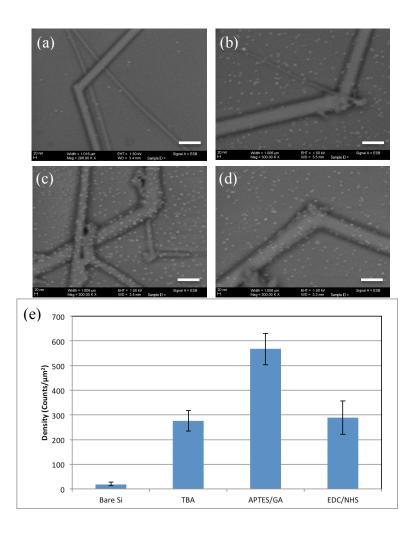

Figure 4-12 | Statistical analysis of anti-PSA density on SiNW after surface modifications based on SEM imaging in ESB mode (pg. 107)

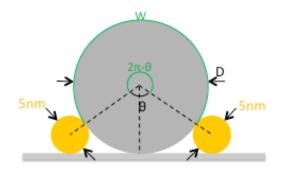

Figure 4-13 | Schematic for calculation of the effective area where 5-nm diameter gold nanoparticles can bind (pg. 109)

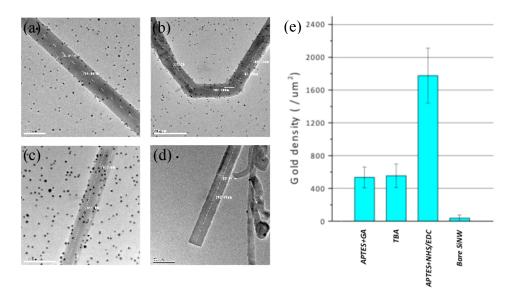

Figure 4-14 | Statistical analysis of anti-PSA density on SiNW after surface modifications based on TEM imaging (pg. 109)

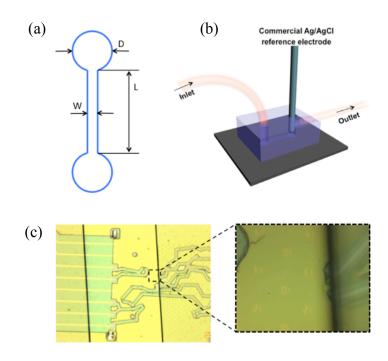

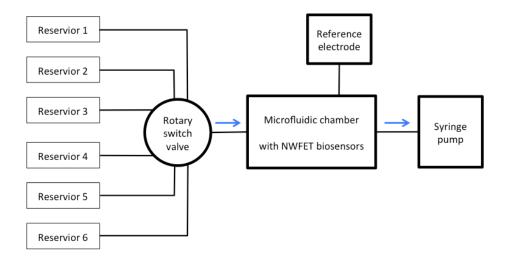

Figure 5-1 | Microfluidics (pg. 119)

Figure 5-2 | Block diagram of the microfluidic system for biosensing (pg. 120)

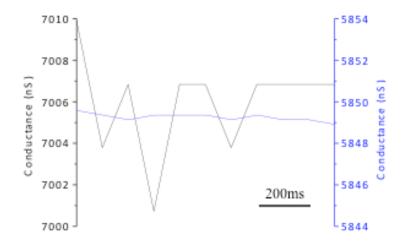

Figure 5-3 | Noise levels for DC and AC measurement (pg. 121)

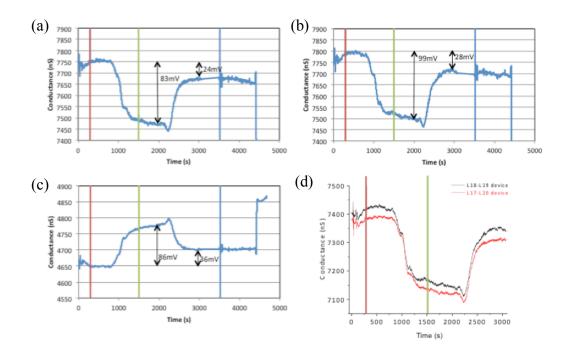

Figure 5-4 | Au-CSA sensing results (pg. 124)

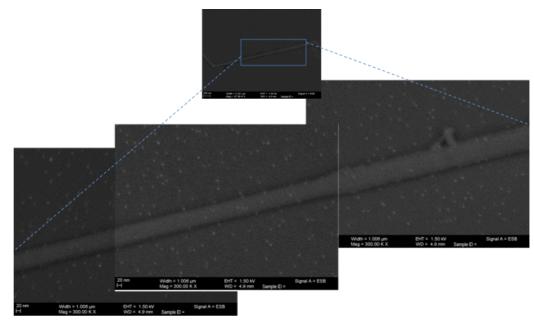

Figure 5-5 | Typical SEM images of NWFET biosensor in ESB mode after the Au-CSA sensing experiment (pg. 126)

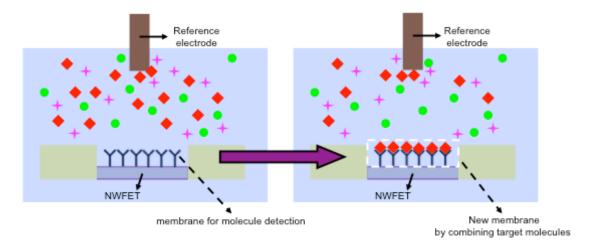

Figure 5-6 | Schematic of NWFET biosensor in electrolyte before and after target antigen binding (pg. 127)

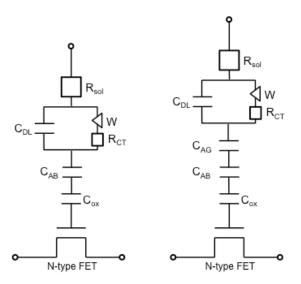

Figure 5-7 | Equivalent circuits of n-type NWFET biosensor before and after target antigens (pg. 129)

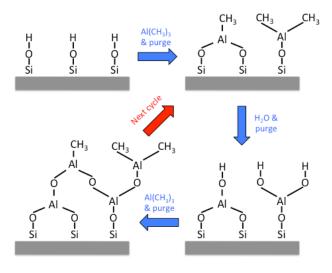

Figure A-1 | Schematic of an ALD process for Al<sub>2</sub>O<sub>3</sub> deposition (pg. 138)

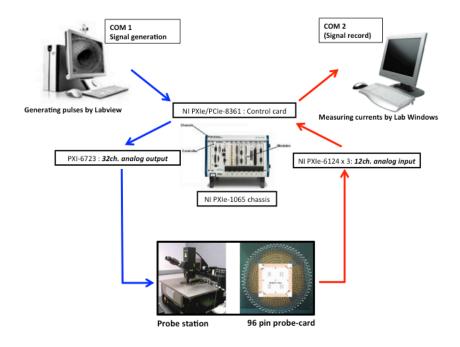

Figure B-1 | Schematic of the multi-channel I/O system (pg. 140)

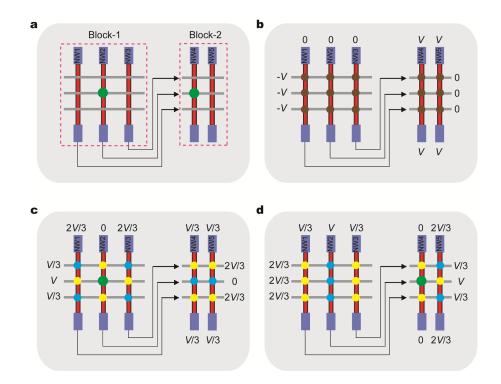

Figure B-2 | Schematic of active node pattern programming using the V/3 rule (pg. 142)

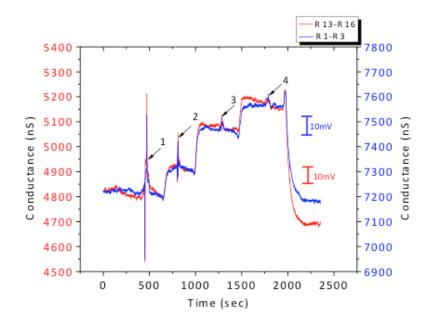

Figure C-1 | Conductance vs. time curves of n-type kinked NWFETs in different ionic strength solutions (pg. 144)

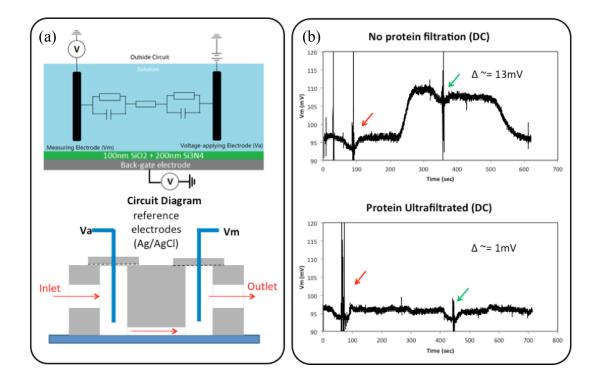

Figure C-2 | Dual Ag/AgCl electrode microfluidic setup and the potential changes between them induced by flow of filtered and unfiltered protein samples (pg. 145)

## **List of Tables**

Table 2-1 | Parameters of the charge-trapping NWFET for the simulation (pg. 31)

Table 3-1 | Possible logic gates of a  $4 \times 1$  CTNWFET crossbar array of Fig. 3-2a by the node programming (pg. 53)

Table 3-2 | Truth table of full-adder logic and results of all eight input states in Fig. 3-8b (pg. 64)

Table 3-3 | Truth table of full-subtractor logic and results of all eight input states in Fig. 3-9b (pg. 65)

Table 3-4 | Comparison between present and projected bottom-up nanoprocessor and topdown CMOS systems (pg. 74)

Table 4-1 | Main parameters used for the simulation in Fig. 4-1b (pg. 87)

Table 5-1 | Summary of results for Fig. 5-4a-c (pg. 125)

Table 5-2 | Specific values of each component in Fig. 5-7 (pg. 130)

## Chapter 1

## Introduction

Nanoscience and nanotechnology had their beginnings with the invention of scanning tunneling microscopy (STM) and discovery of fullerenes in the 1980s. Since then, research on nanoscale phenomena has led to significant advances in physics, chemistry, biology and material science. In particular, the emergence of zero-dimensional (0D) structures such as quantum dots, one-dimensional (1D) structures such as carbon nanotubes (CNT), semiconductor nanowires (NW), and two-dimensional (2D) structures such as graphene has enabled not only examination of new optical, electrical, mechanical, and thermal properties based on quantum effects, but also realization of other novel properties never observed in classical systems. For the last decade, 1D semiconductor NWs have fueled intense progress in nanotechnology and nanoscience due to their several unique advantages and characteristics. First, it is possible to design and develop various 1D nanostructures through precise control of size, morphology, structure, and composition in two and three dimensions. Second, controllable material modulation over many length scales and in many directions enables novel multi-functional devices and new nanoscale heterostructures for study of quantum confinement. Third, synthesized NWs can easily be combined with other nanostructures such as quantum dots, nanopores, or graphene to create

next-generation devices. In this chapter, I will provide a brief overview of nanoscience and nanotechnology with an emphasis on the synthesis of NWs and NW heterostructure systems and also on nanowire field-effect transistors (NWFETs) and their applications.

## 1.1 Overview of nanotechnology and nanoscience

Since Richard Feynman inspired the concept of nanotechnology,<sup>1</sup> scientists have imagined controllable synthesis of structures through direct manipulation of atoms. Nanotechnology and nanoscience deal with understanding and controlling matter at the length scale of approximately 1 to 100 nanometers.<sup>2</sup> Significantly, nanoscale materials present intriguing phenomena not anticipated by classical physics. First, a nanoscale confined structure, whose size approaches the Fermi wavelength of an electron, has quantized energy levels (Fig. 1-1), in contrast to the continuous energy levels of bulk structures.<sup>3</sup> The small number of confined electrons in a nanosystem causes an electronic density of states which is quantized and which corresponds to harmonics of electron wave functions confined to the quantum dot. This unique property leads to applications in homogenous light-emitting diodes (LED),<sup>4</sup> highly efficient solar cells,<sup>5-6</sup> quantum dot biosensors with high fluorescence quantum yields,<sup>7-8</sup> qubits,<sup>9-11</sup> single electron transistors.<sup>12</sup> and high-performance FETs based on 1D NWs<sup>13-14</sup> or NTs.<sup>15</sup> Second. nanostructures have a large surface-area-to-volume ratio (SA:V). Fig. 1-2 demonstrates the dramatic increase of SA:V from the millimeter to nanometer scale in a cubic structure. This trend is significant for nanoscale applications in sensing,<sup>16-17</sup> catalysis,<sup>18</sup> and spectroscopy<sup>19</sup> because higher chemical reactivity may be associated with the higher surface area available to reactions.

Last, the size of nanomaterials is compatible with essential biological structures and this may enable non-invasive *in-situ* biological research.<sup>20</sup> Due to their small size, nanostructures are less likely to disturb cellular metabolism when injected into the cell.<sup>21-25</sup> Furthermore, direct culture of biological systems on nanostructure-based complex templates<sup>26</sup> is possible and relevant for directly probing key nanomaterial-biological interfaces.

Figure 1-1 Confined structure in 0D, 1D and 2D (from top-right to top-left) and corresponding densities of electron states g(i)(W) (from bottom-right to bottom-left). Courtesy of Ref [3].

To explore and exploit the nano-world, three things are essential: seeing, manipulating, and synthesizing nanoscale matter. Scanning electron microscopy (SEM),<sup>27</sup> tunneling electron microscopy (TEM)<sup>28</sup> and scanning probe microscopy (SPM), including atomic force microscopy (AFM),<sup>27, 29</sup> scanning tunneling microscopy (STM),<sup>30</sup> electrostatic force microscopy (EFM),<sup>31</sup> near-field scanning optical microscopy (NSOM),<sup>32</sup> magnetic resonance force microscopy (MRFM),<sup>33</sup> are generally used to observe and analyze nanostructures. Interestingly, a

combination of STM and AFM techniques allows for observation of morphology and manipulation of atoms (mostly STM) and molecules (e.g. AFM).<sup>34, 35</sup> In addition, strong electric,<sup>36</sup> magnetic,<sup>37</sup> or electromagnetic fields<sup>38</sup> can be implemented in conjunction with the aforementioned techniques to induce specific interactions with nanomaterials. A critical task of nanotechnology and nanoscience is synthesis of nanostructures and nanomaterials in a controllable and reliable manner to yield materials with novel and unique properties. Processes by which nanostructures are produced are largely classified as either "top-down" or "bottom-up." Top-down methods are based on creation of smaller structures or devices by manipulation of a larger material source. Photolithography,<sup>39</sup> e-beam lithography,<sup>40</sup> and dip-pen lithography,<sup>41</sup> followed by etching or deposition of materials, are representative of the top-down process. A key advantage of the top-down approach is that patterning directly defines devices with exquisite alignment and precision. The bottom-up method, on the contrary, relies on synthesis and subsequent organization/assembly of smaller functional components into more complicated structures. Synthesis of quantum dots,<sup>42</sup> nanowires<sup>43-46</sup>/nanotubes,<sup>44, 47</sup> and graphene<sup>48</sup> through chemical deposition is representative of the bottom-up approach. The bottom-up approach offers great flexibility in synthesis and integration to create high-quality homogeneous systems as well as heterogeneous systems with *in-situ* modulation of nanomaterials.<sup>45-46</sup> However, devising methods to self-assemble nanodevice building blocks with high precision and uniformity over large areas remains a significant challenge.

Figure 1-2 Scheme demonstrating the effect of the increased surface area provided by nanostructured materials

The bottom-up method has distinct advantages in the research and application of nanotechnology and nanoscience. In particular, NW research from the bottom-up perspective has the potential for significant impact in nanoelectronics and biosensing. In the next section, I will describe the synthesis of semiconductor nanowires and nanowire heterostructures with precise control of morphology, composition, and electronic properties. Subsequently, I will introduce nanowire field-effect transistors that serve as the basic building blocks for nanoelectronics and nanobiosensors.

## 1.2 Rational synthesis of semiconductor nanowires and heterostructures

Synthesis of semiconductor nanowire

Nanowires can be grown using electrochemical deposition<sup>49</sup> or chemical vapor deposition (CVD)<sup>43-46</sup> based on a vapor phase mechanism such as vapor-liquid-solid (VLS),<sup>43-46, 50</sup> vapor-solid-solid (VSS),<sup>51-52</sup> oxide-assisted growth (OAG),<sup>53</sup> and self-catalyst growth (SCG).<sup>54</sup> Electrochemical deposition is mainly used for synthesis of metallic nanowires,<sup>49</sup> while CVD is a very common technique for synthesis of semiconductor nanowires.<sup>43-46, 50</sup>

Understanding the VLS mechanism is central to rational synthesis of not only onedimensional nanowires but also heterostructures. When target atoms of a semiconductor in the vapor phase are supplied to a metal nanocluster catalyst at an appropriate growth temperature, the two components will form a eutectic liquid alloy. Once sufficient target atoms supersaturate the metal-semiconductor eutectic alloy, homogeneous nucleation of a single-crystalline onedimensional solid will begin. The continuous uptake of target semiconductor atoms induces elongation of the nanowire. The nucleation and growth of NWs has been observed by in-situ transmission electron microscopy<sup>55</sup>. During synthesis, the nanowire diameter is dictated by metal catalyst size<sup>56</sup> while nanowire length is modulated by growth time. For example, nanowires with ~3 nm diameter ("molecular-scale" nanowires)<sup>57</sup> and millimeter long nanowires<sup>58</sup> have been demonstrated with high controllability and uniformity. Furthermore, switching target atoms capable of eutectic formation with the catalyst enables modulation of material composition during the growth process, making possible the synthesis of superlattices<sup>45, 59</sup>. Furthermore, *in*situ doping of semiconductor nanowires can be well controlled by the judicious choice of doping material and by control of the dopant feed-in ratio.<sup>59-60</sup>

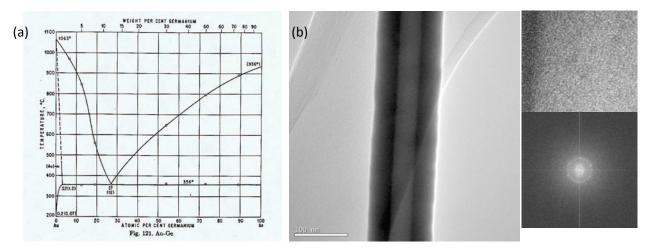

To choose a suitable metal catalyst and target material for synthesis of semiconductor nanowire the binary phase diagram is consulted. Fig. 1-3a shows the silicon-gold phase diagram. The diagram depicts distinct phases separated by curves that correspond to non-analytic solutions to the free energy as a function of temperature and percentage of Si atoms. An optimal growth temperature can be found at the intersection of the liquid + metal catalyst and liquid + semiconductor phase boundaries (Fig. 1-3a). In this region, supersaturation can readily occur at low atomic percentages of the target semiconductor. VLS growth entails nucleation and elongation of the nanowire (Fig. 1-3b).

Figure 1-3 VLS mechanism in phase diagram. (a), Liquid-solid phase diagram of Au-Si. Blue arrow corresponds to phase transition in VLS mechanism at growth temperature (blue dashed line). Courtesy of Ref [61]. (b) Schematics of nucleation and elongation in nanowire synthesis by VLS mechanism.

The synthesis of p-type silicon nanowires (p-SiNWs) proceeds as follows. First, a piece of silicon wafer with a top layer of 600 nm silicon oxide (SiO<sub>2</sub>) is cleaned with O<sub>2</sub> plasma (100W RF, 1 min at 0.6 Torr) followed by modification with poly-L-lysine (PLL) (0.1% w/v aqueous solution, Ted Pella Inc.) for 10 min. After rinsing with deionized (DI) water, a colloid of 30 nm-diameter Au nanoparticles (Au-NPs) ( $2x10^{11}$  particles/ml in water, Ted Pella Inc.) is applied to

the substrate for 10 min and then rinsed off with DI water. Au-NPs disperse and adhere to the PLL-modified growth substrates without aggregation, because Au-NPs in water are negatively charged and thus not only repel each other but also adhere to the positively charged PLL.<sup>62</sup> The catalyst substrate is loaded in the tube-furnace of the CVD system and heated to 460°C. The growth temperature, 460°C, which is higher than the Au-Si eutectic temperature of 370°C, is chosen from the Au-Si phase diagram (Blue dashed line in Fig. 1-3a). To synthesize p-type silicon nanowires with a 4000:1 silicon (Si) to boron (B) ratio (number of boron:  $1.5 \times 10^{20}$  atoms/mol), 2 sccm SiH<sub>4</sub> (100%), and 2.5 sccm B<sub>2</sub>H<sub>6</sub> (100ppm in H<sub>2</sub> or He) are introduced into the reactor as precursors for Si and B respectively. Either 60 sccm H<sub>2</sub> or 10 sccm Ar carrier gases are delivered to the catalyst substrate. Total gas pressure is maintained at 40 Torr during growth. After growth for 40 min, nanowires on the substrate are analyzed by SEM and TEM. As shown in Fig. 1-4a, the nanowires are uniform and grown in high yield. Furthermore, high-resolution SEM and TEM images of a single nanowire (Fig. 1-4b) reveal a clear interface between the Au catalyst and Si body at the tip of nanowire.

Figure 1.4

#### Figure 1.4 (Continued)

Figure 1-4 P-type silicon nanowire synthesized by the VLS-CVD method. (a), SEM image of p-type silicon nanowire on the growth substrate. Scale bar: 10  $\mu$ m. (b), (Upper panel) High-resolution SEM image of one nanowire from image (a). Scale bar: 100 nm. (Lower panel) TEM image of one nanowire transferred from the grown substrate. Scale bar: 200 nm.

#### Synthesis of core/shell semiconductor nanowire heterostructures

A number of techniques have been developed over the past decades to deposit uniform thin films ranging in thickness from a few monolayers to several micrometers. These techniques can be broadly categorized as physical deposition and chemical deposition.<sup>63</sup> Physical deposition implements mechanical, electromechanical or thermodynamic methods<sup>63</sup>. Chemical deposition, on the other hand, uses precursors that chemically react at the solid surface and leave a solid layer via a vapor-solid (VS) mechanism.<sup>64</sup> The interesting feature of semiconductor nanowire synthesis is that the VLS mechanism entails anisotropic chemical deposition of precursors in only one dimension. However, at different values of temperature (typically higher) and pressure, material precursors decompose in the gas phase or at all nanowire surfaces leading to uniform (radial) deposition of material.

For successful shell growth, chemical deposition must predominate in the radial direction with effective suppression of any axial growth. Typically, either a high temperature and low vapor pressure of precursors,<sup>46, 65</sup> or low temperature (<eutectic) and high vapor pressure of precursors,<sup>46, 66</sup> suffices to suppress axial growth of a nanowire. Under these conditions, the

liquid-solid binary phase diagram has only a liquid phase or solid phase region for both the semiconductor material and catalyst.<sup>61</sup>

The synthesis of intrinsic Si (i-Si)/intrinsic Ge (i-Ge) core/shell nanowires proceeds as follows. The preparation of substrates functionalized with 30 nm Au catalyst is the same as introduced in section 2.1 of this chapter. The catalyst substrate is loaded into a CVD furnace and heated to 465°C for growth of the i-SiNW core. Once the temperature stabilizes, 1 sccm SiH<sub>4</sub> and 60 sccm H<sub>2</sub> are introduced with a total gas pressure of 40 Torr. Growth continues under these conditions for 20 min and is then interrupted by evacuating the reactor and changing the furnace temperature to 330°C for preparation of the i-Ge shell. The growth temperature of 330°C for the i-Ge shell is lower than the eutectic temperature (356°C) of the Ge-Au alloy as shown in Fig 1-5a. After 2 mins at 330°C, 50 sccm GeH<sub>4</sub> (10% concentration) is introduced, and the total gas pressure maintained at 100 Torr for 5 min. TEM images of the nanowire reveal an explicit core/shell nanowire structure with a uniform diameter, in which the core and shell have singlecrystalline and amorphous structures, respectively. Under these growth conditions, the shell has growth rate of ~10 nm/min.

Figure 1.5

#### Figure 1.5 (Continued)

Figure 1-5 Synthesized i-Si/i-Ge core/shell nanowire with CVD-VLS mechanism. (a), Liquid-solid phase diagram of Au-Ge alloy. Courtesy of Ref [61] (b), (Left panel) TEM image of i-Si/i-Ge core/shell nanowire. Scale bar: 100 nm. (Upper right panel) TEM image of interface between i-Si core and i-Ge shell. Scale bar: 10 nm. (Lower right panel) Fast Fourier transform (FFT) image of i-Si core (upper right panel).

### **1.3** Semiconductor nanowire field-effect transistor (NWFET)

A semiconductor is a material which has a bandgap on the order of 1 eV, intermediate between that of a metal or an insulator. This small bandgap allows conductivities intermediate between those of insulators and conductors and, more significantly, for the conductivity to be sensitive to temperature, illumination, magnetic field, electric field and impurity atoms. Based on these novel properties, semiconductor materials have been implemented in thermal sensors,<sup>67</sup> photodetectors,<sup>68-70</sup> solar cells,<sup>59, 71-72</sup> magnetic sensors<sup>73</sup> and charge sensors utilizing a p-n junction diode<sup>74</sup> or a transistor.<sup>75</sup>

The transistor has been central to the development of modern electronic systems, including logic and memory, and critical scientific research tools. In particular, the field-effect transistor (FET) has served as the foundation of modern electronics. It is distinguished by an ability to undergo significant conductivity modulation under application of external electric fields, and possesses several other key characteristics. First, the device has a high input impedance, which enables a lower noise intrusion from the environment and less cross-talk from adjacent devices. Second, the size of devices can be scaled down to the molecular level without significant degradation of performance, because the operation of the device is rooted in the control of the number of majority carriers such as "electrons" or "holes" in the channel.<sup>76</sup> Last, compared to other logic circuits, static power dissipation is very small when two complementary FETs are implemented in a complementary metal-oxide-semiconductor (CMOS) circuit<sup>77</sup>.

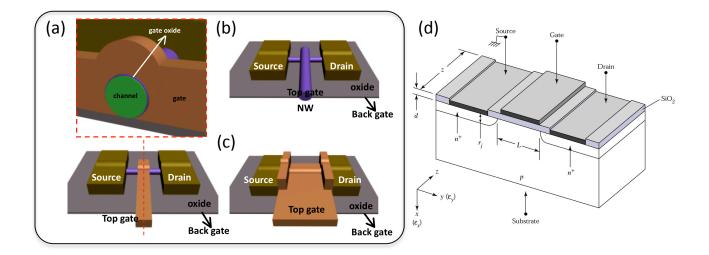

A semiconductor nanowire field-effect transistor (NWFET) is a molecular-scale analog of a conventional FET and has a number of versatile and powerful functions that can be modulated by rational synthesis. The typical NWFET is composed of four main components (Fig. 1-6a): a semiconducting nanowire, metal contacts, a gate electrode, and an oxide supporting substrate. Two metal electrodes at the edges of the nanowire, a highly conductive electrode positioned in the middle of the nanowire, the nanowire body, and substrate serve as the source/drain, top-gate, channel, and back-gate, respectively. Fig. 1-6a-c shows various top-gate architectures of a NWFET, which can be generally classified as full-top-gate or partial-top-gate structures. These structures share several essential components with conventional metal-oxidesemiconductor field-effect transistors (MOSFETs). As shown in Fig. 1-6b, the MOSFET consists of a p-type semiconductor channel, two heavily n-doped regions for the source and drain, gate electrode, and ohmic-contacted substrate. Three MOSFET performance regimes can be identified depending on the magnitude of the gate-to-source bias ( $V_{GS}$ ) and drain-to-source bias ( $V_{DS}$ ):<sup>77</sup> subthreshold, linear, and saturation modes. In the case of most NWFETs, the channel has only one majority carrier and is ohmically contacted with metal electrodes so that there is neither an inversion layer along the channel nor pinch-off in the channel. This means that the NWFET can only operate in two modes such as accumulation mode (channel conductive) for the on-state and depletion mode (channel non-conductive) for the off-state. Significantly, a NWFET with p-n

junction or Schottky contacts for the source and drain<sup>78</sup> reported an inversion mode for lightly doped or intrinsic channels<sup>79</sup>. However, this section will focus on general NWFET mechanisms based on either a full-top-gate or partial-top-gate structure.

Figure 1-6 FET structures. (a), Scheme of typical NWFET with partial top-gate. (b), Scheme of NWFET with nanowire-based partial top-gate (c), Scheme of NWFET with full top-gate. (d), Scheme of typical MOSFET, showing the channel length  $\mathbf{L}$ , the channel width  $\mathbf{Z}$ , the oxide thickness  $\mathbf{d}$ , the junction depth  $\mathbf{r}_i$ . Courtesy of Ref [77].

For a NWFET with a full-top-gate, the drain current in depletion mode (gate voltage below threshold voltage) is dominated by carrier diffusion due to the depletion of majority carriers in the channel. For a p-type NWFET with channel length L, nanowire diameter R, the current can be described as

$$I_{DS} = -q(\pi R^2) D_n \frac{\partial n}{\partial x} = -q(\pi R^2) D_n \frac{n(0) - n(L)}{L}$$

(1-1)

where  $D_n$  is the diffusion constant in the depletion layers, n(x) is the electron density in the channel, and source and drain are at x=0 and x=L. The electron density at the source and drain are given by

$$n(0) = n_i e^{\frac{q(\psi_s - \psi_B)}{kT}}, \quad n(L) = n_i e^{\frac{q(\psi_s - \psi_B - V_D)}{kT}}$$

(1-2)

where  $\psi_S$ ,  $\psi_B$ , and  $\psi_D$  are the potential at source, nanowire body, and drain,  $n_i$  is intrinsic carrier concentration, k is the Boltzmann constant, and T is absolute temperature. Inserting (2) into (1) gives

$$I_{DS} = -q(\pi R^2) D_n \frac{n_i e^{\frac{q(\psi_s - \psi_B)}{kT}} - n_i e^{\frac{q(\psi_s - \psi_B - V_D)}{kT}}}{L}$$

$$= \frac{-q(\pi R^2) D_n n_i e^{\frac{q(\psi_s - \psi_B)}{kT}}}{L} \left(1 - e^{\frac{-qV_D}{kT}}\right)$$

(1-3)

Note the exponential dependence of  $I_D$  for  $V_G$ - $V_T < 0$ . In accumulation mode, where the gate voltage is higher than the threshold voltage, majority carriers induce the conducting channel, such that the channel acts as a resistor. As the drain voltage increases, with the source to gate bias ( $V_{GS}$ ) maintaining its initial value, the drain to gate bias ( $V_{GD}$ ) decreases. This effect is referred to as pinch-off and leads to the same operation as in the linear and saturation mode of a conventional MOSFET. The drain currents  $I_D$  in the modes<sup>77</sup> are

$$I_{DS} = \frac{1}{L^2} \mu C_{ox} \left( (V_G - V_T) V_{DS} \right) \quad for \, V_{DS} \ll (V_G - V_T) \text{ in linear mode}$$

(1-4)

$$I_{DS} = \frac{\mu C_{ox}}{2L^2} (V_G - V_T)^2 \quad for V_{DS} \gg (V_G - V_T) \text{ in saturation mode}$$

(1-5)

where  $\mu$  is carrier mobility,  $C_{ox}$  is the capacitance of gate oxide,  $V_G$  is the gate voltage,  $V_T$  is the threshold voltage, and  $V_{DS}$  is the drain voltage. The transconductance  $g_m$  of the NWFET, which

is an important indicator of electrical device performance, is expressed in different operational modes as

$$g_m = \frac{\partial I_{DS}}{\partial V_G}\Big|_{V_{DS}=\ constant} = \frac{1}{L^2}\mu C_{ox}V_{DS} \qquad in\ linear\ mode \tag{1-6}$$

$$g_m = \frac{\partial I_{DS}}{\partial V_G}\Big|_{V_{DS}=\ constant} = \frac{1}{L^2}\mu C_{ox}(V_G - V_T) \quad in\ saturation\ mode \tag{1-7}$$

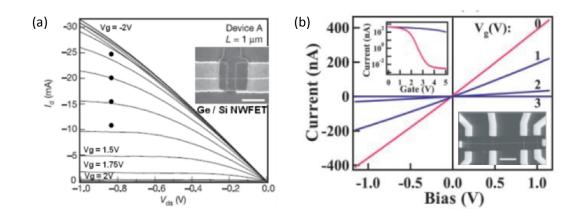

Fig. 1-7a shows the  $I_{DS}$ - $V_{DS}$  plot of a full-top-gate NWFET which demonstrates linear and saturation regions.

For a NWFET with a partial-top-gate geometry, interestingly, there are uncovered, topgate-free parts of the nanowire between the channel and source/drain contacts. These parts are highly conductive with abundant majority carriers so that the nanowire body does not exhibit pinch-off. Therefore, the source-drain current of a NWFET with a single partial-top-gate in the middle of the semiconductor channel can be expressed in linear mode as follows,

$$I_{DS} = \frac{1}{L^2} \mu C_{ox} \left( (V_{GS'} - V_T) V_{D'S'} \right) = \frac{V_{S'} - V_S}{R_{SS'}} = \frac{V_D - V_{D'}}{R_{DD'}}$$

(1-8)

where  $V_{S'}$  and  $V_{D'}$  are the voltage at the interface of the top-gate-free and gate regions close to the source and drain, respectively,  $V_{D'S'}$  is the voltage difference in the channel covered by the top-gate, and  $R_{SS'}$  and  $R_{DD'}$  are the resistance of top-gate-free parts close to source and drain, respectively. Fig. 1-7b shows the  $I_{DS}$ - $V_{DS}$  and  $I_{DS}$ - $V_{GS}$  curves for a partial-top-gate NWFET which correspond to electrical transport in linear mode.

Figure 1-7 Electrical characteristics of NWFET. (a),  $I_{DS}$ - $V_{DS}$  data for Ge/Si core/shell nanowire device ( $L = 1\mu m$ , 4 nm HfO<sub>2</sub> dielectric) with  $V_G = -2$  to 2V in 0.25V steps from top to bottom. Inset: Top-view SEM image of the NWFET device. The Au top-gate overlaps with the Ni source/drain electrodes to ensure full coverage of the channel. Scale bar: 500 nm. Courtesy of Ref [13]. (b), Gate-dependent  $I_{DS}$ - $V_{DS}$  characteristics of NW-top-gated NWFET. The NW gate voltage for each  $I_{DS}$ - $V_{DS}$  curve is indicated (0, 1, 2, and 3V). (Top left inset) The red and blue curves show  $I_{DS}$ - $V_{GS}$  for n-type NW (red) and global back-gate (blue) when the bias is set at 1V. (Bottom right inset) SEM image of a multiple crossed NW-top-gated NWFET. Scale bar: 2  $\mu m$ . Courtesy of Ref [80].

### **1.4 Organization of thesis**

Semiconductor nanowire building blocks coupled with functional materials through bottom-up methods can provide unique properties for use in novel nanoelectronic and nanobiomolecular applications. This thesis studies how to encode new functions into nanowire building blocks through physical design and synthesis and explores new nanoscale architectures for the realization of a nanoprocessor and unique biosensing device. In part I, Chapters 2-3, we describe how charge-trapping field-effect transistors (CTNWFETs) based on semiconductor/high-*k*-oxide-stack core/shell nanowires were developed, studied, characterized, and assembled to demonstrate reconfigurable multi-functional nanowire circuits for a nanoprocessor. Specifically, chapter 2 describes the bandgap design and development of CTNWFETs through integration of an amorphous shell of a high-*k* oxide stack over single-crystalline semiconductor nanowires using atomic layer deposition (ALD). Furthermore, employing a high-performance Ge/Si core/shell nanowire structure for the core successfully yields enhanced device uniformity, a prerequisite for building complex circuits. In addition, this novel device shows bistable conductance with high ON/OFF ratios (>10<sup>6</sup>) and can be used for not only logic gates but also memory elements at the nanoscale.

In Chapter 3, we propose a crossbar array architecture consisting of non-volatile CTNWFET as the platform for a programmable integrated nanowire circuit. A simple but effective nanowire assembly method is introduced to enable fabrication of CTNWFET crossbar arrays. A multi-channel electrical measurement system is described. Based on two blocks (one unit tile) of CTNWFET crossbar arrays, we realize a number of complex logic circuits such as NOR, XOR, half-adder, full-adder, full-subtractor, multiplexer, demultiplexer, and D-latch. Furthermore, we demonstrate how this architecture can be scaled to develop a full nanoprocessor system and comment on the low power consumption characteristics of this design.

In part II, Chapters 4-5, we present a novel NWFET biosensor and use this platform to understand the fundamentals of electrically-based biomolecular detection. Critical factors underpinning such detection are explored by means of not only surface modification analysis with X-ray photoelectron spectroscopy (XPS) and contact angle measurement but also enzymelinked immunosorbent assays (ELISA). In addition, nanowire biosensing in the high-frequency regime is studied to overcome the limits of charge-based sensing in high ionic strength solutions. In Chapter 4, the theoretical sensitivity of a NWFET biosensor is investigated for design and development of high-sensitivity NWFET through modulation of dopants and morphology in synthesis. The surface modification of a SiNWFET with (3-aminopropyl)triethoxysilane (APTES) and glutaraldehyde (GA), 3-(trimethoxysilyl)butyl aldehyde (TBA), or APTES and N-hydroxysuccinimide (NHS)/1-ethyl-3-(3-dimethylaminopropyl) carbodiimide (EDC) is inspected by XPS and contact angle measurements. Furthermore, ELISA experiments using gold-conjugated secondary antibodies in a microfluidic system reveal ~2000 antibody sites per μm<sup>2</sup> and eventually prove that electrical signal changes from a NWFET biosensor correspond to specific association-dissociation events of charged target proteins.

Finally, in chapter 5, we discuss issues related to the use of electrically-based biosensors and demonstrate a new NWFET-based biosensor in high ionic strength solutions. This biomolecule-sensing nanoelectronic probe has the potential to open up new opportunities in nanoproteomics and help advance nanoelectronic sensing from *in vitro* to *in vivo* studies.

## **Bibliography**

- 1 Eric, D. "There's Plenty of Room at the Bottom" (Richard Feynman, Pasadena, 29 December 1959).

- 2 National Nanotechnology Initiative, <u>www.nano.gov.</u>

- 3 Waser, R. *Nanoelectronics and information Technology (Advanced Electronic Materials and Novel Devices).* (WILEY-VCH Verlag GmbH & Co. KGaA, 2005).

- 4 Alivisatos, A. P. Semiconductor clusters, nanocrystals, and quantum dots. *Science* **271**, 933-937 (1994).

- 5 Nozik, A. J. Quantum dot solar cells. *Physica E* 14, 115-120 (2002).

- 6 Semonin, O. E., Luther, J. M., Choi, S., Chen, H., Gao, J., Nozik, A. J. & Beard, M. C. Peak external photocurrent quantum efficiency exceeding 100% via MEG in a quantum dot solar cell. *Science* 334, 1530-1533 (2011).

- 7 Medintz, I. L., Clapp, A. R., Mattoussi, H., Goldman, E. R., Fisher, B. & Mauro, J. M. Selfassembled nanoscale biosensors based on quantum dot FRET donors. *Nature Mater.* 2, 630-638 (2003).

- 8 Medintz, I. L., Uyeda, H. T., Goldman, E. R. & Mattoussi, H. Quantum dot bioconjugates for imaging, labeling and sensing. *Nat. Mater.* **4**, 435-446 (2005).

- 9 Hu, Y., Churchill, H. O. H., Reilly, D. J., Xiang, J., Lieber, C. M. & Marcus, C. M. A Ge/Si heterostructure nanowire-based double quantum dot with integrated charge sensor. *Nature Nanotechnol.* 2, 622-625 (2007).

- 10 Ladd, T. D., Jelezko, F., Laflamme, R., Nakamura, Y., Monroe, C. & O'Brien, J. L. Quantum computers. *Nature* **464**, 45-53 (2010).

- 11 Hu, Y., Kuemmeth, F., Lieber, C. M. & Marcus, C. M., Hole spin relaxation in Ge/Si coreshell nanowire qubits. *Nature Nanotechnol.* 7, 47-50 (2012).

- 12 Kastner, M. A. The single electron transistor. Rev. Mod. Phys. 64, 849-858 (1992).

- 13 Xiang, J., Lu, W., Hu, Y., Wu, Y., Yan, H. & Lieber, C. M. Ge/Si nanowire heterostructures as high-performance field-effect transistors. *Nature* **441**, 489-493 (2006).

- 14 Jiang, X., Xiong, Q., Nam, S., Qian, F., Li, Y. & Lieber, C. M. InAs/InP radial nanowire heterostructures as high electron mobility devices. *Nano Lett.* **7**, 3214-3218 (2007).

- 15 Javey, A., Guo, J., Wang, Q., Lundstrom, M. & Dai, H. Ballistic carbon nanotube fieldeffect transistor. *Nature* **424**, 654-657 (2003).

- 16 Patolsky, F., Zheng, G., Hayden, O., Lakadamyali, M., Zhuang, X. & Lieber, C. M. Electrical detection of single viruses. *Proc. Natl. Acad. Sci. USA* 101, 14017-14022 (2004).

- 17 Zheng, G., Patolsky, F., Cui, Y., Wang, W. U. & Lieber, C. M. Multiplexed electrical detection of cancer markers with nanowire sensor arrays. *Nature Biotechnol.* 23, 1294-1301 (2005).

- 18 Yi, D., Lee, S. & Ying, J. Y. Synthesis and applications of magnetic nanocomposite catalysts. *Chem. Mater.* **18**, 2459-2461 (2006).

- 19 Gammon, D., Brown, S. W., Snow, E. S., Kennedy, T. A., Katzer, D. S. & Park, D. Nuclear spectroscopy in single quantum dots: Nanoscopic Raman scattering and nuclear magnetic resonance. *Science* 277, 85-88 (1997).

- 20 Ferrari, M. Cancer nanotechnology: opportunities and challenges. *Nature Rev. Cancer* 5, 161-171 (2005).

- 21 Patolsky, F., Timko, B. P., Yu, G., Fang, Y., Greytak, A. B., Zheng, G. & Lieber, C. M. Detection, stimulation, and inhibition of neuronal signals with high-density nanowire transistor arrays. *Science* **313**, 1100-1104 (2006).

- 22 Tian, B., Cohen-Karni, T., Qing, Q., Duan, X., Xie, P., & Lieber, C. M. Three-dimensional, flexible nanoscale field-effect transistors as localized bioprobes. *Science* **329**, 831-834 (2010).

- 23 Duan, X., Gao, R., Xie, P., Cohen-Karni, T., Qing, Q., Choe, H., Tian, B., Jiang, X. & Lieber, C. M. Intracellular recordings of action potentials by an extracellular nanoscale field-effect transistor. *Nature Nanotechnol.* 7, 174-179 (2012).

- 24 Gao, R., Strehle S., Tian, B., Cohen-Karni, T., Xie, P., Duan, X., Qing, Q. & Lieber, C. M. Outside looking in: Nanotube transistor intracellular sensors. *Nano Lett.* **12**, 3329-3333 (2012).

- 25 Shalek, A. K., Gaublomme, J. T., Wang, L., Yosef, N., Chevrier, N., Anderson, M. S., Robinson, J. T., Pochet, N., Neuberg, D., Gertner, R. S., Amit, I., Brown, J. R., Hacohen, N., Regev, A., Wu, C. J. & Park, H. Nanowire-mediated delivery enables functional interrogation of primary immune cells: Application to the analysis of chronic lymphocytic leukemia. *Nano Lett.* **12**, 6498-6504 (2012).

- 26 Tian, B., Liu, J., Dvir, T., Jin, L., Tsui, J. H., Qing, Q., Suo, Z., Langer, R., Kohane, D. S. & Lieber, C. M. Macroporous nanowire nanoelectronic scaffolds for synthetic tissues. *Nature Mater.* 11, 986-994 (2012).

- 27 Crawford, S. A., Higgins, M. J., Mulvaney, P. & Wetherbee, R. Nanostructure of the diatom frustule as revealed by atomic force and scanning electron microscopy. *J. Phycol.* 37, 543-554 (2001).

- 28 Wang, Z. L. Transmission electron microscopy of shape-controlled nanocrystals and their assemblies. *J. Phys. Chem. B* **104**, 1153-1175 (2000).

- 29 Binnig, G., Quate, C. F. & Gerber, Ch. Atomic Force Microscope. *Phys. Rev. Lett.* 56, 930-933 (1986).

- 30 Shen, T. C., Hubacek, J. S., Tucker, John R. & Abeln, G. C. Nanoscale patterning and oxidation of H-passivated Si (100)-2x1 surfaces with an ultrahigh vacuum scanning tunneling microscope. *Appl. Phys. Lett.* **64**, 2010-2012 (1994).

- 31 Barboza, A. P. M., Gomes, A. P., Archanjo, B. S., Araujo, P. T., Jorio, A., Ferlauto, A. S., Mazzoni, M. S. C., Chacham, H. & Neves, B. R. A. Deformation induced semiconductormetal transition in single wall carbon nanotubes probed by electric force microscopy. *Phys. Rev. Lett.* 100, 256804 (2008).

- 32 Dürig, U. T., Pohl D. W. & Rohner, F. Near-field optical-scanning microscopy. J. Appl. Phys. 59, 3318-3327 (1986).

- 33 Rugar, D., Budakian, R., Mamin, H. J. & Chui, B. W. Single spin detection by magnetic resonance force microscopy. *Nature* **430**, 329-332 (2004).

- 34 Snow, E. S., Campbell, P. M. Fabrication of Si nanostructures with an atomic force microscope. *Appl. Phys. Lett.* **64**, 1932-1934 (1994).

- 35 Sugimoto, Y., Pou, P., Custance, O., Jelinek, P., Abe, M., Perez, R. & Morita, S. Complex patterning by vertical interchange atom manipulation using atomic force microscopy. *Science* **322**, 413-417 (2008).

- 36 Kim, P. & Lieber, C. M. Nanotube nanotweezers. Science 286, 2148-2150 (1999).

- 37 Hancox, C. I., Doret, S. C., Hummon, M. T., Luo, L. & Doyle, J. M. Magnetic trapping of rare-earth atoms at millikelvin temperatures. *Nature* **431**, 281-284 (2004).

- 38 Chaumet, P. C., Rahmani, A. & Nieto-Vesperinas, M. Optical trapping and manipulation of nano-objects with an apertureless probe. *Phys. Rev. Lett.* **88**, 123601 (2002).

- 39 Sundaramurthy, A., Schuck, P. J., Conley, N. R., Fromm, D. P., Kino, G. S. & Moerner, W. E. Toward nanometer-scale optical photolithography: Utilizing the near-field of bowtie optical nanoantennas. *Nano Lett.* 6, 355-360 (2006).

- 40 Craighead, H. G., Howard, R. E., Jackel, L. D. & Mankiewich, P. M. 10-nm linewidth electron beam lithography on GaAs. *Appl. Phys. Lett.* **42**, 38-40 (1983).

- 41 Piner, R. D., Zhu, J., Xu, F., Hong, S. & Mirkin, C. A. "Dip-pen" nanolithography. *Science* **283**, 661-663 (1999).

- 42 Klimov, V. I., Mikhailovsky, A. A., Xu, S., Malko, A., Hollingsworth, J. A., Leatherdale, C. A., Eisler, H. J. & Bawendi, M. G. Optical gain and stimulated emission in nanocrystal quantum dots. *Science* **290**, 314-317 (2000).

- 43 Morales, A. M. & Lieber, C. M. A laser ablation method for the synthesis of crystalline semiconductor nanowires. *Science* **279**, 208-211 (1998).

- 44 Hu, J., Ouyang, M., Yang, P., & Lieber, C. M. Controlled growth and electrical properties of heterojunctions of carbon nanotubes and silicon nanowires. *Nature* **399**, 48-51 (1999).

- 45 Gudiksen, M. S., Lauhon, L. J., Wang, J., Smith, D. & Lieber, C. M. Growth of nanowire superlattice structures for nanoscale photonics and electronics. *Nature* **415**, 617-620 (2002).

- 46 Lauhon, L. J., Gudiksen, M. S., Wang, D. & Lieber, C. M. Epitaxial core-shell and coremulti-shell nanowire heterostructures. *Nature* **420**, 57-61 (2002).

- 47 José-Yacamán1, M., Miki-Yoshida, M., Rendón, L. & Santiesteban, J. G. Catalytic growth of carbon microtubules with fullerene structure. *Appl. Phys, Lett.* **62**, 657 (1993).

- 48 Kim, K., Zhao, Y., Jang, H., Lee, S., Kim, J., Kim, K., Ahn, J., Kim, P., Choi, J. & Hong, B. Large-scale pattern growth of graphene films for stretchable transparent electrodes. *Nature* 457, 706-710 (2009).

- 49 Sun, L., Searson, P. C. & Chien, C. L. Electrochemical deposition of nickel nanowire arrays in single-crystal mica films. *Appl. Phys. Lett.* **74**, 2803-2805 (1999).

- 50 Duan, X. & Lieber, C. M. General synthesis of compound semiconductor nanowires. *Adv. Mat.* **12**, 298-302 (2000).

- 51 Kodambaka, S., Tersoff, J., Reuter, M. C. & Ross, M. F. Germanium nanowire growth below the eutectic temperature. *Science* **316**, 729-732 (2007).

- 52 Cohen-Karni, T., Casanova, D., Cahoon, J., Qing, Q., Bell, D. & Lieber, C. M. Synthetically-encoded ultrashort-channel nanowire transistors for fast, point-like cellular signal detection. *Nano Lett.* **12**, 2639-2644 (2012).

- 53 Zhang, R., Lifshitz, Y. & Lee, S. Oxide-assisted growth of semiconducting nanowires. *Adv. Mater.* **15**, 635-640 (2003).

- 54 Mandl, B., Stangl, J., Hilner, E., Zakharov, A. A., Hillerich, K., Dey, A. W., Samuelson, L., Bauer, G., Deppert, K. & Mikkelsen, A. Growth mechanism of self-catalyzed group III–V nanowires. *Nano Lett.* **10**, 4443-4449 (2010).

- 55 Wu, Y. & Yang, P. Direct observation of vapor-liquid-solid nanowire growth. J. Am. Chem. Soc. **123**, 3165-3166 (2001).

- 56 Cui, Y., Lauhon, L. J., Gudiksen, M. S., Wang, J. & Lieber, C. M. Diameter-controlled synthesis of single-crystal silicon nanowires. *Appl. Phys. Lett.* **78**, 2214-2216 (2001).

- 57 Wu, Y., Cui, Y., Huynh, L., Barrelet, C. J., Bell, D. C. & Lieber, C. M. Controlled growth and structures of molecular-scale silicon nanowires. *Nano Lett.* **4**, 433-436 (2004).

- 58 Park, W. I., Zheng, G., Jiang, X., Tian, B. & Lieber, C. M. Controlled synthesis of millimeter-long silicon nanowires with uniform electronic properties. *Nano Lett.* 8, 3004-3009 (2008).

- 59 Kempa, T. J., Tian, B., Kim, D. R., Hu, J., Zheng, X. & Lieber, C. M. Single and tandem axial p-i-n nanowire photovoltaic devices. *Nano Lett.* **8**, 3456-3460 (2008).

- 60 Xu, L., Jiang, Z., Qing, Q., Mai, L., Zhang, Q. & Lieber, C. M. Design and synthesis of diverse functional kinked nanowire structures for nanoelectronic bioprobes. *Nano Lett.* 13, 746-751 (2013).

- 61 Hansen & Anderko, Constitution of Binary Alloys, p. 206 & p.232 (1958).

- 62 Murthy, V. S., Cha, J. N., Stucky, G. D. & Wong, M. S. Charge-driven flocculation of poly(L-lysine) – Gold nanoparticle assemblies leading to hollow microspheres. *J. Am. Chem. Soc.* **126**, 5292-5299 (2004).

- 63 Seshan, K. Handbook of Thin film Deposition Processes and Techniques (Noyes, 2002).

- 64 Masaki, Y., LeComber, P. G & Fitzgerald, A. G. Solid phase crystallization of thin films of Si prepared by plasma-enhanced chemical vapor deposition. J. Appl. Phys. 74, 129-134 (1993).

- 65 Tian, B., Zheng, X., Kempa, T. J., Fang, Y., Yu, N., Yu, G., Huang, J. & Lieber, C. M. Coaxial silicon nanowires as solar cells and nanoelectronic power sources. *Nature* 449, 885-890 (2007).

- 66 Ben-Ishai, M. & Patolsky, F. A route to high-quality crystalline coaxial core/multishell Ge@ Si (GeSi) n and Si@(GeSi) n nanowire heterostructures. *Adv. Mater.* **22**, 902-906 (2010).

- 67 Krummenacher, P. & Oguey, H. Smart temperature sensor in CMOS technology. *Sensors. Actuat. A-Phys.* **22**, 636-638 (1989).

- 68 Cleland, A. N., Estève, D., Urbina, C. & Devoret, M. H. Very low noise photodetector based on the single electron transistor. *Appl. Phys. Lett.* **61**, 2820-2822 (1992).

- 69 Wang, J., Gudiksen, M. S., Duan, X., Cui, Y. & Lieber, C. M. Highly polarized photoluminescence and photodetection from single indium phosphide nanowires. *Science* 293, 1455-1457 (2001).

- 70 Yang, C., Barrelet, C. J., Capasso, F. & Lieber, C. M. Single p-type/intrinsic/n-type silicon nanowires as nanoscale avalanche photodetectors. *Nano Lett.* **6**, 2929-2934 (2006).

- 71 Chapin, D. M., Fuller, C. S. & Pearson, G. L. A new junction photocell for converting solar radiation into power. J. Awl. Phys. 25, 676-677 (1954).

- 72 Kempa, T., Day, R., Kim, S., Park, H., & Lieber, C. M. Semiconductor nanowires: A platform for exploring limits and concepts for nano-enabled solar cells. *Energy Environ. Sci.* 6, 719-733 (2013).

- 73 Vinal, A. W. & Masnari, N. A. Operating principles of bipolar transistor magnetic sensors. *IEEE Trans. Electron Devices* **2**, 1219-1226 (1994).

- 74 Chase, F. H., Hamilton, B. H. & Smith, D. H. Transistors and junction diodes in telephone power plants. *Bell Syst. Tech. J.* **33**, 827-858 (1954).

- 75 Bardeen, J. & Brattain, W. H. The transistor, a semi-conductor triode. *Phys. Rev.* **74**, 230-231 (1948).

- 76 Cao, L., Chen, S., Wei, D., Liu, Y., Fu, L., Yu, G., Liu, H., Liu, X. & Wu, D. Fabrication and characterization of molecular scale field-effect transistors. *J. Mater. Chem.* 20, 2305-2309 (2010).

- 77 Sze, S. M. & Lee, M.-K. Semiconductor Devices: Physics and Technology (John Wiley & Sons, 2002).

- 78 Schmidt, V., Riel, H., Senz, S., Karg, S., Riess, W. & Gçsele, U. Realization of a silicon nanowire vertical surround-gate field-effect transistor. *Small* **2**, 85-88 (2006).

- 79 Hayden, O., Bjçrk, M. T., Schmid, H., Riel, H., Drechsler, U., Karg, S. F., Lçrtscher, E. & Riess, W. Fully depleted nanowire field-effect transistor in inversion mode. *Small* 3, 230-234 (2007).

- 80 Huang, Y., Duan, X., Cui, Y., Lauhon, L., Kim, K. & Lieber, C. M. Logic gates and computation from assembled nanowire building blocks. *Science* **294**, 1313-1317 (2001).

## **Part I : Programmable multi-functional**

## nanowire array circuit

for nanoprocessor

## Chapter 2

## Design, synthesis, and characterization of non-volatile NWFET for nanoprocessor building block

Conventional CMOS technology has led the nanoelectronic industry for several decades and has altered lifestyles in modern society. However, as devices approach their physical limits in size and as power consumption surges with an increase of transistors,<sup>1</sup> a paradigm shift will be needed to contend with dramatic increases in manufacturing costs. Field-effect transistor (FET) devices based on semiconducting nanowires produced by bottom-up methods are good candidates for nanoelectronic building blocks due to their relative ease of modulation for multiple functions at the nanoscale,<sup>2-4</sup> low-power consumption,<sup>5</sup> and excellent electrical performance.<sup>6, 7</sup> The ability to modulate diameter size, nanomaterial type and electrical properties (by doping) presents new opportunities to produce diverse functional building blocks for nanoelectronics through intelligent design of nanowire structure. This chapter starts with a discussion of NWFETs as the building blocks of electronic applications and addresses design, synthesis, and characterization of novel non-volatile charge-trapping NWFET for the realization of integrated complex circuits in nanoelectronics.

#### **2.1 NWFET for nanoelectronics**

An essential factor in electronics is uniform performance between circuit units in terms of threshold voltage and on/off currents, which is one of the critical reasons CMOS technology based on top-down methods has been highly successful. As device features scale down to the sub-100 nm regime, uniformity is key to the success of the device; enormous resources are expended by top-down technology on lithography equipment and operating facilities to minimize fluctuations in device characteristics.<sup>1</sup>

Using nanostructures to assemble devices from the bottom up, analogous to the way that nature builds biological systems,<sup>8, 9</sup> is a possible solution to the problem of maintaining uniformity. Hence, for the past two decades, carbon nanotubes (CNTs)<sup>10, 11</sup> and semiconductor nanowires<sup>12-17</sup> have been investigated and implemented in logic and memory for integrated complex circuits. Their unique controllability in terms of material, structure and impurities<sup>18-21</sup> makes semiconductor nanowires the more promising of these two types of materials for nanoelectronics. Compared to materials produced by top-down methods, the self-assembled semiconducting nanowire guarantees high electrical performance due to single crystallinity with smooth surface boundaries.<sup>22, 23</sup>

For this reason, many researchers have attempted to build complex logic and high capacity memory using semiconducting nanowire building blocks or, more specifically, the NWFET platform. NWFET-nanowire crossbar arrays have successfully demonstrated 'OR,' 'AND,' 'NOR,' 'XOR,' 'half-adder' logic gates,<sup>13</sup> 2 by 2 decoder,<sup>15</sup> ring oscillator,<sup>16, 17</sup> bipolar transistor,<sup>14</sup> CMOS circuit,<sup>14,17</sup> and non-volatile memory.<sup>12</sup> Surprisingly, although a decade has passed since the introduction of functional NWFETs for logic and memory building blocks, one

of the most complex circuits utilizing NWFET building blocks in the history of nanoelectronics is the 2 by 2 decoder. This fact speaks to the significant challenges of high-density integrated complex circuits. These challenges include 1) how to solve variations in device characteristics, 2) which architecture is best to enable complex functionality and 3) how to assemble the individual components in high-density circuits on a large scale.<sup>24</sup> To address these issues and realize integrated multi-functional complex NWFET circuits, in this chapter and the following one we have demonstrated non-volatile NWFET with highly uniform electrical performance capable of both logic and memory functions, a new architecture consisting of a cascade multiple 2D nanowire crossbar array, and a lubricant-assisted contact printing method capable of axial alignment with control of NW density.

## 2.2 Physical design of charge-trapping NWFET as logic and memory elements

In attempting to realize a complex circuit based on a one-dimensional structure, crossbar array architecture presents itself as an obvious way to achieve not only high device density but also efficient interconnection.<sup>25</sup> However, if all junctions in the crossbar have NWFET functions, it is impossible to demonstrate logic gates, because each row or column in the crossbar array shares the same potential. To address this issue, we consider a bistable NWFET that can achieve two states of an electrical property, FET or highly conductive junction. This concept has been successfully realized by non-volatile NWFET through a surface coating of redox active molecules, cobalt phthalocyanine (CoPc),<sup>12</sup> though it falls short of controllability of electrical properties, such as threshold voltages or on/off currents between devices. We reasoned that the

development of a new multi-state NWFET, with non-volatile, uniform, high on/off ratio electrical performance, is central to achieving integrated complex circuits.

There are two main strategies for conferring non-volatile multi-stable properties on NWFET in which doubling the capacity of stored data and creating multiple bits per cell are feasible. One approach is to couple intrinsic properties of materials, such as ferroelectricity,<sup>26, 27</sup> magnetoresistivity,<sup>28</sup> multiferroicity<sup>29</sup> and phase transition<sup>30, 31</sup> with the NWFET. A second approach is to build a quantum well structure on the NWFET by designing a stack of different dielectrics as a charge-trapping device<sup>32</sup> to control the electron/hole concentration in a confined area. The additional structure on the NWFET would need to play the roles of non-volatility, gate oxide, and multi-stable switching functions simultaneously.

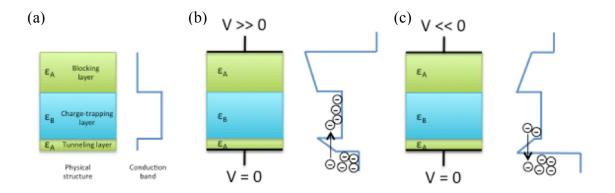

Fig 2-1a-c show a charge-trapping mechanism in which the structure is composed of a tunneling layer, a charge-trapping layer, and a blocking layer. The bandgap energies of the tunneling and blocking layers are much larger than that of the charge-trapping layer, such that joining these heterogeneous materials generates a quantum well where electrons or holes can be trapped. Furthermore, the tunneling layer is designed to be thinner than the blocking layer to make quantum penetration of electrons or holes easy in the tunneling layer and difficult in the blocking layer. Through the quantum tunneling effect, electric charges can pass through the tunneling layer and be trapped in the charge-trapping layer under large bias (Fig 2-1b) on the dielectric stack. Applying a large bias of reverse polarity to the system ejects the trapped charges by the same mechanism.

Figure 2-1 Charge-trapping mechanisms. (a), Band structure of a dielectric stack comprising a quantum well, composed of tunneling, charge-trapping, and blocking layers. (b), Applying large positive bias to the dielectric stack. The tunneling effect traps electrons in the middle layer. (c), Applying large negative bias to the dielectric stack. The tunneling effect causes electrons to escape from the charge-trapping layer.

In order to analyze this system quantitatively, a simple simulation of p-type Si/Al<sub>2</sub>O<sub>3</sub>-ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub>-ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> 30nm/1nm-2nm-1nm-2nm-5nm core/shell NWFET was performed to calculate the threshold shift between the two different NWFET states by the change in hole concentration in the functional gate oxides stack due to charge-trapping. The bandgaps of amorphous alumina, zirconia and silicon dioxide are known to be ~8.8 eV, ~5.8 eV, and ~9 eV,<sup>33</sup> respectively, so that 1nm SiO2, 2nm-1nm-2nm ZrO<sub>2</sub>-Al2O<sub>3</sub>-ZrO<sub>2</sub>, and 5nm Al<sub>2</sub>O<sub>3</sub> constitute the tunneling, hole-trapping, and blocking layers, respectively. Fig. 2-2 and Table 2-1 show the physical structure, estimated bandgap structure and parameters of the charge-trapping NWFET for this simulation. In addition, Three features are assumed for the simulation of NWFET: First, this NWFET system assumes that the source and drain contacts are ohmic on the nanowire by etching through the gate oxides. Second, the shape of the gate metal and oxides is cylindrical. Third, the distribution of dopants is uniform throughout the volume of the NWFET.

| Parameter                                    | Value                                                         |  |

|----------------------------------------------|---------------------------------------------------------------|--|

| radius of nanowire core (r <sub>core</sub> ) | 15 nm                                                         |  |

| Length of nanowire channel (L)               | 0.1 μm                                                        |  |

| Length of nanowire                           | 2.1 μm                                                        |  |

| Mobility of silicon nanowire $(\mu_p)$       | $3.65 \text{ x } 10^2 \text{ cm}^2 / \text{V} \text{ s}^{16}$ |  |

| Temperature (T)                              | 300 K                                                         |  |

Table 2-1 Parameters of the charge-trapping NWFET for the simulation

Figure 2-2 Physical and bandgap structure of simulated CTNWFET. (a), Prospective and cross-sectional view of p-type Si/Al2O<sub>3</sub>-ZrO<sub>2</sub>-Al2O<sub>3</sub>-ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> core/shell NWFET with a single partial top-gate. (b), Bandgap structure of 1nm-2nm-1nm-2nm-5nm  $Al_2O_3$ -ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub>-ZrO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> multi-dielectric stack. Applying large positive (negative) bias on the top-gate induces the threshold shift to right (left) side.

To estimate the resistivity of nanowire and boron dopant density, we use the empirical results from p-type SiNW grown with a 4000-to-1 atomic ratio of silicon to boron, 2  $\mu$ m in length and 30 nm in diameter. The measured conductivity is approximately 5  $\mu$ S, yielding the resistivity and number of boron atoms in the dopant:

$$\rho = \frac{A}{GL} = \frac{\pi \times (30 \times 10^{-7} cm)^2}{5 \times 10^{-6} S \times 2 \times 10^{-4} cm} = 2.8 \times 10^{-2} \Omega \cdot cm$$

$$= \frac{1}{\sigma} = \frac{1}{q\mu_n n + q\mu_p p} \approx \frac{1}{q\mu_p p} \qquad (\because n \ll p)$$

$$\therefore p = \frac{1}{q\mu_p \times 2.8 \times 10^{-2} \Omega \cdot cm}$$

$$= \frac{1}{1.6 \times 10^{-19} C \times 3.65 \times 10^2 cm^2 \cdot V^{-1} \cdot s^{-1} \times 2.8 \times 10^{-2} \Omega \cdot cm}$$

$$= 6.11 \times 10^{17} cm^{-3} \qquad (2-1)$$