## Reducing Power Loss, Cost and Complexity of SoC Power Delivery Using Integrated 3-Level Voltage Regulators

The Harvard community has made this article openly available. Please share how this access benefits you. Your story matters.

| Citation     | Kim, Wonyoung. 2013. Reducing Power Loss, Cost and<br>Complexity of SoC Power Delivery Using Integrated 3-Level<br>Voltage Regulators. Doctoral dissertation, Harvard University.                                                                                      |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Accessed     | April 17, 2018 3:59:31 PM EDT                                                                                                                                                                                                                                          |  |

| Citable Link | http://nrs.harvard.edu/urn-3:HUL.InstRepos:10423839                                                                                                                                                                                                                    |  |

| Terms of Use | This article was downloaded from Harvard University's DASH<br>repository, and is made available under the terms and conditions<br>applicable to Other Posted Material, as set forth at<br>http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-<br>use#LAA |  |

(Article begins on next page)

02013 - Wonyoung Kim

All rights reserved.

**Gu-Yeon Wei and David Brooks**

## Reducing Power Loss, Cost and Complexity of SoC Power Delivery using Integrated 3-Level Voltage Regulators

### Abstract

Traditional methods of system-on-chip (SoC) power management based on dynamic voltage and frequency scaling (DVFS) is limited by 1) cores/IP blocks sharing a voltage domain provided by off-chip voltage regulators (VR) and 2) slow voltage scaling time ( $<0.1V/\mu$ s). This global, slow DVFS cannot track the increasingly heterogeneous, fluctuating performance requirements of individual microprocessor cores and SoC components. Furthermore, traditional off-chip VRs add significant area overhead and component cost on the board.

This thesis explores replacing a large portion of existing off-chip VRs with integrated voltage regulators (IVR) that can scale the voltage at a 50 mV/ns rate, which is 500 times faster than microsecond-scale voltage scaling with existing off-chip VRs. IVRs occupy 10 times smaller footprint than off-chip VRs, making it easy to duplicate them to provide per-core or per-IP-block voltage control. This thesis starts by summarizing the benefits of using IVRs to deliver power to SoCs. Based on a simulation study targeting a 1.6W, 4-core SoC, I show that greater than 20% energy savings is possible with fast, per-core DVFS enabled by IVRs. Next, I present two stand-alone IVR test-chips converting 1.8V and 2.4V to 0.4-1.4V while delivering maximum 1W to the output. Both test-chips incorporate a 3-level VR topology, which is suitable for integration because the topology allows for much smaller inductors (1nH) than existing inductor-based buck VRs. I also discuss reasons behind lower-than-simulated efficiencies in the test-chips and ways to improve. Finally, I conclude with future process technologies that can boost IVR conversion efficiencies and power densities.

# Contents

|          | Title | e Page   |                                                           | i         |

|----------|-------|----------|-----------------------------------------------------------|-----------|

|          | Abs   | tract .  |                                                           | iii       |

|          | Tab   | le of Co | ontents                                                   | V         |

|          |       | 0        | lres                                                      | vii       |

|          | List  | of Tab   | les                                                       | xi        |

|          |       |          | Previously Published Work                                 | xii       |

|          | Ack   | nowledg  | gments                                                    | xiii      |

| 1        |       | 0        | s of Delivering Power to SoCs and the Need for Integrated | ł         |

|          | Vol   | 0        | egulators                                                 | 1         |

|          | 1.1   |          | enge of delivering power to modern SoCs                   | 2         |

|          | 1.2   | Soluti   | on: Integrated Voltage Regulators                         | 5         |

| <b>2</b> | Bas   | ics of   | Voltage Regulators and Challenges of Integration          | 12        |

|          | 2.1   | Basics   | s of step-down voltage regulators                         | 13        |

|          | 2.2   | Challe   | enges of Integrating Voltage Regulators                   | 15        |

|          | 2.3   | Evolu    | tion of IVRs                                              | 21        |

| 3        | Sys   | tem-Le   | evel Energy Savings with Fast, Per-Core DVFS using In     | -         |

|          | tegi  | rated V  | Voltage Regulators                                        | <b>24</b> |

|          | 3.1   | Prior    | Works on Fine-Grain DVFS                                  | 28        |

|          | 3.2   | Poten    | tial of Fast and Per-Core DVFS Schemes                    | 29        |

|          |       | 3.2.1    | Simulation Framework                                      | 31        |

|          |       | 3.2.2    | Offline DVFS Algorithm                                    | 32        |

|          |       | 3.2.3    | Effects of Finer Temporal Resolution                      | 34        |

|          |       | 3.2.4    | Per-Core vs. Chip-Wide DVFS                               | 36        |

|          | 3.3   |          | cteristics of On-Chip Regulators                          | 40        |

|          |       | 3.3.1    | Model and Simulation of Buck VR                           | 40        |

|          |       | 3.3.2    | Design trade-offs of IVRs                                 | 41        |

|          |       | 3.3.3    | Regulator Efficiency                                      | 44        |

|          |       | 3.3.4    | Load Transient Response                                   | 47        |

|          |        | 3.3.5   | Voltage Scaling Time                                       | 49  |

|----------|--------|---------|------------------------------------------------------------|-----|

|          |        | 3.3.6   | On-Chip Regulators for Single and Multiple Power Domains . | 50  |

|          | 3.4    | Energ   | y Savings for Per-Core and Chip-Wide DVFS using On-Chip    |     |

|          |        | Regul   | ators                                                      | 53  |

|          |        | 3.4.1   | Comparison of Energy Savings                               | 54  |

|          |        | 3.4.2   | Power Domain Scalability                                   |     |

| 4        | Full   | ly-Inte | grated 3-Level Voltage Regulators                          | 61  |

|          | 4.1    | Buck,   | Switched-Capacitor and 3-Level IVRs                        | 62  |

|          | 4.2    | 3-Leve  | el Voltage Converter                                       | 65  |

|          |        | 4.2.1   | Design Parameters for 3-Level Converters                   | 65  |

|          |        | 4.2.2   | Comparison to Buck and SC Converters                       | 69  |

|          | 4.3    | 3-Leve  | el Implementation: Open-Loop                               | 74  |

|          |        | 4.3.1   | Power FETs                                                 | 76  |

|          |        | 4.3.2   | Driver circuits                                            | 78  |

|          |        | 4.3.3   | Passive elements                                           | 80  |

|          |        | 4.3.4   | Feedback loop and shunt regulator                          | 82  |

|          | 4.4    | Measu   | rement: Open-Loop                                          | 83  |

|          | 4.5    | 3-Leve  | el VR: Closed-Loop                                         | 94  |

| <b>5</b> | Tec    | hnolog  | gies on the Horizon                                        | 108 |

| Bi       | ibliog | graphy  |                                                            | 112 |

# List of Figures

| 1.1 | Power delivery in mobile and server systems                                                                                                   | 3               |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.2 | Illustration showing how shared voltage domains and slow DVFS lead                                                                            |                 |

|     | to wasted energy.                                                                                                                             | 4               |

| 1.3 | Large amounts of decaps in the board, package and SoC die decrease                                                                            |                 |

|     | the speed of voltage scaling                                                                                                                  | 4               |

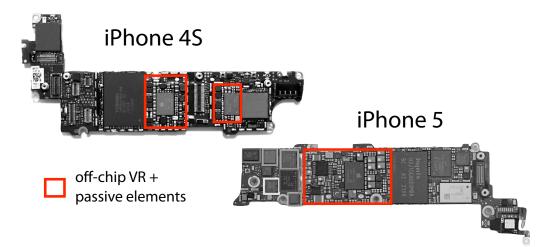

| 1.4 | Teardown images of iPhone 4S and iPhone 5 show that off-chip VRs<br>and required passive elements occupy a significant area on the board      | 4               |

| 1.5 | Power delivery using IVRs in a server system                                                                                                  | 6               |

| 1.6 | IVR enables nanosecond timescale DVFS compared to microsecond                                                                                 |                 |

|     | DVFS with existing off-chip VRs                                                                                                               | 7               |

| 1.7 | IVR enables fast voltage scaling by reducing the amount of decap to charge/discharge                                                          | 7               |

| 1.8 | Efficiency and footprint data for TI voltage regulator products plot-<br>ted using TI's WEBENCH, a simulator provided by TI for its voltage   |                 |

|     | regulator products $[13]$                                                                                                                     | 8               |

| 1.9 | IVRs can reduce $I^2R$ loss on the board by delivering power at a high voltage and low current and converting to a lower voltage at the point | 10              |

|     | of load                                                                                                                                       | 10              |

| 2.1 | Buck converter schematics                                                                                                                     | 14              |

| 2.2 | Dimensions, DC resistance and inductance of various chip inductors<br>from Coilcraft [4]. Images of inductors is roughly to scale.            | 16              |

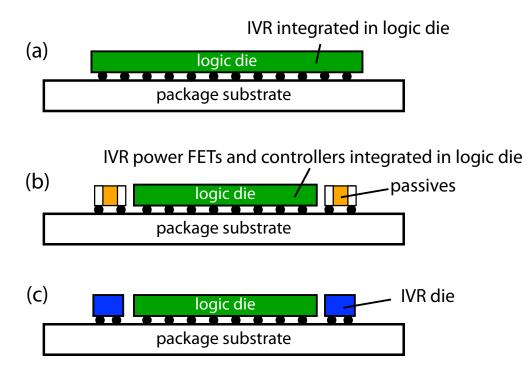

| 2.3 | IVRs can be integrated on the package-level (a,b) or in the logic IC die (c).                                                                 | 17              |

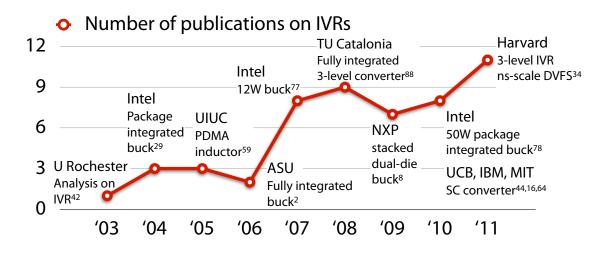

| 2.4 | There has been increasing interest on IVRs by industry and research communities.                                                              | 21              |

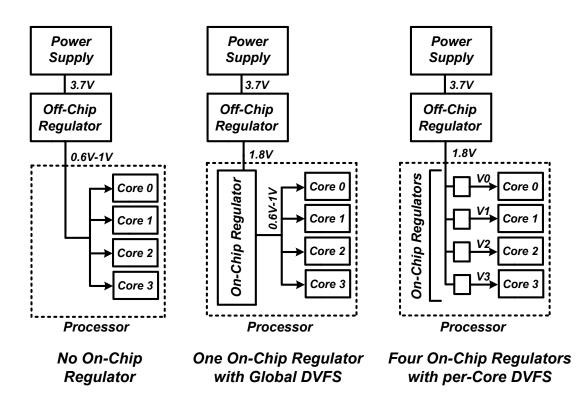

| 3.1 | Three power-supply configurations for a 4-core CMP                                                                                            | 27              |

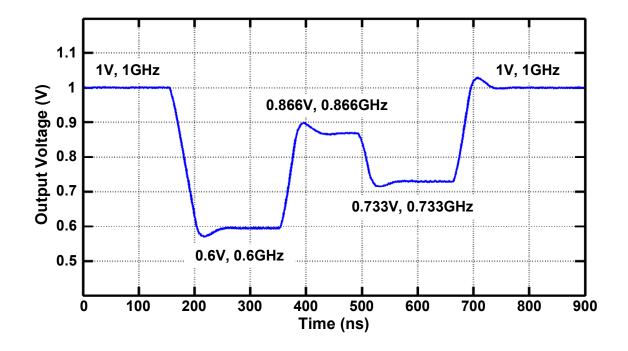

| 3.2 | DVFS transition times with an IVR                                                                                                             | $\frac{21}{30}$ |

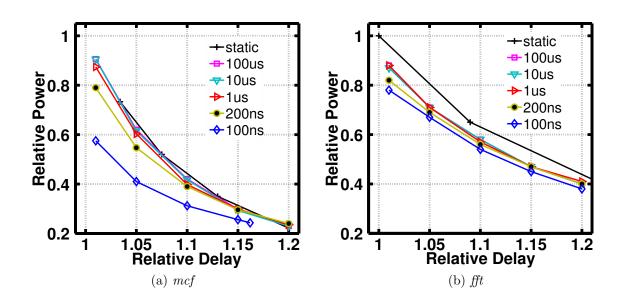

| 3.3 | Benefits of fine-grained DVFS scheme for $mcf$ and $fft$ .                                                                                    | 35              |

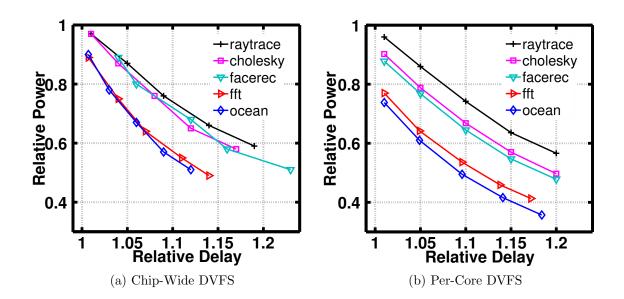

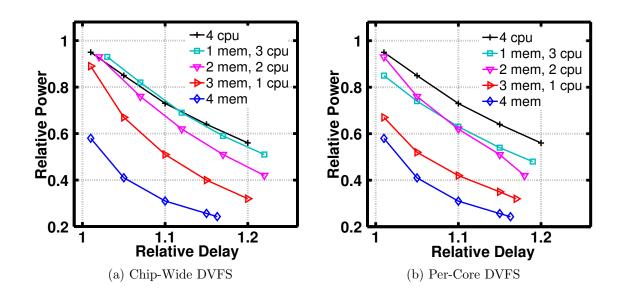

| 3.4 | Per-Core DVFS for multi-threaded applications.                                                                                                | 37              |

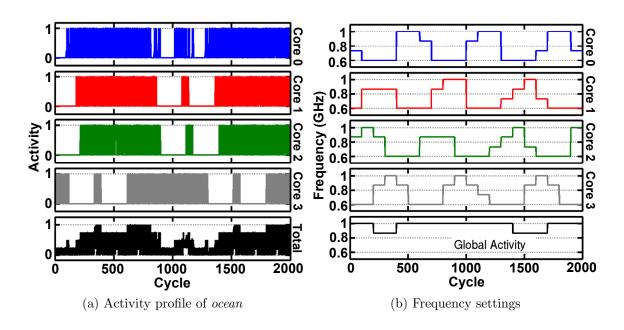

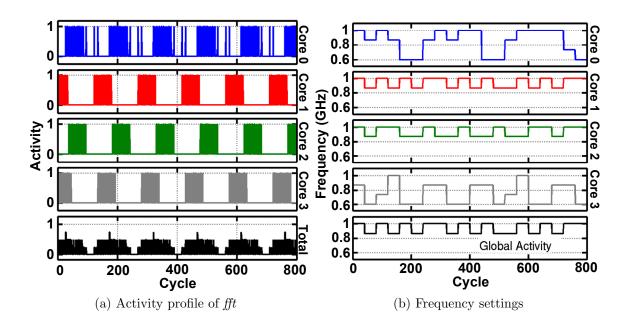

| 3.5  | Snapshot of <i>ocean</i> with per-core and chip-wide DVFS                                                 | 38  |

|------|-----------------------------------------------------------------------------------------------------------|-----|

| 3.6  | Snapshot of <i>fft</i> with per-core and chip-wide DVFS                                                   | 38  |

| 3.7  | Per-core DVFS for multi-programming scenarios.                                                            | 39  |

| 3.8  | Power delivery network using (a) only off-chip and (b) both off-chip                                      |     |

|      | and on-chip VRs                                                                                           | 42  |

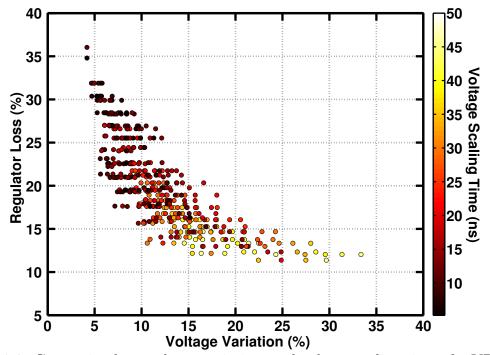

| 3.9  | Conversion loss, voltage variation, and voltage scaling time of a VR                                      |     |

|      | with different parameters                                                                                 | 44  |

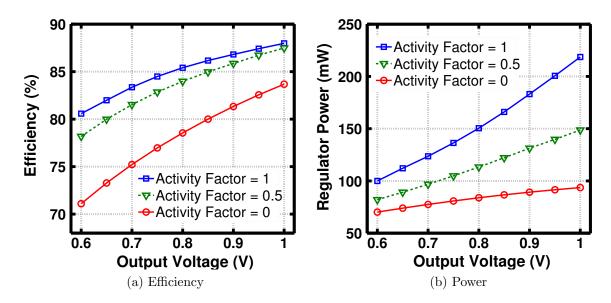

|      | VR efficiency and power vs. output voltage for different activity factors.                                | 45  |

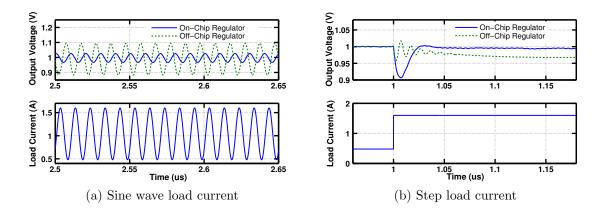

| 3.11 | Voltage fluctuation of off-chip and on-chip VRs during step and sine                                      |     |

|      | wave load current transient                                                                               | 46  |

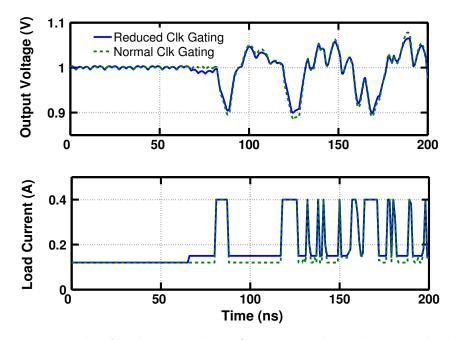

| 3.12 | Example of reducing voltage fluctuations by selectively disabling clock                                   |     |

|      | gating.                                                                                                   | 50  |

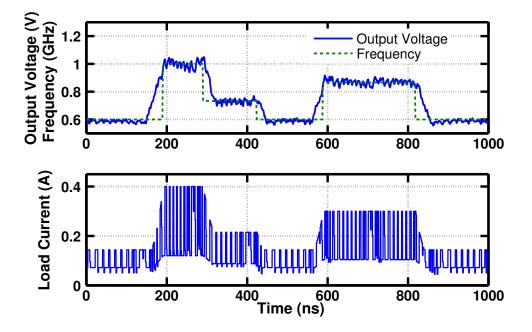

| 3.13 | Snapshot of output voltage, frequency, and load current traces with                                       | • 4 |

| 014  | DVFS.                                                                                                     | 51  |

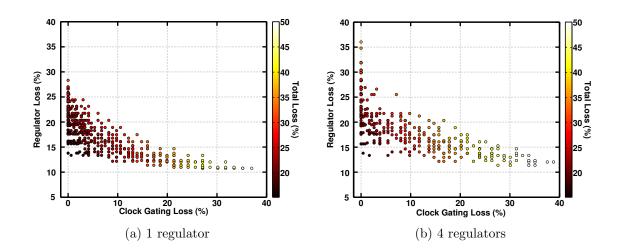

|      | Total energy overhead with different regulator settings for <i>facerec</i>                                | 52  |

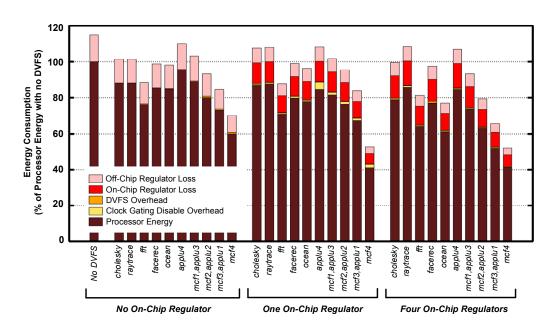

| 3.15 | Detailed breakdown of energy consumption for the processor and VR                                         | 55  |

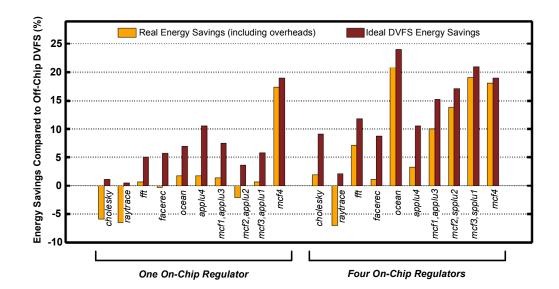

| 2 16 | for single power domain (global) and multiple domains (per-core) DVFS.                                    | 55  |

| 5.10 | Relative energy consumption of on-chip VR configurations compared<br>to a off-chip VR with DVFS           | 56  |

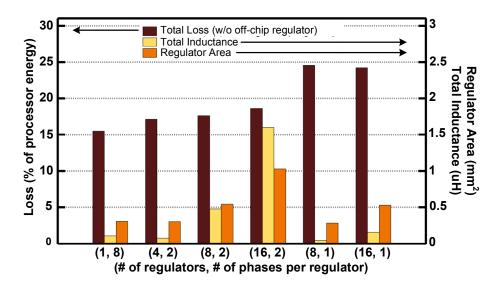

| 3.17 | Loss, inductor size, and area of on-chip VRs for different numbers of                                     | 50  |

| 0.17 | power domains.                                                                                            | 58  |

|      |                                                                                                           | 00  |

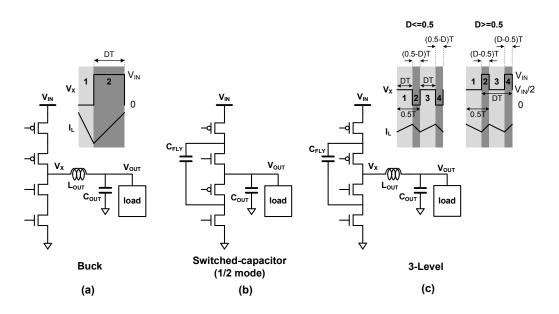

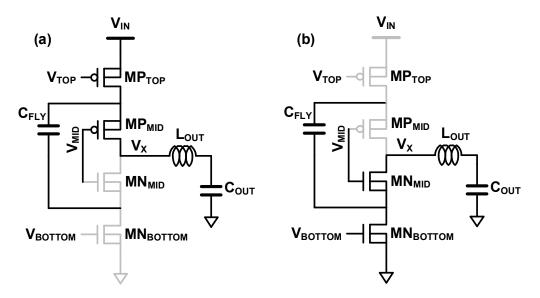

| 4.1  | Power FET and output filters of (a) buck, (b) switched-capacitor, and                                     |     |

|      | (c) 3-level VRs $\ldots$ | 65  |

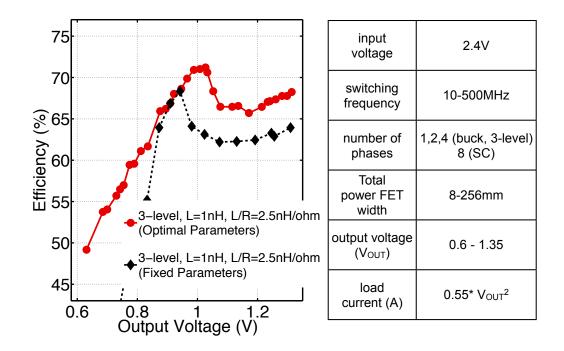

| 4.2  | Simulated conversion efficiencies of 3-level VRs with fixed and optimal                                   |     |

|      | design parameters. Table shows the range of design parameters used                                        |     |

|      | in simulations                                                                                            | 66  |

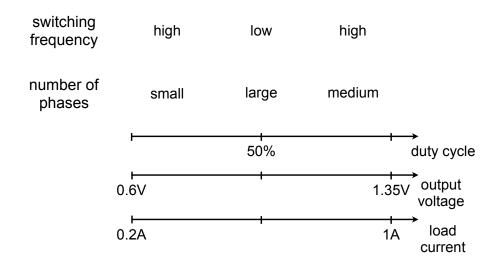

| 4.3  | Design parameters that maximize efficiencies across duty cycle, output                                    |     |

|      | voltage and load current ranges.                                                                          | 67  |

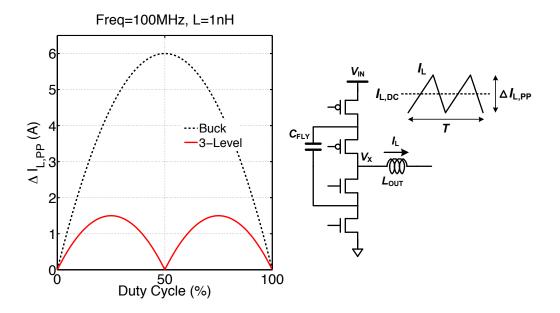

| 4.4  | Simulated peak-to-peak inductor current ripple ( $\Delta I_{L,PP}$ ) of 3-level and                       |     |

|      | buck VRs in continuous conduction mode (CCM).                                                             | 68  |

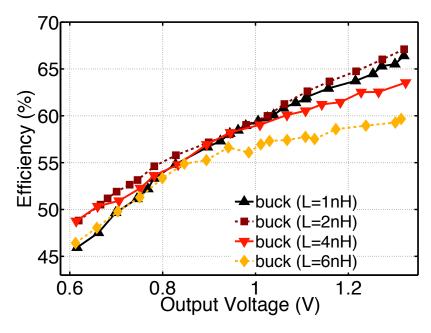

| 4.5  | Simulated conversion efficiencies of buck VRs across inductance values $(L/D) = 2.5 \cdot L/(Q)$          | -   |

| 1.0  | $(L/R = 2.5 nH/\Omega)$ .                                                                                 | 70  |

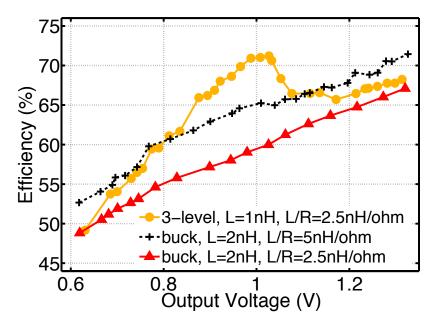

| 4.6  | Simulated conversion efficiencies of 3-level and buck VRs across induc-                                   | 71  |

| 4 7  | tor qualities                                                                                             | 71  |

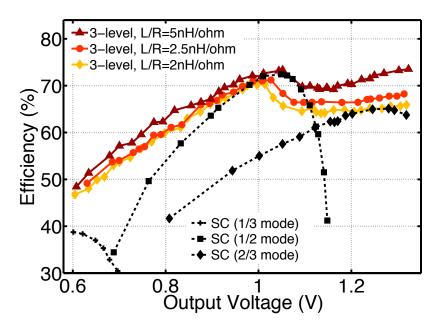

| 4.7  | Simulated conversion efficiencies of 3-level and switched-capacitor VRs                                   | 72  |

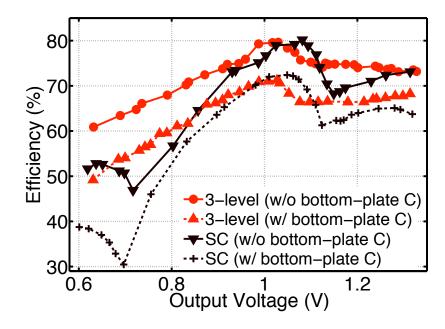

| 4.8  | across inductor qualities                                                                                 | 12  |

| 4.0  | out bottom-plate parasitic capacitance                                                                    | 73  |

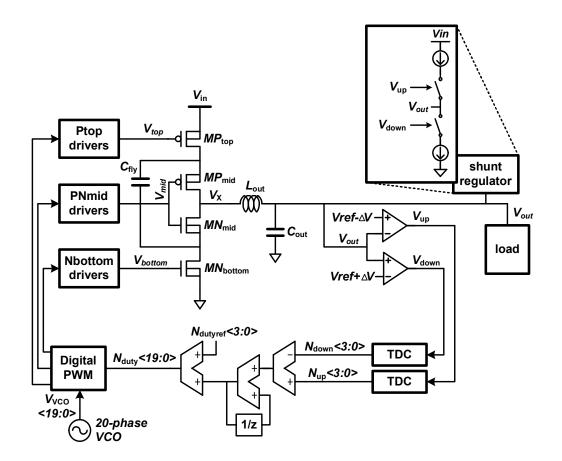

| 4.9  | Block diagram of 3-level converter with slow digital feedback control                                     | 10  |

| т.Ј  | and fast shunt regulation. Finer duty cycle control is necessary to avoid                                 |     |

|      | limit-cycling.                                                                                            | 75  |

|      |                                                                                                           | 10  |

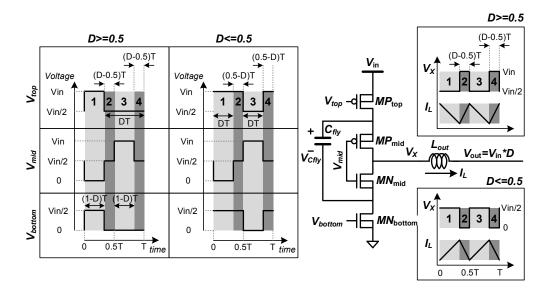

| 4.10       | Schematic of the proposed 3-level power converter. Signal timing dia-<br>grams illustrate different operating modes.                                                                                                                                                                               | 77  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

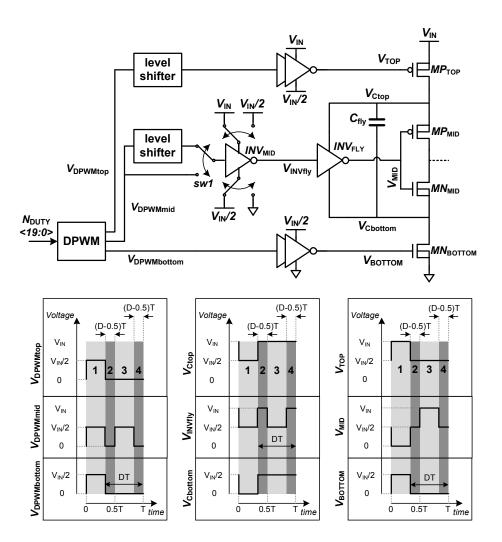

| 4.11       | Schematic and waveforms that drive power FETs when duty cycle is over 50%.                                                                                                                                                                                                                         | 79  |

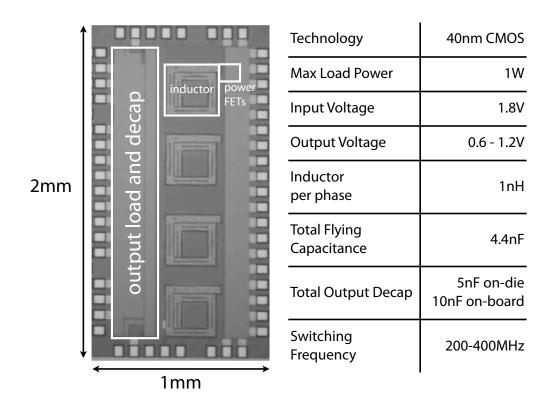

| 4.12       | High-level architecture of the 3-level converter test-chip prototype                                                                                                                                                                                                                               | 84  |

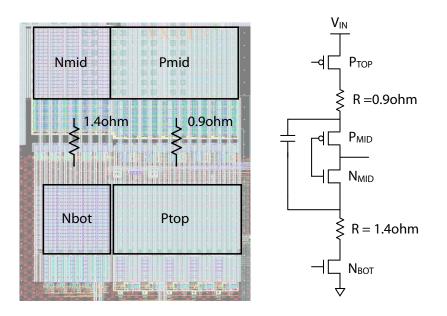

|            | Die micrograph of the converter with dimensions of main blocks. Fly-<br>ing capacitors are placed underneath the inductors to reduce area over-<br>head. The table shows converter specifications.                                                                                                 | 85  |

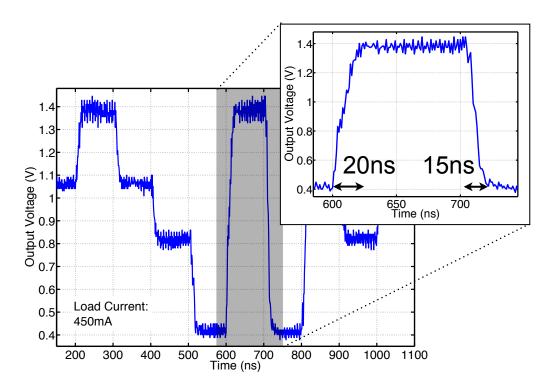

| 4.14       | Measured snapshot of fast dynamic voltage scaling of the converter operating in open-loop. Voltage scales from 1.4V to 0.4V and vice versa within 20ns                                                                                                                                             | 86  |

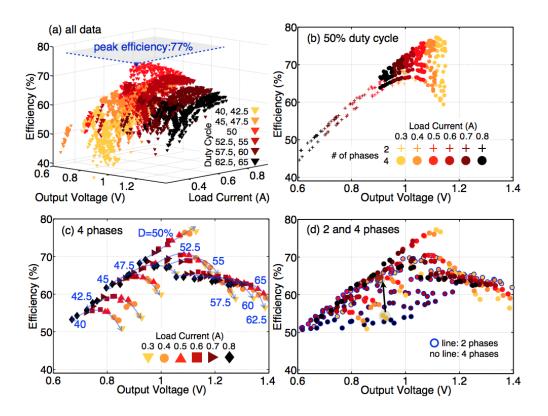

| 4.15       | Measured efficiency of converter operating in open-loop                                                                                                                                                                                                                                            | 87  |

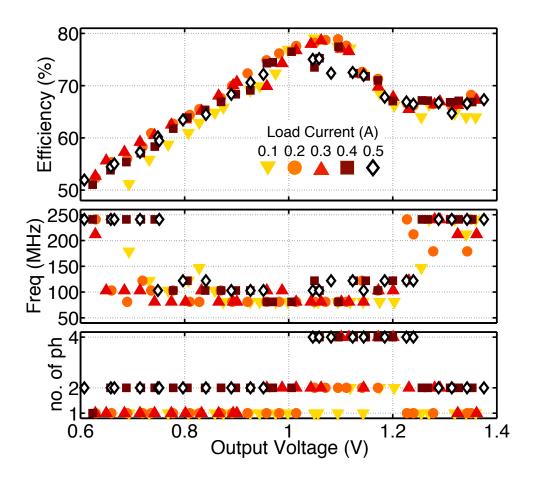

|            | Measured conversion efficiency with optimal switching frequencies and<br>number of phases                                                                                                                                                                                                          | 88  |

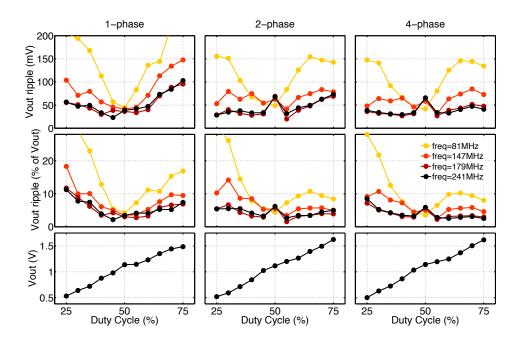

| 4.17       | Open-loop measurement of peak-to-peak output voltage ripple of the<br>3-level converter with DC load current. Ripple changes across duty                                                                                                                                                           | 89  |

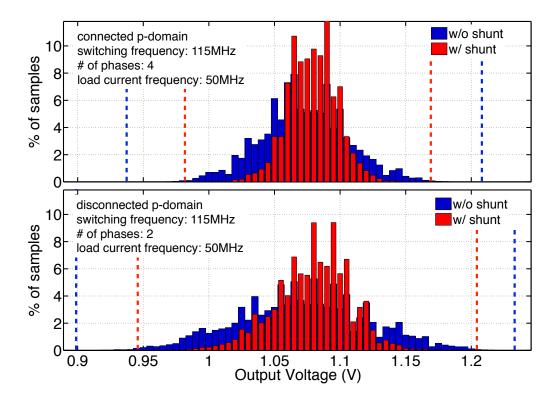

| 4.18       | cycles, switching frequencies and number of phases                                                                                                                                                                                                                                                 |     |

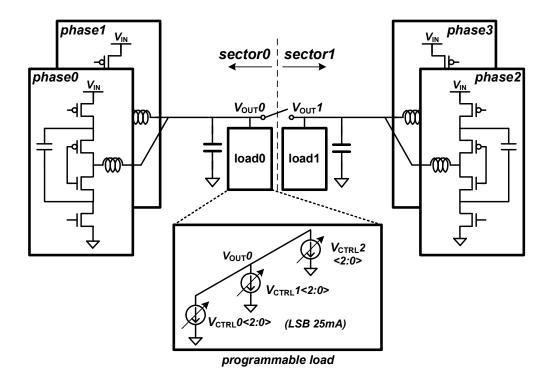

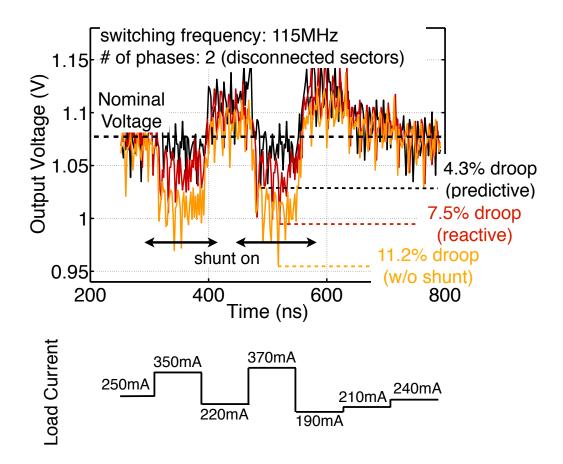

| 4.19       | sectors                                                                                                                                                                                                                                                                                            | 91  |

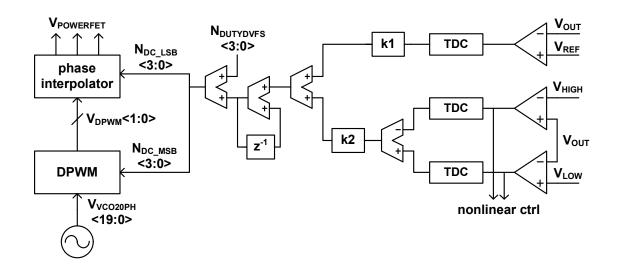

|            | shunt regulator, with reactive shunt, and with predictive shunt<br>High-level diagram of the feedback control in the second version 3-level                                                                                                                                                        | 92  |

|            | VR test-chip.                                                                                                                                                                                                                                                                                      | 95  |

| 4.21       | Illustration of how the nonlinear control works. Both PFETs turn on whenever $V_{OUT}$ drops below $V_{LOW}$ (a), while both NFETs turn on whenever $V_{OUT}$ spikes above $V_{HIGH}$ (b).                                                                                                         | 96  |

| 4.22       | Die photo of the second version 3-level VR test-chip. Similar to the first version, flying capacitors are placed under the inductors to save                                                                                                                                                       |     |

|            | die area.                                                                                                                                                                                                                                                                                          | 97  |

| 4.23       | Snapshot of layout showing that two connections betweeen power FETs $-$ N <sub>BOT</sub> -N <sub>MID</sub> and P <sub>BOT</sub> -P <sub>MID</sub> $-$ have high resistance, which significantly degrades conversion efficiency. This is due to a mistake of using                                  |     |

|            | too narrow and long paths to connect different power FETs                                                                                                                                                                                                                                          | 99  |

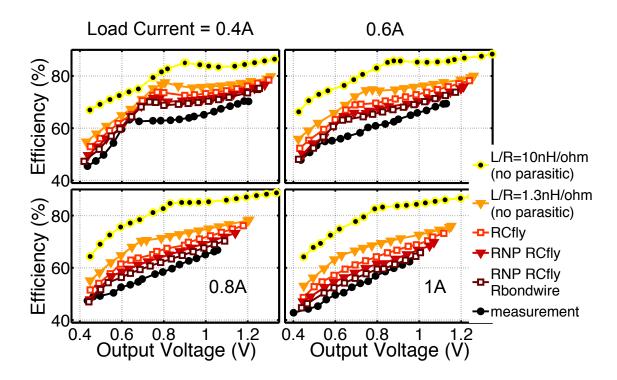

| 4 24       | Measured efficiencies are lower than expected due to parasitic resis-                                                                                                                                                                                                                              | 55  |

| 1.21       | tance caused by wires connecting $C_{FLY}$ (RCfly), wires connecting nFET<br>and pFET power switches (RNP) and bondwires (Rbondwire). Simu-<br>lated efficiencies including three parasitics match well with measured<br>efficiencies. Higher efficiencies are possible with better inductors with |     |

|            | higher Q                                                                                                                                                                                                                                                                                           | 101 |

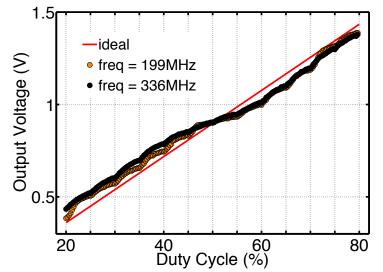

| 4.25       | Measured output voltage across duty cycles at 0A load current in open-                                                                                                                                                                                                                             | TOT |

| <b>_</b> ( |                                                                                                                                                                                                                                                                                                    | 103 |

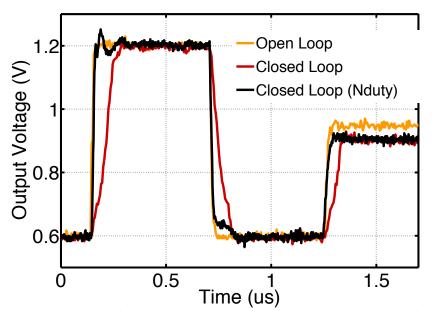

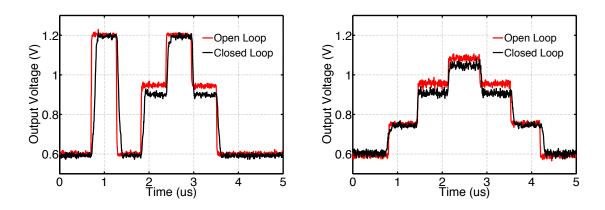

| 4.26 | Measured voltage traces show that using $N_{DUTYDVFS}$ in closed-loop op-   |     |

|------|-----------------------------------------------------------------------------|-----|

|      | eration allows the voltage to scale faster. Load current ranges between     |     |

|      | $0.33 \mathrm{A}$ (at 0.6V output voltage) and 0.38 A (1.2V output voltage) | 104 |

| 4.27 | Measurement shows that voltage scaling is slower in closed-loop than        |     |

|      | in open-loop. Both operate with 0.33-0.38A load current                     | 105 |

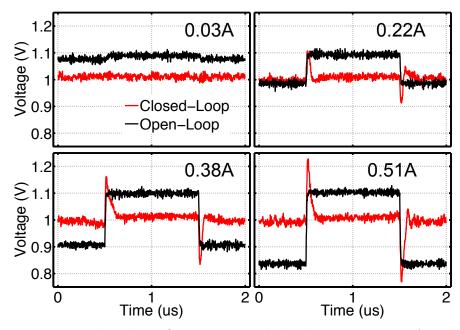

| 4.28 | Measured voltage fluctuation with load current steps of various magni-      |     |

|      | tudes (labeled in each subplot) when converter operates in open- and        |     |

|      | closed-loop                                                                 | 106 |

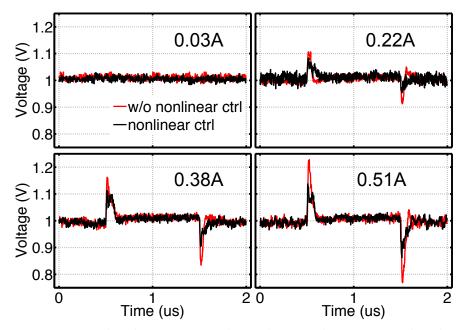

| 4.29 | Measured voltage traces show that nonlinear control reduces voltage         |     |

|      | droops/spikes during load current steps in closed-loop operation            | 106 |

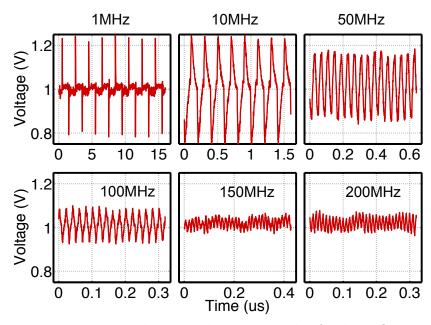

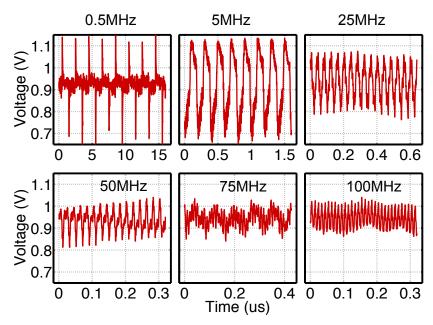

| 4.30 | Measurement results show that magnitude of voltage fluctuation changes      |     |

|      | as frequencies of load current steps change. Regulator operates at          |     |

|      | 200MHz switching frequency. Magnitude of load current step is 0.51A         |     |

|      | and the current transition occurs within 50ps based on simulation           | 107 |

| 4.31 | Measurements with same settings as Figure 4.30 except that regulator        |     |

|      | operates at 100MHz instead of 200MHz                                        | 107 |

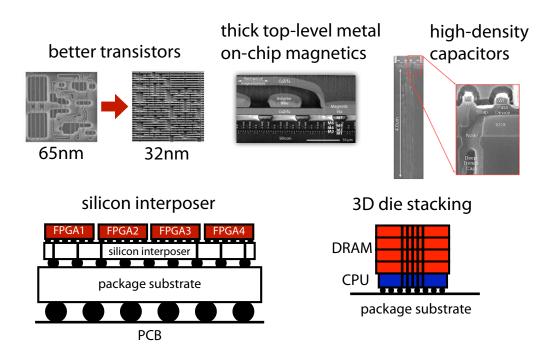

| 5.1  | Technologies that will impact IVR designs include better transistors [56],  |     |

|      | thick metal layers and integrated magnetics [34], dense capacitors [103],   |     |

|      | 2.5D silicon interposers [17] and 3D die stacking [57].                     | 109 |

# List of Tables

| 1.1 | Comparison of existing off-chip voltage regulators offered by TI [13, 12] and IVR published by IBM [28]       | 9  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Processor configuration and system parameters for SESC                                                        | 31 |

| 3.2 | Benchmark Suite.                                                                                              | 32 |

| 3.3 | Characteristics of the on-chip VR (all percentage (%) numbers are relative to the processor energy with DVFS) | 54 |

| 4.1 | Specifications of on-chip spiral inductors modeled using ASITIC [11] and MOS capacitors.                      | 81 |

| 4.2 | Breakdown of conversion loss of the 3-level converter for three design                                        |    |

|     | points                                                                                                        | 90 |

| 4.3 | Comparison with prior IVR designs                                                                             | 94 |

## **Citations to Previously Published Work**

Portions of this dissertation have appeared in the following publications:

"A Fully-Integrated 3-Level DC/DC Converter for Nanosecond-Scale DVFS" IEEE Journal of Solid-State Circuits (JSSC), Jan. 2012 Wonyoung Kim, David Brooks, Gu-Yeon Wei

"A Fully-Integrated 3-Level DC/DC Converter for Nanosecond-Scale DVS with Fast Shunt Regulation" IEEE International Solid-State Circuits Conference (ISSCC), Feb. 2011 Wonyoung Kim, David Brooks, Gu-Yeon Wei "System Level Analysis of Fast, Per-Core DVFS using On-Chip Switching Regulators"

IEEE International Symposium on High-Performance Computer Architecture (HPCA), Feb. 2008

Wonyoung Kim, Meeta S. Gupta, Gu-Yeon Wei, David Brooks

"Enabling On-Chip Switching Regulators for Multi-Core Processors using Current Staggering"

Workshop on Architectural Support for Gigascale Integration (ASGI at ISCA), Jun. 2007

Wonyoung Kim, Meeta S. Gupta, Gu-Yeon Wei, David Brooks

### Acknowledgments

I am who I am thanks to those surrounding me. I used to joke that whenever I read someone's thesis, I would read the acknowledgement section first. That was partly true and not entirely a joke because I thought while the body of the thesis shows what kind of research the person did, the acknowledgement section shows the human side of how the person spent his/her PhD years. It's not just about thanking people, but also about looking back at your graduate school years and cherishing invaluable memories. So here I am, writing this one day before the thesis submission deadline, thinking about all the good things that happened to me in the last six and a half years and the great people that made those days especially memorable (although I still don't know if Gu approved my thesis).

I was really fortunate to have Gu and David as my co-advisors. When I first arrived at Harvard, I was a 21 year old, just-out-of-undergrad student who had little clue about how to do good research, how to write good papers, and how to present my ideas clearly to other people. Gu and David basically taught me a lot of things that I am proud of today. I remember when we were preparing for my first talk to be given at HPCA 2008. I gave a practice talk and apparently it was so terrible that just giving me feedback on the spot was not going to fix it. Gu asked me to video-tape myself, write down what I said and send that to him so that he could fix the script and I could memorize it. Even after I memorized the whole thing, we practiced 6-7 more times to make the whole presentation sound natural, as if I didn't memorize anything. I remember David coming to Ben and my hotel room to have me rehearse the talk one last time. Eventually, I gave a satisfying talk at the conference and was really excited to see well-known academics ask questions about my research. Some people might say this seems pretty tough, but I am really thankful for those experiences and I think those trainings made me who I am today. I am not sure if I would have the patience to sit through 6-7 practice talks for anyone else, but Gu and David was willing to do that for the students. I also have very fond memories of having long - sometimes up to 3 hour long - meetings with Gu, David and Meeta when we were working on the HPCA paper. Gu and David's conversations were not just limited to our paper, but would go off on tangents discussing various topics in the semiconductor industry and other random research ideas not necessarily related to our paper. I would just sit there and try to absorb anything I could hear and process since everything was so new to me. Those were really great learning experiences for me as a G1/G2 PhD student and I think it heavily affected my research moving forward. It was also a great feeling to be able to hear and realize how much passion my advisors have on what they work on. I still chat with David on gchat on all sorts of topics to the point that Jiye started complaining about it =)

I also want to thank my committee members. The first time I met Paul was when he served in my quals committee. I had heard great things about him before, but I realized during the quals that he was genuinely interested in learning new things. He would ask questions not to criticize me, but because he was really interested in the answers. Tanay Karnik was kind enough to fly all the way from Hillsboro to serve in my PhD committee. I had seen his name in numerous IVR papers from Intel and always wanted to talk to him. So I just walked up to him at ISSCC to ask several questions and he was kind of enough to have a discussions with me then and also afterwards via email.

I can't even imagine what my PhD life would have been like without our crazy group members. Crazy here is a compliment. I feel excited, entertained and motivated by crazy people. All of our group people are not only great researchers (or research machines injecting coffee and spitting out papers), but are also people who are interested in a wide variety of things and love to have lively discussions. The VLSI group people when I first got here - Hayun, Andrew, Ankur, Ruwan, Amber and Mark - were all kind enough to teach me all the nitty-gritty things I should know to start designing chips. Once I started working with Meeta around March 2007, she taught me so many things, although she might not have realized that. I think that was when I started going over to MD307 often to hang out with Alex, who would be often focused in day-trading, and Ben, who would always be very well organized and dressed formally. I really enjoyed going to ISCA and HPCA with Alex and Ben. It was my first time going to a conference and they introduced me to a lot of people and taught me what to do in conferences. I have lots of good memories having endless conversations with Vijay about random stuff. Vijay might like to think they were philosophical conversations, but I recall most of them were not = P I learned a lot from his work ethics and perfectionist tendencies when writing papers. I was always worried whenever group members left that life would be more boring without those leaving. It turned out there were always new members who were as interesting as those who left. Tao, Saekyu, Silvia, Mario in MD311 and Svilen, Kevin, Simone, Brandon, Mike, Bob, Sophia, Amanda in 307. It even feels almost meaningless to list people from two groups separately since we always have lunch together and somehow find different topics to talk about everyday. I'll never forget the fun conversations over lunch and feeling sleepy after filling myself up with truck food. I'll definitely miss Svilen's daily greetings of "What's going on Wonyoung", Kevin's socks that used to lie around in 307, Kevin and Mike's absurd debates, learning about China from Tao and Silvia and countless memories of crunching before tape-out and paper deadlines. I can bet with pretty high confidence that our group has one of the most exciting group dinners. I hope we'll have a chance to gather altogether in the future.

I would also like to thank Glenn for his tremendous help throughout the years. I think Glenn might be the single most important person in our group since he boosts the productivity of everyone! Arriving at Harvard with little idea on how a server works, he was very patient in teaching me all the nitty-gritty things I should know to make the best use of our high-performance linux machines. One unfortunate thing that might bother Glenn is that I still open multiple emacs windows...

I have long-lasting memories with friends outside of lab. Taeg Sang hyung, Myung Jin nuna, Will and HwanChul. At some point we were spending so much time together that it was hard to believe we will be apart someday. Everyone is now scattered across different states and countries, but I'm sure we'll have a chance to get together to do some stupid things (we'll need Will for that haha). Hong Ha, Jung Ook, Yejin, all born in 84, were really good friends. Hye Young nuna, In Keun hyung - it was unfortunate we met so late into my PhD years, but it was always a joy to discuss Korean and US politics with them. I also have fun memories with my high-school friends, Heesang and Leebong, both being energetic and passionate people that I love to mingle with.

I cannot thank my family enough for all the love they've given me. Although far

away in Korea, my parents and my older brother were always supportive of whatever I wanted to do with my life (although it's true I've never set out to do something really crazy). They were always there to give me love and advice full of wisdom. I miss them very much and often wish I could've visited Korea more often during my PhD. Thankfully, Jiye was here for me at Boston. This journey would have been so much more boring, dull and less colorful had Jiye not been there the whole time with me. Memories are best when shared with someone you love. Since coming to Boston as 21-year old students with no clue about research or living in the US, Jiye and I have gone through so many experiences together and I am thankful to be able to share so much memories with her. After 3 years of married life and 7 years since we started dating in December 2005, she still surprises me with her thoughtfulness and understanding towards other people and herself.

Thank you so much for everything everyone. I am who I am thanks to all of you.

## Chapter 1

# Challenges of Delivering Power to SoCs and the Need for Integrated Voltage Regulators

#### Contents

| 1.1 | Challenge of delivering power to modern SoCs | <b>2</b> |

|-----|----------------------------------------------|----------|

| 1.2 | Solution: Integrated Voltage Regulators      | <b>5</b> |

## 1.1 Challenge of delivering power to modern SoCs

The rise of mobile computing places ever-increasing demands on high performance and low power for future microprocessor designs, not only for the mobile devices but also for the back-end servers needed to support their proliferation. In light of these demands, chip architects have moved towards tightly integrated system-on-chips (SoC) that incorporate multiple cores and heterogeneous components (e.g., memory controllers, hardware accelerators, etc.) into a single chip. Such complex SoC systems require sophisticated power delivery schemes to manage power efficiently.

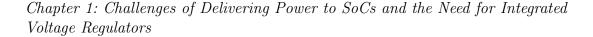

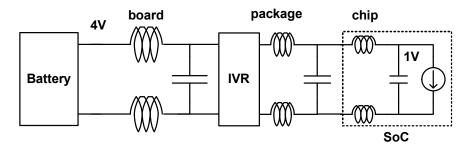

Figure 1.1 shows a high-level diagram of how power is typically delivered from a high-voltage source to an SoC that operates at around 1V in mobile and server systems. In mobile handsets and laptops, power comes from batteries operating at around 3.7V and 5-15V, respectively. Server systems deliver power at higher voltages such as, for example, 480VDC in Facebook's datacenters [5] and 110VAC from wall plugs for smaller servers, and convert them down to 12V at the motherboard where the SoC sits. The conversion from a higher voltage to 12V is not drawn in Figure 1.1. Off-chip voltage regulators (VRs or often called DC-DC converters) convert the high 3.7V or 12V down to a voltage range that the SoC can operate under, which is 0.7-1.1V in this case. This form of power delivery has the following problems.

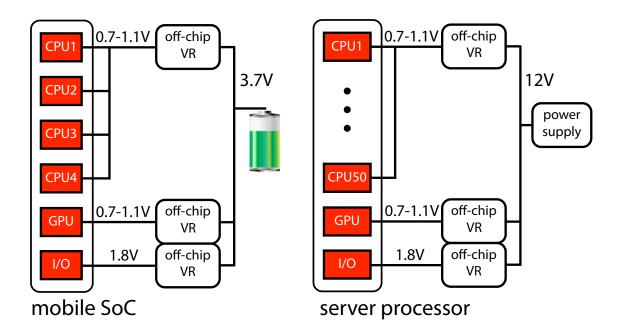

1. Wastes power due to shared voltage domains across multiple cores and IP blocks: Since one VR can deliver one voltage, the number of required VRs and associated board components is proportional to the number of SoC voltage domains. Multiple cores typically share a single voltage partly because it is difficult to duplicate bulky off-chip VRs due to board area overhead and

Figure 1.1: Power delivery in mobile and server systems

the challenge of routing large numbers of voltage rails on the board. Since performance demands can vary widely across cores [51], a shared voltage cannot track the different demands, which leads to wasted energy (Figure 1.2).

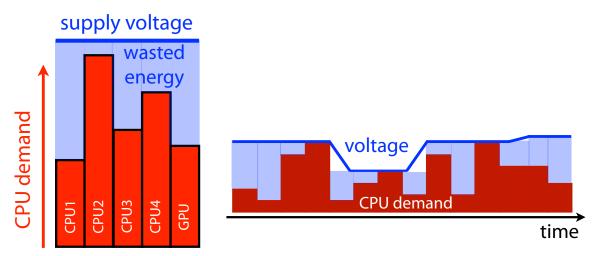

2. Wastes power due to slow DVFS: Existing off-chip VRs can scale the voltage at microsecond timescales [32], which is not fast enough to track fast-changing CPU demands [84]. The mismatch between the voltage and CPU demand results in wasted energy (Figure 1.2). Voltage scaling is slow with off-chip VRs because of large amounts of decouling capacitors (decap) on the board, package and SoC die (Figure 1.3). There are parasitic inductance on the path connecting the off-chip VR and SoC die. Since the parasitic inductance can cause large voltage fluctuation, designers place decaps on the board, package and SoC dies to suppress voltage noise. Whenever the off-chip VR changes

Figure 1.2: Illustration showing how shared voltage domains and slow DVFS lead to wasted energy.

Figure 1.3: Large amounts of decaps in the board, package and SoC die decrease the speed of voltage scaling

Figure 1.4: Teardown images of iPhone 4S and iPhone 5 show that off-chip VRs and required passive elements occupy a significant area on the board

the voltage, it has to charge/discharge all of the decaps, which makes voltage transition slow.

- 3. Occupies large board area: Reducing board area is important especially for portable electronics because a smaller board leaves more room to fit a larger battery in a constrained space, which enables longer battery life. Figure 1.4, a teardown image of iPhone 4S and iPhone 5 [8], shows that off-chip VRs and required board-level inductors and capacitors occupy a significant area. It also shows that off-chip VR area has not decreased over phone generations.

- 4. Costly due to multiple board-level components: Existing off-chip VRs usually consist of three board-level components power switches, inductors and capacitors. Some VRs use a separate feedback controller chip, but others integrate them in the same die as the power switches. As the number of SoC voltage domains increase, the number of board components required for off-chip VRs increase proportionally, increasing cost and complexity of board design. As logic ICs become more complex, there can be up to 10 voltage domains [14], which requires roughly 30 board components for off-chip VRs. A VR solution using fewer board components has the potential to reduce component cost and simplify power delivery on the board.

#### **1.2** Solution: Integrated Voltage Regulators

What if we can design a VR that drastically reduces the number and size of required board-level passives? What if the entire VR solution — including power

Figure 1.5: Power delivery using IVRs in a server system

switches and passives — could be small enough to be integrated in the SoC die or package? There has been a rising interest in building integrated VRs (IVR) occupying much smaller footprint and using fewer discrete components than off-chip VRs [42, 88, 91]. To tackle the aforementioned problems of existing off-chip VRs, this thesis builds upon prior works and studies system-level benefits of IVRs and proposes ways to build more efficient IVRs.

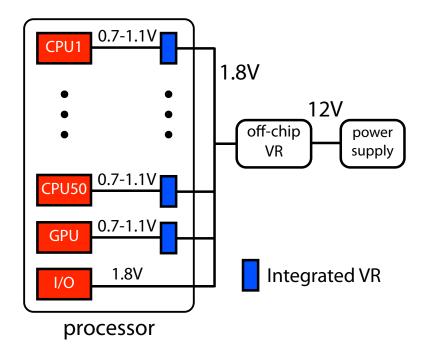

Figure 1.5 shows an example of how IVRs can change power delivery in a server system. An off-chip VR converts 12V to an intermediate voltage, which is 1.8V in this example, and multiple IVRs integrated in the processor die or package deliver different voltages to each core/IP-block depending on their processing demands. Following are potential benefits of this power delivery scheme using IVRs.

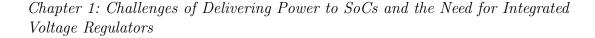

1. 1000 times faster voltage scaling than off-chip VRs:. Figure 1.6 compares

#### conventional (µs-scale)

IVR (ns-scale)

Figure 1.6: IVR enables nanosecond timescale DVFS compared to microsecond DVFS with existing off-chip VRs

Figure 1.7: IVR enables fast voltage scaling by reducing the amount of decap to charge/discharge

voltage traces of a typical off-chip VR [32] and measured results of an IVR test-chip [53]. The IVR can scale the voltage across 1V within 20ns, which is more than 1000 times faster than the microsecond time-scale in the off-chip VR case. Nanosecond timescale voltage scaling is possible because IVRs are placed close to the processor, either on the same die or package, and hence need to charge/discharge less capacitance than conventional off-chip VRs (Figure 1.7).

#### 2. 10 times smaller footprint than the smallest off-chip VRs commer-

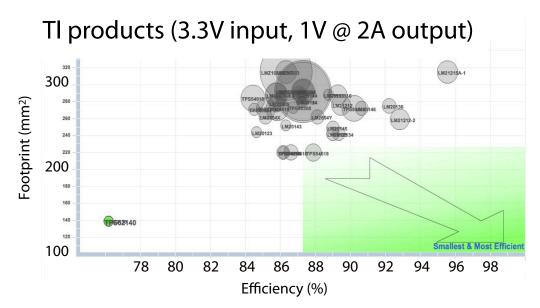

Figure 1.8: Efficiency and footprint data for TI voltage regulator products plotted using TI's WEBENCH, a simulator provided by TI for its voltage regulator products [13]

cially available: With smaller footprints, IVRs can reduce board area, leaving more room for larger batteries in mobile electronics. Figure 1.8 presents efficiency and footprint data for TI's off-chip VR products plotted using TI's WEBENCH, a simulator provided by TI. Existing off-chip VRs from TI occupy 100-300mm<sup>2</sup> with 75-96% efficiency when converting 3.3V to 1V at 2A current. Since regulator footprint is roughly proportional to the current that needs to be delivered to the output, we use current density(A/mm<sup>2</sup>) to compare regulator footprints across a wide range of load currents. TI's products in Figure 1.8 presents 0.007-0.02A/mm<sup>2</sup> current densities. In contrast, IBM recently reported an IVR that is 90% efficient with current densities as high as 2A/mm<sup>2</sup>, albeit at a lower input voltage of 2V being converted down to 1V [28]. TI's recent 2012 product called MicroSiP, not included in Figure 1.8, is specifically tuned

|                            | TI other<br>products | TI MicroSiP | IBM IVR |

|----------------------------|----------------------|-------------|---------|

| efficiency (%)             | 75-96                | 80          | 90      |

| current density<br>(A/mm²) | 0.007-0.02           | 0.07        | 2       |

| input voltage<br>(V)       | 3.3                  | 3.3         | 2       |

| output voltage<br>(V)      | 1                    | 1.2         | 1       |

Table 1.1: Comparison of existing off-chip voltage regulators offered by TI [13, 12] and IVR published by IBM [28].

towards lower footprint [12]. When converting 3.3V to 1.2V, MicroSiP is 80% efficient with 0.07A/mm<sup>2</sup>, which translates into a more than 20 times larger footprint per delivered current compared to IBM's IVR. Table 1.1 summarizes the specifications of existing off-chip regulators versus the IVR presented by IBM.

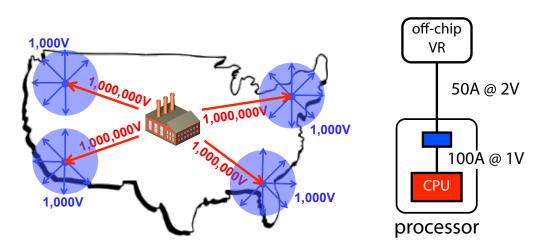

3. Reduce I<sup>2</sup>R loss and simplify board-level power distribution: Crosscountry grids deliver electricity at a high voltage and low current to reduce I<sup>2</sup>R loss. Similarly, IVRs can reduce I<sup>2</sup>R loss on the board by delivery power at a high voltage and converting down to a lower voltage at the point of load (Figure 1.9). This is especially important for high-performance server processors with maximum current exceeding 100A [10]. In these processors, a mere 1mΩ parasitic resistance on the board can add 10W of I<sup>2</sup>R loss, assuming 100A delivered at 1V. Using an IVR that instead delivers 50A at 2V, we can reduce

Figure 1.9: IVRs can reduce  $I^2R$  loss on the board by delivering power at a high voltage and low current and converting to a lower voltage at the point of load.

this loss to 2.5W. Moreover, IVRs can simplify board-level power distribution and potentially reduce parasitic resistance especially for processors that need large numbers of voltage domains. Revisting Figure 1.5, IVRs let the off-chip VR deliver only a single voltage on the board. Compared to a case where the board is split into multiple voltage planes for delivering multiple voltages, power distribution using IVRs simplifies board-level power distribution and allows the single voltage plane to have less parasitic resistance than split power planes.

To study the benefits of IVRs in delivering power to SoCs, this thesis presents the following points in the next chapters.

- I provide a brief background on the basics of VR design and prior works on IVRs that this thesis has built upon (Chapter 2).

- Through a system-level simulation study on the benefits of using IVRs, I show that fast, per-core DVFS can save up to 20% power in a 1.6W 4-core processor (Chapter 3).

- 3. I present measurement results from two IVR test-chips built using a 3-level topology, which is a hybrid form of an inductor-based buck and a switchedcapacitor VR. The 3-level VR reduces inductor size and presents higher efficiencies compared to existing buck VRs (Chapter 4).

- 4. I discuss what future process technologies can further improve IVR efficiencies and current densities beyond those of IVRs built using standard digital CMOS processes (Chapter 5).

## Chapter 2

# Basics of Voltage Regulators and Challenges of Integration

#### Contents

| <b>2.1</b> | Basics of step-down voltage regulators       | <b>13</b> |

|------------|----------------------------------------------|-----------|

| 2.2        | Challenges of Integrating Voltage Regulators | 15        |

| <b>2.3</b> | Evolution of IVRs                            | <b>21</b> |

#### 2.1 Basics of step-down voltage regulators

While IVRs facilitate fast, per-core DVFS, they also introduce various overheads compared to existing off-chip VRs. In order to understand these overheads, this section provides an overview of existing step-down off-chip VRs and IVRs.

Switching and linear VRs are two widely-used step-down VR topologies. Linear VRs offer several advantages: ease of on-chip integration, relatively small size, and good response to load current transients [39]. Unfortunately, the maximum achievable power-conversion efficiency of a linear VR is constrained by the ratio of  $V_{OUT}$  (the output voltage of the VR) to  $V_{IN}$  (the input voltage to the VR). For example, when a linear regulator converts a 1.1V  $V_{IN}$  to a 1V  $V_{OUT}$ , high power conversion efficiency (~90%) is possible. However, as  $V_{OUT}$  decreases further and deviates away from the input voltage, maximum efficiency degrades linearly. When delivering power to a processor using DVFS, the VR has to deliver a wide range of output voltage levels (e.g., 0.7-1.1V), in which case the efficiency degradation of a linear VR can be prohibitively high at low  $V_{OUT}$  levels.

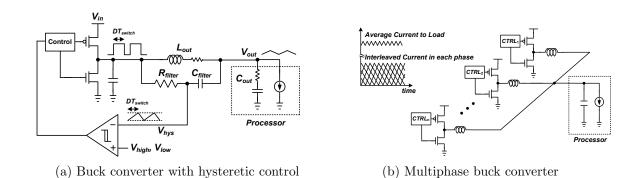

In contrast, a switching VR can regulate a wide range of output voltage levels with higher power-conversion efficiency that is less sensitive to the  $V_{OUT}/V_{IN}$  ratio. Hence, switching VRs are better suited for loads employing DVFS [111]. This higher conversion efficiency stems from its reliance on inductors and/or capacitors as low-loss energy-transfer devices between  $V_{IN}$  and  $V_{OUT}$ , but they can be bulky and consume large area. While there are several types of step-down switching VRs — those using inductors (buck VR), capacitors (switched-capacitor VR) or both (3-level VR) to transfer energy, we will first study inductor-based buck VRs, which is the most

Figure 2.1: Buck converter schematics

popular topology for existing off-chip VRs. We will examine the two other topologies, switched-capacitor and 3-level VRs, in more detail later in Chapter 4.

A typical inductor-based buck VR, shown in Figure 2.1(a), consists of three sets of components: switching power transistors, the output filter inductor ( $L_{OUT}$ ) and capacitor ( $C_{OUT}$ ), and the feedback control consisting of a hysteretic comparator and associated filter elements ( $C_{FILTER}$  and  $R_{FILTER}$ ) that enhance loop stability. The power transistors can simply be viewed as an inverter that switches on and off at a switching frequency and provides a square wave to the low-pass output filter composed of  $L_{OUT}$  and  $C_{OUT}$ . The VR output,  $V_{OUT}$ , powers the microprocessor load and its voltage is approximately set by the duty cycle of the square wave. This regulated voltage exhibits small ripples since the filter attenuates the high-frequency square wave. The feedback loop is closed by feeding  $V_{HYS}$ , which is the output of the filter composed of  $C_{FILTER}$  and  $R_{FILTER}$ , to the hysteretic comparator. The duty cycle of the square-wave input to the power transistors is set by the hysteretic comparator output. As shown in Figure 2.1(a), the hysteretic comparator has a high threshold ( $V_{HIGH}$ ) and a low threshold voltage ( $V_{LOW}$ ). The PMOS power switch turns on when  $V_{HYS}$  drops below  $V_{LOW}$ , and the NMOS turns on when the  $V_{HYS}$  increases above  $V_{HIGH}$ . Since  $V_{OUT}$  directly affects  $V_{HYS}$ , when  $V_{OUT}$  fluctuates in response to load current transients, hysteretic control can react very quickly. While there are several other feedback control schemes one can employ for a buck VR, hysteretic control is one example that offers fast transient response characteristics while keeping design complexity low [69].

The power transistors and inductor shown in Figure 2.1(b) can be interleaved to form a multiphase buck converter. Researchers have proposed multiphase converters for high load current applications [117, 76, 122], since they can reduce the peak current in each inductor. Parallel sets of power transistors and inductors are interleaved and connected to the same load such that current through each inductor is interleaved across even time intervals. Hence these interleaved inductor currents cancel out at the output node and result in an average current that has small ripple. Moreover, this interleaving accommodates the use of small output filter capacitance while meeting small voltage ripple constraints. Since the number of necessary phases increase with load current, VR footprint is roughly proportional to load current.

#### 2.2 Challenges of Integrating Voltage Regulators

While there are various specifications in VR design, conversion efficiency and footprint (or current density) are two of the most important for both off-chip and integrated VRs. Revisiting Figure 1.8, we see that there is a trade-off between footprint and efficiency. As all designs in the figure are buck VRs, the trade-off is present because larger inductors have higher Q, which leads to smaller conversion loss. A 10nH, 0.4ohm 10nH, 0.08ohm 10nH, 0.04ohm 0.4 x 0.6 x 0.45mm 0.5 x 1 x 0.6mm 1.3 x 2.3 x 1.5mm

Figure 2.2: Dimensions, DC resistance and inductance of various chip inductors from Coilcraft [4]. Images of inductors is roughly to scale.

big challenge of building IVRs is to make the footprint small enough for integration while achieving high efficiencies. To maximize efficiency (and minimize loss), it is important to understand the sources of VR losses.

Typical buck VRs have the following three main sources of losses.

- Capacitive loss of power transistors: When power transistors switch on and off to generate a square wave on the output (input of inductor), there is a CV<sup>2</sup>f loss due to parasitic gate capacitance of the power transistors. This loss is proportional to switching frequency and power switch width.

- Resistive loss of power transistors: As current flows through the power transistors, there is I<sup>2</sup>R loss due to on-state parasitic resistance of the power transistors. This loss is inversely proportional to power switch width. As a result, there is a trade-off between capacitive and resistive loss of power transistors [96].

- 3. Resistive loss of inductors: Non-ideal inductors lead to I<sup>2</sup>R loss associated

Figure 2.3: IVRs can be integrated on the package-level (a,b) or in the logic IC die (c).

with the inductor coil resistance. Larger inductors have higher Q and lower resistance (Figure 2.2), which leads to a trade-off between conversion efficiency and footprint. Since inductors small enough to be integrated on-die or onpackage have lower Q than larger inductors, they tend to have larger parasitic resistance. Assuming a fixed material and process for the inductor, one way to reduce inductor resistance is to reduce the inductance (L), since Q is equal to  $2\pi fL/R$  (Note that Q changes with L, so R does not stay proportional to L. The relationship between R and L depends on the structure of the inductor.). To reduce L, we need to increase the switching frequency of the VR to maintain small output voltage ripple. This leads to larger capacitive loss of power transistors, resulting in a trade-off between transistor capacitive loss and inductor resistive loss.

With unlimited footprint, designers can maximize VR efficiency by using large inductors with high Q, power transistors with high breakdown voltages and switch them at very low frequencies to minimize capacitive losses. However, to implement IVRs with small footprint, designers are forced to use low Q, small L inductors and switch power transistors at high frequencies. Since conventional power transistors with high breakdown voltages are not suitable for high switching frequencies, researchers have proposed using standard digital CMOS transistors as power transistors in IVRs [58, 88]. These transistors cannot sustain high voltages, which is why Figure 1.5 in the previous chapter uses an off-chip VR to convert 12V to an intermediate voltage of 1.8V instead of using IVRs to convert 12V to 1V.

Given these challenges in implementing IVRs, there are several ways to integrate VRs with technologies that exist today (Figure 2.3).

1. Single-die integration: Integrating IVRs and logic ICs on a single die offers the highest level of scalability in terms of the number of voltages that can be provided to the logic IC (Figure 2.3(a)). Integrated in the logic die, IVRs could be scattered around the die to provide per-core voltage control even in manycore processors with over 50 cores such as Intel's Xeon Phi [6] or Tilera's Tile 64 [7]. However, the problem is that standard logic process technologies typically do not offer high quality passives and metal layers that are thick enough to deliver large amounts of current. Including these processes in the logic die incurs cost of adding mask layers. Furthermore, IVRs can add large die area, which is especially costly in cutting-edge processes (e.g., 20/22nm, 28/32nm) that are used to fabricate new logic IC products. Amount of IVR die area overhead depends on the power densities of the IVR and processor. For example, Intel's high-end laptop processor (Core i7-3940XM Ivy Bridge) has 55W TDP with 160mm<sup>2</sup> die area, which results in a maximum power density of 0.34W/mm<sup>2</sup> [9]. Assuming an area-efficient IVR with 2W/mm<sup>2</sup> power density, which is one of the highest values reported, the IVR adds 17% additional die area when integrated on the processor die. IVR area overhead can be smaller in processors with lower power consumption. Intel's Core i7-3612QM, which is slightly less powerful than Core i7-3940XM, has 35W TDP with 160mm<sup>2</sup> die area, which results in a maximum power density of 0.22W/mm<sup>2</sup> and 11% IVR die overhead. As a result, single-die integration could be more suitable for low-power SoCs than high-performance servers with high power densities.

2. Package-level integration with on-package SMT passives: Designers can integrate power transistors and VR controller blocks in the logic IC die while mounting small SMT chip inductors and capacitors on the package (Figure 2.3(b)). They can take advantage of high-quality passives without adding costly masks to the logic die. Cost of adding on-package passives might be acceptable for high-performance processors since they already have a large number of on-package decoupling capacitors, but the cost might be not as acceptable for mobile SoCs that do not have any discrete deoupling capacitors on-package. Moreoever, SoCs in mobile phones are typically contained in a package-onpackage (PoP) in which the package is too thin to mount SMT passives unless the passives are custom-made to be thinner than standard ones. Revisiting Figure 2.2, it shows that the thickness of an 0201 inductor is 0.45mm, which is too thick to fit in the 0.2mm thick bottom layer of a PoP where the logic package usually sits [3].

3. Package-level integration with separate IVR dies: IVRs can be implemented in a separate die using process technologies optimized for high-quality passives, thick metal layers and transistors with low on-state resistance (Figure 2.3(c)). Instead of paying the price of larger die area in expensive, cutting-edge processes, IVRs can be fabricated in a separate die using a process that is not as advanced as those for logic ICs, but more optimized for VR applications. However, known-good-die (KGD) is a problem as is the case in any multi-chip module (MCM) with multiple dies. If there is an error in the relatively cheaper IVR die, the entire package, including the more expensive logic die, is considered faulty since it is very costly to dissemble the MCM and replace the IVR die. To reduce the cost of dealing with faulty IVR dies, it is very important to fully test the IVR die on the wafer-level to guarantee it is a "good die" before integrating in the MCM. However, this is challenging because wafer-level testing is usually more costly and has more restrictions than package-level testing.

There has been various prior works on implementing IVRs using the aforementioned integration methods. The next section lists prior works on IVRs and how these designs integrated different IVR components.

Figure 2.4: There has been increasing interest on IVRs by industry and research communities.

#### 2.3 Evolution of IVRs

IVR publications started to appear in 2003 and have steadily increased, constantly introducing new demonstrations and techniques for IVR design (Figure 2.4).

- Before 2003: PCB mounted buck VRs mainly consisted of power switches, controller chips, inductors and capacitors mounted on the board in separate packages. Power switches built in mature process technologies limited the switching frequency usually to lower than 1MHz, requiring large inductors (≥1µH) and capacitors. Efficiencies reached 95%, but footprints were large and current densities were low in the order of 1-10mA/mm<sup>2</sup>.

- 2003-2007: Package- and chip-level integration: Following feasibility analyses on integrated buck converters [58, 88], researchers presented buck converters with package- and chip-level integration [41, 91, 42, 71, 70, 74, 19, 112, 100, 73, 107, 89, 62, 21]. Intel used standard digital CMOS transistors cascoded

to sustain higher input voltages switching at over 100MHz. Instead of using low Q on-chip spiral inductors, they mounted small, high-quality SMT chip inductors in the range of 1-20nH on the package. efficiency. Using on-package inductors could be a viable solution for Intel since their processors already have a large number of on-package capacitors and adding several more inductors might not add much cost. However, adding on-package inductors could be a bigger leap for mobile SoCs with no existing on-package capacitance. Other works presented a single-chip solution using on-chip spiral inductors to simplify package design, albeit with lower efficiency due to poor inductor quality.

3. 2008-2011: Fully-integrated switched-capacitor and 3-level converters: To rely less on low-quality inductors while providing a single-chip solution, other works proposed fully-integrated SC and 3-level converters [82, 102, 81, 60, 28, 83, 52, 121, 48, 36, 26, 59]. We will compare these topologies in more detail in Chapter 4. IBM presented a switched-capacitor converter using deep trench capacitors that are 20 times denser than MOSFET capacitors, saving significant amount of die area and achieving high current densities. Harvard designed a 3-level converter using a 1nH inductor with capacitors placed underneath to save die area. At the same time, researchers continued to improve both package-integrated [98, 63, 43, 25, 24, 65, 38, 46, 90, 37, 97, 64] and fully-integrated buck converters [108, 101, 113, 22, 20, 99, 72, 54, 110, 68, 55]. Intel presented a buck converter that could deliver 50W [90], paving the way for IVRs to be integrated in high-performance systems. NXP proposed a dual-die solution where a die optimized for high-quality inductors is stacked on top of

another die containing power switches and control circuitry [25].

Now that we have studied the basics of IVR design and what the main challenges are, we take a step back and analyze how much system-level energy savings is possible using IVRs.

## Chapter 3

# System-Level Energy Savings with Fast, Per-Core DVFS using

## **Integrated Voltage Regulators**

#### Contents

| 3.1        | Prio  | r Works on Fine-Grain DVFS                               | 28 |

|------------|-------|----------------------------------------------------------|----|

| <b>3.2</b> | Pote  | ntial of Fast and Per-Core DVFS Schemes                  | 29 |

|            | 3.2.1 | Simulation Framework                                     | 31 |

|            | 3.2.2 | Offline DVFS Algorithm                                   | 32 |

|            | 3.2.3 | Effects of Finer Temporal Resolution                     | 34 |

|            | 3.2.4 | Per-Core vs. Chip-Wide DVFS                              | 36 |

| 3.3        | Cha   | racteristics of On-Chip Regulators                       | 40 |

|            | 3.3.1 | Model and Simulation of Buck VR                          | 40 |

|            | 3.3.2 | Design trade-offs of IVRs                                | 41 |

|            | 3.3.3 | Regulator Efficiency                                     | 44 |

|            | 3.3.4 | Load Transient Response                                  | 47 |

|            | 3.3.5 | Voltage Scaling Time                                     | 49 |

|            | 3.3.6 | On-Chip Regulators for Single and Multiple Power Domains | 50 |

| 3.4 Energy Savings for Per-Core and Chip-Wide DVFS us- |                              |    |  |  |

|--------------------------------------------------------|------------------------------|----|--|--|

| $\mathbf{in}$                                          | g On-Chip Regulators         | 53 |  |  |

| 3.4.                                                   | Comparison of Energy Savings | 54 |  |  |

| 3.4.                                                   | 2 Power Domain Scalability   | 58 |  |  |

Dynamic voltage and frequency scaling (DVFS) was introduced in the 90's [66], offering great promise to dramatically reduce power consumption in large digital systems by adapting both voltage and frequency of the system with respect to changing workloads [93, 95, 45, 116]. Unfortunately, the full promise of DVFS has been hindered by slow off-chip voltage VRs that lack the ability to adjust to different voltages at small time scales. Modern implementations are limited to temporally coarse-grained adjustments governed by runtime software (i.e. the operating system) [1]. Moreover, the large footprint of off-chip VRs make it difficult to use large numbers of them for per-core or per-IP block voltage control.

This chapter explores the interplay of the promising characteristics and costs of employing IVR designs in modern CMP system architectures. While this study considers CMP designs comprising multiple low-power processor cores within the context of a mobile embedded system, the analysis described can be extended to higher-power processors as well.

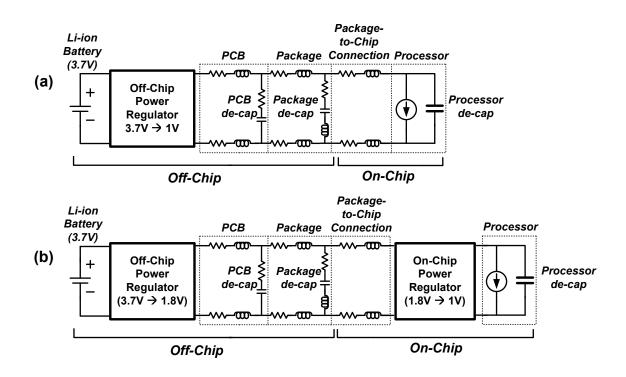

Figure 3.1 illustrates three power-supply configurations that this chapter studies.

- Slow, Global DVFS: The first configuration (left) represents a conventional design scenario that only uses an off-chip VR. This VR directly steps the power supply voltage, assumed to be 3.7V provided by a Li-Ion battery, down to a processor voltage ranging from 0.6V to 1V.

- 2. Fast, Global DVFS: The second configuration (middle) implements a twostep voltage conversion scenario. Given an inherent degradation in conversion efficiencies for large step-down ratios, an off-chip regulator performs the initial step-down from 3.7V to 1.8V, which can be shared by other on-board compo-

Chapter 3: System-Level Energy Savings with Fast, Per-Core DVFS using Integrated Voltage Regulators 27

Figure 3.1: Three power-supply configurations for a 4-core CMP.

nents. The 1.8V supply then drives an on-chip voltage regulator that further steps the voltage down to a range of 0.6V to 1V as a single power supply domain distributed across a 4-core CMP.

3. Fast, Per-Core DVFS: The third configuration (right) expands on the second configuration by providing four separate on-chip power domains via individual IVRs. These three configurations constitute the framework through which we compare the costs and benefits of fast, per-core DVFS enabled by IVRs.

The main points of this chapter are as follows:

• We explore the energy savings offered by implementing both temporally finegrained and per-core DVFS in a 4-core CMP system using an offline DVFS algorithm (Section 3.2).

- We present a buck-type IVR design space analysis that considers key regulator characteristics—DVFS transition times and overheads, load current transient response, and regulator conversion losses (Section 3.3).

- We combine the energy savings with the IVR cost models and come to several conclusions. For a single power domain, on-chip regulator losses offset the gains from fast DVFS for many workloads. In contrast, fast, per-core DVFS can achieve energy savings (≥20%) when compared to conventional, single power domain, off-chip VRs with comparatively slow DVFS (Section 3.4).

#### 3.1 Prior Works on Fine-Grain DVFS

There has been prior work that has focused on exploring the benefits of multiple frequency/power domains in microprocessors compared to a global frequency/voltage. In the area of CMP systems, per-core DVFS has been shown to offer larger energy savings than chip-wide DVFS using four different voltage and frequency levels [45], but this work considered relatively coarse DVFS time intervals and did not consider any of the issues related to power supply regulation. Other works explore multiple clock domain (MCD) architectures, which use globally asynchronous, locally synchronous (GALS) techniques to provide *within-core* energy control. These techniques have demonstrated 17% improvement in energy-delay product compared to using a single domain [93]. An adaptive reaction time scheme for multiple clock domain processors have been proposed [116]. These works focus on the energy savings of the processor using per-core DVFS, and the algorithms associated with it, but do not consider the practical overheads of integrating multiple on-chip regulators. As this chapter shows, the practical overheads of on-chip regulators must be considered to argue that percore DVFS actually has large energy savings. At the circuit-level, there have been many works demonstrating on-chip regulators [40, 87, 111, 18], but these works solely analyze the energy conversion efficiency of regulators. These works do not consider any of the system-level overheads (DVFS scaling and voltage transient analysis) or the system-level benefits of on-chip regulators. The contribution of this chapter is the aggregation of ideal energy savings using per-core DVFS with the practical overheads of integrating on-chip regulators within each processor core.

#### 3.2 Potential of Fast and Per-Core DVFS Schemes

Dynamic voltage and frequency scaling can be an effective technique to reduce power consumption in processors. DVFS control algorithms can be implemented at different levels, such as in the processor microarchitecture [67], the operating system scheduler [47], or through compiler algorithms [118, 44]. Most previous work in the domain of DVFS control algorithms focus on coarse temporal granularity, e.g., voltage changes on the order of several microseconds, which is appropriate given slow response times of off-chip VRs. In contrast, on-chip regulators offer much faster voltage transitions as presented in Figure 3.2. This figure, a simulation of the IVR model described in a later section, shows voltage transitions can occur on the order of tens of nanoseconds, several orders of magnitude faster than off-chip VRs. DVFS algorithms implemented at the microarchitecture level provide the finest level of temporal control, hence, are good candidates for the fine-grained approach that we consider.

Chapter 3: System-Level Energy Savings with Fast, Per-Core DVFS using Integrated Voltage Regulators 30

Figure 3.2: DVFS transition times with an IVR

In this section, we explore the benefits of fast DVFS with fine temporal resolution and also highlight the benefits of per-core voltage domains compared to chip-wide DVFS. To explore the benefits and tradeoffs associated with temporally fine-grained and per-core DVFS, we rely on an offline DVFS algorithm that can easily be applied across the wide range of DVFS transition times we consider. Section 3.2.1 provides a brief overview of the simulation framework used in our study, and the methodology of the offline DVFS algorithm is described in Section 3.2.2. We then discuss the effects of finer temporal granularity (Section 3.2.3), and the savings for per-core versus chip-wide DVFS schemes (Section 3.2.4).

| Frequency         | 1GHz @ 65nm                                           | Vdd                | 1 V                                                                    |

|-------------------|-------------------------------------------------------|--------------------|------------------------------------------------------------------------|

| Core Area         | 16mm <sup>2</sup>                                     | Fetch/Issue/Retire | 2/2/2                                                                  |

| Branch<br>Penalty | 7 cycles<br>Hybrid Branch Predictor                   | Branch Predictor   | BTB (1K entries)<br>RAS (32 entries)                                   |

| Int registers     | 32                                                    | FP registers       | 32                                                                     |

| IL1               | 32KB, 32-way, 32B block<br>Hi/Miss latency 2/1 cycles | DL1                | 32KB, 32-way, 32B block<br>Hi/Miss latency 2/1 cycles<br>MESI-protocol |

| ITLB entries      | 64                                                    | DTLB entries       | 128                                                                    |

| MSHR size         | 8                                                     | Write Buffer size  | 16                                                                     |

| L2 size           | 512 KB                                                | MSHR size          | 16                                                                     |

Table 3.1: Processor configuration and system parameters for SESC.

#### **3.2.1** Simulation Framework

We employ an architectural power-performance simulator that generates realistic current traces. We use SESC [86], a multi-core simulator, integrated with powermodels based on Wattch [27], Cacti [94], and Orion [104]. A simple in-order processor model represents configurations similar to embedded processors like Xscale [31]. The per-core current load is 400mA when fully active and 120mA when idle. We model a configuration with a shared-L2 configuration, private-L1 caches in each processor, and a MESI-based coherence protocol. Table 3.1 lists the details of the 4-core processor configuration and system parameters. The simulator was modified to obtain cycleby-cycle current profiles for each core in the system.

In a CMP-based system, it is important to understand the interactions between the multiple cores. These interactions can be accurately characterized by analyzing a mix of multi-threaded and multi-programmed benchmarks. We use a composite benchmark suite composed of applications from SPEC2K, ALPBench [61], and SPLASH2 [114]. For multi-programmed scenarios, we consider several mixtures of a

Chapter 3: System-Level Energy Savings with Fast, Per-Core DVFS using Integrated Voltage Regulators 32

| Benchmarks   | Description                                                                                  | Memory Cycles<br>Total Runtime |  |

|--------------|----------------------------------------------------------------------------------------------|--------------------------------|--|

| ocean-con    | Large Scale Ocean Simulation                                                                 | 0.47                           |  |

| fft          | Fast Fourier Transform                                                                       | 0.4                            |  |

| facerec      | CSU Face Recognizer                                                                          | 0.22                           |  |

| cholesky     | Cholesky Factorization                                                                       | 0.197                          |  |

| raytrace     | Tachyon Ray Tracer                                                                           | 0.058                          |  |

| mcf4         | 4-high memory-bound (mcf)                                                                    | 0.697                          |  |

| mcf3, applu1 | 3-high memory-bound (mcf) and 1-high cpu-bound (applu)                                       | 0.697 ( <i>mcf</i> )           |  |

| mcf2, applu2 | <i>mcf2, applu2</i> 2-high memory-bound ( <i>mcf</i> ) and 2-high cpu-bound ( <i>applu</i> ) |                                |  |

| mcf1, applu3 | 1-high memory-bound (mcf) and 3-high cpu-bound (applu)                                       | 0.051 ( <i>applu</i> )         |  |

| applu4       | applu4 4-high cpu-bound (applu)                                                              |                                |  |

Table 3.2: Benchmark Suite.

memory-bound benchmark (*mcf*) and a cpu-bound benchmark (*applu*) from SPEC2K. Table 3.2 lists the different benchmarks used in this study along with the ratio of memory cycles to total runtime of the application for each. All benchmarks are run for 400M instructions after fast forwarding through the initialization phase.

#### 3.2.2 Offline DVFS Algorithm