## Ice Lithography for Nano-Devices

The Harvard community has made this article openly available. Please share how this access benefits you. Your story matters.

| Citation          | Han, Anpan, Dimitar Vlassarev, Jenny Wang, Jene A. Golvchenko, and Daniel Branton. 2010. Nano Letters 10(12): 5056-5059.                                                                                                                                                                                                                               |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Published Version | doi:10.1021/n11032815                                                                                                                                                                                                                                                                                                                                  |

| Accessed          | February 19, 2015 7:36:30 AM EST                                                                                                                                                                                                                                                                                                                       |

| Citable Link      | http://nrs.harvard.edu/urn-3:HUL.InstRepos:4635033                                                                                                                                                                                                                                                                                                     |

| Terms of Use      | This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at <a href="http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP">http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP</a> |

(Article begins on next page)

# Ice Lithography for Nano-Devices

Anpan Han<sup>1</sup>, Dimitar Vlassarev<sup>1</sup>, Jenny Wang<sup>1</sup>, Jene A. Golovchenko<sup>1,2</sup> and Daniel Branton<sup>3</sup>\*

<sup>1</sup>Department of Physics, Harvard University, Cambridge, MA 02138, USA.

<sup>2</sup>School of Engineering and Applied Sciences, Harvard University, Cambridge, MA 02138, USA.

<sup>3</sup>Department of Molecular and Cellular Biology, Harvard University, Cambridge, MA 02138, USA.

\*Corresponding Author. e-mail: <a href="mailto:dbranton@harvard.edu">dbranton@harvard.edu</a>; telephone 617-495-2685; fax 617-496-0189

ABSTRACT. We report the successful application of a new approach, ice lithography (IL), to fabricate nanoscale devices. The entire IL process takes place inside a modified scanning electron microscope (SEM), where a vapor-deposited film of water ice serves as a resist for e-beam lithography, greatly simplifying and streamlining device fabrication. We show that labile nanostructures such as carbon nanotubes can be safely imaged in an SEM when coated in ice. The ice film is patterned at high e-beam intensity and serves as a mask for lift-off without the device degradation and contamination associated with e-beam imaging and polymer resist residues. We demonstrate the IL preparation of carbon nanotubes field effect transistors (FETs) with high quality trans-conductance properties.

KEYWORDS. e-beam lithography, carbon nanotube, nano-device, field effect transistor

It was recently shown that water ice can serve as a resist during high resolution e-beam lithography<sup>1</sup>, easily achieving sub-10nm features. The special properties of water ice allow direct application in a vacuum environment, conformal coating of complex 3-D structures, through-resist mapping and registration of nanostructures, and simple, contamination-free removal. Here we demonstrate that high quality carbon nanotube FETs can be fabricated with ice lithography.

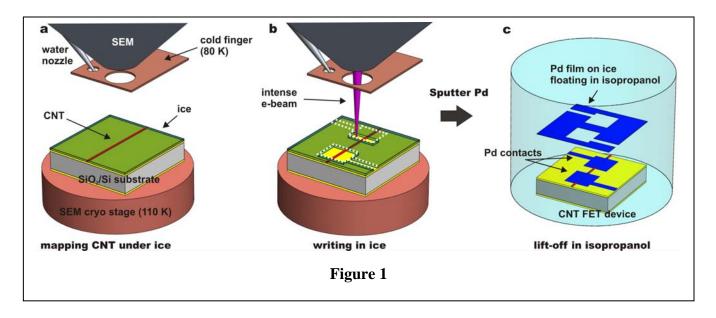

We extensively modified a field emission scanning and e-beam writing electron microscope (SEM) for device fabrication using IL (Figure 1). Based on our previous work fabricating sub 20 nm-wide metal lines by nano-patterning ice<sup>1</sup>, our new instrument is a cluster-tool that allows the entire IL process to be effected and examined within one vacuum system<sup>2</sup>. A sample containing the desired nano-device elements is first cooled to cryogenic temperatures in the microscope vacuum (for detailed methods, see Supporting Materials). Our sample consists of single walled carbon nanotubes (SWCNTs) grown by chemical vapor deposition (CVD) from an iron catalyst pad<sup>3, 4</sup>. When cooled to ~110 K the sample is exposed to water vapor from a gas injection system. A thin, conformal layer of amorphous ice, several

tens of nanometers thick, forms on the surface of the sample. The nanotubes are then located by imaging

through the ice layer with a low intensity e-beam. As shown below, typical damage and contamination associated with direct e-beam exposure are eliminated when imaging through ice. The ice resist is then appropriately patterned relative to the underlying nanostructures with a high intensity e-beam guided by an e-beam writing system built into the SEM. The patterning removes ice from those regions where metallic contacts are desired. The cold sample is then rapidly transferred through the vacuum onto a second cryostage located in a specially designed metal deposition chamber that had been incorporated onto the SEM. Here, metal films are plasma sputter-deposited onto the ice patterned sample surface. Two different metals can be deposited, including an adhesion layer which is critical for noble metal adhesion onto dielectric surfaces. Finally, the device is removed from the metal deposition chamber and immersed into isopropanol, which lifts off the metal where no ice had been removed. Thus, the standard processes of mapping SWCNT, Poly(methyl methacrylate) (PMMA) resist spinning, resist baking, e-beam exposure, development, and metal evaporation, which normally use 6 different instruments, are accomplished using the IL process in one instrument.

To electrically connect a CVD grown SWCNT to a pre-existing metal contact pad, the first step is to locate a SWCNT and map its position on the device substrate surface.

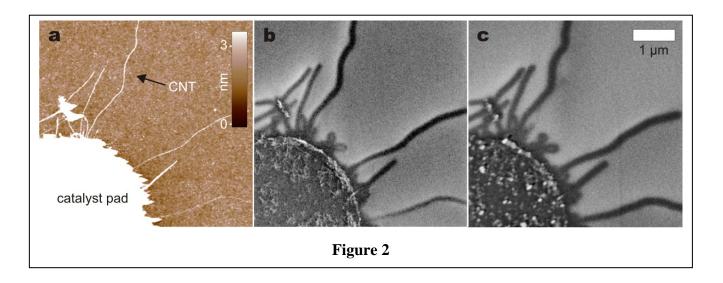

Figure 2 demonstrates that all SWCNTs visible in an AFM image can also be visualized through ice with the SEM. It normally takes 4 hours to image and map a  $50 \times 50 \mu m$  area with an AFM. We can easily map this area through ice in the SEM in just a few minutes. The e-beam dose used for imaging is

four orders of magnitude smaller than that required for actual patterning, so no significant ice removal occurs during imaging. Aside from the time saving aspects of *in situ* SEM imaging, e-beam damage and contamination<sup>5</sup> that have previously limited the usefulness of SEM mapping are avoided (see below).

Contrast for imaging SWCNT in the SEM is the result of dynamic charging of insulating layers by the incident e-beam<sup>6-9</sup>. Here, the underlying SiO<sub>2</sub> back gate insulator and the amorphous ice serve as the charged insulator layer, whereas the conducting SWCNTs are electrically grounded through the iron catalyst pad from which they grow. The insulating layers become negatively charged by exposure to the primary e-beam and the SWCNT remains at ground potential. Consequently, low-energy secondary electrons emitted near the nanotube are collected by the nanotube rather than the microscope's secondary electron detector. This visibly distinguishes the nanotubes as dark lines (Figure 2). Note that the image of the nanotube diameter can be much greater than its geometrical diameter, enabling even low resolution microscopes to image carbon nanotubes. Imaging the SWCNT through a thin dielectric layer can also be used as a non-invasive method for rapid quality control of the electrical integrity of nanodevices after dielectric coating and passivation.

The next step of IL is patterned ice removal to form the mask for metal deposition<sup>1</sup>. Guided by the SEM image of the nanotubes, the e-beam patterning system selectively removes ice to form the designed mask (Figure 1b). At 20 kV e-beam energy, typically a dose of 1 C/cm<sup>2</sup> is required to remove 80 nm thick ice. After the writing process, the sample can be immediately imaged again, at low SEM beam intensity to inspect the writing quality. Such inspection, which is not possible with standard lithography, provides a valuable opportunity to make minor corrections or abort further processing.

The patterned sample is next transferred onto the metal deposition cryostage held at 165 K. At this temperature, 14 nm of ice sublimes in 1 min. Five nm of ice are allowed to sublime from the entire sample surface to assure that any remaining ice at the bottom of the patterned mask wells is removed before depositing metals., and lift-off is finally carried out in isopropanol (Fig. 1c).

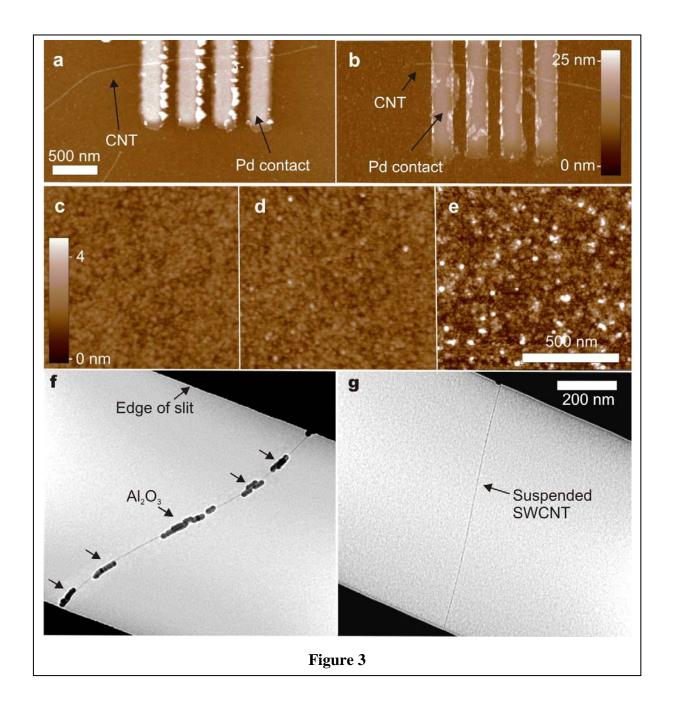

Two methods were used to evaluate e-beam induced defects or contaminants on the finished device. First, tapping mode AFM was used to inspect and compare SWCNT-metal nanostructures made by IL vs. standard e-beam lithography using a PMMA resist (Figure 3a-e). Following IL, the root-mean-

square surface roughness of the device surfaces barely increases from its initial value of 0.25 - 0.27 nm to a value of 0.31 nm. This small increase in surface roughness using IL contrasts with the much greater increase to 0.81 nm after using a standard PMMA resist. Second, we tested the ability of free-standing nanotubes to nucleate the growth of Al<sub>2</sub>O<sub>3</sub> during atomic layer deposition (ALD) of Al<sub>2</sub>O<sub>3</sub> on the entire sample. Pristine, defect-free nanotubes do not nucleate the growth of Al<sub>2</sub>O<sub>3</sub> whereas contaminants or SEM-induced damage sites do<sup>10-12</sup>. Figure 3f-g shows an example of how free-standing, unprotected nanotubes imaged by SEM do nucleate Al<sub>2</sub>O<sub>3</sub> growth, while those imaged through ice do not. Thus, IL can produce devices that remain free of processing residues and e-beam induced defects.

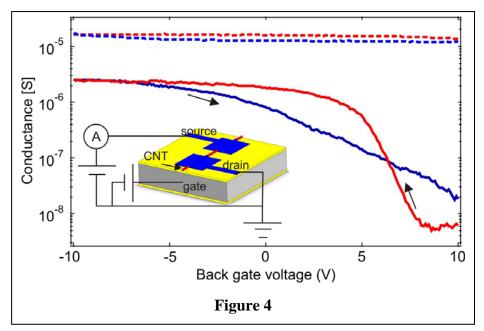

Electrical measurements under ambient room temperature conditions showed that the SWCNTs contacted by IL contained both semiconducting and metallic tubes at a ratio of 2:1, as commonly observed for CVD grown tubes. Examples of the electrical responses of a metallic and a semi-conducting SWCNT FET produced on Si<sub>3</sub>N<sub>4</sub> are shown in Figure 4. While sweeping the back-gate bias from -10 V to 10 V, the semiconducting tube switches to its ON state at a negative gate bias, indicating

hole conduction<sup>13</sup>, while the metallic tube did not show a significant back gate The hysteresis response. commonly observed in conditions ambient for conventionally made SWCNT FETs<sup>14</sup> is noted.

Because it is known that

metal films deposited onto cold surfaces tend to be nanoporous<sup>15</sup>, we were concerned that the metal contacts and leads formed on cold device structures by IL would not be of the highest electrical quality. We compared IL fabricated devices with more conventionally fabricated nanotube devices on SiO<sub>2</sub> coated Si. Each 10-nm-thick source and drain Pd electrode covered a 0.8 µm long segment of the

SWCNT, with 2  $\mu$ m between the two electrodes. The IL-made SWCNT FET source drain resistances (R<sub>sd</sub>) ranged between 0.33 and 16 M $\Omega$ , significantly higher than the R<sub>sd</sub> of ~50 k $\Omega$  for metallic FETs we fabricated using conventional e-beam lithography with PMMA resist (results not shown). But straightforward annealing of IL samples in an Ar atmosphere at temperatures ranging from 300 °C to 600 °C reduced the IL FET R<sub>sd</sub> by more than 10 fold and yielded contacts whose R<sub>sd</sub>'s were comparable to those obtained using standard resist based e-beam lithography: metallic FET devices with R<sub>sd</sub> between 60 and 90 k $\Omega$ , and semiconducting tubes with R<sub>sd</sub> down to 100 k $\Omega$ . We attribute the improved contacts to high temperature densification of the cold deposited Pd contacts.

Our results demonstrate a new approach to nano-device fabrication that solves several problems often faced in designing and producing devices. We foresee that IL could also be used to pattern high purity metal onto three dimensional structures. Automation and scaling up are also feasible. We anticipate that IL can be incorporated into more complex cluster tool environments for making graphene nano-ribbons and nanopore devices<sup>16</sup>.

ACKNOWLEDGMENT The authors thank Slaven Garaj and Chris Russo for valuable discussions, and John Chervinsky for engineering the SEM modifications required for the IL instrument. Anpan Han was supported by a post-doctoral fellowship from the Carlsberg Foundation, Denmark. Research was also supported by Grant # 5R014G003703 from the National Human Genome Research Institute, National Institutes of Health, to J. A. Golovchenko and D. Branton.

**Supporting Information Available**: Detailed description of sample preparation and IL process. This material is available free of charge via the Internet at <a href="http://pubs.acs.org">http://pubs.acs.org</a>.

#### FIGURE CAPTIONS

FIGURE 1. IL process. (a) The sample with pre-formed Mo micro-leads and SWCNT on the  $SiO_2$  coated Si substrate is loaded into the SEM via the load-lock and cooled down to ~110 K on the SEM cryo-stage. Water vapor is leaked into the SEM through a nozzle just above the sample and condenses

as amorphous ice on the cold sample. Typically, 80 nm of ice is deposited in 30 s. The location of a SWCNT under the ice is mapped. (b) An intense e-beam draws patterns for the contacts (white dotted line) and removes ice, forming a mask for metal electrodes contacting the SWCNT. (c) The sample with nano-patterned ice resist is transferred onto the metal deposition chamber and Pd is sputtered over the entire sample. The sample is removed from the metal deposition chamber and, while still frozen, immediately immersed into isopropanol held at room temperature, whereupon the Pd film on top of the ice resist drifts away, leaving the pre-formed Mo leads connected to the SWCNT with Pd interconnections only where the ice had been removed by the e-beam.

FIGURE 2. Imaging CVD SWCNT through ice on 300 nm thick SiO<sub>2</sub> coated Si substrates. (a) Tapping mode AFM image of nanotubes grown from a catalyst pad on a grounded lead. (b) SEM image of same area as in (a) with sample at ~110K before ice deposition (primary beam energy 2 keV; probe current 17 pA). (c) As in (b), but SEM imaged after deposition of a 25 nm ice layer. (Primary beam energy 1.35 keV; probe current 20 pA.)

FIGURE 3. **Detecting contaminants and e-beam damage.** Tapping mode AFM images of SWCNT contacted by four 200-nm-wide Pd electrodes using (a) IL or (b) standard lithography using PMMA resist. (c-e) High magnification AFM of (c) clean chips before the contacting process (RMSSR=0.25-0.27 nm), (d) after IL (RMSSR=0.31 nm), and (e) after PMMA lithography (RMSSR=0.81 nm). All samples on identical Si<sub>3</sub>N<sub>4</sub> surfaces. (f) Transmission electron microscopy image of a typical CVD SWCNT suspended across 750-nm-wide slits in a Si<sub>3</sub>N<sub>4</sub> membrane that was SEM imaged at room temperature prior to ALD of 11 nm of Al<sub>2</sub>O<sub>3</sub>. (g) Image of a representative SWCNT after ALD, under identical conditions as in (f) except that it was protected with a 120 nm layer of ice prior to SEM imaging.

FIGURE 4. Conductance measurement in ambient conditions of two SWCNT FETs made by IL. Si substrates coated with 500 nm of  $SiO_2$  and 60 nm of  $Si_3N_4$ . Lower left corner illustrates the measurement set-up. Keeping the source-drain voltage over the SWCNT constant at 10 mV, the gate voltage was swept at 5 V/min from -10 to 10 V (blue) and back from 10 to -10 V (red). Arrows indicate sweep direction. Dotted lines show a 60 kΩ metallic tube after annealing at 300°C. The solid lines show a semiconducting tube after annealing at 600 °C. The ON resistance is 380 kΩ.

## REFERENCES

- 1. King, G. M.; Schurmann, G.; Branton, D.; Golovchenko, J. A. Nano Letters 2005, 5, 1157.

- 2. Han, A.; Chervinsky, J.; Golovchenko, J. A.; Branton, D. *Review of Scientific Instruments* **2010**, In Preparation.

- 3. Soh, H. T.; Quate, C. F.; Morpurgo, A. F.; Marcus, C. M.; Kong, J.; Dai, H. J. *App. Phys. Lett.* **1999**, 75, 627.

- 4. Kong, J.; Soh, H. T.; Cassell, A. M.; Quate, C. F.; Dai, H. *Nature* **1998**, *395*, 878.

- 5. Suzuki, S.; Kanzaki, K.; Homma, Y.; Fukuba, S. Jpn. J. Appl. Phys. 2004, 43, L1118.

- 6. Vijayaraghavan, A.; Blatt, S.; Marquardt, C.; Dehm, S.; Wahi, R.; Hennrich, F.; Krupke, R. *Nano. Res.* **2008**, *1*, 321.

- 7. Brintlinger, T.; Chen, Y. F.; Durkop, T.; Cobas, E.; Fuhrer, M. S.; Barry, J. D.; Melngailis, J. App. Phys. Lett. 2002, 81, 2454.

- 8. Homma, Y.; Suzuki, S.; Kobayashi, Y.; Nagase, M.; Takagi, D. App. Phys. Lett. 2004, 84, 1750.

- 9. Zhang, R. Y.; Wei, Y.; Nagahara, L. A.; Amlani, I.; Tsui, R. K. Nanotechnology 2006, 17, 272.

- Farmer, D. B. Atomic Layer Deposition on Single-Walled Carbon Nanotubes via Electron Irradiation (Chapter 6 of PhD thesis, "Applications of Atomic Layer Deposition in Nanoelectronic Systems"). Harvard University, 2007.

- 11. Farmer, D. B.; Gordon, R. G. Electrochemical and Solid-State Letters 2005, 8, G89.

- 12. Farmer, D. B.; Gordon, R. G. Nano Lett. 2006, 6, 699.

- 13. Jorio, A.; Dresselhaus, M.; Dresselhaus, G., Carbon Nanotubes. Springer: 2008.

- 14. Kim, W.; Javey, A.; Vermesh, O.; Wang, O.; Li, Y. M.; Dai, H. J. Nano Lett. 2003, 3, 193.

- 15. Kim, J.; Dohna'lek, Z.; Kay, B. D. Surface Science 2005, 586, 137.

- Garaj, S.; Hubbard, W.; Reina, A.; Kong, J.; Branton, D.; Golovchenko, J. A. *Nature* **2010**, *467*, 190.

SUPPORTING INFORMATION

Ice Lithography for Nano-Devices

Han et al.

**Sample Preparation**

Samples with pre-patterned molybdenum electrode pads and CVD grown SWCNT were fabricated essentially as described<sup>1, 2</sup>. Iron catalyst pads for SWCNT growth were patterned by standard e-beam lithography and lift-off to overlap preformed Mo pads that could be held at ground potential. The SWCNT samples used for the experiments in Figure 3 were prepared by growing SWCNTs across focused ion beam-milled slits in free-standing 200-nm-thick  $Si_3N_4$  membranes spanning KOH-etched trenches in n-doped Si wafers (1-10  $\Omega$ cm<sup>-1</sup>). This created ideal conditions for imaging the SWCNTs by transmission electron microscopy. The iron catalyst pads for SWCNT growth were patterned to lie near the focused ion beam-milled slits such that the SWCNT would grow across the slits.

ALD of  $Al_2O_3$  was carried out in an in-house designed system using 100 cycles to grow ~11nm-thick  $Al_2O_3$  with trimethyl aluminum and water as reagents. The reactor temperature was set at 240 °C, and purge pressure was set to 100 mTorr.

Sample annealing was carried out in a tube furnace in Ar gas. For experiments that required annealing temperatures above 300°C, Si<sub>3</sub>N<sub>4</sub> rather than SiO<sub>2</sub> coated Si substrate chips were always used and the contacts were made by depositing a 1-nm-thick Cr adhesion layer before the Pd. The rationale for these steps is that Pd diffuses into SiO<sub>2</sub> coatings<sup>3</sup> at temperatures above 300°C and causes short circuits between the silicon back-gate and source drain electrodes. A Si<sub>3</sub>N<sub>4</sub> substrate inhibits such diffusion. Furthermore, Pd de-wets and forms islands when annealed above 300 °C. The 1-nm-thick Cr layer improves Pd adhesion and inhibits such island formation and the associated metal contact discontinuities.

1

#### **IL** process

The sample was loaded into SEM via a door on the metal deposition chamber that served as a load lock which could be isolated from our modified JEOL JSM-7001F SEM main chamber with a butterfly valve. Design and mechanical details of our modifications will be reported elsewhere<sup>4</sup>. After evacuating the metal deposition chamber, the sample was moved onto the SEM's cryo-stage and cooled down to ~110 K. Base pressure in the SEM was typically < 0.8 x 10<sup>-4</sup> Pa. A large cold finger held at ~80 K maintained the partial pressure of water to < 3 x 10<sup>-6</sup> Pa as measured by a residual gas analyzer. Sample loading, cooling and stage thermal stabilization required about one hour. Water vapor from a hydrated salt (MgSO<sub>4</sub>·7H<sub>2</sub>O) was leaked into the SEM through a nozzle just above the sample and condensed as amorphous ice on the cold sample. Ice thickness was determined by patterning wells into the ice and measuring their height projection by tilting the sample. Typically, 80 nm of ice was deposited in 30 s. The ice deposited even around free-standing SWCNTs.

After ten minutes of beam conditioning the SWCNTs positions were mapped through the ice using a 20 pA beam at 2-4 kV. This exposed the ice to about 10<sup>-4</sup> C/cm<sup>2</sup>. An intense 15 kV or 30 kV, 1 – 2 nA e-beam was then used to remove the ice in a pattern that formed a mask for metal electrodes contacting the SWCNT. As in King *et al.*<sup>5</sup>, a dose test determined the required number of electrons to remove sufficient ice to expose the underlying substrate, typically 1 C/cm<sup>2</sup> at 15 kV. Dose testing, computer assisted design of electrodes, alignment, and ice mask patterning required about one hour. The sample with nano-patterned ice resist was then transferred onto the metal deposition chamber cryostage that was held at 165 K, where ~5 nm of ice was allowed to sublime off the entire sample before metal deposition. Metals, such as a 1 nm thick Cr film, when desired, and a 10 to 20 nm thick Pd film, were sputtered over the entire sample. Before sputtering, typical base pressure in the MDC was 3 x 10<sup>-6</sup> Pa. During Pd sputtering, at a rate of 1 Å/s, the Ar processing gas pressure was maintained at 0.7 Pa. The sample was removed from the metal deposition chamber while still frozen and immediately immersed into isopropanol held at room temperature, whereupon the Pd film on top of the rapidly melting ice resist drifted away, leaving pre-formed Mo pads connected to the SWCNT by the Pd only where the ice

had been removed by the e-beam. The Pd deposition and lift-off step took about one hour, resulting in a total process time of about three hours.

## References:

- 1. Soh, H. T.; Quate, C. F.; Morpurgo, A. F.; Marcus, C. M.; Kong, J.; Dai, H. J. *App. Phys. Lett.* **1999,** 75, 627.

- 2. Kong, J.; Soh, H. T.; Cassell, A. M.; Quate, C. F.; Dai, H. *Nature* **1998,** *395*, 878.

- 3. Schleich, B.; Schmeisser, D.; Gopel, W. Surface Science 1987, 191, 367.

- 4. Han, A.; Chervinsky, J.; Branton, D.; Golovchenko, J. *Review of Scientific Instruments* **2010,** *in preparation*.

- 5. King, G. M.; Schurmann, G.; Branton, D.; Golovchenko, J. A. Nano Letters 2005, 5, 1157.