## **Implementation and Characterisation of Monolithic CMOS Pixel Sensors for the CLIC Vertex and Tracking Detectors**

Zur Erlangung des akademischen Grades eines

### **DOKTOR-INGENIEURS**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) genehmigte

### DISSERTATION

von

#### M.Sc. Iraklis Kremastiotis

geb. in: Cholargos, GR

Tag der mündlichen Prüfung: 27.01.2020

Hauptreferent: Prof. Dr. Ivan Peric Korreferent: Prof. Attilio Andreazza

#### Abstract

Different CMOS technologies are being considered for the vertex and tracking layers of the detector at the proposed high-energy  $e^+e^-$  Compact Linear Collider (CLIC). CMOS processes have been proven to be suitable for building high granularity, large area detector systems with low material budget and low power consumption. An effort is put on implementing detectors capable of performing precise timing measurements. Two Application-Specific Integrated Circuits (ASICs) for particle detection have been developed in the framework of this thesis, following the specifications of the CLIC vertex and tracking detectors. The process choice was based on a study of the features of each of the different available technologies and an evaluation of their suitability for each application.

The CLICpix Capacitively Coupled Pixel Detector (C3PD) is a pixelated detector chip designed to be used in capacitively coupled assemblies with the CLICpix2 readout chip, in the framework of the vertex detector at CLIC. The chip comprises a matrix of  $128 \times 128$  square pixels with 25 µm pitch. A commercial 180 nm High-Voltage (HV) CMOS process was used for the C3PD design. The charge is collected with a large deep N-well, while each pixel includes a preamplifier placed on top of the collecting electrode. The C3PD chip was produced on wafers with different values for the substrate resistivity (~ 20, 80, 200 and 1000  $\Omega$ cm) and has been extensively tested through laboratory measurements and beam tests. The design details and characterisation results of the C3PD chip will be presented.

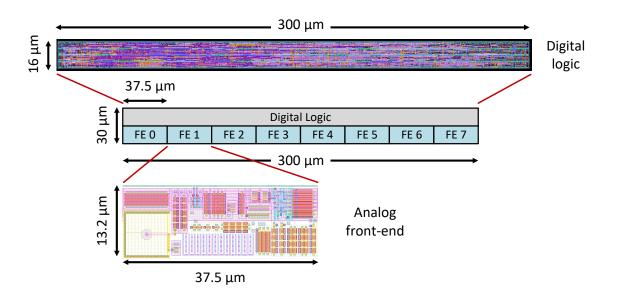

The CLIC Tracker Detector (CLICTD) is a novel monolithic detector chip developed in the context of the silicon tracker at CLIC. The CLICTD chip combines high density, mixed mode circuits on the same substrate, while it performs a fast time-tagging measurement with 10 ns time bins. The chip is produced in a 180 nm CMOS imaging process with a High-Resistivity (HR) epitaxial layer. A matrix of  $16 \times 128$  detecting cells, each measuring  $300 \times 30 \ \mu\text{m}^2$ , is included. A small N-well is used to collect the charge generated in the sensor volume, while an additional deep N-type implant is used to fully deplete the epitaxial layer. Using a process split, additional wafers are produced with a segmented deep N-type implant, a modification that has been simulated to result in a faster charge collection time. Each detecting cell is segmented into eight front-ends to ensure prompt charge collection in the sensor diodes. A simultaneous 8-bit timing and 5-bit energy measurement is performed in each detecting cell. A detailed description of the CLICTD design will be given, followed by the first measurement results.

### Zusammenfassung

Verschiedene CMOS-Technologien werden für die Vertex- und Tracking-Detektoren des Multi-TeV e<sup>+</sup>e<sup>-</sup> Compact Linear Collider (CLIC) Projekts in Betracht gezogen. CMOS-Prozesse sind hierfür besonders geeignet, da sie es ermöglichen, hochgranulare und großflächige Detektorsysteme mit geringem Materialbudget und niedrigem Stromverbrauch zu bauen. Derzeit werden Detektoren entwickelt, die darüber hinaus auch präzise Zeitmessungen ermöglichen sollen. Im Rahmen dieser Arbeit wurden zwei anwendungsspezifische integrierte Schaltungen (ASICs) zur Detektion von ionisierenden Teilchen entwickelt, die den Spezifikationen der CLIC-Vertex- und Tracking-Detektoren genügen. Die Wahl der Prozesse basiert auf einer umfassenden Studie der Eigenschaften verschiedener verfügbarer Technologien sowie einer Bewertung ihrer Eignung für die jeweilige Anwendung.

Der CLICpix Capacitively Coupled Pixel Detector (C3PD) ist ein Pixeldetektor-Chip, der für den Einsatz als Sensor in kapazitiv gekoppelten Detektoren mit dem Auslesechip CLICpix2 für den CLIC Vertexdetektor entwickelt wurde. Der C3PD-Chip verfügt über eine Matrix von  $128 \times 128$  quadratischen Pixeln mit einer Seitenlänge von  $25 \,\mu\text{m}$  und wurde in einem 180 nm High-Voltage (HV)-CMOS-Prozess implementiert. Die Ladung wird mithilfe einer großen N-dotierten Elektrode gesammelt, die den in jedem Pixel implementierten Vorverstärker umgibt. Der C3PD-Chip wurde auf Wafern mit unterschiedlichen Substratwiderständen hergestellt ( $\sim 20, 80, 200 \,\text{und} 1000 \,\Omega\text{cm}$ ) und mithilfe von Labormessungen sowie Messungen an Teststrahlen umfassend getestet. In der vorliegenden Arbeit werden Details zum Chip-Design sowie Charakterisierungsergebnisse des C3PD-Chips vorgestellt.

Der CLIC Tracker Detector (CLICTD) ist ein innovativer monolithischer Detektorchip, der für den CLIC Silizum-Trackingdetektor entwickelt wurde. Der CLICTD-Chip kombiniert analoge und digitale Schaltkreise auf dem gleichen Substrat und ermöglicht eine präzise Messung der Ankunftszeit von Teilchen mit einer Genauigkeit von unter 10 ns. Der Chip wird in einem 180 nm CMOS-Imaging-Prozess mit einer hochohmigen (HR) epitaktischen Siliziumschicht hergestellt und umfasst eine Matrix aus  $16 \times 128$  Detektorzellen mit einer Größe von jeweils  $300 \times 30 \ \mu\text{m}^2$ . Eine kleine N-dotierte Elektrode wird verwendet, um die erzeugten Ladungsträger zu sammeln, während ein zusätzliches, tiefes N-Implantat eine vollständige Ladungsträgerverarmung der epitaktischen Schicht ermöglicht. Durch einen sogenannten Prozess-Split werden zusätzliche Wafer mit einem segmentierten tiefen N-Implantat hergestellt, für das Simulationen eine Beschleunigung der Ladungssammlung vorhersagen. Jedes der Pixel ist in acht Sensor-Segmente unterteilt, um eine schnelle Ladungssammlung in den einzelnen Zellen zu gewährleisten. Der Chip ermöglicht eine simultane 8-Bit-Zeit- und 5-Bit-Energiemessung in jeder Detektorzelle. Die vorliegende Arbeit enthält eine detaillierte Beschreibung des CLICTD-Designs sowie erster Messergebnisse.

### Acknowledgements

At this point I would like to thank and acknowledge everyone who contributed to this work. Completing this PhD thesis would not have been possible without their assistance and collaboration.

First, I would like to thank my supervisor at CERN, Rafael Ballabriga, for his overall help, support and collaboration while I was working on my thesis. I would also like to thank him for the design of the C3PD analog front-end and the CLICTD analog front-end and analog periphery.

I would also like to thank my supervisor at KIT, Ivan Peric, for accepting me as a PhD student under his supervision, for his guidance during these years, and for sharing the CCPDv3 design, which was the starting point for the design of the C3PD chip.

I would like to express my gratitude to Lucie Linssen, Michael Campbell and Dominik Dannheim for their trust and support during the years that I was working on my thesis.

Special thanks to all my colleagues at CERN who contributed to this work. Xavi Llopart for always being available to help and answer my questions on the digital design, timing analysis and chip integration. Szymon Kulis for his overall help with the C3PD chip design and characterisation. Andreas Nurnberg, Simon Spannagel and Tomas Vanat for their help with the DAQ systems. Matthew Buckland and Daniel Hynds for their input on the C3PD design. Adrian Fiergolski for verifying the digital logic of the C3PD chip. Walter Snoeys, Thanushan Kugathasan and Magdalena Munker for their valuable input on the CLICTD chip design. Nuria Egidos for verifying the CLICTD chip. Jerome Alozy for his advice on my PCB designs. Katharina Dort for her contribution to the CLICTD characterisation.

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 654168.

I first came to CERN in 2014 as a Technical Student. Thanks to Sandro Bonacini and Kostas Kloukinas for giving me the chance to join the CERN microelectronics section.

I would also like to thank Grigorios Kalyvas and the dearly departed Kostas Efstathiou for supervising my diploma thesis during my studies in the University of Patras.

Finally, I would like to thank my family for their support over these years, the friends I made during my stay in the area of Geneva, and my friends from Keratsini and Patra.

Ηρακλής Κρεμαστιώτης

# Contents

| st of I | Figures                                                    |                                                                                                                                                                                             | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of ] | <b>Fables</b>                                              |                                                                                                                                                                                             | xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Intro   | oductio                                                    | n                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| The     | Compa                                                      | ct Linear Collider                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1     | The sta                                                    | ages of the CLIC accelerator                                                                                                                                                                | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2     | The Cl                                                     | LIC beam structure                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3     | Overvi                                                     | iew of the CLIC detector                                                                                                                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.3.1                                                      | Vertex detector                                                                                                                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 2.3.2                                                      | Silicon tracker                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.3.3                                                      | Electromagnetic and hadronic calorimeter                                                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.3.4                                                      | Magnet system and muon detection                                                                                                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 2.3.5                                                      | Forward region                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rad     | iation d                                                   | letectors                                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1     | Worki                                                      | ng principle and operation of pixel detectors                                                                                                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.1.1                                                      | Interaction of radiation with matter                                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.1.2                                                      | The diode                                                                                                                                                                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.1.3                                                      | The sensor                                                                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

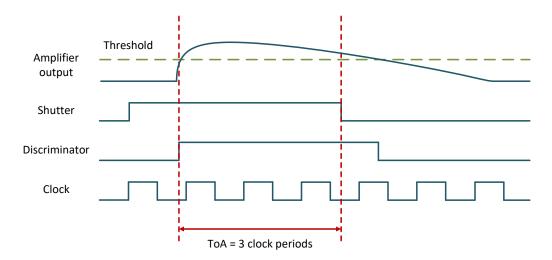

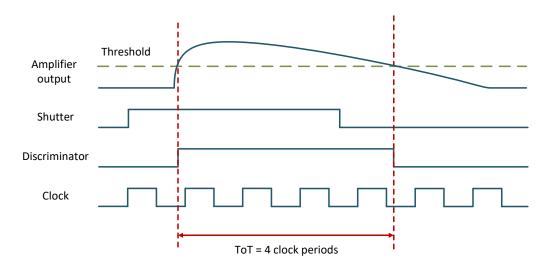

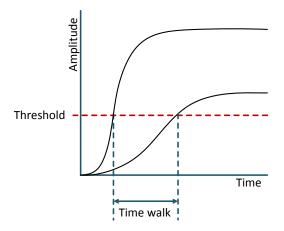

|         | 3.1.4                                                      | The processing chain                                                                                                                                                                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

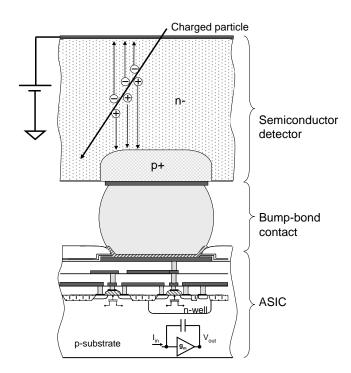

| 3.2     | Hybrid                                                     | l pixel detectors                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.2.1                                                      | Developments in hybrid pixel detectors                                                                                                                                                      | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.2.2                                                      | Bump-bonding                                                                                                                                                                                | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

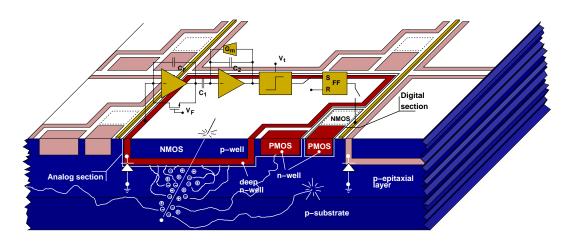

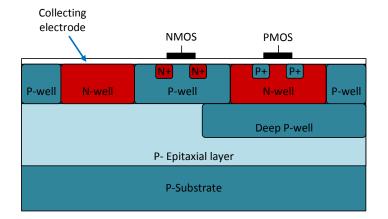

| 3.3     | Monol                                                      | ithic pixel sensors                                                                                                                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.3.1                                                      | Developments in monolithic pixel sensors                                                                                                                                                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

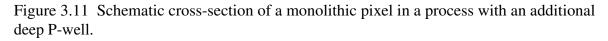

|         | 3.3.2                                                      | High-Voltage monolithic pixel sensors                                                                                                                                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | 3.3.3                                                      | Capacitively coupled HV-CMOS sensors                                                                                                                                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | st of 7<br>Intro<br>The<br>2.1<br>2.2<br>2.3<br>Rad<br>3.1 | The Compa2.1The sta2.2The Cl2.3Overvi2.3.1 $2.3.2$ 2.3.3 $2.3.4$ 2.3.5 $2.3.4$ Radiation d3.1Workin3.1.1 $3.1.2$ $3.1.3$ $3.1.4$ 3.2Hybrid $3.2.1$ $3.2.2$ 3.3Monol $3.3.1$ $3.3.1$ $3.3.2$ | st of Tables         Introduction         The Compact Linear Collider         2.1 The stages of the CLIC accelerator         2.2 The CLIC beam structure         2.3 Overview of the CLIC detector         2.3.1 Vertex detector         2.3.2 Silicon tracker         2.3.3 Electromagnetic and hadronic calorimeter         2.3.4 Magnet system and muon detection         2.3.5 Forward region         Radiation detectors         3.1 Working principle and operation of pixel detectors         3.1.1 Interaction of radiation with matter         3.1.2 The diode         3.1.3 The sensor         3.1.4 The processing chain         3.2 Hybrid pixel detectors         3.2.1 Developments in hybrid pixel detectors         3.2.2 Bump-bonding         3.3 Monolithic pixel sensors         3.3.1 Developments in monolithic pixel sensors         3.3.2 High-Voltage monolithic pixel sensors |

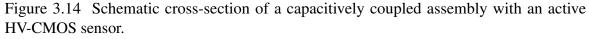

|   |      | 3.3.4    | Monolithic pixel sensors with charge collection on epitaxial layer . | 41 |

|---|------|----------|----------------------------------------------------------------------|----|

|   |      | 3.3.5    | Monolithic SOI pixel detectors                                       | 43 |

|   |      | 3.3.6    | Charged Coupled Devices                                              | 44 |

|   |      | 3.3.7    | DEPFETs                                                              | 45 |

|   |      | 3.3.8    | Trends and future perspectives                                       | 46 |

|   | 3.4  | Select   | ing the process                                                      | 46 |

| 4 | Req  | uireme   | nts for the ASICs in the CLIC vertex and tracking detector layers    | 51 |

|   | 4.1  | Requir   | rements for the CLIC vertex detector                                 | 51 |

|   | 4.2  | Requi    | rements for the CLIC silicon tracker                                 | 52 |

| 5 | Desi | gn of tl | he C3PD HV-CMOS active sensor chip                                   | 55 |

|   | 5.1  | The se   | elected process for the C3PD design                                  | 55 |

|   | 5.2  | The C    | 3PD chip design                                                      | 56 |

|   |      | 5.2.1    | The C3PD pixel                                                       | 56 |

|   |      | 5.2.2    | The C3PD periphery and interface                                     | 60 |

|   |      | 5.2.3    | Integration and verification of the C3PD chip                        | 62 |

|   | 5.3  | Submi    | ission with higher resistivity wafers                                | 65 |

|   | 5.4  | Summ     | nary                                                                 | 65 |

| 6 | Cha  | racteris | sation of the C3PD chip                                              | 67 |

|   | 6.1  | Standa   | alone characterisation                                               | 67 |

|   |      | 6.1.1    | Measurement setup                                                    | 67 |

|   |      | 6.1.2    | I-V characteristic                                                   | 68 |

|   |      | 6.1.3    | Measurements with test pulses                                        | 69 |

|   |      | 6.1.4    | Measurements with a radiation source                                 | 74 |

|   |      | 6.1.5    | Feedback and test capacitance calculation                            | 74 |

|   |      | 6.1.6    | Samples with higher substrate resistivity                            | 76 |

|   | 6.2  | Charac   | cterisation of capacitively coupled assemblies                       | 80 |

|   |      | 6.2.1    | Measurement setup                                                    | 80 |

|   |      | 6.2.2    | I-V characteristic                                                   | 81 |

|   |      | 6.2.3    | Calibration of the sensor chip with test pulses                      | 83 |

|   |      | 6.2.4    | Test pulses with the readout chip                                    | 87 |

|   |      | 6.2.5    | Coupling capacitance calculation                                     | 88 |

|   |      | 6.2.6    | Radiation sources                                                    | 89 |

|   |      | 6.2.7    | Beam tests                                                           | 90 |

|   | 6.3  | Summ     | nary                                                                 | 94 |

| 7  | The    | CLICTD chip design                                                    | 97  |

|----|--------|-----------------------------------------------------------------------|-----|

|    | 7.1    | The selected process                                                  | 97  |

|    | 7.2    | The CLICTD detector channel                                           | 100 |

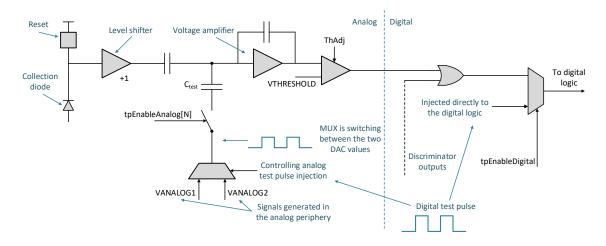

|    |        | 7.2.1 Analog front-end                                                | 100 |

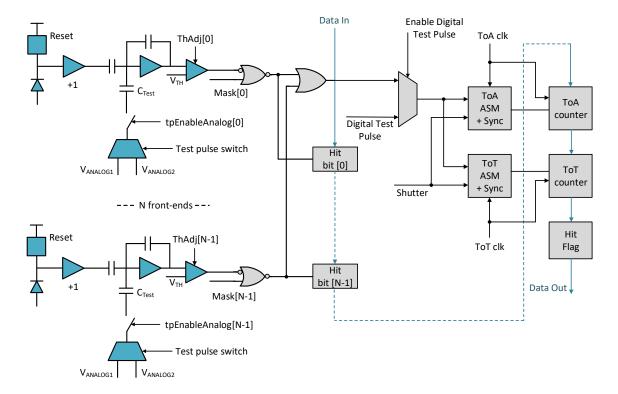

|    |        | 7.2.2 Digital logic                                                   | 101 |

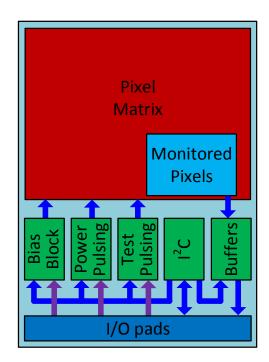

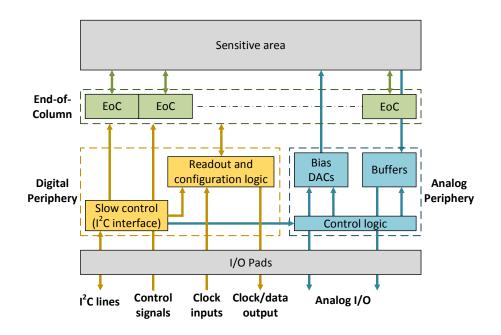

|    | 7.3    | The CLICTD periphery and chip interface                               | 107 |

|    |        | 7.3.1 The CLICTD analog periphery                                     | 107 |

|    |        | 7.3.2 The CLICTD digital periphery                                    | 108 |

|    |        | 7.3.3 Slow control                                                    | 108 |

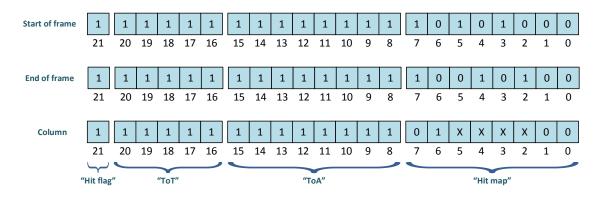

|    |        |                                                                       | 111 |

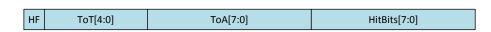

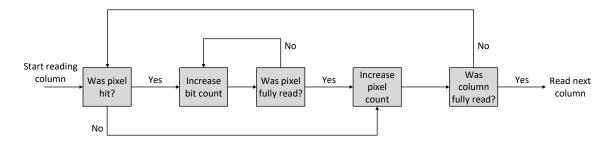

|    |        | 7.3.5 Compression algorithm                                           | 113 |

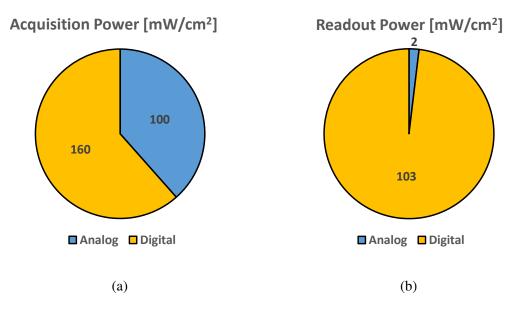

|    |        | 7.3.6 Power consumption                                               | 113 |

|    | 7.4    | Integration and verification of the CLICTD chip                       | 115 |

|    | 7.5    | Summary                                                               | 119 |

| 8  | Mea    | surements with the CLICTD chip                                        | 121 |

| U  | 8.1    | Measurement setup                                                     |     |

|    | 8.2    | -                                                                     | 123 |

|    | 8.3    | Slow control                                                          | _   |

|    | 8.4    |                                                                       | 128 |

|    | 8.5    |                                                                       | 128 |

|    | 8.6    |                                                                       | 131 |

|    | 8.7    |                                                                       | 132 |

|    | 8.8    | Summary and next steps                                                |     |

| 9  | Con    | clusions                                                              | 135 |

| _  | _      |                                                                       |     |

| Re | eferen | ces                                                                   | 139 |

| Ap | opend  | ix A PCB Designs                                                      | 147 |

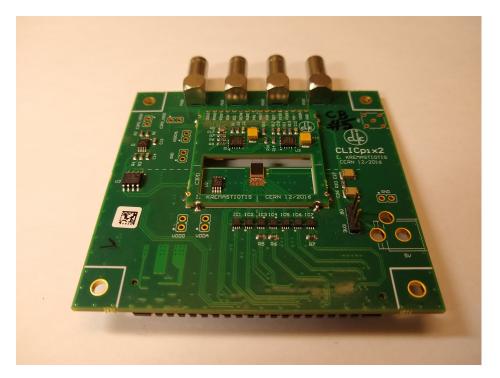

|    | A.1    | Board for testing the C3PD chip in standalone tests                   | 147 |

|    | A.2    | Board for testing the CLICpix2 and C3PD chips in capacitively coupled |     |

|    |        |                                                                       | 149 |

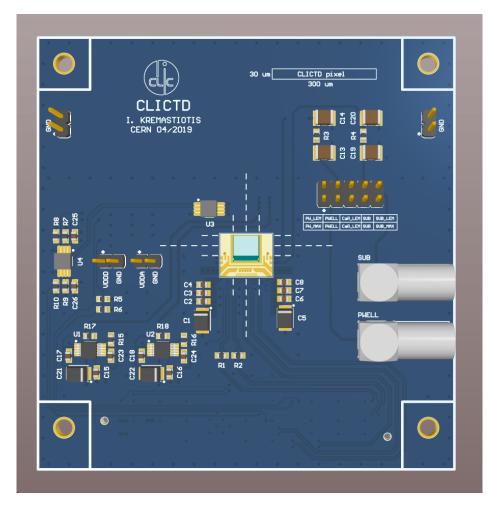

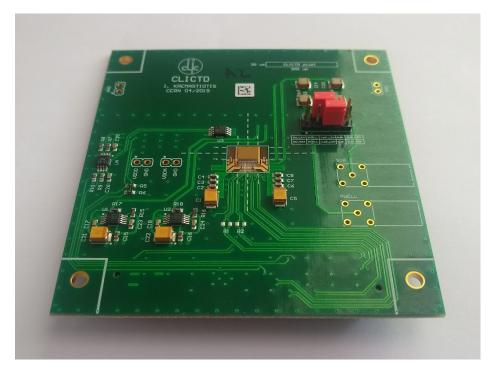

|    | A.3    | Board for testing the CLICTD chip                                     | 151 |

# **List of Figures**

| 2.1  | The CLIC accelerator footprint near CERN. The three foreseen energy stages    |    |

|------|-------------------------------------------------------------------------------|----|

|      | are presented. From [5]                                                       | 5  |

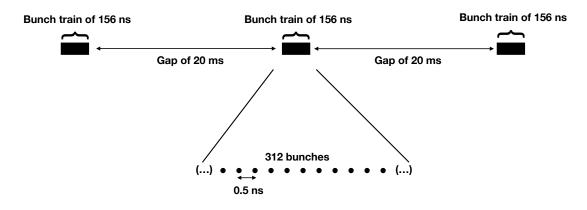

| 2.2  | The CLIC beam structure (not to scale). From [7]                              | 7  |

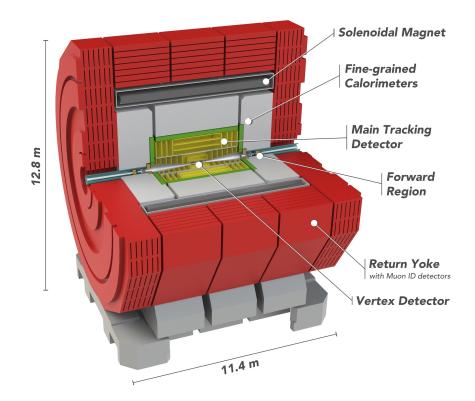

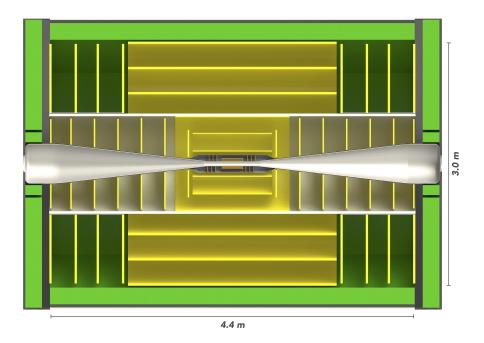

| 2.3  | The CLIC detector. From [9]                                                   | 8  |

| 2.4  | 3-D model of the CLIC vertex detector. From [9]                               | 9  |

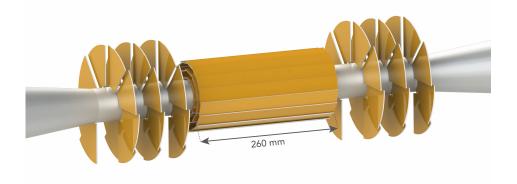

| 2.5  | 3-D model of the CLIC tracking detector. From [9]                             | 10 |

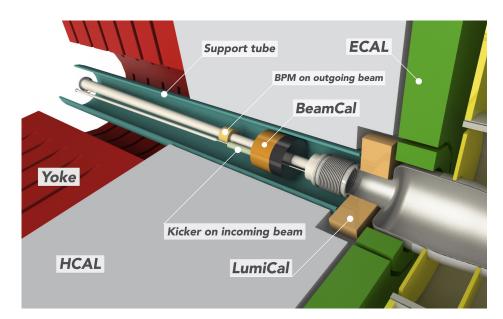

| 2.6  | A zoom in the CLIC detector forward region. From [9]                          | 13 |

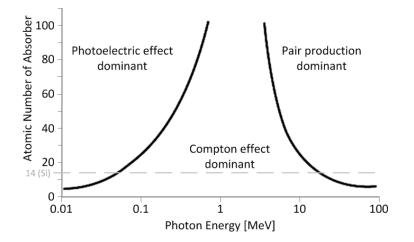

| 3.1  | Interaction of photons with matter. From [12]                                 | 16 |

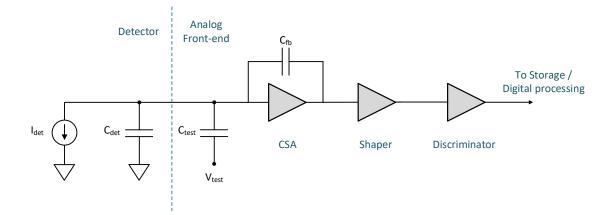

| 3.2  | Block diagram of a typical processing chain in a particle detector            | 21 |

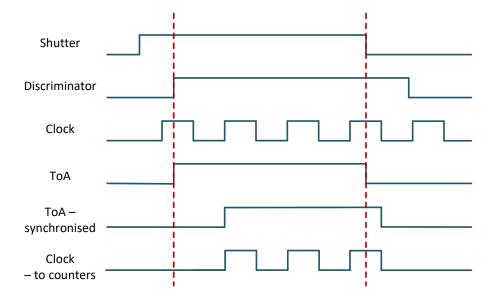

| 3.3  | Timing diagram of a ToA measurement.                                          | 23 |

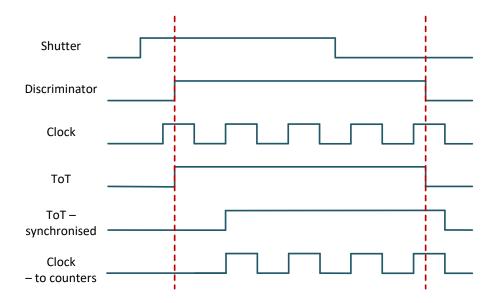

| 3.4  | Timing diagram of a ToT measurement.                                          | 24 |

| 3.5  | Time walk in a detector                                                       | 24 |

| 3.6  | Schematic cross-section of a hybrid pixel detector (not to scale). From [29]. | 26 |

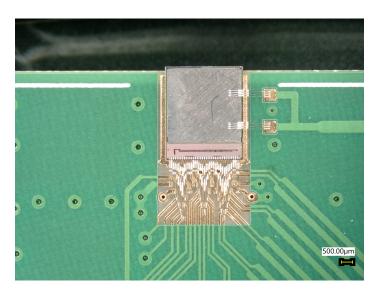

| 3.7  | Photo of a hybrid pixel detector mounted on a PCB, with a silicon sensor      |    |

|      | bump-bonded on the CLICpix2 readout chip.                                     | 27 |

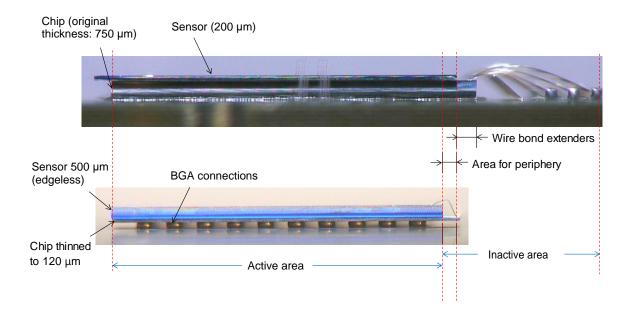

| 3.8  | The Medipix3 chip, connected to the data acquisition system using wire-       |    |

|      | bonds (top) and TSVs (bottom).                                                | 32 |

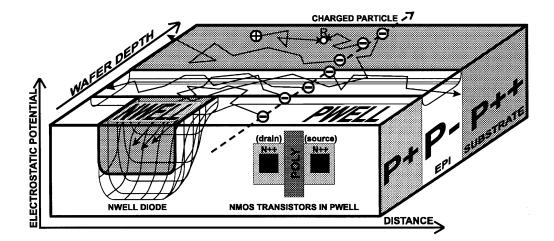

| 3.9  | Schematic cross-section of a monolithic sensor pixel with charge collection   |    |

|      | on epitaxial layer. From [61]                                                 | 34 |

| 3.10 | Schematic cross-section of a triple-well monolithic pixel. From [64]          | 36 |

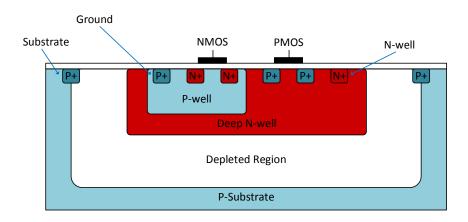

| 3.11 | Schematic cross-section of a monolithic pixel in a process with an additional |    |

|      | deep P-well                                                                   | 36 |

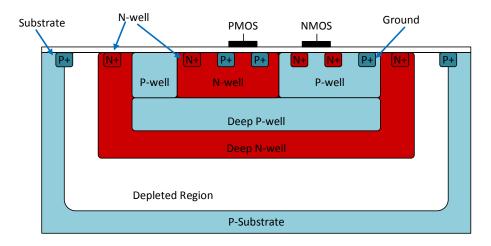

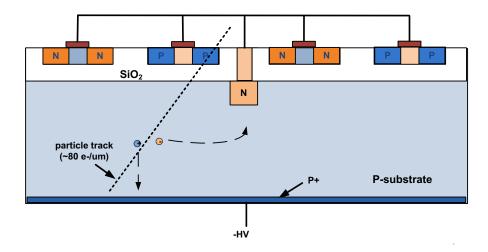

| 3.12 | Schematic cross-section of a HV-CMOS process.                                 | 37 |

| 3.13 | Schematic cross-section of a quadruple-well HV-CMOS process                   | 39 |

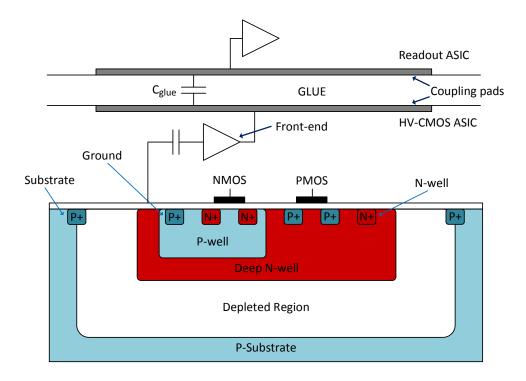

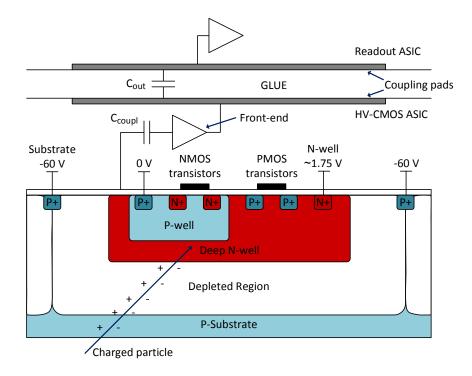

| 3.14 | Schematic cross-section of a capacitively coupled assembly with an active     |    |

|      | HV-CMOS sensor.                                                               | 41 |

| 3.15 | Schematic cross-section of a monolithic pixel in a process with an additional                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | deep P-well and charge collection on epitaxial layer. From [75]                                                                                      | 42 |

| 3.16 | Schematic cross-section of a monolithic pixel in a SOI process. From [78].                                                                           | 44 |

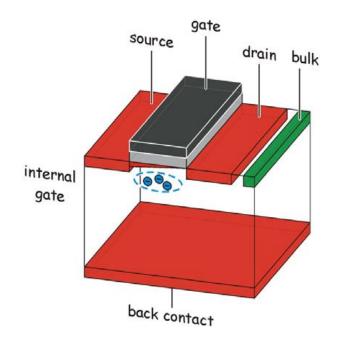

| 3.17 | Schematic cross-section of a DEPFET pixel (from [83]).                                                                                               | 45 |

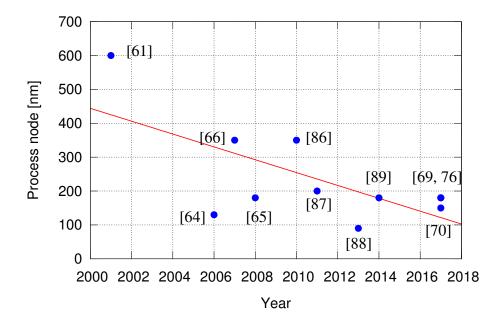

| 3.18 | Different process nodes used for designing monolithic detectors over the years.                                                                      | 47 |

| 5.1  | Schematic cross-section of a capacitively coupled assembly                                                                                           | 57 |

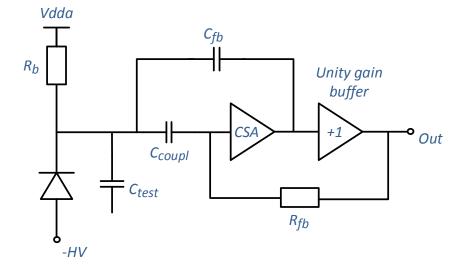

| 5.2  | C3PD pixel block diagram.                                                                                                                            | 59 |

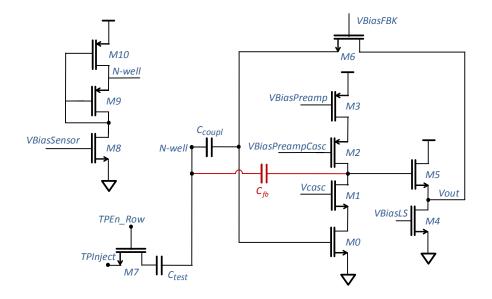

| 5.3  | C3PD pixel schematic. The parasitic feedback capacitance is shown in red colour.                                                                     | 59 |

| 5.4  | C3PD double pixel layout. The pixels are shown to the left and the right side.                                                                       |    |

|      | The biasing lines are routed between the pixels                                                                                                      | 60 |

| 5.5  | C3PD chip block diagram.                                                                                                                             | 61 |

| 5.6  | Configurations of the C3PD monitored pixel cluster. The monitored pixels in each configuration are marked in green. Pixel "7" is used for monitoring |    |

|      | the test pulse voltage amplitude.                                                                                                                    | 63 |

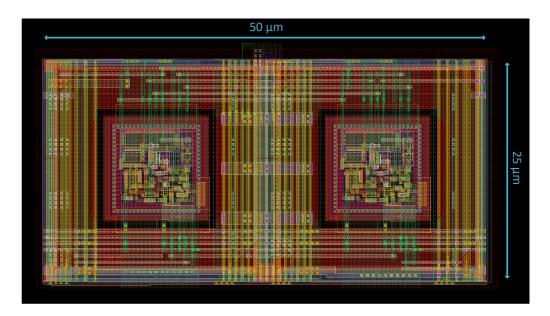

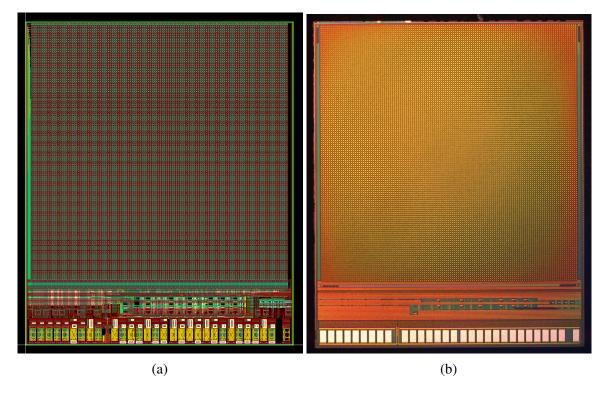

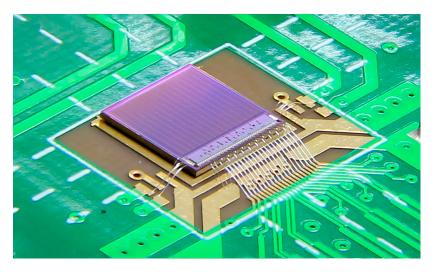

| 5.7  | (a) Layout and (b) microscope photo of the C3PD chip                                                                                                 | 64 |

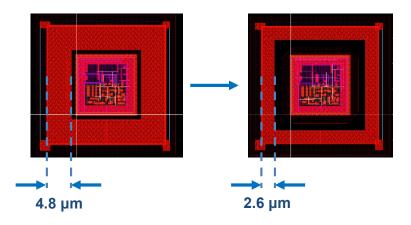

| 5.8  | Modification in the metal contact of the HV-guardring in the C3PD pixel.                                                                             | 65 |

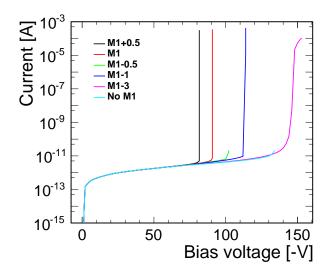

| 5.9  | Leakage current as a function of the reverse bias voltage for different width                                                                        |    |

|      | of the metal contact. M1 is the original width of $4.8 \mu\text{m}$ . From [99]                                                                      | 66 |

| 6.1  | Photo of the uASIC setup. From left to right: FPGA development board,                                                                                |    |

|      | uASIC interface board, chip-board with C3PD mounted on it                                                                                            | 68 |

| 6.2  | C3PD chip thinned down to 50 $\mu$ m, mounted and wire-bonded on the PCB.                                                                            | 69 |

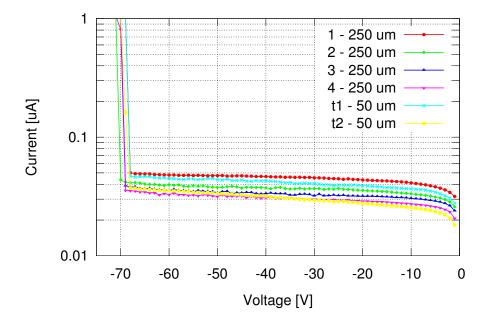

| 6.3  | I-V curves of the measured C3PD chips. Samples with standard substrate                                                                               |    |

|      | resistivity (~ 20 $\Omega$ cm)                                                                                                                       | 70 |

| 6.4  | Fit of a square root function on the measured leakage current for one of the                                                                         |    |

|      | assemblies.                                                                                                                                          | 70 |

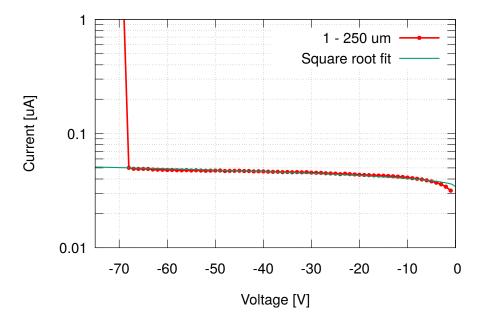

| 6.5  | (a) Signal-to-noise ratio and (b) rise time as measured for different biasing                                                                        |    |

|      | points of the preamplifier and the feedback. The chosen operating point is                                                                           |    |

|      | marked in green.                                                                                                                                     | 71 |

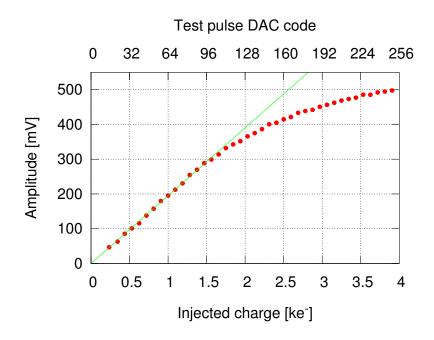

| 6.6  | Output amplitude, averaged over 64 pulses, as a function of the injected test                                                                        |    |

|      | pulse DAC code and corresponding injected charge                                                                                                     | 72 |

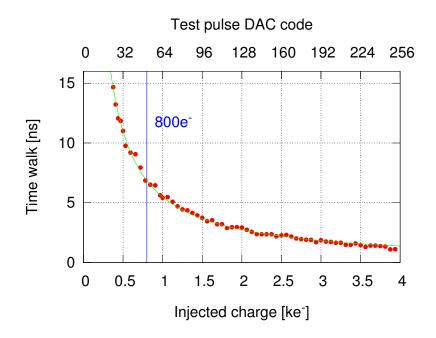

| 6.7  | Time walk, averaged over 64 pulses, as a function of the injected test pulse                                                                         |    |

|      | DAC code and corresponding injected charge                                                                                                           | 73 |

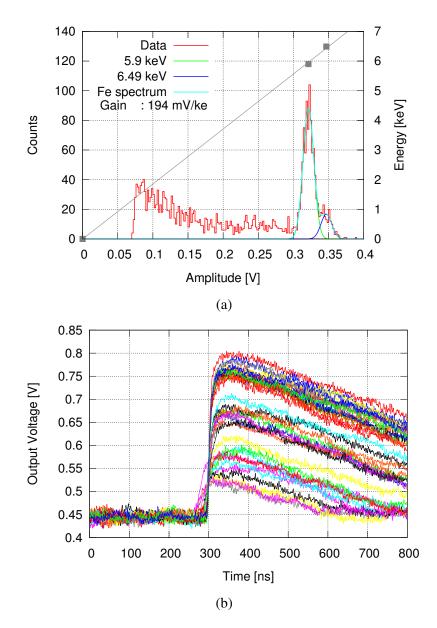

| 6.8  | (a) Resulting amplitude spectrum and double Gaussian fit for one of the                                                                              |    |

|      | monitored pixels and (b) sample pulses from a <sup>55</sup> Fe source                                                                                | 75 |

| 6.9  | High resistivity C3PD chip mounted and wire-bonded on the PCB                           | 77 |

|------|-----------------------------------------------------------------------------------------|----|

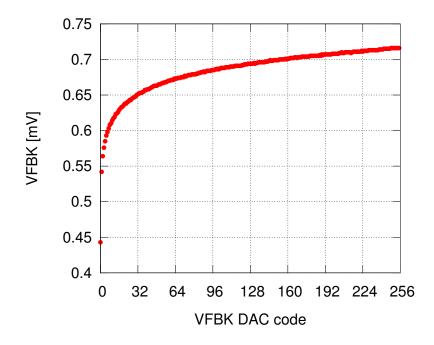

| 6.10 | Bias voltage of the feedback transistor as a function of the DAC code                   | 78 |

| 6.11 | Resulting amplitude spectrum and double Gaussian fit from a <sup>55</sup> Fe source,    |    |

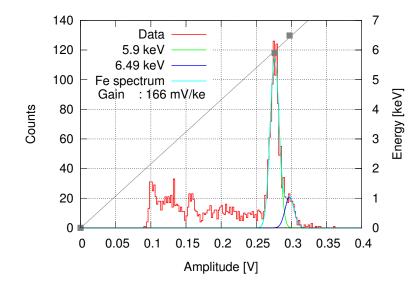

|      | for one of the monitored pixels of a high resistivity C3PD chip                         | 79 |

| 6.12 | Capacitively coupled assembly of C3PD (top) and CLICpix2 (bottom), wire                 |    |

|      | bonded on the PCB.                                                                      | 80 |

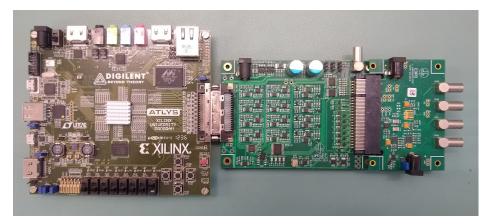

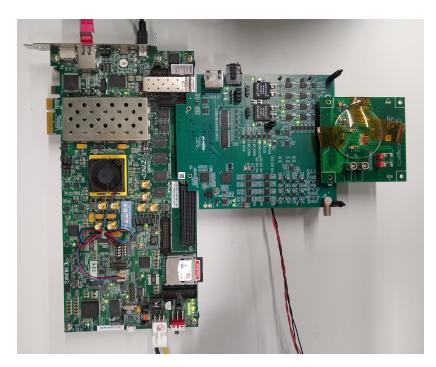

| 6.13 | Photo of the CaRIBOu readout system for testing capacitively coupled as-                |    |

|      | semblies with the CLICpix2 and C3PD chips. From left to right: evaluation               |    |

|      | kit, CaR board, chip-board with CLICpix2/C3PD assembly mounted on it.                   | 81 |

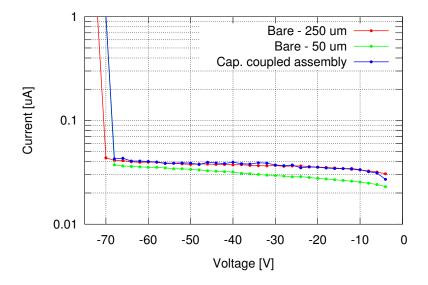

| 6.14 | I-V curve for a C3PD chip in a capacitively coupled assembly, compared to               |    |

|      | the I-V curves for two bare chips: one 250 µm thick and one thinned down                |    |

|      | to 50 μm.                                                                               | 82 |

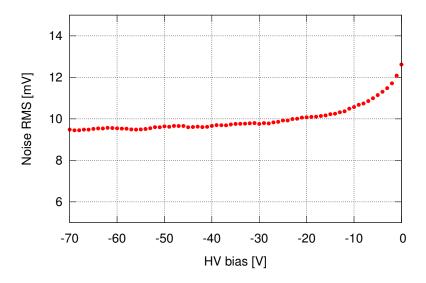

| 6.15 | Noise at the amplifier output as a function of the high voltage bias. From [74].        | 82 |

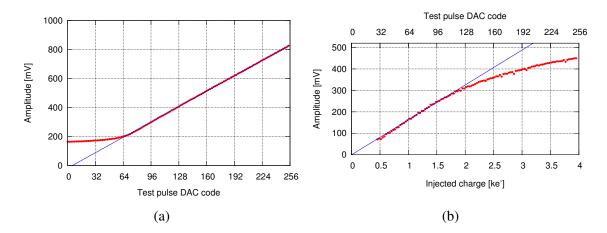

| 6.16 | (a) Injected test pulse amplitude and (b) output amplitude (averaged over 16            |    |

|      | samples) as a function of the test pulse DAC code. From [74].                           | 83 |

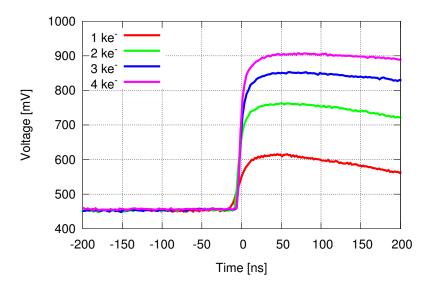

| 6.17 | Output pulses (averaged over 16 samples) for different charge injected using            |    |

|      | test pulse. From [74]                                                                   | 84 |

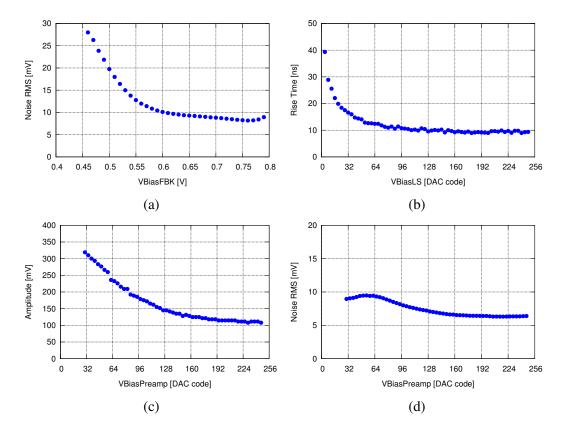

| 6.18 | (a) Noise as a function of the feedback bias, (b) rise time as a function of            |    |

|      | the unity gain buffer bias, (c) output amplitude and (d) noise as a function of         |    |

|      | the charge sensitive amplifier bias for the measured C3PD chip. From [74].              | 85 |

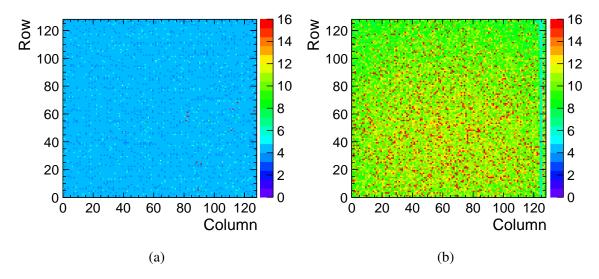

| 6.19 | Noise width measured (in threshold DAC LSBs) in the CLICpix2 chip, with                 |    |

|      | the C3PD sensor chip powered off (a) and on (b). From [106].                            | 86 |

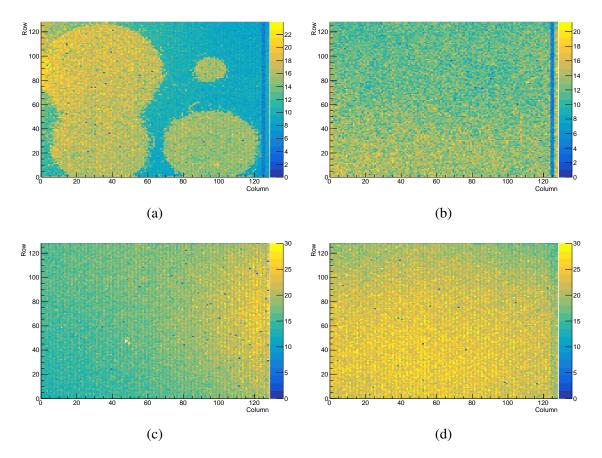

| 6.20 | Hit maps acquired with the CLICpix2 readout chip, after injecting test pulses           |    |

|      | in the C3PD front-end. Figures (a) and (b) present two capacitively coupled             |    |

|      | assemblies with 20 $\Omega$ cm C3PD sensor chips and Figures (c) and (d) present        |    |

|      | two assemblies with 1 k $\Omega$ cm C3PD chips                                          | 87 |

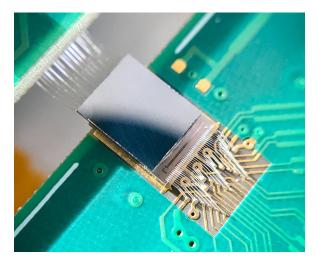

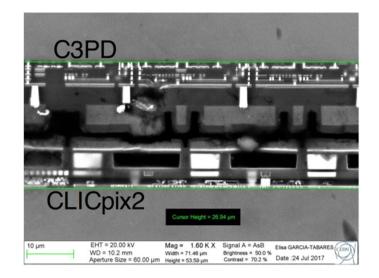

| 6.21 | Cross-section of a capacitively coupled assembly with the CLICpix2 (bottom)             |    |

|      | and C3PD (top) chips (© CERN).                                                          | 88 |

| 6.22 | Resulting amplitude spectrum from a <sup>90</sup> Sr source, for a capacitively coupled |    |

|      | assembly with (a) a 20 $\Omega$ cm and (b) a 1000 $\Omega$ cm C3PD sensor. The peaks    |    |

|      | observed for the ToT value of 30 are resulting from single cluster hits where           |    |

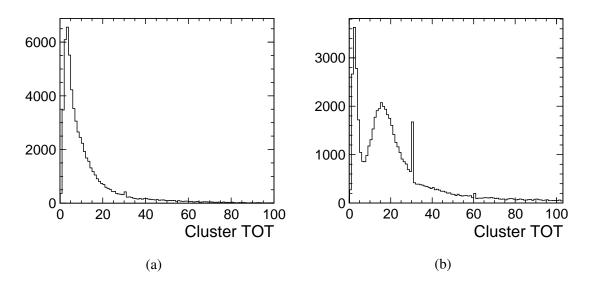

|      | the ToT counter has saturated.                                                          | 90 |

| 6.23 | Measurement setup using the CLICdp Timepix3 telescope in the CERN SPS                   |    |

|      | beamline. The DUT is shown in the middle, with four Timepix3 planes on                  |    |

|      | the left and three on the right (© CERN).                                               | 91 |

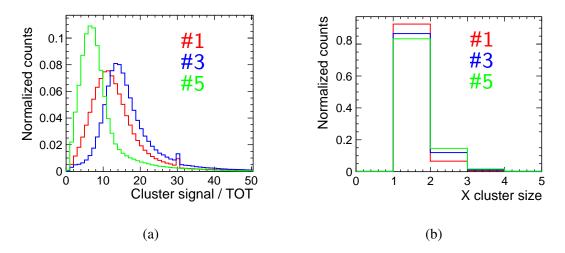

| 6.24 | (a) Cluster signal and (b) cluster size as measured in beam tests with three    |     |

|------|---------------------------------------------------------------------------------|-----|

|      | different capacitively coupled assemblies. From [91]                            | 92  |

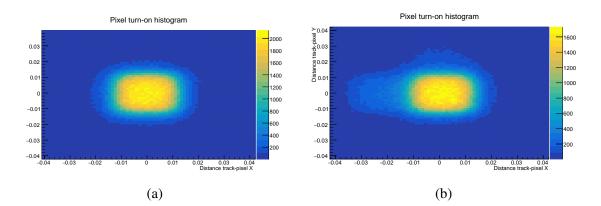

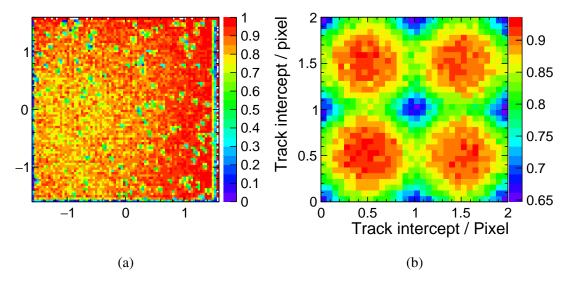

| 6.25 | A histogram for the CLICpix2 pixel response, produced by scanning the           |     |

|      | tracks over the pixel and plotting the pixel response. (a) Assembly with good   |     |

|      | flip-chip alignment and (b) slightly misaligned assembly. From [106]            | 92  |

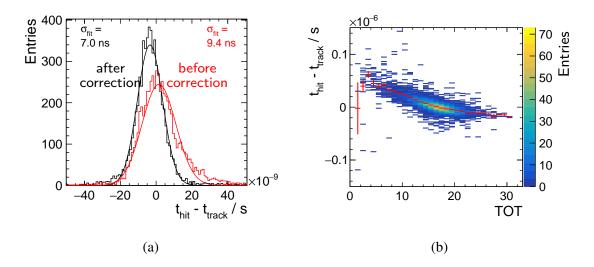

| 6.26 | (a) Time difference between the reconstructed hit and the track and (b) ToT     |     |

|      | information used to correct for the time walk effect. From [91]                 | 93  |

| 6.27 | Efficiency measurement (a) across the matrix and (b) folded into a $2 \times 2$ |     |

|      | pixel array. From [106]                                                         | 94  |

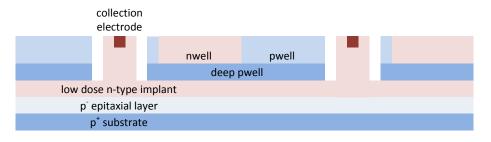

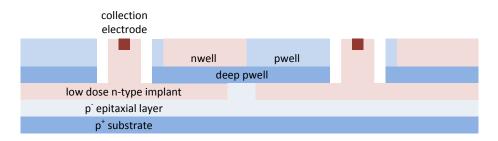

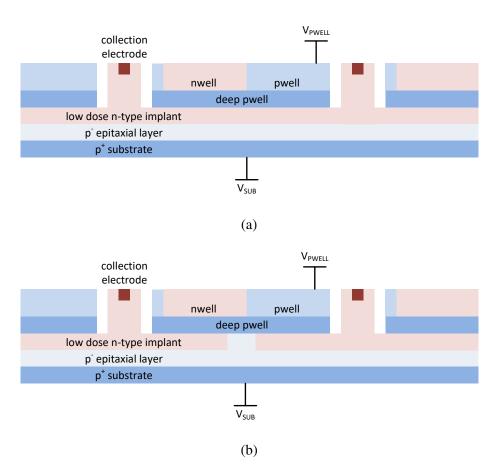

| 7.1  | Process cross-section - continuous N-implant (not to scale)                     | 98  |

| 7.2  | Process cross-section - gap in N-implant (not to scale).                        | 99  |

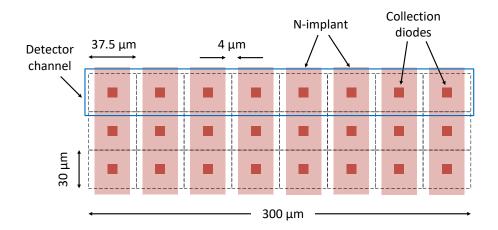

| 7.3  | Top view of the segmentation of the deep N-implant in the CLICTD pixel          |     |

| ,    | matrix (not to scale).                                                          | 99  |

| 7.4  | Layout of the CLICTD pixel, where the analog part is segmented in eight         |     |

| ,    | front-ends.                                                                     | 101 |

| 7.5  | Block diagram of the CLICTD channel.                                            | 102 |

| 7.6  | Data stored in one CLICTD pixel.                                                | 102 |

| 7.7  | Test pulse injection in the CLICTD cell.                                        | 105 |

| 7.8  | ToA measurement in the CLICTD cell.                                             | 106 |

| 7.9  | ToT measurement in the CLICTD cell.                                             | 107 |

| 7.10 | Algorithm diagram of the CLICTD End-of-Column block.                            | 108 |

| 7.11 | Block diagram of the CLICTD periphery.                                          | 110 |

|      | CLICTD headers.                                                                 | 112 |

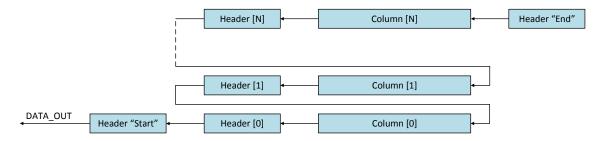

|      | CLICTD data stream.                                                             | 112 |

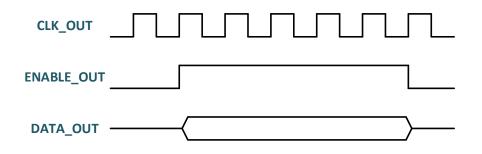

| 7.14 | Timing diagram of the CLICTD readout.                                           | 112 |

|      | Contributions of the analog and digital power consumption of the CLICTD         |     |

|      | matrix (a) during acquisition and (b) during readout (simulated values)         | 114 |

| 7.16 | Layout of the CLICTD chip                                                       | 117 |

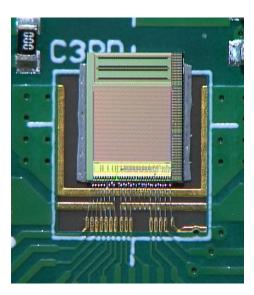

| 8.1  | Photo of the CLICTD chip, wire bonded on the PCB                                | 122 |

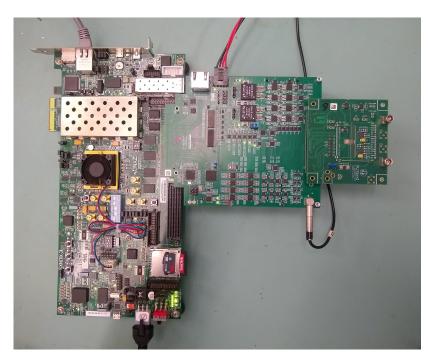

| 8.2  | Photo of the CaRIBOu readout system for testing the CLICTD chip. From           |     |

|      | left to right: evaluation kit, CaR board, chip board with a CLICTD sample       |     |

|      | mounted on it.                                                                  | 122 |

| 8.3  | The two CLICTD process splits: (a) the first CLICTD process split, with         |     |

|      | continuous N-implant, and (b) the second CLICTD process split, with gap in      |     |

|      | N-implant (not to scale).                                                       | 123 |

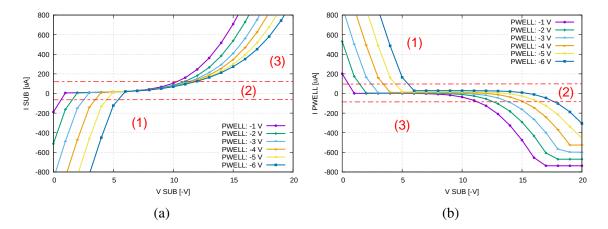

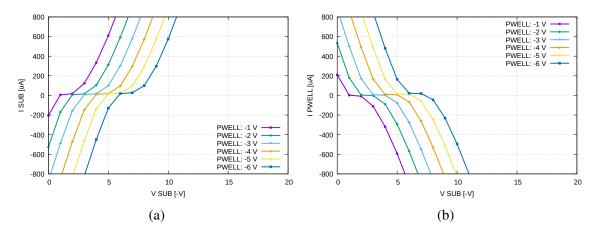

| 8.4         | Leakage current measured at (a) the substrate and (b) the P-wells in the      |     |

|-------------|-------------------------------------------------------------------------------|-----|

|             | CLICTD matrix as a function of the applied substrate bias. Each curve is      |     |

|             | measured for a different value of the P-well bias. Results shown for the      |     |

|             | CLICTD sample from the first process split - continuous N-implant             | 124 |

| 8.5         | Leakage current measured at (a) the substrate and (b) the P-wells in the      |     |

|             | CLICTD matrix as a function of the applied substrate bias. Each curve is      |     |

|             | measured for a different value of the P-well bias. Results shown for the      |     |

|             | CLICTD sample from the second process split - gap in N-implant                | 126 |

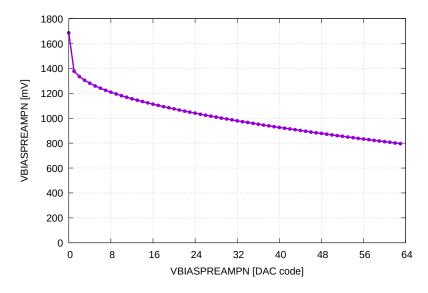

| 8.6         | Measured voltage level at the output of the preamplifier bias current DAC     | 128 |

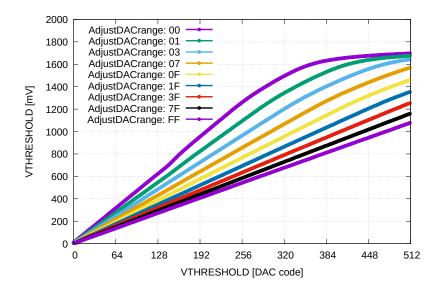

| 8.7         | Measured voltage level at the output of the threshold voltage DAC, for        |     |

|             | different values of the adjustable DAC range.                                 | 129 |

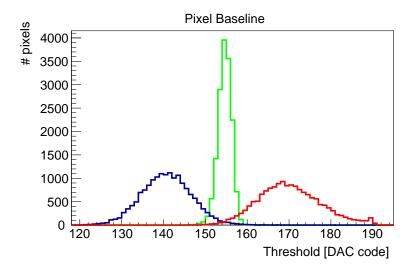

| 8.8         | CLICTD threshold scan for minimum (blue), maximum (red) and equalised         |     |

|             | (green) local threshold tuning DAC code.                                      | 130 |

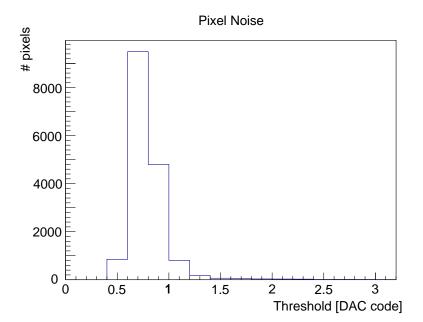

| 8.9         | Histogram of noise RMS per pixel for the CLICTD chip, measured in thresh-     |     |

|             | old DAC codes.                                                                | 130 |

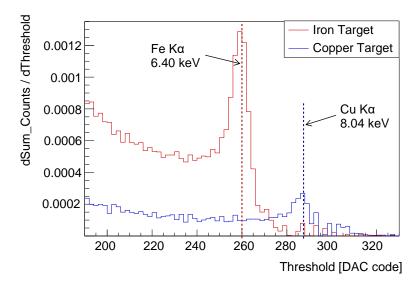

| 8.10        | Fluorescence spectra using iron (red) and copper (blue) targets, measured     |     |

|             | with the CLICTD chip.                                                         | 131 |

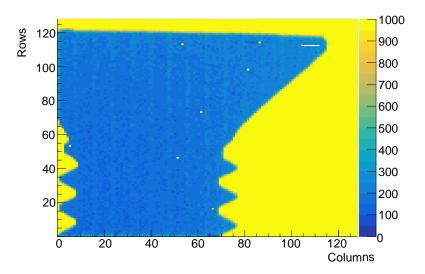

| 8.11        | X-ray image of a screw, recorded with the CLICTD chip                         | 132 |

| A.1         | Visualisation of the PCB designed for testing the C3PD chip in standalone     |     |

| <b>A.</b> 1 | mode.                                                                         | 148 |

| A.2         | Photo of the C3PD PCB.                                                        | 148 |

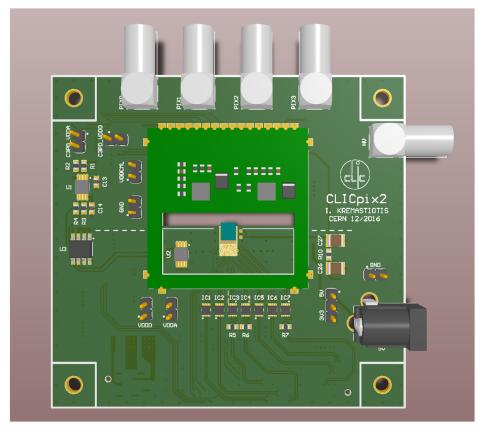

| A.2         | Visualisation of the PCB designed for testing capacitively coupled assemblies | 140 |

| 11.5        |                                                                               | 149 |

| A.4         | Photo of the CLICpix2/C3PD PCB.                                               |     |

| A.5         | Visualisation of the PCB designed for testing the CLICTD chip.                |     |

|             |                                                                               | 151 |

| 11.0        |                                                                               | 104 |

# **List of Tables**

| 2.1 | Main parameters of the three energy stages for CLIC. From [6].                        | 6   |

|-----|---------------------------------------------------------------------------------------|-----|

| 2.2 | Cell sizes in the CLIC tracker. From [10]                                             | 11  |

| 3.1 | Overview of monolithic detector ASICs, representative of the available                |     |

|     | technologies.                                                                         | 47  |

| 3.2 | Design parameters of monolithic detector ASICs                                        | 48  |

| 4.1 | Requirements for the CLIC vertex detector.                                            | 52  |

| 4.2 | Requirements for a chip for the CLIC silicon tracker.                                 | 54  |

| 5.1 | Requirements for the C3PD prototype                                                   | 58  |

| 5.2 | List of DACs in the C3PD analog periphery                                             | 62  |

| 5.3 | List of I/O pins in the C3PD prototype                                                | 64  |

| 6.1 | Pixel characteristics for monitored pixels, averaged over 6 assemblies, mea-          |     |

|     | sured with test pulses of 1.63 ke <sup>-</sup> charge. The simulated values are shown |     |

|     | in the rightmost column.                                                              | 74  |

| 6.2 | Pixel characteristics for the measured higher resistivity C3PD chip, compared         |     |

|     | to the standard resistivity samples.                                                  | 78  |

| 6.3 | Pixel characteristics, averaged for all monitored pixels of the measured              |     |

|     | assembly, measured with test pulses of 1.63 ke <sup>-</sup> (charge equivalent to the |     |

|     | most probable energy of the photons from an $^{55}$ Fe source)                        | 86  |

| 6.4 | Glue capacitance for different CLICpix2 and C3PD assemblies, extracted                |     |

|     | from ToT measurements in the CLICpix2 readout chip                                    | 89  |

| 7.1 | ToT clock frequency.                                                                  | 103 |

| 7.2 | Measurement modes of the CLICTD pixel.                                                | 104 |

| 7.3 | List of DACs in the CLICTD analog periphery                                           | 109 |

| 7.4 | Readout time without and with compression                                             | 113 |

| 7.5 | Simulation corners for the CLICTD verification.                                       | 116 |

| 7.6 | List of I/O pins in the CLICTD prototype           | 118 |

|-----|----------------------------------------------------|-----|

| 7.7 | Main parameters of the CLICTD design.              | 119 |

| 8.1 | Reset values of the CLICTD slow control registers. | 127 |

| 9.1 | Summary of the C3PD prototype                      | 136 |

| 9.2 | Summary of the CLICTD prototype                    | 137 |

## Chapter 1

## Introduction

A question that has intrigued the humanity and was the subject of philosophical quests since the ancient times is the understanding of the elements which compose the matter. The ancient Greek philosopher Democritus believed that the matter is composed of discrete, indestructible, invisible to the human eye elements, the "atoms". It took several centuries for this idea to move from the theoretical wording to the field of natural sciences. The Standard Model of particle physics is the current description of the subatomic particles and their interactions. It has been a subject of study for decades, with the Higgs boson (discovered at the CERN LHC in 2012) being the last piece of this model.

One of the instruments that are being used during the past decades in High Energy Physics (HEP) experiments in search of new particles is the particle accelerator. In such a machine, beams of particles are accelerated to very high speeds and energies. The particle beams are then collided and the products of each collision are studied and analysed to potentially discover new particles. Based on the nature of the particles that are collided, the particle accelerators can be divided in two categories: the lepton colliders and the hadron colliders.

In a lepton (or electron-positron -  $e^+e^-$ ) collider, electrons are collided with positrons (the antimatter complement of the electron). Lepton colliders are suitable for highly precise measurements, thanks to the fact that fundamental particles are collided. They are therefore appropriate for measuring the properties of a particle, such as the Higgs boson, with very good precision. On the other hand, one limitation in lepton colliders is that when an electron is accelerated in a circle, it emits electromagnetic radiation (known as the synchrotron radiation) and is gradually losing its energy. Thus, it is challenging to achieve very high collision energies in a lepton collider. As an example, the Large Electron-Positron (LEP) collider, a circular collider with 27 km circumference, operated at CERN between the years 1989 and 2000, reached a maximum energy of 209 GeV. LEP allowed for precise measurements of the

W and Z bosons (first discovered in the CERN Super Proton Synchrotron - SPS) and helped in understanding the nature of the weak nuclear force.

In a hadron collider, the particle beams consist of hadrons, which are particles composed by quarks. The Large Hadron Collider (LHC) [1] at CERN is the world's largest and most powerful particle accelerator, with a collision energy up to 13 TeV, and the biggest scientific instrument built up to this day. The LHC, which includes four large detector experiments, started its operation in 2008 and is responsible for the discovery of the Higgs boson, which was first described in 1964. The LHC operation is foreseen to continue until the year 2035, with several upgrades through the years. In the LHC, and generally in hadron colliders, the particle beams consist primarily by protons. Heavy ions, such as lead particles, are also collided in hadron accelerators. Protons, and hadrons in general, are not elementary particles as they are composed by quarks. They are a lot heavier compared to the electrons (or positrons) and they emit lower synchrotron radiation. Consequently, higher collision energies can be reached in hadron colliders, which can potentially lead to the production of more massive particles. On the other hand, since hadrons are not fundamental particles, they result in a higher background which imposes further challenges in the data analysis. Another limitation is the fact that strong, and costly, magnets are needed in order to bend the particle beam around the accelerator's ring.

Particle accelerators have so far contributed to momentous discoveries in the physics worlds, with the latest being the discovery of the Higgs boson at the CERN LHC. Although the Higgs boson was the last missing piece of the physics Standard Model, there are still further challenges to be investigated in the physics world. The LHC programme is foreseen to keep running until 2035, however, it is unlikely it will provide explanations to all questions that current physics cannot answer. Future experiments, with higher precision, or with larger collision energies, are currently under study in order to investigate the open questions in the future decades.

Different future accelerators have been proposed for the post-LHC era. The Future Linear Collider (FCC) [2] is a proposed circular collider with a circumference of 100 km and a collision energy up to 100 TeV. It is foreseen to be operated in two stages: first as an electron-positron collider (FCC-ee) and later as a hadron collider (FCC-hh). The losses resulting from synchrotron radiation in electron-positron colliders are eliminated in linear colliders. The International Linear Collider (ILC) [3] and the Compact Linear Collider (CLIC, further described in Chapter 2) [4] are two proposed future linear electron-positron accelerators.

A very important component of such machines is the detector. One or more detectors are placed in caverns along the accelerator tunnel. The detector can be described as a large-scale three-dimensional digital camera, that records what happens during the particle collisions. Analysing the data stored in the detector can provide information on the particles produced from the collision and potentially lead to the discovery of new particles. A chain of electronic circuits is installed inside the detector in order to collect and store the data from the collisions. The information can be first processed by the front-end electronics (the level of processing depends on the requirements of the detector) before being transmitted and stored externally. Therefore, reliable electronic circuits are crucial for the successful operation of the detector. Developments in electronics are being investigated for a large variety of applications in the different parts of the detector, such as front-end electronics, signal processing, trigger systems and high-speed links.

This thesis presents the design and characterisation of two Application Specific Integrated Circuits (ASICs) targeted at the CLIC detector. The first ASIC was designed in the context of the CLIC vertex detector study, and the second for the CLIC silicon tracker. In Chapter 2, a brief introduction to the CLIC experiment and a synopsis of the CLIC detector are given. Chapter 3 presents an overview of the different technologies used for implementing integrated circuits for particle detectors. The design of a HV-CMOS chip, the CLICpix Capacitively Coupled Pixel Detector (C3PD), in view of the CLIC vertex detector is explained in Chapter 5. Characterisation results with the C3PD chip are presented in Chapter 6. Next, the design of a monolithic HR-CMOS chip, the CLIC Tracker Detector (CLICTD), targeted at the CLIC silicon tracker is described in Chapter 7. This is followed by the first measurement results with the CLICTD chip in Chapter 8. Last, a summary of the two chip designs and conclusions based on the measurement results are given in Chapter 9.

## **Chapter 2**

## **The Compact Linear Collider**

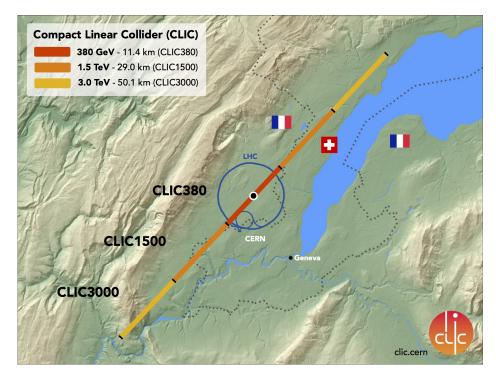

The work presented in this thesis was carried out in the framework of the Compact Linear Collider (CLIC) study. CLIC is a proposed linear electron-positron  $(e^+e^-)$  collider with a centre-of-mass energy up to 3 TeV [4]. The collider, which is currently in the Research and Development (R&D) phase, is envisaged to be built near the European Organisation for Nuclear Research (CERN) facilities in the area of Geneva, as presented in Figure 2.1.

Figure 2.1 The CLIC accelerator footprint near CERN. The three foreseen energy stages are presented. From [5].

### 2.1 The stages of the CLIC accelerator

Taking advantage of its linearity, the CLIC machine can be modular and its operation can be extended in different stages. Three stages are currently foreseen for the operation of the CLIC accelerator, based on various studies for exploiting the physics potential [6]. First, a shorter linear accelerator (11.4 km) will be built, delivering collisions at a centre-of-mass energy of 380 GeV. The second stage will be a 29.0 km long accelerator with a centre-of-mass energy of 1.5 TeV, before implementing the final upgrade which will be a 50.1 km long accelerator with a centre-of-mass energy of 3 TeV. The layout of the three stages of the CLIC accelerator near CERN and the area of Geneva is presented in Figure 2.1.

The target for the integrated luminosity at each stage is:  $500 \text{ fb}^{-1}$  at 380 GeV, 1.5 ab<sup>-1</sup> at 1.5 GeV and 3 ab<sup>-1</sup> at 3 GeV. The main parameters of the three energy stages of the CLIC accelerator are presented in Table 2.1.

| Parameter                          | Symbol               | Unit                                       | Stage 1 | Stage 2       | Stage 3     |

|------------------------------------|----------------------|--------------------------------------------|---------|---------------|-------------|

| Centre-of-mass energy              | $\sqrt{s}$           | GeV                                        | 380     | 1500          | 3000        |

| Repetition frequency               | frep                 | Hz                                         | 50      | 50            | 50          |

| Number of bunches per train        | $n_b$                |                                            | 352     | 312           | 312         |

| Bunch separation                   | $\Delta t$           | ns                                         | 0.5     | 0.5           | 0.5         |

| Accelerating gradient              | G                    | MV/m                                       | 72      | 72/100        | 72/100      |

| Total luminosity                   | L                    | $10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1}$ | 1.5     | 3.7           | 5.9         |

| Luminosity above 99% of $\sqrt{s}$ | $\mathscr{L}_{0.01}$ | $10^{34} \mathrm{cm}^{-2} \mathrm{s}^{-1}$ | 0.9     | 1.4           | 2           |

| Main tunnel length                 |                      | km                                         | 11.4    | 29.0          | 50.1        |

| Number of particles per bunch      | N                    | 10 <sup>9</sup>                            | 5.2     | 3.7           | 3.7         |

| Bunch length                       | $\sigma_z$           | μm                                         | 70      | 44            | 44          |

| IP beam size                       | $\sigma_x/\sigma_y$  | nm                                         | 149/2.9 | $\sim 60/1.5$ | $\sim 40/1$ |