# ALGORITHM DEVELOPMENT AND VLSI IMPLEMENTATION OF ENERGY EFFICIENT DECODERS OF POLAR CODES

A Dissertation

by

# JINGWEI XU

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Seong G. Choi       |

|---------------------|---------------------|

| Committee Members,  | Eun Kim             |

|                     | Peng Li             |

|                     | Narayanan Krishna   |

| Head of Department, | Miroslav M. Begovic |

May 2016

Major Subject: Computer Engineering

Copyright 2016 Jingwei Xu

### ABSTRACT

With its low error-floor performance, polar codes attract significant attention as the potential standard error correction code (ECC) for future communication and data storage. However, the VLSI implementation complexity of polar codes decoders is largely influenced by its nature of in-series decoding. This dissertation is dedicated to presenting optimal decoder architectures for polar codes. This dissertation addresses several structural properties of polar codes and key properties of decoding algorithms that are not dealt with in the prior researches. The underlying concept of the proposed architectures is a paradigm that simplifies and schedules the computations such that hardware is simplified, latency is minimized and bandwidth is maximized.

In pursuit of the above, throughput centric successive cancellation (TCSC) and overlapping path list successive cancellation (OPLSC) VLSI architectures and express journey BP (XJBP) decoders for the polar codes are presented.

An arbitrary polar code can be decomposed by a set of shorter polar codes with special characteristics, those shorter polar codes are referred to as constituent polar codes. By exploiting the homogeneousness between decoding processes of different constituent polar codes, TCSC reduces the decoding latency of the SC decoder by 60% for codes with length n = 1024. The error correction performance of SC decoding is inferior to that of list successive cancellation decoding. The LSC decoding algorithm delivers the most reliable decoding results; however, it consumes most hardware resources and decoding cycles. Instead of using multiple instances of decoding cores in the LSC decoders, a single SC decoder is used in the OPLSC architecture. The computations of each path in the LSC are arranged to occupy the decoder hardware stages serially in a streamlined fashion. This yields a significant reduction of hardware complexity. The OPLSC decoder has achieved about 1.4 times hardware efficiency improvement compared with traditional LSC decoders. The hardware efficient VLSI architectures for TCSC and OPLSC polar codes decoders are also introduced.

Decoders based on SC or LSC algorithms suffer from high latency and limited throughput due to their serial decoding natures. An alternative approach to decode the polar codes is belief propagation (BP) based algorithm. In BP algorithm, a graph is set up to guide the beliefs propagated and refined, which is usually referred to as factor graph. BP decoding algorithm allows decoding in parallel to achieve much higher throughput. XJBP decoder facilitates belief propagation by utilizing the specific constituent codes that exist in the conventional factor graph, which results in an express journey (XJ) decoder. Compared with the conventional BP decoding algorithm for polar codes, the proposed decoder reduces the computational complexity by about 40.6%. This enables an energy-efficient hardware implementation. To further explore the hardware consumption of the proposed XJBP decoder, the computations scheduling is modeled and analyzed in this dissertation. With discussions on different hardware scenarios, the optimal scheduling plans are developed. A novel memory-distributed micro-architecture of the XJBP decoder is proposed and analyzed to solve the potential memory access problems of the proposed scheduling strategy. The register-transfer level (RTL) models of the XJBP decoder are set up for comparisons with other state-of-the-art BP decoders. The results show that the power efficiency of BP decoders is improved by about 3 times.

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my advisor, Dr. Gwan Choi, for his financial support and encouragement for my research. He supported me in all the difficult situations where I needed help. I would like to thank Dr. Krishna Narayanan, Dr. Peng Li and Dr. Eun Kim for their time in serving in my committee. I appreciate Dr. Narayanan's introduction and suggestions on polar codes, which made me focus exclusively on polar codes decoders though initially I set out to work on conglomeration of different topics. Dr. Peng Li has been very helpful and he gave me a lot of guidance not only on academic study but also on my career path. In addition, he did provide me with many opportunities to review peers' works, which broadened my horizons and inspired me to think problems in different aspects. I would also like to thank Dr. Eun Kim. Through her excellent and impressive teaching skills, I was enlightened on the ideas and concepts of modern computer architectures which are of the great significance to the fundamental of my research works.

Several other students and people at Texas A&M helped me in my research work. Thanks to Ehsan Rohani for his guidance on standard communication protocols to develop practical hardware architectures. Thanks to Mehnaz Rahman on her working on the Matlab simulation for my architecture on the compressive sensing receiver for MIMO-OFDM cognitive radio. Special thanks to Tiben Che, in particular, for his working on the verification of some of the HDL modules for my architecture on belief propagation decoder. In addition, Tiben spent several weeks with me in working on the paper writing. Thanks to Honghuang Lin, Jimmy Jin, for their helping and guiding me to set up efficient simulation programs by their expertise and carefulness on programming. I would like to thank Mr. Qian Wang for his guidance on the exploration of hardware architectures.

My lovely wife, Lei, has supported me in much more ways than meets the eye. She did a difficult task of pursuing her Ph.D. degree at Texas A&M University, while taking care of different things at home. Last but not least, I would like to thank my parents for their constant support and encouragement through every major decision in my life.

# TABLE OF CONTENTS

|                                           | ]                                                                                      | Page                                                                                         |  |

|-------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| ABSTRA                                    | ACT                                                                                    | ii                                                                                           |  |

| ACKNO                                     | OWLEDGEMENTS                                                                           | iv                                                                                           |  |

| TABLE                                     | OF CONTENTS                                                                            | vi                                                                                           |  |

| LIST OF                                   | F FIGURES                                                                              | ix                                                                                           |  |

| LIST OF                                   | F TABLES                                                                               | xiii                                                                                         |  |

| 1. INTH                                   | RODUCTION                                                                              | 1                                                                                            |  |

| $\begin{array}{c} 1.2 \\ 1.3 \end{array}$ | Motivation                                                                             | $     \begin{array}{c}       1 \\       3 \\       5 \\       7 \\       7     \end{array} $ |  |

| 2. POL                                    | 2. POLAR CODES AND DECODING                                                            |                                                                                              |  |

| $2.2 \\ 2.3 \\ 2.4$                       | Polar Encoder                                                                          | 9<br>10<br>12<br>14<br>15                                                                    |  |

| 3. CON                                    | STITUENT CODE PROPERTIES OF POLAR CODES                                                | 19                                                                                           |  |

| 3.2                                       | All-frozen $\mathcal{N}^0$ Codes and All-information $\mathcal{N}^1$ Codes             | 19<br>20<br>21                                                                               |  |

| 4. VLSI                                   | I ARCHITECTURE FOR POLAR CODES DECODERS                                                | 23                                                                                           |  |

|                                           | Belief Propagation4.1.1Array Architecture4.1.2Line ArchitectureSuccessive Cancellation | 23<br>24<br>25<br>26                                                                         |  |

|    | 4.3                                                                                      | List Successive Cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                                                                                          |

|----|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 5. | . THROUGHPUT CENTRIC SUCCESSIVE CANCELLATION DECODER                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|    | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                          | Fast SC Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>33<br>34<br>36<br>38<br>38<br>39                                                      |

| 6. | OVE                                                                                      | ERLAPPING-PATH LIST SUCCESSIVE CANCELLATION DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44                                                                                          |

|    | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                | VLSI Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44<br>45<br>49<br>50<br>51<br>51<br>53                                                      |

| 7. | EXF                                                                                      | PRESS JOURNEY BELIEF PROPAGATION DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                          |

|    | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ul> | Algorithm Simplification7.1.1All-frozen $\mathcal{N}^0$ Codes7.1.2All-information $\mathcal{N}^1$ Codes7.1.3Repetition $\mathcal{N}^{REP}$ Codes7.1.4Single Parity Check $\mathcal{N}^{SPC}$ CodesEarly TerminationVLSI Architecture and Resource AssignmentsXJBP Scheduling7.4.1Round-trip Scheduling7.4.2Dependency7.4.3Scheduling Without Priority7.4.4Scheduling With Priority7.6.1Complexity Estimation and Analysis7.6.2Fixed-point Analysis7.6.3Synthesis Results and Discussion | $54 \\ 55 \\ 56 \\ 58 \\ 60 \\ 61 \\ 63 \\ 63 \\ 67 \\ 70 \\ 71 \\ 78 \\ 84 \\ 88 \\ 89 \\$ |

| 8. | OTI                                                                                      | IER WORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                                                                                          |

|    | 8.1  | Asynch | nronous Design for Precision-Scaleable LDPC Decoder 96                       |

|----|------|--------|------------------------------------------------------------------------------|

|    |      | 8.1.1  | Proposed System                                                              |

|    |      | 8.1.2  | Implementation of the Proposed System 101                                    |

|    |      | 8.1.3  | Simulations and Analysis                                                     |

|    | 8.2  | Recons | struction of Compressive Sensing                                             |

|    |      | 8.2.1  | Compressive Sensing Model                                                    |

|    |      | 8.2.2  | Reconstruction Algorithm                                                     |

|    |      | 8.2.3  | Modification on IHT                                                          |

|    |      | 8.2.4  | Implementation of Proposed Algorithm                                         |

|    |      | 8.2.5  | Simulations and Analysis                                                     |

|    | 8.3  | Compr  | ressive Sensing on MIMO-OFDM Cognitive Radio 119                             |

|    |      | 8.3.1  | Proposed System                                                              |

|    |      | 8.3.2  | Sparse Signal Model                                                          |

|    |      | 8.3.3  | Reconstruction                                                               |

|    |      | 8.3.4  | Setup and Simulation                                                         |

|    | 8.4  | Summa  | ary                                                                          |

| 9. | SUM  | IMARY  | ·                                                                            |

|    | 9.1  | Contri | butions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $134$ |

|    | 9.2  | Future | Work                                                                         |

| RF | EFER | ENCES  | 8                                                                            |

# LIST OF FIGURES

# FIGURE

# Page

| 1.1 | Block diagram of communication systems                                                                                                                                                                                                   | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

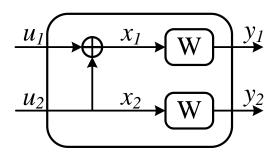

| 2.1 | Channel polarization example of 2 B-DMC channels                                                                                                                                                                                         | 11 |

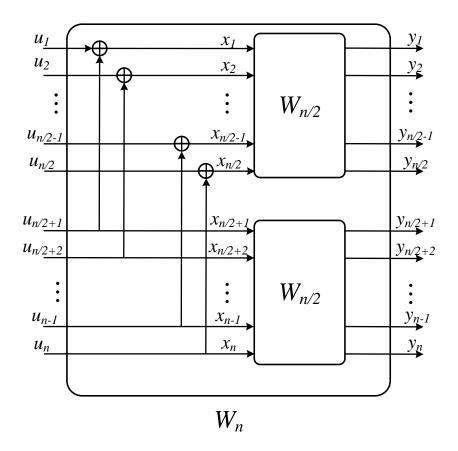

| 2.2 | Recursive construction of $n$ channel polarization                                                                                                                                                                                       | 13 |

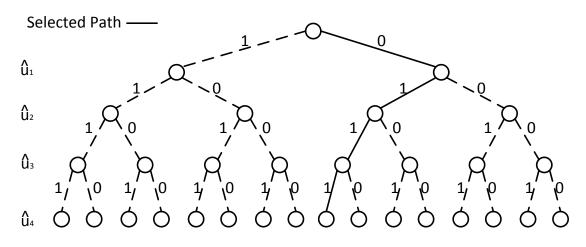

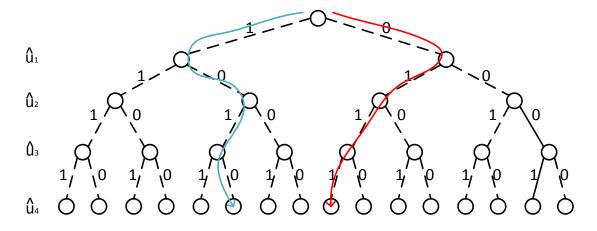

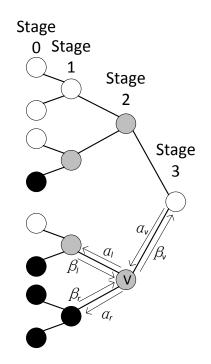

| 2.3 | Successive cancellation path on decoding tree                                                                                                                                                                                            | 14 |

| 2.4 | List successive cancellation decoding paths on decoding tree $\ . \ . \ .$                                                                                                                                                               | 15 |

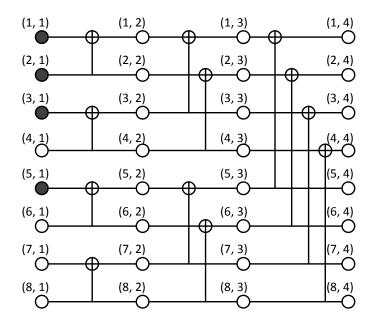

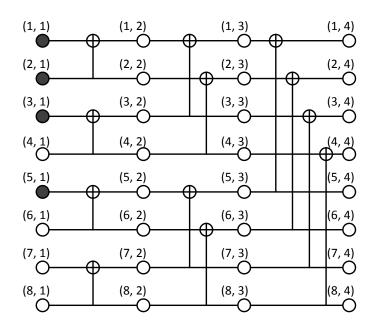

| 2.5 | Conventional BP factor graph of $N = 8$ polar codes                                                                                                                                                                                      | 16 |

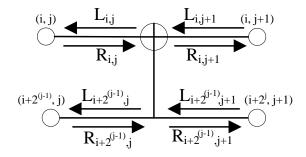

| 2.6 | Processing element of conventional BP algorithm                                                                                                                                                                                          | 17 |

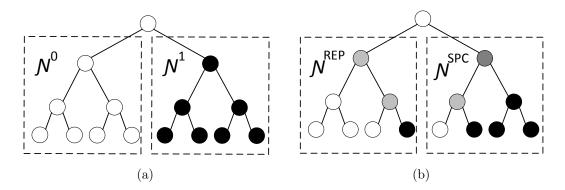

| 3.1 | An example of $\mathcal{N}^{REP}$ codes and $\mathcal{N}^{SPC}$ codes                                                                                                                                                                    | 20 |

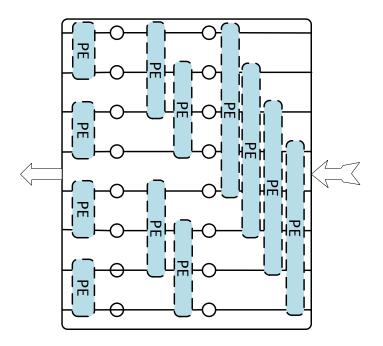

| 4.1 | The architecture for an array based BP decoder for a $n = 8$ , $rate = 0.5$ polar code                                                                                                                                                   | 24 |

| 4.2 | The scheduling for an array based BP decoder for a $n = 8, rate = 0.5$<br>polar code                                                                                                                                                     | 25 |

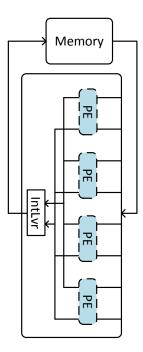

| 4.3 | The folding scheduling technique for a line based BP decoder for a $n = 8, rate = 0.5$ polar code $\ldots \ldots \ldots$ | 26 |

| 4.4 | The architecture for a line based BP decoder for a $n = 8, rate = 0.5$<br>polar code                                                                                                                                                     | 27 |

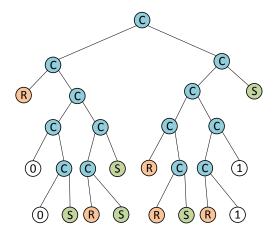

| 5.1 | Tree presentation of SC decoding processes for a $(8,4)$ polar code                                                                                                                                                                      | 30 |

| 5.2 | (a) An example of $\mathcal{N}^0$ and $\mathcal{N}^1$ codes in a (8, 4) polar code tree, and<br>(b) an example of $\mathcal{N}^{REP}$ and $\mathcal{N}^{SPC}$ in a (8, 4) polar code tree                                                | 33 |

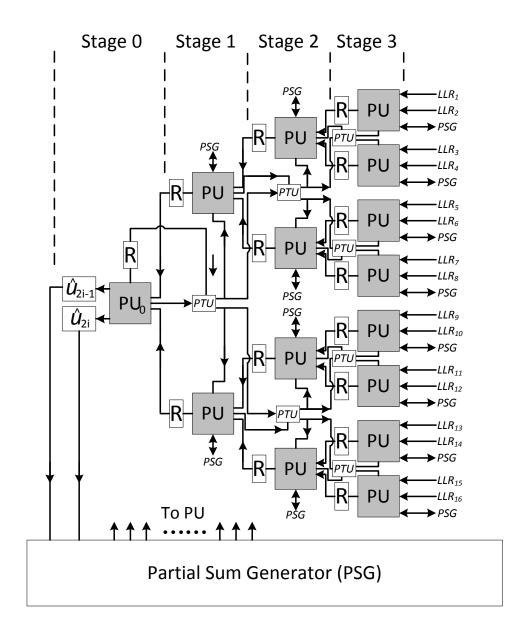

| 5.3 | Overview architecture of TCSC decoder for a $(8,4)$ polar code                                                                                                                                                                           | 41 |

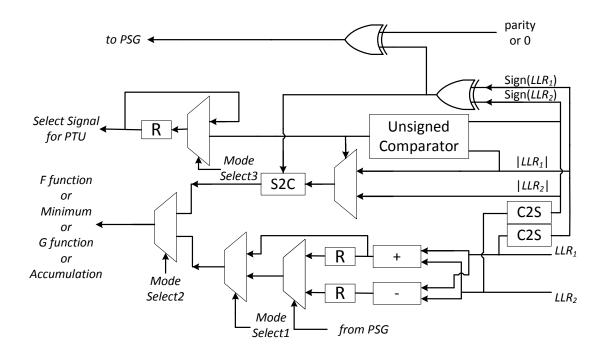

| 5.4 | The design details of PU in TCSC decoder                                                                                                                                                                                                 | 42 |

| 5.5 | The design details of PU0 in TCSC decoder                                                                                                                                                                                                | 42 |

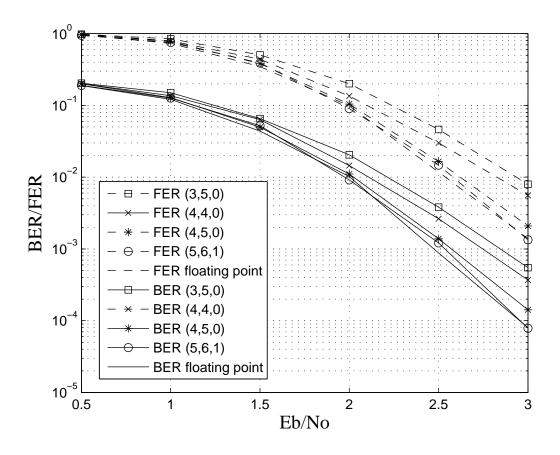

| 5.6  | Effect of quantization on the BER/FER performance of a (1024, 512) polar code                                                                                            | 43 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

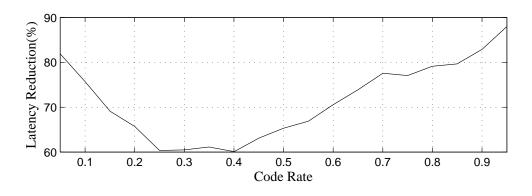

| 5.7  | The trend of latency reductions on code rates                                                                                                                            | 43 |

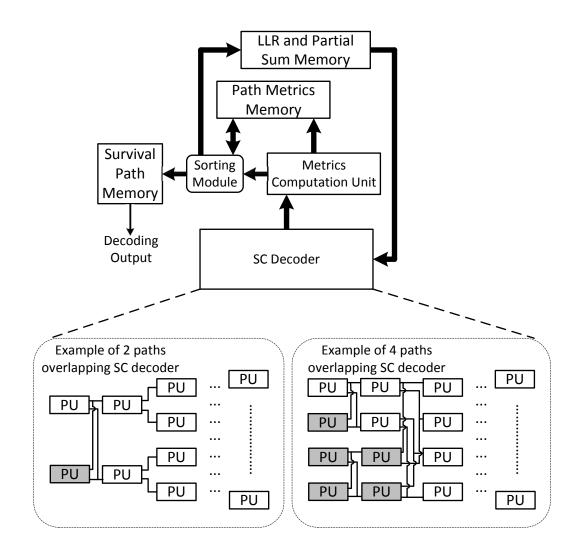

| 6.1  | The overall architecture of overlapping-path list successive cancella-<br>tion decoder.                                                                                  | 45 |

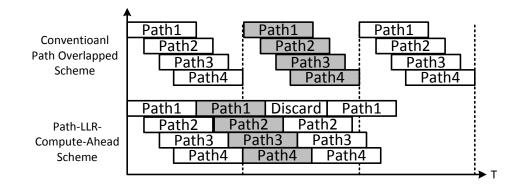

| 6.2  | Decoding schedule of the path-overlapping scheme for 2 lists (a) and 4 lists (b)                                                                                         | 46 |

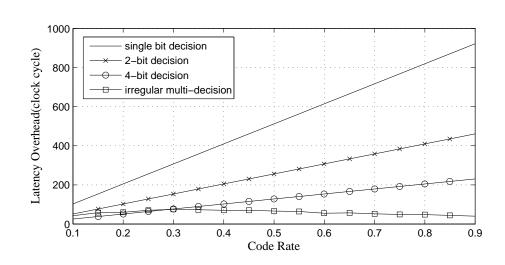

| 6.3  | The total latency overhead versus the polar codes rates                                                                                                                  | 49 |

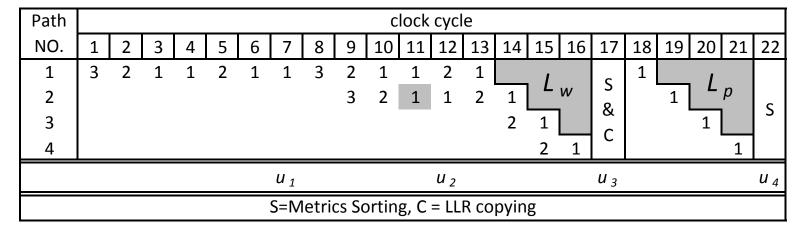

| 6.4  | Decoding schedule of OPLSC                                                                                                                                               | 50 |

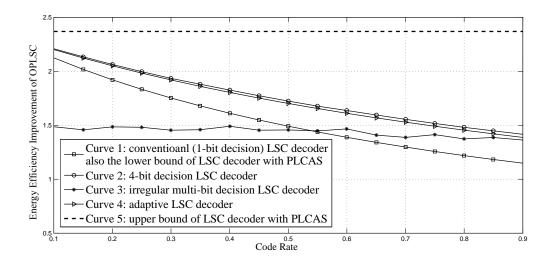

| 6.5  | The improvement of energy efficiency of OPLSC                                                                                                                            | 52 |

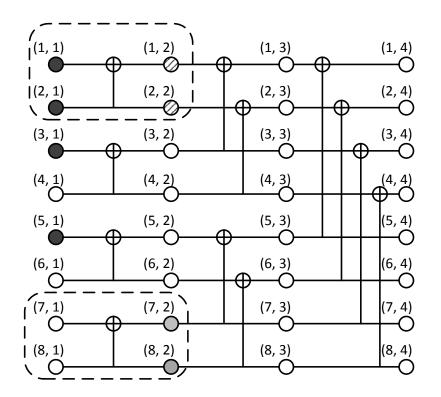

| 7.1  | An example of $\mathcal{N}^0$ codes in shadow and $\mathcal{N}^1$ codes in gray                                                                                          | 55 |

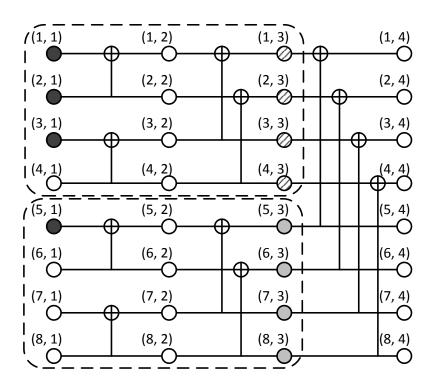

| 7.2  | An example of $\mathcal{N}^{REP}$ codes in shadow and $\mathcal{N}^{SPC}$ codes in gray                                                                                  | 56 |

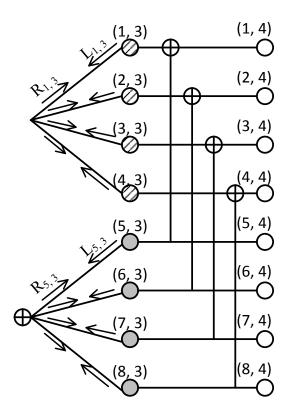

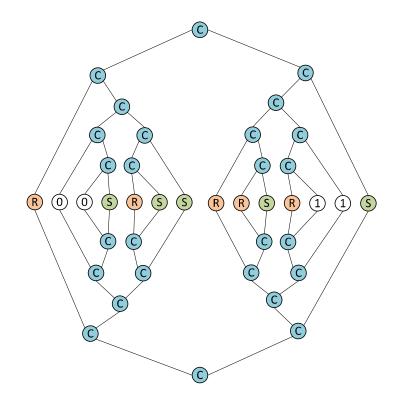

| 7.3  | The simplified factor graph for the example of $\mathcal{N}^{REP}$ and $\mathcal{N}^{SPC}$ codes.                                                                        | 57 |

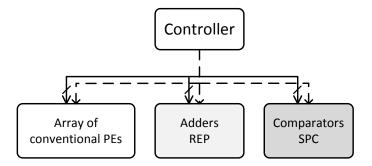

| 7.4  | An overview of XJBP decoder                                                                                                                                              | 61 |

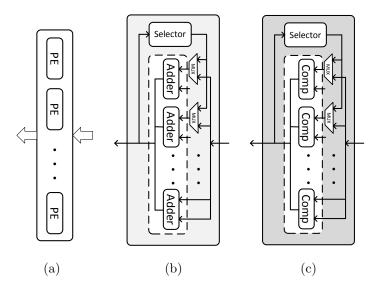

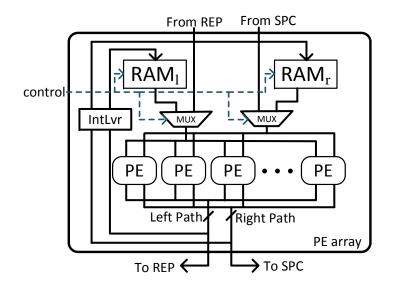

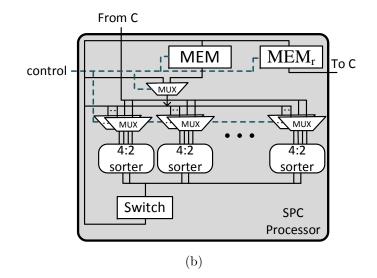

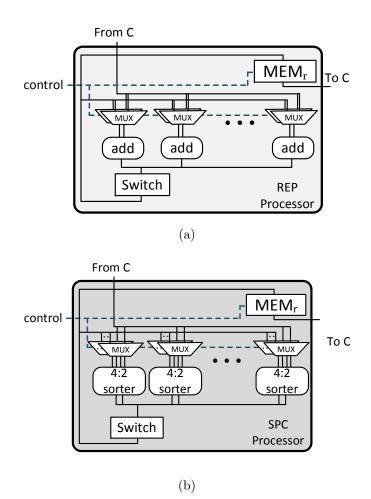

| 7.5  | (a) Structure of array of processing elements. (b) Array of adders to decoder repetition codes. (c) Array of comparators to decoder SPC codes                            | 63 |

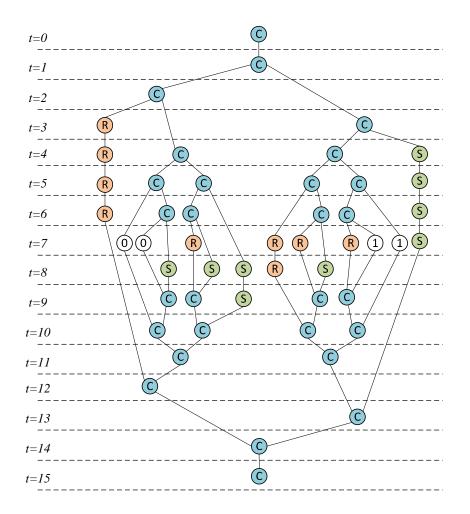

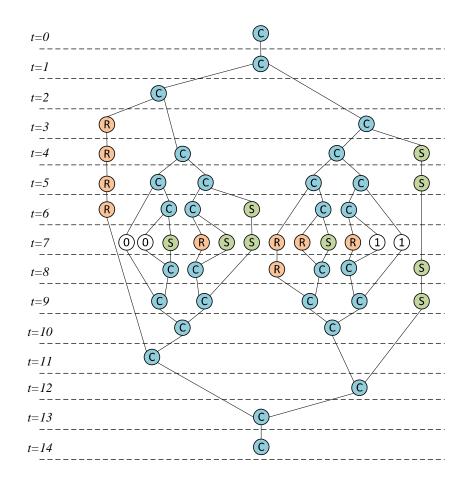

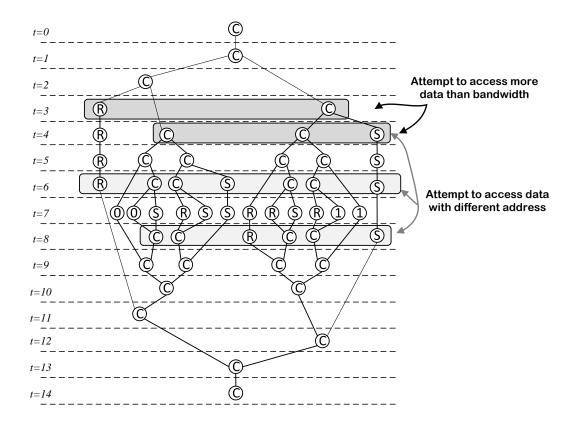

| 7.6  | The computation scheduling and dependency for round trip BP of a $n = 8, r = 0.5$ polar code                                                                             | 64 |

| 7.7  | The computation scheduling and dependency for round trip XJBP of<br>a $n = 8, r = 0.5$ polar code.                                                                       | 65 |

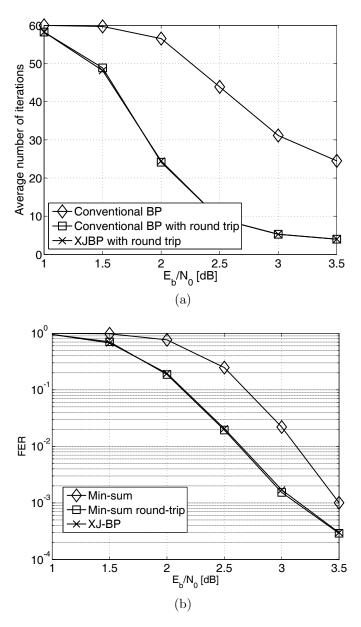

| 7.8  | The comparison between roundtrip scheduling and conventional schedul-<br>ing in terms of efficiency (number of iterations) (a) and performance<br>(Frame error rate) (b) | 66 |

| 7.9  | The dependency for belief propagation of a $n = 128, r = 0.5$ polar code.                                                                                                | 68 |

| 7.10 | The dependency for an iteration of BP decoding of a $n = 128, r = 0.5$<br>polar code                                                                                     | 69 |

| 7.11 | An example of ASAP scheduling for XJBP decoding of a $n = 128, r = 0.5$ polar code                                                                                       | 71 |

| 7.12 | An example of preemptive scheduling with priority for XJBP decoding<br>of a $n = 128, r = 0.5$ polar code                                                     | 73  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.13 | An example of non preemptive scheduling with priority for XJBP de-<br>coding of a $n = 128, r = 0.5$ polar code                                               | 76  |

| 7.14 | An example of memory accesses for XJBP decoding of a $n = 128, r = 0.5$ polar code                                                                            | 78  |

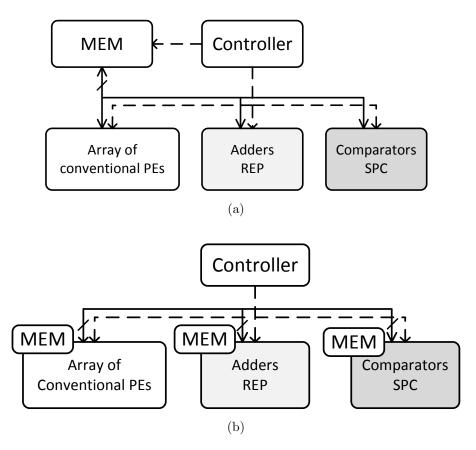

| 7.15 | The comparison between shared memory micro-architecture (a) and distributed memory micro-architecture (b)                                                     | 79  |

| 7.16 | Implementation of a conventional processing element of XJBP decoder.                                                                                          | 80  |

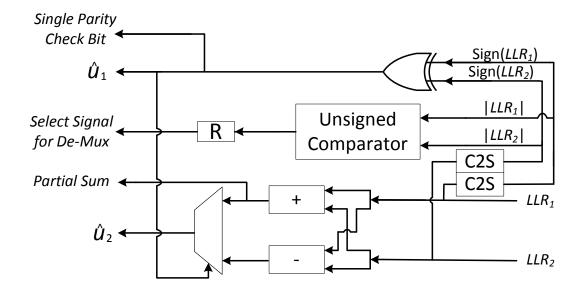

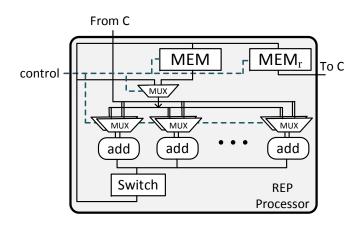

| 7.17 | The implementation details of REP processor(a) and SPC processor<br>(b)                                                                                       | 82  |

| 7.18 | The implementation details of non-preemptive REP processor(a) and SPC processor(b)                                                                            | 83  |

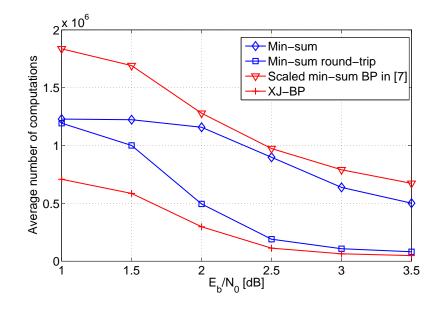

| 7.19 | Average numbers of computations consumed to decode each codeword<br>of by the proposed BP decoding algorithm for $(1024, 512)$ polar code<br>with rate = 0.5. | 87  |

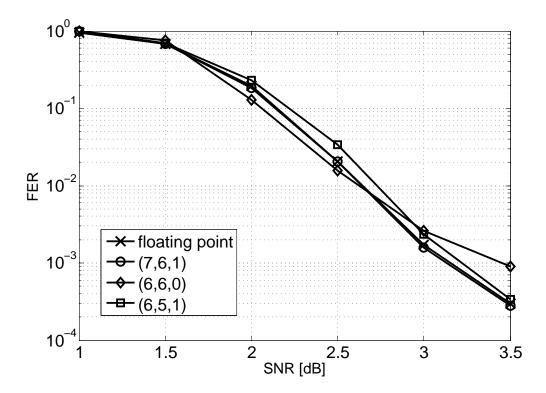

| 7.20 | Quantized error correction performance of XJBP.                                                                                                               | 88  |

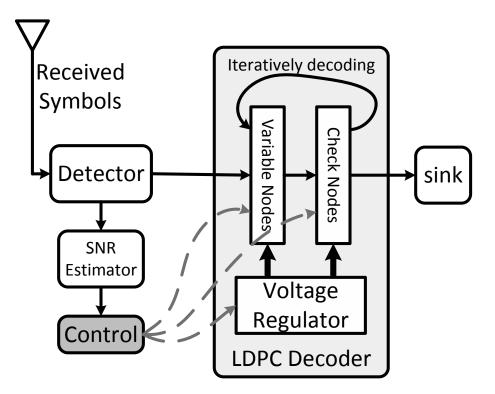

| 8.1  | The overview system flow proposed LDPC decoder                                                                                                                | 99  |

| 8.2  | Generic LDPC decoding data flow graph                                                                                                                         | 100 |

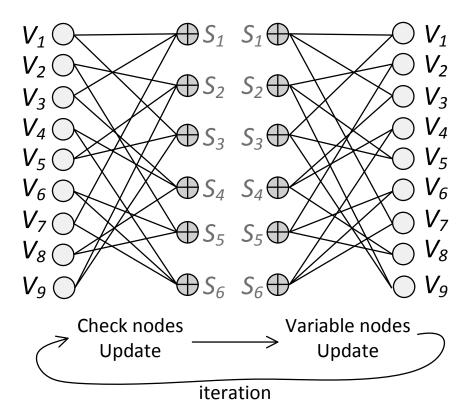

| 8.3  | Asynchronous circuits data path model                                                                                                                         | 101 |

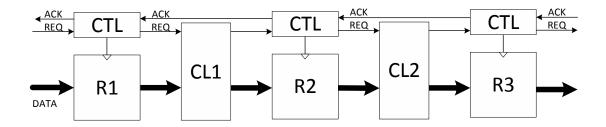

| 8.4  | Asynchronous precision-salable VNU design                                                                                                                     | 102 |

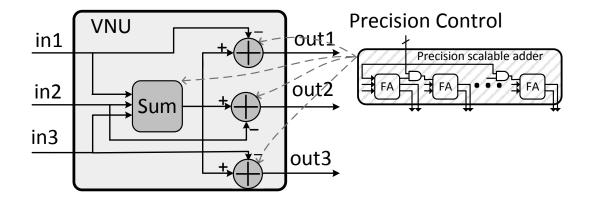

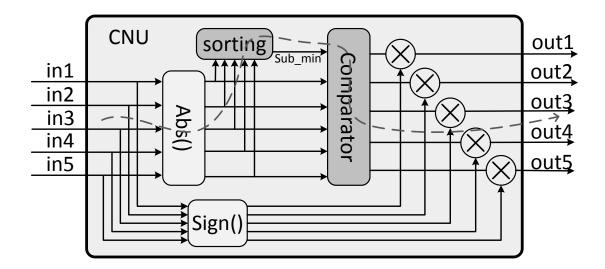

| 8.5  | Asynchronous precision-salable CNU design                                                                                                                     | 103 |

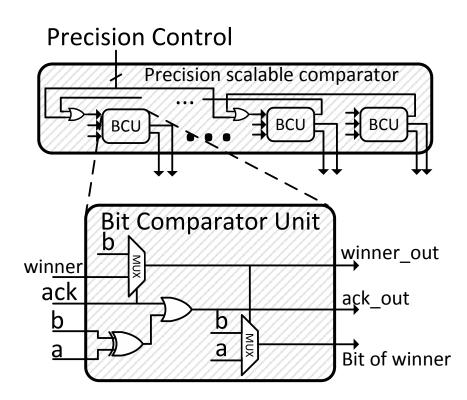

| 8.6  | Proposed asynchronous comparator                                                                                                                              | 104 |

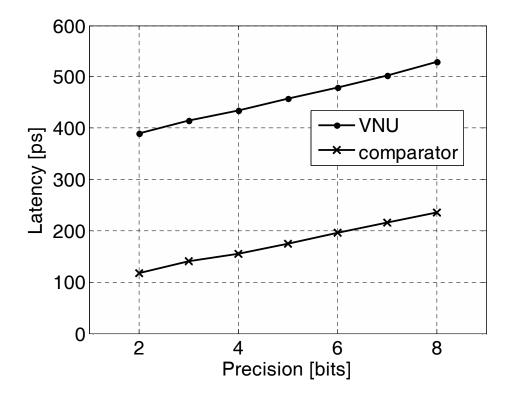

| 8.7  | Units delays for different bits of precision                                                                                                                  | 106 |

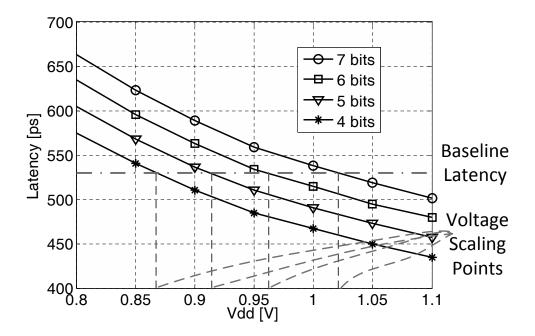

| 8.8  | Voltage scaling to align processing latency                                                                                                                   | 107 |

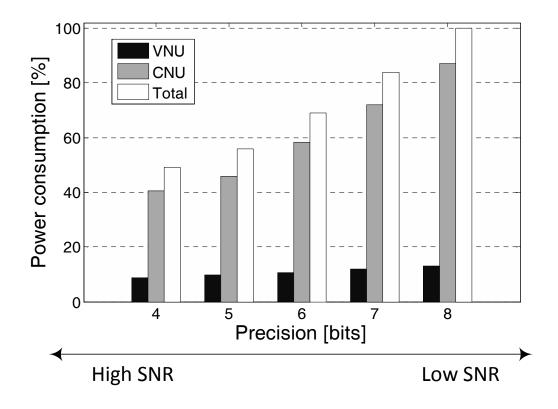

| 8.9  | Normalized power reduction compared with fixed precision LDPC de-<br>coder                                                                                    | 108 |

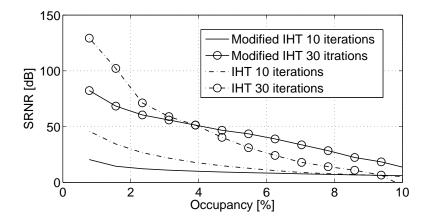

| 8.10 | Comparison between modified IHT with $t_0 = 0.82$ and original IHT<br>at 25% Nyquist sampling rate $\ldots \ldots \ldots$ | 13 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

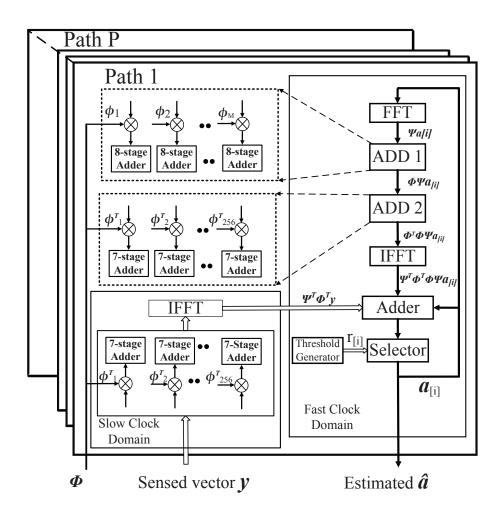

| 8.11 | Parallel architecture for compressive sensing reconstruction 11                                                                                                                                                                           | 14 |

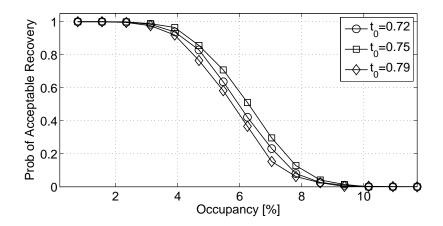

| 8.12 | Successful recovery rate with different threshold function coefficient $t_0$ at 20 iterations                                                                                                                                             | 16 |

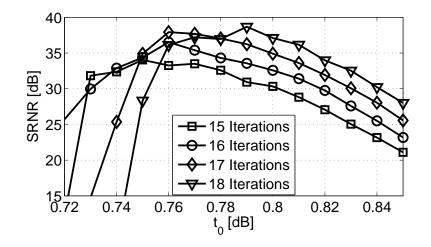

| 8.13 | SRNR with different threshold function coefficient $t_0$                                                                                                                                                                                  | 17 |

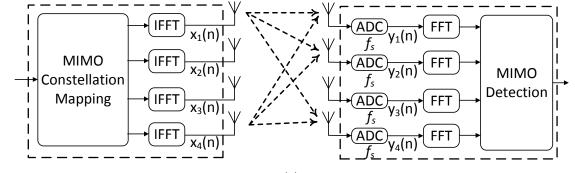

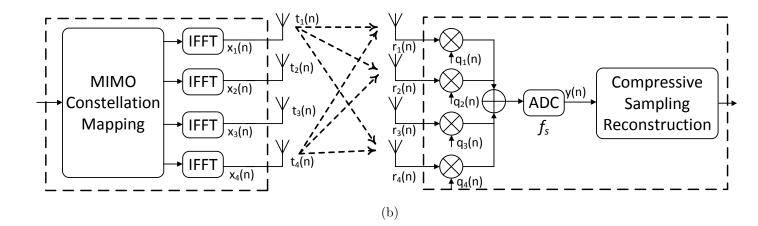

| 8.14 | Structures of conventional (a) and proposed (b) MIMO-OFDM transmission system.                                                                                                                                                            | 20 |

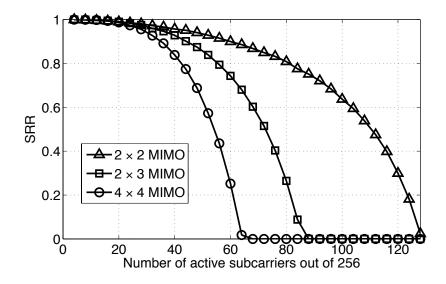

| 8.15 | Successful reconstruction rate at 15 dB SNR                                                                                                                                                                                               | 29 |

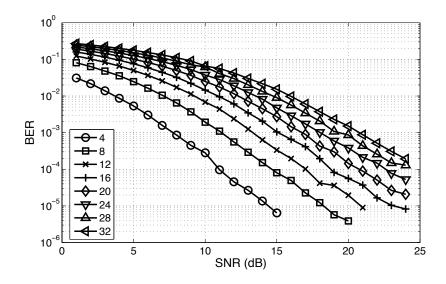

| 8.16 | Detection performance of the proposed system at $4 \times 4$ MIMO 13                                                                                                                                                                      | 30 |

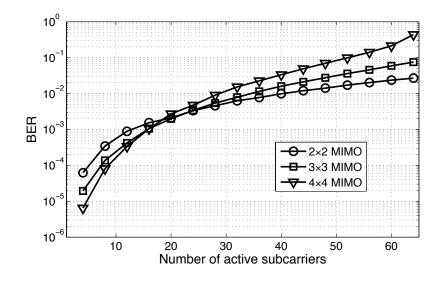

| 8.17 | Detection performance of different MIMO scales at 15 dB SNR 13 $$                                                                                                                                                                         | 31 |

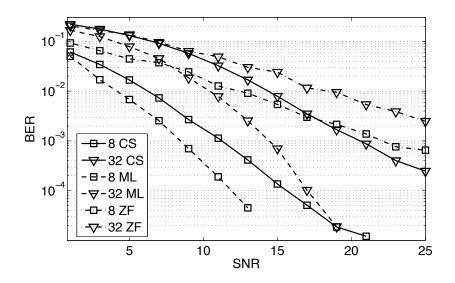

| 8.18 | The performances comparisons with conventional MIMO detection 13                                                                                                                                                                          | 32 |

# LIST OF TABLES

| TABLE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1   | Truth table of PTU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36  |

| 5.2   | Hardware comparison of different $(n, k)$ SC decoder with q-bit quantization for inner LLRs using tree architecture $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38  |

| 5.3   | Synthesis result for $(1024, 870)$ and $(1024, 512)$ polar codes $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39  |

| 7.1   | Number of all constituent codes with different sizes in a (1024, 512) polar code with rate of 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59  |

| 7.2   | This is a comparison of number of iterations in different BP decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65  |

| 7.3   | Decoding delays of XJBP with different code sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75  |

| 7.4   | Number of computations of XJ-BP algorithm with all polar codes at rate = $0.5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86  |

| 7.5   | Computations of XJ-BP algorithm in each iteration at different code rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86  |

| 7.6   | This is a logic consumption table for XJBP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89  |

| 7.7   | This is a memory consumption table for XJBP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90  |

| 7.8   | This is a total hardware consumption table for XJBP $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \hfil$ | 91  |

| 7.9   | This is a hardware comparison table between XJBP and other state-<br>of-the-art BP decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93  |

| 7.10  | Hardware consumption comparisons among SC and BP decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95  |

| 8.1   | SRNR with different numbers of iterations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 117 |

| 8.2   | CS reconstruction design power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 118 |

### 1. INTRODUCTION

This introduction describes the demands of advanced error correction coding techniques for evolving communications and storage systems. With the introduction of the advantages of polar codes over other existing error correction codes, the main contributions of this dissertation is presented. Through the similar hardware development methodology, other contributions made for problems within same mathematical problem scope for advanced communication and storage system are also listed in this dissertation. The outlines of this dissertation is given in the end of this chapter to guide readers follow this dissertation.

### 1.1 Motivation

The communications markets are continuously facilitated by the diverse and increasing demands of acquiring data and sharing information. With the enormous amount of data swapped, the communication technology is undergoing tremendous rapid escalation from hundred kilobits per second 3G to gigabit per second 5G of mobile telecommunication, from multi-megabits per second to multi-gigabits per second of Ethernet communication, from multi-megabyte portable MP3 player to multi-gigabyte mobile smart phone. The progress and evolution on communication are primarily driven by the discoveries on information theory and advances on the integrated circuits.

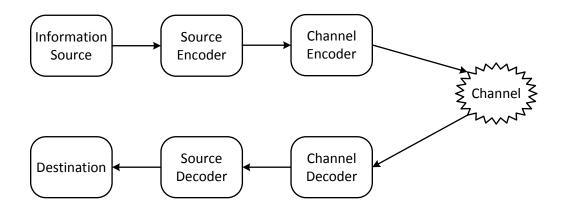

Figure 1.1 shows a simplified block diagram of a digital communication system [1]. First, the source data of information such as voice, video is sampled and encoded through the source encoder, so as to be compressed to remove any unnecessary redundancy in the data. Then channel encoder codes the redundancy removed sequences so that it can recover the correct information after passing through the channel. The

Figure 1.1: Block diagram of communication systems

coded bit sequences of data are transmitted through the channel to receiver. The mediums of channels could be varied as copper (wired communication), air (wireless communication), water (underwater communication), flash memory and so on.

There are two important topics in the communication. They are the source coding and channel coding for efficient compression as and the reliable transmission of the data respectively.

The information is firstly fed through the source encoder or data compression to remove unnecessary redundant data or compact and encapsulate data in smaller sizes. If the data consists of bank records or personal details we cannot afford to lose any information. In such cases, the compression is achieved by exploiting patterns in the data. Before transmission over noisy mediums, the compressed data are coded again by channel encoder, which is the second central topic of information theory. To make communication reliable in the presence of noise, the common procedure is to add redundancy to the data before transmission. The intended receiver only has access to a noisy version of the data. However, if the redundancy is added in a clever way, then it is possible to reconstruct the original data at the receiver. Adding redundancy for reliable transmission is also referred as error correcting coding (ECC). Coding is a central part of any communication systems; e.g., consider wired phones, mobile phones, or the Internet. Coding is also used for storage on CDs and flash memories to prevent data loss due to scratches or errors during the reading process.

Since the Shannon's work on 1948 [2], research on ECC has developed for several decades. Error correcting codes such as convolutional [3], Turbo [4] and LDPC [5] are typical error correcting codes widely used in protocols. Among them, Turbo [6] and LDPC [7,8] are proven to be very close to Shannon limit.

Although great success has been achieved by existing near-capacity error correction codes, promoted by the continuously growing demand for reliable big data storage and high-speed communication, the exploration on better correction codes does never stop. In 2008, Polar codes [9] are found as error correcting codes which provable achieve the capacity of symmetric binary-input discrete memoryless channels (B-DMCs).

### 1.2 Problem Overview

Polar codes proposed by Arikan [9] are not only first provably capacity achieving codes for any B-DMCs, but also have low encoding and decoding complexity. With its low error-floor performance [10] and high regularity in coding structure, polar codes attract a significant attention from the coding theory community [11–28] and have the potential to become a standard ECC for the future communication and data storage systems.

However, the VLSI implementation complexity of polar codes decoder is largely influenced by its nature of in-series decoding. There are three widely-considered approaches to decode polar codes. These are successive cancellation (SC), its variant successive cancellation list (SCL) decoders and belief propagation (BP) algorithms. The SC algorithm receives more attentions because of its low computational complexity  $\mathcal{O}(nlogn)$ , where *n* is the code length. But, decoders based on SC algorithm suffer from the high latency and limited throughput due to their serial decoding natures. Recently several efforts have been taken into reducing the SC decoding latency [29, 30]. Sarkis et al. utilized the constituent codes that exist in the polar codes to significantly reduce the SC decoding latency by avoiding tree traversals [30]. Although the latency of SC algorithm is substantially improved, the time complexity of it is still  $\mathcal{O}(n)$ . Thus with longer polar codes, SC algorithm is still limited in terms of the throughput. However, polar codes with longer length are more attractive, because the performance of polar codes is superior to other codes at long codeword lengths.

Although polar codes have inherent capacity-achieving property, with small and medium code lengths, the error correction performances of polar codes are inferior to Turbo codes and LDPC. [14] proposes SCL decoder, which is also inherent serial decoding method similar as SC decoder. SCL improves the error correction performance of polar codes, it requires more hardware resource to upgrade the performance as well still suffers from the long latency which is intolerable for real-time transmission.

Another approach to decode the polar codes is belief propagation-based (BP) algorithm, which allows decoding in parallel to achieve much higher throughput in dedicated hardware implementation. Due to its higher computational demand, compared with SC algorithms, BP does not receive much attentions. The first attempt at implementing BP on field programmable gate array (FPGA) is presented by Pamuk in [31], where the message passing functions are approximated by the min-sum (MS) algorithm for efficient hardware design. However, the performance of BP decoding is degraded because of the approximations. Thus, Yuan et al. explored scaled min-sum (SMS) approximation for message passing functions in [32] to remedy the performance penalty. However, compared with MS algorithm, SMS incurs one extra scaling operations in each message passing. Yuan et al. further improved the efficiency of SMS BP decoders using early termination in [33]. On the other hand, by removing unnecessary computations for frozen bits in polar codes, Zhang et al. reduce the complexity for sum-product (SP) BP decoding in [34] by around 25% without decoding performance degradation.

# 1.3 Main Contributions

Motivated by the challenges mentioned above on polar codes decoders, a set of methodologies are developed as the guidance to design a hardware-efficient polar codes decoders for next-generation communication and storage systems. Optimization on both algorithm and hardware levels are explored as the core methodology for achieving the objective. In particular, the main contributions of this work are listed in the following:

- 1. The simplifications on polar codes decoding algorithm which takes the advantage of the existences of the constitute codes of polar codes.

- 2. The static scheduling computation paradigm by which the proposed advanced belief propagation algorithm is used to reduce the computations, memory and interconnect.

- 3. The hardware architecture is explored from bottom up to implement the simplifications of polar code decoding algorithms and computation paradigms....

This dissertation summarizes works on two types of hardware-efficiency polar codes decoders based on SC, LSC decoding algorithm, that substantially reduce the computational complexity over same type of state-of-the-art decoders. The dissertation will emphasize the work on algorithm development on the XJBP and the micro-architecture exploration and implementation for the XJBP decoder.