# MILLIMETER-WAVE CONCURRENT DUAL-BAND SIGE BICMOS RFIC PHASED-ARRAY TRANSMITTER AND COMPONENTS

A Dissertation

by

## JUSEOK BAE

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Cam Nguyen Committee Members, Aydin Karsilayan

Laszlo B. Kish Mark Everett

Head of Department, Miroslav M. Begovic

December 2017

Major Subject: Electrical Engineering

Copyright 2017 Juseok Bae

#### **ABSTRACT**

A concurrent dual-band phased-array transmitter (TX) and its constituent components are studied in this dissertation. The TX and components are designed for the unlicensed bands, 22–29 and 57–64 GHz, using a 0.18-μm BiCMOS technology. Various studies have been done to design the components, which are suitable for the concurrent dual-band phased-array TX. The designed and developed components in this study are an attenuator, switch, phase shifter, power amplifier and power divider.

Attenuators play a key role in tailoring main beam and side-lobe patterns in a phased-array TX. To perform the function in the concurrent dual-band phased-array TX, a 22–29 and 57–64 GHz concurrent dual-band attenuator with low phase variations is designed.

Signal detection paths are employed at the output of the phased-array TX to monitor the phase and amplitude deviations/errors, which are larger in the high-frequency design. The detected information enables the TX to have an accurate beam tailoring and steering. A 10–67 GHz wide-band attenuator, covering the dual bands, is designed to manipulate the amplitude of the detected signal. New design techniques for an attenuator with a wide attenuation range and improved flatness are proposed. Also, a topology of dual-function circuit, attenuation and switching, is proposed. The switching turns on and off the detection path to minimize the leakages while the path is not used.

Switches are used to minimize the number of components in the phased-array transceiver. With the switches, some of the bi-directional components in the transceiver

such as an attenuator, phase shifter, filter, and antenna can be shared by the TX and receiver (RX) parts. In this dissertation, a high-isolation switch with a band-pass filtering response is proposed. The band-pass filtering response suppresses the undesired harmonics and intermodulation products of the TX.

Phase shifters are used in phased-array TXs to steer the direction of the beam. A 24-GHz phase shifter with low insertion loss variation is designed using a transistor-body-floating technique for our phased-array TX. The low insertion loss variation minimizes the interference in the amplitude control operation (by attenuator or variable gain amplifier) in phased-array systems.

BJTs in a BiCMOS process are characterized across dc to 67 GHz. A novel characterization technique, using on-wafer calibration and EM-based de-embedding both, is proposed and its accuracy at high frequencies is verified. The characterized BJT is used in designing the amplifiers in the phased-array TX.

A concurrent dual-band power amplifier (PA) centered at 24 and 60 GHz is proposed and designed for the dual-band phased-array TX. Since the PA is operating in the dual frequency bands simultaneously, significant linearity issues occur. To resolve the problems, a study to find significant intermodulation (IM) products, which increase the third intermodulation (IM3) products most, has been done. Also, an advanced simulation and measurement methodology using three fundamental tones is proposed.

An 8-way power divider with dual-band frequency response of 22–29 and 57–64 GHz is designed as a constituent component of the phased-array TX.

# **DEDICATION**

To my parents, Mr. Bongjin Bae and Mrs. Jungsim Cho,

my wife, Hyunsuk,

my sister, Joohyun,

and all of those who have inspired me to become what I am today.

#### **ACKNOWLEDGEMENTS**

I would like to sincerely thank my advisor Prof. Cam Nguyen for his endless support and education. It is a great pleasure to work with him in his research group and an honor to be one of his students. Thanks to him, my wife and I had a happy life in Doha, Qatar, for three years of my doctoral study when he decided to take up a position in Doha. Back then, my wife and I were unfamiliar with the city and the country and afraid of the life in the strange place. However, I sincerely believed Prof. Cam Nguyen, and I was confident that there would be more chances to learn by staying near him during my Ph.D. I was right. My life in Doha was great, and I could have many opportunities for my studies. I was able to publish papers in the renowned journals as many as I want and attend various conferences, which help me extend the research scope. Prof. Cam Nguyen and his wife (Mrs. Ngoc-Diep Tran) took good care of me and my wife (Ms. Hyunsuk Tak), which makes us feel comfortable and safe in the unfamiliar city. I will never forget their kindness and thoughts for us. He also taught me many important lessons in life. His courage and success in the face of adversity in his life always encouraged me to keep me going when times were challenging, which will guide me for the rest of my life. I also appreciate his open mind on new ideas and his scholarly foresight, which makes me feel comfortable while I attempt novel designs.

I sincerely thank my dissertation committee members, Prof. Aydin Karsilayan, Prof. Laszlo B. Kish, and Prof. Mark Everett for their time, interest, and valuable comments.

I would like to thank my labmates and friends, Dr. Jaeyoung Lee, Dr. Kyoungwoon Kim, Dr. Donghyun Lee, Dr. Youngman Um, Dr. Sunhwan Jang, Dr. Sanghun Lee, Dr. Chadi Geha, and Yuan Luo, for their technical discussions, help, and a warm heart. The mere fact that there are friends around me who work hard to make the world a better place was encouraging me.

I especially thank my parents, Mr. Bongjin Bae and Mrs. Jungsim Cho, for their endless love and faith in me. It was not possible to complete my Ph.D. work without them. I was not an outstanding student in my adolescence, but they never doubt my success on the long journey of studies, bachelor, master, and Ph.D., which always let me carry out my studies with confidence. They have always been my role models. Their lives with hard works to provide better environments for my sister and me makes me go further without giving up whenever I have hardship. I sincerely respect my parents and their lives and appreciate their unconditional sacrifices they made for me. I hope they now put down their burdensome duties as parents and rely on their son to get rest as the son has been done so far.

My appreciation also goes to my sister, Joohyun Bae, for her love and support. She has been a good friend and role model in my life. I know she always cares about me, her younger brother. Without her support, I would not have been able to start my Ph.D. My lovely nephew and niece, Jiho and Jiaha, are the sunshine of our family and the source of our happiness. I hope they fill their lives with laughter, joy, and happiness, and even if they face unexpected hardship, I hope they wisely get over it and make their lives more worthwhile.

Finally, I would like to thank my lifelong partner, Hyunsuk Tak, for all of her unconditional love and devotion. Getting married to her is the best thing I have done in my Ph.D. period and my life. I believe our happier life is waiting for us right around the corner.

Some chapters in the dissertation are reprints of the paper published. The dissertation author is the primary author of the papers. The reference papers are:

For Chapter III, Juseok Bae and Cam Nguyen, "A novel concurrent 22–29/57–64-GHz dual-band CMOS step attenuator with low phase variations," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 64, no. 6, pp.1867–1875, April 2016.

For Chapter IV, Juseok Bae, Jaeyoung Lee, and Cam Nguyen, "A 10–67-GHz CMOS dual-function switching attenuator with improved flatness and large attenuation range," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 61, no. 12, pp. 4118-4129, Dec. 2013.

For Chapter VI, J. Bae and C. Nguyen, "On the design of CMOS phase shifters with small insertion-loss variation for phased arrays and its validation at 24 GHz", *Microwave and Optical Technology Letters*, vol. 58, issue 9, pp. 2203–2201, June 2016.

For Chapter VIII, J. Bae, S. Jordan, and C. Nguyen, "Dc-to-67Ghz high-speed BiCMOS BJT characterization with on-wafer calibration and

EM-based de-embedding", *Microwave and Optical Technology Letters*, vol. 56, issue 6, pp. 1285-1292, June 2014.

- For Appendix A, Juseok Bae and Cam Nguyen, "A 44 GHz CMOS RFIC dual-function attenuator with band-pass-filter response," *IEEE Microwave and Wireless Components Letters*, vol. 25, no. 4, pp. 241–243, Apr. 2015.

- For Appendix B, Juseok Bae and Cam Nguyen, "New dual-band band-pass filter design with enhanced dual-band skirt characteristics," *IEEE Microwave Conference Proceedings (APMC)*, 2013 Asia-Pacific, Seoul, South Korea, Nov. 2013, pp. 599-901.

## CONTRIBUTORS AND FUNDING SOURCES

## **Contributors**

This work was supervised by a dissertation committee consisting of Professors Cam Nguyen, Aydin Karsilayan and Laszlo B. Kish of the Department of Electrical and Computer Engineering and Professor Mark Everett of the Department of Geology and Geophysics.

The feasibility studies for the design depicted in Chapter IV were conducted in part by Jaeyoung Lee of the Department of Electrical Engineering.

All other work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

This work was made possible in part by the Qatar National Research Fund (a member of Qatar Foundation) under Grant Number NPRP 6-241-2-102.

This work was supported in part by the U.S. Air Force Office of Scientific Research and in part by the U.S. National Institute of Justice.

# TABLE OF CONTENTS

|                                                                               |                                                                                                                                                                                                                          | Page                                    |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| ABSTRACT                                                                      |                                                                                                                                                                                                                          | ii                                      |

| DEDICATION                                                                    |                                                                                                                                                                                                                          | iv                                      |

| ACKNOWLED                                                                     | GEMENTS                                                                                                                                                                                                                  | v                                       |

| CONTRIBUTO                                                                    | RS AND FUNDING SOURCES                                                                                                                                                                                                   | ix                                      |

| TABLE OF CO                                                                   | NTENTS                                                                                                                                                                                                                   | X                                       |

| LIST OF FIGURE                                                                | RES                                                                                                                                                                                                                      | xiv                                     |

| LIST OF TABL                                                                  | ES                                                                                                                                                                                                                       | xxiv                                    |

| CHAPTER I                                                                     | INTRODUCTION & BACKGROUND                                                                                                                                                                                                | 1                                       |

| 1.1.1 SiG<br>1.2 RFIC Ph<br>1.2.1 Ph<br>1.2.2 Ph<br>1.2.3 Co<br>1.3 Frequence | Based Millimeter-Wave RFICs Ge BiCMOS Technology nased-Array System ased-Array Beam Steering with Varying Phases ased-Array Beam Tailoring with Amplitude Varied ncurrent Dual-Band Phased-Array System cy Band Planning | 1<br>2<br>3<br>6<br>8<br>11<br>14<br>15 |

| CHAPTER II                                                                    | CONCURRENT DUAL-BAND PHASED-ARRAY TRANSCEIVER                                                                                                                                                                            | 16                                      |

| 2.1 24/60-G                                                                   | Hz Concurrent Dual-Band Phased-Array Transceiver/Transmitter.                                                                                                                                                            | 16                                      |

| CHAPTER III                                                                   | CONCURRENT 22–29/57–64-GHZ DUAL-BAND CMOS STEP ATTENUATOR WITH LOW PHASE VARIATIONS                                                                                                                                      | 18                                      |

|                                                                               | ent Dual-Band and Low-Phase-Variation Attenuators                                                                                                                                                                        | 20<br>23                                |

| 3.1.2 In    | tegrated Diplexer-Attenuator and Constituent Low- and High-Band |

|-------------|-----------------------------------------------------------------|

|             | and-Pass-Filter-Attenuators                                     |

|             | ow-Phase-Variation Attenuator                                   |

|             | ent Dual-Band Attenuator with Low Phase Variations              |

| 3.2.1 De    | esign and Fabrication                                           |

| 3.2.2 Si    | mulations and Measurements                                      |

| 3.3 Conclus | ion                                                             |

| 3.4 Referen | ces                                                             |

|             |                                                                 |

| CHAPTER IV  | 10–67-GHZ CMOS DUAL-FUNCTION SWITCHING                          |

|             | ATTENUATOR WITH IMPROVED FLATNESS AND                           |

|             | ATTENUATION RANGE                                               |

|             |                                                                 |

|             | s of Conventional Attenuators                                   |

| 4.1.1 Pi    | - and T-Attenuator                                              |

| 4.1.2 Di    | stributed Attenuator                                            |

| 4.2 Propose | d Attenuator Architecture                                       |

| 4.2.1 At    | tenuator Topology for Improved Attenuation Flatness and Range   |

|             | ody-Floating Technique for Improved Attenuation Flatness and    |

|             | ansmission Performance                                          |

|             | ual-Function of Attenuating and Switching                       |

|             | stributed Attenuator Design                                     |

|             | ed and Measured Results                                         |

|             | ion                                                             |

|             | ces                                                             |

| 4.0 Referen |                                                                 |

| CHAPTER V   | CMOS HIGH-ISOLATION SPDT SWITCH WITH                            |

|             | BAND-PASS-FILTER RESPONSE                                       |

|             |                                                                 |

| 5.1 Design  |                                                                 |

| _           | and-pass filter topology for high-isolation SPST switch design  |

|             | gh-isolation SPDT switch with band-pass filtering response      |

|             | ion                                                             |

|             | ces                                                             |

| 3.3 Referen |                                                                 |

| CHAPTER VI  | DESIGN OF CMOS PHASE SHIFTERS WITH SMALL                        |

| CHAITER VI  | INSERTION-LOSS VARIATION FOR PHASED ARRAYS                      |

|             | AND ITS VALIDATION AT 24 GHZ                                    |

|             | AND ITS VALIDATION AT 24 UTZ                                    |

| 6.1 Phase S | hifter Design                                                   |

|             | ody-Floating Technique on Phase Shifter Design                  |

| 6.1.2 Optimization of Transistor's Size                            |

|--------------------------------------------------------------------|

| 6.1.3 Design of a 4-Bit Phase Shifter with Body-Floating Technique |

| 6.2 Conclusion                                                     |

| 6.3 References                                                     |

| CHAPTER VII 57–64 GHZ CMOS 4-BIT PHASE SHIFTER WITH SMALL          |

| INSERTION-LOSS VARIATION                                           |

| 7.1 Design, Simulation, and Measurement                            |

| 7.2 Conclusion                                                     |

| CHAPTER VIII DC-TO-67 GHZ HIGH-SPEED BICMOS BJT                    |

| CHARACTERIZATION WITH ON-WAFER CALIBRATION                         |

| AND EM-BASED DE-EMBEDDING                                          |

| 8.1 On-Wafer Calibration and EM-based De-embedding                 |

| 8.1.1 On-wafer Calibration Structures and Issues                   |

| 8.1.2 EM-based De-Embedding Procedure                              |

| 8.2 Simulated and Measured Results                                 |

| 8.3 Conclusion                                                     |

| 8.4 References                                                     |

| CHAPTER IX 24/60-GHZ CONCURRENT DUAL-BAND                          |

| POWER AMPLIFIER                                                    |

| 9.1 Concurrent Dual-Band Power Amplifier                           |

| 9.1.1 Proposed Topology and Design Challenge                       |

| 9.1.2 Three-Tone Test for Concurrent Dual-Band Power Amplifier     |

| 9.1.3 Cascaded PA with Three-Tone Test and Significant IM Products |

| 9.1.4 Concurrent Dual-Band Power Amplifier Design & Simulation     |

| 9.2 Conclusion                                                     |

| 9.3 References                                                     |

| CHAPTER X 24/60-GHZ DUAL-BAND 8-WAY DIVIDER                        |

| 10.1 Dual-Band Power Divider Design and Simulations                |

| APPENDIX A  | 44-GHZ CMOS RFIC DUAL-FUNCTION ATTENUATOR WITH BAND-PASS-FILTER RESPONSE              |

|-------------|---------------------------------------------------------------------------------------|

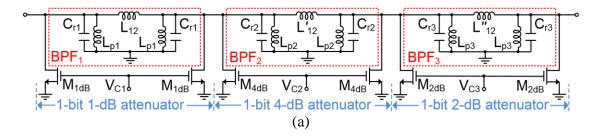

| A.1 Circuit | Design                                                                                |

|             | esign Formulas                                                                        |

|             | esign of 3-bit CMOS Dual-Function Band-Pass Attenuator                                |

|             | sion                                                                                  |

| A.3 Referen | ces                                                                                   |

| APPENDIX B  | NEW DUAL-BAND BAND-PASS FILTER DESIGN WITH                                            |

|             | ENHANCED DUAL-BAND SKIRT CHARACTERISTICS                                              |

|             | Theory                                                                                |

|             | onventional Frequency Transformation Methodoposed Frequency Transformation Method and |

| D           | ual-Band BPF Design                                                                   |

| B.2 Simulat | ion and Measurement                                                                   |

| B.3 Conclus | ion                                                                                   |

| B.4 Referen | ces                                                                                   |

| APPENDIX C  | 44/60-GHZ CONCURRENT DUAL-BAND 0.18-μm                                                |

|             | BICMOS POWER AMPLIFIER                                                                |

| C.1 Circuit | Design                                                                                |

| C.2 Perform | ance                                                                                  |

| C.3 Conclus | ion                                                                                   |

| C.4 Referen | ces                                                                                   |

| APPENDIX D  | 44/60 GHZ DUAL-BAND 0.18-μm CMOS PHASE SHIFTER                                        |

|             | Design                                                                                |

| D.2 Perform | ance                                                                                  |

| D.3 Conclus | sion                                                                                  |

| D / Referen | CAS                                                                                   |

# LIST OF FIGURES

| FIC | FIGURE |                                                                                                                                                                                     | Page |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     | 1.1    | Silicon-based millimeter-wave RFIC single-chip-solution and its applications                                                                                                        | 2    |

|     | 1.2    | Cross section of SiGe BiCMOS containing nMOS and pMOS FETs, and SiGe NPN and PNP BJTs                                                                                               | 4    |

|     | 1.3    | Phased-array transmitter and its high-gain beam                                                                                                                                     | 5    |

|     | 1.4    | 7-channel phased-array transmitter and beam steering                                                                                                                                | 7    |

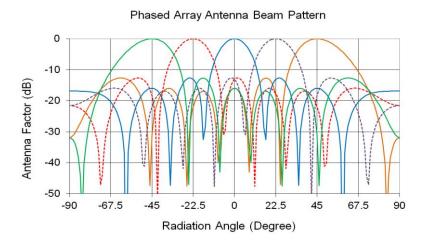

|     | 1.5    | Antenna factor of the steered beam with the varied phases, $\phi_{1\sim7}$                                                                                                          | 7    |

|     | 1.6    | (a) Phase shifting and array antenna spacing of the 24-GHz 7-channel phased-array transmitter for the 26° steering direction, and (b) its array factors showing 52° steering range. | 9    |

|     | 1.7    | 7-channel phased-array transmitter and beam tailored                                                                                                                                | 10   |

|     | 1.8    | Antenna factor of the tailored beam with varied amplitudes, $A_{1\sim7}$                                                                                                            | 10   |

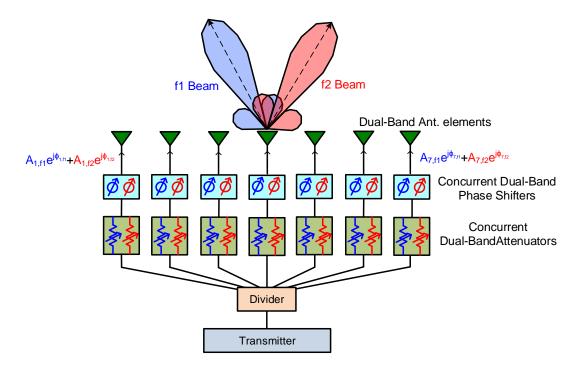

|     | 1.9    | 7-channel concurrent dual-band phased-array transmitter with dual independent beams                                                                                                 | 11   |

|     | 1.10   | Concurrent dual-band phased-array automotive radar with independent beams                                                                                                           | 12   |

|     | 1.11   | (a) Conventional and (b) proposed concurrent dual-band transmitter                                                                                                                  | 13   |

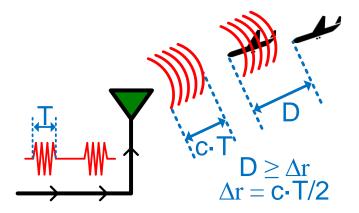

|     | 1.12   | Radar range resolution $(\Delta r)$ to discriminate the objects close to each other                                                                                                 | 14   |

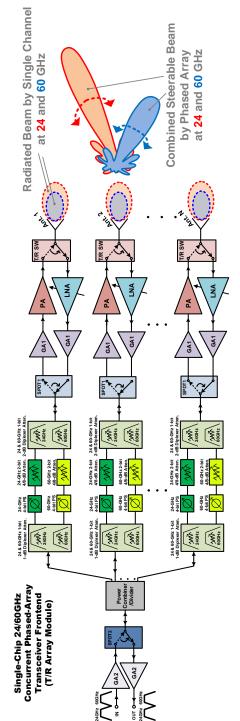

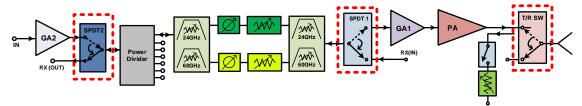

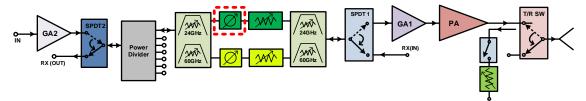

|     | 2.1    | 24/60-GHz concurrent dual-band phased-array transceiver                                                                                                                             | 17   |

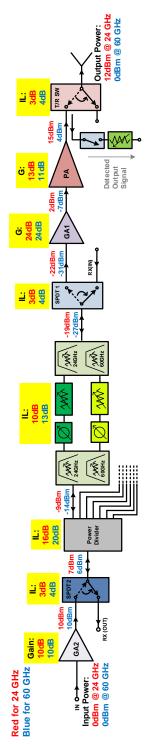

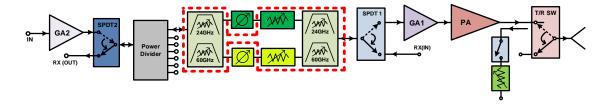

|     | 2.2    | 24/60-GHz concurrent dual-band phased-array transmitter and its estimated input/output power                                                                                        | 17   |

|     | 3.1    | Concurrent dual-band attenuator in the phased-array transmitter (in the dotted boxes)                                                                                               | 19   |

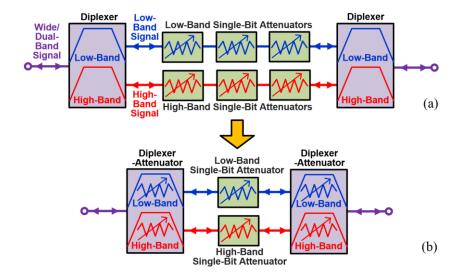

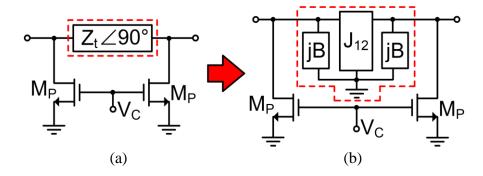

| 3.2  | (a) Conventional concurrent dual-band attenuator realized with separate diplexers and attenuators. (b) Proposed concurrent dual-band attenuator implementing attenuators and integrated diplexer-attenuators having dual functions of diplexer and attenuation | 20 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

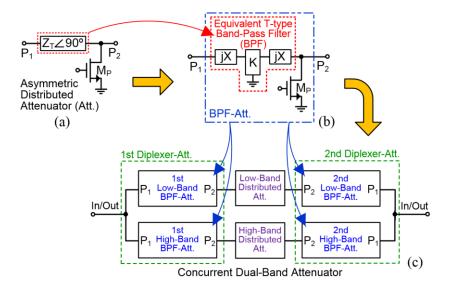

| 3.3  | Design process of the proposed concurrent dual-band attenuator                                                                                                                                                                                                 | 21 |

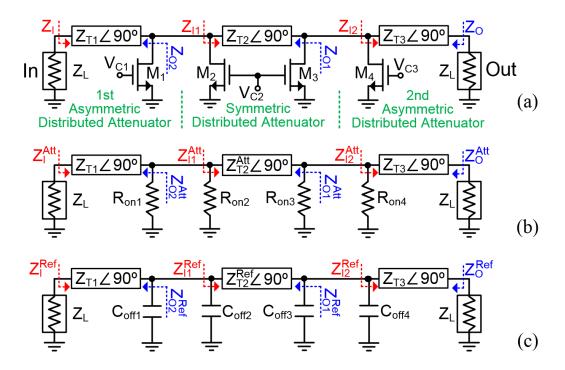

| 3.4  | Core attenuator of the concurrent dual-band attenuator: topology (a) and equivalent circuits at maximum attenuation state (b) and reference state (c)                                                                                                          | 22 |

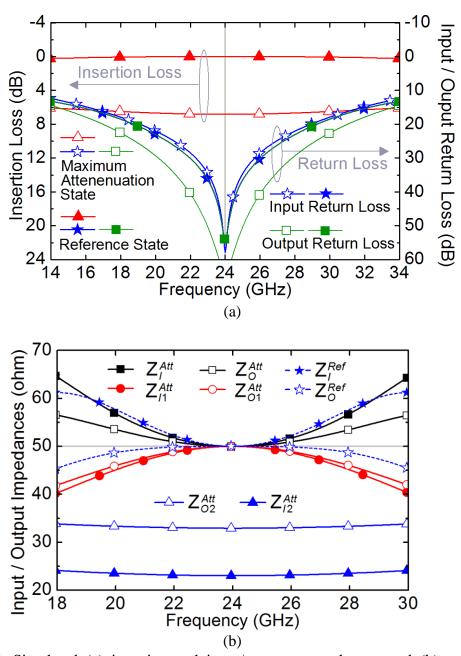

| 3.5  | Simulated (a) insertion and input/output return losses, and (b) constituent attenuators' input/output impedances of the 7-dB step attenuator at the maximum attenuation and reference states                                                                   | 26 |

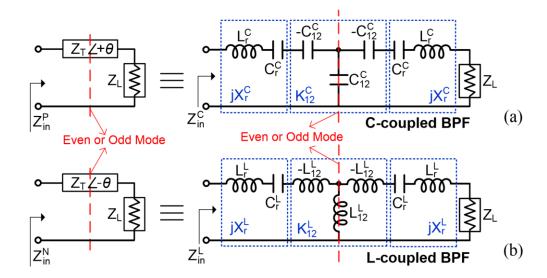

| 3.6  | Equivalences between $\pm\theta$ transmission lines and $2^{nd}$ -order K-inverter BPFs with (a) C-coupled and (b) L-coupled networks                                                                                                                          | 28 |

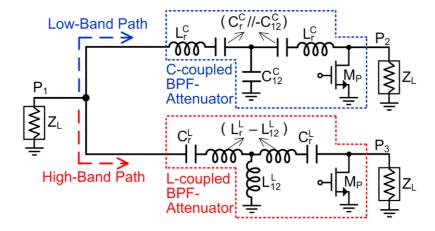

| 3.7  | Integrated diplexer-attenuator consisting of the C- and L-coupled BPF-attenuators constituting the low- and high-band BPF-attenuators, respectively                                                                                                            | 28 |

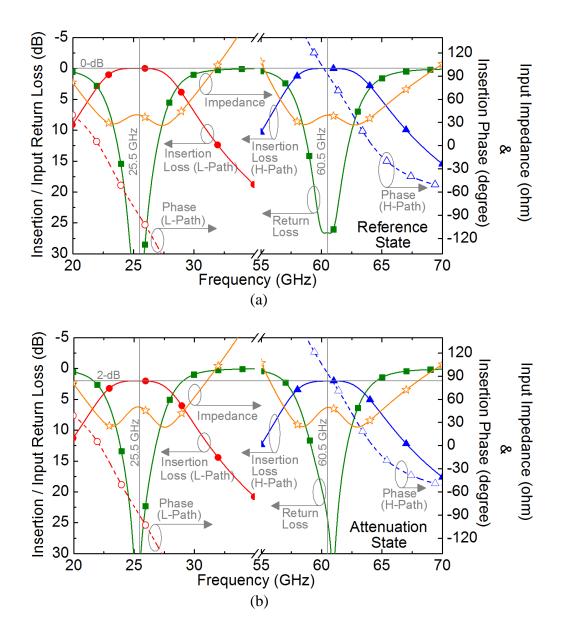

| 3.8  | Simulations of the 2-dB integrated diplexer-attenuator at (a) reference and (b) attenuation states. L-path: low-band path and H-path: high-band path                                                                                                           | 30 |

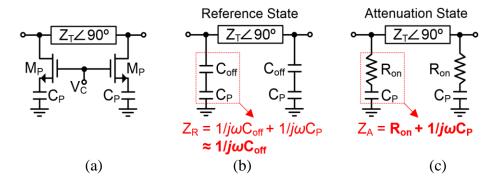

| 3.9  | Low-phase-variation attenuator (a) and its equivalent circuits at reference (b) and attenuation (c) states                                                                                                                                                     | 32 |

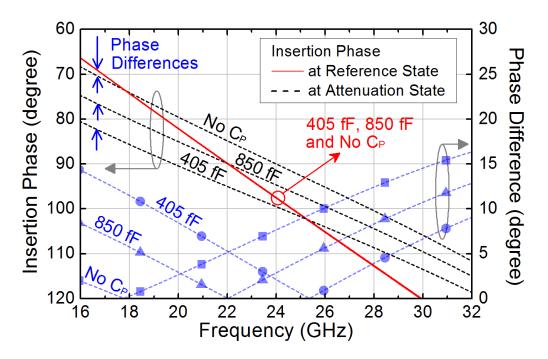

| 3.10 | Simulated (a) insertion phase and (b) phase difference of the low-phase-variation attenuator with $C_P$ of 405- and 850-fF and without $C_P$                                                                                                                   | 33 |

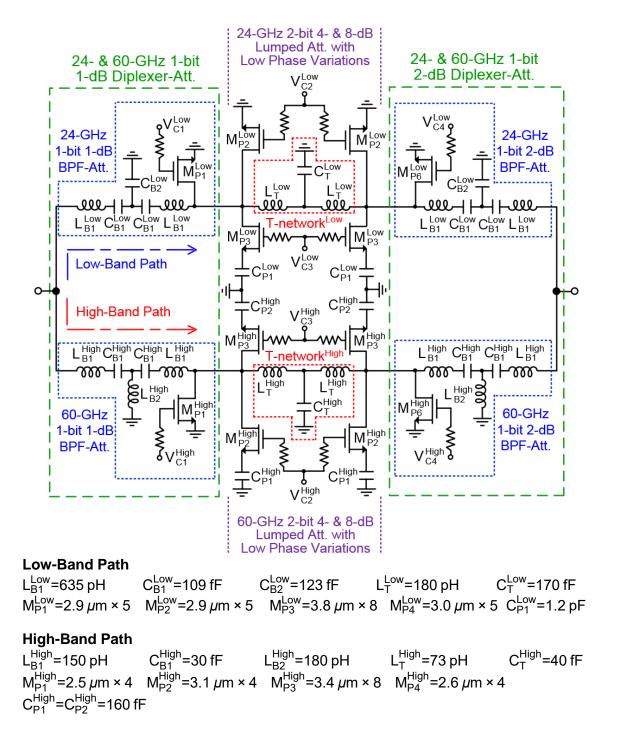

| 3.11 | Schematic of the 4-bit 24/60-GHz concurrent dual-band step attenuator with low phase variations                                                                                                                                                                | 36 |

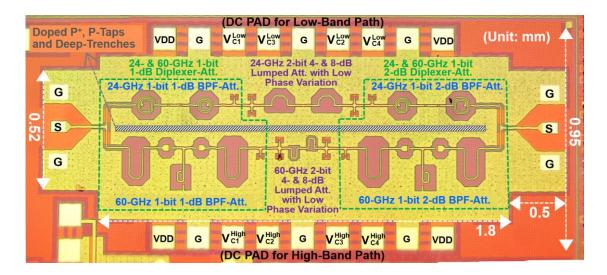

| 3.12 | Micrograph of the 4-bit 24/60-GHz concurrent dual-band step attenuator with low phase variations. Chip size (core part): $1.8 \times 0.52 \text{ mm}^2$                                                                                                        | 37 |

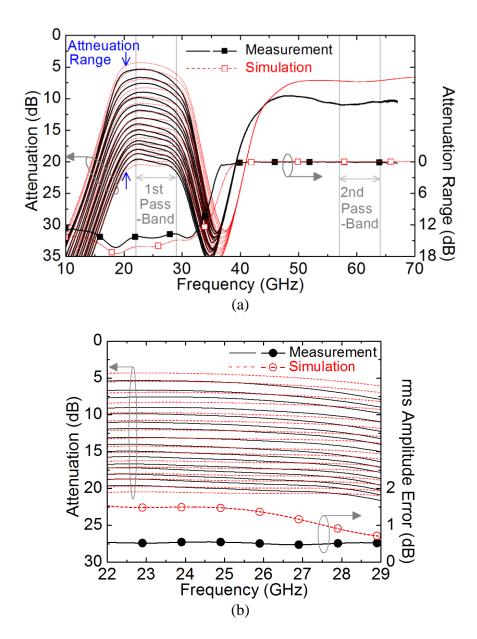

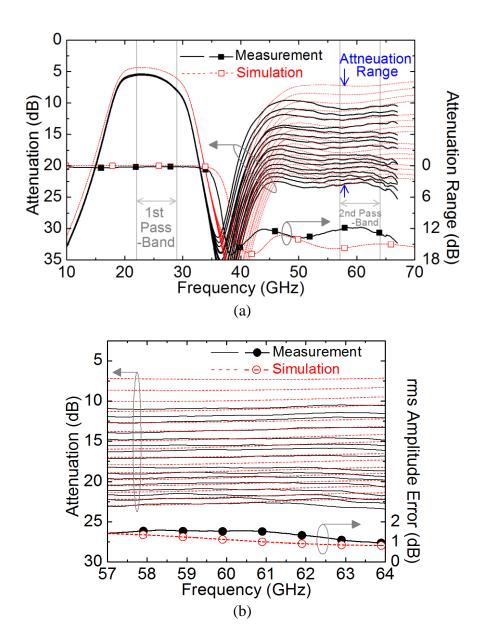

| 3.13 | Simulated and measured (a) attenuation and attenuation range, and (b) zoomed-in attenuation and RMS amplitude error during the 16-state amplitude control in the 1 <sup>st</sup> pass-band                                                                     | 40 |

| 3.14 | Simulated and measured (a) attenuation and attenuation range, and (b) zoomed-in attenuation and RMS amplitude error during the 16-state amplitude control at the 2 <sup>nd</sup> pass-band                                                                     | 41 |

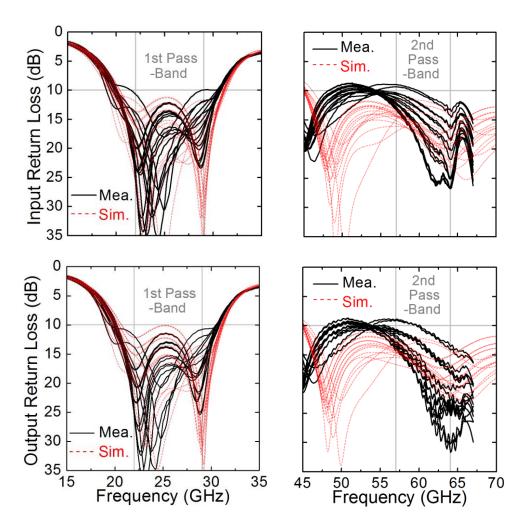

| 3.15 | Simulated and measured input and output return losses corresponding to the plots in Figs. 3.13 and 14                                                                                                                           | 42 |

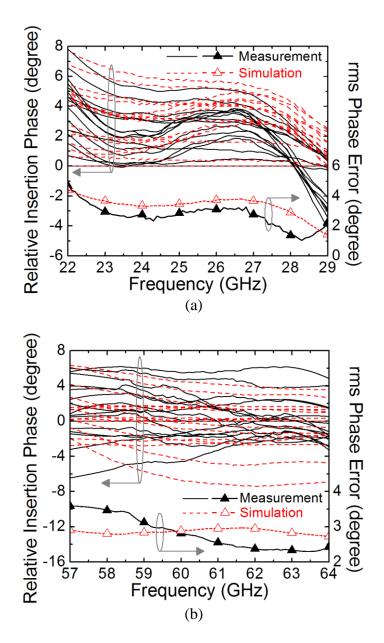

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.16 | Simulated and measured relative insertion phases and RMS phase errors during the 16-state amplitude control in (a) the 1 <sup>st</sup> pass-band and (b) the 2 <sup>nd</sup> pass-band                                          | 43 |

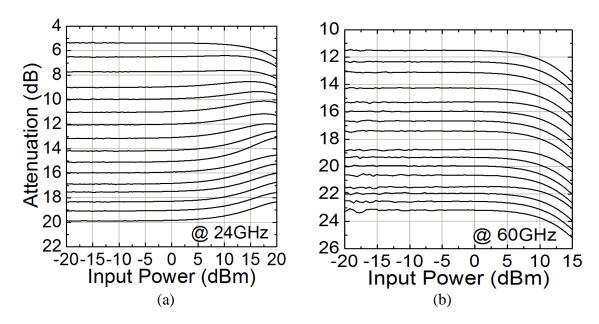

| 3.17 | Measured power handling over 16 states at (a) 24 GHz and (b) 60 GHz                                                                                                                                                             | 44 |

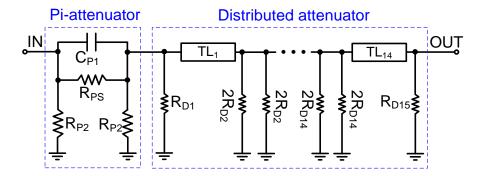

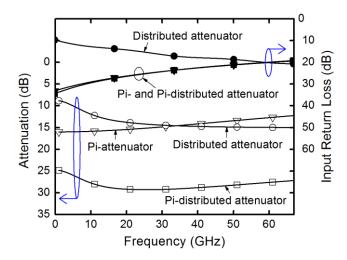

| 4.1  | Wide-band attenuator for the output signal detection in the phased-array transmitter (in the dotted boxes)                                                                                                                      | 50 |

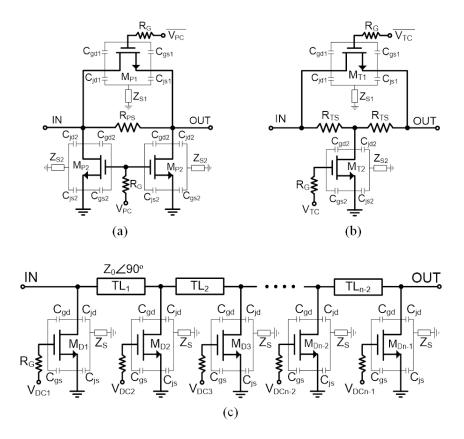

| 4.2  | Conventional attenuator topologies: (a) 1-bit Pi-, (b) 1-bit T-, and (c) n-state distributed attenuators                                                                                                                        | 51 |

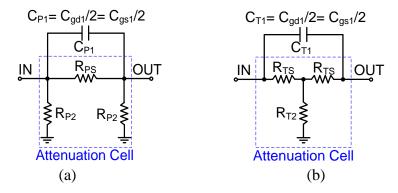

| 4.3  | Equivalent circuits at an attenuation state of the Pi-attenuator (a) and T-attenuator (b)                                                                                                                                       | 53 |

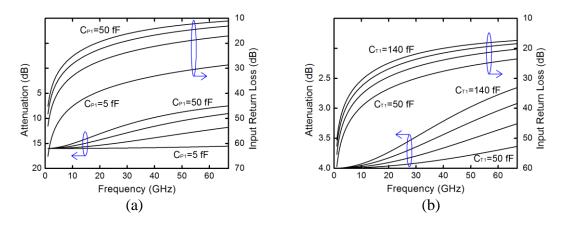

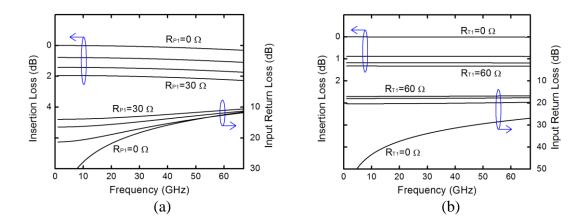

| 4.4  | Attenuation and input return loss of (a) 16-dB Pi-attenuator for $C_{P1}$ from 5 to 50 fF in 15-fF steps and (b) 4-dB T-attenuator for $C_{T1}$ from 50 to 140 fF in 30-fF steps                                                | 53 |

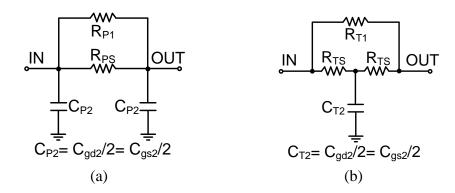

| 4.5  | Equivalent circuits at a reference state of (a) the Pi-attenuator and (b) the T-attenuator                                                                                                                                      | 56 |

| 4.6  | Insertion loss and input return loss at a reference state of (a16-dB Pi-attenuator for $R_{P1}$ from 30 to 0 $\Omega$ in 10- $\Omega$ steps, and (b) 4-dB T-attenuator for $R_{T1}$ from 60 to 0 $\Omega$ in 20- $\Omega$ steps | 56 |

| 4.7  | Equivalent circuit for the highest attenuation state of the n-state distributed attenuator                                                                                                                                      | 59 |

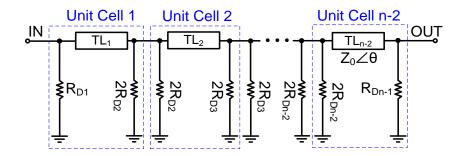

| 4.8  | Attenuation and input return loss at the highest attenuation state of a 4-bit distributed attenuator for transmission-line electrical length $\theta$ at 30 GHz of 90°, 45°, 22.5°, and 11.25°                                  | 59 |

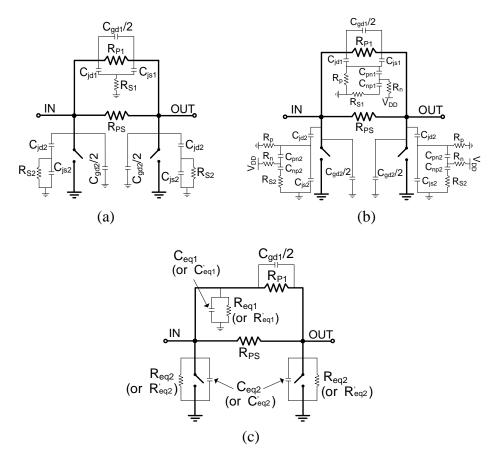

| 4.9  | Equivalent circuit of Pi-distributed attenuator consisting of 1-bit Pi- and 4-bit distributed attenuators at an attenuation state                                                                                               | 61 |

| 4.10 | Attenuations and input return losses of the Pi-distributed attenuator, and Pi- and distributed attenuator constituents                                                                                                          | 61 |

| 4.11 | Equivalent circuits at a reference state of the Pi-attenuator consisting of (a) normal transistors and (b) transistors designed by body-floating techniqu (c) An approximate equivalent circuit of (a) or (b). $R_{eq1,2}$ and $C_{eq1,2}$ are for |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | normal transistors, while $R'_{eq1,2}$ and $C'_{eq1,2}$ are for body-floated transistors                                                                                                                                                           | 64 |

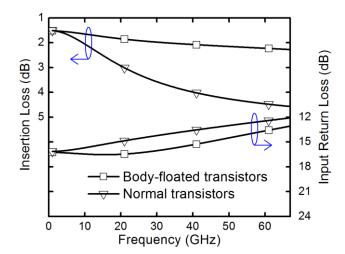

| 4.12 | Simulated insertion loss and return loss at a reference state of the Pi-attenuator with normal and body-floated transistors                                                                                                                        | 66 |

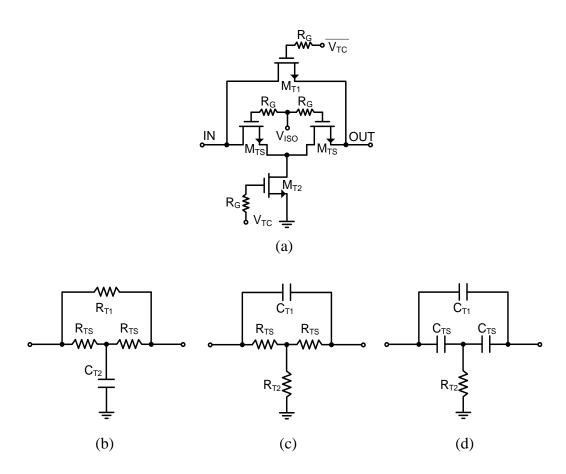

| 4.13 | <ul><li>(a) A switching 1-bit T-attenuator and its equivalent circuit at (a) a reference/switching-on, (b) attenuation, and</li><li>(c) isolation/switching-off state</li></ul>                                                                    | 67 |

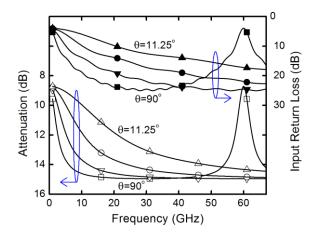

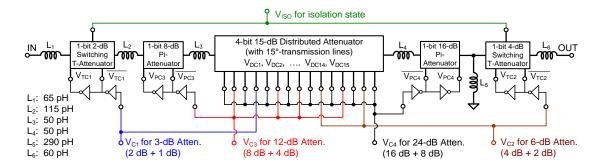

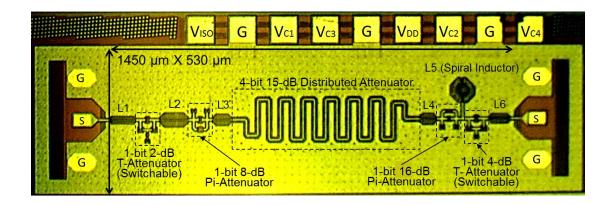

| 4.14 | Diagram of the 4-bit switching Pi/T-distributed attenuator                                                                                                                                                                                         | 68 |

| 4.15 | Micrograph of the 4-bit switching Pi/T-distributed attenuator                                                                                                                                                                                      | 68 |

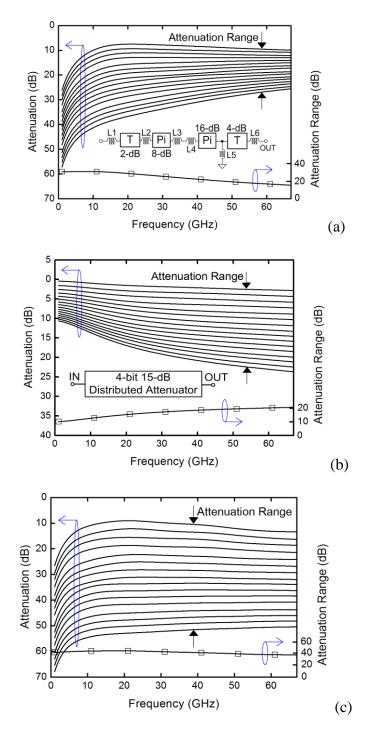

| 4.16 | Simulated attenuation and attenuation range of the combined 4-bit 30-dB Pi- and T-attenuator (a), 4-bit 15-dB distributed attenuator (b), and 4-bit 45-dB switching Pi/T-distributed attenuator (c)                                                | 72 |

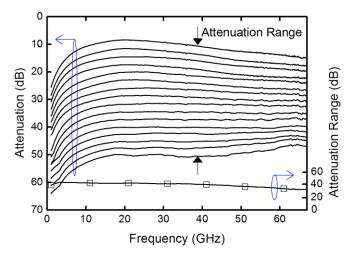

| 4.17 | Measured attenuation and attenuation range of the 4-bit switching Pi/T-distributed attenuator                                                                                                                                                      | 73 |

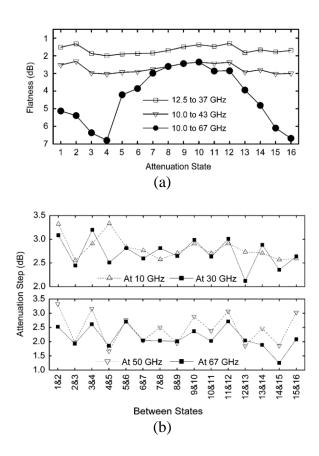

| 4.18 | Measured (a) flatness and (b) attenuation step of the 4-bit switching Pi/T-distributed attenuator                                                                                                                                                  | 75 |

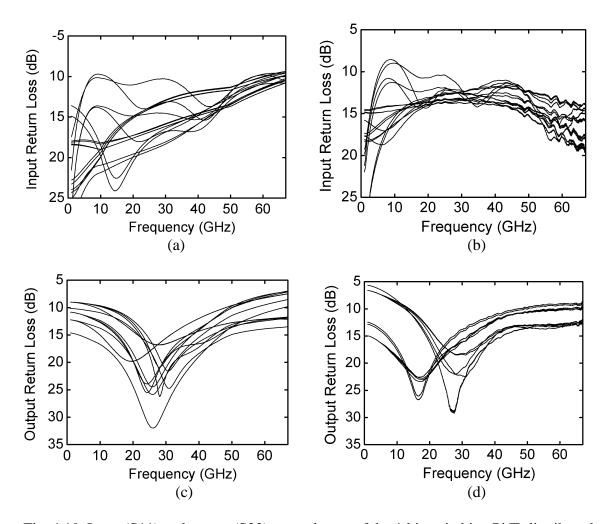

| 4.19 | Input (S11) and output (S22) return losses of the 4-bit switching Pi/T-distributed attenuator: (a) Simulated S11, (b) measured S11, (c) simulated S22, and (d) measured S22.                                                                       | 77 |

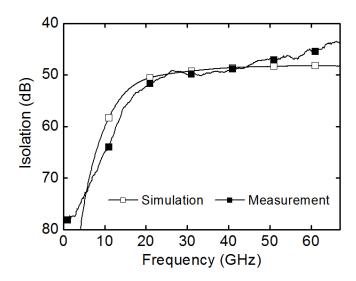

| 4.20 | Simulated and measured isolations of the 4-bit switching Pi/T-distributed attenuator in isolation state                                                                                                                                            | 79 |

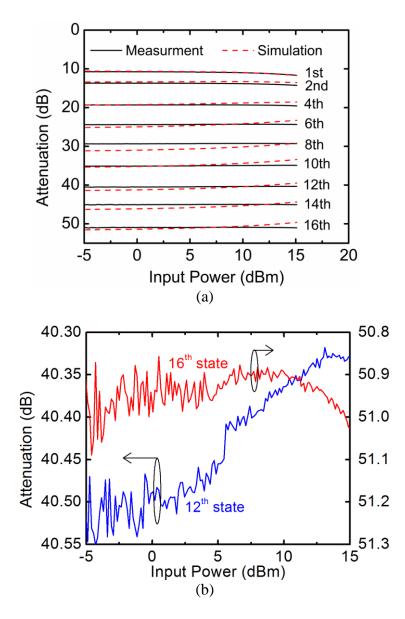

| 4.21 | Simulated and measured power handling for different attenuation states at 40 GHz. (a) and expansion of the measured results for the 12 <sup>th</sup> and 16 <sup>th</sup> attenuation state (b)                                                    | 80 |

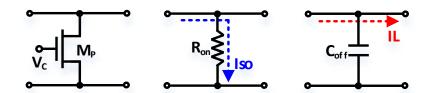

| 5.1  | Switches in the phased-array transmitter (in the dotted boxes)                                                                                                                                                                                     | 87 |

| 5.2  | Shunt RF switch and its switching-off and switching-on states                                                                                                                                                                                      | 87 |

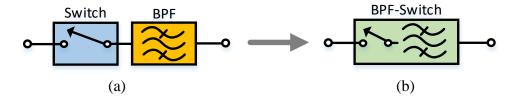

| 5.3  | Band-pass filtering and switching functions realized with  (a) cascaded switch and BPF and (b) switch having dual-function of switching and band-pass filtering                                                                                    | 87 |

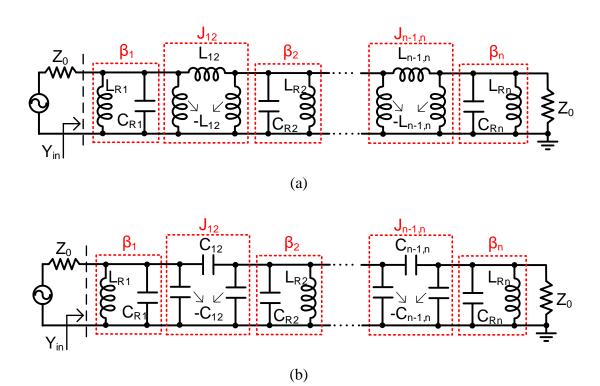

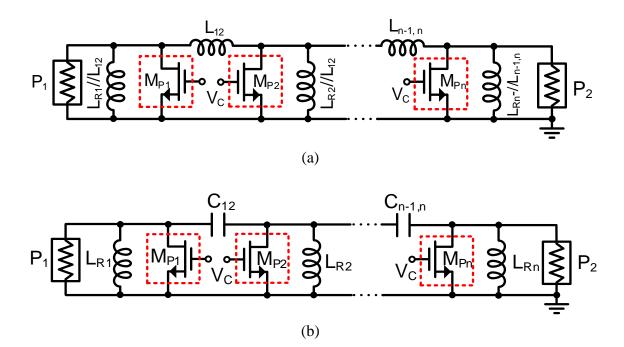

| 5.4 | <i>N</i> -order BPF with (a) inductive and (b) capacitive J-inverter Pi-networks                                                                                                                                                                                                                                                                                                                                                       | 89  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5 | SPST switch with band-pass filtering response whose isolation is increased by reducing the bandwidth                                                                                                                                                                                                                                                                                                                                   | 91  |

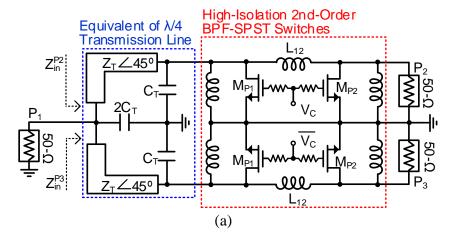

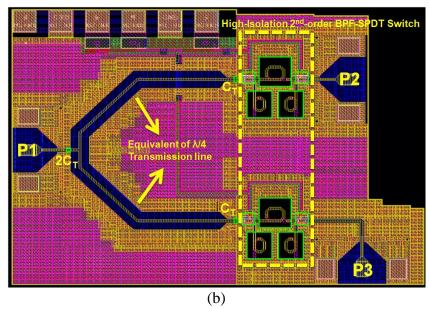

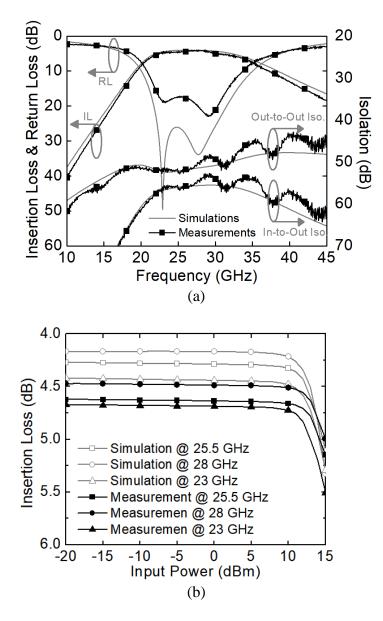

| 5.6 | High-isolation band-pass SPDT switch consisting of equivalents of $\lambda/4$ transmission line and high-isolation band-pass SPST switches: (a) schematic and (b) layout. Chip size (core part): $520\times600~\mu\text{m}^2$                                                                                                                                                                                                          | 92  |

| 5.7 | Simulations and measurements: (a) insertion loss, return loss and isolations, and (b) power handling at 23, 25.5 and 28 GHz                                                                                                                                                                                                                                                                                                            | 93  |

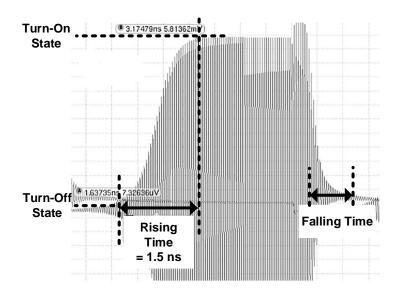

| 5.8 | Simulation of switch rising time (turn-on time)                                                                                                                                                                                                                                                                                                                                                                                        | 94  |

| 6.1 | A24-GHz phase shifter in the phased-array transmitter (in the dotted box)                                                                                                                                                                                                                                                                                                                                                              | 98  |

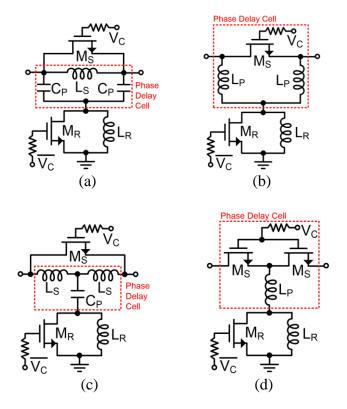

| 6.2 | 1-bit phase shifter topologies based on conventional (a) low-pass Pi-, (b) high-pass Pi-, (c) low-pass T-, and (d) high-pass T-type phase delay networks                                                                                                                                                                                                                                                                               | 98  |

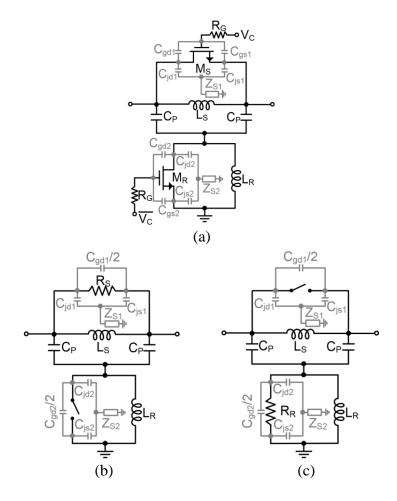

| 6.3 | (a) A 1-bit low-pass Pi-type phase shifter with parasitic elements in nMOS transistors, and its equivalent circuits (b) at bypass and (c) phase delay states                                                                                                                                                                                                                                                                           | 99  |

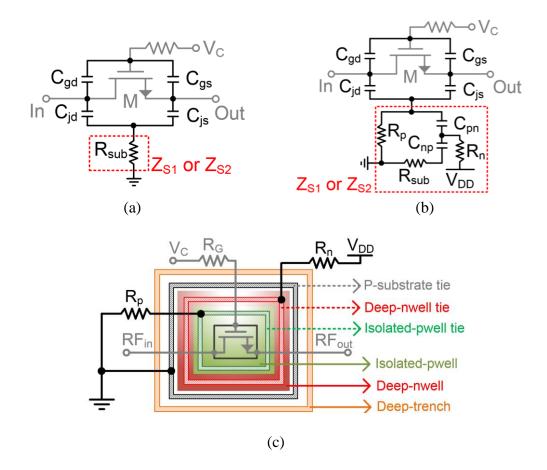

| 6.4 | Parasitic elements in a nMOS transistor (a) without floating body and (b) with floating body, and (c) a top view of the nMOS transistor with floating body. $Z_{S1}$ and $Z_{S2}$ are shown in Fig. 6.3                                                                                                                                                                                                                                | 101 |

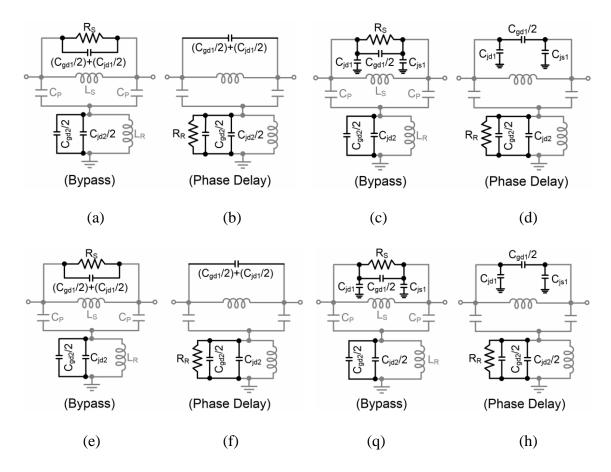

| 6.5 | Simplified equivalent circuits at bypass and phase delay states of the 1-bit low-pass Pi-type phase shifter in Fig. 2 consisting of: series and shunt transistors with floating body (a, b), series and shunt transistors without floating body (c, d), series transistor with floating body and shunt transistor without floating body (e, f), series transistor without floating body and shunt transistor with floating body (g, h) | 103 |

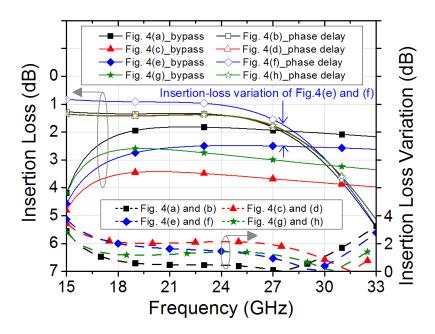

| 6.6 | Simulated insertion losses and insertion-loss variations of a 1-bit phase shifter based on the equivalent circuits in Fig. 4                                                                                                                                                                                                                                                                                                           | 104 |

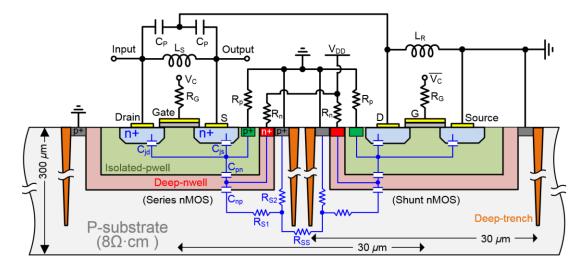

| 6.7 | A cross-section of a low-pass Pi-type 1-bit phase shifter with a deep-nwell body-floating technique.  The transistors are simplified with a single-finger gate                                                                                                                                                                                                                                                                         | 106 |

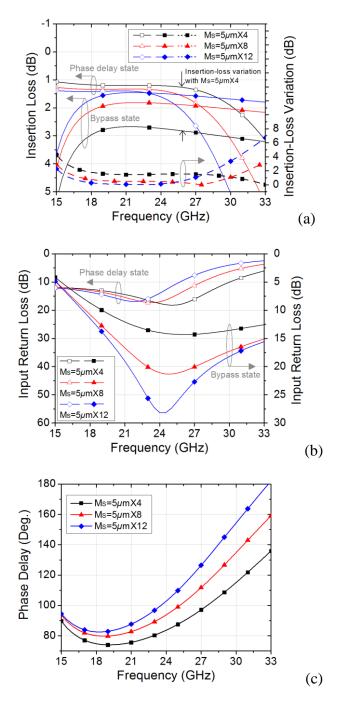

| 6.8  | Simulations of the 90° phase shifter with different $M_S$ (5 $\mu$ m×4, 5 $\mu$ m×8 or 5 $\mu$ m×12) for bypass and phase delay states: (a) insertion loss and insertion-loss variation, (b) input return loss, and (c) phase delay representing the phase difference between the bypass and phase delay states       | 108 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.9  | Simulations of the 90° phase shifter with different $M_R$ (10 $\mu$ m×9, 10 $\mu$ m×12 or 10 $\mu$ m×18) for bypass and phase delay states: (a) insertion loss and insertion-loss variation, (b) input return loss, and (c) phase delay representing the phase difference between the bypass and phase delay states   | 109 |

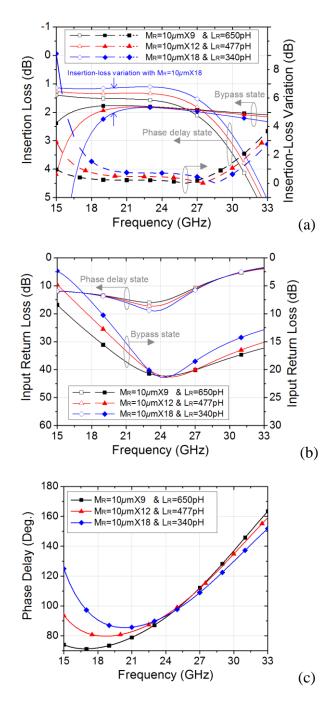

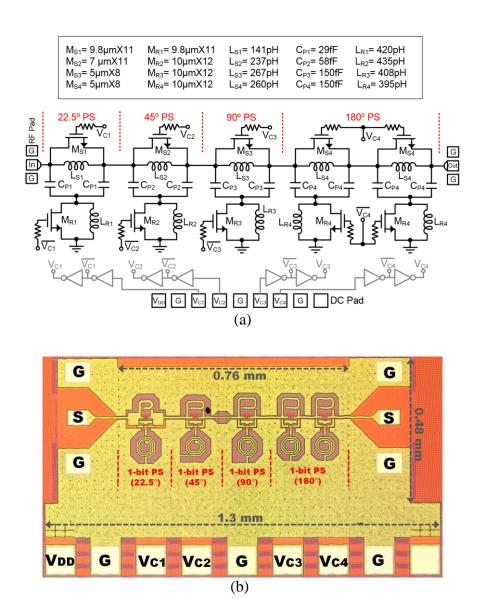

| 6.10 | A 4-bit CMOS digital phase shifter: (a) schematic and (b) microphotograph. Chip size (core part): $760 \times 480 \mu\text{m}^2$                                                                                                                                                                                      | 111 |

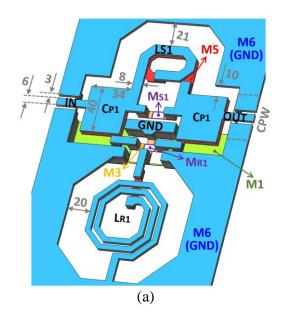

| 6.11 | (a) 3-D view of the 22.5° section in the 4-bit phase shifter and (b) cross-section view of metal and substrate layers. For the metal layers, the same colors are used in (a) and (b). Unit is $\mu$ m                                                                                                                 | 112 |

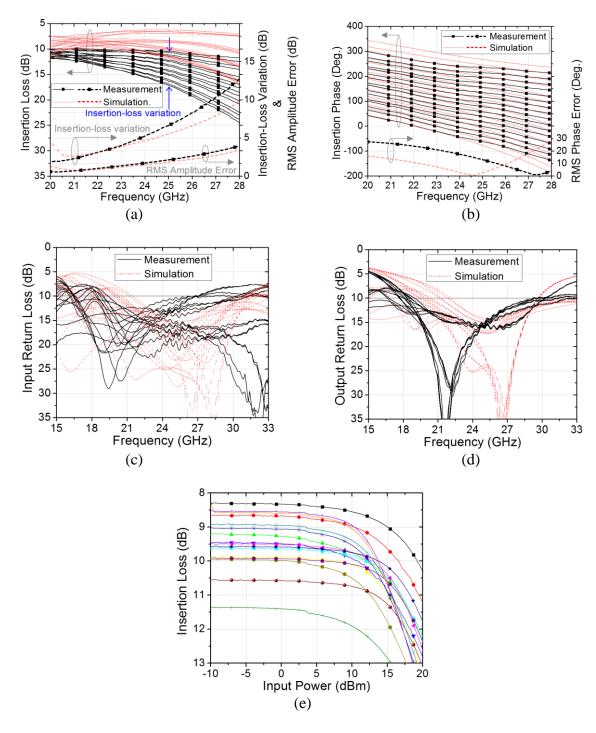

| 6.12 | Simulated and measured (a) insertion loss, insertion-loss variation and RMS amplitude error, (b) insertion phase and RMS phase error, (c) input return loss, (d) output return loss over 16 states of the 4-bit CMOS digital phase shifter. (e) Measured power handling of the phase shifter over 16 states at 24 GHz | 114 |

| 7.1  | A 57–64 GHz phase shifter in the phased-array transmitter (in the dotted box)                                                                                                                                                                                                                                         | 118 |

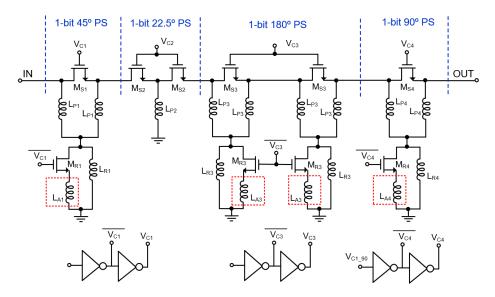

| 7.2  | A proposed 57–64 GHz 4-bit phase shifter topology with additional shunt inductors ( $L_{A1}$ , $L_{A3}$ , and $L_{A4}$ ) designed based on conventional high-pass Pi- and high-pass T-type phase delay networks                                                                                                       | 119 |

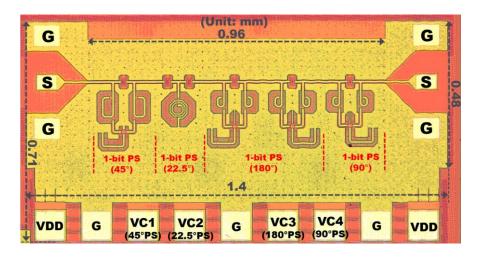

| 7.3  | A microphotograph of the 57–64 GHz 4-bit CMOS digital phase shifter .                                                                                                                                                                                                                                                 | 119 |

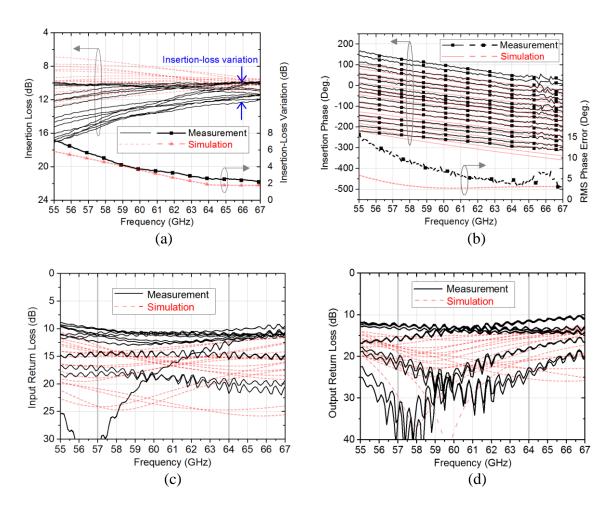

| 7.4  | Simulated and measured (a) insertion loss and insertion-loss variation, (b) insertion phase and RMS phase error, (c) input return loss, (d) output return loss                                                                                                                                                        |     |

|      | over 16 states of the 4-bit CMOS digital phase shifter                                                                                                                                                                                                                                                                | 120 |

| 8.1  | Amplifiers designed with bipolar junction transistors (BJTs) in the phased-array transmitter                                                                                                                                                                                                                          | 122 |

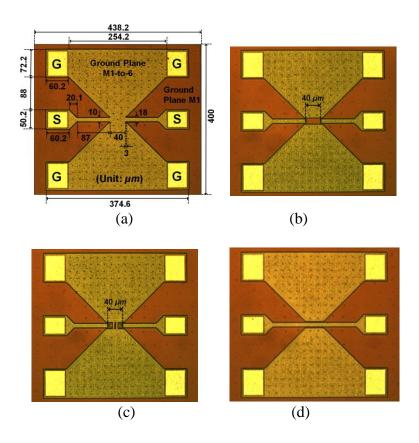

| 8.2  | Photographs of fabricated on-wafer calibration standards: (a) short, (b) open, (c) load, and (d) thru                                                                                                                                                                                                                 | 126 |

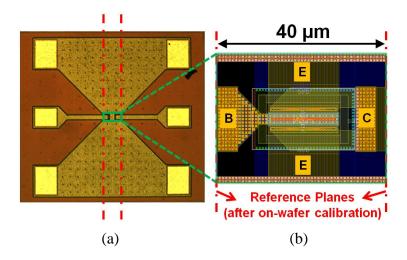

| 8.3  | (a) Photograph of fabricated test structure for BJT1 configured as a common-emitter amplifier and (b) zoomed view showing the layout of the extra interconnects for the base (B), collector (C) and emitter (E) within the 40-µm gap | 128 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

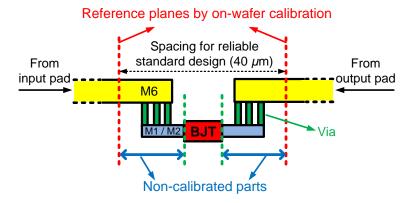

| 8.4  | A simplified cross-sectional view of the BJT-test structure showing the reference planes by the on-wafer calibration and the non-calibrated parts                                                                                    | 129 |

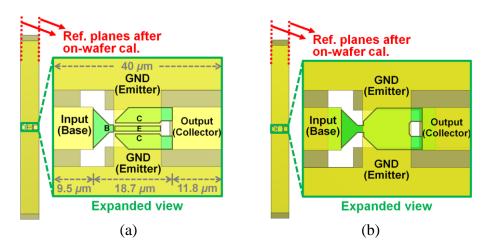

| 8.5  | Layouts of open (a) and short (b) dummies used in EM-simulations for BJT1 de-embedding and their expanded views. The dimensions for the short dummy are the same as those for the open dummy                                         | 130 |

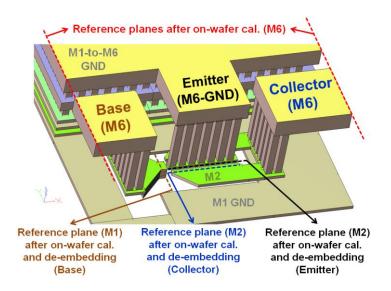

| 8.6  | 3-D view of the open dummy for BJT1 characterization. For better visibility, only one emitter connection and ground plane are shown                                                                                                  | 131 |

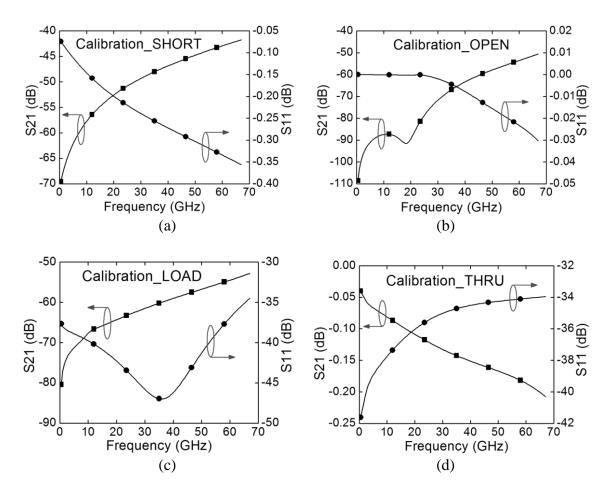

| 8.7  | EM-simulated results of the on-wafer calibration standards: short (a), open (b), load (c), and thru (d)                                                                                                                              | 132 |

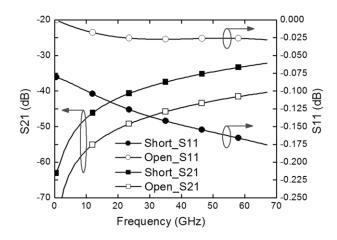

| 8.8  | EM-simulated results of the de-embedding dummies for BJT1: open (a) and short (b)                                                                                                                                                    | 133 |

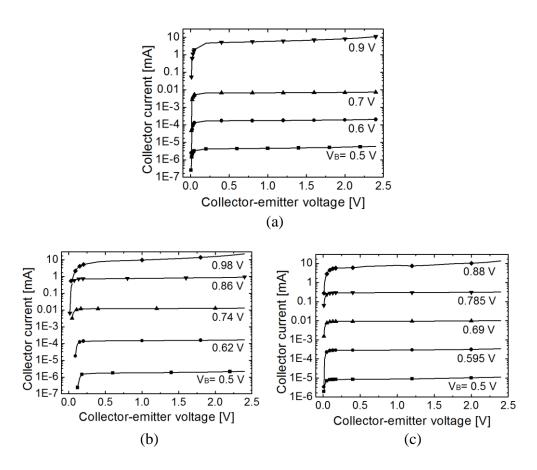

| 8.9  | Measured I-V curves of (a) BJT1, (b) BJT2 and (c) BJT3                                                                                                                                                                               | 134 |

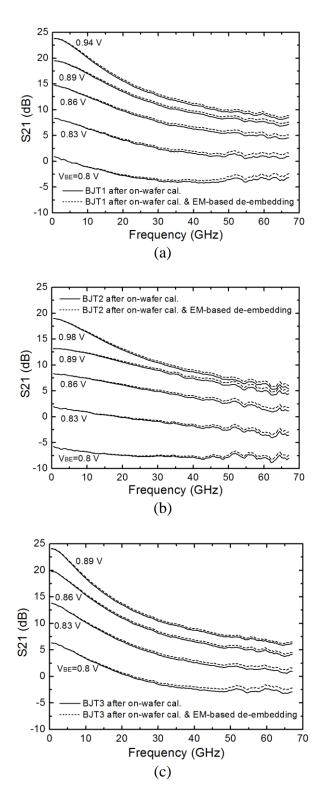

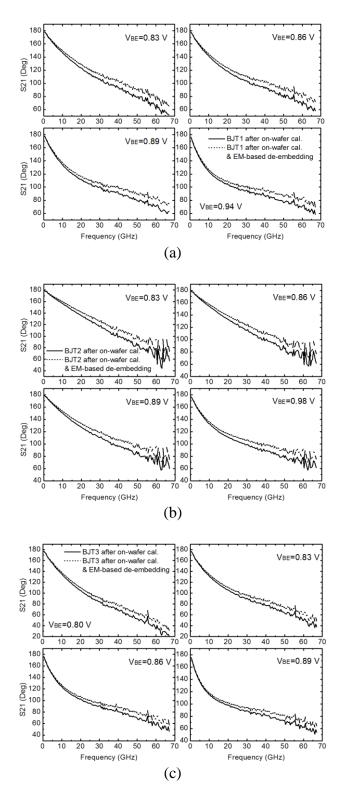

| 8.10 | Measured S21 magnitude versus frequency of (a) BJT1, (b) BJT2 and (c) BJT3 for different $V_{BE}$                                                                                                                                    | 135 |

| 8.11 | Measured S21 phase versus frequency of (a) BJT1, (b) BJT2 and (c) BJT3 for different $V_{BE}$                                                                                                                                        | 136 |

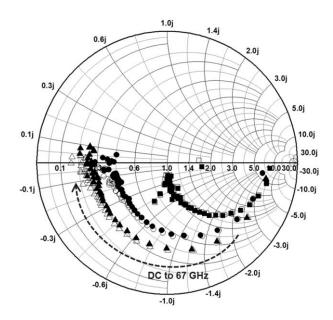

| 8.12 | Measured input reflection coefficients for BJT1, BJT2, and BJT3. Filled and non-filled symbols show results after on-wafer cal. and after on-wafer cal. and EM-based de-embedding, respectively.                                     |     |

|      | $lue{}$ $\bigcirc$ BJT1 at $V_{BE}$ =0.94 V; $\blacksquare$ $\Box$ BJT2 at $V_{BE}$ =0.98 V;                                                                                                                                         |     |

|      | $\triangle$ BJT3 at $V_{BE}$ =0.89 V                                                                                                                                                                                                 | 137 |

| 9.1  | Power amplifier in the phased-array transmitter (in the dotted box)                                                                                                                                                                  | 141 |

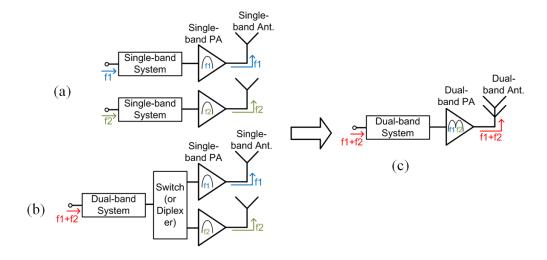

| 9.2  | Conventional (a) multi-path and (b) selectable/diplexing dual-band transmitters (c) Proposed concurrent dual-band transmitter                                                                                                        | 141 |

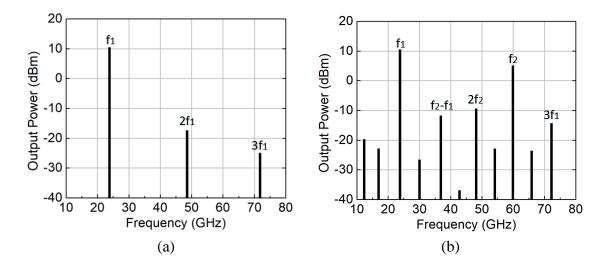

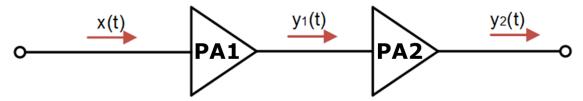

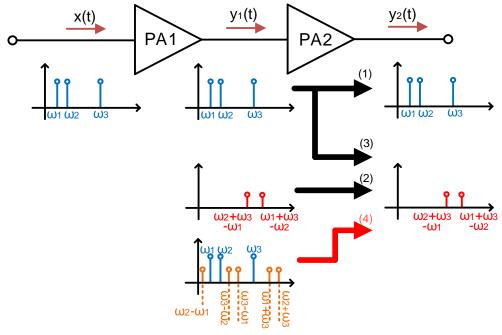

| 9.3  | (a) Harmonics by the single main tone at $f_1$ in a conventional single-band PA, and (b) IM products and harmonics caused by the dual main tones at $f_1$ and $f_2$ in the concurrent dual-band PA | 142 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

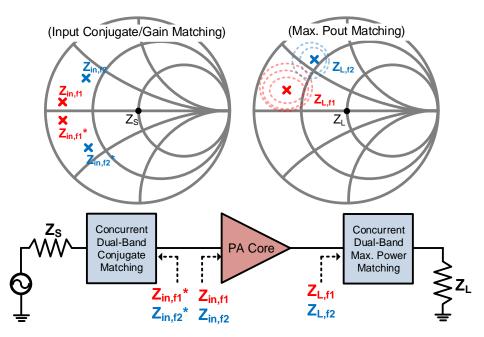

| 9.4  | Dual-point Input/output matching in a concurrent dual-band PA design                                                                                                                               | 143 |

| 9.5  | Nonlinear amplifier with the three-tone injected signal                                                                                                                                            | 144 |

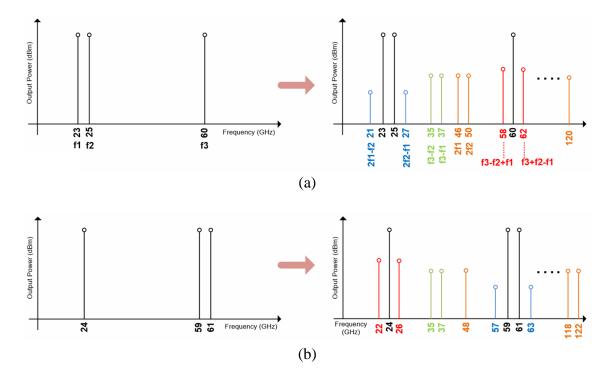

| 9.6  | The three tones injected (a) at 23, 25 and 60 GHz and (b) 24, 59, and 61 GHz, and their IMD products and harmonics                                                                                 | 144 |

| 9.7  | Cascaded 2-stage PA with the three-tone input signal                                                                                                                                               | 145 |

| 9.8  | Intermodulation mechanisms in cascade of two PAs with a three-tone input injection                                                                                                                 | 147 |

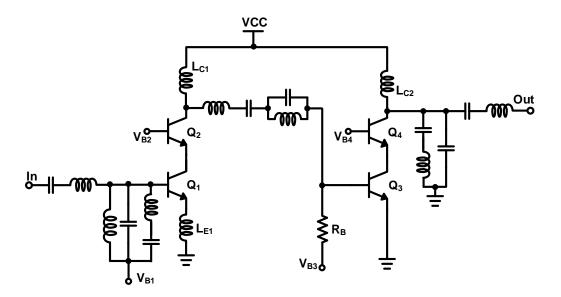

| 9.9  | 24/60-GHz concurrent dual-band 2-stage PA for low IM3 products                                                                                                                                     | 148 |

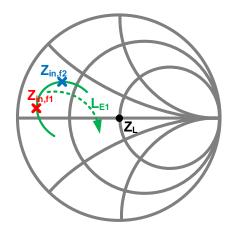

| 9.10 | Input matching with an inductive degeneration $(L_{El})$                                                                                                                                           | 149 |

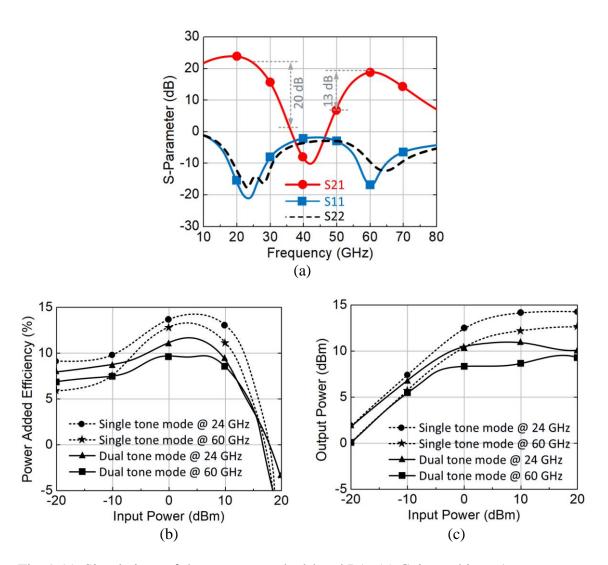

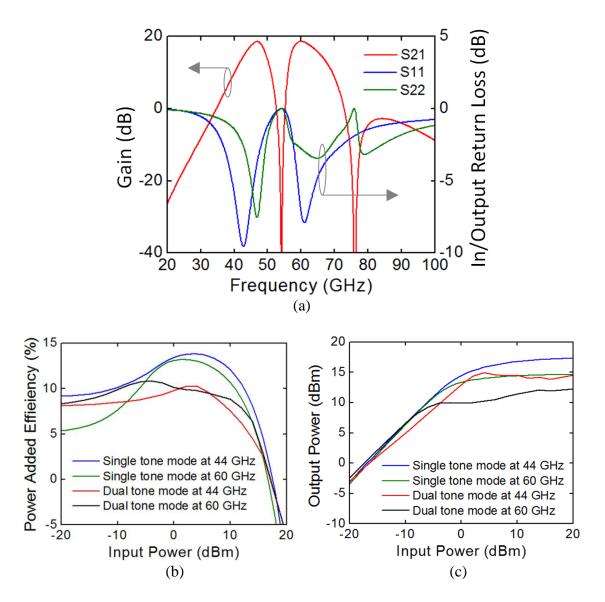

| 9.11 | Simulations of the concurrent dual-band PA: (a) Gain, and input/output return loss, (b) power added efficiency, and (c) output P1dB for the single- and dual-tone modes                            | 150 |

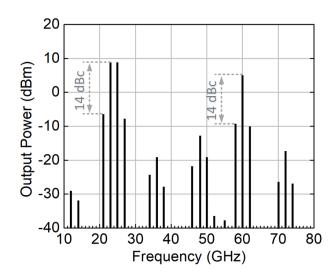

| 9.12 | Frequency specturm by the three-tone test with -15, -15, and -13-dBm inputs at 23, 25 and 60 GHz, respectively                                                                                     | 151 |

| 10.1 | 8-way power divider in the phased-array transmitter (in the dotted box)                                                                                                                            | 155 |

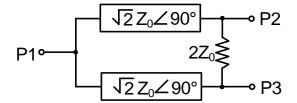

| 10.2 | Conventional Wilkinson power divider                                                                                                                                                               | 155 |

| 10.3 | Transmission line and its equivalent pi-type network                                                                                                                                               | 155 |

| 10.4 | Shunt susceptance and its equivalent LC resonator                                                                                                                                                  | 155 |

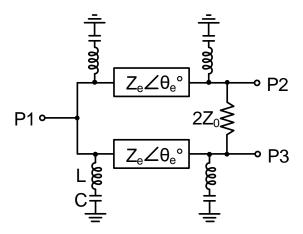

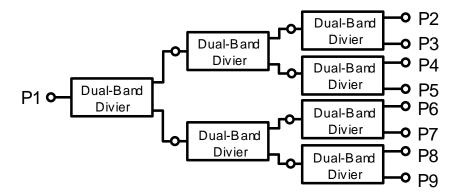

| 10.5 | Dual-band divider with equivalent transmission lines and resonators                                                                                                                                | 156 |

| 10.6 | 8-way dual-band divider consisting of the divider in Fig. 10.5                                                                                                                                     | 156 |

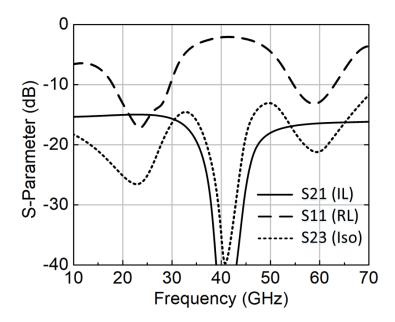

| 10.7 | Simulations of the 8-way dual-band divider in Fig. 10.6                                                                                                                                            | 157 |

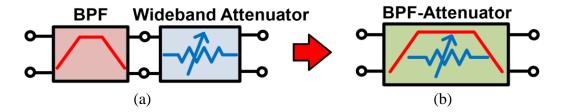

| A.1 | Band-pass filtering and attenuating responses realized with  (a) cascaded BPF and attenuator and (b) attenuator having dual-function of attenuation and band-pass filtering                                                                                             | 159      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

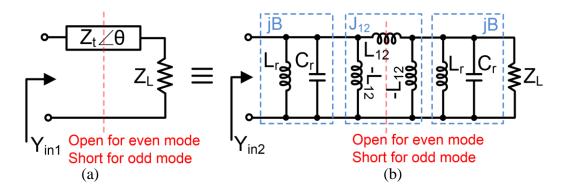

| A.2 | Attenuator employing (a) a quarter-wavelength line and (b) a 2 <sup>nd</sup> -order J-inverter BPF (shown inside the dashed boxes)                                                                                                                                      | 159      |

| A.3 | Equivalence between (a) a transmission line and (b) a 2 <sup>nd</sup> -order J-inverter BPF                                                                                                                                                                             | 161      |

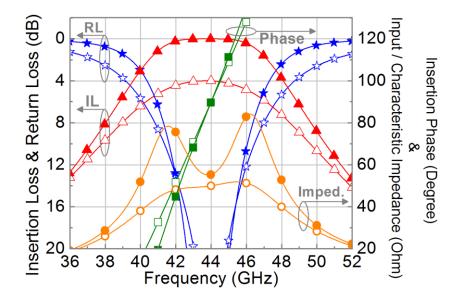

| A.4 | Simulation results for the constituent BPF (filled symbol) and 1-bit 4-dB dual-function band-pass attenuator (non-filled symbol). Input impedance: $Z_{in2}$ . Characteristic impedance: $Z_t$                                                                          | 161      |

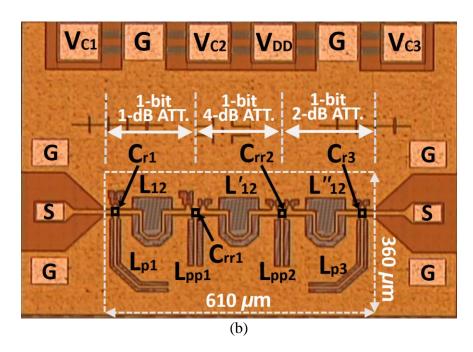

| A.5 | 3-bit CMOS dual-function band-pass step attenuator: (a) schematic and (b) microphotograph. Chip size (core part): $610 \times 360  \mu \text{m}^2$                                                                                                                      | 164      |

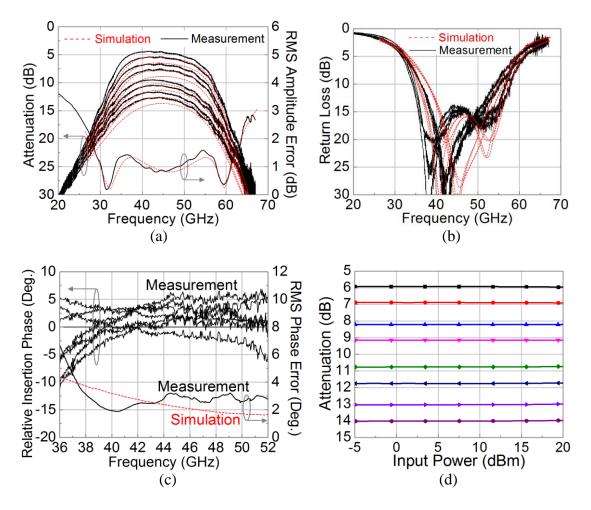

| A.6 | Simulated and measured (a) insertion loss and RMS attenuation error, (b) return loss, and (c) relative insertion phase and RMS phase error over 8 states of the 3-bit CMOS dual-function band-pass step attenuator. (d) Measured power handling over 8 states at 44 GHz | 165      |

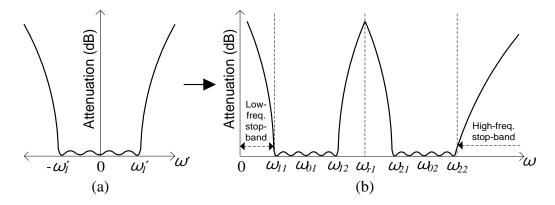

| B.1 | Frequency transformation from a low-pass response (a) to a dual band-pas response (b), leading to poor skirt selectivity at the high-frequency stop-band                                                                                                                | s<br>172 |

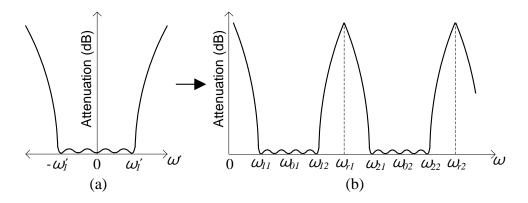

| B.2 | Proposed frequency transformation from a low-pass response (a) to a dual band-pass response (b) with a frequency parameter ( $\omega_{r2}$ ) added for improved symmetrical stop-band response                                                                          | 172      |

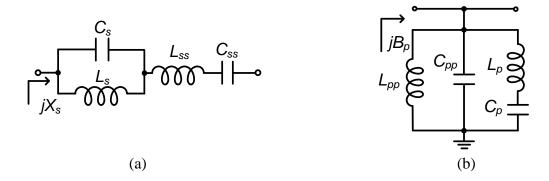

| B.3 | (a) Series and (b) shunt resonators for realizing the conventional frequency transformation technique and used in the conventional dual-band BPF design                                                                                                                 |          |

| B.4 | (a) Series and (b) shunt resonators for realizing the proposed frequency transformation technique and used in the proposed dual-band BPF                                                                                                                                | 174      |

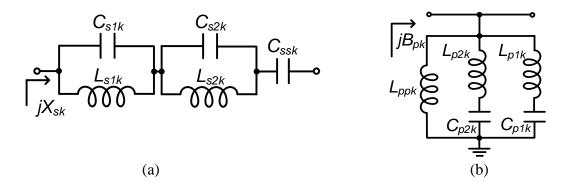

| B.5 | Proposed five-element dual-band BPF                                                                                                                                                                                                                                     | 175      |

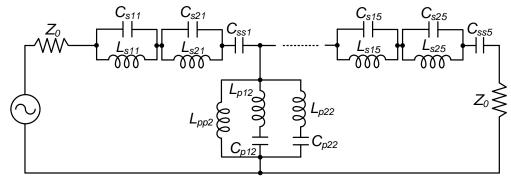

| B.6 | Simulated insertion loss and return loss of the proposed dual-band BPF                                                                                                                                                                                                  | 177      |

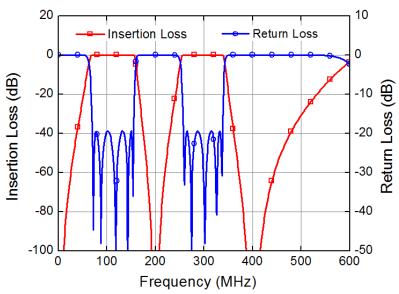

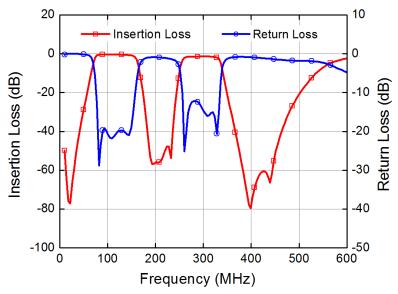

| B.7 | Measured insertion loss and return loss of the proposed dual-band BPF                                                                                                                                                                                                   | 177      |

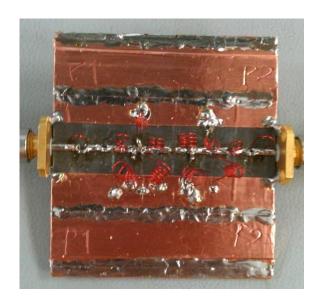

| R & | Photograph of the proposed dual-hand RPF                                                                                                                                                                                                                                | 178      |

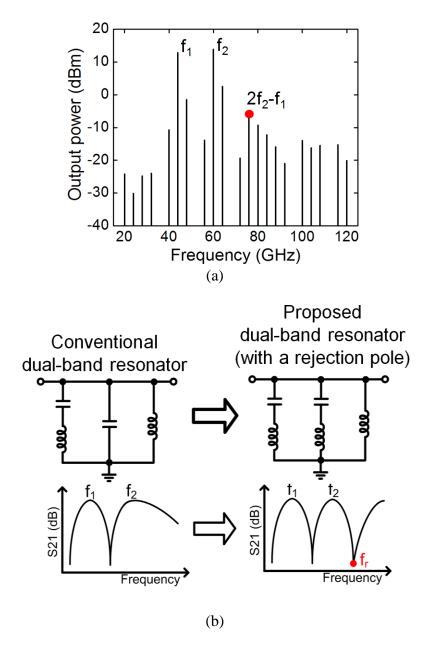

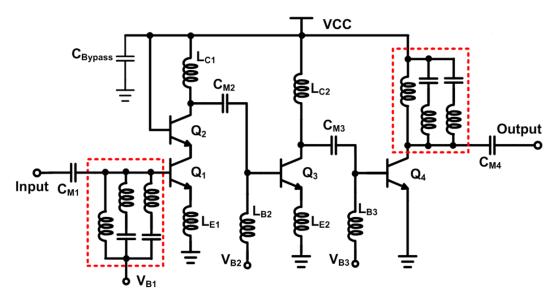

| C.1 | (a) IM products and harmonics caused by the dual main tones at $f_1$ and $f_2$ in the concurrent dual-band PA. (b) Conventinoal dual-passband and proposed dual-passband and single-stopband resonators                                                                                   | 181        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| C.2 | 3-stage concurrent dual-band PA with the proposed dual-band resonators                                                                                                                                                                                                                    | 182        |

| C.3 | Simulations of the concurrent dual-band PA:  (a) Gain, and input/output return loss, (b) power added efficiency, and (c) output P1dB for the single- and dual-tone modes                                                                                                                  | 183        |

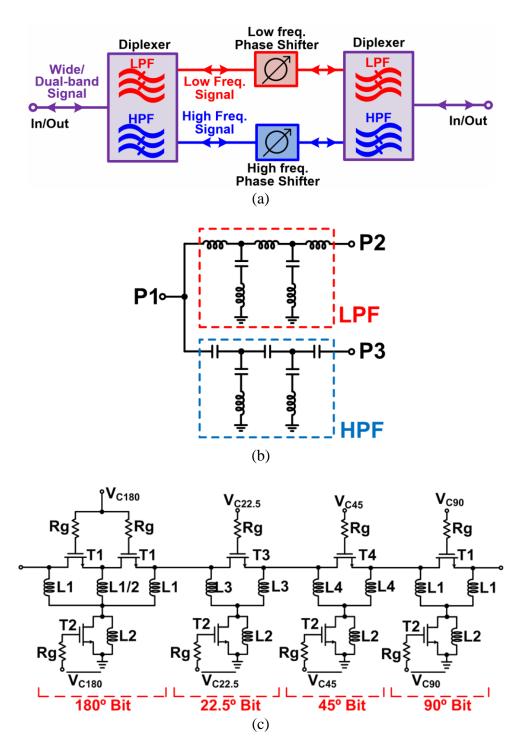

| D.1 | (b) its constituent diplexer consisting of high-pass and low-pass filters, and                                                                                                                                                                                                            | l<br>187   |

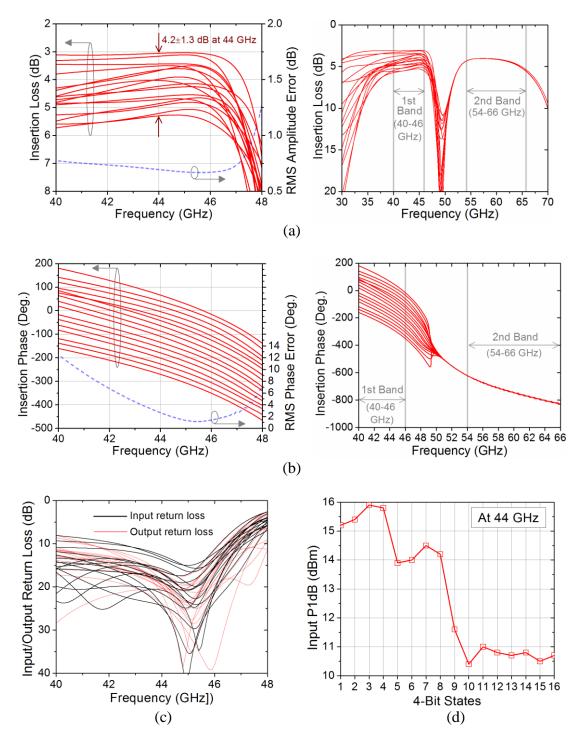

| D.2 | of the 44-GHz phase shifter: (a) insertion loss and RMS amplitude error zoomed in and out, (b) insertion phase and RMS phase error zoomed in                                                                                                                                              | ion<br>190 |

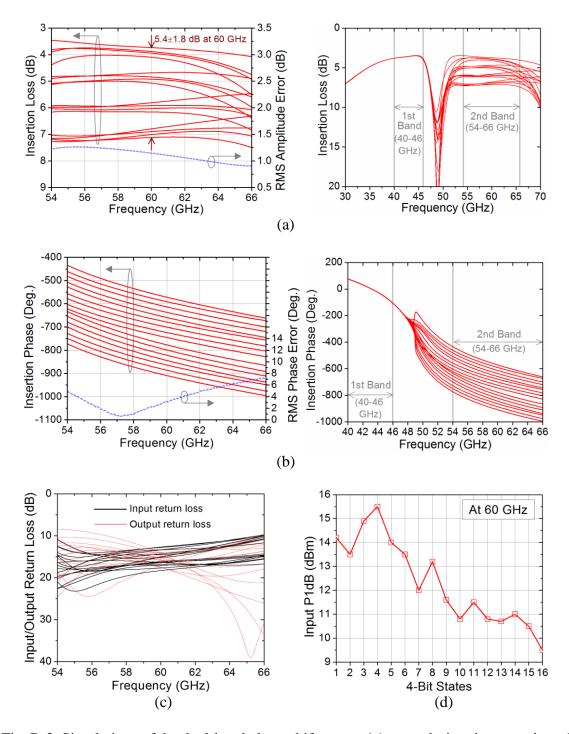

| D.3 | Simulations of the dual-band phase shifter over 16 states during the operation of the 60-GHz phase shifter: (a) insertion loss and RMS amplitude error zoomed in and out, (b) insertion phase and RMS phase error zoomed in and out, (c) input and output return loss, and (d) input P1dB | ion<br>191 |

# LIST OF TABLES

| TABLE |                                                                                             |     |

|-------|---------------------------------------------------------------------------------------------|-----|

| 3.1   | Design parameters of the BPFs and attenuators composing the concurrent dual-band attenuator | 38  |

| 3.2   | Comparison of step CMOS attenuators                                                         | 45  |

| 4.1   | Summary of the calculations in Fig. 4.10                                                    | 63  |

| 4.2   | Control voltages and target attenuations at all states                                      | 71  |

| 4.3   | Comparison of CMOS/BiCMOS attenuators                                                       | 82  |

| 8.1   | Size and configuration of BJTs                                                              | 125 |

| 9.1   | Simulations of the concurrent dual-band PA with single-tone and dual-tone modes             | 151 |

| A.1   | Comparison of CMOS attenuators                                                              | 166 |

| C.1   | Simulations of the concurrent dual-band PA with single-tone and dual-tone modes             | 184 |

### **CHAPTER I**

#### INTRODUCTION & BACKGROUND

#### 1.1 Silicon-Based Millimeter-Wave RFICs

Wireless communications, sensing, and radar plays an essential role in the life of human being living in a fast-growing information era and are indeed necessary that the world cannot function properly without. Building RF wireless communications, sensing, and radar systems in single chips is no longer a "dream," but becoming a "reality." Silicon (Si)-based Radio-Frequency Integrated Circuits (RFICs), working within the RF/electromagnetic (EM) spectrum, are making this reality possible. RF transceivers and digital control circuits can be integrated on the same chip enabling low-cost, small-size, and high-performance single-chip solution. Advanced RF wireless systems and, in turn, RFICs are relevant not only to commercial and military applications but also to national infrastructures. This importance is even more pronounced as the development of civilian technologies becomes increasingly important to the national economic growth. New applications utilizing RFIC technologies continue to emerge, spanning across the EM spectrum, from ultra-wideband to millimeter-wave and sub-millimeter-wave ultra-highcapacity wireless communications; from sensing abnormal human body condition, diagnosing it and imaging the effect to early detection of cancer and un-attended health monitoring and examination; from sensing for airport security to through-wall imaging and inventory for gas and oil; and from detection and inspection of buried mine, UXO, underground oil and gas pipes to wireless power transmission and data communications

Fig. 1.1. Silicon-based millimeter-wave RFIC single-chip-solution and its applications.

for smart wells, etc. (Fig. 1.1). Research and development of new RFICs and systems are thus vital for both the commercial and defense sectors in a nation. They are particularly important for the development and advancement of wireless communications, sensing and radar technologies.

## 1.1.1 SiGe BiCMOS Technology

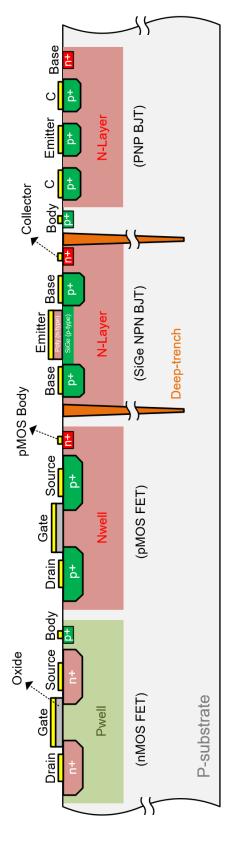

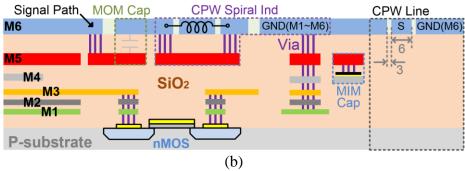

Silicon germanium (SiGe) Bipolar Complementary Metal Oxide Semiconductor (BiCMOS) is the technology of choice for millimeter-wave RFICs due to its various merits. The cross-section of the SiGe BiCMOS process is simply shown in Fig. 1.2, which consists of nMOS and pMOS field effect transistors (FETs), and NPN and PNP bipolar-junction-transistors (BJTs). A SiGe NPN BJT is an advanced technology from Si NPN

BJT. The main difference between them is the material of base of BJT. By using SiGe for the base, the speed, gain, RF and 1/f noises, base resistance and operating frequency of the BJT are improved. In comparison with CMOS, although the BiCMOS process consumes more time and cost, it has a benefit of having available BJTs and CMOS FETs on the same substrate. The two types of transistors enable enhanced system performances, integration, and functionalities. The BJT has higher speed and better high-frequency characteristics ( $f_i \approx 200 \text{ GHz}$ ) than CMOS. Also, it provides a larger current capability, which means more output power, and higher transconductance ( $g_m$ ) and lower RF noise. So, the BJT is considered better for active circuits such as power amplifier (PA), low noise amplifier (LNA), and gain amplifier (GA) in RFIC systems. On the other hand, CMOS has lower cost and can be used more than BJT for passive or digital circuits such as an attenuator, phase shifter, switch, DC control circuit, etc., since CMOS has lower static power dissipation without DC current at gate, and higher yield capability (passive-type circuits usually needs bigger transistor size.)

# 1.2 RFIC Phased-Array System

The first phased-array systems were proposed in the 1950's [1-1]. Since then, they have broadly used in radar and communication applications due to their high directivity, beam-tailoring/steering ability, fast beam scanning/tracking response, etc. [1-2, 1-3]. In spite of their attractive properties, they were expensive, and applications had been limited only to high-cost and big-size systems such as airplane radar, military missile warning/tracking, space surveillance, etc. because of the plenty of constituent circuits. In

Fig. 1.2. Cross section of SiGe BiCMOS containing nMOS and pMOS FETs, and SiGe NPN and PNP BJTs.

Fig. 1.3. Phased-array transmitter and its high-gain beam.

2007, the first fully integrated phased-array RFIC receiver is demonstrated with a SiGe BiCMOS technology in [1-4] achieving significant reductions in cost, weight and power consumption. It is an appropriate design for the modern economic systems such as radars for human-driven/autonomous cars, personal health monitoring devices and wearable/mobile devices requiring high data-rate communications. There have been researching efforts in the last ten years to realize millimeter-wave phased-array systems in silicon-based RFIC processes for a higher integration (on-chip antenna) and wider bandwidth [5th generation (5G) wireless communication].

The intrinsic transistors in RFIC are not able to handle high power due to low current density, breakdown voltage, and lossy substrate. These drawbacks can be remedied with phased arrays. As shown in Fig. 1.3, the low-gain beams radiated by the single array

antennas are spatially combined on the space building the high-gain array beam. The effective isotropic power (EIRP) of a phased-array system is the sum of the output power, antenna gain and array gain (EIRP= $P_{out}+G_{ant}+G_{Array}$ ). So, a 7-channel phased-array transmitter has 8.5-dB array gain more than a single antenna transmitter.

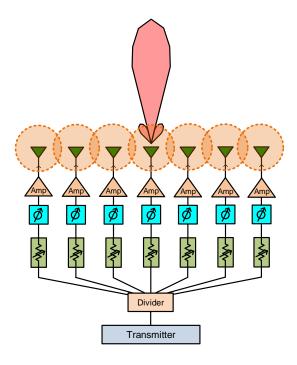

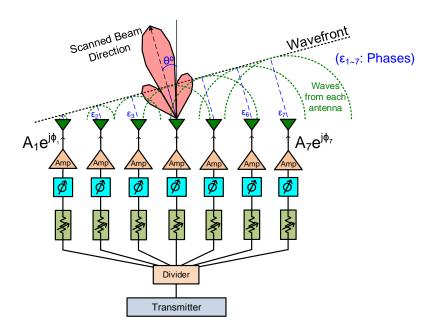

## 1.2.1 Phased-Array Beam Steering with Varying Phases

In phased-array systems, the individual antenna beams at each of the channels construct a high gain beam as mentioned previously. The constructed beam can be steered in the desired direction by varying the phase of the signal at each channel, which is called beam-steering. Fig. 1.4 show the beam direction/range,  $\theta$ , of a phased-array transmitter which consists of antennas, amplifiers, phase shifters, attenuators, and a divider. The phase shifters are employed to adjust the phase/delay of the signal at each channel,  $\phi$ , for having the high gain beam pointing in the desired direction. For the beam direction in Fig. 1.4, the phases are normally  $\phi_1 > \phi_2 > \phi_3 > \phi_4 > \phi_5 > \phi_7 > \phi_7$ . The array factors (AF) of the steered beam are plotted in Fig. 1.5, which are calculated with

$$AF = \sum_{n=1}^{N} A_n e^{j(\phi_n + \varepsilon_n)} . \tag{1.1}$$

The steering range of the phased-array system is practically limited by the phase shift range of the constituent phase shifters. For example, a 4-bit phase shifter with 22.5° least significant bit (LSB) and 0–337.5° phase shift range is employed at each channel of a 24-GHz 7-channel phased-array system. The maximum phase difference ( $\Delta\phi_{\rm max}$ ) between the channels is chosen as 55° since the total phase difference over the seven

Fig. 1.4. 7-channel phased-array transmitter and beam steering.

Fig. 1.5. Antenna factor of the steered beam with the varied phases,  $\phi_{1\sim7}$ .

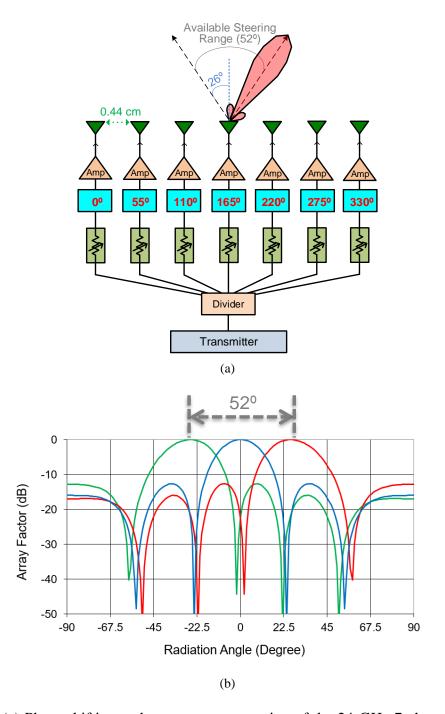

channels should be smaller than the maximum phase shift  $(55^{\circ} \times 6=330^{\circ} < 337.5^{\circ})$  as shown in Fig. 1.6. If the spacing between the array antennas (d) is assumed as 0.44 cm, the steering range  $(\theta)$ ,  $\pm 26^{\circ}$ , can be calculated with

$$|\theta| = \sin^{-1} \frac{\Delta \phi_{\text{max}} \cdot \lambda}{360 \cdot d}. \tag{1.2}$$

The total steering range calculated is  $52^{\circ}$  from the left to right direction as shown in Fig. 1.6. The assumption of the 0.44-cm spacing (d) can be verified with the maximum antenna spacing ( $d_{\text{max}}$ ) calculated with

$$d_{\max} = \frac{\lambda}{1 + \sin \theta} \,. \tag{1.3}$$

The spacing between antennas should be smaller than  $d_{\text{max}}$  in the arrays to facilitate the decent beam combining on space. The 0.44-cm array spacing assumed is acceptable based on the  $d_{\text{max}}$  of 0.73 cm calculated. There are several ways to increase the steering range. Firstly, we reduce the antenna spacing or the number of arrays/channels, but the directivity of the beam is degraded. Secondly, we also increase the phase shifting range of the phase shifters, but more phase shifters are needed at the cost of insertion loss and size.

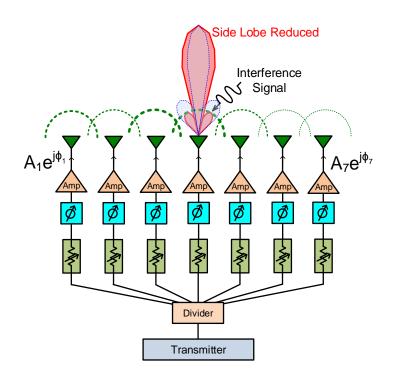

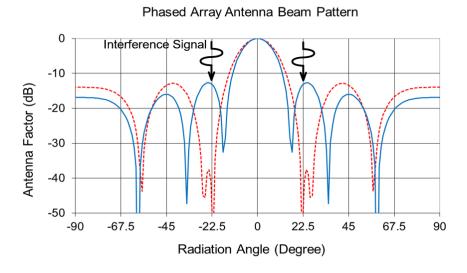

## 1.2.2 Phased-Array Beam Tailoring with Amplitude Varied

The beam steering function with the phase shifters is introduced in the previous chapter. As another remarkable function of a phased-array system, the high gain beam can be shaped as desired, which is caller beam tailoring. The attenuators in the phased-array transmitter in Fig. 1.7 are used to control the amplitude of the signal at each channel. By changing the amplitude in specific ways, we can reduce the side lobe to a certain degree, which means the interference signal at certain degree can be reduced. Fig. 1.8 shows the reduced side lobes at  $\pm 22.5^{\circ}$  in red dotted line, which are calculated with the varying amplitudes,  $A_1$ =1.3,  $A_2$ =0.8,  $A_3$ =1.6,  $A_4$ =1.6,  $A_5$ =0.8,  $A_6$ =0.4, and  $A_7$ =0.5.

Fig. 1.6. (a) Phase shifting and array antenna spacing of the 24-GHz 7-channel phased-array transmitter for the 26° steering direction, and (b) its array factors showing 52° steering range.

Fig. 1.7. 7-channel phased-array transmitter with beam tailored.

Fig. 1.8. Antenna factor of the tailored beam with varied amplitudes,  $A_{1\sim7}$ .

Fig. 1.9. 7-channel concurrent dual-band phased-array transmitter with dual independent beams.

## 1.2.3 Concurrent Dual-Band Phased-Array System

Dual-band communication and radar systems, particularly those that can work in different bands at the same time, have become attractive in addressing increasing demands of military and industry applications. Accordingly, phased-array systems working concurrently over multiple bands are needed to push the wireless communications and sensing to the next level with its numerous advantages. Concurrent dual-band phased-array systems bring the inherent strengths of phased arrays, such as high directivity, beamtailoring/steering ability, fast beam scanning/tracking response, etc., in different bands together into a single system. Consequently, dual-band phased-array systems are capable of forming and steering multiple electronic beams in different frequency bands

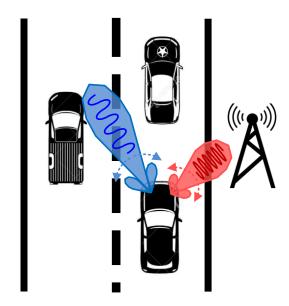

Fig. 1.10. Concurrent dual-band phased-array automotive radar with independent beams.

simultaneously, which significantly improve the systems' diversity, ability, reliability, and performance. The higher frequencies of a dual-band system enable a high-data-rate communication and a high-detection-sensitivity radar, but at the cost of increased noise and propagation loss. On the other hand, the lower frequencies minimize noise and propagation loss. Fig. 1.9 shows the concurrent dual-band phased-array transmitter for  $f_1$  and  $f_2$  frequencies. The single constituent components, concurrent dual-band phase shifters and attenuators, are able to operate at the dual bands individually without interference in another band, which enable the control of the dual array beams. The dual-band phased-array transmitter/receiver can be employed in various systems such as an automotive radar enabling dual-target tracking, dual-point communication, simultaneous tracking/sensing, etc, as shown in Fig. 1.10.

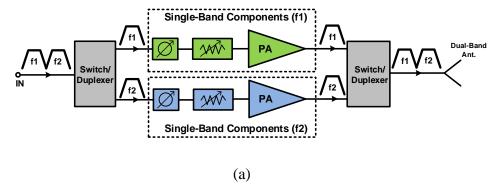

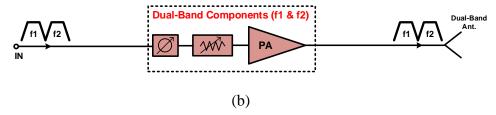

# **Conventional Dual-Band TX:**

# **Proposed Concurrent Dual-Band TX:**

Fig. 1.11. (a) Conventional and (b) proposed concurrent dual-band transmitter.

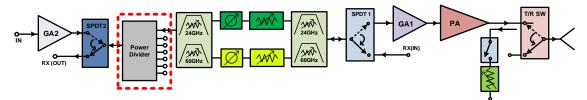

Conventionally, the concurrent dual-band transmitters are designed with two separate paths with switches or duplexers as shown in Fig. 1.11(a). We propose the transmitter shown in Fig. 1.11(b) to reduce the number of components, loss, power consumption, size, and cost. The proposed concurrent dual-band transmitter consists of the concurrent dual-band constituent components, which would have more linearity issues compared to the single-band components because the dual frequencies are simultaneously processed. This approach is more challenging but deserves significant attention, as it enables fully integrated dual-band transceiver in a single unit, bringing more cost-effective and better-performance systems to both military and commercial sectors.

Fig. 1.12. Radar range resolution  $(\Delta r)$  to discriminate the objects close to each other.

# 1.3 Frequency Band Planning

For our phased-array design, two unlicensed bands of 22–29 and 57–64 GHz are chosen. The high frequencies enable a compact design of the phased-array system. Also, for radar application, it can have broad bandwidth, which leads to high data rate and low range resolution ( $\Delta r$ ) based on

$$FBW = \frac{f_2 - f_1}{f_C} \tag{1.4}$$

and

$$\Delta r = \frac{c \cdot T}{2} = \frac{c}{2 \cdot BW} \,. \tag{1.5}$$

Fig. 1.12 shows why a low range resolution is needed for the radar system. The low range resolution enables us to discriminate the objects located closely apart. On the other hand, the high frequencies degrade the radar detection range ( $R_{max}$ ),

$$R_{\text{max}} = \sqrt[4]{\frac{P_t G^2 c^2 \sigma}{f_0^2 (4\pi)^3 P_{\text{min}}}}$$

(1.6)

, but it can be compensated with the array structure. The high-frequency design also increases the gain of the beam, which is good for discriminating multiple targets in radar. The correlation between the gain of beam and operating frequency is expressed as

$$G = \frac{4\pi A_e f_0^2}{c^2} \,. \tag{1.7}$$

# 1.4 References

- [A-1] B. A. Kopp, M. Borkowski, and G. Jerinic, "Transmit/receive modules," Kopp,

B.A.; Borkowski, M.; Jerinic, G., "Transmit/receive modules," in *Microwave Theory and Techniques*, *IEEE Transactions on*, vol. 50, no. 3, pp. 827-834, Mar. 2002.

- [A-2] Parker, D.; Zimmermann, D.C., "Phased arrays part 1: theory and architectures," in *Microwave Theory and Techniques, IEEE Transactions on*, vol. 50, no. 3, pp. 678-687, Mar. 2002.

- [A-3] Koh. K.; Rebeiz, G.M., "An X- and Ku-Band 8-Element Linear Phased Array Receiver," in *Custom Integrated Circuits Conference*, 2007. CICC '07. IEEE, pp. 761-764, 16-19 Sept. 2007.

- [A-4] Kwang-Jin Koh; Rebeiz, G.M., "0.13-μm CMOS Phase Shifters for X-, Ku-, and K-Band Phased Arrays," in *Solid-State Circuits, IEEE Journal of*, vol. 42, no. 11, pp. 2535-2546, Nov. 2007.

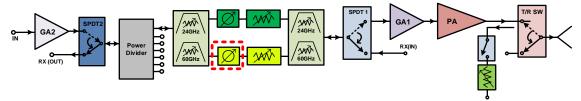

#### **CHAPTER II**

#### CONCURRENT DUAL-BAND PHASED-ARRAY TRANSCEIVER

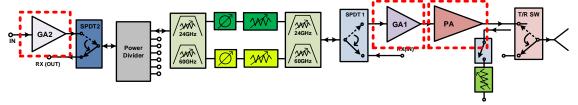

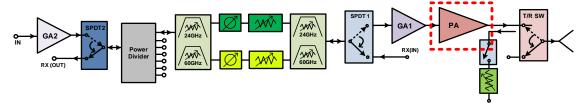

# 2.1 24/60-GHz Concurrent Dual-Band Phased-Array Transceiver/Transmitter