# DIGITAL CIRCUIT DESIGN USING FLOATING GATE TRANSISTORS

#### A Dissertation

by

## MONTHER Y. A. ABUSULTAN

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirement for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Sunil P. Khatri

Committee Members, Peng Li

Laszlo B. Kish

Duncan M. Walker

Head of Department, Miroslav M. Begovic

May 2017

Major Subject: Computer Engineering

Copyright 2017 Monther Y. A. Abusultan

#### ABSTRACT

Floating gate (flash) transistors are used exclusively for memory applications today. These applications include SD cards of various form factors, USB flash drives and SSDs. In this thesis, we explore the use of flash transistors to implement digital logic circuits. Since the threshold voltage of flash transistors can be modified at a fine granularity during programming, several advantages are obtained by our flash-based digital circuit design approach. For one, speed binning at the factory can be controlled with precision. Secondly, an IC can be re-programmed in the field, to negate effects such as aging, which has been a significant problem in recent times, particularly for mission-critical applications. Thirdly, unlike a regular MOSFET, which has one threshold voltage level, a flash transistor can have multiple threshold voltage levels. The benefit of having multiple threshold voltage levels in a flash transistor is that it allows the ability to encode more symbols in each device, unlike a regular MOSFET. This allows us to implement multi-valued logic functions natively. In this thesis, we evaluate different flash-based digital circuit design approaches and compare their performance with a traditional CMOS standard cell-based design approach. We begin by evaluating our design approach at the cell level to optimize the design's delay, power energy and physical area characteristics. The flash-based approach is demonstrated to be better than the CMOS standard cell approach, for these performance metrics. Afterwards, we present the performance of our design approach at the block level. We describe a synthesis flow to decompose a circuit block into a network of interconnected flash-based circuit cells. We also describe techniques to optimize the resulting network of flash-based circuit cells using don't cares. Our optimization approach distinguishes itself from other optimization techniques that use don't cares, since it a) targets a flash-based design flow, b) optimizes clusters of logic nodes at once instead of one node at a time, c) attempts to reduce the number of cubes instead of reducing the number of literals in each cube and d) performs optimization on the post-technology mapped netlist which results in a direct improvement in result quality, as compared to pre-technology mapping logic optimization that is typically done in the literature. The resulting network characteristics (delay, power, energy and physical area) are presented. These results are compared with a standard cell-based realization of the same block (obtained using commercial tools) and we demonstrate significant improvements in all the design metrics. We also study flashbased FPGA designs (both static and dynamic), and present the tradeoff of delay, power dissipation and energy consumption of the various designs. Our work differs from previously proposed flash-based FPGAs, since we embed the flash transistors (which store the configuration bits) directly within the logic and interconnect fabrics. We also present a detailed description of how the programming of the configuration bits is accomplished, for all the proposed designs.

To my parents.

#### **ACKNOWLEDGMENTS**

My sincere thanks to my committee chair, Dr. Sunil P. Khatri. I thank him for his guidance, support and encouragement throughout my Ph.D. program.

I would also like to thank my committee members: Dr. Peng Li, Dr. Laszlo B. Kish, Dr. Duncan M. Walker and Dr. Gianfranco Gerosa for their valuable suggestions and feedback. Dr. Gerosa deserves special thanks for his insightful feedback and comments that helped me strengthen this work further. His industrial background bridged the gap between my research and current VLSI industry challenges and needs.

Finally and most importantly, I would like to thank my dear mother, father and siblings for their endless encouragement and support. They have always stood behind me in every step towards my success. I would also like to thank my loving wife for her support and for standing next to me during the stressful times I have been through. I thank her also for taking care of our baby, especially during the late and long hours I have spent in the office working on my research.

# CONTRIBUTORS AND FUNDING SOURCES

## **Contributors**

This work was supported by a dissertation committee consisting of Professors Sunil P. Khatri (advisor), Peng Li and Laszlo B. Kish of the Department of Electrical and Computer Engineering, Professor Duncan M. Walker of the Department of Computer Science and Engineering and Dr. Gian Gerosa from Intel Corporation.

All work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

Graduate study was supported by a research assistantship from Texas A&M University.

# TABLE OF CONTENTS

|                          | Page                                                                                                                                                                                      |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTRAC                  | T                                                                                                                                                                                         |

| DEDICATI                 | ON iv                                                                                                                                                                                     |

| ACKNOW                   | LEDGMENTS                                                                                                                                                                                 |

| CONTRIB                  | UTORS AND FUNDING SOURCES vi                                                                                                                                                              |

| TABLE OF                 | CONTENTS vii                                                                                                                                                                              |

| LIST OF F                | IGURES xii                                                                                                                                                                                |

| LIST OF T                | ABLES xvi                                                                                                                                                                                 |

| CHAPTER                  | I INTRODUCTION                                                                                                                                                                            |

| I.2 I.3 I.3 I.3 I.3      | Digital Circuit Design1Design Performance Metrics32.1 Delay32.2 Power Dissipation52.3 Energy Consumption62.4 Area7Digital Design Challenges83.1 Process Variations83.2 Design Regularity8 |

| I.4<br>I.4<br>I.4<br>I.5 | Digital Design Approaches                                                                                                                                                                 |

| I.7<br>I.8               | Application Specific Integrated Circuits       14         Programmable Logic Arrays       16         Field Programmable Gate Arrays       18                                              |

| I.9<br>I.9<br>I.9        | Floating Gate (Flash) Transistors209.1 Device Structure209.2 Programming the Flash Transistor219.3 Flash Transistors in Memory229.4 Read and Write Disturb249.5 Write Endurance25         |

| CHAPTER II THESIS OUTLINE                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| II.1 Implementation of Flash-based Cells II.1.1 Ternary-valued, Flash-based Digital II.1.2 Binary-valued, Flash-based Digital II.1.3 PLA-like, Flash-based Digital Logi II.1.4 Multi-valued, Flash-based Digital I                                                                                                                                                                                                                              | 1 Logic Cell Implementation 28<br>Logic Cell Implementation 28<br>c Cell Implementation 29<br>Logic Cell Implementation 29 |

| II.2 CAD Flow                                                                                                                                                                                                                                                                                                                                                                                                                                   | ary-valued, Flash-based Dig-                                                                                               |

| II.3 Field Programmable Gate Array (FPGA) .  II.3.1 Flash-based Field Programmable G                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| CHAPTER III TERNARY-VALUED, FLASH-BASI IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| III.1 Background  III.2 Previous Work  III.3 Approach  III.3.1 Overview  III.3.2 Ternary Logic Flash-based Design of the III.3.3 Ternary Logic Cluster (TLC) Circulli.3.4 Programming the Flash Ternary Logic III.3.5 Logic Minimization of the TLC  III.4 Experiments  III.4.1 Simulation Environment  III.4.2 Flash Model Card Regression  III.4.3 Ternary-valued, Flash-based Implemited III.4.4 Results and Analysis  III.5 Chapter Summary | 35 36 36 36 36 Conversion 36 it Design 39 gic Cluster 47 48 48 49 50 mentation Details 51                                  |

| CHAPTER IV BINARY-VALUED, FLASH-BASE IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| IV.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58         58         59         61         68                                                                             |

| CHAPTER VI SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | IV.3.5  | Mapping a CMOS-based Design into a Flash-based Design                                                          | 71  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------|-----|

| IV.4.2   Flash-based Implementation Details   17.5     IV.4.3   Results and Analysis   7.5     IV.5   Chapter Summary   80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IV.4     | Exper   |                                                                                                                | 71  |

| IV.4.3   Results and Analysis   72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | IV.4.1  | Simulation Environment                                                                                         | 72  |

| IV.5 Chapter Summary 86  CHAPTER V BLOCK-LEVEL IMPLEMENTATION OF BINARY-VALUED, FLASH-BASED DIGITAL DESIGNS 83  V.1 Background 85  V.2 Previous Work 85  V.3 Approach 86  V.3.1 Overview 86  V.3.2 Flash-based Design Conversion 87  V.4 Experiments 91  V.4.1 Simulation Environment 91  V.4.2 Flash-based Analysis Details 92  V.4.3 Results and Analysis 92  V.4.4 FC Statistics 90  V.4.5 Shifting the Threshold Voltage 100  V.5 Chapter Summary 104  CHAPTER VI SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS 100  VI.1 Background 100  VI.2 Previous Work 100  VI.3 Approach 111  VI.3.1 Overview 111  VI.3.2 Flash Cluster Circuit Design 113  VI.3.3 FC-based CAD Flow 112  VI.4 Experiments 121  VI.4.2 Results and Analysis 122  VI.4.2 Results and Analysis 122  VI.5 Chapter Summary 124  CHAPTER VI PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION 136  VII.1 Background 137  VII.1 Background 136  VII.1 Background 136  VII.2 Previous Work 132 |          | IV.4.2  | Flash-based Implementation Details                                                                             | 73  |

| IV.5 Chapter Summary       86         CHAPTER V BLOCK-LEVEL IMPLEMENTATION OF BINARY-VALUED, FLASH-BASED DIGITAL DESIGNS       83         V.1 Background       85         V.2 Previous Work       85         V.3 Approach       85         V.3.1 Overview       85         V.3.2 Flash-based Design Conversion       86         V.3.3 FC-based CAD Flow Overview       86         V.4.1 Simulation Environment       91         V.4.2 Flash-based Analysis Details       92         V.4.3 Results and Analysis       93         V.4.4 FC Statistics       100         V.4.5 Shifting the Threshold Voltage       100         V.5 Chapter Summary       104         CHAPTER VI SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS         UV.1.2 Previous Work       105         VI.3 Approach       111         VI.3.1 Overview       111         VI.3.2 Flash Cluster Circuit Design       112         VI.4 Experiments       121         VI.4.2 Results and Analysis       122         VI.4.2 Results and Analysis       122 <t< td=""><td></td><td>IV.4.3</td><td>Results and Analysis</td><td>73</td></t<>                                                                                                                                                                                                           |          | IV.4.3  | Results and Analysis                                                                                           | 73  |

| FLASH-BASED DIGITAL DESIGNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IV.5     | Chapt   |                                                                                                                | 80  |

| V.1       Background       85         V.2       Previous Work       85         V.3       Approach       85         V.3.1       Overview       85         V.3.2       Flash-based Design Conversion       86         V.3.3       FC-based CAD Flow Overview       87         V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       92         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       100         VI.1       Background       100         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.4       Experiments       121         VI.4.1       Simulation Environment       122         VI.4.2       Results and Analysis       122                                                                                                                                                                                                                    | СНАРТ    | ER V    | BLOCK-LEVEL IMPLEMENTATION OF BINARY-VALUED,                                                                   |     |

| V.2       Previous Work       85         V.3       Approach       85         V.3.1       Overview       85         V.3.2       Flash-based Design Conversion       86         V.3.3       FC-based CAD Flow Overview       86         V.4       Experiments       91         V.4       Experiments       92         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       97         V.4.4       FC Statistics       106         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       106         VI.3       Approach       111         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122                                                                                                                                                                                                                      |          |         | FLASH-BASED DIGITAL DESIGNS                                                                                    | 83  |

| V.3       Approach       85         V.3.1       Overview       85         V.3.2       Flash-based Design Conversion       86         V.3.3       FC-based CAD Flow Overview       87         V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       95         V.4.4       FC Statistics       106         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.4.1       Simulation Environment <td></td> <td>Backg</td> <td>ground</td> <td></td>                                                                                                                                                   |          | Backg   | ground                                                                                                         |     |

| V.3.1       Overview       85         V.3.2       Flash-based Design Conversion       86         V.3.3       FC-based CAD Flow Overview       87         V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       97         V.4.4       FC Statistics       106         V.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       123         VI.5       Chapter Summary                                                                                                                                                                                                        | V.2      | Previo  | ous Work                                                                                                       |     |

| V.3.2       Flash-based Design Conversion       86         V.3.3       FC-based CAD Flow Overview       87         V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       95         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130                                                                                                                                                                                  | V.3      | Appro   | oach                                                                                                           | 85  |

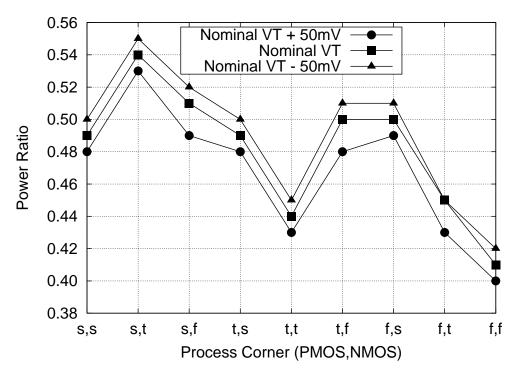

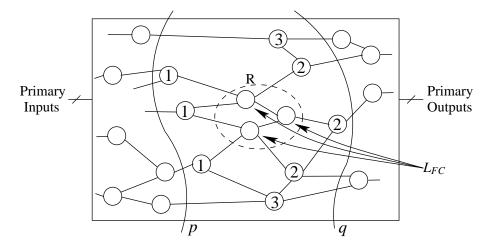

| V.3.3       FC-based CAD Flow Overview       87         V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       97         V.4.4       FC Statistics       100         V.5.       Shifting the Threshold Voltage       102         V.5.       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       100         VI.1       Background       100         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       115         VI.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII                                                                                                                                                                                          |          | V.3.1   | Overview                                                                                                       | 85  |

| V.4       Experiments       91         V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       95         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                |          | V.3.2   | Flash-based Design Conversion                                                                                  | 86  |

| V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       95         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                       |          | V.3.3   |                                                                                                                | 87  |

| V.4.1       Simulation Environment       91         V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       95         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                       | V.4      | Exper   | iments                                                                                                         | 91  |

| V.4.2       Flash-based Analysis Details       92         V.4.3       Results and Analysis       97         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       122         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       136         VII.1       Background       136         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                 |          |         |                                                                                                                | 91  |

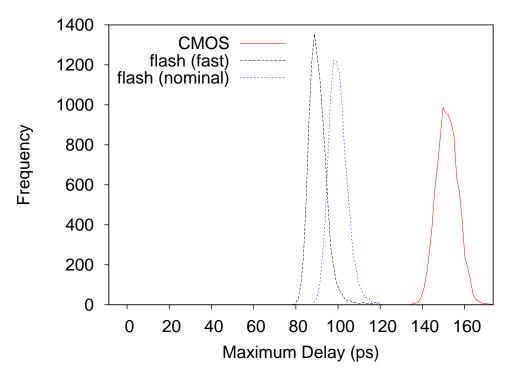

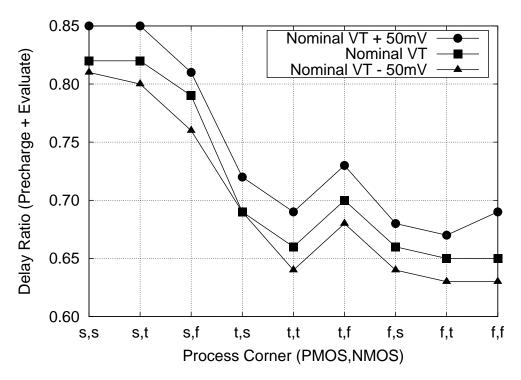

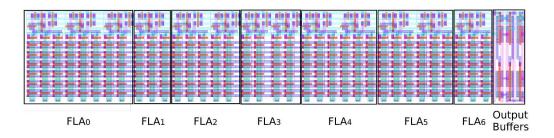

| V.4.3       Results and Analysis       97         V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       123         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                                                                           |          | V.4.2   |                                                                                                                |     |

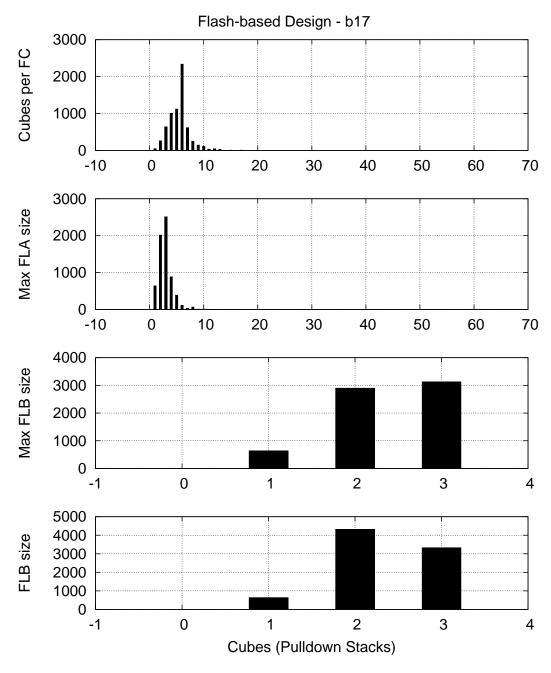

| V.4.4       FC Statistics       100         V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       123         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                       |          |         |                                                                                                                |     |

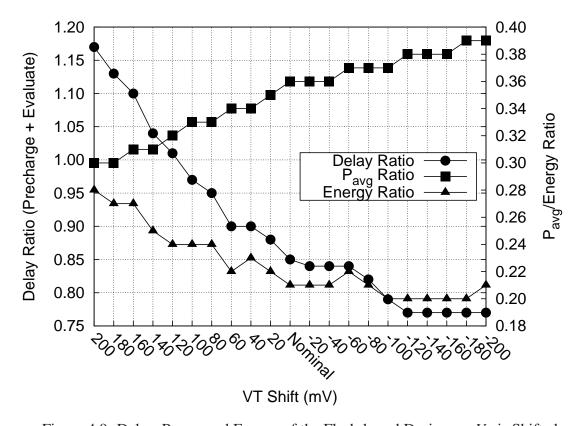

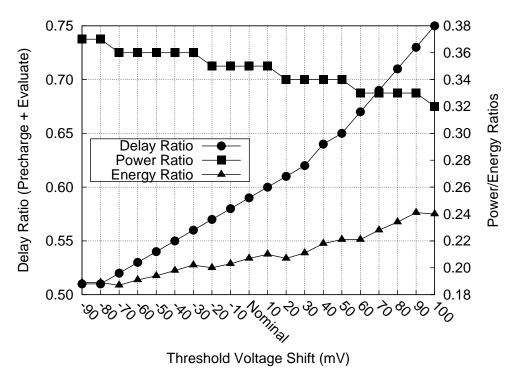

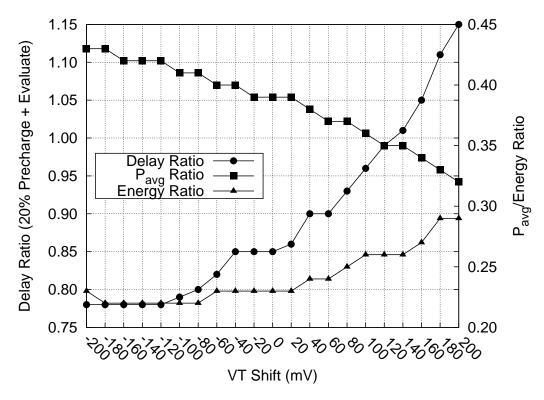

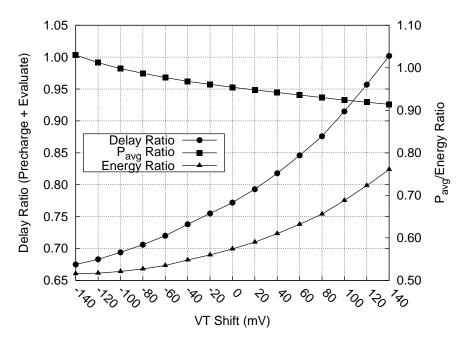

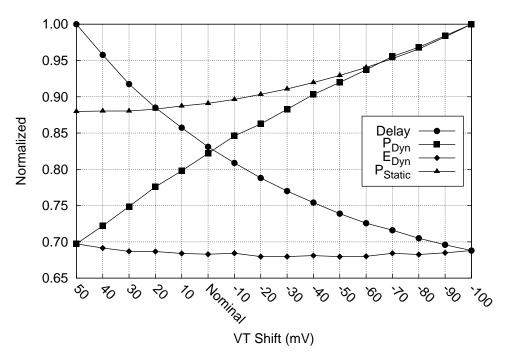

| V.4.5       Shifting the Threshold Voltage       102         V.5       Chapter Summary       104         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       123         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                          |          |         |                                                                                                                |     |

| V.5       Chapter Summary       102         CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       112         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       123         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |         |                                                                                                                |     |

| CHAPTER VI       SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL DESIGNS       106         VI.1       Background       106         VI.2       Previous Work       109         VI.3       Approach       111         VI.3.1       Overview       111         VI.3.2       Flash Cluster Circuit Design       113         VI.3.3       FC-based CAD Flow       115         VI.4       Experiments       121         VI.4.1       Simulation Environment       121         VI.4.2       Results and Analysis       123         VI.5       Chapter Summary       128         CHAPTER VII       PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1       Background       130         VII.2       Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V 5      |         | $\mathcal{E}$                                                                                                  |     |

| DESIGNS       106         VI.1 Background       106         VI.2 Previous Work       109         VI.3 Approach       111         VI.3.1 Overview       111         VI.3.2 Flash Cluster Circuit Design       113         VI.3.3 FC-based CAD Flow       115         VI.4 Experiments       121         VI.4.1 Simulation Environment       121         VI.4.2 Results and Analysis       123         VI.5 Chapter Summary       128         CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | , .c     | Спарс   | or summary                                                                                                     | 10  |

| VI.1 Background       106         VI.2 Previous Work       109         VI.3 Approach       111         VI.3.1 Overview       111         VI.3.2 Flash Cluster Circuit Design       113         VI.3.3 FC-based CAD Flow       115         VI.4 Experiments       121         VI.4.1 Simulation Environment       121         VI.4.2 Results and Analysis       123         VI.5 Chapter Summary       128         CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHAPT    | ER VI   | SAT-BASED OPTIMIZATION FOR FLASH-BASED DIGITAL                                                                 |     |

| VI.2 Previous Work       109         VI.3 Approach       111         VI.3.1 Overview       111         VI.3.2 Flash Cluster Circuit Design       113         VI.3.3 FC-based CAD Flow       115         VI.4 Experiments       121         VI.4.1 Simulation Environment       123         VI.4.2 Results and Analysis       123         VI.5 Chapter Summary       128         CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |         | DESIGNS                                                                                                        | 106 |

| VI.2 Previous Work       109         VI.3 Approach       111         VI.3.1 Overview       113         VI.3.2 Flash Cluster Circuit Design       113         VI.3.3 FC-based CAD Flow       115         VI.4 Experiments       121         VI.4.1 Simulation Environment       123         VI.4.2 Results and Analysis       123         VI.5 Chapter Summary       128         CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4        |         |                                                                                                                | 10  |

| VI.3 Approach       111         VI.3.1 Overview       111         VI.3.2 Flash Cluster Circuit Design       113         VI.3.3 FC-based CAD Flow       115         VI.4 Experiments       121         VI.4.1 Simulation Environment       123         VI.4.2 Results and Analysis       123         VI.5 Chapter Summary       128         CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |         |                                                                                                                |     |

| VI.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |         |                                                                                                                |     |

| VI.3.2 Flash Cluster Circuit Design VI.3.3 FC-based CAD Flow  VI.4 Experiments  VI.4.1 Simulation Environment  VI.4.2 Results and Analysis  VI.5 Chapter Summary  CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION  VII.1 Background  VII.2 Previous Work  133  134  135  136  137  137  138  139  130  130  130  130  130  130  130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VI.3     | Appro   |                                                                                                                |     |

| VI.3.3 FC-based CAD Flow  VI.4 Experiments  VI.4.1 Simulation Environment  VI.4.2 Results and Analysis  VI.5 Chapter Summary  CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION  VII.1 Background  VII.2 Previous Work  130  VII.3 Previous Work  131  132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | VI.3.1  |                                                                                                                | 111 |

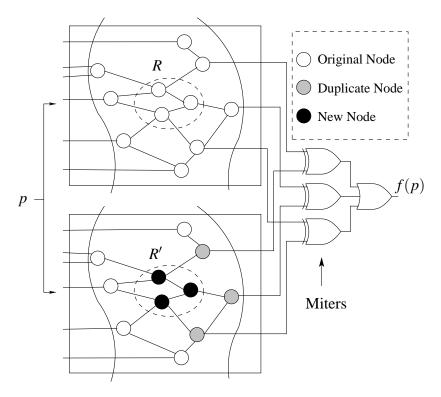

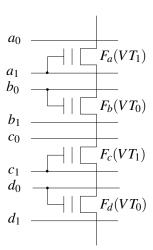

| VI.3.3 FC-based CAD Flow  VI.4 Experiments  VI.4.1 Simulation Environment  VI.4.2 Results and Analysis  VI.5 Chapter Summary  CHAPTER VII PLA-LIKE, FLASH-BASED DIGITAL LOGIC CELL IMPLE-MENTATION  VII.1 Background  VII.2 Previous Work  130  VII.3 Previous Work  131  132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | VI.3.2  | Flash Cluster Circuit Design                                                                                   | 113 |

| VI.4.1 Simulation Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | VI.3.3  | FC-based CAD Flow                                                                                              | 115 |

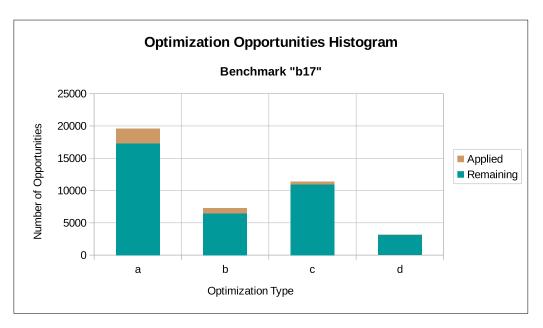

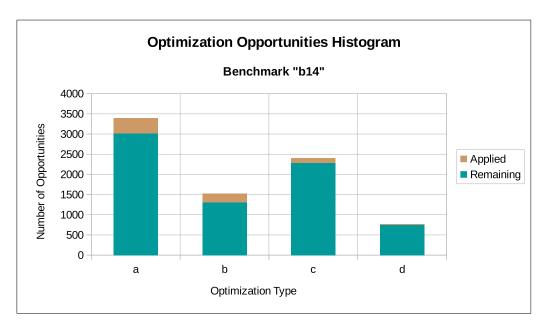

| VI.4.2 Results and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VI.4     | Exper   | iments                                                                                                         | 121 |

| VI.4.2 Results and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | VI.4.1  | Simulation Environment                                                                                         | 121 |

| VI.5 Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | VI.4.2  |                                                                                                                | 123 |

| MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VI.5     | Chapt   | , and the second se |     |

| MENTATION       130         VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OII A DO | ED 1777 | DIALINE EL AGUIDAGES DIGITALITAGES CELL DOTE                                                                   |     |

| VII.1 Background       130         VII.2 Previous Work       132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CHAPT    | EK VII  | ·                                                                                                              | 10- |

| VII.2 Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |         | MENTATION                                                                                                      | 130 |

| VII.2 Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VII.     | l Backs | ground                                                                                                         | 130 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | _       |                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |         |                                                                                                                |     |

| VII.3.1 Overview                                              | 134 |

|---------------------------------------------------------------|-----|

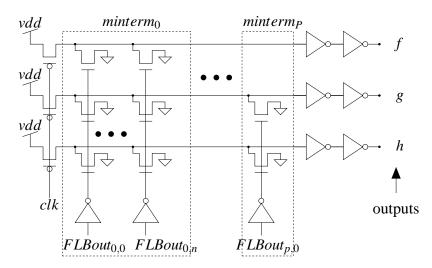

| VII.3.2 PLA-like Flash Cluster (PFC) Circuit Design           | 134 |

| VII.3.3 Programming the PFC                                   | 143 |

| VII.4 Experiments                                             | 143 |

| VII.4.1 Simulation Environment                                | 144 |

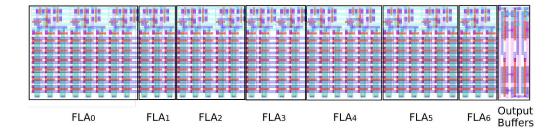

| VII.4.2 Flash-based Implementation Details                    | 145 |

| VII.4.3 Results and Analysis                                  | 145 |

| VII.5 Chapter Summary                                         | 149 |

| CHAPTER VIII MULTI-VALUED, FLASH-BASED DIGITAL LOGIC CELL     |     |

| IMPLEMENTATION                                                | 151 |

| VIII.1 Background                                             | 151 |

| VIII.2 Previous Work                                          | 152 |

| VIII.3 Approach                                               | 154 |

| VIII.3.1 Overview                                             | 154 |

| VIII.3.2 Flash-based Design Conversion                        | 154 |

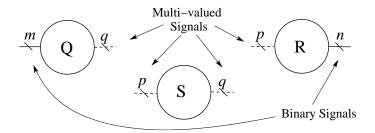

| VIII.3.3 Multi-valued Logic Flash-based Design Conversion     | 155 |

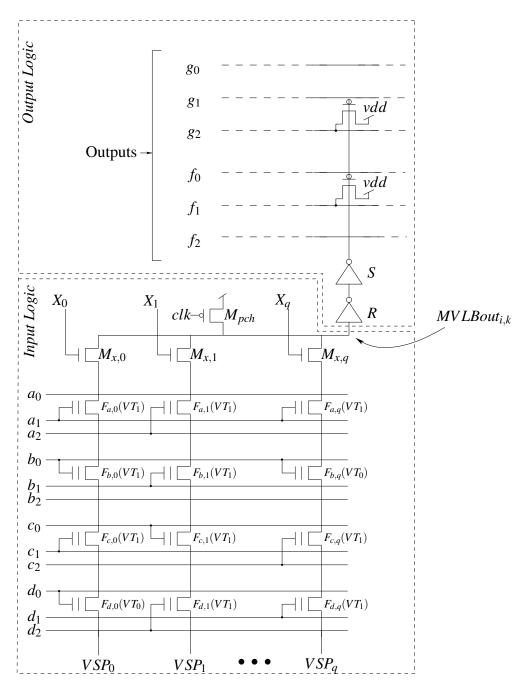

| VIII.3.4 Multi-valued Flash Cluster Circuit Design            | 157 |

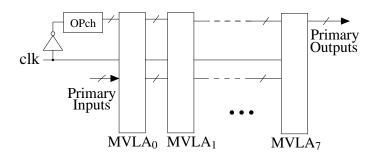

| VIII.3.5 Multi-valued Logic Array                             | 159 |

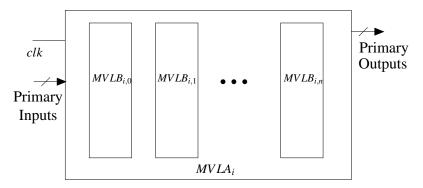

| VIII.3.6 Multi-valued Logic Bundles                           | 162 |

| VIII.3.7 MVLB Configuration                                   | 164 |

| VIII.3.8 Programming the Multi-valued Flash Cluster           | 166 |

| VIII.3.9 Logic Minimization of the MVFC                       | 167 |

| VIII.4 Experiments                                            | 168 |

| VIII.4.1 Simulation Environment                               | 168 |

| VIII.4.2 Results and Analysis                                 | 170 |

| VIII.5 Chapter Summary                                        | 173 |

| CHAPTER IX FLASH-BASED FIELD PROGRAMMABLE GATE ARRAY          |     |

| (FPGA)                                                        | 175 |

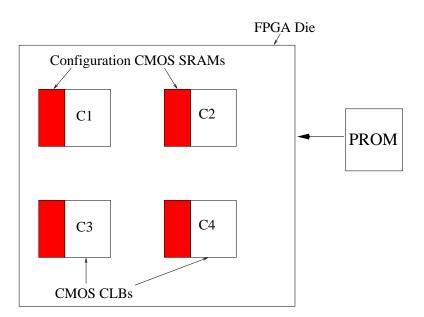

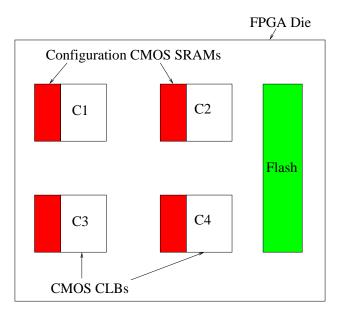

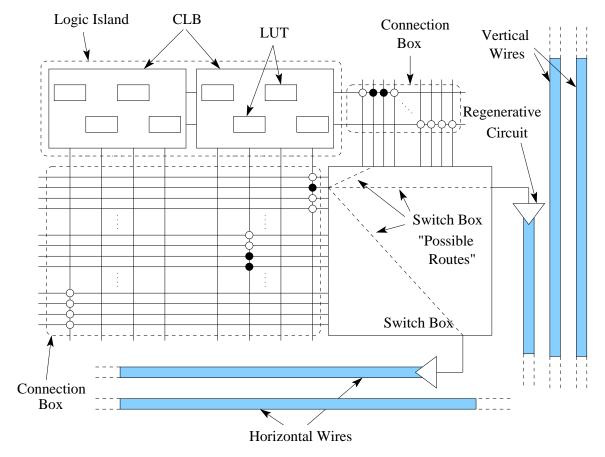

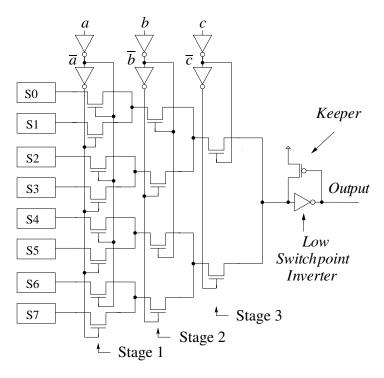

| IX.1 Background                                               | 175 |

| IX.2 Previous Work                                            | 181 |

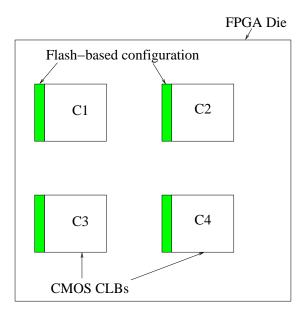

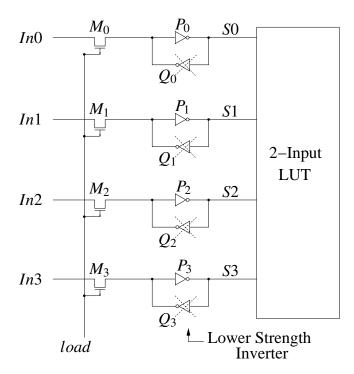

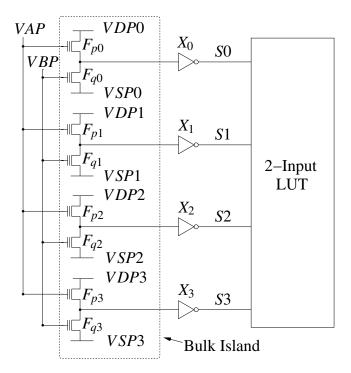

| IX.3 Approach                                                 | 183 |

| IX.3.1 Overview                                               | 183 |

| IX.3.2 Conventional SRAM-based LUT Structure                  | 184 |

| IX.3.3 Conventional Flash-based LUT Structure                 | 186 |

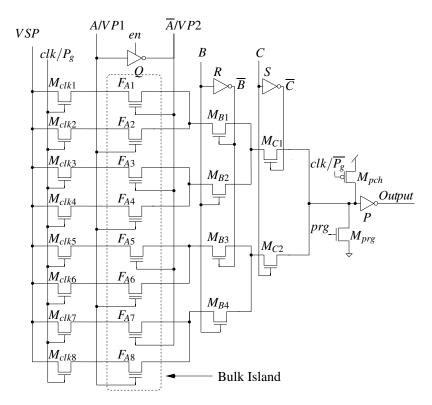

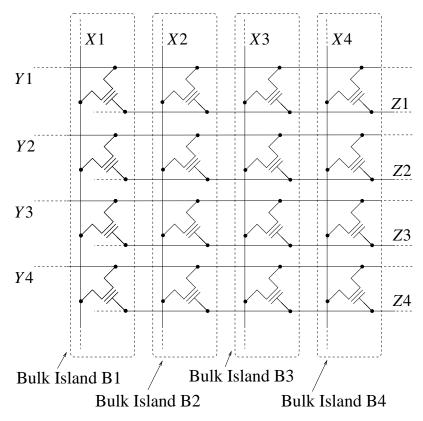

| IX.3.4 Proposed Static Flash-based LUT (SF-LUT)               | 190 |

| IX.3.5 Proposed Dynamic Flash-based LUT (DF-LUT)              | 194 |

| IX.3.6 Configuration Time                                     | 198 |

| IX.3.7 Conventional SRAM-based Programmable Switch Structure  | 199 |

| IX.3.8 Conventional Flash-based Programmable Switch Structure | 199 |

| L       | X.3.9    | Proposed Flash-in-path (FIP) Programmable Switch       | <br>. 200 |

|---------|----------|--------------------------------------------------------|-----------|

| IX.4    | Experin  | nents                                                  | <br>. 202 |

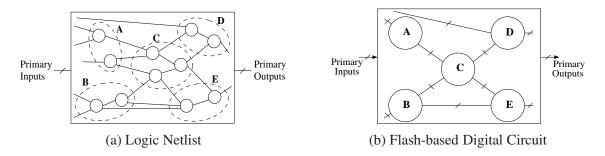

|         |          | Simulation Environment                                 |           |

| Ι       |          | LUT Implementation Details                             |           |

| I       |          | Results and Analysis                                   |           |

| IX.5    |          | Summary                                                |           |

| СНАРТЕ  | R X T    | THESIS SUMMARY AND CONCLUSIONS                         | <br>. 208 |

| X.1     | Choosin  | ng the Right Flash-based Design Approach               | <br>. 209 |

| СНАРТЕ  | R XI F   | FUTURE WORK                                            | <br>. 212 |

| XI.1    | Flash To | echnology Scaling                                      | <br>. 212 |

| XI.2    |          | ND Technology                                          |           |

| XI.3    | Static F | lash-based Implementation Using P-type Flash           | <br>. 215 |

| XI.4    | Preset V | $V_T$ Levels to Meet Application Needs                 | <br>. 216 |

| XI.5    | Replaci  | ng Always-on Flash Transistors with Metal Wires        | <br>. 217 |

| XI.6    | Custom   | ized Espresso-MV for Multi-valued Flash-based Design . | <br>. 219 |

| XI.7    | Delay I  | Oriven Optimization                                    | <br>. 220 |

| REFEREN | NCES .   |                                                        | <br>. 224 |

# LIST OF FIGURES

| FIGURE |                                                              | Page |

|--------|--------------------------------------------------------------|------|

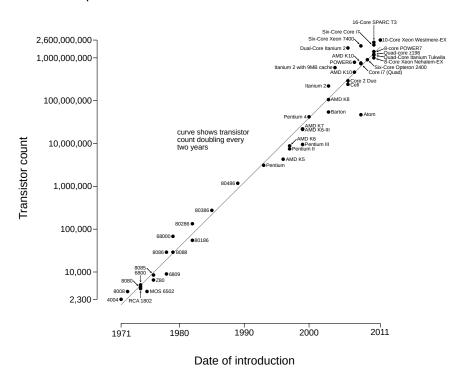

| 1.1    | Moore's Law Trend from 1971 to 2011                          | 1    |

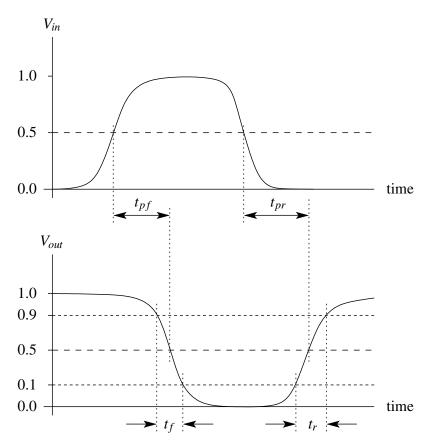

| 1.2    | Transition and Propagation Delays                            | 4    |

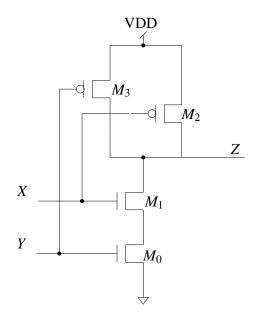

| 1.3    | Static CMOS NAND Gate                                        | 11   |

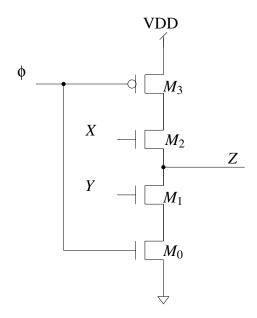

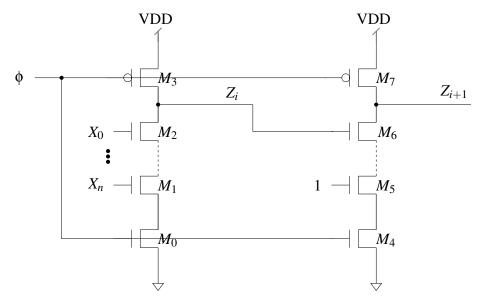

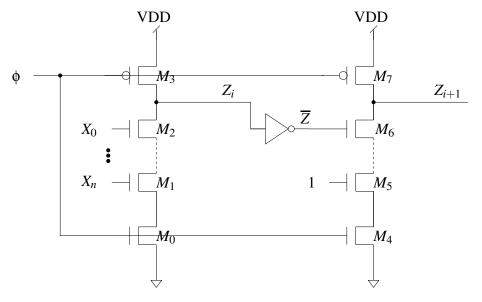

| 1.4    | Dynamic Logic NAND Gate                                      | 12   |

| 1.5    | Premature Discharge in Dynamic Logic                         | 13   |

| 1.6    | Domino Logic Circuit                                         | 14   |

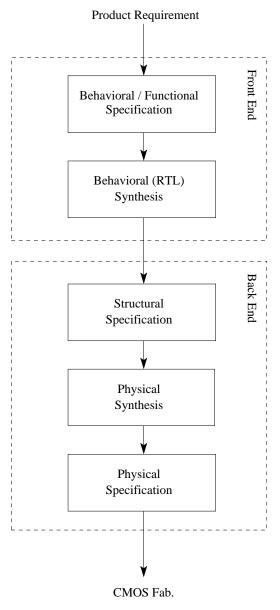

| 1.7    | ASIC Design Flow                                             | 15   |

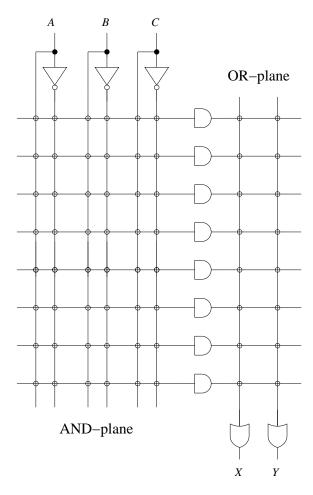

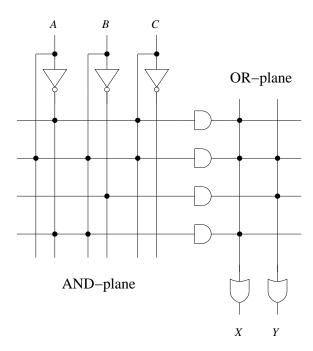

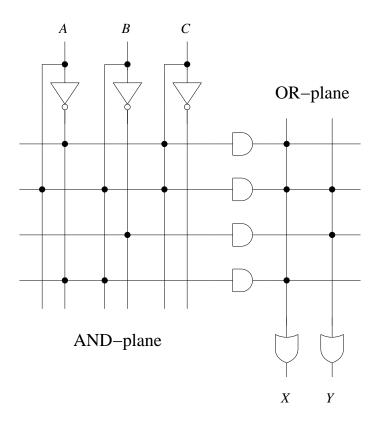

| 1.8    | Generic PLA Structure                                        | 17   |

| 1.9    | Example PLA Structure That Implements the Function $G_{3,2}$ | 19   |

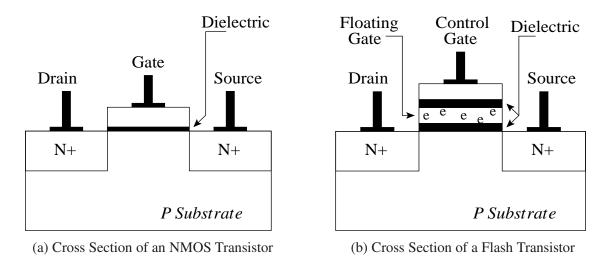

| 1.10   | NMOS and Flash Device Structures                             | 20   |

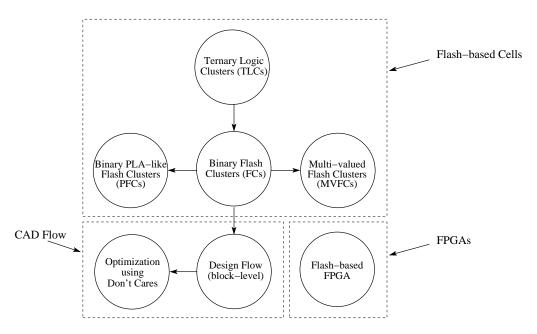

| 2.1    | Thesis Outline Diagram                                       | 26   |

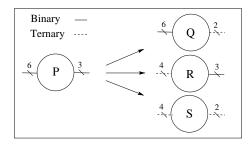

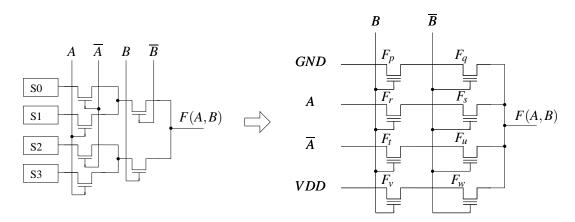

| 3.1    | Types of Ternary Logic Nodes in Our Implementation           | 37   |

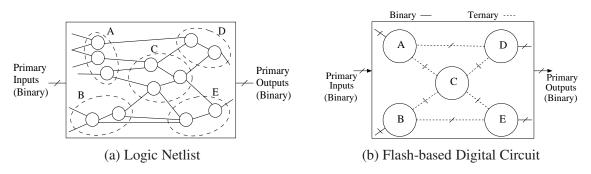

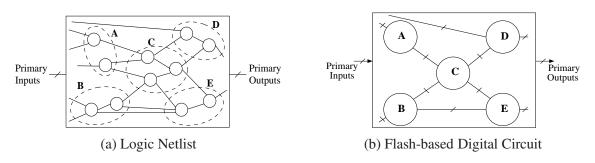

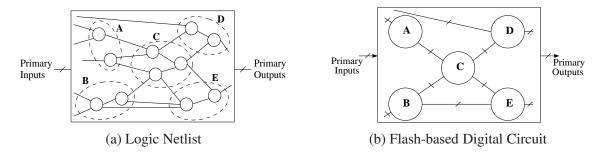

| 3.2    | Converting a Logic Netlist into a Flash-based Design         | 38   |

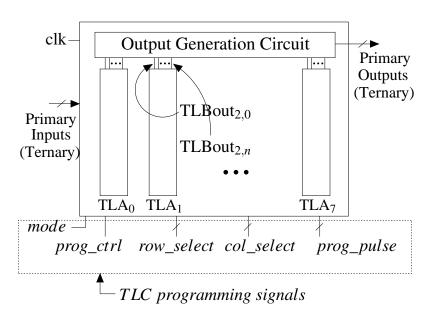

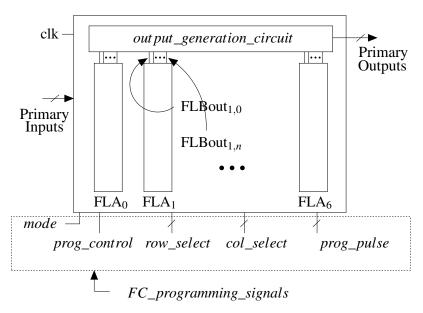

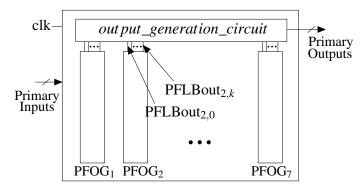

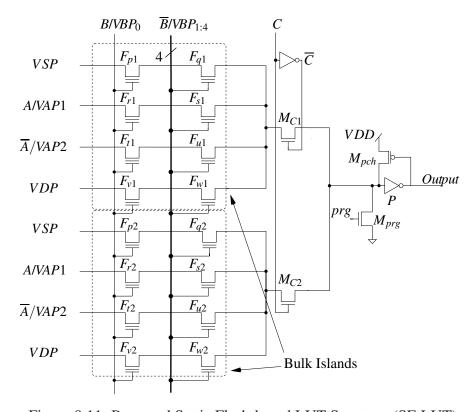

| 3.3    | Ternary Logic Cluster (TLC)                                  | 40   |

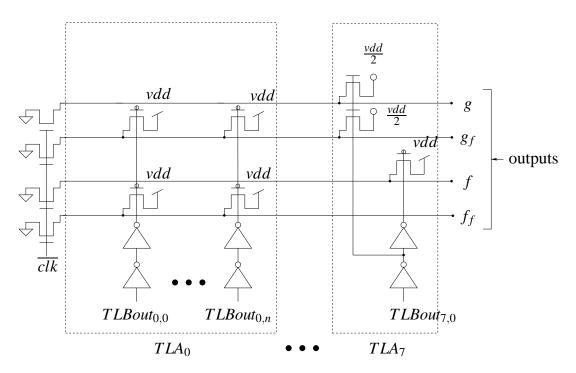

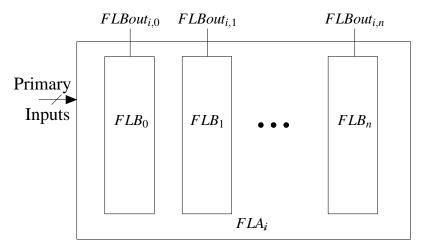

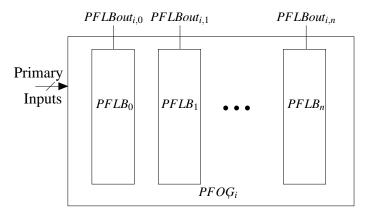

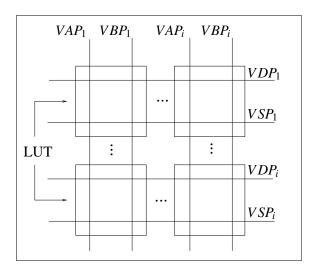

| 3.4    | $i^{th}$ Ternary Logic Array (TLA <sub>i</sub> ) Structure   | 42   |

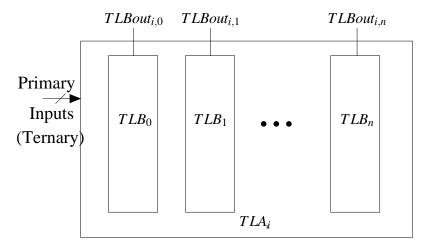

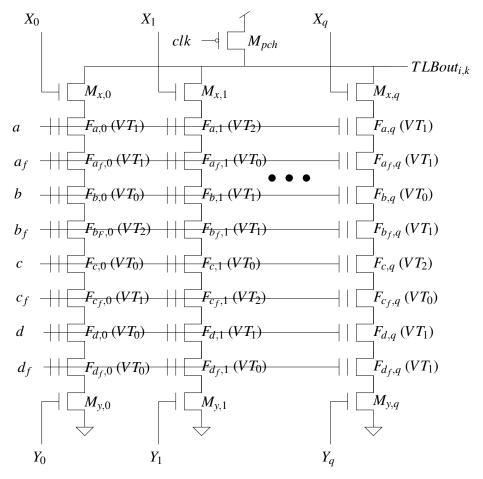

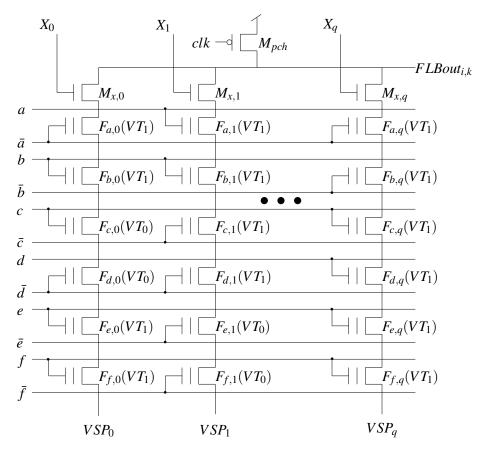

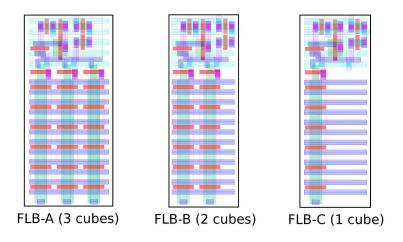

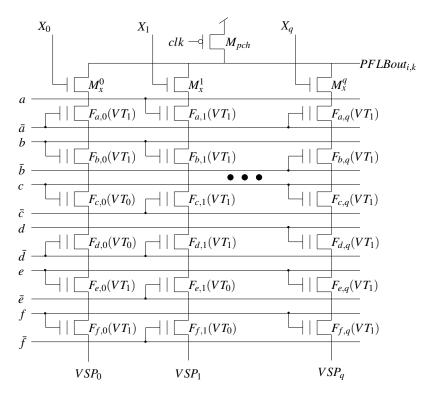

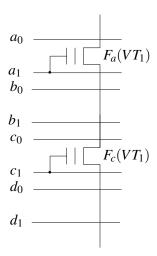

| 3.5    | $k^{th}$ Ternary Logic Bundle in $TLA_i$ ( $TLB_{i,k}$ )     | 43   |

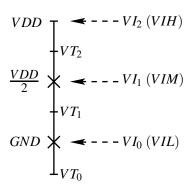

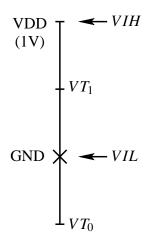

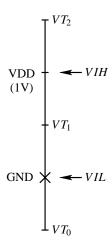

| 3.6    | Flash Transistor Threshold Voltages                          | 44   |

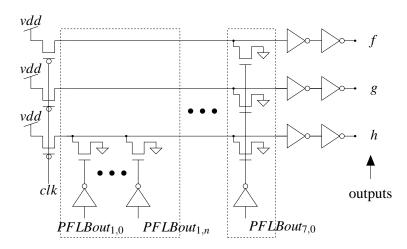

| 3.7    | Flash Output Generation Circuit                              | 47   |

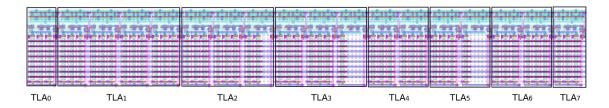

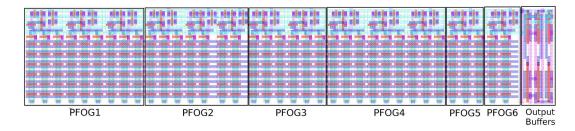

| 3.8    | Layout View of a TLC (des00)                                 | 53   |

| 4.1    | Converting a Logic Netlist into a Flash-based Design         | 59   |