# XDense: A Mesh Grid Sensor Network for Extreme Dense Sensing

## João Loureiro

Supervisor: Eduardo Médicis Tovar

Co-Supervisor: Raghuraman Rangarajan

Programa Doutoral em Engenharia Electrotécnica e de Computadores

## Faculdade de Engenharia da Universidade do Porto

## **XDense: A Mesh Grid Sensor Network for Extreme Dense Sensing**

## João Loureiro

Dissertation submitted to Faculdade de Engenharia da Universidade do Porto to obtain the degree of

#### **Doctor Philosophiae in Electrical and Computer Engineering**

President: José Silva Matos

External referee: Leandro Indrusiak External referee: Jean-luc Scharbarg

Referee: Paulo Portugal Referee: João Cardoso

Supervisor: Eduardo Tovar

## **Abstract**

We introduce XDense, a novel sensor network system for application scenarios that could benefit from densely physically deployed sensors. More specifically, XDense was conceived for cyber-physical systems (CPS) that require real-time dense sensing, for example, involving hundreds of sensors per square meter in real-time.

We motivate our work by presenting CPS application scenarios that could potentially benefit of dense sensor networks, which are currently limited by available technology. Out of the different application fields we discuss, we give special focus to aviation. More specifically, we focus on active flow control (AFC) on aircraft wing surfaces. We aim at providing means of sampling data with a high spatial and temporal granularity about the air flowing through an aircraft wing, so that active control over the aerodynamics of the wing is feasible.

The XDense architecture consists of a wired 2D-mesh grid network that provides it distributed processing capabilities, that are used to enable real-time complex environmental data extraction in a distributed fashion. It resembles Networks-on-Chip (NoC) architecture, principles of operation and temporal behavior. The similarities and differences are discussed.

We detail XDense's node and network architecture, protocols, and principles of operation. We evaluate the performance of XDense in fluid dynamic application scenarios with extensive experiments on sensing and feature detection capabilities.

We also tackle the issue of time predictability of XDense. We present a methodology that uses traffic shaping heuristics to guarantee bounded communication delays while fulfilling memory constraints. We evaluate the model for multiple network configurations and workloads, and present a comparative performance analysis in terms of link utilization, queue size and execution time. With the proposed traffic shaping heuristics, we endow XDense with the capabilities required for real-time applications.

We also discuss the practical issues involved in implementing XDense and the steps for its experimental validation. A prototype node and a test-bed was implemented to validate our assumptions and to assess the performance capabilities.

**Keywords:** Real-time Embedded Systems, Real-time Communication, Traffic Shaping, Feature Detection, Distributed Computing, Dense Sensor Networks, Active Flow Control.

## Resumo

Apresentamos o XDense, um novo sistema de rede de sensores para cenários que poderiam se beneficiar de instalações densas de sensores. Mais especificamente, o XDense foi concebido para sistemas ciber-físicos (CPS) que requerem operação em tempo real, por exemplo, para amostrar milhares de sensores por metro quadrado em tempo real.

Motivamos nosso trabalho apresentando cenários de aplicação dos CPS que poderiam beneficiar de redes densas de sensores, que atualmente são limitadas pela tecnologia disponível. Dos diferentes campos de aplicação que discutimos, damos especial atenção à aviônica. Mais especificamente, nos concentramos no controle de fluxo ativo (AFC) nas superfícies das asas das aeronaves. Nosso objetivo é fornecer meios de amostragem de dados com alta granularidade espacial e temporal sobre o ar que flui através de uma asa de aeronave, para que o controle ativo sobre a aerodinâmica da asa seja viável.

A arquitetura XDense consiste em uma rede de malha 2D, com fio, que fornece recursos de processamento distribuído, que são usados para permitir a extração de dados ambientais complexos em tempo real de maneira distribuída. Esta arquitectura se assemelha à arquitetura das Network-on-Chip (NoCs), aos seus princípios de operação e comportamento temporal. As semelhanças e diferenças são discutidas.

Nós detalhamos o projeto do XDense e a arquitetura de rede, protocolos e princípios de operação. Avaliamos o desempenho do XDense em cenários de aplicação de dinâmica de fluidos com experimentação extensa em monitorização e estração de detalhes de sinais físicos.

Também abordamos a questão da previsibilidade temporal do XDense. Apresentamos uma metodologia que utiliza heurísticas de modelação de tráfego de comunicação para garantir atrasos de comunicação limitados e o cumprimento dos requisitos de memória. Avaliamos o modelo para diferentes configurações de rede e carga de trabalho e apresentamos uma análise de desempenho comparativa em termos de utilização de "link", tamanho de fila e tempo de execução. Com a heurística de modelagem de tráfego proposta, nós possibilitamos aplicações em tempo real no XDense.

Também discutimos as questões práticas envolvidas na implementação do XDense e as etapas para sua validação experimental. Um nó protótipo e um banco de testes são implementados para validar nossas suposições e para a medição de desempenho.

**Keywords:** Sistemas Embarcados em Tempo Real, Comunicação em Tempo Real, Modelagem de Tráfego, Detecção de Recursos, Computação Distribuída, Redes de Sen-

sores Densos, Controle de Fluxo Ativo.

## Acknowledgments

First and foremost, I would like to thank my supervisor, Eduardo Tovar for his support during my PhD. Despite his busy schedule as the director of CISTER, he was always available to advise. I am thankful for the opportunity to conduct my PhD in such prestigious laboratory.

I thank Raghuraman Rangarajan for his guidance during my PhD. He was very helpful on the development, maturing and consolidation of ideas. His support in writing was also fundamental. It helped me greatly to develop a critical sense of scientific writing.

I express my gratitude to Borislav Nicolic, Shashank Gaur, Vikram Gupta and Vicent Nélis, who were available to discuss and develop ideas. Pedro Santos also helped greatly with the programming tasks related to the development and experimentation with the hardware prototypes. It was a pleasant experience to co-work with them. Their knowledge and advises were clearly beneficial to my learning and overall PhD experience. Several contributions in this Thesis resulted from collaborations with other researchers in CISTER, to which I am grateful.

I thank to Inês and Sandra who contributed in administrative and everyday bureaucracy.

I thank my family for their support, and for understanding my absence in important moments due to our physical distance. Finally, and most importantly, I would like to thank my beloved wife Sandra Montes, for her support, encouragement, patience and unwavering love. I dedicate this work to my son Gabriel, who was born meanwhile, and brought the most joyful moments of my life.

João Loureiro

<sup>&</sup>lt;sup>1</sup>This work was supported by CNPq (Brazilian National Council for Scientific and Technological Development) under the PhD grant 201176/2012-2.

## **Publications related with the Thesis**

- E. Tovar, N. Pereira, I. Bate, L. Indrusiak, S. Penna, J. Negrão, J. C. Viana, F. Philipp, D. Mayer, J. Heras et al., "Networked embedded systems for active flow control in aircraft," in Proceedings of the 11th International Workshop on Real-Time Networks (RTN 2012). 10, Jul, 2012. Pisa, Italy.

- J. Loureiro, N. Pereira, P. Santos, and E. Tovar, "A sensing platform for high visibility of the datacenter." in Proceedings of the 4th International Workshop on Networks of Cooperating Objects for Smart Cities 2013 (CONET/UBICITEC 2013). 8, Apr, 2013. Philadelphia, PA, U.S.A.

- J. Loureiro, V. Gupta, N. Pereira, E. Tovar, and R. Rangarajan, "XDense: A sensor network for extreme dense sensing," Proceedings of the Work-In-Progress Session at the 2013 IEEE Real- Time Systems Symposium RTSS, pp. 19–20, 2013.

- J. Loureiro, N. Pereira, P. Santos, and E. Tovar, "Experiments with a sensing platform for high visibility of the data center," in Internet of Things Based on Smart Objects, ser. Internet of Things, G. Fortino and P. Trunfio, Eds. Springer International Publishing, 2014, pp. 181–198.

- N. Pereira, S. Tennina, J. Loureiro, R. Severino, B. Saraiva, M. Santos, F. Pacheco, and E. Tovar, "A microscope for the data center," International Journal of Sensor Networks, 2015.

- J. Loureiro, R. Rangarajan, and E. Tovar, "Demo abstract: Towards the development of XDense, a sensor network for dense sensing," Poster presented in 12th European Conference on Wireless Sensor Networks (EWSN 2015). 9 to 11, Feb, 2015, pp 23-24. Porto, Portugal.

- J. Loureiro, R. Rangarajan, and E. Tovar, "XDense: A dense grid sensor network for distributed feature extraction," 330 Simpósio Brasileiro de Redes de Computadores e Sistemas Distribuídos (SBRC 2015) Workshop de Comunicação em Sistemas Embarcados Críticos (WoCCES), 2015.

- J. Loureiro, M. Albano, T. Cerqueira, R. Rangarajan and E. Tovar, "A module for the XDense architecture in ns-3," Demo in Workshop on ns-3 (WNS3 2015). 13 to 14, May,

- 2015. Castelldefels, Spain.

- J. Loureiro, R. Rangarajan, and E. Tovar, "Distributed sensing of fluid dynamic phenomena with the XDense sensor grid network," Proceedings of the IEEE International Conference on Cyber Physical Systems, Networks and Applications (CPSNA'15). 19 to 21, Aug, 2015. Hong Kong, China.

- J. Loureiro, R. Rangarajan, B. Nikolic, L. Indrusiak, and E. Tovar. 2017. "Real-time dense wired sensor network based on traffic shaping". In proceedings of the 23rd IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA). 16 to 18, Aug, 2017. Hsinchu, Taiwan. 1–10. https://doi.org/10.1109/RTCSA.2017.8046307

- J. Loureiro, P. J. Santos, R. Rangarajan, E. Tovar, "Simulation Module and Tools for XDense Sensor Network". In proceedings of the Workshop on NS-3 (WNS3'17). 13 to 14, Jun, 2017, pp 110-117. Porto, Portugal.

- R. Robles, J. C. Viana, J. Loureiro, J. Cintra, A. Rocha, E. Tovar, "Active Flow Control using Dense Wireless Sensor and Actuator Networks". In proceedings of Microprocessors and Microsystems: Embedded Hardware Design (MICPRO), Elsevier. 2018, Volume 61, pp 279-295.

- Loureiro J, Rangarajan R, Nikolic B, Soares Indrusiak L, Tovar E. "Extensive Analysis of a Real-Time Dense Wired Sensor Network Based on Traffic Shaping". ACM Transactions on Cyber-Physical Systems. https://doi.org/10.1145/3230872.

## **Contents**

| Li | st of l | Figures                                                             | xvii |

|----|---------|---------------------------------------------------------------------|------|

| Li | st of ' | Tables                                                              | xix  |

| Li | st of A | Abbreviations                                                       | xxii |

| 1  | Intr    | roduction                                                           | 1    |

|    | 1.1     | Motivation and Challenges                                           | 2    |

|    | 1.2     | Thesis Statement                                                    | 5    |

|    | 1.3     | System Requirements and Proposed Approach                           | 6    |

|    | 1.4     | Methodology                                                         | 9    |

|    | 1.5     | Thesis Structure                                                    | 10   |

| Ι  | Ba      | ckground                                                            | 11   |

| 2  | App     | olications and Technology Enablers                                  | 13   |

|    | 2.1     | Introduction                                                        | 13   |

|    | 2.2     | Related Network Architectures                                       | 13   |

|    |         | 2.2.1 Computation Arrays                                            | 13   |

|    |         | 2.2.2 Many-core Systems and Networks on Chip                        | 14   |

|    |         | 2.2.3 Study Case: The Epiphany Processor                            | 19   |

|    | 2.3     | Dense Deployments of Sensors                                        | 21   |

|    |         | 2.3.1 Airflow Sensing                                               | 21   |

|    |         | 2.3.2 Other Dense Deployments of Sensor and Actuators               | 26   |

|    | 2.4     | Summary                                                             | 29   |

| 3  |         | vey of Distributed Data Processing Techniques for Dense Sensing     | 31   |

|    | 3.1     | Introduction                                                        | 31   |

|    | 3.2     | Feature Detection and Extraction                                    |      |

|    |         | 3.2.1 Using Many-core Processors                                    |      |

|    |         | 3.2.2 Feature Extraction in Sensor Networks                         |      |

|    | 3.3     | Real-time Communication                                             | 35   |

|    |         | 3.3.1 Real-time Guarantees for NoCs                                 | 35   |

|    |         | 3.3.2 Real-time Guarantees for General Purpose Networks Using Traf- |      |

|    |         | fic Shaping                                                         | 36   |

X CONTENTS

|    | 3.4  | Summ    | ary                                                              | 37  |

|----|------|---------|------------------------------------------------------------------|-----|

| II | Pr   | opose   | d Novel Design: XDense                                           | 39  |

| 4  | Netv | work D  | esign and Principles of Operation                                | 41  |

|    | 4.1  | Introd  | uction                                                           | 41  |

|    | 4.2  |         | ork Design                                                       |     |

|    |      | 4.2.1   | Networking Device                                                | 43  |

|    |      | 4.2.2   | Router                                                           | 44  |

|    |      | 4.2.3   | Processor                                                        | 44  |

|    |      | 4.2.4   | Sensor                                                           | 45  |

|    | 4.3  | Assun   | nptions and System Definitions                                   | 45  |

|    |      | 4.3.1   | Network Temporal Behavior                                        | 45  |

|    |      | 4.3.2   | Packet Structure                                                 | 46  |

|    |      | 4.3.3   | Addressing                                                       | 47  |

|    | 4.4  | Netwo   | orking Protocols                                                 | 48  |

|    |      | 4.4.1   | Routing Protocols                                                | 48  |

|    |      | 4.4.2   | Communication Protocols                                          | 50  |

|    |      | 4.4.3   | Application Protocols                                            | 57  |

|    | 4.5  | Examp   | ple Scenario                                                     | 59  |

|    | 4.6  | Concl   | uding Remarks                                                    | 60  |

| 5  | Sim  | ulation | Model for Fluid Dynamics Sensing                                 | 61  |

|    | 5.1  | Introd  | uction                                                           | 61  |

|    | 5.2  | Simula  | ation Model                                                      | 61  |

|    |      | 5.2.1   | Pre-processing Tools                                             |     |

|    |      | 5.2.2   | Post-processing Tools                                            |     |

|    | 5.3  | Perfor  | mance Evaluation With Airflow Input Data                         |     |

|    |      | 5.3.1   | Distributed Application Execution                                |     |

|    |      | 5.3.2   | Experiment I: Sensing Compressed Static CFD Data                 |     |

|    |      | 5.3.3   |                                                                  |     |

|    |      | 5.3.4   | Experiment III: Detecting Transition Region on Static Image Data |     |

|    |      | 5.3.5   | Experiment IV: Sensing Temporal CFD Data                         |     |

|    | 5.4  | Concl   | uding Remarks                                                    | 91  |

| 6  | Ana  | •       | Model for Real-time Sensing Using Traffic Shaping                | 93  |

|    | 6.1  |         | uction                                                           | 93  |

|    | 6.2  |         | cation Execution                                                 |     |

|    |      | 6.2.1   | Clustering Nodes                                                 |     |

|    |      | 6.2.2   | Temporal Isolation Through Phases                                |     |

|    |      | 6.2.3   | Spatial Isolation Through Routing Schemes                        |     |

|    | 6.3  |         | ime Networking Model                                             |     |

|    |      | 6.3.1   | Shaping Flows and Traffic Throughout the Network                 |     |

|    |      | 6.3.2   | Shaping Traffic at a Single Output Port                          |     |

|    |      | 6.3.3   | Worst-case Per-hop Delays and Maximum Queue Sizes                | 103 |

*CONTENTS* xi

|    | 6.4   | Validation Example                                                | 6 |

|----|-------|-------------------------------------------------------------------|---|

|    | 6.5   | Evaluation of Traffic Shaping Heuristics                          |   |

|    |       | 6.5.1 Maximum queue size with homogeneous load distribution 10    | 9 |

|    |       | 6.5.2 Phase execution time for homogeneous load distribution 11   | 2 |

|    |       | 6.5.3 Maximum queue size with heterogeneous load distribution 11  | 4 |

|    |       | 6.5.4 Phase execution time for heterogeneous load distribution 11 |   |

|    | 6.6   | Concluding Remarks                                                |   |

| 7  | Har   | dware Implementation and Performance Evaluation 12                | 1 |

|    | 7.1   | Introduction                                                      | 1 |

|    | 7.2   | Hardware Design                                                   |   |

|    | 7.3   | System Requirements                                               |   |

|    | 7.4   | Design Decisions                                                  |   |

|    |       | 7.4.1 Composing an FPGA XDense node                               |   |

|    |       | 7.4.2 Microcontroller Based XDense Node                           |   |

|    | 7.5   | Performance Evaluation and Comparison                             |   |

|    |       | 7.5.1 Experiment 1: Single Hop Delay                              |   |

|    |       | 7.5.2 Experiment 2: Multi-hop Delay                               |   |

|    |       | 7.5.3 Current Limitations                                         |   |

|    | 7.6   | Concluding Remarks                                                |   |

| 8  | Con   | clusions and Future Directions 13                                 | 9 |

|    | 8.1   | Summary of Contributions                                          | 9 |

|    | 8.2   | Future Directions                                                 |   |

| D' |       | . 1                                                               | 3 |

| Вl | DHOGI | raphy 14                                                          | Í |

## **List of Figures**

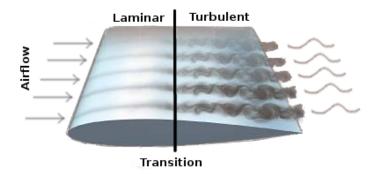

| 1.1 | Example fluid dynamic application scenario: Airflow over a wing surface exhibiting transition from laminar to turbulent flow                                                                                                                                                                                                                                    | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

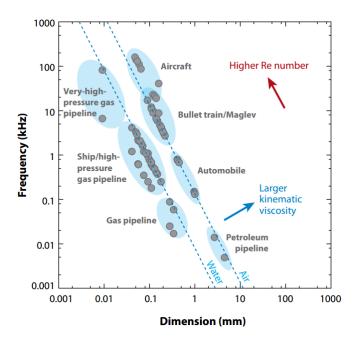

| 1.2 | Spatial and temporal scales of coherent structures in various applications. Closed circles correspond to a 30 wall-unit length and 0.01 wall-unit frequency in different applications. Ovals represent different application groups. The figure is taken from [1]                                                                                               | 4  |

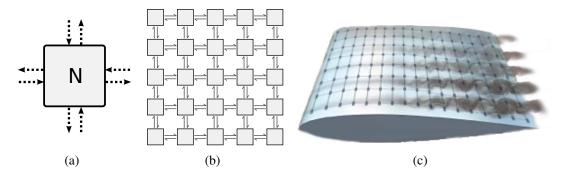

| 1.3 | Proposed XDense network: (a) A single node with four ports in the four directions; (b) Example of a $5 \times 5$ mesh grid network; (c) Deployment envisioned for XDense                                                                                                                                                                                        | 6  |

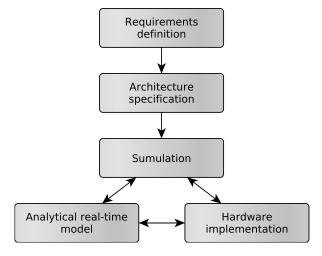

| 1.4 | Tasks to be executed iteratively for the completeness of this research                                                                                                                                                                                                                                                                                          | 8  |

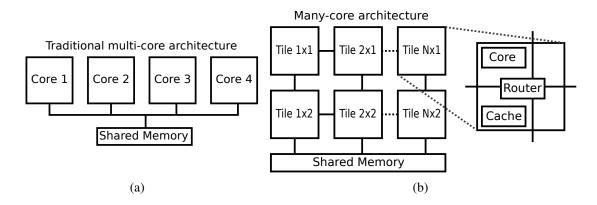

| 2.1 | (a) Multi-core vs. (b) many-core systems                                                                                                                                                                                                                                                                                                                        | 15 |

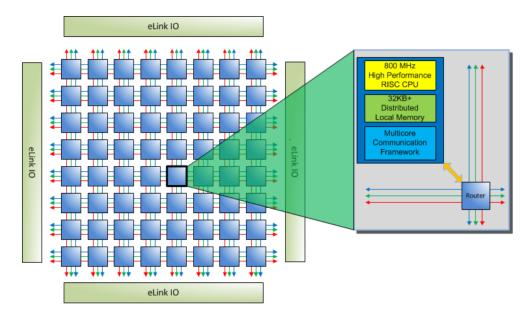

| 2.2 | Epiphany processor internals. It shows 64 cores interconnected by a mesh grid NoC. Each node on the network consists of a router, CPU, Memory and communication framework.                                                                                                                                                                                      | 19 |

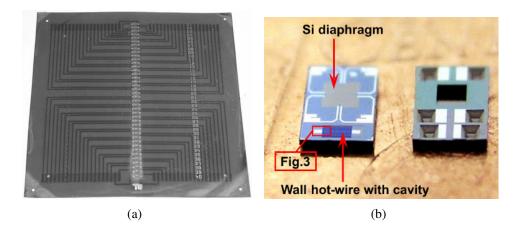

| 2.3 | (a) A linear array of forty of the same MEMS sensors mounted on a polymer foil; (b) pressure sensor diaphragm and a hot-wire MEMS sensors on top of an Euro cent coin; (Figures taken from [2])                                                                                                                                                                 | 22 |

| 2.4 | Schematic representation of an aircraft concept with a multi-modal sensor networks embedded inside the composite structural components to enable "fly-by-feel" (Figure taken from [3]                                                                                                                                                                           | 24 |

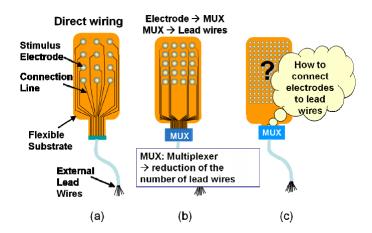

| 2.5 | (a-b) Different interconnection schemes of electrodes of a brain implantable stimulator and (c) the interconnections limitations faced as the number of electrodes scale. (Figure taken from [4])                                                                                                                                                               | 28 |

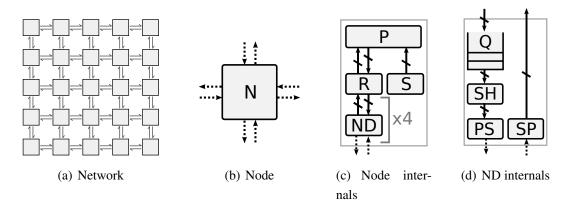

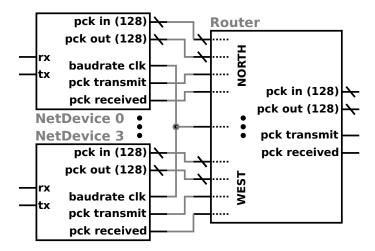

| 4.1 | Overview of XDense architecture. (a) It is a 2-D mesh network; (b) Node pinout: two channels per port for transmitting and receiving data; (c) Node internals: processor (P), router (R), net-device (ND) and the sensor (S); (d) net-device's internals: output queue (Q), traffic shaper (SH), and a parallel-to-serial/serial-to-parallel (PS/SP) converters | 42 |

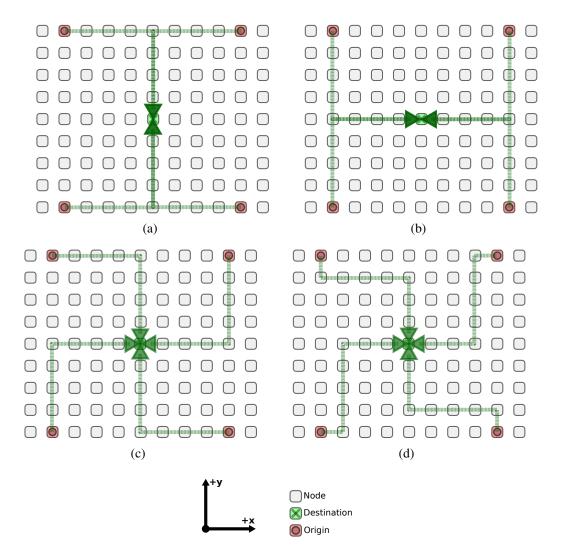

| 4.2 | Routing protocols - Nodes unicast to the node in the center using different routing algorithms: (a) XY; (b) YX; (c) Clockwise; (d) Shifted-clockwise.                                                                                                                                                                                                           | 49 |

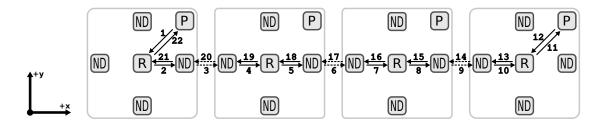

| 4.3 | Unicast example: Node on left requests data from node on right with a unicast request. The figure shows all internal logical steps taken in the                                                                                                                                                                                                                 | 49 |

|     | process of exchanging data between nodes                                                                                                                                                                                                                                                                                                                        | 51 |

xiv LIST OF FIGURES

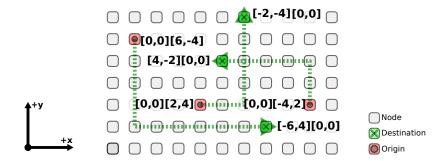

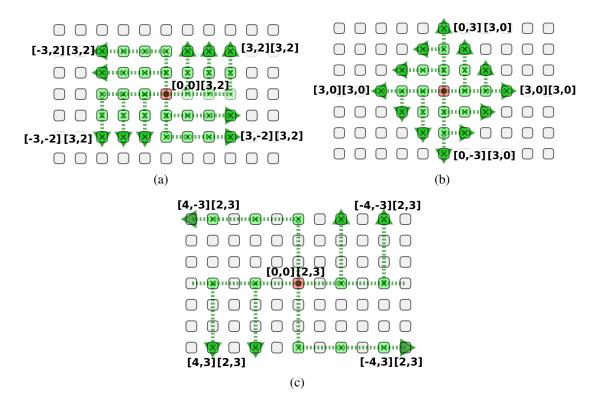

| 4.4  | Example of three concurrent and non-interfering unicast transmissions. The coordinate pairs inside the square brackets show the content of $[x_a, y_a]$ and $[x_b, y_b]$ respectively, at the origin and destination of the packet                                                                                                                                                                                                                                                                                                                                  | 52         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.5  | Multicast example - with relative addressing. The two coordinate pairs show the packet content of $x_a, y_a$ and $x_b, y_b$ at origin and destination                                                                                                                                                                                                                                                                                                                                                                                                               | 53         |

| 4.6  | Broadcast example: packet flow from origin to destination, using relative addressing scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56         |

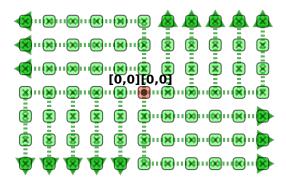

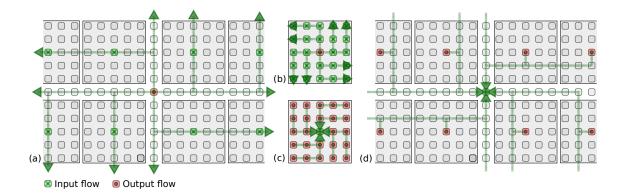

| 4.7  | Example of networking protocols utilization. The application execution consists of: (a) Nodes requests data from cluster of nodes using multicastalternative data request using counter-clockwise routing; (b) Cluster heads in turn request data from their cluster using multicast area with counter-clockwise routing; (c) Nodes unicast sensor data back to the requester using conter-clockwise routing; (d) Cluster heads process received data unicast it back to the requester using shifted couter-clockwise routing to avoid concurrency and contentions. | 59         |

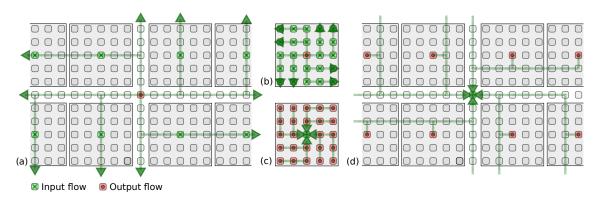

| 5.1  | XDenseSim list of classes and their hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63         |

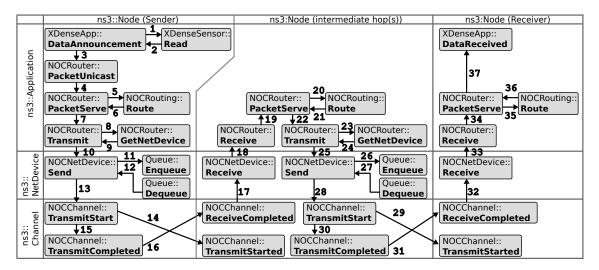

| 5.2  | XDenseSim example: main steps involved on the simulation of a <i>Data Announcement</i> between two nodes, unicast with one intermediate hop                                                                                                                                                                                                                                                                                                                                                                                                                         | 65         |

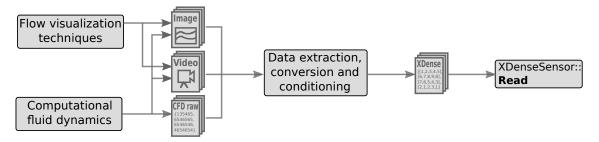

| 5.3  | Steps required to import data from different external sources into XDense sensor input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66         |

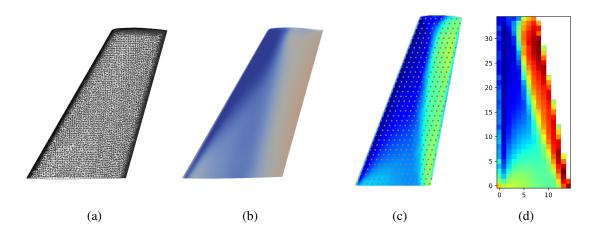

| 5.4  | sensor input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00         |

|      | each sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67         |

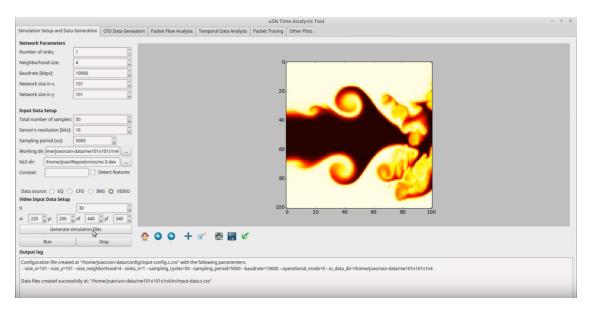

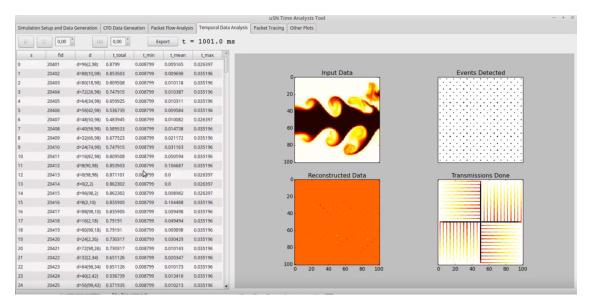

| 5.5  | Tool for generating temporal sensor data from a video files of a CFD simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68         |

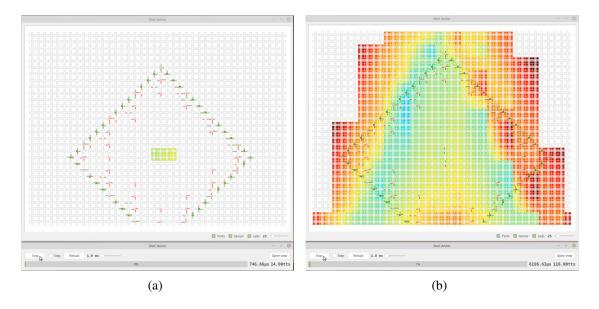

| 5.6  | The node in the center (sink) requests and receives back compressed data from clusters. (a) and (b) show different snapshots of the reconstruction of the data by the sink, as the data is received                                                                                                                                                                                                                                                                                                                                                                 | 69         |

| 5.7  | Packet trace (in the left) and extracted information on the right. It shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| 5 Q  | the input data and node's activity heatmaps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70         |

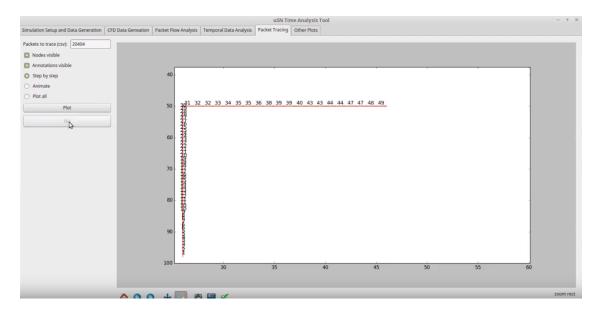

| 5.8  | Single packet trace. It shows the time instant at which each transmission occurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71         |

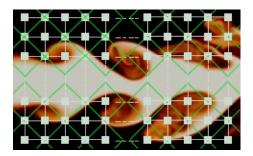

| 5.9  | XDense network superimposed on the CFD dataset snapshot from [6], showing clustering for $n_{\text{radius}} = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71         |

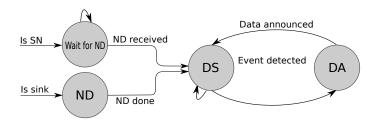

| 5.10 | State diagram for an XDense node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73         |

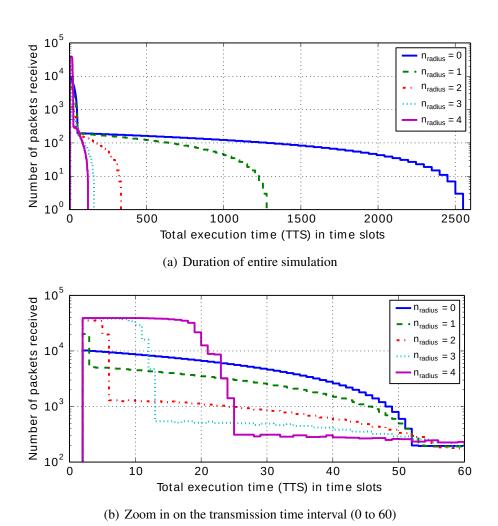

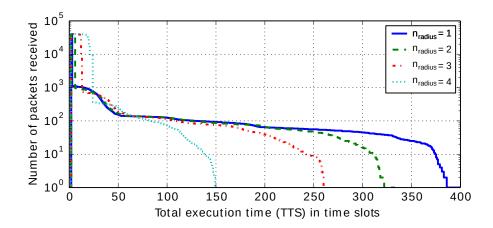

|      | Reading sensed data: Number of receptions over time for different values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|      | of $n_{\text{radius}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76         |

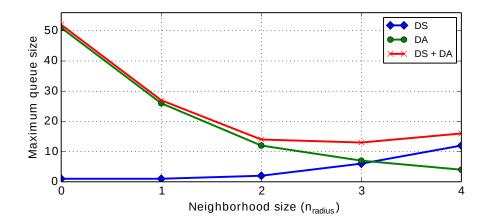

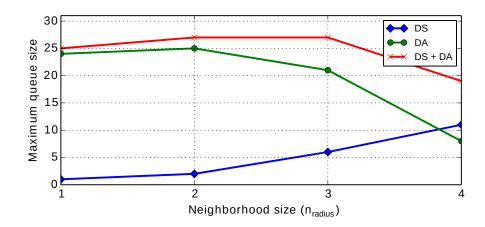

|      | Reading sensed data: Maximum queue size for $n_{\text{radius}} = 1$ to 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77         |

|      | Total number of packets transmitted in the network with $n_{\text{radius}} = 1$ to 4, using clustering ( <i>CL</i> )                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78         |

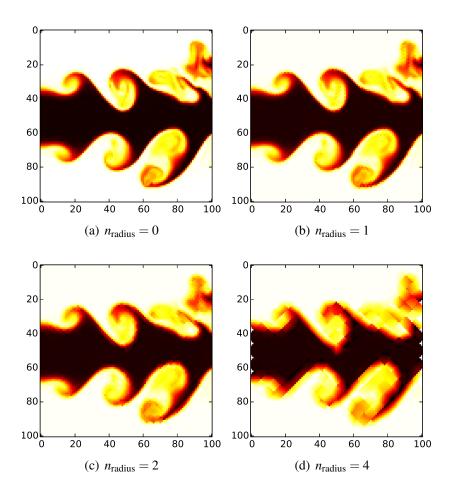

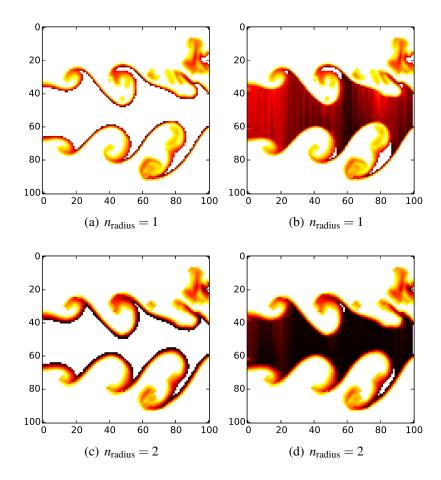

|      | Reading sensed data: Extracted data for different values of $n_{\text{radius}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79         |

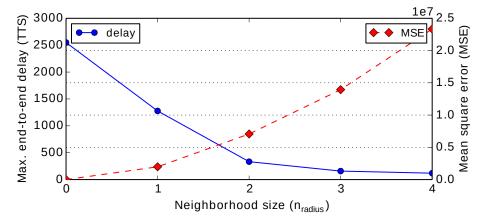

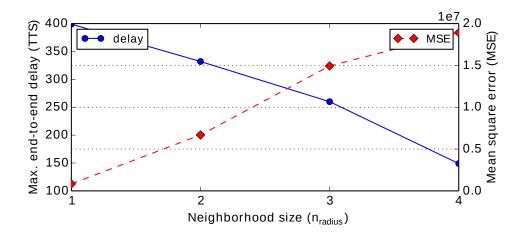

| 5.15 | Reading sensed data: Trade-off between mean square error and maximum acquisition delay delay for different values of $n_{\text{radius}}$                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>7</b> 9 |

LIST OF FIGURES xv

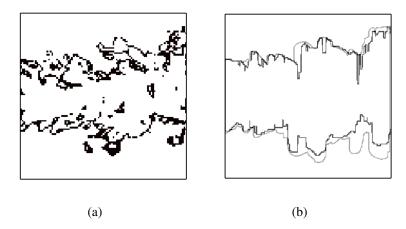

| 5.16 | Feature detection: Extracted boundary data, and reconstruction of boundary data for $n_{\text{radius}} = 1$ to 2                                                                                                                                                                                                                                                                                                                    | 81 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.17 | Feature detection: Extracted boundary data, and reconstruction of boundary data for $n_{\text{radius}} = 3$ to 4 for comparison                                                                                                                                                                                                                                                                                                     | 82 |

| 5.18 | Feature detection: Maximum queue size for $n_{\text{radius}} = 1 \text{ to } 4$                                                                                                                                                                                                                                                                                                                                                     | 83 |

| 5.19 | Feature detection: Number of receptions over time for different values of $n_{\text{radius}}$                                                                                                                                                                                                                                                                                                                                       | 83 |

| 5.20 | Feature detection: Trade-off between mean square error and maximum acquisition delay for different values of $n_{\text{radius}}$                                                                                                                                                                                                                                                                                                    | 83 |

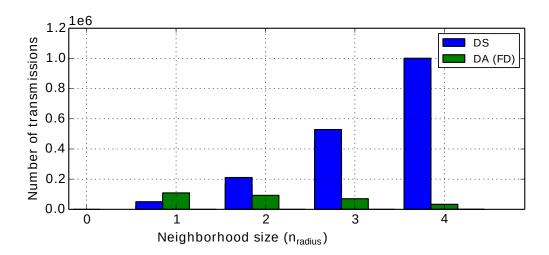

| 5.21 | Total number of packets transmitted in the network with $n_{\text{radius}} = 1$ to 4, using feature detection $(FD)$                                                                                                                                                                                                                                                                                                                | 84 |

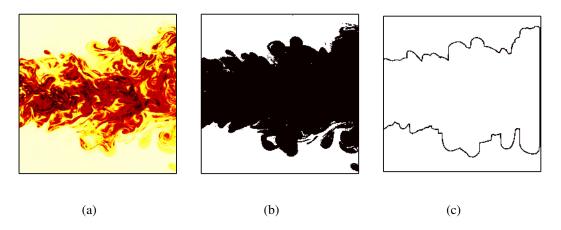

| 5.22 | Process steps for boundary computation described in [7]: (a) Original image; (b) binarized image; (c) contour tracing and contour smoothing.                                                                                                                                                                                                                                                                                        | 86 |

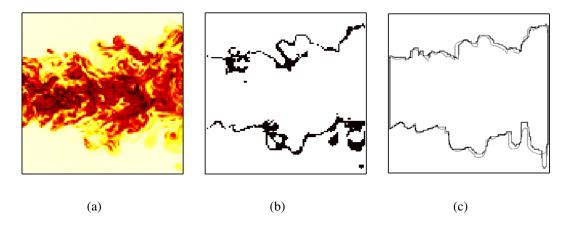

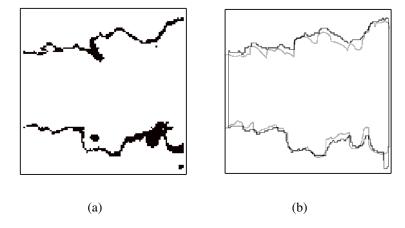

| 5.23 | Processing steps of our network. (a) Is the phenomena as seem by our network, after downsampling the full resolution image to $101 \times 101$ pixels. (b) is the gradient detection by the sensor nodes with $n_{\text{radius}} = 3$ , and (c) is the contour smoothing post-processing done by the sink                                                                                                                           | 86 |

| 5.24 | Processing steps of our network. (a) Transition region detection by the sensor nodes with $n_{\text{radius}} = 1$ , and (b) is the contour smoothing post-processing done by the sink in black, superimposed on $5.22(c)$                                                                                                                                                                                                           | 87 |

| 5.25 | Processing steps of our network. (a) Transition region detection by the sensor nodes with $n_{\text{radius}} = 7$ , and (b) is the contour smoothing post-processing done by the sink in black, superimposed on $5.22(c)$                                                                                                                                                                                                           | 87 |

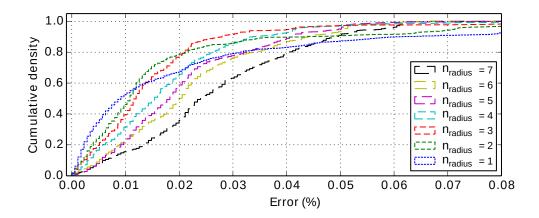

| 5.26 | Cumulative density function for different $n_{\text{radius}}$ , of the error between                                                                                                                                                                                                                                                                                                                                                | 88 |

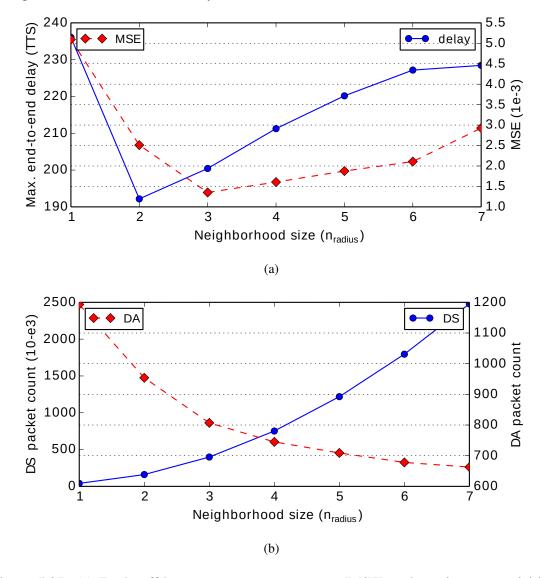

| 5.27 | (a) Trade-off between mean square error (MSE) and maximum acquisition delay (TTS) for different values of $n_{\rm radius}$ , and (b) is the total number of transmissions for the different protocols, for the same values of $n_{\rm radius}$ .                                                                                                                                                                                    | 88 |

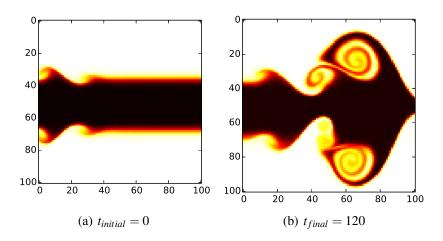

| 5.28 | Real-time sensing: Input data at (a) $t = 0$ and (b) $t = 120$ sampling time slots (STS)                                                                                                                                                                                                                                                                                                                                            | 89 |

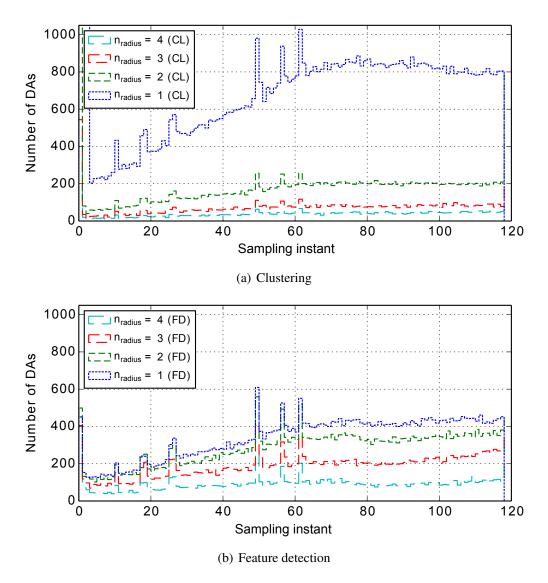

| 5.29 | Real-time sensing: Network activity, shown as number of $DAs$ per sampling instant, over 120 sampling instants, for $n_{\text{radius}} = 1$ to 4                                                                                                                                                                                                                                                                                    | 90 |

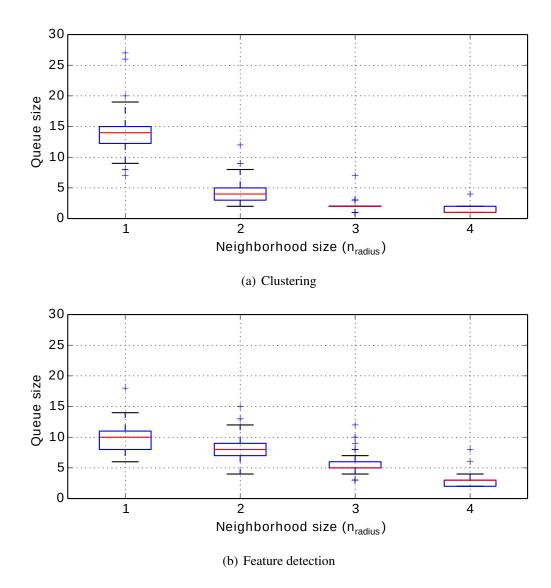

| 5.30 | Realtime sensing: $pI$ queue sizes for $n_{\text{radius}} = 1$ to 4                                                                                                                                                                                                                                                                                                                                                                 | 91 |

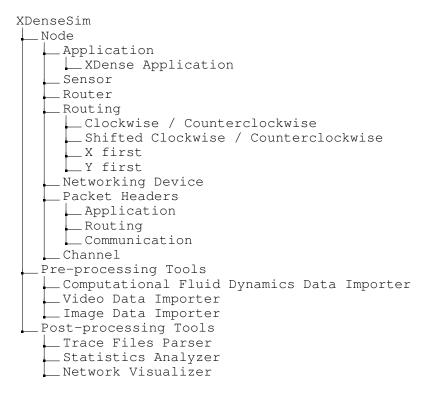

| 6.1  | Example $45 \times 45$ network, with a single central sink. In this case, with $n_{\text{radius}} = 2$ . Application phases: (a) $\phi_1$ – Sink requests data from cluster-heads; (b) $\phi_2$ – cluster-heads in turn send a multicast request to nodes in their cluster; (c) $\phi_3$ – Nodes send sensor data back to their respective cluster-head; (d) $\phi_4$ – cluster-heads process received data and send result to sink | 94 |

| 6.2  | Traffic shaper example scenario: two input flows shaped by an intermediate node as an output flow. Parameters for the input flows are $f_1 = \{O = 2.5, \beta = 1, \sigma = 10\}$ and $f_2 = \{O = 1, \beta = \frac{1}{5}, \sigma = 3\}$ . The resulting flow is $f_3 = \{O = 2, \beta = \frac{1}{2}, \sigma = 13\}$                                                                                                                | 98 |

xvi LIST OF FIGURES

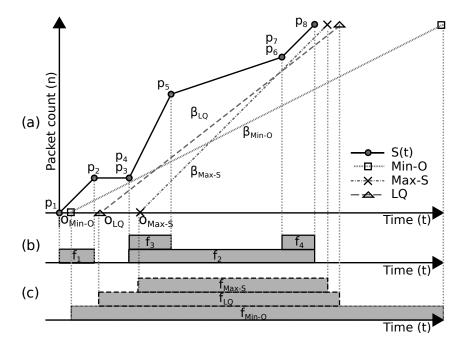

| 6.3                                | Traffic shaping heuristics: (a) input, and output flows using the proposed heuristics; time-line showing offset and duration of (b) arriving flows and (c) departure flows                                                                                                                                                              |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

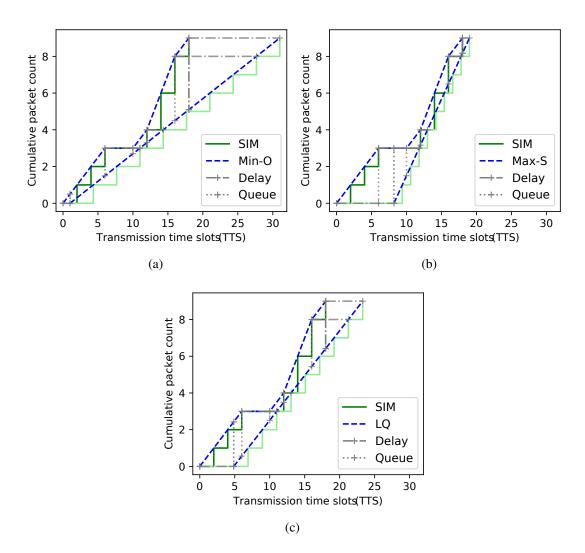

| 6.4                                | Cumulative arrival/departure curves for a single node, using (a) Min-O, (b) Max-S and (c) LQ heuristics                                                                                                                                                                                                                                 |

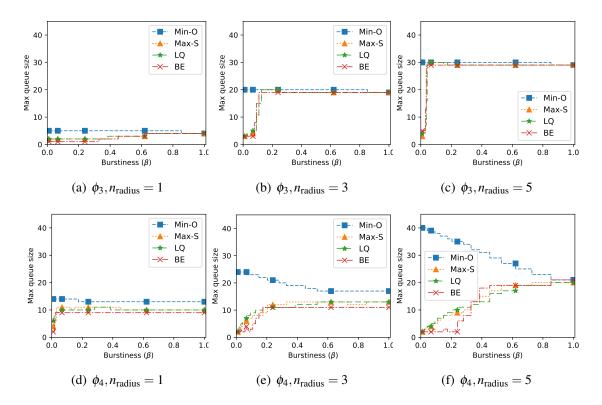

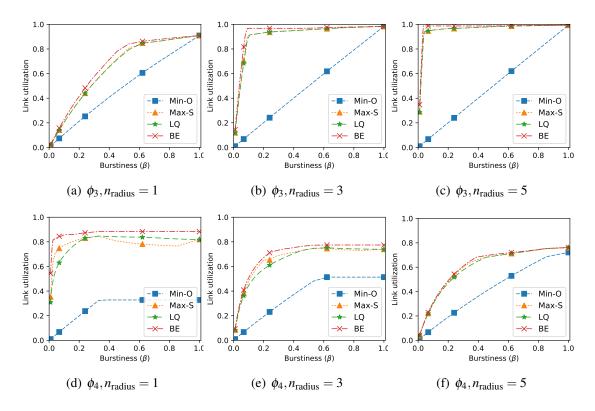

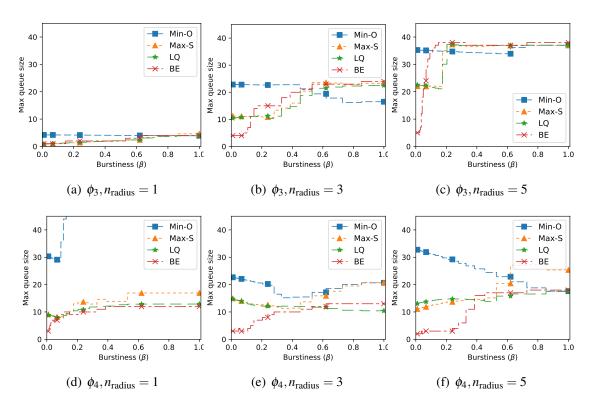

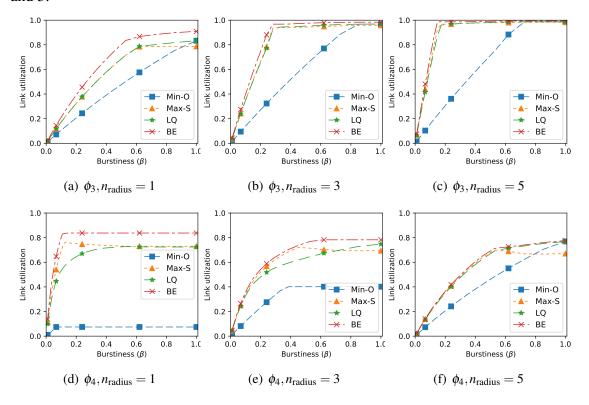

| 6.5                                | Homogeneous flow scenario: Maximum queue size for traffic shaping heuristics against simulation. Results are for phases $\phi_3$ and $\phi_4$ and $n_{\text{radius}}$ set to 1, 3 and 5                                                                                                                                                 |

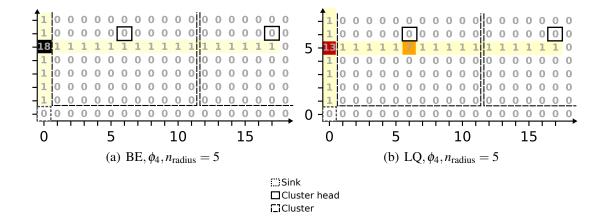

| 6.6                                | Queue size density map of the top-right quadrant of the network (17×7 nodes), for heuristics (a) LQ and (b) BE. X and Y axis are nodes coordinates relative to the sink                                                                                                                                                                 |

| 6.7                                | Homogeneous flow scenario: Link utilization for traffic shaping heuristics against simulation. Results are for phases $\phi_3$ and $\phi_4$ and $n_{\text{radius}}$ set to 1, 3 and 5                                                                                                                                                   |

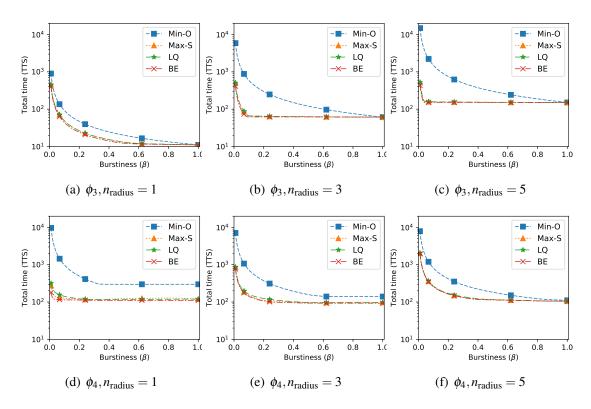

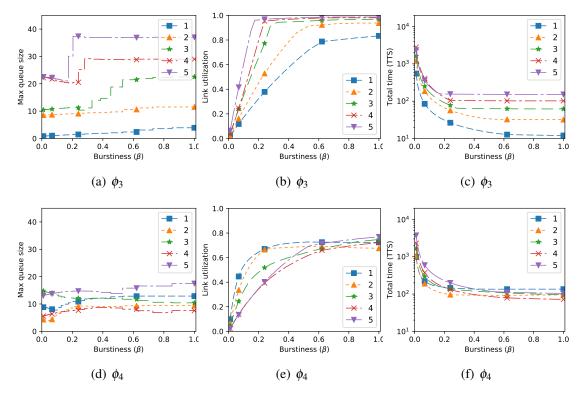

| 6.8                                | Homogeneous flow scenario: Execution time of phases $\phi_3$ and $\phi_4$ for traffic shaping heuristics against simulation                                                                                                                                                                                                             |

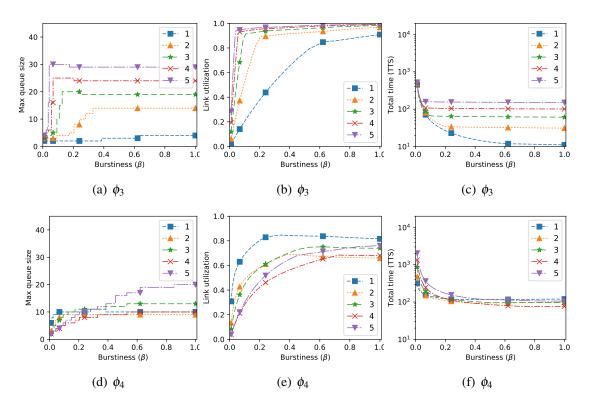

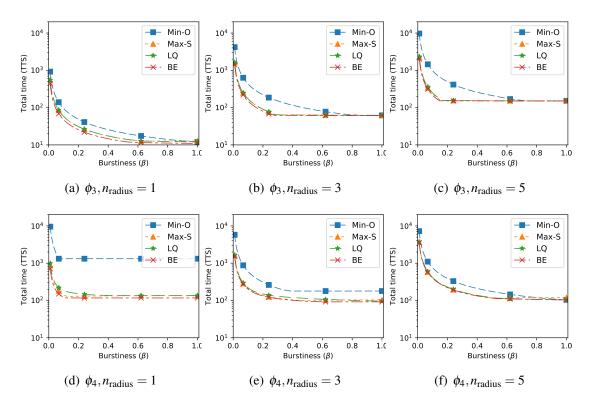

| <ul><li>6.9</li><li>6.10</li></ul> | LQ heuristic - (a) link utilization, (b) maximum queue size and (c) total execution time, with varying burstiness and $n_{\text{radius}} = [1, 2, 3, 4, 5]$ 114 Heterogeneous flow scenario: Maximum queue size for traffic shaping heuristics against simulation. Results are for phases $\phi_3$ and $\phi_4$ and $n_{\text{radius}}$ |

| 6.11                               | set to 1, 3 and 5                                                                                                                                                                                                                                                                                                                       |

| 6.12                               | 1, 2 and 5)                                                                                                                                                                                                                                                                                                                             |

| 6.13                               | Link utilization (a), maximum queue size (b) and total execution time (c) with varying burstiness, for the LQ heuristic only, for $n_{\text{radius}} = [1, 2, 3, 4, 5]$ . 118                                                                                                                                                           |

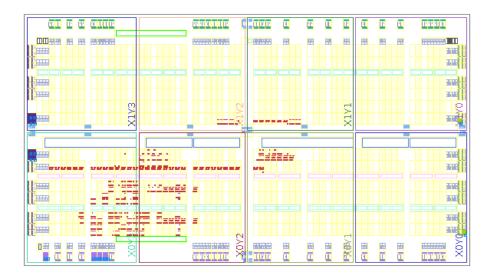

| 7.1                                | Simplified schematic of the XDense node's Switch and Net-Device implementation using on a FPGA                                                                                                                                                                                                                                          |

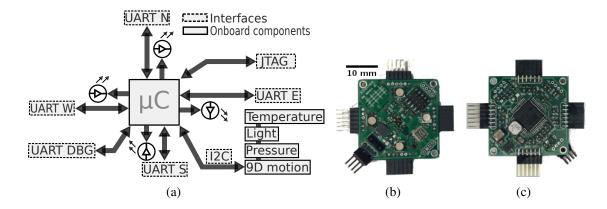

| 7.2<br>7.3                         | FPGA implementation: floor plan of the router and four networking devices. 126 (a) Node's schematic showing each of the major components of the system. (b) and (c) show the top and the bottom sides of the PCB, respectively.                                                                                                         |

| 7.4                                | tively                                                                                                                                                                                                                                                                                                                                  |

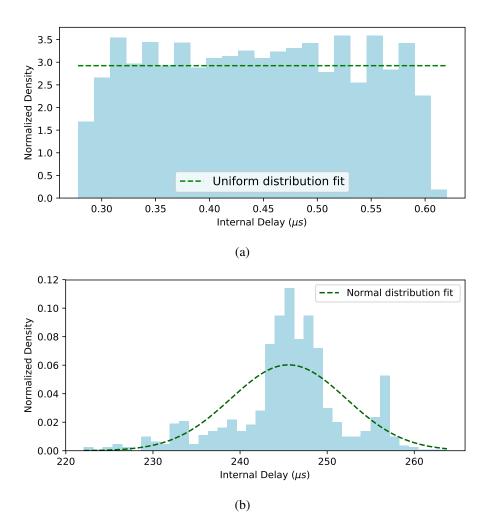

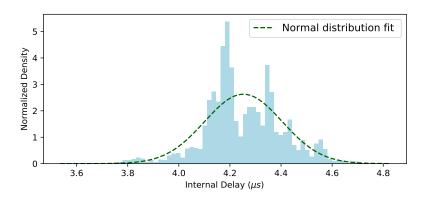

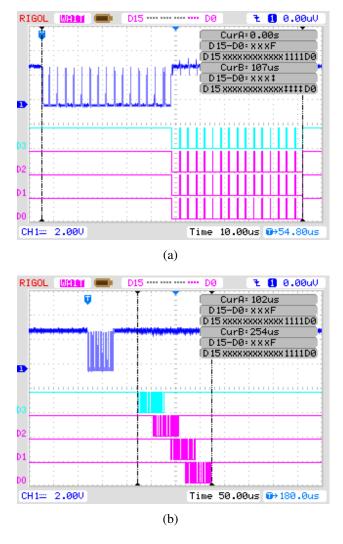

| 7.5                                | Packet forwarding internal delay on a single hop, using (a) a FPGA-based node and (b) a $\mu$ C-based node                                                                                                                                                                                                                              |

| 7.6                                | $3 \times 3$ testbed deployment                                                                                                                                                                                                                                                                                                         |

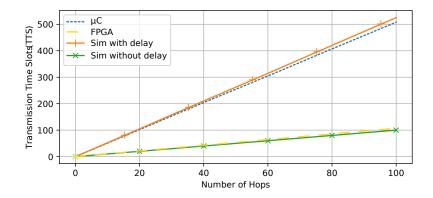

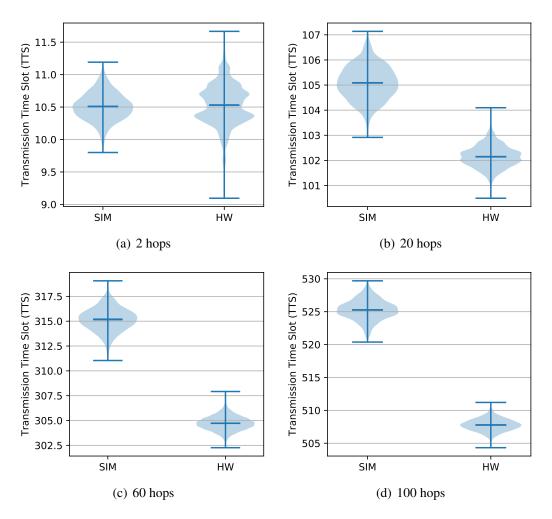

| 7.7                                | Average trip delay in a multi-hop scenario for varying trip distances 133                                                                                                                                                                                                                                                               |

| 7.8                                | Comparison between simulation and hardware of the packet trip delay distribution, for different number of hops                                                                                                                                                                                                                          |

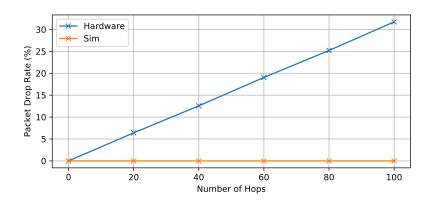

| 7.9                                | Packet drop ratio in a multi-hop scenario for varying trip distances 134                                                                                                                                                                                                                                                                |

| 7.10                               | Packet forwarding internal delay on a single hop without RTOS 135                                                                                                                                                                                                                                                                       |

LIST OF FIGURES xvii

| 7.11 | Waveform showing the internal delay due to concurrent transmissions on   |     |

|------|--------------------------------------------------------------------------|-----|

|      | (a) FPGA implementation and (b) $\mu$ C implementation. Note the differ- |     |

|      | ence in time scales                                                      | 136 |

## **List of Tables**

| 4.1 | Packet structure and size in bits, totaling 128 bits (16 bytes)           | 47  |

|-----|---------------------------------------------------------------------------|-----|

| 4.2 | List of routing protocols and content of the RP packet field              | 50  |

| 4.3 | Unicast example - Packet content at each numerated instant of Figure 4.3. | 51  |

| 4.4 | Unicast example - TTS: Transmission Time Slot (TTS) in which each         |     |

|     | logical step from the example of Figure 4.3 occur                         | 52  |

| 4.5 | List of communication protocols and content of the CP packet field        | 56  |

| 4.6 | List of application protocols and content of the AP packet field          | 59  |

| 5.1 | XDense simulation parameters                                              | 72  |

| 7.1 | FPGA implementation: Resource utilization due to XDense's communi-        |     |

|     | cation logic                                                              | 125 |

| 7.2 | Resource utilization of the Atmel ATSAM4N8 ARM Cortex M4 running          |     |

|     | XDense                                                                    | 127 |

| 7.3 | XDense testbed configuration                                              | 129 |

## List of Abbreviations

FEUP Faculdade de Engenharia da Universidade do Porto

AFC Active Flow Control

SJA Synthetic Jet Actuator

NS-3 Network-Simulator-3

MSE Mean square error

CDF Cumulative density function TTS Transmission time slots

DOR Dimensional ordered routing COTS Commercial off-the-shelf

FIFO First-in-first-out

ADC Analog-to-digital-converter

SN Sensor network

WSN Wireless sensor network COTS Commercial-of-the-shelf

IP Intellectual property

FIFO First-in-firs-out

MEMS Microelectromechanical systems

GPU Graphic processing units

CPU Central processing unit

LIDAR Light detection and ranging

MAC Media access control

BE Best-effort

GS Guaranteed service

MR Multicast radius

MT Multicast alternative

MA Multicast area

BC Broadcast

BC Guaranteed service

MSE Mean square error

xxii List of Abbreviations

|  | FPGA | Field | programmable | gate array |

|--|------|-------|--------------|------------|

|--|------|-------|--------------|------------|

$\mu$ C Microcontroller RP Routing protocol

CP Communication protocol

AP Application protocol

## Chapter 1

## Introduction

As a consequence of Moore's law, single embedded computers equipped with increasing processing, communication and sensing capabilities are tending to be minimally priced. This makes it economically feasible to deploy dense sensor networks with very large quantities of computing capable sensor nodes. Accordingly, it is possible to take a very large number of sensor readings from the physical world, perform computation on sensed quantities and take decisions from the results.

Very dense sensor networks can offer information about the physical world with greater spatial resolution. When associated with high temporal capabilities, such sensor networks can offer better opportunities in detecting the occurrence of dynamic events with high resolution on an observed natural phenomenon. This is of paramount importance for a number of applications with high spatial and temporal sensing resolution requirements. Some examples are: (i) airflow monitoring on aircraft wings [8]; (ii) fluid dynamic tests on under-water vehicles [9]; (iii) fine-grained structural monitoring [10]; (iv) biomedical devices for electroencephalogram [11]; (v) robotic e-skins [12]; (vi) health-monitoring wearable sensor networks [13] and others.

Such densely instrumented systems face serious scalability issues in many key aspects, such as: communication and processing time, predictability of time, interconnectivity, power requirements, reliability and cost [14]. Moreover, the need for high spatial and temporal resolutions are related, but are concurring requirements, which are difficult to address simultaneously.

Today's dense sensor deployments usually have each sensing element connected to a central digital processor, with multiplexed analogue inputs that allow reading each sensor individually [15]. This usually involves impractical complex wiring setups, in witch sensors are read at predefined time slots [16, 17].

Furthermore, collecting and processing data from a dense sensor network is costly

2 Introduction

in terms of communication and computation. Feature extraction is challenging and very difficult to achieve in real-time, hence prohibiting real-time dense sensing and its use in real-time applications.

Despite the various applications of dense sensor networks mentioned, in this thesis we focus on fluid dynamic applications and its related challenges. More specifically, we focus on airflow sensing on aircraft wings for active flow control (AFC); a scenario that benefits from such dense deployments of cyber-physical systems.

In the next section, we give an overview of the importance of airflow monitoring for AFC in aviation and its spatial and temporal requirements. We also discuss the involved challenges on implementing a sensing system for AFC.

## 1.1 Motivation and Challenges

In order to understand the importance of AFC, we first have to understand the benefits it can have in terms of flight costs reduction to the growing aerospatial industry.<sup>1</sup>

Cost reduction is often associated with the reduction of fuel consumption, which is important because of both environmental effects and cost efficiency. It is known from the Breguet range equation [19] that improvements in aerodynamics, engines, and structure have major importance in reducing weight and drag of the aircraft. In fact aerodynamic drag due to skin friction is known to be one of the main factors contributing to increased fuel consumption. It constitutes approximately one half of the total drag for a typical long range aircraft at cruise conditions [20].

A significant part of the skin friction is due to turbulent airflow over the wing [21]. Turbulent airflow is composed of coherent structures of chaotic temporal evolution, such as vortices. This chaotic behavior causes an increase in interaction between the air and the wing (and the fuselage, in general), and consequently an increase in total skin friction [22]. Turbulent airflow is usually undesirable on aircraft as it increases drag and noise, and consequently fuel expended [23].

The main cause of the occurrence of turbulent airflow on an aircraft, is the flow separation from the wing's surface. The airflow tends to separate from the solid surface due to its high speed and high inertial forces, that exceed the viscous-elastic forces that keep it attached to the surface. This excess causes its detachment from the surface of the wing, and creates a low pressure zone under the airflow. This difference is pressure leads the

<sup>&</sup>lt;sup>1</sup>According to the Airbus 2016-2035 Global Market Forecast, it is expected that until 2035 the world passenger traffic will nearly triple, and airlines will more than double their fleets of passenger aircraft (with over 100 seats) [18].

Figure 1.1: Example fluid dynamic application scenario: Airflow over a wing surface exhibiting transition from laminar to turbulent flow.

airflow into turbulent chaotic behavior as the air tends to spread and mix while flowing to the low pressure zone [24].

The region in which the separation initiates is called transition region. It is where the airflow transits from the laminar regime (with a more homogeneous speed profile distribution) to turbulent regime (with coherent structures of chaotic temporal evolution) [22].

In an aircraft, a high speed airflow over a wing can present both laminar and turbulent characteristics at the same time at different regions. Figure 1.1 shows an airflow over a wing surface, illustrating the transition region.

In order to minimize turbulent airflow, it is crucial to understand, distinguish, characterize and quantify the physical mechanisms taking place in the transition region. This is where the separation takes place and originate the turbulent airflow [25]. More importantly, in some applications, detecting where the transition takes place may be enough to enable efficient AFC.

Many studies have been conducted towards flow characterization and features extraction. A direct approach consists of developing sensor deployments to study the airflow by measuring its properties on-site, such as pressure, speed and temperature. However, in order to depict such phenomena with enough granularity, deployments of sensors with inter-space smaller than that of the spatial granularity of the observed phenomena may be required. That is for example, of  $100 \ \mu m$  or less, with sampling rates in excess of  $100 \ kHz$ . Figure 1.2 shows the spatial and temporal scales of coherent structures from different application scenarios.

Along these lines, in 2011, NASA proposed a design concept called "fly-by-feel" that also tries to address the challenge of dense sensing [26]. Their objective was to equip the next generation aircraft with a self-sensing capability via an integration of a dense network of sensors within the wing structure to achieve high spatial and temporal sensing resolutions.

4 Introduction

Figure 1.2: Spatial and temporal scales of coherent structures in various applications. Closed circles correspond to a 30 wall-unit length and 0.01 wall-unit frequency in different applications. Ovals represent different application groups. The figure is taken from [1].

A "fly-by-feel" system could measure the aerodynamic forces directly on the aircraft surfaces and use that information in a physics-based adaptive flight controls system to increase maneuverability, safety and fuel efficiency. In this way, the wing would be able to "feel", "think" and "react" in real-time for increased performance through autonomous control. Other advantages are also foreseen in [3], such as:

- structural complexity reduction by saving the efforts of large sensors installation;

- structural health monitoring through the embedded multi-functional sensor network;

- extreme conditions investigation and prevention for flight safety improvement;

- autonomous flight control for real-time optimum decision-making;

- maintenance cost reduction and structural design optimization.

Microelectromechanical systems (MEMS) are a technology with the potential to enable dense micro sensing, and are widely found in literature. More specifically to fluid dynamics, micro flow sensor arrays for AFC that try to meet such requirements are surveyed in [1].

1.2 Thesis Statement 5

However, as mentioned previously, such dense sensor deployments are challenged by the dynamics and complex nature of the data. Due to that, validations are usually done by individually connecting each of the many sensors to multiplexed channels of an analog-to-digital-converter (ADC), and data acquisition and analysis are limited to laboratory controlled conditions, with off-line data processing [27, 28, 29].

In order to achieve AFC, actuation technology is also required. A promising actuator technology that aims at doing that is the Synthetic Jet Actuator (SJA). SJAs run at key positions on the wing and continuously energize the low pressure zone by blowing jets of air into it. This action displaces the transition region towards the back of the wing, and consequently reduces the overall friction [30]. The weakness of SJAs is to *not* use sensors to detect and trace the turbulent flows and hence offer only open loop actuation. This compromises the efficiency of AFC, leading to waste of energy resources when there is no turbulent flow or when the turbulence lies outside the actuators' control field.

Morphing wings are another potential actuating technology to enable AFC, as it allows wings to actively change their shape in order to achieve efficient flight conditions. However, none of the proposed solutions perform closed-loop actuation through dense sensing [31]. Cattafesta and others survey these and other actuators for AFC [32].

The importance and challenges related to airflow sensing discussed, and the availability and low cost of computationally powerful COTS microcontrollers, have led us to believe in the potential of a custom design network architecture. Following, we elaborate the objectives of this research work and the proposed approach.

#### 1.2 Thesis Statement

Considering the aforementioned requirements of AFC applications, we state our thesis as following:

By associating low latency mesh grid communication networks, with computationally capable sensor nodes, it should be possible to sense a phenomena and perform in-network distributed complex feature extraction in real-time. Such sensor networks should enable dense deployments that fulfill the spatial and temporal granularity required by AFC applications, while keeping low spatial and temporal complexity, minimally influenced by the large number of nodes on the network.

6 Introduction

Figure 1.3: Proposed XDense network: (a) A single node with four ports in the four directions; (b) Example of a  $5 \times 5$  mesh grid network; (c) Deployment envisioned for XDense.

## 1.3 System Requirements and Proposed Approach

Having introduced the application requirements and challenges, next we state the requirements of the sensor network targeted, which were considered while deciding on the system architecture:

- (a) Efficient data extraction: The network infrastructure should allow efficient extraction of complex information about the phenomena. This should be done without the need of centralized data collection or processing. The network should provide mechanisms to allow distributed data exchange and processing for efficient feature extraction;

- (b) Scalable infrastructure: The network infrastructure should allow scalability in terms of nodes count and density of deployments. An increase in sensor count should have minimal impact on the complexity of the architecture (spatial and temporal);

- (c) Real-time behavior: Along with efficiency, the network infrastructure should also be able to respond with timeliness, so that actions can be taken in real-time based on the extracted data. Metrics such as end-to-end delay, response time, network load need to be considered in the design;

- (d) Plug-n-Play: The network should accommodate different kinds of sensors. The system should also allow communication, data processing and high level data extraction algorithms to be co-designed with the application's requirements. Robustness and cost should also be taken into account.

In order to fulfill such system requirements, a custom designed network seems to be the most suitable solution. Therefore, we propose XDense: a sensor network tailored to address the challenges of eXtremely **Dense** sensor deployments for real-time applications.

The network uses a 2-D mesh grid architecture where each node is connected with four neighbors. Figure 1.3 shows (a) the XDense node and (b) network, along with the (c) envisioned deployment for airflow monitoring.

In order to enable efficient data extraction of the observed phenomena, XDense takes advantages of the mesh topology. That is, it exploits the available throughput and computational power (that scales with the number of nodes on the network) to extract data of interest, in real-time, without the need of collecting the data from each individual node centrally. Furthermore, because the network is based on regular structures, it allows dense and scalable sensor deployments.

The data of interest here are the airflow characteristics. More specifically, the feature we want to detect is the transition region, which is (as stated before), the region of the wing on which the airflow transits from laminar to turbulent regime. For this detection process, we use distributed feature detection and extraction algorithms to localize the transition region, by detecting the presence/absence of vortices that characterize turbulent/laminar airflow.

To detect the transition region, XDense performs local data sharing and processing operations in clusters of nodes before communicating pre-processed results to a central node, which is connected to a gateway link. By reducing the number of transmissions to a central node on the network (gateway), we achieve better network load distribution, decreased congestion and improved response time.

XDense differs from other sensor network (SN) architectures that also use nodes clustering with similar purposes. The main difference is that XDense was conceptualized and designed specifically to maximize opportunities on distributed processing for demanding real-time applications, keeping scalability and low system complexity as an important requirement. We state the following main differences from traditional wired/wireless sensor network approaches:

- (a) Communication link: XDense uses point-to-point (P2P) links, which are not subject to concurrency for shared media, and are very little susceptible to noise issues when compared to shared buses and wireless star or multi-hop networks;

- (b) Density: we consider a far more denser deployment scenario than traditional SNs (up to hundreds of nodes per square meter);

- (c) Power constraints: XDense nodes may share power supply and the impact of communication on power is negligible, specially when compared to battery powered radio links on wireless networks:

8 Introduction

(d) Communication rate: assuming wired links, rates are expected to be higher when compared with wireless links.

XDense builds a SN that behaves as if it is a distributed many-core computation platform, but programmed with specific sensing applications in mind. In a sense, it resembles Network-on-Chip (NoC) architectures. This is especially true regarding aspects like network topology (based on regular structures that compose mesh grids), routing schemes, timing properties and distributed computing capabilities [33]. On the other hand, it also differs from NoCs. The key differentiating aspects:

- (a) The network is not on a single chip, but built on a larger surface that is physically attached to the phenomena of interest;

- (b) Node count is greater than that for typical NoC applications;

- (c) Input data is locally generated at each node by its sensor (which imposes different restrictions and opportunities);

- (d) Distributed algorithms will have to be designed taking into account nodes location on the network;

- (e) NoCs are likely to have communication links with higher throughput (as they tend to be parallel links), because of the lower cost of interconnecting nodes at such scales.

Moreover, the XDense topology is not limited to static layouts, protocols or applications. Quite the contrary, our design goal is to allow plug-n-play nodes and applications for a diversity of deployment scenarios.

Figure 1.4: Tasks to be executed iteratively for the completeness of this research.

1.4 Methodology 9

### 1.4 Methodology

To realize XDense, we elaborate on the methodology of this work by identifying a set of sub-tasks that should be executed in sequence in order to achieve our overall goal. Figure 1.4 outlines that.

In summary, we define the application requirements, specify the network architecture, protocols and its principles of operation. Having that defined, we enter into an iterative co-design process in order to develop and refine the simulation, analytical and implementation models.

Each of these tasks are summarized individually in the following paragraphs, that serves as an introduction to the next chapters in the thesis in which we address each of these issues in details.

#### **Requirements Definition**

An in depth understanding of the airflow phenomena is required to determine the sensing requirements in terms of magnitude, rate of change and granularity.

We do this with a detailed literature survey. We also survey the available network architectures which are suitable to dense deployments of nodes, and the protocols utilized. A special attention is given to 2-D mesh grid networks. Finally, we survey currently available dense sensing solutions, airflow sensing, visualization and feature detection methods.

#### **Network Design**

Taking into account the application requirements definition, we specify the network architecture. Its feasibility, performance and impact of different communication protocols, and data processing techniques are studied. We ensure that the specified network architecture and protocols are suitable to the hardware implementation.

#### Simulation Model

Having specified the network architecture and protocols, we develop a simulation model to test and debug the protocols, measure the performance and identify the limitations of the proposed network architecture. Our simulator also allows investigating distributed processing algorithms for feature detection applied on fluid dynamics data.

The simulation model also serves as a validation tool for any feature conceived during the development of the analytical model or hardware implementation. 10 Introduction

#### **Analytical Model**

In carrying out the analytical model of XDense, we provide time guarantees and bounds on the resource utilization for real-time applications like AFC. The bounds provided are crucial to correctly dimension the hardware implementation.

The resulting model is validated using the simulation model, and its feasibility is demonstrated.

#### **Hardware Implementation**

We then implement and benchmark XDense nodes using different hardware in order to identify the potential performance bottlenecks associated with each implementation.

To close the design loop, the benchmark data is feed into the simulation model, in order to approximate the performance results from the simulation to the ones measured in the hardware.

#### 1.5 Thesis Structure

The reminder of this thesis is structured as follows: In Chapter 2 we discuss the different technologies that inspired XDense, followed by a literature survey of dense sensor networks and their limitations. In Chapter 3, we review the theoretical background and state-of-the-art on techniques utilized for airflow features detection for AFC, as well as for real-time communication networks. Chapters 2 and 3 correspond to Part I (Background) of this Thesis. In Chapter 4, we detail the design of XDense by presenting its architecture, protocols and principles of operation.

Following, in Chapter 5, we present the proposed simulation model along with results from experiments with airflow feature extraction algorithms. In Chapter 6, we present our analytical model and traffic shaping heuristics, that enables real-time communication and provides memory bounds for XDense. We simulate various scenarios to evaluate the performance resulting from the heuristics proposed. In Chapter 7 we present the hardware implementation of XDense using commercial-of-the-shelf (COTS) hardware, along with benchmark results for various implementation approaches. Chapters 4-7 correspond to Part II (Proposed Novel Design: XDense) of this Thesis. Finally, in Chapter 8, we conclude this Thesis by providing a summary of the present research contributions and the future research plan.

## Part I Background

#### **Chapter 2**

#### **Applications and Technology Enablers**

#### 2.1 Introduction

XDense is a sensor network inspired by modern networking and sensing technologies, which have demonstrated feasibility, benefits and performance. In this chapter we review these technologies, which, in different contexts, partially deal with the challenges that XDense tries to address.