### uc3m Universidad Carlos III de Madrid

Bachelor's Degree in Biomedical Engineering 2017-2018

**Bachelor Thesis**

"DESIGN AND CHARACTERIZATION OF LOW VOLTAGE OPERATIONAL AMPLIFIERS FOR SMART SENSORS USING LOW COST CMOS TECHNOLOGY"

Alexander Martínez Pasek

Tutor: Enrique Prefasi Sen

Leganés, July 2018

This work is licensed under Creative Commons Attribution – Non Commercial – Non Derivatives

#### TRABAJO DE FIN DE GRADO – BACHELOR THESIS

### DESIGN AND CHARACTERIZATION OF LOW VOLTAGE OPERATIONAL AMPLIFIERS FOR SMART SENSORS USING LOW COST CMOS TECHNOLOGY

Autor: Alexander Martínez Pasek

Tutor: Enrique Prefasi Sen

### **Tribunal Calificador**

**Presidente:** D. Luis Hernández Corporales

Secretario: Dña. Claudia de Molina Gómez

Vocal: Dña. Lorena Cusso Mula

Tras haberse realizado el acto de defensa y la lectura del Trabajo de Fin de Grado el día 5 de Julio de 2018 en la Universidad Carlos III de Madrid, Escuela Politécnica Superior, Leganés, el Tribunal acuerda otorgarle la CALIFICACIÓN de:

VOCAL

SECRETARIO

PRESIDENTE

### ABSTRACT

This bachelor thesis brackets the use of different OTA topologies and compares them under the scope of their application as low power comparators and adders for a  $\Sigma\Delta$  ADC. This was undertaken under the "*Design and characterization of main building blocks for Medical instrumentation ADCs*" research project and, more specifically, in the "*Design of a Low-IF Sigma-Delta Modulator*" section.

The researched topologies include a folded cascode, telescopic cascode, class A Miller as well as a class AB Miller. The implementation was performed at transistor level of the for all topologies in a 0.18  $\mu$ m with original 1.8 V, downscaled to 1.5 V with the goal of reducing power consumption.

**Keywords:** CMOS integrated circuits, Differential amplifiers, Circuit simulation, Biomedical electronics, Analog integrated circuits.

### ACKNOWLEDGEMENTS

It doesn't seem it has been four years already since I started this bachelor degree. Back at the beginning, during the first day of the degree, I did not realize what a huge journey all this would turn out to be. I have met my best friends (Roberto, thank you for all of your support during these years, my fellow engineer!), colleagues and soul mate, countless with whom I have crossed paths and have allowed me to become what I am today. To all of them I want to thank, since this seems the most appropriate place and date.

A mis padres, Juan Carlos y Joanna, así como a mi hermana Selene. Muchísimas gracias por todo el apoyo, desde el fondo de mi corazón. I jak mógł bym zapomnieć o mojej rodzinie w Polsce, dziękuję wam wszystkim za całą troske o mnie.

No puedo olvidar a quienes me inspiraron en seguir el camino de la ciencia allá en los primeros años de instituto. Vivian, Emilia, Juan Carlos, muchísimas gracias por animarme a seguir este camino tan apasionante.

А так же, моей девушке и родственной душе, спасибо тебе за всю твою поддержку и за прекрасное время проведённое вместе. Ты всегда заставляешь меня улыбаться и помогаешь становиться лучше. Я люблю тебя.

Finally, I want to thank all those in the Electronics Department, specially Enrique, for giving me this chance to learn about the thrilling subject that is electronic technology. I cannot forget about Marcos, thank you for inspiring me, Лети высоко мой друг, and Rubén, thank you for withstanding the constant questions I was subjecting you to.

#### INDEX

| 1 INTRODUCTION                                      | 1  |

|-----------------------------------------------------|----|

| 1.1 MOTIVATIONS                                     | 1  |

| 1.2 BRIEF OVERVIEW OF OPERATIONAL AMPLIFIERS        | 1  |

| 1.2.1 SOURCE CLASSIFICATION                         | 2  |

| 1.2.2 I/O CLASSIFICATION                            | 2  |

| 1.3 OBJECTIVES                                      | 3  |

| 1.4 STATE OF THE ART                                | 4  |

| 2 CMOS TECHNOLOGY                                   | 6  |

| 2.1 INTRODUCTION TO CMOS TECHNOLOGY                 | 6  |

| 2.1.1 SILICON AND DOPING                            | 6  |

| 2.1.2 THE PN JUNCTION                               | 7  |

| 2.1.3 THE TRANSISTOR                                | 8  |

| 2.1.4 THE MOSFET                                    | 9  |

| Triode region                                       |    |

| Saturation region                                   | 11 |

| Channel length modulation                           |    |

| 2.1.5 CMOS TECHNOLOGY                               | 14 |

| 2.2 SMALL SIGNAL MODEL PARAMETERS                   | 14 |

| 2.2.1 TRANSCONDUCTANCE                              | 15 |

| 2.2.2 DRAIN-SOURCE RESISTANCE                       | 15 |

| 2.2.3 PARASITIC CAPACITANCES                        | 15 |

| 2.2.4 SMALL SIGNAL MODEL                            |    |

| 2.3 DESCRIPTION OF THE USED CMOS TECHNOLOGY         |    |

| 2.3.1 SHORT CHANNEL EFFECTS                         |    |

| Carrier velocity saturation                         | 17 |

| Mobility degradation                                |    |

| Drain induced barrier lowering (DIBL)               |    |

| Impact ionization and Hot carrier injection         |    |

| 2.3.2 ANALOG TECHNOLOGY                             |    |

| 2.3.3 DESIGN TIME AND COST                          |    |

| 2.3.4 TRANSISTOR CUT OFF FREQUENCY                  |    |

| 2.3.5 THRESHOLD AND SATURATION VOLTAGE IMPLICATIONS |    |

| 2.4 MOTIVATIONS BEHIND THE TECHNOLOGY CHOICE        |    |

| 3 OTA TOPOLOGIES                                 | 23 |

|--------------------------------------------------|----|

| 3.1 INTRODUCTORY CONCENPTS                       | 23 |

| 3.1.1 CURRENT MIRRORS                            | 23 |

| 3.1.2 CASCODING THE CURRENT MIRROR               | 24 |

| 3.1.3 MILLER'S THEOREM                           | 25 |

| 3.2 SYSTEM STABILITY AND COMPENSATION            | 26 |

| 3.2.1 STABILITY                                  | 26 |

| 3.2.2 FREQUENCY COMPENSATION                     | 30 |

| 3.3 SINGLE STAGE TOPOLOGIES                      | 31 |

| 3.3.1 FOLDED CASCODE OTA                         | 31 |

| 3.3.2 TELESCOPIC CASCODE OTA                     | 34 |

| 3.4 TWO STAGE TOPOLOGIES                         | 36 |

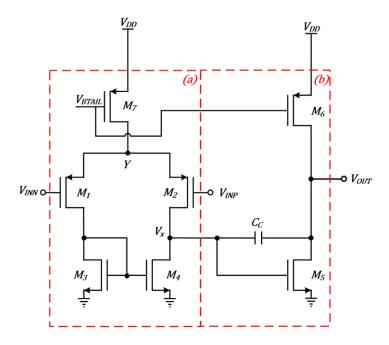

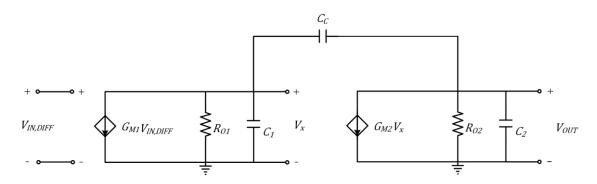

| 3.4.1 MILLER-COMPENSATED OTA                     | 36 |

| 3.4.2 CLASS A AND A/B                            | 40 |

| Class A                                          | 40 |

| Class AB                                         | 41 |

| Class A vs AB                                    | 42 |

| The class AB buffer and its biasing              | 43 |

| 3.5 SINGLE ENDED AND DIFFERENTIAL TOPOLOGIES     | 44 |

| 3.5.1 FROM SINGLE-ENDED TO FULLY DIFFERENTIAL    | 44 |

| 3.5.2 INCREASE IN DYNAMIC RANGE                  | 44 |

| 3.5.3 NOISE ISOLATION                            | 45 |

| 3.5.4 BIAS POINT VARIATION                       | 46 |

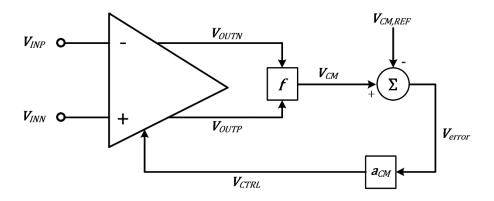

| 3.5.5 CMFB CIRCUITS                              | 47 |

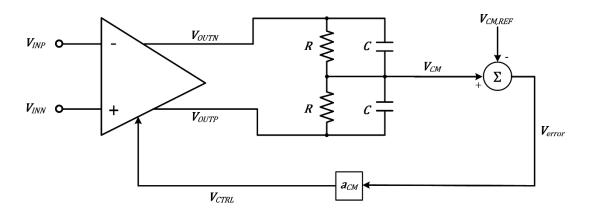

| Resistor-Capacitor network CMFB                  | 48 |

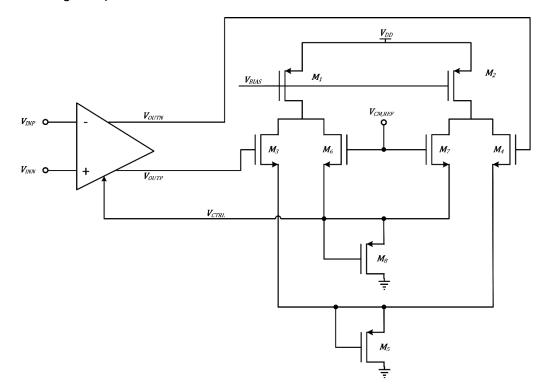

| Differential Pair CMFB                           | 49 |

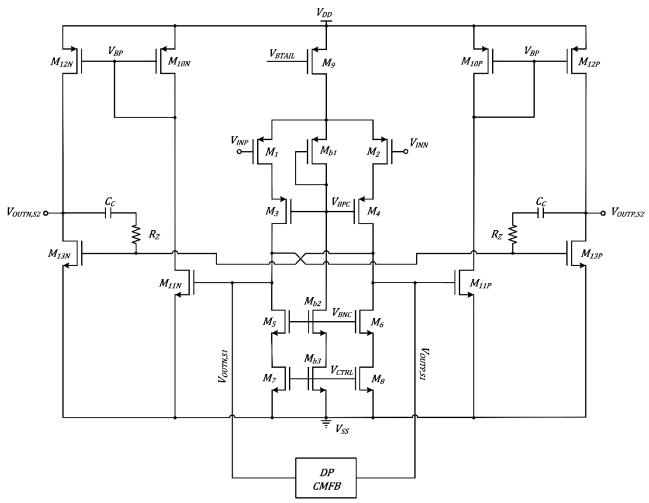

| 3.5.6 FULLY DIFFERENTIAL CLASS AB IMPLEMENTATION | 50 |

| 3.6 COMPARISON                                   | 52 |

| 3.6.1 FOLDED CASCODE OTA                         | 52 |

| 3.6.2 TELESCOPIC CASCODE OTA                     | 53 |

| 3.6.3 TWO STAGE MILLER-COMPESNATED OTA           | 53 |

| 3.6.4 TWO STAGE CLASS AB OTA                     | 54 |

| 4 DESIGNED CIRCUIT                               | 55 |

| 4.1 DESIGN EQUATIONS                             | 55 |

| 4.1.1 FOLDED CASCODE                             | 57 |

| 4.1.2 TWO STAGE, CLASS A MILLER        | 60 |

|----------------------------------------|----|

| 4.1.3 TWO STAGE, CLASS AB MILLER       | 62 |

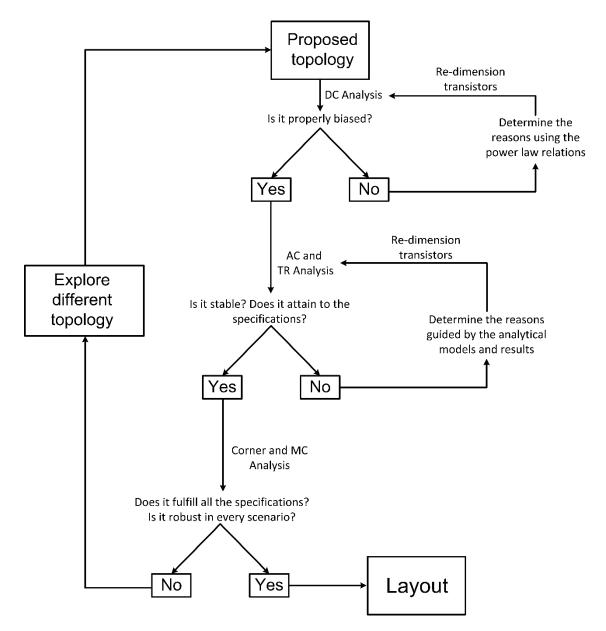

| 4.2 SIMULATIONS                        | 66 |

| 4.2.1 DC ANALYSIS                      | 66 |

| 4.2.2 AC ANALYSIS                      | 66 |

| 4.2.3 TRANSIENT ANALYSIS               | 67 |

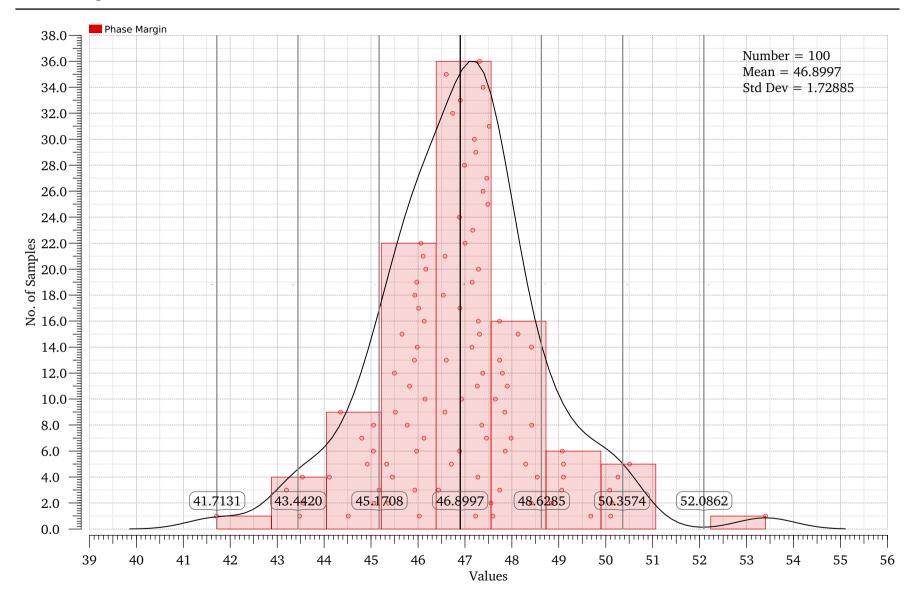

| 4.2.4 CORNERS AND MONTE CARLO ANALYSES | 67 |

| 4.3 RESULTS AND DISCUSSION             | 69 |

| 4.3.1 CMFB                             | 69 |

| RC CMFB Circuit                        | 69 |

| Differential Pair CMFB Circuit         | 69 |

| 4.3.2 FOLDED CASCODE                   | 71 |

| 4.3.3 MILLER CLASS A                   | 75 |

| 4.3.4 MILLER CLASS AB                  | 78 |

| 4.4 DESIGN CONCLUSIONS                 | 81 |

| 4.4.1 CMFB                             | 81 |

| 4.4.2 FOLDED CASCODE                   | 81 |

| 4.4.3 TWO STAGE MILLER CLASS A         | 81 |

| 4.4.4 TWO STAGE MILLER CLASS AB        | 81 |

| 4.5 FUTURE WORK                        | 82 |

| 5 CONCLUSIONS                          | 83 |

| 6 BUDGET AND WORK PLAN                 | 84 |

| 7 BIBLIOGRAPHY                         | 86 |

### LIST OF FIGURES

| Figure 1.1 – I/O classification of amplifiers                                          | 3    |

|----------------------------------------------------------------------------------------|------|

| Figure 1.2 – Local feedforward topology                                                | 4    |

| Figure 2.1 – Silicon bonding in lattice (a), phosphorus doped silicon (b) and boron do | ped  |

| silicon (c)                                                                            | 7    |

| Figure 2.2 – pn junction and depletion region                                          | 7    |

| Figure 2.3 – BJTs and FETs                                                             | 8    |

| Figure 2.4 – nMOS device structure                                                     | 9    |

| Figure 2.5 – Channel formation in nMOS devices.                                        | . 10 |

| Figure 2.6 – nMOS device in pinch off                                                  | . 12 |

| Figure 2.7 – Channel length modulation effect on an nMOS device                        | . 12 |

| Figure 2.8 – Application of the model in the different working regions                 |      |

| Figure 2.9 – Small signal model assumptions [8].                                       | . 14 |

| Figure 2.10 – Parasitic capacitances on an nMOS device.                                | . 16 |

| Figure 2.11 – nMOS small signal model equivalent circuit                               | . 16 |

| Figure 2.12 – Dependence of threshold voltage on pair length (minimal length for a gi  | ven  |

| fabrication technology)                                                                | . 21 |

| Figure 2.13 – Trade-offs of analog design in digital CMOS processes [2]                | . 22 |

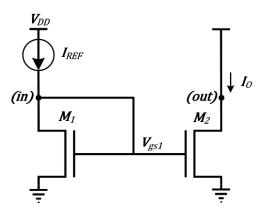

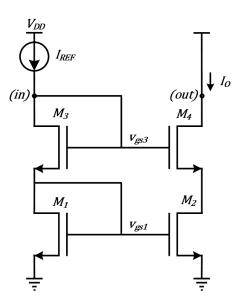

| Figure 3.1 – Simple current mirror                                                     | . 23 |

| Figure 3.2 – Small signal equivalent circuit of the simple current mirror              | . 23 |

| Figure 3.3 – Cascode current mirror                                                    | . 24 |

| Figure 3.4 – Miller effect demonstration                                               | . 25 |

| Figure 3.5 – LTI, open loop system.                                                    | . 26 |

| Figure 3.6 – Response of the LTI system to an input.                                   | . 26 |

| Figure 3.7 – LTI, closed loop system                                                   | . 27 |

| Figure 3.8 – Bode plot for gain increase                                               | . 27 |

| Figure 3.9 – Pole-zero diagram for equation 3.8 and its closed loop system             | . 28 |

| Figure 3.10 – Nyquist diagram for Figure 3.9.                                          | . 29 |

| Figure 3.11 – Gain and frequency normalized plot for closed loop amplifiers with diffe | rent |

| phase margins [14]                                                                     | . 30 |

| Figure 3.12 – Single-ended, folded cascode topology                                    | . 31 |

| Figure 3.13 – Small signal equivalent circuit for single-ended folded cascode          | . 32 |

| Figure 3.14 – Output resistance for a folded cascode                                   | . 33 |

| Figure 3.15 – Single-ended, telescopic cascode topology                                | . 34 |

| Figure 3.16 – Two stage amplifier topologies.                                          | . 36 |

| Figure 3.17 – Two stage, Miller-compensated OTA.                                       | . 36 |

| Figure 3.18 – Two stage, Miller-compensated OTA small signal equivalent circuit        | . 37 |

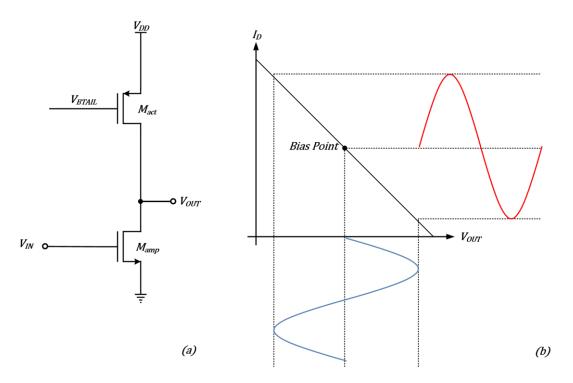

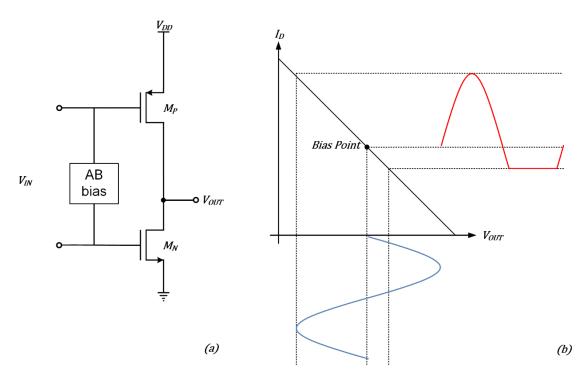

| Figure 3.19 – Class A, actively loaded, common source amplifier operation              | . 41 |

| Figure 3.20 – Class AB amplifier operation                                             | . 42 |

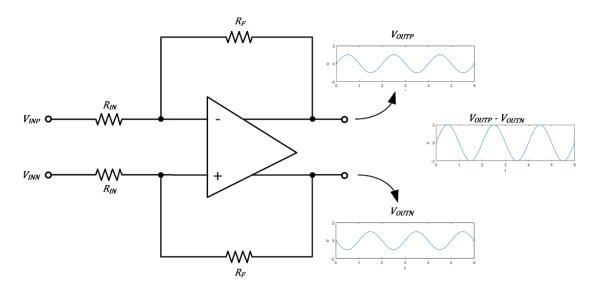

| Figure 3.21 – Increase in Dynamic Range                                                | . 45 |

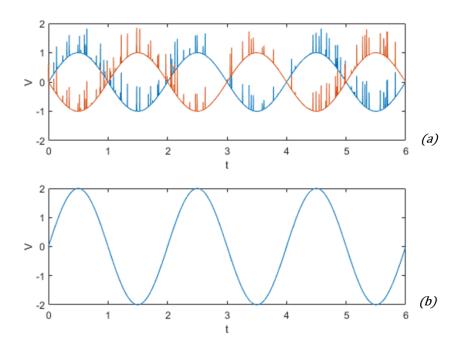

| Figure 3.22 – Common mode noise cancellation, (a) noisy half-signals and (b) diff        |           |

|------------------------------------------------------------------------------------------|-----------|

|                                                                                          |           |

| Figure 3.23 – Differential pair amplifier [24].                                          |           |

| Figure 3.24 – Stages of a CMFB circuit.                                                  |           |

| Figure 3.25 – CMFB loop implemented using a resistor and capacitor CM sense              |           |

| Figure 3.26 - CMFB loop implemented using a resistor and capacitor CM sens               |           |

| together with the comparison and amplification blocks.                                   |           |

| Figure 3.27 – CMFB loop implemented using a differential pair CM sense block.            |           |

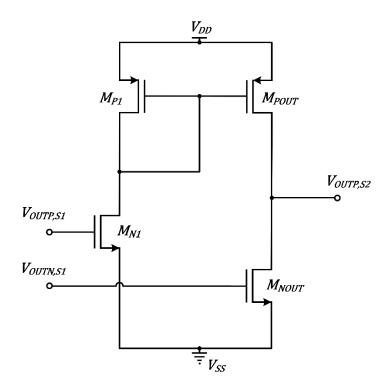

| Figure 3.28 – Fully differential class AB output stage half circuit.                     | 51        |

| Figure 4.1 – Transconductance dependencies                                               | 55        |

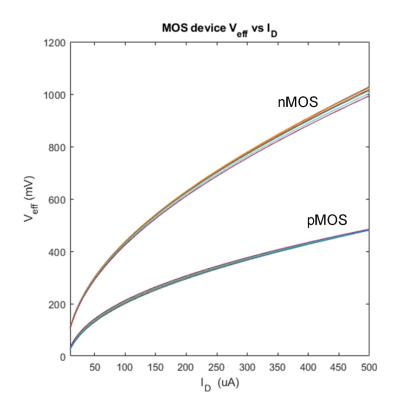

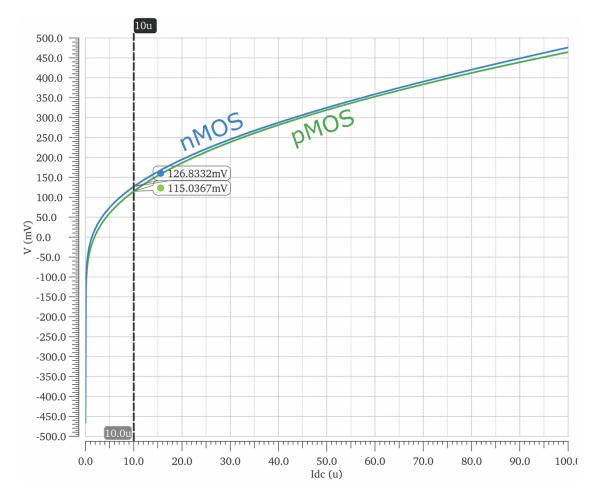

| Figure 4.2 - Veff vs ID.                                                                 | 56        |

| Figure 4.3 – Results for effective voltage at different drain-source currents, Idc,      |           |

| nMOS and pMOS devices with the dimensions reported above                                 |           |

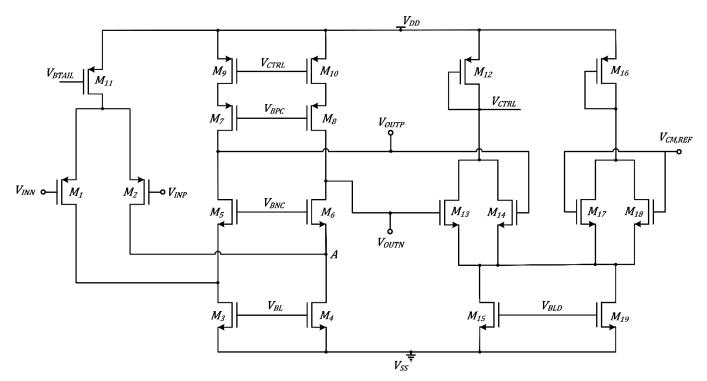

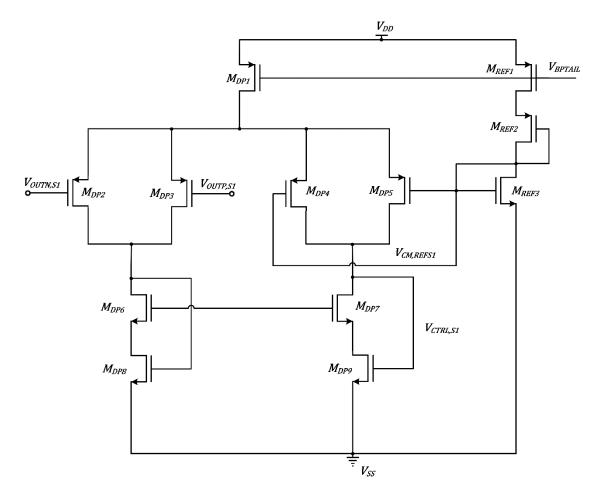

| Figure 4.4 – Fully differential, folded cascode OTA with differential pair CMFB n        |           |

| Figure 4.5 – Biasing circuit for fully differential, folded cascode OTA                  |           |

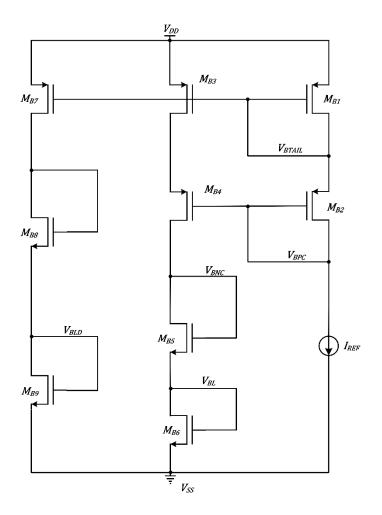

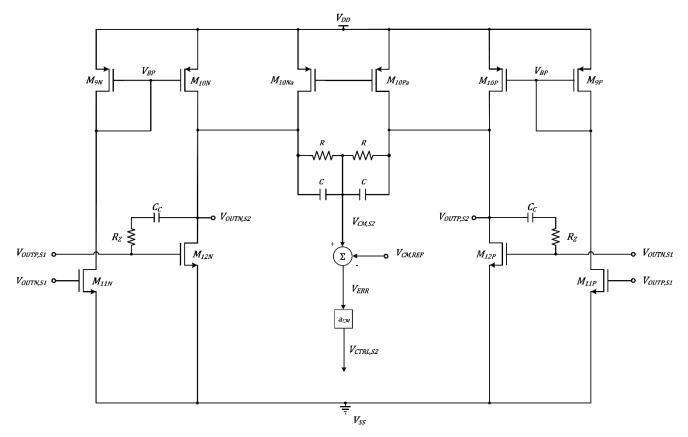

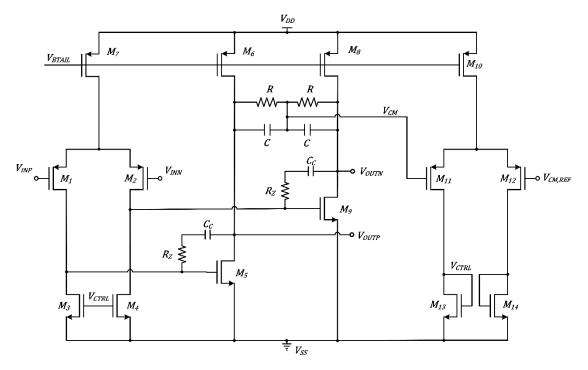

| Figure 4.6 - Fully differential, two stage, Miller-compensated OTA with different        | tial pair |

| CMFB network.                                                                            | 61        |

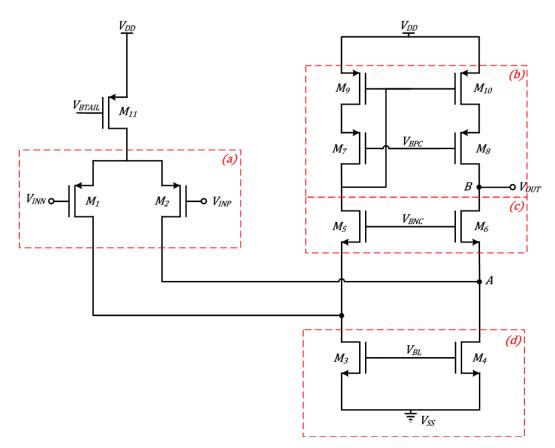

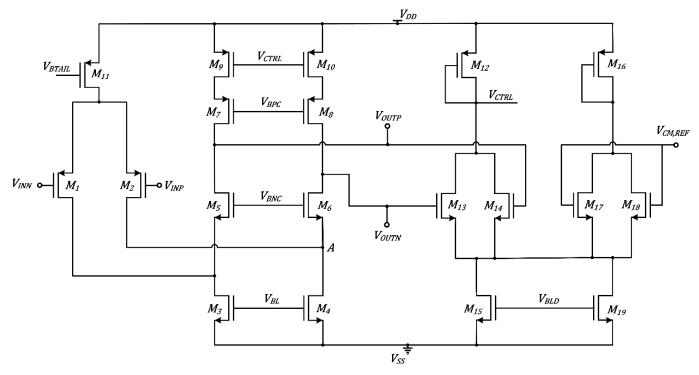

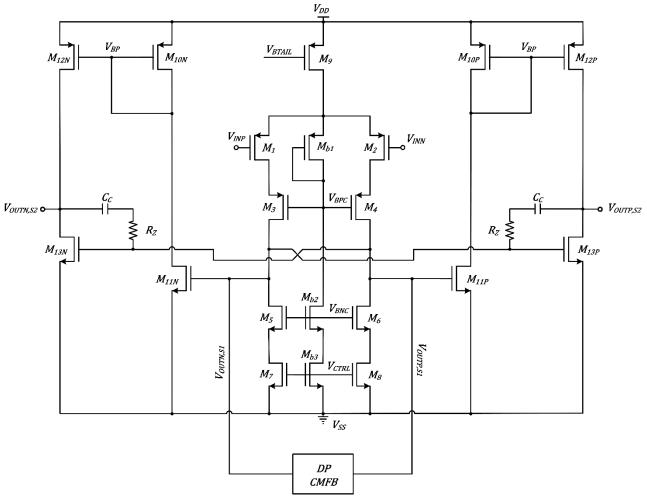

| Figure 4.7 - Two stage, Miller-compensated, class AB amplifier with DP CMF               | B block   |

| and no output CMFB network                                                               | 62        |

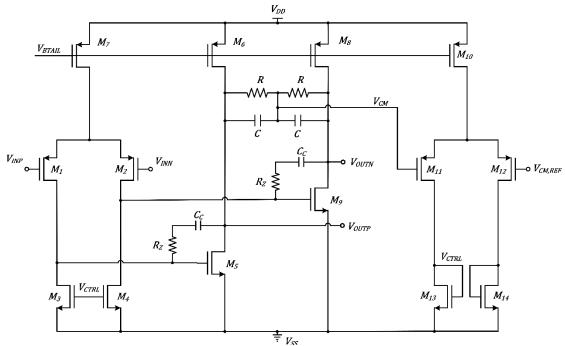

| Figure 4.8 – Differential pair (DP) CMFB circuit used for the first stage with the re    | ference   |

| generation circuit.                                                                      |           |

| Figure 4.9 – Diagram implementation of the RC CMFB circuit for a fully differenti AB.    |           |

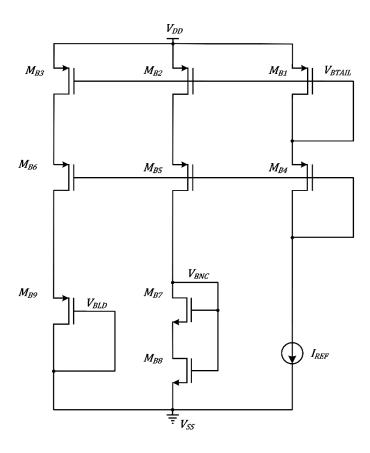

| Figure 4.10 – Bias circuit branches for the two stage, Miller-compensated, cl amplifier. |           |

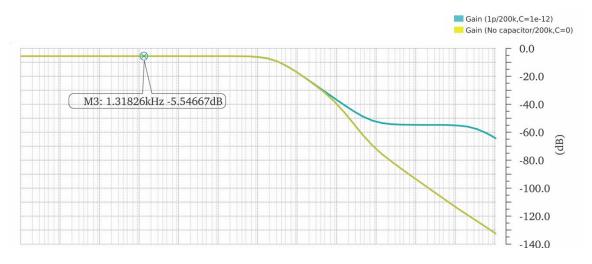

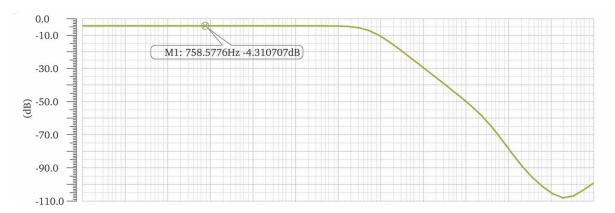

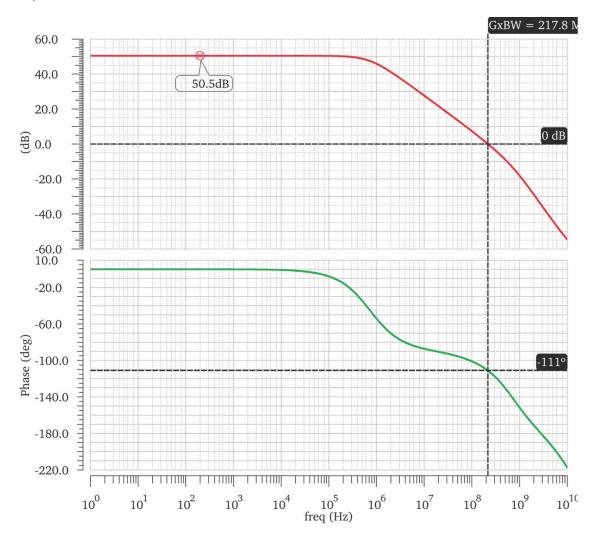

| Figure 4.11 – AC analysis results for the RC CMFB circuit implementation                 |           |

| Figure 4.12 – AC analysis results for the differential pair CMFB circuit impleme         | ntation.  |

| Figure 4.13 – Fully differential folded cascode OTA                                      |           |

| Figure 4.14 - AC results as a Bode plot for fully the differential folded cascode C      |           |

| Figure 4.15 – Slew rate results for fully differential folded cascode OTA.               |           |

| Figure 4.16 – AC results as a Bode plot for fully the differential folded casco          |           |

| without the load resistor                                                                |           |

| Figure 4.17 – Two stage, Miller-compensated, class A amplifier.                          |           |

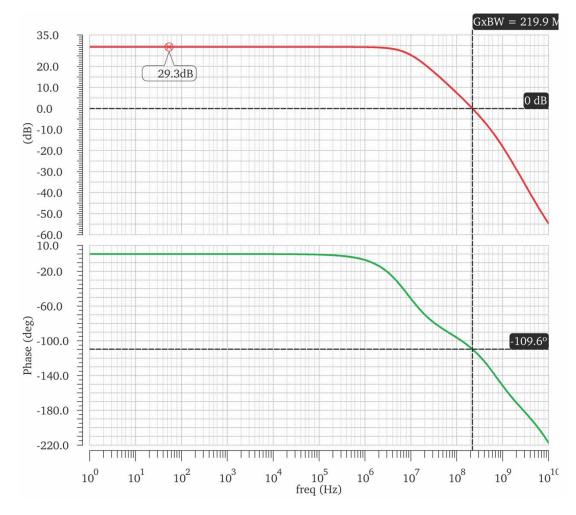

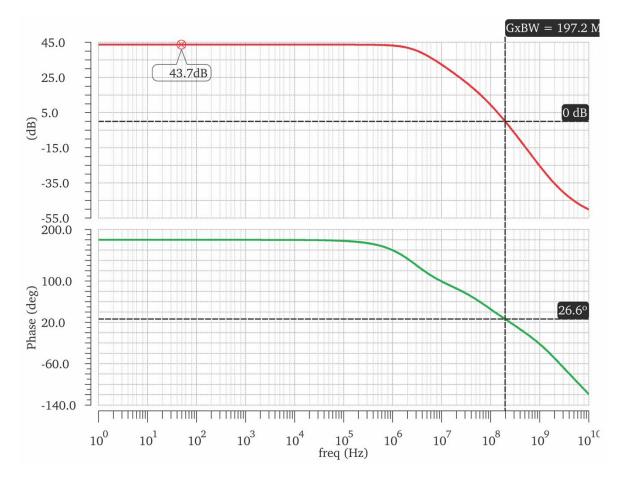

| Figure 4.18 – AC analysis results for two stage, Miller-compensated, class A a           |           |

| with load resistor.                                                                      | •         |

| Figure 4.19 – AC analysis results for two stage, Miller-compensated, class A a           | mplifier  |

| without load resistor                                                                    | 77        |

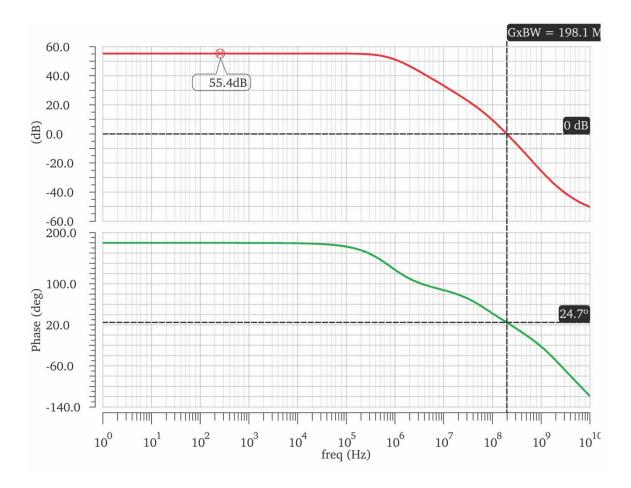

| Figure 4.20 – Two stage, Miller-compensated, class AB amplifier                          | 78        |

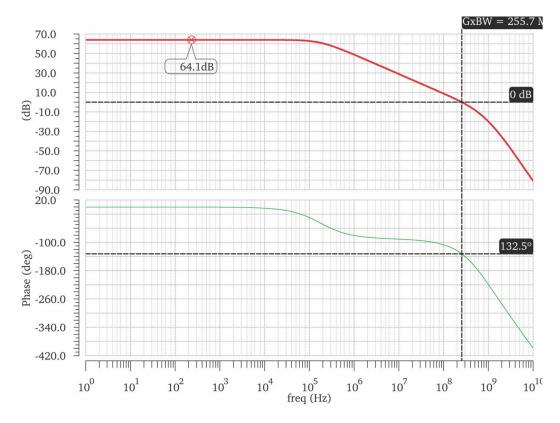

| Figure 4.21 - AC Analysis results for the two stage, Miller-compensated, cl              | ass AB    |

| amplifier.                                                                               | 79        |

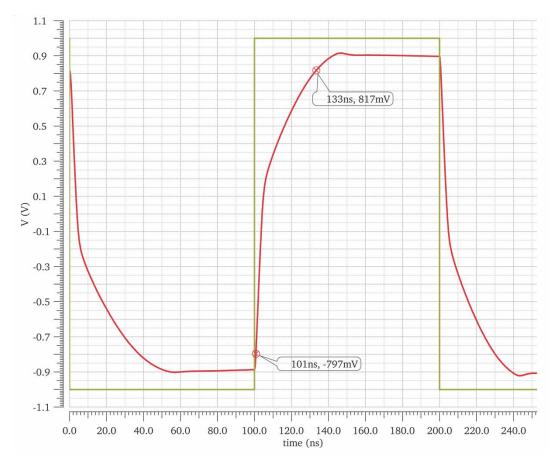

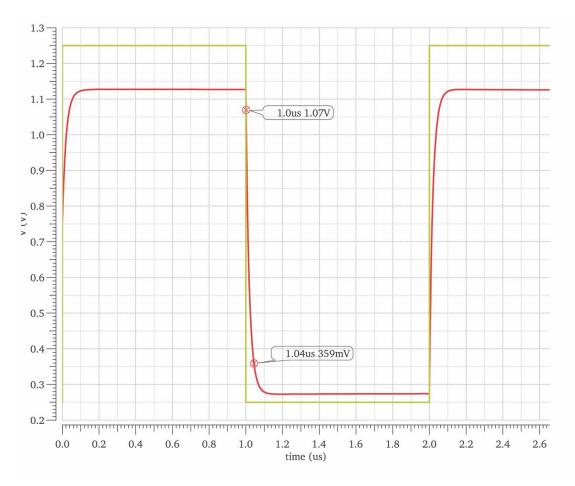

| Figure 4.22 – Slew rate results for the two stage, Miller-compensated, class AB and      | •         |

| Figure 6.1 – Work plan applied throughout the thesis.                                    |           |

|                                                                                          |           |

### LIST OF TABLES

| Table 1.1 – Design Parameters for the amplifiers.                                       | 3       |

|-----------------------------------------------------------------------------------------|---------|

| Table 2.1 – KVL applied to the terminals of an nMOS device.                             | 11      |

| Table 2.2 - Large signal equations for nMOS devices neglecting some second of           | order   |

| effects.                                                                                | 13      |

| Table 3.1 – Single-ended, folded cascode equations                                      | 34      |

| Table 3.2 - Single-ended, telescopic cascode equations                                  | 35      |

| Table 3.3 – Single-ended two stage, Miller compensated OTA equations                    |         |

| Table 3.4 – Class A and Class AB comparison.                                            | 43      |

| Table 3.5 – Comparison of different amplifier topologies.                               | 54      |

| Table 4.1 – Values of k for the 180 nm pMOS and nMOS devices                            | 56      |

| Table 4.2 – DC analysis results for RC network CMFB circuit.                            | 69      |

| Table 4.3 - DC analysis results for differential pair CMFB circuit                      | 70      |

| Table 4.4 – Folded cascode OTA DC analysis, bias results                                | 71      |

| Table 4.5 – Corner process analysis results for the fully differential folded cascode ( | OTA.    |

|                                                                                         | 74      |

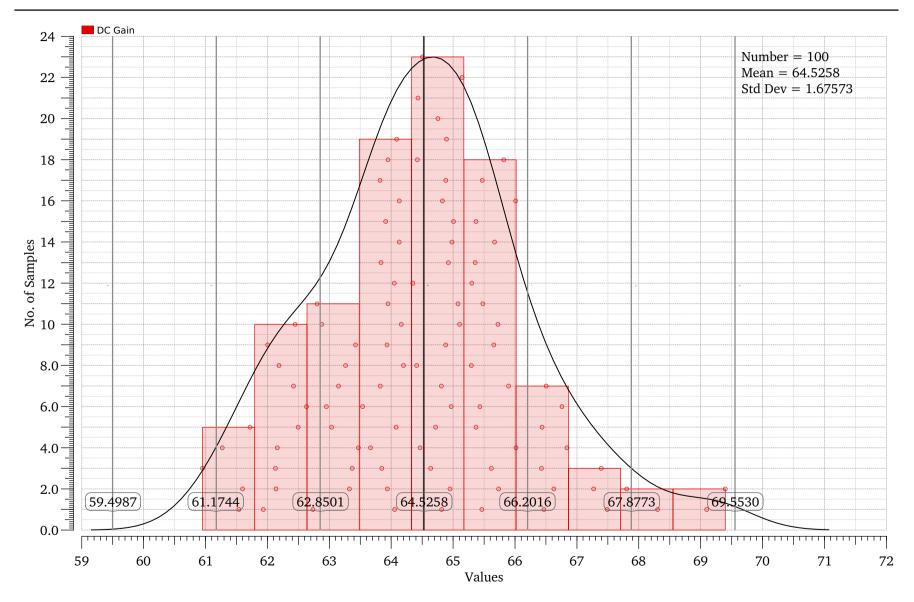

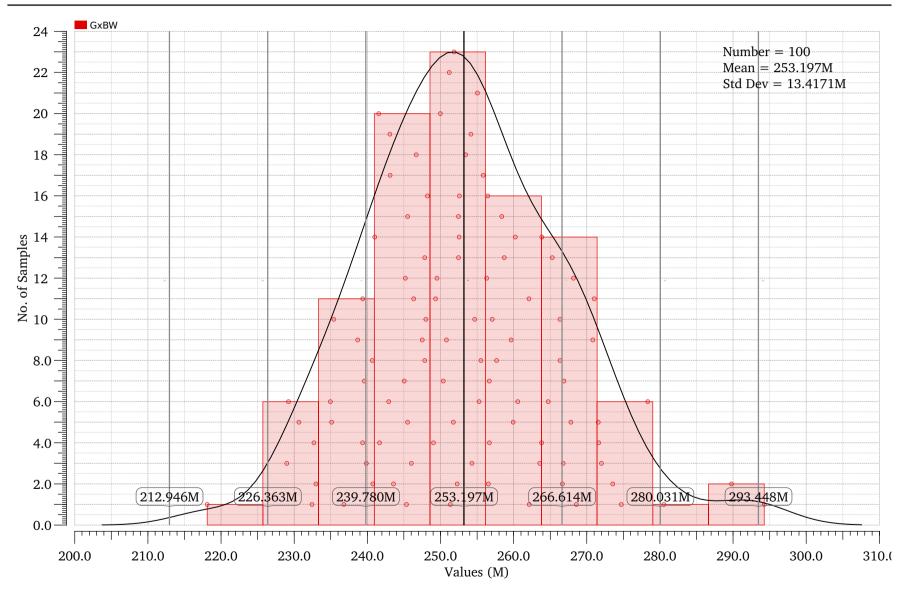

| Table 4.6 – Monte-Carlo analysis results for fully differential folded cascode OTA      | 74      |

| Table 4.7 – Two stage, Miller-compensated, class A amplifier DC analysis results        | 75      |

| Table 4.8 – Corner analysis results for two stage, Miller class A amplifier             | 76      |

| Table 4.9 – Two stage, Miller-compensated, class AB amplifier DC analysis results       | 78      |

| Table 4.10 - Corner analysis results for two stage, Miller class AB amplifier           | 79      |

| Table 4.11 - Monte-Carlo analysis results for the two stage, Miller class AB amp        | lifier. |

|                                                                                         | 80      |

| Table 5.1 – Update topology comparison table.                                           | 83      |

| Table 6.1 – Budget of the developed research                                            | 84      |

|                                                                                         |         |

### 1.-INTRODUCTION

#### **1.1.-MOTIVATIONS**

Ever since the advent of portable electrical devices power consumption has been a paramount issue. Since these systems have to be connected to a battery, a dependency upon the available electric charge exists, and thus there is a limit to its service life.

One of such first devices is considered to be the electrically-powered watch, driven through a pair of solenoids and developed in the late 50s. During the next two decades these devices became transistorized, transforming into electronic wrist-watches. The advent of the 70s brought up the first pocket electronic calculators, and coupled to the rest of computing devices, it was clear that the path to follow was marked by transistors.

As the century approached the 90s, more and more transistors were crammed into the same area with each passing year, following the trend stated by Moore's law. Parallel to this, batteries kept increasing in size and charge capacity while remaining comfortable enough to handle.

It was not until the start of the millennium that Moore's law predicted the density of transistors needed to embed computers in wafers with size in the order of decimeters and below. With this quantity of transistors came a corresponding power consumption that had to be provided by batteries which, at that point, were already on the verge of their capacity/size ratio. Henceforth, an initial true effort was started to scale down voltages and currents in an attempt to scale down power consumption.

Nowadays, the onset of *smart* devices is seeing this effort pushed strongly, trying to reduce power consumption by the means of scaling down the voltage of the used transistor technologies to 1.5, 1.2 and even 0.8 or 0.5 V. As a prospect for the future, this downscaling will allow to develop smaller, lighter (and thus more portable) devices, which allow for a more efficient use of energy.

The use of these efficient devices is appealing in the medical field, and concerns analog microelectronic blocks of systems such as DACs and ADCs. Having this in mind, the thesis was developed in a research project titled "*Design and characterization of main building blocks for Medical Instrumentation ADCs*" at the Microelectronics Design and Applications (DMA) research group at Carlos III University of Madrid.

#### 1.2.-BRIEF OVERVIEW OF OPERATIONAL AMPLIFIERS

The term *amplifier* is used to define a family of electronic devices that perform the same basic task. Throughout the document the term *amplifier* will be used in reference to operational amplifiers. Their function consists on taking a certain signal as an input and, through one or more stages, boost or enlarge it obtaining a scaled output. Of course, this signal can be a current or a voltage, and depending on whether one is converted into another during the amplification, one can think of four different scenarios.

#### **1.2.1.-SOURCE CLASSIFICATION**

Take for instance a voltage input and feed it into an amplifier. If the output was to be an amplified voltage signal, one could label the amplifier as voltage-controlled voltage source, a VC-VS. However, if the output was an [amplified] current signal, the device would be now labelled as a voltage-controlled current source, VC-CS for short. Conversely, if the input signal was a current and the output a voltage, it would be labelled as a current-controlled voltage source (CC-VS). Finally, the last combination suggests a current input for a current output, making it a current-controlled current source (CC-CS).

Current and voltage inevitably coexist as Ohm's law states, so how can one talk about a signal being "current" or a signal being "voltage"? The truth is that a signal has two characteristics: the current and the voltage. Only one of them is controlled, being the other one determined by the load through which the signal is being forced. In amplifier applications, depending on the type of the signal and the characteristics of the load, one will use any of the four aforementioned combinations.

A classification intro *controlled sources* was mentioned above. It is true that one can think of an amplifier as a current or voltage source controlled by a certain parameter. Nevertheless, let's analyze the properties one would wish those devices had to achieve that *controlled source* definition.

For instance, take a voltage-controlled voltage source. This implies that given a voltage input, another voltage output is provided, regardless of the demanded current. This is in conjunction with the definition of voltage source, a device that provides a constant voltage despite of the required current. This is achieved by placing a very low impedance at the output (if this resistance was to be null, the voltage drop across the output would be exactly zero). Analogously, when considering the input of the device, one wants it to *sense* the same voltage, no matter the current. This is typically done by applying a very high input resistance.

These are key points one has to bear in mind when designing amplifiers, as depending on the application one or another topology will be used as a function the signal characteristics and the load requirements.

Finally, it is mandatory to introduce some nomenclature. While the vast majority of amplifiers are preferred to have an infinite input impedance (as already mentioned, to sense the input voltage without interfering with it), the output impedance is a factor that attends to the necessities of the design. As such, two types of infinite input impedance amplifiers arise: those who present a low output impedance, and those with a high output impedance. These are referred to as operational amplifiers (Op-Amps or OAs, for short) and operational transconductance amplifiers (OTAs).

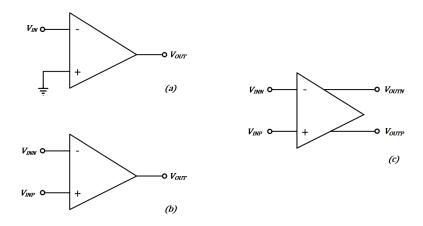

#### 1.2.2.-I/O CLASSIFICATION

Another classification can be established based on their type of input/output (IO), amplifiers are segregated into single-ended and differential IOs. An amplifier can be configured into a single-ended input by referencing one of its inputs to ground, being the other the signal carrier. On the other hand, if they are presented with two inputs which are complementary, they are said to be configured into a differential input.

One can already realize that the vast majority of designs make use of differential inputs and that they are used in one fashion or another. However, one cannot configure the outputs as it is done with the inputs in such a straight-forward manner. The topologies used in amplifiers require them to be designed as differential or single-ended outputs themselves, due to the control of the common mode level within the amplification stages.

In short, there exist four different categories:

- Single-ended input, single-ended output, shown in Figure 1.1 (a).

- Single-ended input, differential output.

- Differential input, single-ended output, represented below as Figure 1.1 (b).

- Differential input, differential output, depicted in Figure 1.1 (c).

This leads to the used classification, the first and third categories are termed as differential amplifiers mostly because, as aforementioned, one can convert the differential input into a single-ended one. And fully differential amplifiers that present two differential inputs and a differential output.

Figure 1.1 – I/O classification of amplifiers.

#### 1.3.-OBJECTIVES

The objective of this bachelor thesis span over the design and characterization of different operational amplifiers at low voltage for a  $\Sigma\Delta$  ADC specifically designed for biomedical sensors [1]. The characteristics of this amplifier have to meet a maximum specified in the table below.

|                                           | A <sub>dc</sub> | GxBW    | SR      | $I_{DC}^{max}$ |

|-------------------------------------------|-----------------|---------|---------|----------------|

|                                           | 55 dB           | 200 MHz | 15 V/µs | 5 mA           |

| l = 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 |                 |         |         |                |

Table 1.1 – Design Parameters for the amplifiers.

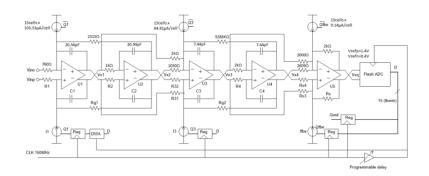

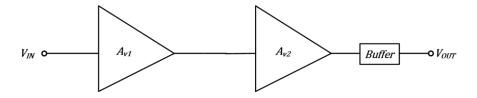

The system for which the amplifiers have to be designed is shown in Figure 1.2. The first four amplifiers are acting as integrators, while the fifth and last one acts as an adder. The connected resistances and capacitors are given by the state variables of the system.

Note that the maximum capacitance that the amplifiers will see is of 20 pF, and a minimum resistance of 1 k $\Omega$ . This has to be taken into account when designing the

amplifier, as the equivalent load in open loop will amount to the capacitances in parallel to the resistor.

The integrator-configured amplifiers will be designed with the same specifications, in open loop with a 20 pF load and a 1 k $\Omega$  resistor. The adder-configured amplifier will be moving the inputs of the flash ADC, modelled by a 3 pF load.

Figure 1.2 – Local feedforward topology.

Nevertheless, the main goal of this thesis will be to assess the differences between the different topologies as well as implementation possibilities both analytically and through simulation results.

#### **1.4.-STATE OF THE ART**

It is no mystery that the analog microelectronics field has been approaching its extinction. With the exception of current drivers, ADCs and RF systems, the industry is quickly shifting towards digital design. As a consequence, the available technologies are shrinking in size and being optimized in delay times rather than in the aspect of their linearity.

The explained above implies that analog design hast to be usually undertaken with technologies meant for digital design. This, in turn, causes that the accuracy of the fabricated circuit does not match the simulations which, consequently, do not follow accurately the predictions of the equations that describe the topologies. This adds up to the design and development time of analog systems and causes them to lag behind digital design. This phenomenon is caused by the rapid migration from one technology to the next, smaller one [2].

Nowadays, the field has been revisited due to the rise in consumer portable devices such as smart-devices which have to present an array of sensors and instruments. It is precisely the need of interaction with analog signals in the form of ADCs and amplifiers that still drives the interest in the analog field.

In the case of this bachelor thesis, the objective focus on designing an OTA as a part of an ADC system. A search powered by IEEE Xplore Digital Library reveals that there are few OTA designed in 0.18  $\mu$ m at voltage lower than 1.8 V with the characteristics specified above.

There are several publications that report amplifiers using 180 and 65 nm processes at extremely low voltages [3], [4], [5]. Nevertheless, these present very small unity-gain frequencies (under the 100 MHz range). Older publications [6] have reported results at the tenths of MHz at 3.3 V.

This analysis reveals that the imposed specifications are indeed ambitious at the targeted supply voltage with the goal of optimizing power consumption.

### 2.-CMOS TECHNOLOGY

The designed amplifier will be part of a microelectronic system integrated on a chip. As such, it has to be designed with the same CMOS technology as the rest of the circuit in order to portray a coherent structure. The manufacturing technology was chosen to be the AMS (Austria Mikro Systeme) 0.18  $\mu$ m platform, specifically designed for low power applications.

Along the next sections a brief description will be given on the basics of the CMOS technology and its main parameters.

#### 2.1.-INTRODUCTION TO CMOS TECHNOLOGY

The semiconductor industry is based around one type of material: semiconductors. These are defined as being materials composed by semiconductor elements with an electrical conductivity that lays in between that of materials like metals and insulators. The default semiconductor elements are silicon and germanium, being the first one the dominant in the industry.

#### 2.1.1.-SILICON AND DOPING

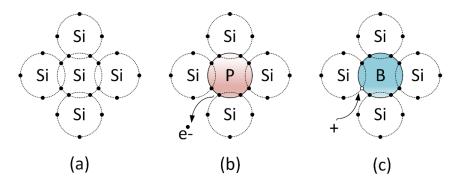

Silicon presents four electrons in its valence shell, thus being four electrons short of completing the octet rule. When arranged in a crystalline structure, each silicon atom will try to acquire those four vacant electrons from its immediate neighbors in order to remain energetically stable. Singularly, in a crystal lattice, silicon will be achieving this by sharing each one of its four valence electrons with four other alike atoms (and therefore creating a covalent bond), one electron per adjoining silicon.

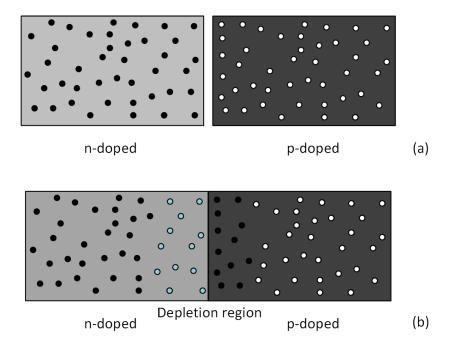

One can view each silicon atom inside a silicon crystal lattice as having four free electrons and four vacancies or holes, shown in Figure 2.1 - (a). If some other foreign atom, with a different number of valence electrons, was to be introduced into the crystal lattice, the balance between holes and electrons would be shifted towards one side or another. This process is called doping.

One can introduce an atom with either five or three valence electrons, being phosphorus and boron the most commonly used ones, respectively.

- If phosphorus is added, one extra free electron is introduced per foreign atom into the lattice, which will turn into a charge carrier. This can be seen represented in Figure 2.1 – Silicon bonding in lattice (a), phosphorus doped silicon (b) and boron doped silicon (c).. Note that the crystal is now said to be n-doped (as there is an excess of *negative* charge).

- On the other hand, if a boron atom is introduced with its three free electrons, there will be one fewer electron in the lattice per introduced impurity. This is equivalent to the addition of one extra positive carrier to the lattice as it is shown below, in Figure 2.1 Silicon bonding in lattice (a), phosphorus doped silicon (b) and boron doped silicon (c). (c). Analogously as with phosphorus, the silicon crystal is now said to be p-doped (as there is a lack of negative charge).

The basic building blocks of any transistor circuit hinge around the phenomenon that takes place when two oppositely-doped silicon lattices are found facing each other.

*Figure 2.1 – Silicon bonding in lattice (a), phosphorus doped silicon (b) and boron doped silicon (c).*

#### 2.1.2.-THE PN JUNCTION

When one half of a silicon crystal is p-doped and the other half is n-doped, the space in region in between them is called the pn junction, which is the area of interest for any diode device. This can be seen in Figure 2.2 - (a).

The n-doped region is rich in free electron carriers, while the p junction is rich in holes, or positive charge carriers. If the conditions are favorable enough, an electron will *jump* into the p-doped region, *filling* a hole (a process known as recombination). This will take place for as long as the potential allows electrons from the n-doped region to jump and recombine with the positive charge carriers in the p-doped region, creating a charge carrier-lacking area known as the depletion region, shown in Figure 2.2 - (b).

*Figure 2.2 – pn junction and depletion region.*

As the p-doped region has gained electrons, it now presents a slightly negative charge, while the converse is true for the n-doped region. If a power source is to be connected between the terminals of the silicon crystal, the depletion region will act as an insulator impeding the transit of electrons. Once the voltage between the terminals of the silicon crystal exceeds 0.6 V (the breakdown voltage), the depletion region will collapse and allow the transit of electrons.

#### 2.1.3.-THE TRANSISTOR

In order to dive deeper into the phenomena that govern the operation of transistors, it is necessary to obtain some intuitive understanding of their purpose and working.

It is commonly explained that a transistor behaves like a switch: when some voltage is applied to one of its three inputs, the switch opens letting current flow through the other two terminals. In fact, it is a controlled current source, this is: by applying some input in the form of either a voltage or a current, another current flows through the remaining terminals.

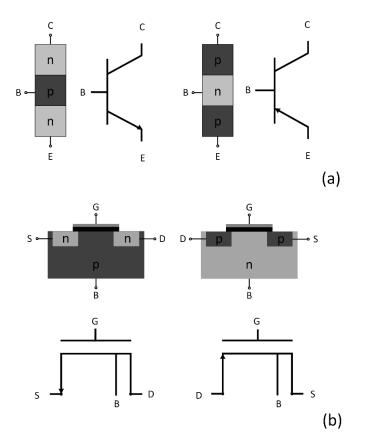

Once known this, one can be introduced to the two main different types of transistors in electronics: the BJTs and the FETs. A transistor can be built by arranging the differently doped regions in several ways. The two most common ways give rise to bipolar junction transistors (BJTs) in Figure 2.3 - (a), and to metal oxide semiconductor field effect transistors (MOSFETs) in Figure 2.3 - (b).

Figure 2.3 – BJTs and FETs.

It is important to note that the two main transistor technologies are the BJTs and the FETs, as already mentioned above. Among the FET transistors there exist different technologies as well like the MOSFETs, JFETs, IGBTs, and many other devices. Nevertheless, the most interesting for CMOS technology are MOSFETs.

BJTs are, in essence, two diodes joined by the base lead. Focusing on an NPN BJT transistor, Figure 2.3 - (a, left). If a voltage higher than the breakdown potential is applied to this terminal (positive to the base, and negative towards the emitter) current will flow through the emitter to the base, as the "diode" becomes forward biased. Moreover, as one applies an additional voltage across collector and emitter, a current will flow between these two terminals. This provides the intuition behind the reason why BJTs are usually referred to as current controlled current sources.

#### 2.1.4.-THE MOSFET

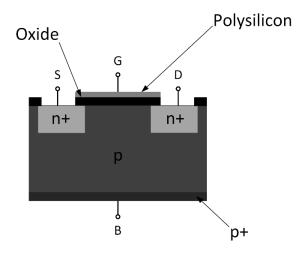

The most commonly used type of MOSFET transistor is the one depicted in Figure 2.3 - (b, left). The device's structure is represented in more detail below.

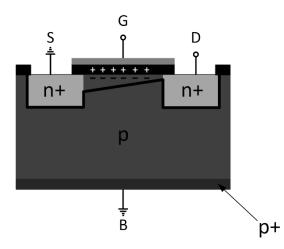

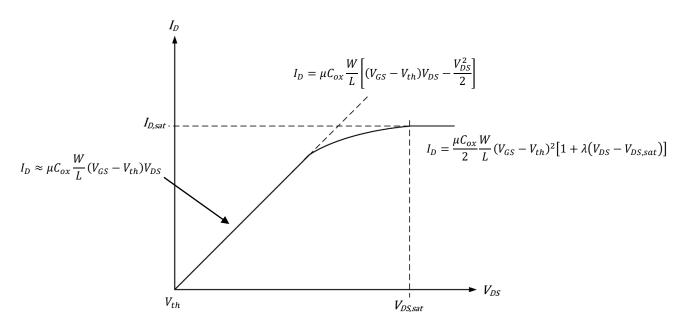

Figure 2.4 – nMOS device structure.

As depicted above, an nMOS-type FET is fabricated on top of a p-doped wafer. Two wells, noted as n-wells, are deposited on the surface of the p-doped crystal. They are referred to as n+, as they are strongly doped. Furthermore, a region called the body is fabricated by strongly p-doping the silicon crystal. Covering the p-region between the n-wells, a thin layer of silicon oxide (SiO<sub>2</sub>) is formed onto which another layer of polysilicon is deposited. It is to this film that the gate terminal will be attached. Lastly, note that the oxide layer will behave as an insulator.

Since the technology is fabricated on top of a p-doped crystal, in order to fabricated a PMOS type FET transistor it is necessary to deposit an n-doped region first onto which p-wells will be placed.

The n+ and p interfaces are pn junctions and, consequently, will result in corresponding depletion regions, being equivalent to two diodes placed back-to-back.

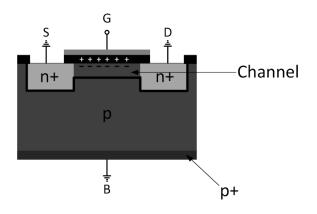

#### TRIODE REGION

When both source and drain are grounded, and a voltage large enough is applied to the gate terminal, the accumulation of positive charges in the polysilicon will induce the accumulation of negative carriers in the p-doped region underneath. Furthermore, when the concentration of negative charges is equal to the concentration of holes in the region, a depletion zone appears between the n-wells. The voltage at which this takes place is referred to as the threshold voltage of the transistor, also known as  $V_{th}$ .

If the potential at the gate is increased, and the concentration of electrons becomes that of the holes further away from the oxide layer, a channel is formed as the p-doped region becomes n-type in the proximity of the oxide layer, shown in Figure 2.5.

Figure 2.5 – Channel formation in nMOS devices.

It is intuitive that the carrier density of the channel depends on the respective voltages between source, gate and drain. On the other hand, as the potential between gate and source ( $V_{GS}$ ) increases, so does the *effective* concentration of negative charge carriers in the formed channel. Hence, the voltage that is related to this increase is noted as effective gate-source voltage,  $V_{eff} = V_{GS} - V_{th}$ .

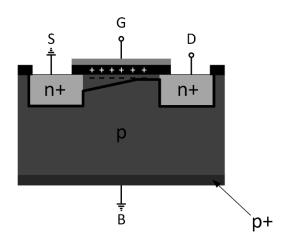

When the drain potential is increased, a current appears between drain and source. The relationship between this drain-source current is a non-linear function and it is given by equation 2.1 [7].

$$I_D = \mu C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.1)

Where  $\mu$  is the mobility of electrons through the semiconductor,  $C_{ox}$  is the capacitance of the oxide layer, W is the width of the transistor device and L is the length between the n-wells.

Note that when the channel is starting to form due to the accumulation of charges in the region, the current through the device can be assumed to scale linearly with  $V_{DS}$ , since it is small enough to neglect the squared term.

This equation is only valid for a certain range of the gate-source voltage. Until this paragraph, the range is known to be from  $V_{GS} > V_{th}$  up until a yet unknown value.

As a final remark, applying Kirchhoff's voltage rule between the terminals of the nMOS device yields the expressions summarized in Table 2.1.

| Gate-source                                                  | Drain-source         | Drain-gate                             |

|--------------------------------------------------------------|----------------------|----------------------------------------|

| $V_{GS} = V_G - V_S$                                         | $V_{DS} = V_D - V_S$ | $V_{DG} = V_{DS} - V_{GS} = V_D - V_G$ |

| Table 2.1 – $KVI$ applied to the terminals of an nMOS device |                      |                                        |

Table 2.1 – KVL applied to the terminals of an nMOS device.

#### SATURATION REGION

As the drain voltage is increased, there is an accumulation of positive carriers that will deflect the charge density of the channel near the drain terminal, shown in Figure 2.6. This takes place until a voltage that does not allow the sustenance of the channel anymore, this is: until the voltage potential between the gate and the channel reaches the value of the threshold voltage. This has to be expressed mathematically, the channel's voltage at the drain region can be thought as being:

$$V_{GD} = V_{GS} - V_{DS} \tag{2.2}$$

Since  $V_{DS}$  is being increased and  $V_{GS}$  is assumed to be constant for the time being, then  $V_{GD}$  is decreasing steadily. The condition of the channel being narrowed until it can no longer be sustained can be expressed as:

$$V_{GD} \ge V_{th} \tag{2.3}$$

Combining equations 2.2 and 2.3 one obtains the limit of  $V_{DS}$  for which any further increase in voltage will yield no further current.

$$V_{GS} - V_{DS} \ge V_{th} \to V_{DS} \ge V_{GS} - V_{th}$$

$$(2.4)$$

At that point the channel is said to be *pinched-off*. Ideally, any further increase in  $V_{DS}$  will not increase the maximum current through the channel, which is said to be *saturated*. Thus, equation 2.4 serves as a limiting value between the triode and saturation regions and it is noted as  $V_{DSat}$ .

Figure 2.6 – nMOS device in pinch off.

Substituting equation 2.4 into 2.1 yields the relationship of the drain-source current as a function of the transistor's biasing and parameters.

$$I_D = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

(2.5)

#### CHANNEL LENGTH MODULATION

Equation 2.5 implies that if  $V_{DS}$  is increased beyond  $V_{GS} - V_{th}$  the current through the device,  $I_D$ , stays constant. This is only partially true since the equation was derived neglecting an effect known as channel length modulation.

As  $V_{DS}$  is increased beyond  $V_{DS,sat}$  the effective length of the channel is reduced. This increases the depletion region (shown as a black line in Figure 2.7) while shortening the channel and increasing the current through the device.

*Figure 2.7 – Channel length modulation effect on an nMOS device.*

This increase in current can be modeled by modifying equation 2.5 as shown below.

$$I_D = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2 \left[ 1 + \lambda (V_{DS} - V_{DS,sat}) \right]$$

(2.6)

The parameter that accounts for the *amount of extra current* due to channel length modulation is termed as  $\lambda$ , also called the output impedance constant since it is the factor that decreases the output impedance of the device. It can be modelled as a function of the effective length of the channel, as shown by equation 2.7.

$$\lambda = \frac{\Delta L}{LV_{DS}} \tag{2.7}$$

These equations, also known as power law equations, describe the approximate behavior of transistor for *large signals*, both in the triode and saturation regions, a graph with the applications of the equations can be seen in Figure 2.8, for a constant  $V_{GS}$ . It is important to realize that they do not acquaint second order effects such as body effect.

| Region                  | Condition                                   | Equation                                                                                             |

|-------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------|

| Cut off                 | $V_{GS} < V_{th}$                           | -                                                                                                    |

| Triode                  | $V_{GS} > V_{th}, V_{DS} < V_{GS} - V_{th}$ | $I_D = \mu C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$          |

| Saturation <sup>1</sup> | $V_{DS} \ge V_{GS} - V_{th}$                | $I_{D} = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^{2} [1 + \lambda (V_{DS} - V_{DS,sat})]$ |

Table 2.2 – Large signal equations for nMOS devices neglecting some second order effects.

Figure 2.8 – Application of the model in the different working regions.

<sup>&</sup>lt;sup>1</sup> Channel length modulation has been included into the equation for the current in order to derive the drain-source resistance for the small signal model.

#### 2.1.5.-CMOS TECHNOLOGY

Complementary MOS technology refers to the design technology that uses both nMOS and pMOS FET devices together. It is important to distinguish between what fabrication and design technologies are. CMOS design technology is widely used in the semiconductor industry for the design and fabrication of microprocessors, amplifiers, and all suits of both analog and digital circuits. On top of this, each manufacturer can use another fabrication technology.

As already mentioned before, since both n and p devices have to be fabricated on the same wafer, the pMOS devices need to be placed on top of an n-well deposited on top of the common p-type wafer. How this fabrication is performed, and with what techniques describes the fabrication technology for a CMOS design technology.

CMOS is widely used nowadays due to its numerous advantages like its high input impedance. This high resistance comes from the gate of the device which presents a small capacitance, being the current going through the gate in the order of nano-amperes (a phenomenon known as leakage current). Another one of its most notable advantages is the relatively low power consumption, due to the device's charge and discharge of its parasitic capacitances when current flows through them. Nevertheless, they present a considerable mismatch as well as second order effects that renders them unsuitable for certain applications.

#### 2.2.-SMALL SIGNAL MODEL PARAMETERS

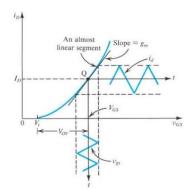

In the last section the power law equations were described, these relations are also known as the large signal model (in the case of the last section, without including second order effects). When designing an analog system in CMOS, one wants to stand on a model that is linear so that everything can be described in terms of linear relationships. This is only possible if the devices are biased for the saturation region, where the relationships between current and voltage can be assumed to be linear around the bias point.

This is why the model is called *small signal*, as one needs to assume that the linearity only holds for small deviations around the bias point. In addition, the relationship between  $V_{GS}$  and  $I_D$  can be thought of as a line with a slope and an intercept instead of the second order relationship posed by the square law equations, shown in Figure 2.9.

Figure 2.9 – Small signal model assumptions [8].

#### 2.2.1.-TRANSCONDUCTANCE

The slope of the linear relationship mentioned above is known as the gate-source transconductance. The line is defined to be  $I_D(V_{GS})$ . The slope of that line is the first order derivative, neglecting channel length modulation and body effects:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = \mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})$$

(2.8)

It is important to understand the concept of transconductance, which is the relationship between the output current of a device and the applied voltage.

#### 2.2.2.-DRAIN-SOURCE RESISTANCE

The output resistance in the saturation region, also called drain-source resistance, is an important small signal parameter as well. It is obtained as the inverse of the drain-source transconductance:

$$r_{ds} = r_o = \left(\frac{\partial I_D}{\partial V_{DS}}\right)^{-1} = \frac{1}{\lambda I_{D,sat}}$$

(2.9)

#### 2.2.3.-PARASITIC CAPACITANCES

A capacitance arises whenever there is an accumulation of charge and a consequent voltage difference between them. This means that, whenever there are two electrical components together, unavoidably, an unwanted capacitance will appear. When dealing with transistors, one can assume that the doped regions behave like plates, which are joined in parallel at an interface with other ones. The capacitance of a parallel plate capacitor is described as:

$$C = \frac{\varepsilon_o A}{d} \tag{2.10}$$

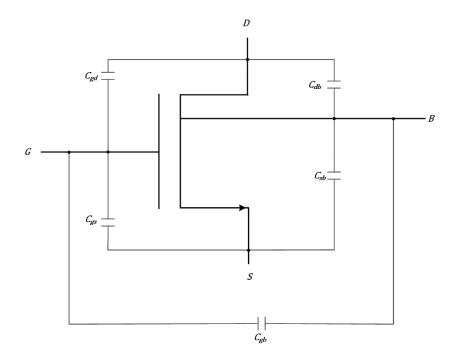

Where  $\varepsilon_o$  is known as vacuum permittivity, *A* is the area of the each plate and *d* is the distance between them. Knowing this, one can identify a set of capacitances in a typical MOSFET device whenever two differently doped regions are confronted. These can be seen in Figure 2.10.

Among all of these capacitances, the ones with the highest values are  $C_{gs}$  and  $C_{gd}$ . The latter one is often termed as the Miller capacitance when designing amplifier circuits. The capacitances related to the body appear if there is a voltage difference between the body and source (known as the body effect). Nevertheless, assuming that this potential different is null (neglecting the body effect), the capacitances can be understood as nonexistent.

These capacitances can be described, in the saturation region, by the oxide capacitance times the dimension parameters, and following equation 2.10 one can write:

$$C_{gs} \cong \frac{2}{3} C_{ox} L W \tag{2.11}$$

$$C_{gd} = W C_{GDO} \tag{2.12}$$

Where  $C_{GDO}$  is described by the channel length and the oxide capacitance. This comes from the fact that the length is not constant in saturation region due to pinch-off and channel length modulation.

Figure 2.10 – Parasitic capacitances on an nMOS device.

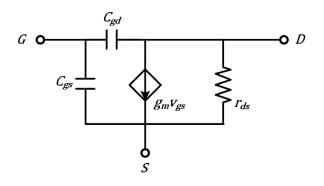

#### 2.2.4.-SMALL SIGNAL MODEL

The small signal model of an nMOS device can be represented through a small signal equivalent circuit. If body effect and channel length modulation are neglected (this is: the body and the source are at the same potential), then this circuit is shown in Figure 2.11.

Figure 2.11 – nMOS small signal model equivalent circuit.

This circuit will be useful when analyzing some of the transistor parameters discussed in the upcoming sections. As a final note, the body effect is neglected and, therefore, the capacitances related with the body vanish.

#### 2.3.-DESCRIPTION OF THE USED CMOS TECHNOLOGY

Regarding analog design, CMOS technologies are usually divided among short and long channel processes, having each their respective models. In addition to this, not all technologies are suitable for analog design, as their parameters vary from process to process.

The used CMOS technology presents a minimal channel length of 180 nm, hence not being considered short channel. In order to understand better why it can be considered a good analog technology, one needs to first review some of the concepts that lay behind analog process characterization.

#### 2.3.1.-SHORT CHANNEL EFFECTS

Short channel effects are pronounced phenomena in MOSFET devices whose channel length, L, is in the same order of magnitude as the size of depletion regions of the drain and sources with the substrate.

As transistors shrink in size, the effect of short channel effects is more prominent and the power law equations have to be rewritten. This is particularly problematic when designing analog systems, as the designs are based around the very same models that have to be modified. This is why, in general, most of analog systems are designed with a much higher *L* than the allowed minimum.

It is important to differentiate secondary effects, which are already present in long channel devices but whose magnitude increases as the length is decreased, from strict short channel effects [9]. Two of the most prominent phenomena that worsen with channel length decrease are the saturation of the carrier velocity and their mobility degeneration. Secondly, some of the most notable *strict short channel effects* are the drain-induced barrier lowering (DIBL), impact ionization and hot carrier injection (HCI).

Short channel effects will affect the transconductance parameters, carrier mobility, threshold voltage, induction of parasitic effects, and deviation from the relationships of power law equations.

#### **C**ARRIER VELOCITY SATURATION

In every transistor there exists a voltage difference across the terminals, this creates electric fields that affect charges flowing through it. One can obtain the horizontal field across the device as:

$$E_H = \frac{V_{DS}}{L} \tag{2.13}$$

This field determines the drift velocity of charge carriers across the channel up to a certain point. One cannot increase the field and expect the carrier velocity to increase infinitely as, eventually, the thermal velocity is reached.

Hence, by decreasing L, one increases the field and, at some point, the carriers' velocity due to the electric field reaches the thermal velocities. This has an impact in the power

law equations, as the current expected through the device will differ from the predicted one. This has to be accounted for by placing a parallel resistor between drain and source of the devices in order to model this effect [10].

#### **MOBILITY DEGRADATION**

The horizontal field affects the velocity of charge carriers; else ways the vertical field affects their mobility,  $\mu$ . This field is caused by the potential difference due to the device's gate which forces the carriers closer to the surface, where physical impediment takes place due to imperfections, reducing their mobility. This is accounted for by modifying the mobility parameter to account for the deviations arising from this effect.

#### DRAIN INDUCED BARRIER LOWERING (DIBL)

The drain induced barrier refers to the potential difference that an electron has to overcome in order to flow across the channel. If the drain voltage is large enough it can induce *punch through*, the extension of the depletion regions of source and drain, forming a unique one. This lowers the threshold voltage and increases the leakage current, one has to take this into account for accurate modelling of the systems.

#### IMPACT IONIZATION AND HOT CARRIER INJECTION

Both of these effects have to do with the high electric fields as a result of reduced channel lengths, note equation 2.13. Carriers are accelerated to high speed due to strong fields, becoming *hot carriers*.

Impact ionization refers to the effect of hot carriers knocking some electrons in the silicon lattice, causing parasitic effects.

On the other hand, hot carrier injection describes the effect of hot carriers getting trapped between the oxide and the silicon lattice, changing the gate voltage with respect to the channel.

#### 2.3.2.-ANALOG TECHNOLOGY

The most important parameter that describes the performance of analog circuits are transconductance parameters. It basically measures the changes in the output current with respects to variations of the applied voltage across the device, being a good indicator of the device's gain.

The transconductance parameter  $g_m$  describes the gain quality of the device, while the output conductance,  $g_{ds}$ , describes the operation of the device as a current source (note that if taken the inverse of its expression, one is defining the resistance of the MOS transistor).

When designing amplifiers, and in general analog circuits, their output impedance has to be high while maintaining a rather large gain. Defining the *intrinsic gain* as the quotient between the transconductance and the output conductance,  $g_m/g_{ds}$ , one can obtain information about the general device performance for analog design.

Another parameter that has to be taken into account is the technology's matching [2], or how is the reproducibility of a device over the technology, as there are always deviations from transistor to transistor. This is especially critical when designing fully differential amplifiers, as both half circuits need to be as similar as possible to reduce common mode noise.

#### 2.3.3.-DESIGN TIME AND COST

A scalable CMOS technology is defined as any process that presents the possibility to be enlarged with relative ease, referring to the dimensions of the devices.

Scalable technologies are desired for implementation as one can translate the known topologies to the process and then scale them accordingly to match the required specifications. This is of paramount importance in CMOS design as it allows to translate the theoretical topologies and systems easily, and then tailor them accordingly to the design specifications.

Besides the costs related to design, a 0.18 µm technology was chosen as chips for biomedical applications are not produced in quantities large enough to justify the costs of employing cutting edge fabrication technology like 7 nm or 10 nm.

A simplified explanation of this is that chips are fabricated in a fairly standard 7" wafer (without the associated photomask design cost), regardless of the technology. Therefore, the amount of chips one can obtain from a wafer increases with technology shrink down [11]. Nonetheless, the technology jump also comes with an associated cost difference. The amount of chips one can obtain from a wafer fabricated with 18 nm and 0.18  $\mu$ m increases tenfold, but the price may increase by a mere 50%. Since the market is not able to sink the offer for the extra chips resulting from using an 18 nm fabrication process, one is presented with an excess of integrated circuits and would need to increase the price to obtain a profit.

The example posed above shows how demand for a certain integrated circuit may influence the choice for the used fabrication technology.

#### 2.3.4.-TRANSISTOR CUT OFF FREQUENCY

When discussing amplifiers, one of the main parameters is the unity gain frequency, or the frequency at which the gain becomes unity. When discussing a MOSFET device, one wants to know what is the frequency at which the current gain falls to unity. This is known as the transition or cut-off frequency,  $f_T$ , of a MOSFET. It is found using a small signal model that includes all parasitic capacitances as shown in equation 2.14.

$$f_T = \frac{g_m}{2\pi C_{gs}} = \frac{3\mu}{4\pi L^2} (V_{GS} - V_{th})$$

(2.14)

This is computed by taking into account the parasitic capacitances of the transistor, in Figure 2.11 the most influential ones are shown. Nevertheless, since it is held that  $C_{gs} \gg C_{ad}$ , then one can neglect them to obtain the transition frequency.

Equation 2.14 reflects the effect of Moore's law upon the transition frequency of transistors. Whenever *L* is decreased, the speed of the transistor is increased by a factor of  $L^2$ , resulting in faster circuits. It is important to note that this conclusion does not take into account the corrections that are necessary to account for short channel effects.

Even though shrinkage of MOS devices makes circuits faster in general, when designing analog systems short channel effects are avoided at all costs, being thus speed a trade-off one should bear in mind.

#### 2.3.5.-THRESHOLD AND SATURATION VOLTAGE IMPLICATIONS

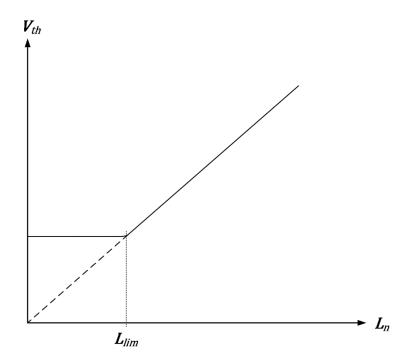

One of the main things one has to take into account when choosing between one technology or another is the saturation, threshold and the rail voltages at which it has to be placed and biased.

The voltage,  $V_{DD}$ , is restricted by the junction breakdown of the device. Ultimately, a transistor presents a series capacitor (as already seen). Equation 2.12 describes how the capacitance scales for the dimensions of the transistor. If the specified bias voltage is exceeded, excessive charges build between the *plates* of the capacitors and it breaks down, allowing current to flow while destroying the device. Even so one cannot exceed the bias voltage, powering the transistor at lower bias voltages is possible. This is also true for the gate-source voltage,  $V_{GS}$ . An excessive  $V_{GS}$  will cause the gate oxide to break down, namely due to the capacitance described by equation 2.11, destroying the device.

On the other hand, the threshold voltage,  $V_{th}$ , is the main concern when trying to bias several transistors connected in series, since it is responsible for the main part of the voltage drop across the device, decreasing the amount of available potential for devices downstream.  $V_{th}$  depends on several variables like the temperature, the carrier mobility and the dimensions of the transistor. There are several models that propose the relationship of the threshold voltage for this parameter, being the one that described it when the source is shorted to ground noted as  $V_{tho}$ , and described by equation 2.15 [12].

$$V_{tho} = V_{FB} + \phi_S \tag{2.15}$$

Where  $V_{FB}$  is the flat band voltage, and  $\phi_S$  is surface potential work function. Moreover,  $V_{FB}$  depends on the respective semiconductor work functions [13] which, in turn, depend on temperature, electron affinity of the semiconductor and the dimensions of the semiconductor device.

The threshold voltage usually decreases with the shortening of the minimal length of the technology. This dependence can be assumed to be linear until a physical limit is reached, this relationship can be described roughly as shown in Figure 2.12.

Since the threshold voltage is in lockstep with the minimal length throughout technologies before the physical limit is imposed, one can keep a more or less constant number of transistors in series. However, after the limit, the threshold voltage does not decrease so steadily and less and less devices can be fitted in design. This is an appalling effect for

analog design which already relies in the use of cascodes in order to fit more transistors into a design.

Withal this, the saturation voltage,  $V_{DS,sat} = V_{GS} - V_{th}$  is also affected, as it decreases abruptly after this limit.

*Figure 2.12 – Dependence of threshold voltage on pair length (minimal length for a given fabrication technology).*

Finally, it is important to note that this limit, in which the threshold voltage varies negligibly after a given length is reached, is imposed by the physics of the material itself, and not by any design characteristic.

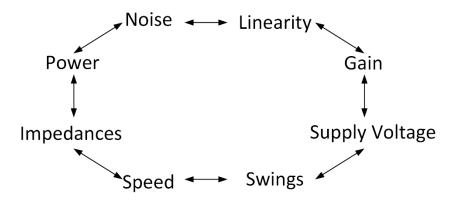

#### 2.4.-MOTIVATIONS BEHIND THE TECHNOLOGY CHOICE

Nowadays choosing a CMOS technology for analog design is extremely troublesome since most of the available processes are optimized for digital control, as already mentioned. Therefore, one needs to stick with digital CMOS technologies and to accept all of the compromises related to it. These parameter trade-offs can be summarized in a simple octagon, shown below in Figure 2.13.

Figure 2.13 – Trade-offs of analog design in digital CMOS processes [2].

Basically, in order to increase one parameter, the other two adjacent parameters will be affected [2]. One of the most importance will be the trade-off between supply voltage, the gain and swing voltages, since the goal is to decrease the power, one will have to decrease current and voltage accordingly. Besides the aforementioned, the compromise between the impedance, speed and power dissipation will be an important point of emphasis as well.

Moving onto the chosen technology, the fact that it is in the midpoint between digital and analog design makes it possible to easily and rapidly integrate analog and digital systems such as ADCs. This comes from the phenomenon that it is small enough to have low delay times (a reasonably high cut-off frequency) while still being large enough to be considered long channel (at > 65 nm minimal length), and thus minimizing short channel effects while maintaining the simpler, long channel models.

Furthermore, it presents a relatively good intrinsic gain compared with purely digital processes, being this ideal for amplifier implementation. Besides, it is a very scalable technology, meaning that the design time and fabrication costs are relatively low in comparison with other technologies.

The size of the process implies that the cut off frequency will not be very high, being it in the range of the GHz, is one of the main compromises of the used technology.

### 3.-OTA TOPOLOGIES

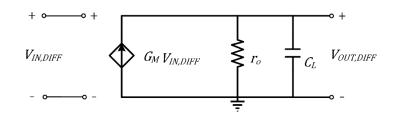

Amplifiers can be cascaded consecutively, being each amplifier a stage of the total system. This effectively increases the gain of the whole circuit, but at the expense of more power consumption and complexity. Furthermore, this means that the output behavior of the amplifier will be mainly dominated by the output stage, being thus important to choose the final stage topology with care for it to remain an OTA.

#### **3.1.-INTRODUCTORY CONCENPTS**

In order to fully grasp the equations and characteristics of the topologies described in this section, it is first necessary to describe some introductory concepts such as current mirrors and the Miller effect.

#### 3.1.1.-CURRENT MIRRORS

These are devices that accept a current input, usually termed  $I_{REF}$ , and provide a unityscaled copy of it at their output, noted as  $I_0$ . They are usually used in circuits as a sensing device for a reference current, which is then copied through a supply, or as a means to copy a current within a circuit itself. As they have to work as current sources, they need to present ideally low input and infinite output impedances.

Figure 3.1 – Simple current mirror

Intuitively one may locate these resistances at the nodes noted as (in) and (out) in Figure 3.1 for the input and output impedances, respectively. One can obtain the values for the input and output impedances of a simple current mirror by analyzing the small-signal circuit of the system, represented below in Figure 3.2.

Figure 3.2 – Small signal equivalent circuit of the simple current mirror

Doing this provides an expression for the input impedance:

$$Z_{in} = \frac{1}{g_{m1}} || r_{ds1} \sim \frac{1}{g_{m1}} \text{ (since } r_{ds1} \ll g_{m1})$$

(3.1)

On the other hand, the output impedance is equal to the drain-source resistance of the other nMOS device:

$$Z_{out} = r_{ds2} \tag{3.2}$$

However, the output resistances are too low, and the input resistances too high. This problem will be addressed in the next section.

The usefulness of current mirrors resides in their application as CC-CS. By taking the ratio between the input and output currents, and neglecting channel-length modulation effects, one can manipulate the power law equations of transistors to obtain that:

$$\frac{I_0}{I_{REF}} = \frac{W_2/L_2}{W_1/L_1}$$

(3.3)

This equation shows that it is possible to manipulate the widths, while maintaining the same length, to up-scale or down-scale the current.

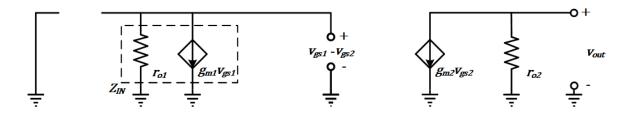

#### 3.1.2.-CASCODING THE CURRENT MIRROR

One way to improve the output impedance is to cascode the current mirror, which is done by adding another pair of transistors. The circuit is depicted in Figure 3.3.

Figure 3.3 – Cascode current mirror

The same type of analysis is performed on this system. From the small signal analysis and neglecting the body effect, one can obtain the output resistance expression:

$$Z_{out} \approx r_{ds4}(1 + r_{ds2}g_{m4}) \cong r_{ds2} \cdot r_{ds4}g_{m4}$$

(3.4)

The output resistance is effectively increased by a factor of  $r_{ds4}g_{m4}$ . However, this will reduce the available voltage for the signal, or in other words: it reduces the voltage swing.

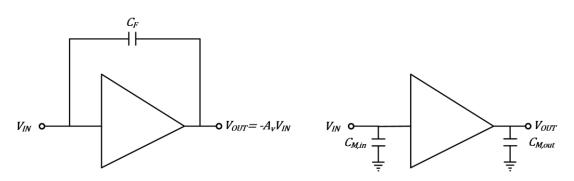

#### 3.1.3.-MILLER'S THEOREM

The Miller effect, named after John Milton Miller, explains the phenomenon that causes the increase of the input capacitance by a factor of an inverting amplifier's gain. This takes place in any amplifier with a negative feedback loop, consider the amplifier in Figure 3.4 with a certain gain  $A_v$ .

Figure 3.4 – Miller effect demonstration.

The current through the capacitor is provided by the difference between the input and output. However, one can decompose the capacitances as shown in Figure 3.4 (right) and obtain the following expressions:

$$C_{M,in} = C_F (1 + |A_v|) \tag{3.5}$$

$$C_{M,out} = C_F \left( 1 + \frac{1}{|A_v|} \right) \tag{3.6}$$

The input capacitance results in the feedback capacitance,  $C_F$ , multiplied by a factor of the gain, effectively increasing it at the input and slowing down the operation of the system.

#### **3.2.-SYSTEM STABILITY AND COMPENSATION**

In this section, the basis and criteria for the stability of a system will be set as well as the introduction and types of phase compensation will be reviewed.

### 3.2.1.-STABILITY

An electronic system, and any system in particular, presents a gain and phase response. Let's assume an LTI (linear and time invariant) system, depicted in Figure 3.5.

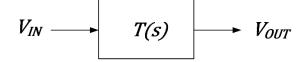

Figure 3.5 – LTI, open loop system.

When an input voltage is applied, the system will provide a modified output. This modification comes from the properties of block T which, in addition, vary with respect to frequency. The gain of a system is the proportion of the input and output magnitudes of the system, while phase is the time shift of the signal. Since the input is a sinusoidal wave, this shift can be measured in terms of degrees or radians. In Figure 3.6 the gain of the system would be 2 (for the given frequency at which the signal is introduced), and a phase shift of  $2\pi/3$ .

Figure 3.6 – Response of the LTI system to an input.

Since the gain and phase shift vary with respect to frequency Bode plots are used to assess the variations of both parameters over the entire frequency spectrum.

A description of margin is the extra amount of *something* that shields from instability. Therefore, the lower the margin, the more likely the system will be to be unstable. When designing amplifiers, one always talks about phase margin. In order to understand the underlying concept to this, it is important to know beforehand what makes a system unstable.

From control theory, a system described by a transfer function, like the one shown in Figure 3.5, will be unstable if there is at least one pole in the right half plane. This can be also extrapolated to closed loop systems, like the one shown in Figure 3.7. Then, the transfer function of the system becomes equation 3.7.

$$G(s) = \frac{T(s)}{1 + T(s)}$$

(3.7)

$$V_{IN} \longrightarrow T(s) \longrightarrow V_{OUT}$$

Figure 3.7 – LTI, closed loop system

Since instability implies having a non-bound parameter, the system can be unstable only if the gain (this is: the modulus of the transfer function) goes to infinity. This only happens whenever the denominator of the transfer function goes to zero, or mathematically:

T(s) = -1

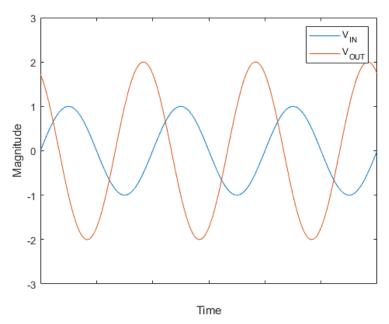

This is what corresponds to a phase shift of -180° and a gain of 0 dB. If one was to adjust the gain of a system, the Bode plot of the gain would move up or down, depending on the adjustment. Whenever the gain is modified, so is the frequency at which 0 dB is attained, until eventually one hits the value at which the phase shift is -180°, rendering the system unstable. This can be intuitively seen in Figure 3.8. The amount which one would have to modify the gain in order to locate the 0 dB gain at the  $\omega_{180}$  frequency is called the gain margin.

Figure 3.8 – Bode plot for gain increase.

The same concept can be extrapolated to phase margin, one looks for how much phase delay it is necessary, at 0 dB gain, to reach the -180° frequency.

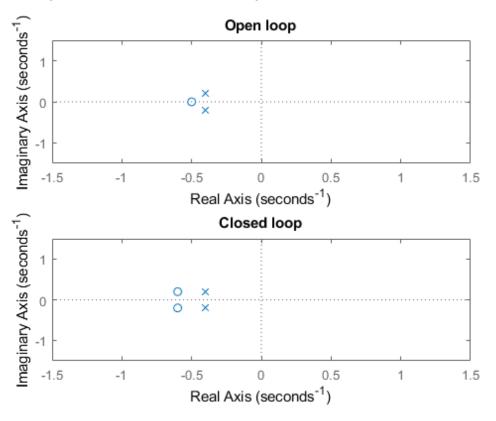

Usually, designing a system in open loop is much easier than doing so in closed loop. But one would like to know if the system is stable in closed loop. Hence, the paramount question arises of how to assure that the closed loop system is stable by looking just at the open loop system.

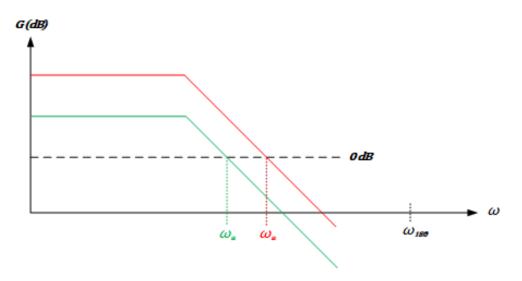

This is where Nyquist plots are useful. Closing the loop alters the locations and amounts of the poles and zeros, one cannot assess stability looking just at the pole-zero diagram. Let's illustrate this with a simple example, for a second order system with a transfer function shown by equation 3.8.

$$T(s) = \frac{2s+1}{5s^2+4s+1}$$

(3.8)

Then, the pole-zero diagram for this open loop system can be sketched as shown in Figure 3.9 (top). However, if the loop is closed, the transfer function is modified according to equation 3.7, and one has to look for the roots of the denominator. Furthermore, the pole-zero diagram is modified as shown in Figure 3.9 (bottom).

Figure 3.9 – Pole-zero diagram for equation 3.8 and its closed loop system.

This simple example illustrates the difficulty of extrapolating information about poles and zeros from an open loop system to a closed loop system using a pole-zero diagram. However, one can make a transformation to change from this diagram to one which is in the  $\omega$  domain. This is, by taking points from the imaginary and real chart and fitting them

into the transfer function, one is able to plot them against an  $\omega$  axis. If one feeds the entire right half plane, the Nyquist diagram is obtained.

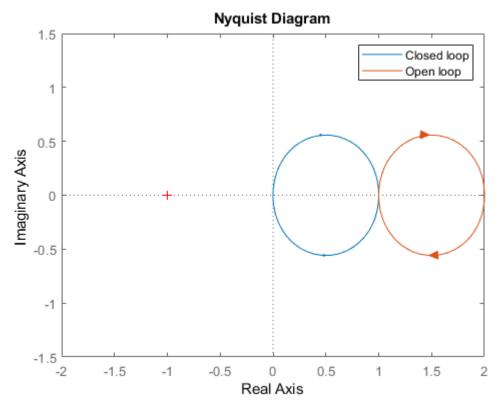

Plotting the Nyquist diagrams for both the open loop and closed loop system, as shown in Figure 3.10, shows that by the difference between the poles of these two systems is a translation.

Figure 3.10 – Nyquist diagram for Figure 3.9.

Besides this, if the system happens to encircle the point (-1,0) it will be unstable. This is known as the Nyquist criterion. It is basically a statement that amounts to having poles in the right half plane.

Having this mathematical criterion is very useful, since one can now set the basis for the phase margin so that the amplifier does not become unstable in closed loop. Defining the phase margin as

Phase margin =

$$180^{\circ}$$

+ (phase at which the system gain is 0 dB)

In practice, one designs its system so that it accommodates for unknown factors. When designing an amplifier one has to account for the mismatches in fabrication, inaccuracies of the theoretical models and many other factors. Henceforth, a positive phase margin of 90° is desirable.

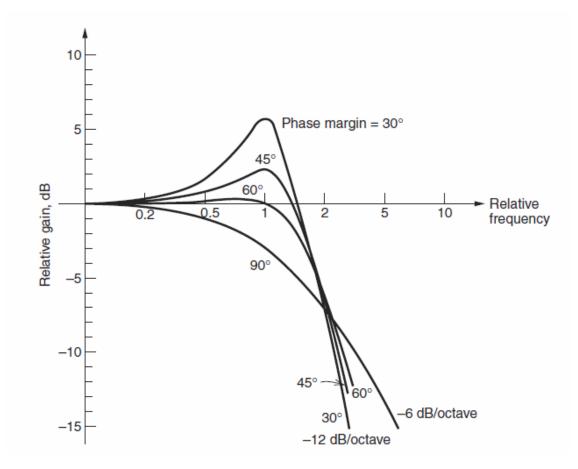

To conclude, an illustration on how phase margin affects the gain of the system around the unity gain value is shown in Figure 3.11 [14]. It is straightforward to see that the tighter the phase margin is, the more unstable the system will appear.

*Figure 3.11 – Gain and frequency normalized plot for closed loop amplifiers with different phase margins [14].*

#### **3.2.2.-FREQUENCY COMPENSATION**

When configuring an amplifier with negative feedback, one is basically trading in open loop gain to obtain a smaller closed loop gain in order to better bound parameters such as distortion, noise and temperature fluctuations, amongst other.

However, if the feedback loop phase shift is taken into account together with the internal stages delay and it amounts to 360°, the output of the device will reinforce the input creating an oscillatory behavior. This is usually measured by taking the step response of the system and measuring parameters such as the overshoot and the settling time. In order to decrease these values, frequency compensation techniques are employed.

There are several techniques that are used when designing amplifiers which try to improve the aforementioned conditions, being the most popular among them pole splitting [15].

Pole splitting refers to the introduction of a capacitor (usually known as Miller capacitance) which takes advantage of the Miller effect to effectively split the equations of the two most prominent poles in the system from each other. In this way their frequencies can be located with different capacitances.

#### **3.3.-SINGLE STAGE TOPOLOGIES**

Single stage topologies refer to systems of CMOS devices that amplify a signal in one single step. This type of topology has usually less gain than cascaded ones, being the first ones simpler to implement.

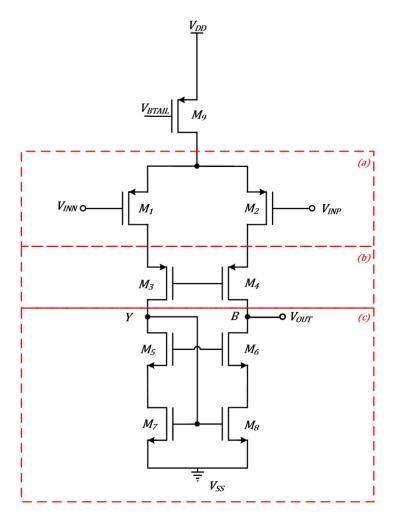

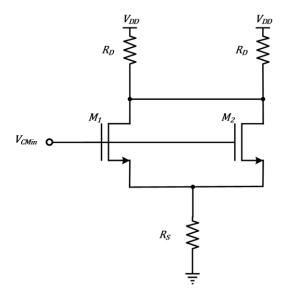

#### 3.3.1.-FOLDED CASCODE OTA