# DESIGN AND CHARACTERIZATION OF A LOW VOLTAGE CMOS ASIC FOR MEDICAL INSTRUMENTATION

BACHELOR THESIS BIOMEDICAL ENGINEERING

AUTHOR: ELENA SÁNCHEZ FERNÁNDEZ TUTOR: Dr. ENRIQUE PREFASI SEN. ASSOCIATE PROFESSOR: MARCOS DOMÍNGUEZ SUÁREZ Leganés, June 2017

## ACKNOWLEDGMENTS

Me gustaría agradecer a mi tutor Enrique Prefasi y a Marcos Domínguez su ayuda y apoyo en todas las fases de este Trabajo Fin de Grado. Gracias a su ayuda, orientación y consejos he podido realizar este Proyecto pudiendo profundizar en algunos temas y ampliando los conocimientos adquiridos.

Dar las gracias a mis padres, Marino y Olga, creo que nunca podré agradecer todo el apoyo, cariño y ayuda que me habéis dado a lo largo de mi vida y por su total confianza en mí durante todos mis estudios.

Por supuesto, dar las gracias a Alberto por hacerme ver que soy capaz de superar los obstáculos aun cuando yo creo que no puedo y por todos los buenos momentos vividos juntos.

Quisiera dedicar este trabajo a mis abuelos Marino, Vitorina, José Luis y Paula por su cariño incondicional. Pero en especial me gustaría dedicarlo a mi abuelo José Luis que a pesar de que no me pueda ver terminar la Carrera y ver cómo me gradúo en la Universidad estaría muy feliz de que concluyera esta etapa de mi vida.

## ABSTRACT

The acquisition of biomedical signals requires analogue to digital converters of high resolution, low voltage of power and low consumption. The solution for this need is the use of new sigma delta conversion architectures such as the one tested in this Bachelor Thesis.

This work covers the design of the instrumentation necessary for the operation of Application-Specific Integrated Circuit Sigma Delta Analog-to-Digital Converter (ASIC  $\Sigma\Delta$  ADC) that is already manufactured and its integration into a Printed Circuit Board (PCB). It also includes the development of the necessary software that facilitates the accomplishment of the necessary tests and the analysis of the data that will allow to characterize the operation of the fabricated prototype. Finally, the results and conclusions of the project will be described.

The ASIC to be tested in this Bachelor Thesis consists of a180-nm Complementary Metal-Oxide Semiconductor (CMOS) bandpass  $\Sigma \Delta$  ADC developed to fulfil the specifications of a fully-integrated receiver for Magnetic Resonance Imaging (MRI). Integrating an integrated CMOS receiver into a single chip will help improve image quality by avoiding the use of many coaxial cables that are used to connect the Radio Frequency (RF) coils to the scanning hardware. The proposal made is a very simple Low-IF receiver characteristics in which a continuous time Low-IF bandpass ADC is the most efficient architecture. The circuit in continuous time replaces the classic filter only thus, an anti-alias filter would be necessary. In addition, the bandpass filter assists in the attenuation of the quantization noise in the bandwidth of interest, while at the same time the stability of the system is easily achieved due to the selected Low-IF.

## INDEX

| ACKNOWLEDGMENTS                                          | i    |

|----------------------------------------------------------|------|

| ABSTRACT                                                 | ii   |

| INDEX OF FIGURES                                         | vi   |

| INDEX OF TABLES                                          | viii |

| GLOSSARY OF TERMS                                        | ix   |

| 1 Introduction                                           | 1    |

| 1.1 State of art                                         | 1    |

| 1.2 Objective                                            | 5    |

| 1.2.1 Block diagram of the project                       | 8    |

| 1.3 Project development stages                           | 10   |

| 1.4 Regulation framework                                 | 11   |

| 1.5 Memory structure                                     | 13   |

| 2 Analog to Digital Converter (ADC)                      | 15   |

| 2.1 Definition of ADC                                    | 15   |

| 2.1.1 Sampling                                           | 15   |

| 2.1.2 Quantization                                       | 16   |

| 2.1.3 Coding                                             | 17   |

| 2.2 Nyquist Theorem                                      |      |

| 2.3 Oversampling                                         |      |

| 2.4 Continuous Time Sigma Delta ADC                      | 19   |

| 2.4.1 Resolution                                         | 22   |

| 2.5 Definitions                                          | 22   |

| 2.5.1 Signal-to-Noise Ratio (SNR)                        | 22   |

| 2.5.2 Dynamic Range (DR) and Effective Resolution (ENOB) | 23   |

| 3 Instrumentation for testing the ASIC (Sigma-Delta ADC) | 24   |

| 3.1 Power supply                                         | 27   |

| 3.1.1 Power supply 1.8 V                                 | 27   |

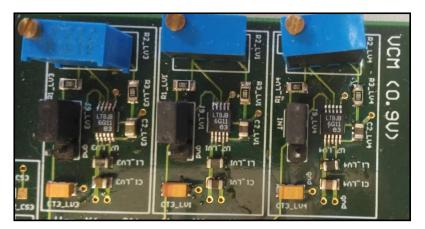

| 3.1.2 Power supply 0.9 V                                 | 29   |

| 3.1.3 Voltage reference                                  |      |

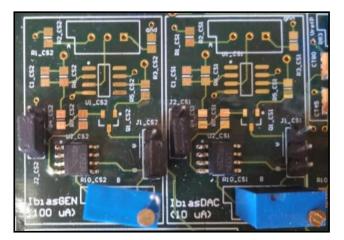

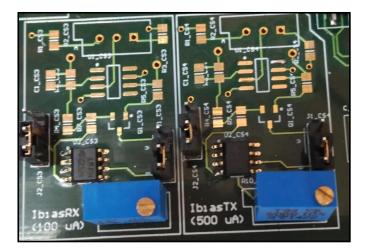

| 3.2 Current source                                    | 31 |

|-------------------------------------------------------|----|

| 3.3 Adaptation of input signals. RF Transformers      | 35 |

| 3.4 Control signals. ARDUINO connections              | 36 |

| 3.5 Output signal. LVDS signal transmission           | 38 |

| 3.5.1 Single-ended transmission                       | 39 |

| 3.5.2 Differential transmission (LVDS)                | 40 |

| 3.5.3 Comparing serial and parallel data transmission | 41 |

| 4 Final PCB and Instrumentation                       | 43 |

| 4.1 External power supply                             | 45 |

| 4.2 Internal power supply                             | 46 |

| 4.3 Differential voltage reference                    | 47 |

| 4.4 Ibias Current                                     | 48 |

| 4.5 Ibias Current LVDS                                | 48 |

| 4.6 Data input / Data output                          | 49 |

| 5 Connections and Close Control Loop                  | 51 |

| 5.1 Power consumption                                 | 56 |

| 6 Measurements                                        | 57 |

| 6.1 Measurements Results                              | 58 |

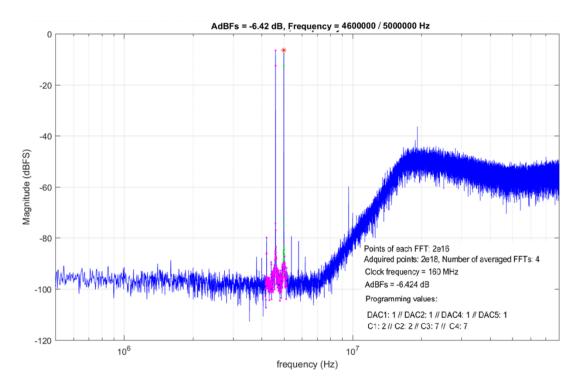

| 6.2 FFT calculation                                   | 58 |

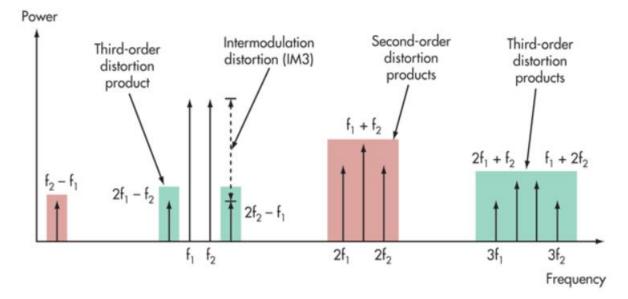

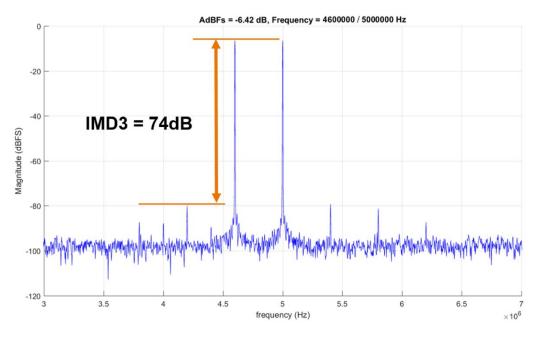

| 6.2.1 Intermodulation                                 | 63 |

| 6.3 Cadence Simulation                                | 65 |

| 6.4 Measurements conclusions                          | 67 |

| 7 Socioeconomical environment                         | 68 |

| 7.1 Financial budget                                  | 68 |

| 7.1.1 Cost of material                                | 68 |

| 7.1.2 Engineering cost                                | 69 |

| 7.1.3 Final budget                                    | 69 |

| 7.2 Socioeconomical impact                            | 70 |

| 8 Conclusions                                         | 71 |

| 8.1 Future work                                       | 72 |

| ANNEX I Programming bits                              | 74 |

| ANNEX II Values of the C1-C4 capacitors of the OA1: OA4 | 78 |

|---------------------------------------------------------|----|

| ANNEX III PCB Layout                                    | 80 |

| ANNEX IV MATLAB Software                                | 82 |

| 9 References                                            |    |

## **INDEX OF FIGURES**

| Figure 1.1 First MRI [1], [2]                                                  | 1   |

|--------------------------------------------------------------------------------|-----|

| Figure 1.2 Actually MRI [3]                                                    | 2   |

| Figure 1.3 Prototype of wearable coil array and integrated electronics and Sem | ıi- |

| rigid PCB [4]                                                                  | 3   |

| Figure 1.4 a)Block Diagram of integrated CMOS receiver [5] and b)Block         |     |

| Diagram of the proposed CMOS receiver                                          | 4   |

| Figure 1.5 Block Diagram of Low-IF $\Sigma \Delta$ ADC                         | 5   |

| Figure 1.6 Detail of the components of Low-IF $\Sigma\Delta$ ADC               | 6   |

| Figure 1.7 Flow of design integrated circuit. Scope of Bachelor Thesis         | 7   |

| Figure 1.8 Configuration Loop of the ASIC                                      | 8   |

| Figure 1.9 Flow of design integrated circuit. Scope of Bachelor Thesis         | .13 |

| Figure 2.1 Analog Digital Converter                                            | .15 |

| Figure 2.2 Quantization error model                                            | .16 |

| Figure 2.3 Signal representation, quantized signal and quantization error [10] | .17 |

| Figure 2.4 Lineal model of a CT - $\sum \Delta$ modulator                      | .21 |

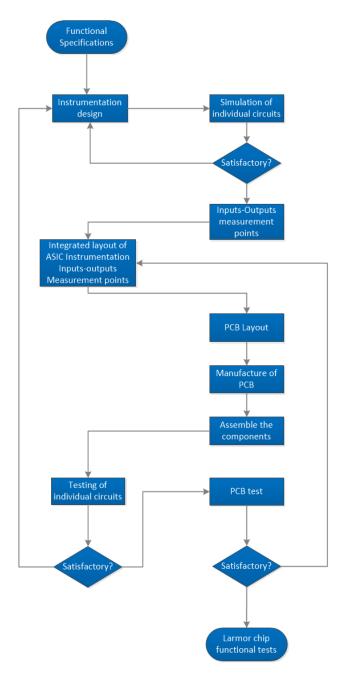

| Figure 3.1 Flow chart PCB board development                                    | .24 |

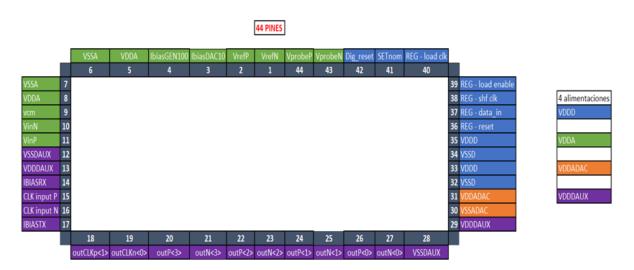

| Figure 3.2 Pinout Chip LARMOR                                                  | .25 |

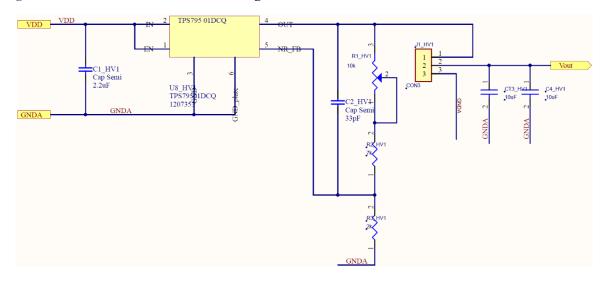

| Figure 3.3 Power supply 1.8V                                                   | .28 |

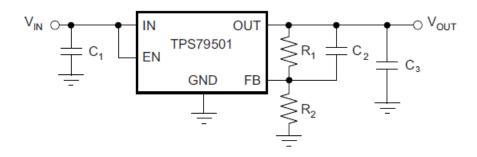

| Figure 3.4 Typical Application, Adjustable Output [13]                         | .28 |

| Figure 3.5 Voltage reference 0.9V                                              | .30 |

| Figure 3.6 Current Source [15]                                                 | .33 |

| Figure 3.7 Turn on voltage [15]                                                | .33 |

| Figure 3.8 Schematic current source                                            | .34 |

| Figure 3.9 Picture of Current Source                                           | .34 |

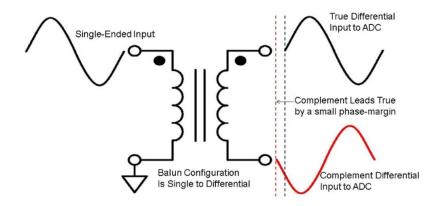

| Figure 3.10 Transformer Single-ended to differential signal [16]               | .35 |

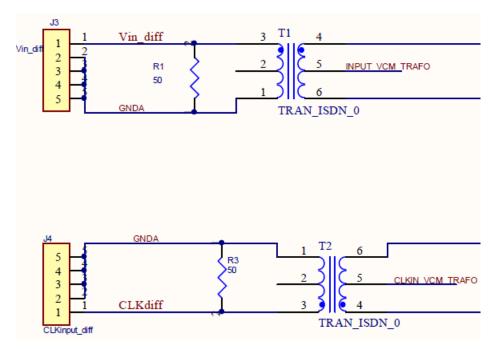

| Figure 3.11 Circuit Single-ended to differential signal                        | .36 |

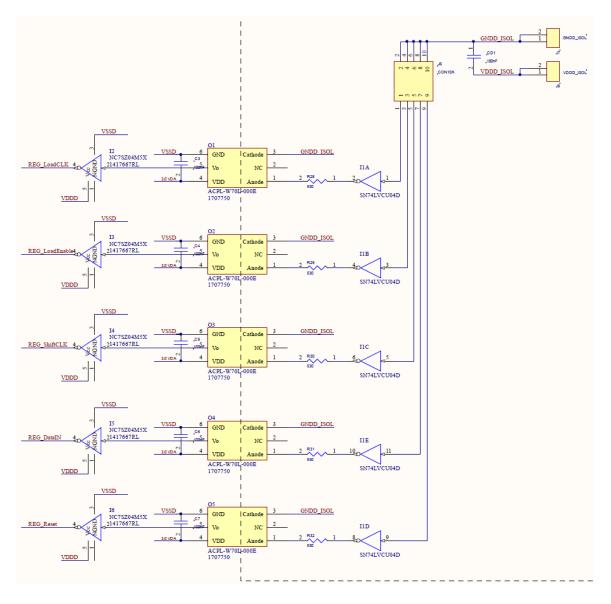

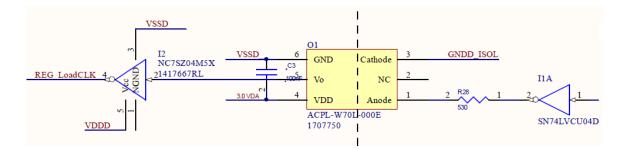

| Figure 3.12 Isolated Arduino signals                                           | .37 |

| Figure 3.13 Individual Arduino signal circuit                                  | .38 |

| Figure 3.14 Single-Ending Interface Circuit Schematic Design [21]              | .39 |

| Figure 3.15 Differential Interface Circuit Schematic Diagram [21]              | .40 |

| Figure 3.16 LVDS Signalling decoding                                           | .41 |

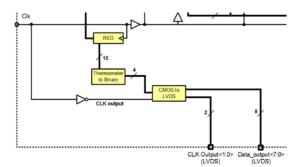

| Figure 3.17 CMOS to LVDS                                                       | .42 |

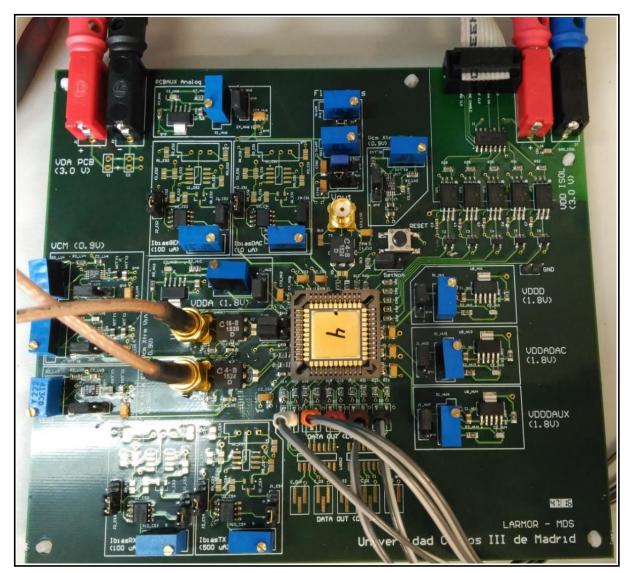

| Figure 4.1 PCB for he ASIC characterization                                    | .43 |

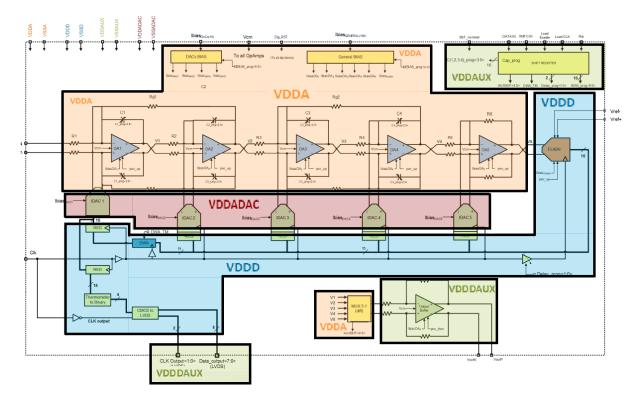

| Figure 4.2 Schematic of the PCB with the restyled subsystems                   | .44 |

| Figure 4.3 ASIC Power domain                                                   | .45 |

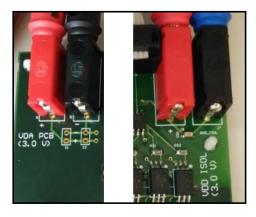

| Figure 4.4 External PCB power supply VDA PCB and VDD Isol Arduino              | .46 |

| Figure 4.5 Internal PCB power supply 1.8 V to obtain reference voltages for |     |

|-----------------------------------------------------------------------------|-----|

| FLASH                                                                       | .46 |

| Figure 4.6 Circuit reference voltages for FLASH                             | .46 |

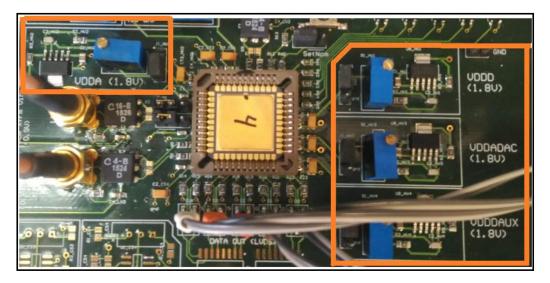

| Figure 4.7 Internal PCB power supply 1.8 V                                  | .47 |

| Figure 4.8 Internal PCB power supply 1.8 V                                  | .47 |

| Figure 4.9 0.9 V differential ASIC Reference                                | .48 |

| Figure 4.10 Ibias OpAmp and DAC                                             | .48 |

| Figure 4.11 Ibias OpAmp and DAC                                             | .49 |

| Figure 4.12 Input signal adaptation circuit                                 | .49 |

| Figure 4.13 ISOL Arduino circuit                                            | .50 |

| Figure 4.14 DATA OUT LVDS                                                   | .50 |

| Figure 5.1 Connections                                                      | .51 |

| Figure 5.2 Arduino                                                          |     |

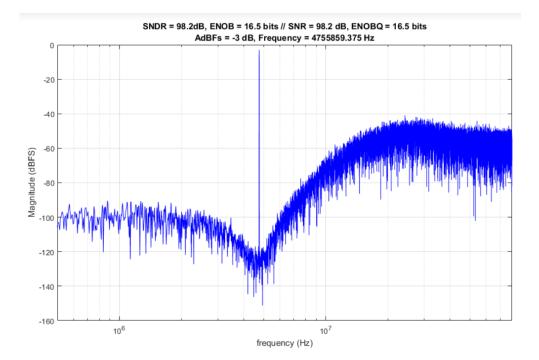

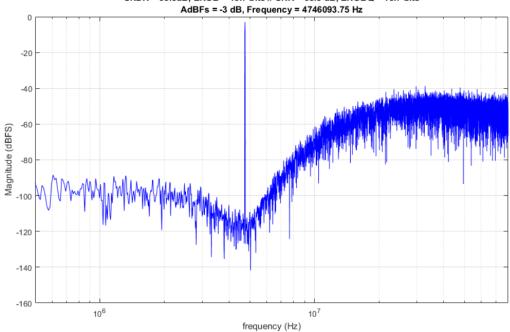

| Figure 6.1 Measured FFT Idle channel                                        |     |

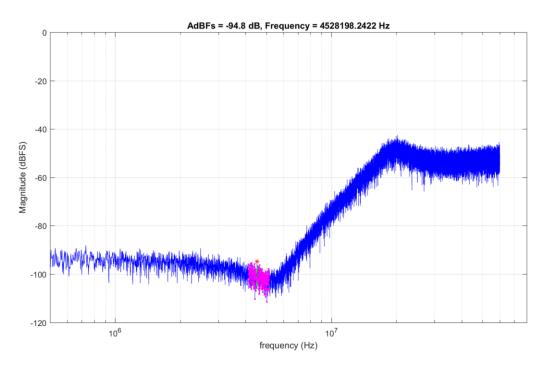

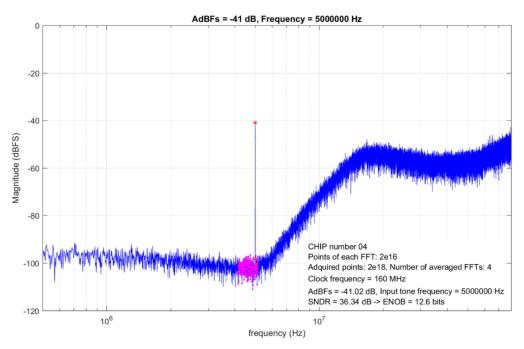

| Figure 6.2 Measured. FFT 5MHz, -41 dBFS signal                              | .59 |

| Figure 6.3 Measured. FFT 5MHz, -41 dBFS signal extension                    | .60 |

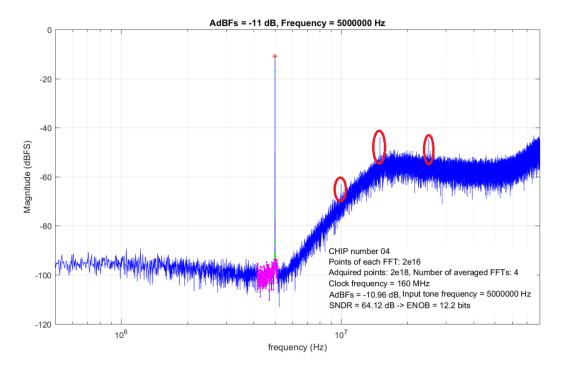

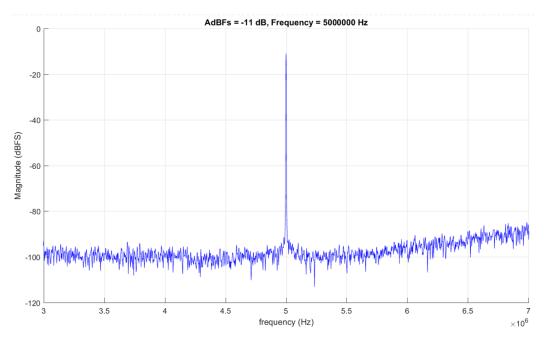

| Figure 6.4 Measured. FFT 5MHz, -11 dBFS signal                              | .60 |

| Figure 6.5 Measured. FFT 5MHz, -11 dBFS signal extension                    | .61 |

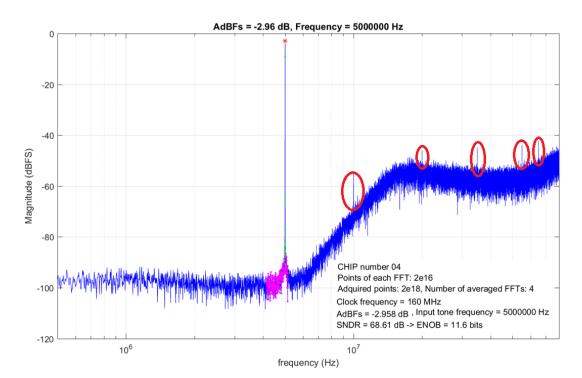

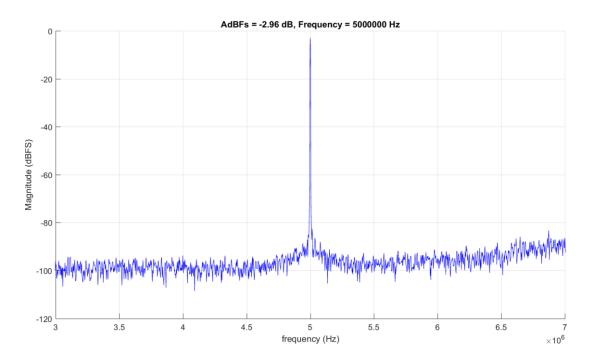

| Figure 6.6 <b>Measured.</b> FFT 5MHz, -3 dBFS signal                        | .61 |

| Figure 6.7 Measured. FFT 5MHz, -3 dBFS signal extension                     | .62 |

| Figure 6.8 Dynamic Range                                                    | .63 |

| Figure 6.9 Intermodulation distortion [22]                                  | .64 |

| Figure 6.10 Intermodulation Test                                            | .64 |

| Figure 6.11 Intermodulation Test extension                                  | .65 |

| Figure 6.12 Simulated. FFT 4.76 MHz, -3 dBFS signal                         | .66 |

| Figure 6.13 <b>Simulated</b> . FFT 4.76 MHz, -3 dBFS signal                 | .66 |

| Figure 1 Annex 1. LVDS coding                                               | .74 |

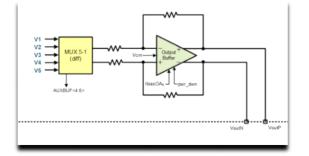

| Figure 2 Annex 1 . Vprobe multiplexer                                       | .75 |

| Figure 3 Annex 1 . IDAC5                                                    | .75 |

| Figure 4 Annex 1. IDAC1/4                                                   | .76 |

| Figure 5 Annex 1 . Delay_prog Flash                                         | .76 |

| Figure 6 Annex 1. Programming the C1:C4 of the integrators                  | .76 |

| Figure 7 Annex 1. SHIFT REGISTER                                            | .77 |

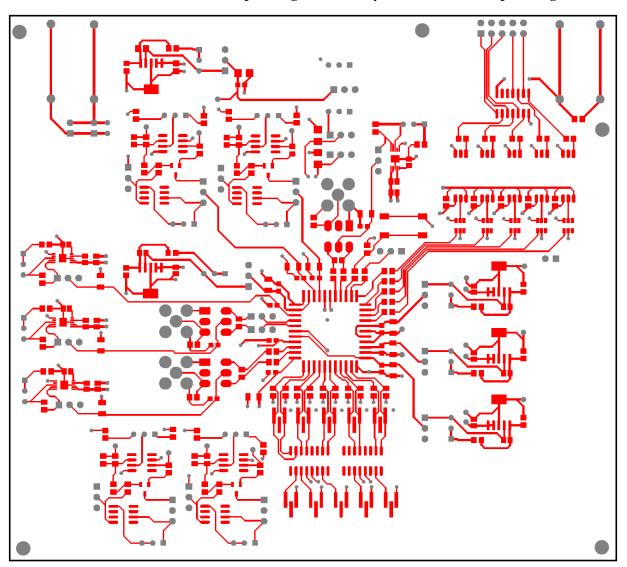

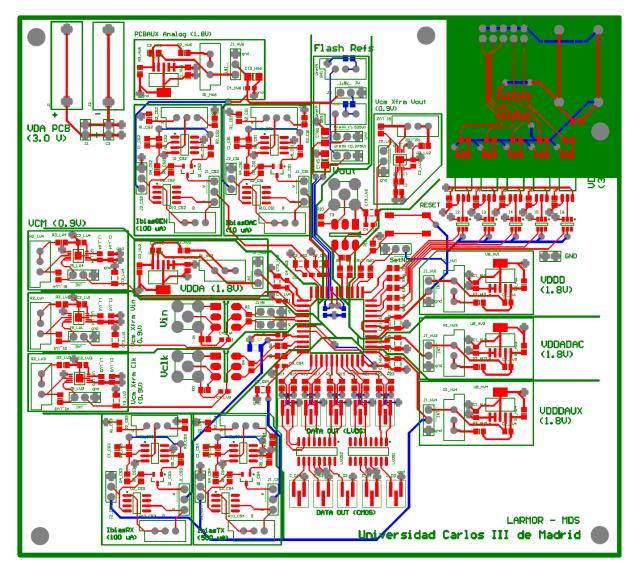

| Figure 1 Annex 3 . Layout1                                                  | .80 |

| Figure 2 Annex 3 . Layout1                                                  | .81 |

## **INDEX OF TABLES**

| Table 1.1 Timetable                          | 10 |

|----------------------------------------------|----|

| Table 3.1 Interfaces all pins ASIC           | 26 |

| Table 3.2 Power supply on the PCB            | 27 |

| Table 3.3 Reference Voltage Flash            | 31 |

| Table 3.4 Ibias                              | 31 |

| Table 3.5 Technical features [17]            | 36 |

| Table 5.1 Initial data for sweeping test     | 54 |

| Table 5.2 ENOB, SNR. Datasheet configuration | 55 |

| Table 5.3. Power Consumption                 |    |

| Table 6.1. Programming bits                  | 58 |

| Table 6.2. Input signal parameters           | 58 |

| Table 7.1 Cost of project materials          | 68 |

| Table 7.2 Cost of personnel                  | 69 |

| Table 7.3 Total Cost of the project          | 69 |

| Table 1 Annex 1. Programming bits            | 74 |

| Table 2 Annex 1. Control bits, dedicated Pin | 77 |

| Table 1 Annex 2. C1 possible values          | 78 |

| Table 2 Annex 2. C2 possible values          | 78 |

| Table 3 Annex 2. C3 possible values          | 79 |

| Table 4 Annex 2. C4 possible values          | 79 |

|                                              |    |

## **GLOSSARY OF TERMS**

| ADC     | Analogic Digital Converter                  |

|---------|---------------------------------------------|

| ARDUINO | Open-source electronic prototyping platform |

| ASIC    | Application-Specific Integrated Circuit     |

| CMOS    | Complementary Metal-Oxide Semiconductor     |

| СТ      | Continuous Time                             |

| DAC     | Digital to Analog Converter                 |

| DC      | Direct Current                              |

| DR      | Dynamic Range                               |

| DRC     | Design Rules Checking                       |

| EMI     | Electromagnetic Interference                |

| ENOB    | Effective Number Of Bits                    |

| ESD     | Electrostatics Discharge                    |

| FFT     | Fast Fourier Transform                      |

| HDD     | Hard Disk Drive                             |

| Hw      | Hardware                                    |

| IF      | Intermediate Frequency                      |

| IFSR    | IF Sampling Frequency Ratio                 |

| IMD     | Intermodulation Distortion                  |

| IMEC    | Interuniversity Microelectronics Centre     |

| IMEC    | Interuniversity Microelectronics Centre     |

| IQ   | In Quadrature                        |

|------|--------------------------------------|

| LDO  | Low dropout                          |

| LNA  | Low Noise Amplifier                  |

| LSB  | Least Significant Bit                |

| LVDS | Low Voltage Differential Signalling  |

| LVS  | Layout versus Schematic              |

| MRI  | Magnetic Resonance Imaging           |

| NAS  | Network Attached Storage             |

| NTF  | Noise Transfer Function              |

| OSR  | Oversampling Ratio                   |

| РСВ  | Printed Circuit Board                |

| RF   | Radio Frequency                      |

| SMD  | Surface Mount Device                 |

| SNDR | Signal to Noise and Distortion ratio |

| SNR  | Signal to Noise Ratio                |

| SQNR | Signal to Quantization Noise Ratio   |

| STF  | Signal Transfer Function             |

| Sw   | Software                             |

| Т    | Tesla                                |

| VCM  | Common Mode Voltage                  |

| VGA  | Variable Gain Amplifier              |

## **1** INTRODUCTION

Magnetic Resonance Imaging (MRI) is one of the most widely used imaging techniques in medical diagnostics. MRI is a non-invasive technique to produce highly detailed images of tissue in the body. A great variety of anatomical and functional features, processes, and diseases can be visualized with this approach.

MRI employed a strong and static magnetic field which is applied to the patient using super-conducting magnets (submerged in liquid helium, -268.9 °C), which aligns the nuclear spin of the abundant hydrogen atoms in water and fat of tissues in the same and opposite direction of the magnetic field. In MRI, a radio frequency wave, or a radio frequency pulse (RF), is transmitted into the patient. When this wave is sent with a very specific frequency, some spins will change their alignment as a result of this new magnetic field. After the RF pulse, they generate a signal as they return to their original alignment. This is the measured MR signal.

## **1.1 STATE OF ART**

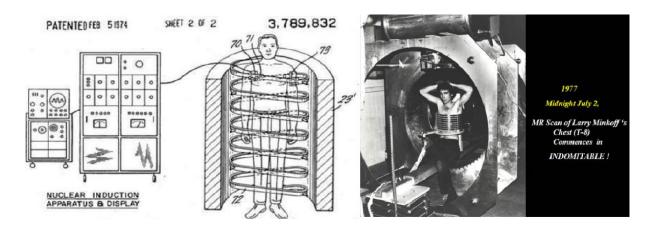

From the first MRI machine manufactured in 1977 by Dr. Raymond Damadian, see Figure 1.1, there have been many advances.

Figure 1.1 First MRI [1], [2]

MRI equipment has improved from devices where coils, signal transmitters and receivers were located in different rooms, which meant that in order to extract the signal from the magnetic fields and be able to process them, a lot of very long shielded coaxial cables were needed. Currently, in magnetic resonance imaging equipment, the instrumentation of the receivers is made up by discrete commercial elements, but as technology has made such a progres it has been possible to make receiver PCBs increasingly smaller and immune to magnetic fields. This has allowed them to be placed within the magnetic field, which has made it possible to shorten the coaxial cables from tenths of meters in length to a few meters, see Figure 1.2

Figure 1.2 Actually MRI [3]

Surface coil arrays brought in proximity to the human body enhance the performance of an MRI measurement both in speed and signal-to-noise ratio. However, size and cabling of such arrays can deteriorate the performance of the imaging. Ultimately, the receiver must be placed directly on the coil to avoid bulky cable blocks and to receive the data directly in bore and send them digitally to the MRI scanner through the optical fiber. This implementation is the cheapest, most flexible and insensitive one to magnetic fields. In order to achieve this configuration, it is necessary for the PCB of the receiver to be as small as possible, and this can only be achieved if you have a receiver fully integrated into a single chip. The integration of the receiver into a single, small, nonmagnetic and very low power CMOS chip is the key to this evolution of MRI equipment. [4]

Figure 1.3 Prototype of wearable coil array and integrated electronics and Semi-rigid PCB [4]

The Department of Electronic Technology of the Carlos III University of Madrid, through the Mixed-Signal Circuits Laboratory and working with IMEC (Interuniversity Microelectronics Centre), have designed an Application-Specific Integrated Circuit (ASIC) for Biomedical Instrumentation, focused on MRI systems. The technology used in this ASIC is 1.8V 180nm CMOS.

The ASIC is suitable for the integration of a multichannel receiver of a MRI scanner. The use of this ASIC will simplify the receiver while also making it cheaper. Due to its low consumption it can be used in portable systems.

The ADC is targeted for receivers with operating carrier frequency between 64 and 128 MHz, which covers commercial 1,5 T and 3T scanners.

In this ASIC only the Analog-to-Digital Converter (ADC) is implemented. This is the first prototype that will be evaluated. It will be used to develop all the instrumentation needed for testing. In further steps, the rest of the blocks of the MRI receiver will be integrated into a second ASIC. The reason for this is that the ADC is the most demanding block, and has to be evaluated separately. In addition, all the instrumentation that will be developed for measuring this first ASIC, will be also used for the second ASIC.

This work will focus on the design and measuring of all the instrumentation needed for testing the ASIC, along with all the back-end digital calibration that will be used in the final system.

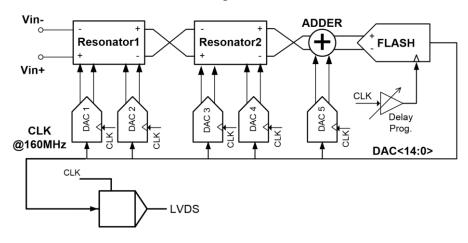

The chip ASIC consists of three main conceptions.

- 1. Firstly, the use of a Continuous- Time  $\Sigma\Delta$  modulator is proposed to exploit its inherent anti-alias filter and remove or at least relax the filter front.

- 2. Secondly, a bandpass loop filter is used which is more efficient for a narrow bandwidth as 1 MHz. Moreover, a low IF (Intermediate Frequency) to Sampling Frequency Ratio (IFSR) allows the ADC to behave close to a low-pass ADC in terms of stability and block requirement.

- 3. Finally, IQ demodulation can be implemented in the digital decimation filter by choosing a proper IFSR.

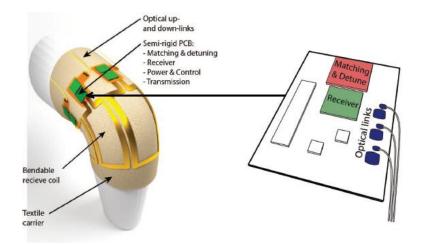

In Figure 1.4 a) the diagram of a receiver which is the most frequently investigated so far can be seen.

Figure 1.4 a)Block Diagram of integrated CMOS receiver [5] and b)Block Diagram of the proposed CMOS receiver.

In Figure 1.4 b) the proposed receiver diagram in which the input filter has been removed and the ADC is a bandpass instead of a low pass can be seen.

It is proposed to change the Low-pass ADC by the Band-pass ADC because it uses an increased IF up to few MHz. The main benefit of increasing IF is the freedom to design a frequency plan that accommodates enough bandwidth, avoid flicker noise and includes mixing of spurious tones which can simplify the Low Noise Amplifier (LNA) and the mixer. A bandpass ADC processes the narrowband signal without a penalty on oversampling. Moreover, a Low IF to sampling frequency Ratio (IFSR) allows the ADC to behave close to a low-pass ADC in terms of stability and block requirements. This option will be more efficient.

## **1.2 OBJECTIVE**

The goal of this Bachelor Thesis is to design all the instrumentation needed in order to evaluate the proposed ASIC. In addition, a close control loop will be also implemented in order to have real time measuring capabilities of the ASIC.

The main objectives of the Bachelor Thesis are:

- 1. Characterize the ASIC that **includes only the ADC**. This Bachelor Thesis is the first step in order to develop the complete MRI ASIC. In next steps this ADC will be integrated in another ASIC together with the sensor, LNA, mixer, ADC and digital filters (see Figure 1.4).

- 2. Develop all the instrumentation needed to measure the ASIC:

- a. The PCB to mount the ASIC

- b. The electronic to supply the ASIC

- c. The electronic to readout the digital Data of the ASIC

- 3. Develop a close control loop of the ASIC

- 4. Develop a software to post-process the data of the ASIC (digital backend filters)

- 5. Validate the Design

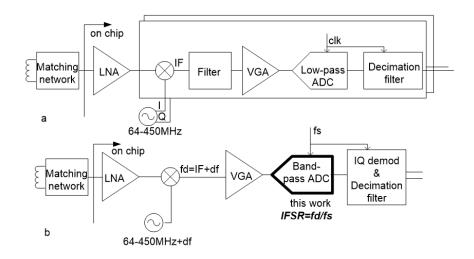

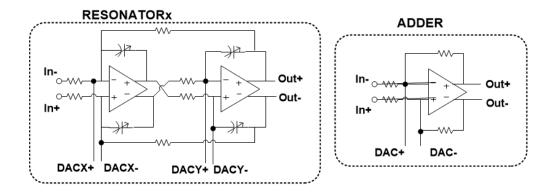

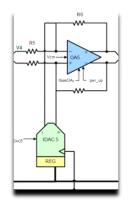

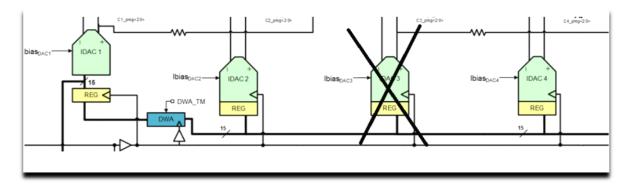

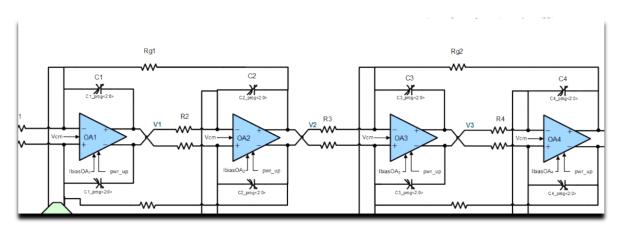

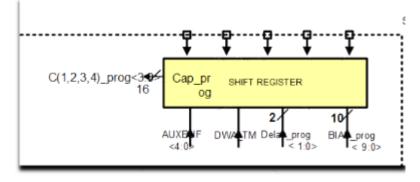

The core of the Continous Time (CT)  $\Sigma\Delta$  ADC implemented in this first version of the ASIC can be observed in Figure 1.5. The details of the schematics of the resonators and the adder are shown in Figure 1.6.

Figure 1.5 Block Diagram of Low-IF  $\Sigma \Delta$  ADC

Figure 1.6 Detail of the components of Low-IF  $\Sigma \Delta$  ADC

By definition an ASIC is a custom-made integrated circuit for a particular use. In order to be able to characterize it after its manufacturing it is necessary to have a controlled Hw-Sw (Hardware – Software) environment where the ASIC can be placed, simulating the expected inputs of previous subsystem and obtaining the outputs which must be delivered to the next subsystem. This is why it is essential to create a test platform where the measures to ensure that chip is correct are carried out. In order to guarantee that the tests have no problem outside the develop platform. Therefore, ASIC will be implemented in a printed circuit, thus it is necessary to generate a PCB.

Once the development platform has been manufactured and tested, ASIC testing is now made possible. The chip has internal elements which by external configuration can have a certain number of values (the measurements have to be done every configuration). Measurements of configurations which do not meet established requirements are discarded and measures meeting requirements are stored. After testing, a set of ASIC configurations are obtained with their measurements now meeting the requirements.

As our ASIC is a part of a larger circuit, we must provide the following subsystem with the values of the measurements of the configurations which meet the requirements, As well as the figures of merit of each configuration.

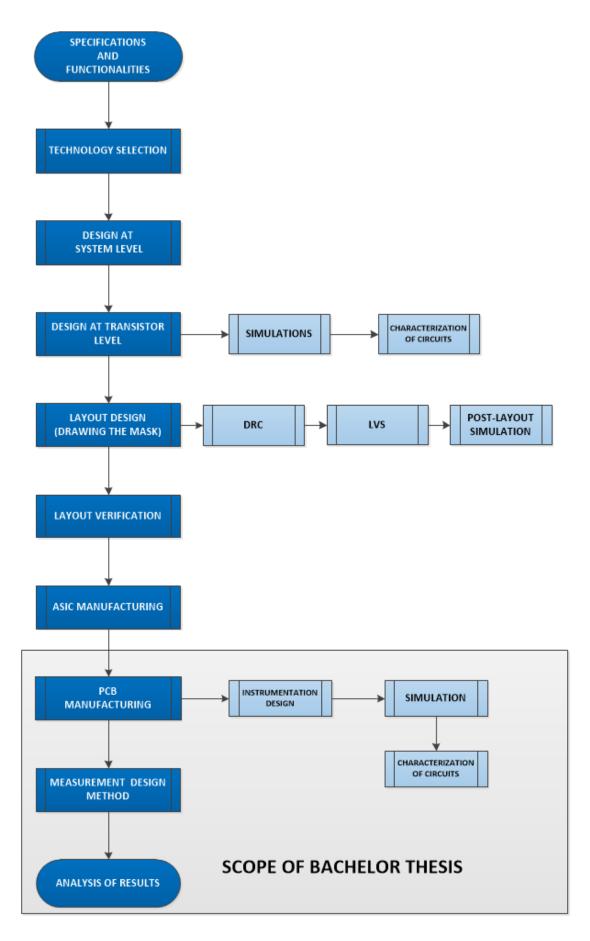

It is time to frame this Bachelor Thesis within the main project, see Figure 1.7.

Figure 1.7 Flow of design integrated circuit. Scope of Bachelor Thesis.

The flow desing of an analog integrated circuit with a custom design (ASIC) is in Figure 1.7. The first stage of this flow is writing the specifications and requirements that must be met by the integrated circuit. In the second stage this technology is chosen, in this case the technology selected is the CMOS of 180nm. Next, the component subcircuits at high level are define. The designs are made at the transistor level, which once simulated and characterized the layout is performed. After carrying out all the necessary checks to ensure that the design corresponds to what has been specified, th ASIC is sent to manufacturing . With all ASIC specifications clear, all necessary instrumentation is prepared to be able to perform the tests. When all the instrumentation of PCB has been characterized, the PCB is made and sent to manufacture. At the end, a systematic method is developed that facilitates the accomplishment of the tests and finally the analysis of the data is done where it will be possible to say if the developed design is valid or not.

#### **1.2.1 BLOCK DIAGRAM OF THE PROJECT**

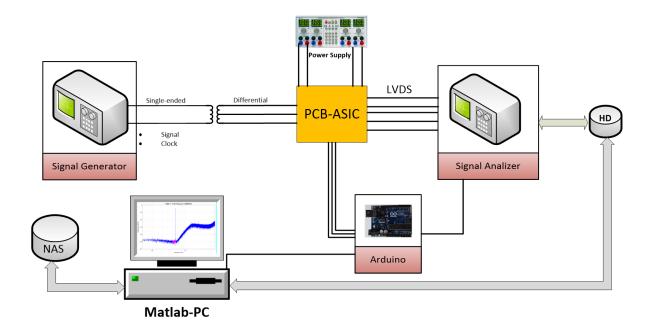

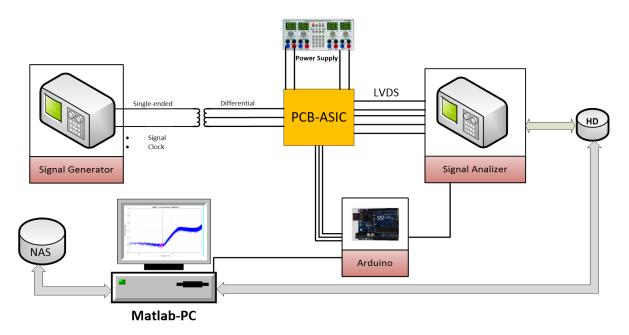

In Figure 1.8 is represented the closed-loop system schematic that controls the tests of the different configurations in "Real Time". Configuration tests have a long duration in time because the possible configurations are very high. The system operates autonomously and only needs a technician initializing it.

Figure 1.8 Configuration Loop of the ASIC

Now, the functional blocks of the ASIC test loop are described below.

- **1. Instrumentation:** for the ASIC chip to perform its function it is necessary to develop the supporting circuitry (current sources, stabilized voltage sources, voltage references, control of digital inputs, etc). All this instrumentation will be integrated in a printed circuit, PCB. This will prevent all problems associated with standard test boards.

- 2. **Power of the system:** The system is powered by a DC (Direct Current) power supply that does not introduce power supply (50 Hz). In the trial it has been used a "**Programmable Power Supply HM7044**" by HAMEG.

- Input signal: to test the different configurations a signal generator is used, performed with "Programmable Synthesizer HM8134-2" by HAMEG. The test signal used in the configuration process is a sinusoidal signal of 5 Mhz.

- 4. The clock: In CT ΣΔ ADC modulators, the sampling frequency is much higher than the Nyquist frequency, the sampling frequency is equal or higher than 160 MHz, so 16 times higher than the Nyquist frequency, a signal generator is used "Vector Signal Generator SMV-03" by Rohde & Schwarz. The ratio between the sampling frequency to the Nyquist frequency is known as OSR ("Oversampling Ratio").

- 5. **Output signal:** The ASIC provides an output that has to be processed, for this purpose a **Logic Analyzer** is used (**Agilent 16902A**). The analyzer captures the digital output data of the CT  $\Sigma\Delta$  ADC modulator, when indicated by the Matlab Script through the "Arduino" system, which is automatically saved in a text file with extension .csv, on a network hard drive.

- 6. **PC with Matlab Script:** A PC with Matlab and library is used to operate the "Arduino" microcontroller system. The Matlab Script performs the following functions:

- a. Handling the ASIC shift register using the Arduino to change the configuration parameters.

- b. Handling of the Logical Analyzer using the Arduino, this microcontroller system indicates to the Logical Analyzer the beginning and end of the capture of the test signal, the average duration of each capture is nine seconds.

- c. Reading the text file that the logical analyzer has recorded in the Hard Disk Drive (HDD). The FFT (Fast Fourier Transform) is calculated (with the FFT, it is verified how good or bad is the output signal), the results of the data processing are saved.

- "Arduino" microcontroller system: the "Arduino" is used to change the digital inputs of the ASIC, and also to handle the Logical Analyzer. ARDUINO is handled by the Matlab script.

A close loop is implemented, this controls:

- 1. The ASIC configuration data.

- 2. The acquisition and storage of the data provided by the ASIC.

- 3. Processing the data to determine which is the best result.

- 4. Storage of data processing.

The configuration of the ASIC will be done with an "Arduino" microcontroller, managed by a Matlab script that will also handle the processing of the data obtained from a logic analyzer.

## **1.3 PROJECT DEVELOPMENT STAGES**

#### Table 1.1 Timetable

The Table 1.1 timetable reunite the different phases of development of this Bachelor Thesis. The different stages took place at different times and with different dedication in terms of workin hours. For this reason, the timeline has been constructed without dates only weeks are counted without indicating the start with a certain date.

The project was separated into 10 stages, the first was to study the  $\Sigma\Delta$  modulation to understand what is going to be tested, the second was to design and

simulate with the program Proteus the designed circuits. Once these circuits are validated, they were designed in the Altium program to integrate all the designs and perform the PCB. With the PCB in the laboratory, the ASIC was inserted and all discrete components (resistors, capacitors, connectors, etc.) were soldered.

The objective was to have the Sw prepared for when the PCB was fully ready. The nominal ASIC configuration data with which it was manufactured were calculated using a proprietary Matlab tool. The results obtained with the nominal configuration will be the basis for comparison with the real results. The simulated characterization will be the reference point for performing selective sweeps of tests in values near the nominal values. The best results of these tests are those that will be compared with the simulation values to determine the validity of the design.

#### **1.4 REGULATION FRAMEWORK**

Within the development of the project it is imperative to take into account certain safety parameters to maintain the good balance of the same. In order to do this, it is necessary to take into consideration both the correct working conditions that must be maintained in a laboratory to avoid damaging the measurement equipment and the electrostatic protection required when handling integrated circuits to avoid damaging them by electrical discharges. Neither should be forgotten the necessary protection of technician to those discharges. It is necessary to establish what steps have to be taken to fulfill the above conditions

In the specific case of this project based on the design and assembly of a PCB, the worker may be exposed to risks that may be related to the welding of different elements in printed circuit boards or the electrical risk involved in electronic operations. [6]

The welding used in electronics belongs to the type known as electric resistance welding with tin, but in this project welding paste has also been used. Although the risks involved in electrical welding with tin are minimal, it is necessary to take into account certain aspects that minimize the risks at work. Thus, it is recommended to check that the electrical equipment and the instruments are in perfect conditions of use. It is essential for the welder to be placed in a support orienting the electrode in the opposite direction of the operator. And finally avoid inhaling the fumes that occur in the welding. This last point is closely related to the welder paste as this one has very toxic fumes so it is necessary a good ventilation of the room where it is being welded, in our case the laboratory, as well as an individual protection for each technician using masks. [7]

Since the main source of energy for this type of electronic devices is the electrical energy , this one must be also taken into account. For this reason, electrical risk (according to RD 614/2001) was defined as that originated by electric power, specifically including the risks of: [6]

- Electrical shock by contact with elements in tension or with masses put accidentally in tension. Because of this, the chip has protections so as not to be burnt. But it also implies that the technician can suffer from this electrical shock, as by touching the pads of the chip currents through the skin may be induced. In addition, these currents, though small may be, are high enough to cause internal damage to the chip. That is why the pads have "ESD (Electrostatic Discharge) protections" which consist of adding suitable circuits, with diodes to give a path to ground current avoiding electrostatic discharge. This would avoid damage to transistors or internal circuits of the chip.

- Electric shock or electric arc burns.

- Fires or explosions caused by electricity

One of the main electrical hazards is electrostatic discharges that can cause random failures in electronic components that are difficult to be controlled and pursued. So it is necessary to take protective measures against them.

These electrostatic discharges occur as a result of the static electricity that is generated due to following processes: [8]

- **By friction (or triboelectricity):** when two materials are rubbed against each other or separated from each other.

- **By load per contact**: because two conductors are one of them more charged than the other. Then the most charged conductor gives charge to the other one up to equally adquiere a potential difference in a value that may not be zero.

- Load crown: occurs when a very small surface is at a very high potential generating corona discharge.

- **Inductive load**: an object produces an electrostatic field which acts at a distance on nearby objects polarizing the charges. When the polarized object contacts another, one more loads are transferred or picked up, resulting in a loaded object.

Due to all these risks it is necessary to take into account prevention techniques such as: [6]

- **Procedural:** They try to establish safe operational methods of a general or specific nature for each activity or work operation.

- **Signaling**: They are based on the location of warning signs, caution, prohibition or information in workplaces with electrical risk.

- **Detection and identification**: They consist of identifying properly and checking the voltage in the electrical installations, before acting on them

- **Instructive:** These are intended to get the training and training of workers exposed to electrical risk, indicating the correct way of using equipment, tools, facilities, symbology and signaling

## **1.5 MEMORY STRUCTURE**

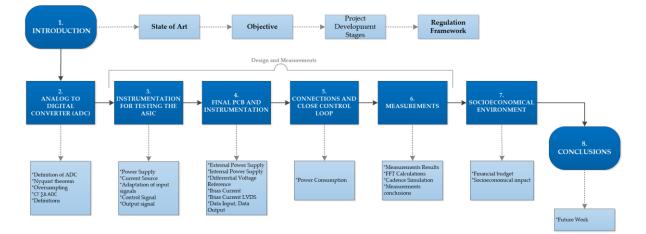

This report is structured in eight chapters, according to Figure 1.9.

Figure 1.9 Flow of design integrated circuit. Scope of Bachelor Thesis

In the **Introduction** this Bachelor Thesis is contextualized within the technological development of the instrumentation of receivers of the MRI equipments. Moreover, the scope within the European project of constructing an integrated Receiver is defined. For this reason the **State of Art** of the MRI equipment, the **Objectives** to comply and the **Regulation Framework** are reflected. Also reflected is the **Project Development Stages**.

Chapter 2 describes what is an ADC and introduces the generalities of CT  $\Sigma\Delta$  ADC and the main figures of merit.

In Chapters 3 and 4, and taking into account the electrical specifications of the ASIC prototype, all the necessary instrumentation is individually designed. Once this is validated through simulation these sepcifications will be used to design the PCB (**Objective 2**).

Chapter 5 shows the connections between the PCBs, the measurement equipment and the PC, which is the close control loop used to carry out the tests and obtain the data for later analysis. It is also show the power consumption of the ASIC for different configurations. Later on, the functionality of the Sw developed is clearly described (**Objective 4**).

In Chapter 6 the results of the ASIC characterization,  $\Sigma\Delta$  ADC modulator, are analyzed. The results obtained from the simulation are compared to the best configurations obtained during the tests in order to decide whether the proposed design is valid or not (**Objective 5**). In the result analysis it is obtained that the ASIC works properly as expected and Its characterization has been possible (Objetive1).

Chapter 7 contains the budget and the socioeconomical impact of the project.

Chapter 8 sets out the scope achieved in each of the objectives, justifying if the principal of this Bachelor Thesis **Objective 1** has been satisfactorily achieved. The possible future works are going to be analyzed in order to improve the test.

## **2** ANALOG TO DIGITAL CONVERTER (ADC)

Within the goals of this Bachelor Thesis, it was indicated that an ASIC which is implemented as an CT  $\Sigma\Delta$  ADC. This section will briefly describe the conversion of the analog signals to digital signal explaining the converter implemented in that ASIC.

### **2.1 DEFINITION OF ADC**

There are many reasons for digitally processing an analog signal instead of processing the signal directly in the analog domain. Firstly, a digital programmable system allows flexibility in reconfiguring the digital processing operations simply by changing the program. Reconfiguration of an analog system usually implies hardware redesigning. Secondly, the tolerance in analog circuit make it extremely difficult for the system designer to control the accuracy of an analog signal processing system. Thirdly, it is more cheaper the digital hardware. [9]

In order to work in the digital world, it is necessary to have an interface that communicates the analog world with the digital world. This interface is the analog to digital converters. One practical limitation is the speed of operation of ADC.

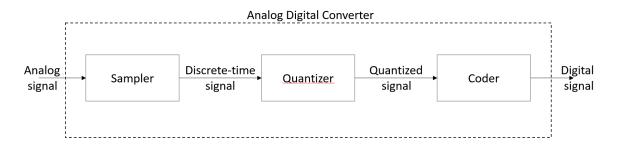

The ADCs have implemented three function: sampling, quantification and coding, as can be seen in Figure 2.1.

Figure 2.1 Analog Digital Converter

#### 2.1.1 SAMPLING

This is the conversion of a continuous-time signal into discrete time signal obtained by taking "samples" of the continuous-time signal at discrete-time instant.

The temporal distance between taking one sample and the next one is called the sampling period and it is denoted as **T**. [9]

#### 2.1.2 QUANTIZATION

This is the conversion of a discrete-time continuous-valued signal into a discrete-time discrete-valued signal. The value of each signal sample is represented by a value selected from a finite set of possible values. The difference between the unquantized sample and the quantized output is called quantization error. [9]

The figures of merit commonly used to characterize the quantization are defined below.

A range of an ADC is defined as the difference between the maximum value that can be measured and the minimum value.

$$R = (Vmax - Vmin) \tag{2.1}$$

It is defined as number of levels of the coding in the equation (2.2) where N is the number of bits of the ADC.

$$L = 2^N \tag{2.2}$$

The quantization step is the ratio between the range equation (2.1) and the number of levels equation (2.2).

$$\Delta = \frac{R}{L} = LSB \tag{2.3}$$

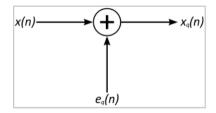

The quantization error follows the logic of Figure 2.2 where X(n) represents the sampled signal and X(q) is the quantized signal, the difference eq(n) is the quantization error, see equation (2.3)

Figure 2.2 Quantization error model

$$e_q(n) = X_{q(n)} - X(n)$$

(2.4)

The quatization error will be between:

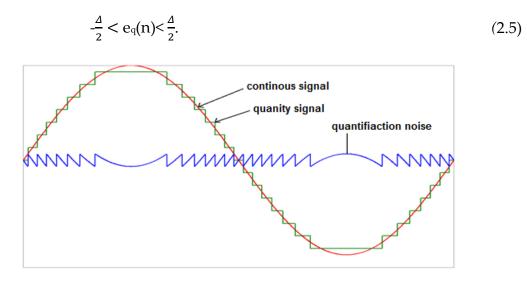

Figure 2.3 Signal representation, quantized signal and quantization error [10]

Although, as shown in Figure 2.3, the quantization error has a well-defined form, when treated with real signals, it can be considered as a White Gaussian noise signal. Also, the error is uniformly distributed across all frequencies, provided that the number of bits 'N' is large, that the input signal is within the quantization range and that the input signal is much larger than the Least Significant Bit (LSB).

It can be shown that for a sinusoidal signal with a peak to peak value equal to "R", the Signal to Quantization Noise Ratio (SQNR), is:

$$SQNR = 6.02 * N + 1.76 [dB]$$

(2.6)

The SNQR gives information about the maximum theoretical efficiency of an ideal ADC converter. Performance will be lower due to others factors such as thermal noise, distortions, converter architecture, nonlinearities etc.

### 2.1.3 CODING

In the coding process, each discrete value that has come out of the quantization process is represented by a **b**-bit binary sequence.

### **2.2 NYQUIST THEOREM**

If a signal is bandlimited and if the samples are taken sufficiently close together, in relation to the highest frequency present in the signal, then the samples uniquely specify the signal and it can be reconstructed perfectly. This result is called the sampling theorem and it can be expressed as follows:

Let X(t) be a bandlimited signal with X( $\omega$ )= 0 for  $|\omega| > \omega_M$ . Then x(t) is uniquely determined by its samples x(nT), n= 0, ± 1, ± 2, ± 3 .... If

$$\omega > 2 \omega_{\rm M}$$

(2.7)

where

$$\omega_s = \frac{2\pi}{T} \tag{2.8}$$

Given these samples, it is possible to reconstruct x(t) by generating a periodic impulse train which successive impulses have amplitudes that are successive sample values. This impulse train is then processed through an ideal lowpass filter with gain T and cutoff frequency greater than  $\omega_M$  and less than ( $\omega_S - 2 \omega_M$ ). The resulting output signal will exactly equal x(t).

The sampling Frequency  $\omega$ s, is also referred to as the Nyquist frequency. The frequency  $2\omega_M$  under the sampling theorem, must be exceeded by the sampling frequency.

### **2.3 OVERSAMPLING**

In signal processing, oversampling is the process of sampling a signal with a sampling frequency significantly higher than the Nyquist frequency. Oversampling improves resolution, reduces noise and helps avoiding aliasing and phase distortion by relaxing anti-aliasing filter performance requirements.

## 2.4 CONTINUOUS TIME SIGMA DELTA ADC

Miniaturization of electronic systems using nanoscale technologies allows to achieve greater speed in the devices. This miniaturization has made possible the development of  $\Sigma\Delta$  modulators. [11]

Analog ADCs have many non-idealities that arise from random and systematic errors in circuit implementation processes, there are errors in the manufacturing process because the silicon is not homogeneous. These errors represent reliability problems; they can be compensated or calibrated after manufacture. On the other hand, these circuits undergo a time-dependent degradation due to the aging of the transistors, which means that the performance of the chip changes over time, which can cause circuits to change from fully functional to non-functional. Also different sources of disturbances such as electromagnetic interference (EMI) or substrate noise coupling can cause the chip to change, functionally correct circuit or failed circuit.

In addition to the above,  $\Sigma\Delta$  ADCs offer a key advantage for their integration into the ASIC. Unlike the Nyquist ADCs, whose resolution depends heavily on the high precision of their component blocks, the oversampling and quantization noise shaping techniques used in the  $\Sigma\Delta$  ADC allow speed to be exchanged for accuracy. Thus it can be obtained a circuit which is relatively insensitive to imperfections and aging of components. For these reasons, the  $\Sigma\Delta$  modulation techniques are ideal for the implementation of high performance ADCs integrated in nanometric CMOS technologies, which are better suited to provide fast digital circuits than accurate analog circuits.

The ASIC chip to be configured is a  $\Sigma\Delta$  modulator in continuous time, and the main features of these modulators will be described below.

Advantages of Modulators CT  $\Sigma\Delta$ . [11]

- Faster operation with lower power consumption, driven by continuous operation time loop filter in which the dynamics of the circuits is not parasitic (as happens in switching capacitor circuits).

- Lower impact of errors caused by the sampling operation. This is a direct consequence of the fact that the sampling operation does not take place at

the input of the modulator, but within the loop. Sampling errors are filtered analogously to quantization noise.

- Lower thermal noise because, when not sampled, there is no folding effect "frequency folding" (which means less aliasing). In discrete-time modulators, high-frequency thermal noise signals collapse in the spectrum because the sampling rate is low, and in the signal recovery process the collapsed frequencies cause distortion and cannot be separated or distinguished of the original signal.

- Less impact of "digital noise" or "switching noise" switching noise is attenuated by the action of the loop filter, in the same way as the quantization noise.

- "Anti-aliasing", the loop filter can be employed for this purpose, relaxing the specifications or even eliminating the need for pre-filtering "anti-aliasing".

In quantization, an error called quantization error is generated. The error is a non-linear function of the input signal and produces a similar effect to a white noise source, because the error sequence is wrong with the signal and will be evenly distributed in the range  $[-\Delta/2, +\Delta/2]$ , see equation (2.5.

The  $\Sigma\Delta$  modulators are based on oversampling and noise shaping, which is responsible for minimizing the quantization noise in the desired band (Nyquist band).

OSR is the Oversampling Ratio:

$$OSR = \frac{fs}{fo} \tag{2.9}$$

Where *fs* is the sampling frequency and *fo* is the Nyquist frequency. The increase of the sampling frequency decreases the noise in the band of our signal.

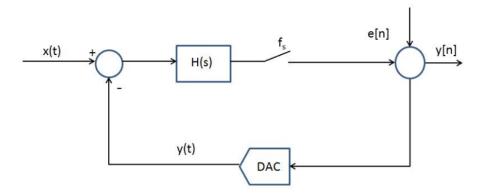

In this modulator there is an H(s) filter whose function is to cause the quantization noise to decrease to low frequencies and increase to high.

Considering the quantizer as the only source of noise that is added to the filtered signal, a linear model equivalent to  $CT-\Sigma\Delta$  can be obtained, as shown in Figure 2.4.

Figure 2.4 Lineal model of a CT -  $\sum \Delta$  modulator

In this case, the modulator can be seen with two inputs **x**, **e** and one output **y**, in domain Z can be represented as:

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E(z)$$

(2.10)

Where X(z) and E(z) are the Z transforms of the input signal and the error, Signal Transfer Function  $S_{TF}(z)$  and Noise Transfer Function  $N_{TF}(z)$  are respectively the transfer function of the input signal and the quantization noise.

$$S_{TF}(z) = \frac{H(z)}{1 + H(z)}$$

(2.11)

$$N_{TF}(z) = \frac{1}{1 + H(z)}$$

(2.12)

For the values where  $H(z) \gg 1$ ,  $N_{TF}(z) \rightarrow 0$  y la  $Y(z) \approx X(z)$ . The spectral noise conformance will be performed by the H(s) filter, if we design it to take as large a value as possible within the bandwidth of our interest, the  $N_{TF}$  will be very close to zero and the  $S_{TF}$  very close to one, managing to take out most of the noise out the bandwidth of our interest. [12]

When implementing a CT- $\Sigma\Delta$  ADC it is very important to calculate the H (z), it will be the starting point to calculate the values of the discrete components. The calculation of this function becomes more complicated as the degree is increased, being extremely complicated above grade 3.

#### 2.4.1 RESOLUTION

Today the CT-  $\Sigma\Delta$  converters are a good choice for applications that require a digital signal processing with high speeds and good resolutions.

The resolution of these modulators depends on the order of the modulator filter, the higher the order of H(s), the higher the resolution however, the higher the order the worse the stability. The higher the filter order the more quantification noise is transferred to high frequencies with the consequent increase of the SNR and therefore of the dynamic range.

Then to increase the resolution of the modulator, an increase in the order of the filter can be performed as well as increasing the number of bits used in the quantification, or even increasing the OSR.

### **2.5 DEFINITIONS**

At this point it is important to define the most important figures of merit that are used to characterize the oversampling converter.

### 2.5.1 SIGNAL-TO-NOISE RATIO (SNR)

It is the ratio of the output power at the frequency of an input sinusoid to the uncorrelated in-band error power. Ideally, only quantization noise is accounted to compute SNR, expressed as:

$$SNR = 10 \ Log_{10} \left(\frac{\frac{A^2}{2}}{P_Q}\right) \tag{2.13}$$

Where:

A= Amplitude sinusoid input signal

PQ = Power noise quantification.

If errors due to noise and distortion are taken into account, the Signal-to-Noise Ratio (SNDR)is normaly used.

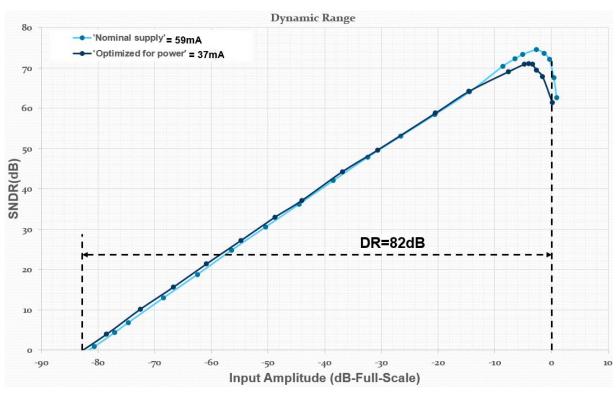

### 2.5.2 DYNAMIC RANGE (DR) AND EFFECTIVE RESOLUTION (ENOB)

The dynamic Range is defined as the ratio of the output power at the frequency of an input sinusoid with maximum amplitude to the output power for a small input for which SNR= 0 dB

Ideally, the dynamic range will correspond to the maximum SNR that can be obtained at the output of the CT  $\sum \Delta$  modulator

$$DR = 10\log_{10}\left[\frac{\left(\frac{A}{2}\right)^2}{2P_Q}\right]$$

(2.14)

Where:

A= Amplitude sinusoid input signal

PQ= Power noise quantification.

It can be shown that the dynamic range of a DAC of B-bit Nyquist can be calculated with the following formula:

$$DR = 10 \log_{10} \left[ 3 * 2^{(2B-1)} \right]$$

(2.15)

Relating the two previous formulas it can be defined the effective number of bits (ENOB) of the DAC as a function of DR as:

$$ENOB = \frac{DR(dB) - 1.76}{6.02}$$

(2.16)

## 3 INSTRUMENTATION FOR TESTING THE ASIC (SIGMA-DELTA ADC)

This chapter presents the circuits that make up the support instrumentation that will allow the realization of ASIC tests. The starting point for this project is the fully developed ASIC. Figure 3.1 shows the workflow followed to obtain the PCB (**objective 2**), which will allow to continue with the rest of the project objectives, until the objective 1, that is to characterize the ASIC, is achieved.

Figure 3.1 Flow chart PCB board development

The first step is to develop the PCB that will be used to test the ASIC. In this PCB the ASIC will be mounted together with all the circuits that are needed to supply the chip. For this is important to focus on different parts of the ASIC. These parts are the following:

- a. The power supply

- b. The Voltage references

- c. The current references

- d. Adaptation of the input signals.

- e. Digital connection with the software that we will use to measure the output of the ASIC.

In this section will be explained the selection and design of all the circuits mentioned above. These circuits are intended to provide power, reference voltages, clock signal, configuration to ASIC. Figure 3.2 describe the pinout of the ASIC. As it can be observed the ASIC have 44 pins. In Table 3.1 each pin is described.

Figure 3.2 Pinout Chip LARMOR

| Pin<br>Number | Signal type and name                              | Alias             | Value     | Unit | Pin<br>Value | Unit | Comments                                                                                                        |

|---------------|---------------------------------------------------|-------------------|-----------|------|--------------|------|-----------------------------------------------------------------------------------------------------------------|

| 1             | VDC Reference for FLASH (N)                       | VrefN             | 0.275     | ٧    |              |      | V reference for FLASH                                                                                           |

| 2             | VDC Reference for FLASH (P)                       | VrefP             | 1.525     | v    |              |      | V reference for FLASH                                                                                           |

| 3             | Ibias current 10 uA                               | IbiasDAC10        | 10        | μΑ   | 600          | mV   | Source current for DAC (1/5)                                                                                    |

| 4             | Ibias current 100 uA                              | IbiasGEN100       | 100       | μΑ   | 650          | mV   | Source current for OAMP(1/5)                                                                                    |

| 5             | Analog Power Supply                               | VDDA              | 1.8       | v    |              |      | Power supply for the filter (OA1:5)                                                                             |

| 6             | Ground                                            | VSSA              | 0         | v    |              |      | Ground                                                                                                          |

| 7             | Ground                                            | VSSA              | 0         | v    |              |      | Ground                                                                                                          |

| 8             | Analog Power Supply                               | VDDA              | 1.8       | v    |              |      | Power supply for the filter (OA1:5)                                                                             |

| 9             | V. Common mode                                    | Vcm               | 0.9       | v    |              |      | Voltage Common Mode for Resonator                                                                               |

| 10            | Vinput N                                          | VinN              | (min 0.2) | v    |              |      | Input differential signal                                                                                       |

| 11            | Vinput P                                          | VinP              | (max 1.6) | V    |              |      | (1.6 VPP differential at full scale)                                                                            |

| 12            | Ground                                            | VSSDAUX           | 0         | v    |              |      | Ground                                                                                                          |

| 13            | Auxiliary Power Supply                            | VDDDAUX           | 1.8       | v    |              |      | SPI and OA AUX (Probe)                                                                                          |

| 14            | Ibias current 100 uA                              | IBIASRX100        | 100       | μΑ   | 900          | mV   | For LVDS RX pads bias (CLK input) -                                                                             |

| 15            | Clock                                             | CLK input P       | 160       | MHz  |              |      | Input Differential Clock                                                                                        |

| 16            | Clock                                             | CLK input N       | 160       | MHz  |              |      | Input Differential Clock                                                                                        |

| 17            | Ibias current 500 uA                              | IBIASTX500        | 500       | μΑ   | 720          | mV   | For LVDS TX pads bias (5 output pads)                                                                           |

| 18            | Data_output LVDS_Clock_P                          | outCLKp<1>        |           |      |              |      | LVDS Clock                                                                                                      |

| 19            | Data_output LVDS_Clock_N                          | outCLKn<0>        |           |      |              |      | LVDS Clock                                                                                                      |

| 20            | Data_output LVDS_3_P                              | outP<3>           |           |      |              |      | LVDS Data                                                                                                       |

| 21            | Data_output LVDS_3_N                              | outN<3>           |           |      |              |      | LVDS Data                                                                                                       |

| 22            | Data_output LVDS_2_P                              | outP<2>           |           |      |              |      | LVDS Data                                                                                                       |

| 23            | Data_output LVDS_2_N                              | outN<2>           |           |      |              |      | LVDS Data                                                                                                       |

| 24            | Data_output LVDS_1_P                              | outP<1>           |           |      |              |      | LVDS Data                                                                                                       |

| 25            | Data_output LVDS_1_N                              | outN<1>           |           |      |              |      | LVDS Data                                                                                                       |

| 26            | Data_output LVDS_0_P                              | outP<0>           |           |      |              |      | LVDS Data                                                                                                       |

| 27            | Data_output LVDS_0_N                              | outN<0>           |           |      |              |      | LVDS Data                                                                                                       |

| 28            | Ground                                            | VSSDAUX           | 0         | V    |              |      | Ground                                                                                                          |

| 29            | Auxiliary Power Supply                            | VDDDAUX           | 1.8       | V    |              |      | SPI and OA AUX (Probe)                                                                                          |

| 30            | Ground                                            | VSSADAC           | 0         | V    |              |      | Ground                                                                                                          |

| 31            | IDAC Power Supply                                 | VDDADAC           | 1.8       | v    |              |      | DAC1-5 current cells only                                                                                       |

| 32            | Ground                                            | VSSD              | 0         | v    |              |      | Ground                                                                                                          |

| 33            | Power supply for FLASH                            | VDDD              | 1.8       | v    |              |      | Power supply for FLASH (37 mA), Clock<br>Delay, DAC1-5 Registers and Data output<br>(register + binary encoder) |

| 34            | Ground                                            | VSSD              | 0         | ٧    |              |      | Ground                                                                                                          |

| 35            | Power supply for FLASH                            | VDDD              | 1.8       | v    |              |      | Power supply for FLASH (37 mA), Clock<br>Delay, DAC1-5 Registers and Data output<br>(register + binary encoder) |

|               | Shift register Reset                              | REG - reset       | 0/1.8     | v    |              |      | Reset signal for the shift register                                                                             |

| 37            | Input data in the shift register                  | REG - data_in     | 0/1.8     | v    |              |      | Input data in the shift register                                                                                |

| 38            | Shift register clock                              | REG - shf clk     |           |      |              |      | Shift register clock                                                                                            |

| 39            | Load Enable                                       | REG - load enable | 0/1.8     | V    |              |      | Enable shift register                                                                                           |

| 40            | Clock                                             | REG - load clk    |           |      |              |      | Load CLOCK                                                                                                      |

|               | Set all programable bits to its<br>nominal value. | SETnom            | 0/1.8     | v    |              |      | Set all programable bits to its nominal value.                                                                  |

| 42            | Allows reset of digital blocks.                   | Dig_reset         | 0/1.8     | V    |              |      | Allows reset of digital blocks.                                                                                 |

| 43            | Test signal                                       | VprobeN           | (min 0.2) | V    |              |      | To test the individual integrators                                                                              |

| 44            | Test signal                                       | VprobeP           | (max 1.6) | V    |              |      | To test the individual integrators                                                                              |

Table 3.1 Interfaces all pins ASIC

For the validation of the circuits and subsequent creation of the PCB, the simulation programs Altium and Proteus have been used.

The PCB will be developed to operate with supply voltages of 3 V and 1.8 V, and with the possibility of further lowering these supply voltages to reduce

consumption. The tests performed on the system will eventually give the minimum supply voltage of the ASIC without loss of functionality.

### **3.1 POWER SUPPLY**

The input voltage of the PCB will be a 3V. VDA voltage, which have been changed to power the PCB with a lower voltage. At first it was thought to feed with 3 V., but finally it was decided to feed with a maximum voltage of 1.8 V to reduce consumption. As the whole system is differential it is necessary the intermediate voltage so that the whole system works correctly. The necessary ones are:

- Four 1.8V voltage sources to be connected directly to the ASIC, see Table 3.1.

- An additional 1.8 V source used to generate the reference voltages required by Flash.

- A source that will generate the common mode voltage Vcm 0.9 V needed by the ASIC integrators, Table 3.1.

- Three 0.9 V sources for adapting single ended input signals to differentials.

| Signal type and name   | Alias   | Value | Unit | Comments                                                                                                        |

|------------------------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------|

| V. Common mode         | Vcm     | 0.9   | V    | Common Mode Voltage for Resonator                                                                               |

| V. Common mode         | VCM     | 0.9   | V    | Common Mode Voltage for input signal                                                                            |

| Analog Power Supply    | VDDA    | 1.8   | V    | Analog Power Supply                                                                                             |

| PCBAUX                 | VDDA_CS | 1.8   | v    | To generate reference voltage for the<br>Flash                                                                  |

| Power supply for FLASH | VDDD    | 1.8   | v    | Power supply for FLASH (37 mA), Clock<br>Delay, DAC1-5 Registers and Data output<br>(register + binary encoder) |

| IDAC Power Supply      | VDDADAC | 1.8   | V    | DAC1-5 current cells only                                                                                       |

| Auxiliary Power Supply | VDDDAUX | 1.8   | V    | SPI and OA AUX (Probe)                                                                                          |

In the Table 3.2. it is possible to see in detail the different sources.

Table 3.2 Power supply on the PCB

### 3.1.1 POWER SUPPLY 1.8 V

After a thorough search among the component manufacturers, voltage regulators that met our requirements were Texas Instrument TPS79501DCQ [13]. The

TPS795 if from a family of low-dropout (LDO), ultralow noise, fast star-up, and excellent line and load transient responses in small outline, 6 pin SOT- 223. Each device in the family is stable with small 2.2- $\mu$ F ceramic capacitor on the output. Values equal to or greater than 10  $\mu$ F are recommended.

With this integrated, 1.8V voltage sources will be designed and simulated. Figure 3.3, shows the schematic designed.

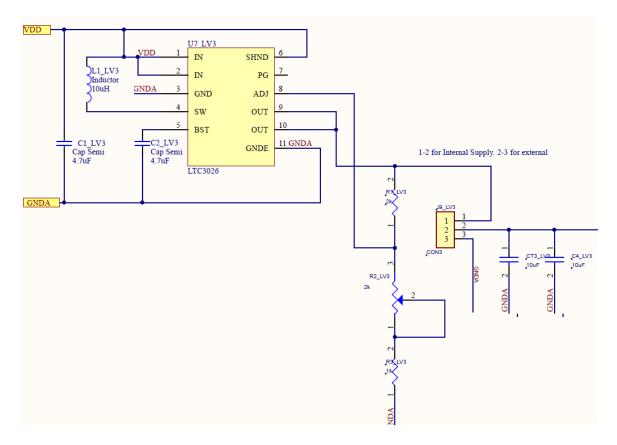

Figure 3.3 Power supply 1.8V

The output voltage of the TPS79501 adjustable regulator is programmed using external resistor divider ( $R_1 // R_2$ ) as shown in Figure 3.4.

Figure 3.4 Typical Application, Adjustable Output [13]

The output voltage is calculated using equation (3.1).

$$V_{OUT} = V_{REF} * \left(1 + \frac{R_1}{R_2}\right)$$

(3.1)

#### Where

V<sub>REF</sub>=1.2246 V. (internal reference voltage)

Resistors  $R_1$  and  $R_2$  should be chosen for approximately 40  $\mu$ A divider current. Lower value resistors can be used for improved noise performance, but the device wastes more power. Higher values should be avoided as increases the output voltage error.

The recommended design procedure when  $V_{OUT} = 1.8V$  is choose  $R_2 = 30.1 K\Omega$ .  $R_1$  and  $R_2$  is a set divider current of 40 µA, with C<sub>2</sub> =33 pF, and then calculate  $R_1$  using equation (3.2).

$$R_{1} = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) * R_{2}$$

(3.2)

In this case, one capacitor of 10  $\mu$ F has been used. The external supply VDD = 3V., will require that the source have V<sub>OUT</sub> = 1.8 V. For this purpose R2 = 30K, and for R1 it have chosen a fixed resistance of 10K and an adjustable of 2K, this way it is possible to sweep the range from 3V to less than 1.8 V.

Test points are designed to allow the configuration of the subcircuit, isolating it from the set.

### 3.1.2 POWER SUPPLY 0.9 V

To form the reference Vcm of 0.9 V the chip LTC3026 [14] of the company Linear Technology was used. This voltage is used to make differential input signals. Four circuits are used, each source feeds one part of the circuit independently of the rest. This allows isolating the signals and thus to be able to detect possible errors in a simpler way.

- INPUT\_VCM\_TRAFO: It is connected to the output at the midpoint of the transformer of the input signal coming from the MRI sensors.

- CLKN\_VCM\_TRAFO: It is connected to the output at the midpoint of the transformer of the input signal clock signal which is the sampling frequency.

- OUTPUT\_VCM\_TRAFO: It is connected to the output at the intermediate point of the test signal transformer, which allows each of the amplifiers of the individual resonators to be tested.

- Vcm: Is the reference voltage that the ASIC needs to generate the internal differential signals is connected to pin 9.

The design of the circuit is the same for the explained four sources see Figure 3.5. At the output of the the manufacturer circuit it is recommended to be stable a small 2.2- $\mu$ F ceramic capacitor on the output, values equal to or greater than 10  $\mu$ F are recommended.

Figure 3.5 Voltage reference 0.9V

The indications of the datasheet are followed as regards the discrete elements that stabilize the chip, and as regards the resistances that allow obtaining the desired value of 0.9 V. corresponding to  $R_1$ ,  $R_2$  y  $R_3$ .

The following values are set:

- R<sub>1</sub>= Fixed resistance of 2k

- R<sub>2</sub>= Adjustable resistance of 2k

• R<sub>3</sub>= Fixed resistance of 1K

The equation to be used as indicated by the manufacturer is the (3.3)

$$V_{OUT} = 0.4 * \left(1 + \frac{R_1}{(R_2 + R_3)}\right)$$

(3.3)

Test points are designed that allow the subcircuit to be configured, isolating it from the set.

### **3.1.3 VOLTAGE REFERENCE**

In order to obtain the Flash references voltages of the Flash a 1.8 V source (generated in the PCB at "PCBAUX") was used.

| Signal type and name        | Alias | Value | Unit | Comments              |

|-----------------------------|-------|-------|------|-----------------------|

| VDC Reference for FLASH (P) | VrefP | 1.525 | V    | V reference for FLASH |

| VDC Reference for FLASH (N) | VrefN | 0.275 | V    | V reference for FLASH |

### Table 3.3 Reference Voltage Flash

The input pins of the references in the ASIC are of high impedance, therefore it was opted to obtain these voltages using two voltage dividers. They are composed with a fixed resistance and another adjustable.

### **3.2 CURRENT SOURCE**

The ASIC has several pins that have to be connected with current sources, these pins offer a constant voltage that must be taken into account when designing the circuit. It is necessary to check the versatility of our chip therefore all the sources of intensity must operate with supply voltages from 3V to 1.8 V and even at lower voltage.

| Pin<br>Number | Signal type and name | Alias       | Value | Unit | Pin<br>Value | Unit | Comments                              |

|---------------|----------------------|-------------|-------|------|--------------|------|---------------------------------------|

| 3             | Ibias current 10 uA  | IbiasDAC10  | 10    | μΑ   | 600          | mV   | Source current for DAC (1/5)          |

| 4             | Ibias current 100 uA | IbiasGEN100 | 100   | μΑ   | 650          | mV   | Source current for OAMP(1/5)          |

| 14            | Ibias current 100 uA | IBIASRX100  | 100   | μΑ   | 900          | mV   | For LVDS RX pads bias (CLK input) -   |

| 17            | Ibias current 500 uA | IBIASTX500  | 500   | μΑ   | 720          | mV   | For LVDS TX pads bias (5 output pads) |

Table 3.4 Ibias

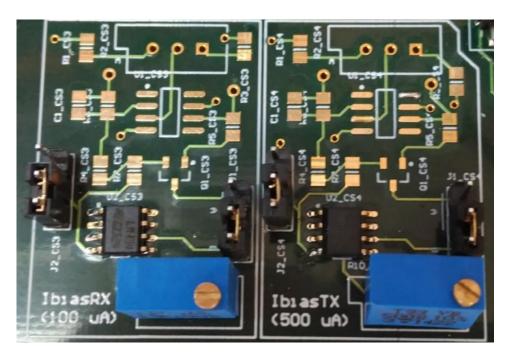

Four sources of intensity are needed. These will connect to the different inputs of the chip. In the design of these intensity sources has taken into account the voltage of the terminal that they are going to feed.

- 1. **Ibias current 100uA**: The terminal of the chip (Ibias100) has a constant voltage of 650 mV (trimmed internally).

- Ibias current 10uA: The chip terminal (Ibias 10) has a constant voltage of 600 mV (trimmed internally) is used in all five DACs.

- Ibias current 500uA: The chip terminal (IbiasTX500u) has a constant voltage of 720 mV. It is used in the transmission of "low voltage differential signal" (LVDS).

- 4. **Ibias current 100uA**: The terminal of the chip (IbiasRX100u) has a constant voltage of 900 mV. It is used in the transmission of "low voltage differential signal" (LVDS).

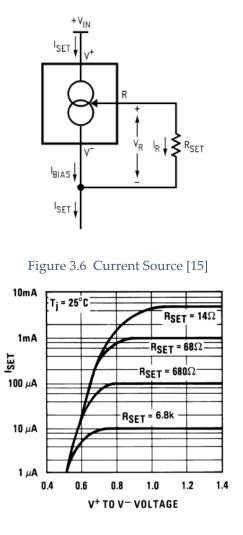

The datasheet of commercial chip manufacturers was searched for the design of current sources, the chip chosen was an **LM334DT-CI** [15], Terminal Adjustable Current Sources, SOIC-8 from STMICROELECTRONICS.

The features are:

- Operates from 1V to 40V

- 0.02%/V current regulation

- Programmable from 1 µA to 10 mA

- ±3% initial accuracy

According to the technical specifications, the area where the operating parameters are best in the LM334 is between 10  $\mu$ A and 1 mA, which is within the working ranges of the specifications of interest. The minimum working voltage in this range is 1 V.

The internal heating can have a significant effect on current regulation for a I<sub>set</sub> above 100  $\mu$ A (in our case, only one source). The output current (I<sub>set</sub>) has a temperature coefficient of about 0.33%/°C. Thermal effects should be taken into account when the regulation is critical and I<sub>set</sub> is higher than 100  $\mu$ A.

The sense voltage is less than 100 mV. at this level, the thermocouple effects and the connection resistance should be reduced by locating the current setting resistor close to the device. Do not use sockets for this Integrated Circuit (IC).

Figure 3.7 Turn on voltage [15]

Figure 3.7 shows the circuit to be used in all current sources. The R<sub>SET</sub> in all of them will be adjustable resistors.

The purpose of the calculation is to obtain the value of the resistance for the supply voltage to 3 V and 1.8 V and with this value choose the adjustable resistance that is to be implemented in the PCB.

The datasheet gives us the equation (3.4) for the calculation of the intensity for a given temperature and resistance. The values will be calculated for a temperature of 298°K.

$$I_{SET} = \frac{\left(\frac{227\mu V}{{}^{9}K}\right) * T}{R_{SET}}$$

(3.4)

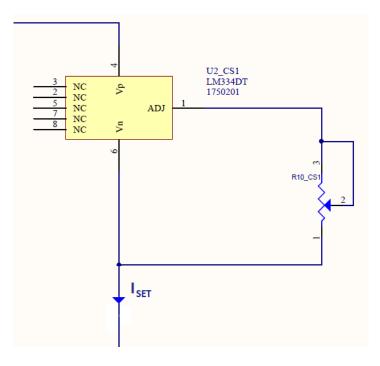

Figure 3.8 Schematic current source

Figure 3.9 Picture of Current Source

As it is possible to see in Figure 3.9 in the area of current sources, is possible to see tracks without elements and without connecting. This is because initially two types of sources were designed in case the main design failed, without having to develop a second PCB, the first design worked correctly.

### **3.3 ADAPTATION OF INPUT SIGNALS. RF TRANSFORMERS**

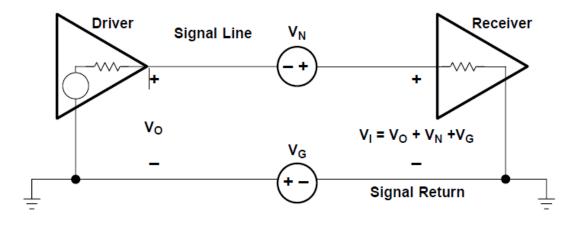

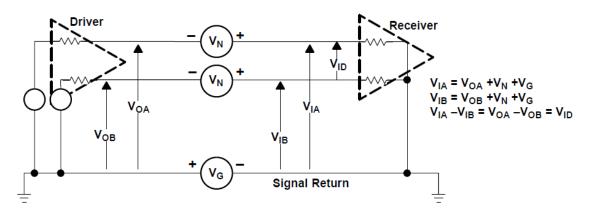

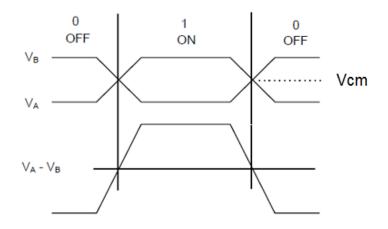

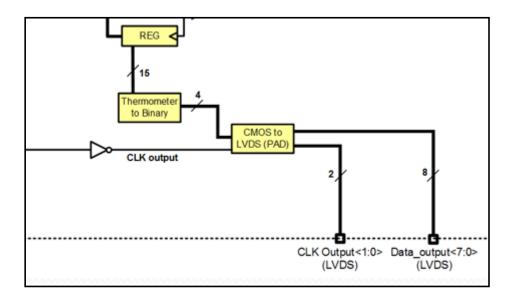

The ASIC is integrated into a signal receiving system within a magnetic resonance device. The signals to be processed will be those received from the sensors when operating in a real way. However, for testing purposes a pure input sinusoidal tone or tone signal is used.