#### **DOCTORAL THESIS**

# Contribution to time domain readout circuits design for multi-standard sensing system for low voltage supply and high-resolution applications

Author:

Javier Pérez Sanjurjo

Ph.D. advisor:

**Enrique Prefasi**

Ph.D. Program

**Electrical Engineering, Electronics and Automation**

## uc3m Universidad Carlos III de Madrid

(a entregar en la Oficina de Postgrado, una vez nombrado el Tribunal evaluador, para preparar el documento para la defensa de tesis)

#### TESIS DOCTORAL

Contribution to time domain readout circuits design for multi-standard sensing system for low voltage supply and high-resolution applications

|                       | PhD author: Javier Pérez Sanjurjo |

|-----------------------|-----------------------------------|

|                       | PhD advisor: Enrique Prefasi Sen  |

| Firma del Tribunal Ca | dificador:                        |

|                       |                                   |

|                       | Firma                             |

| Presidente:           |                                   |

| Vocal:                |                                   |

| Secretario:           |                                   |

| Calificación:         |                                   |

| Leganés,              | de de                             |

## Acknowledgment

All the work presented in this thesis come out as my research during several years. However, all the actions that I performed to achieve the results that I obtained couldn't be possible without all the help that I received during this time from several people that I will try to summarize here. In first place I would like to thank all my researching team for been there every time as back up for some questions or motivation for pending actions. In special the director of the thesis, Enrique Prefasi. During my time in Austria I also received a lot of help to create the prototype with all the actions that I never done before, in the electrical design I would like to thank Cesare Buffa, Christopher Rogi and Richard Gaggl for their support. During my time in the laboratory doing the measurements I had the support from really good people that have make things much easier for me, thanks to Bernhard Kuttin, Andreas and Alex.

All the motivation to continue with this work has been crucial for me. I have to say thanks to all the people that have push me in the right direction. Eric, Marta, Marcos, David, Maxi and Luis. You have been always there making me believe that I was able to finish it.

Estos años podrían haber sido una pesadilla si no fuera por todos los buenos momentos que he vivido con la gente que más quiero. Ellos han sido los que han sabido comprenderme en todos los momentos, especialmente en los más duros. Todos los amigos de la uní y de Villach, tíos y tías, primos y primas, Nacho, Alfonso, Ibai, Peto, Ana, Chals, Carlitos y Papá. Os agradezco todo lo que me habéis ayudado y aguantado.

Mamá, nada tendría sentido sin todo lo que tú me has dado.

## **Contents**

|           | ACKNOWLED    | GMENT                                                                      | 3   |

|-----------|--------------|----------------------------------------------------------------------------|-----|

|           | CONTENTS     |                                                                            | 5   |

|           | LIST OF FIGU | RES                                                                        | 9   |

|           | LIST OF TABL | ES                                                                         | 11  |

|           | LIST OF ABBE | EVIATIONS                                                                  | 13  |

|           | LIST OF PUBL | ICATIONS AND BIOGRAPHY                                                     | 15  |

|           | ABSTRACT     |                                                                            | XIX |

|           | RESUMEN      |                                                                            | 21  |

|           | CHAPTER 1.   | INTRODUCTION, MOTIVATION AND OBJECTIVES                                    | 1   |

|           | 1.1.         | Introduction                                                               | 1   |

|           | 1.2.         | Motivation of the thesis                                                   | 4   |

|           | 1.3.         | Objectives of the thesis                                                   | 5   |

|           | 1.4.         | Document outline                                                           | 6   |

| P.A       | ART I THEOF  | ETICAL INTRODUCTION TO CDC FOR IOT APPLICATIONS AND THEORY OF THE PROPOSED |     |

| ARCHITECT | TURE         |                                                                            | 9   |

|           | CHAPTER 2.   | Sensors and Converters                                                     | 11  |

|           | 2.1.         | Applications                                                               | 11  |

|           | 2.2.         | Sensors and front-end solutions                                            | 13  |

|           | 2.3.         | Capacitance-to-Digital Converter                                           | 14  |

|           | 2.4.         | State-of-the-Art of Converters                                             | 17  |

|           | 2.4.1        | Continuous Converters                                                      | 18  |

|           | 2.4.1.1.     | ΣΔ converters                                                              | 18  |

|           |              |                                                                            |     |

#### Contents

| 2.4.1.2     | 2. Integration converters                                   | 21 |

|-------------|-------------------------------------------------------------|----|

| 2.4         | 4.2. Discontinuous Converters                               | 23 |

| 2.4.2.      | Incremental Data Converters (IDCs)                          | 23 |

| 2.4.2.      | 2. Successive Approximation Register (SAR) Converters       | 25 |

| 2.4.2.      | 3. Voltage Controlled Oscillator (VCO) Converters           | 27 |

| 2.4         | 4.3. SoA Analysis                                           | 29 |

| 2.5.        | Conclusion                                                  | 32 |

| CHAPTER 3   | 3. CDC WITH A SELF-COMPENSATED DUAL SLOPE                   | 33 |

| 3.1.        | Front-end topology                                          | 34 |

| 3.1         | 1.1. Continuous time with AC-bridge and Voltage Amplifier   | 34 |

| 3.1         | 1.2. Continuous time Transimpedance Amplifier               | 35 |

| 3.1         | 1.3. Correlated Double Sampling Switched-capacitor topology | 37 |

| 3.1         | 1.4. Comparison between topologies                          | 38 |

| 3.2.        | Self-Compensated Dual Slope                                 | 39 |

| 3.2         | 2.1. Self-Compensated implementation                        | 43 |

| 3.3.        | Conclusion                                                  | 46 |

| PART II CDC | PROTOTYPE USING A SELF-COMPENSATED DUAL SLOPE CONVERTER     | 48 |

|             |                                                             |    |

| CHAPTER 4   |                                                             |    |

| 4.1.        | MEMS sensors                                                | 50 |

| 4.2.        | SYSTEM LEVEL                                                | 54 |

| 4.1.        | CIRCUIT LEVEL                                               | 59 |

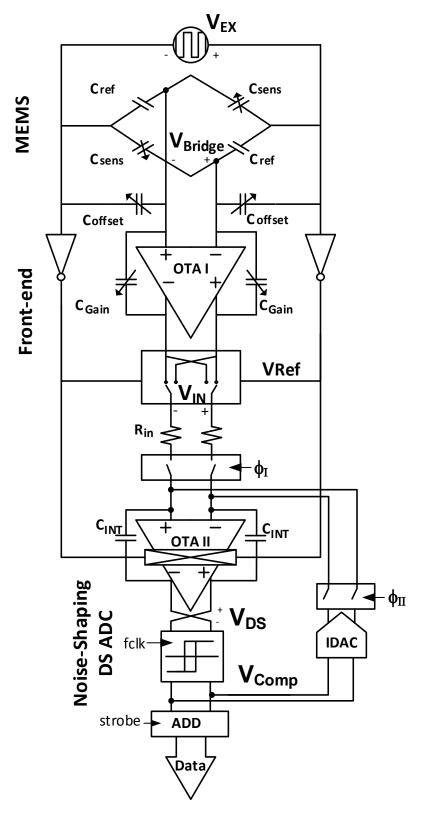

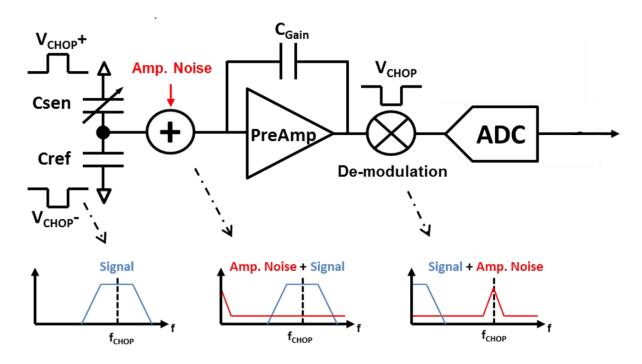

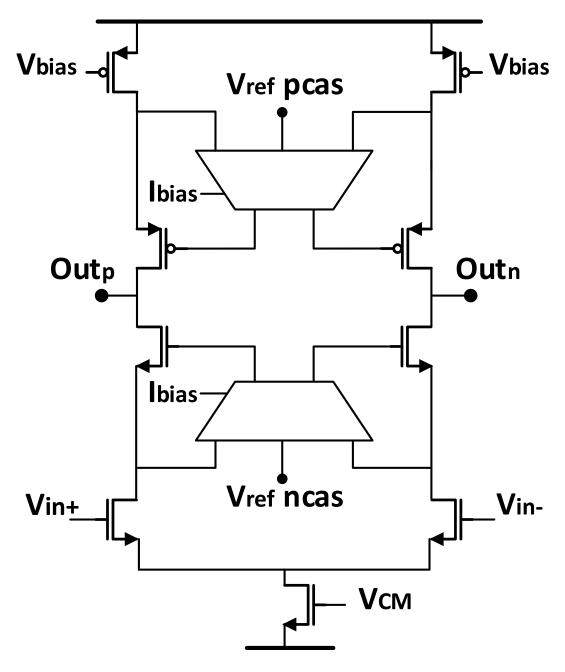

| 4.1         | 1.1. Analog front-end                                       | 59 |

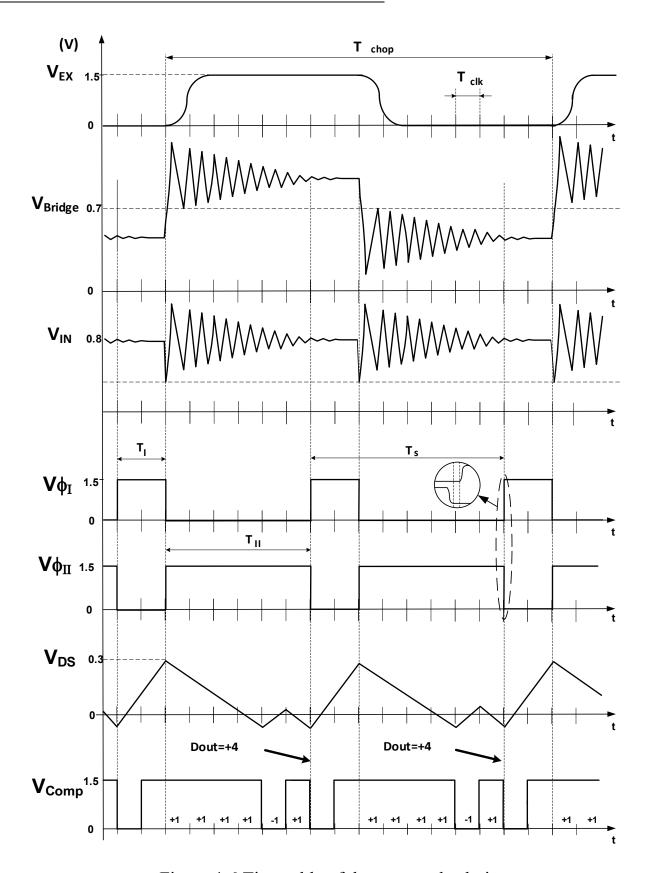

| 4.1         | 1.2. Self-Oscillating Noise-Shaping Dual-Slope              | 63 |

| 4.2.        | LAYOUT DESIGN                                               | 66 |

| 4.2         | 2.1. Distance                                               | 67 |

| 4.2         | 2.2. Size of transistors                                    | 67 |

| 4.2         | 2.3. Dummy transistors                                      | 69 |

| 4.2         | 2.4. Guard-rings                                            | 70 |

| 43          | Package & Bondina                                           | 71 |

| 4.4.          | Conclusion                                       | 72  |

|---------------|--------------------------------------------------|-----|

| PART III EXPE | RIMENTAL RESULTS & RELEVANCE OF THE PROPOSED CDC | 76  |

| CHAPTER 5.    | Experimental Measurements                        | 78  |

| 5.1.          | Setup configuration                              | 78  |

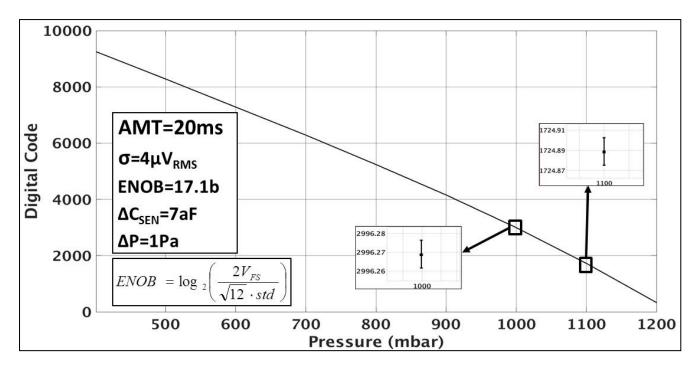

| 5.2.          | Resolution measurements                          | 81  |

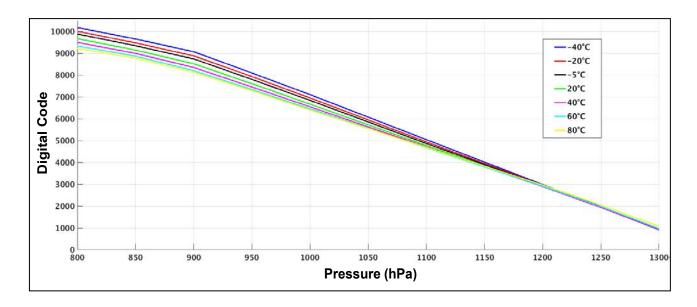

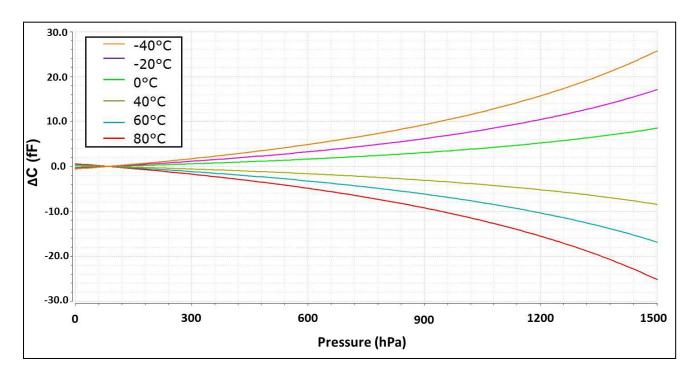

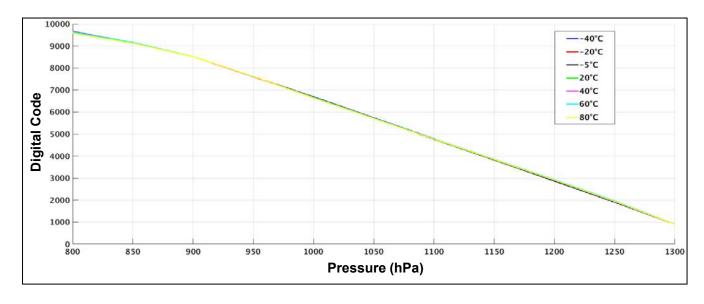

| 5.3.          | Temperature variation                            | 85  |

| 5.4.          | COMPARE WITH THE SOA                             | 87  |

| 5.5.          | Conclusion                                       | 91  |

| CHAPTER 6.    | Conclusions                                      | 92  |

| 6.1.          | Conclusions                                      | 92  |

| 6.2.          | Contributions                                    | 94  |

| 6.3.          | Future work                                      | 96  |

| Conclusion    | IES                                              | 98  |

| RIBLIOGRADI   | 1V                                               | 104 |

## **List of Figures**

| FIGURE 1-1 BLOCK DIAGRAM OF A CDC TOPOLOGY                                                                          | 2   |

|---------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 2-1 BLOCK DIAGRAM OF AN IDC CONVERTER                                                                        | 15  |

| FIGURE 2-2 RELATION BETWEEN SIGNAL AND NOISE RELATED WITH THE SAMPLE FREQUENCY                                      | 16  |

| FIGURE 2-3 COMPARISON OF CONVERSION PERIOD BETWEEN CONTINUOUS AND DISCONTINUOUS CONVERTERS                          | 16  |

| Figure 2-4 Block diagram and transfer function of a $\Sigma\Delta$ modulator                                        | 19  |

| Figure 2-5 FFT of a $\Sigma\Delta$ modulator with noise shaping                                                     | 20  |

| Figure 2-6 Block Diagram of Integration Converters                                                                  | 21  |

| FIGURE 2-7 TIME TABLE OF AN INTEGRATION CONVERTER (DS)                                                              | 22  |

| Figure 2-8 Block diagram of a ΣΔ IDC                                                                                | 24  |

| Figure 2-9 Block diagram of a SAR converter                                                                         | 26  |

| FIGURE 2-10 TIME TABLE OF A SAR CONVERSION WITH 4 BITS                                                              | 26  |

| FIGURE 2-11 BLOCK DIAGRAM OF A VCO CONVERTER                                                                        | 27  |

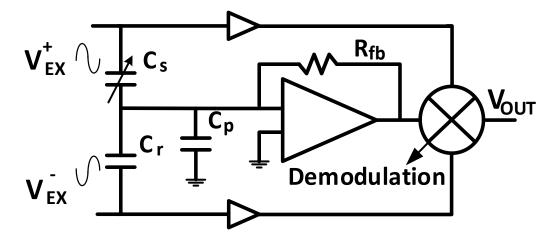

| Figure 3-1 AC-Bridge Schematic                                                                                      | 35  |

| FIGURE 3-2 TRANSIMPEDANCE AMPLIFIER CONFIGURATION SCHEMATIC                                                         | 36  |

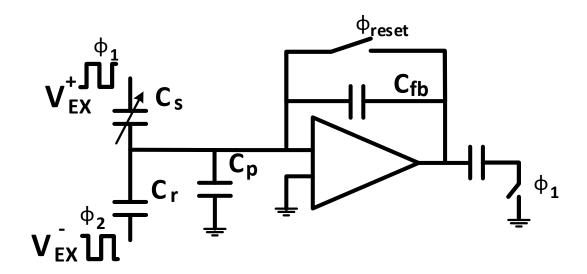

| FIGURE 3-3 CORRELATED DOUBLE SAMPLING SWITCHED-CAPACITOR SCHEMATIC                                                  | 37  |

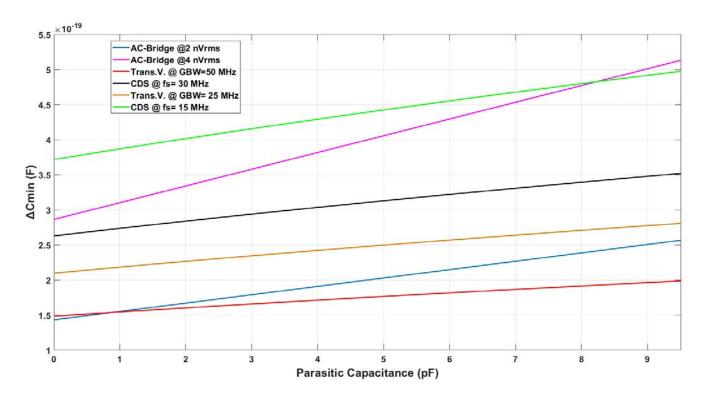

| FIGURE 3-4 COMPARISON OF RESOLUTION BETWEEN DIFFERENT FRONT-END TOPOLOGIES DEPENDING ON PARASITIC CAPACITANCE, VRMS | ;,  |

| GBWAMP AND FS.                                                                                                      | 39  |

| FIGURE 3-5 TIME DIAGRAM OF A INTEGRATING DS ADC                                                                     | 40  |

| Figure 3-6 Transfer function of an Integrating DS                                                                   | 42  |

| FIGURE 3-7 TIME DIAGRAM OF A SELF-COMPENSATED DS                                                                    | 45  |

| Figure 2. 9 To Avere Republication of A Self Connection DC                                                          | 4.0 |

#### List of Figures

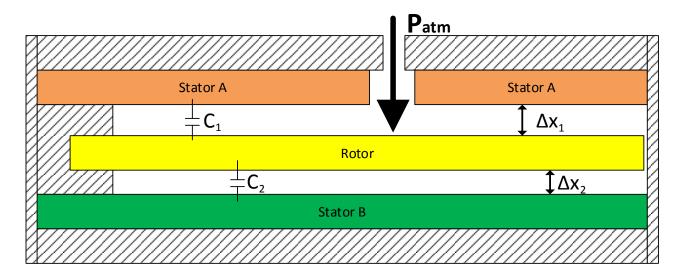

| FIGURE 4-1 SKETCH OF A TYPICAL DIFFERENTIAL CAPACITIVE SENSING CELL FOR A MEMS STRUCTURE. STATORS A AND B FORCING ACTING ON A |   |

|-------------------------------------------------------------------------------------------------------------------------------|---|

| SUSPENDED MASS                                                                                                                | 2 |

| FIGURE 4-2 DIAGRAM WITH FORCING ACTING ON A SUSPENDED MASS.                                                                   | 2 |

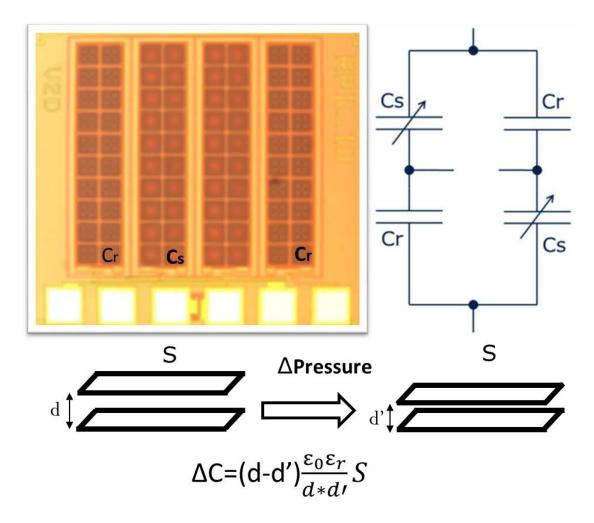

| FIGURE 4-3 PRESSURE SENSOR MEMS USED IN THE PROTOTYPE                                                                         | 5 |

| FIGURE 4-4 BLOCK DIAGRAM OF THE PROPOSED SOLUTION                                                                             | 7 |

| FIGURE 4-5 CHOPPING EFFECT IN FRONT-END CIRCUITS                                                                              | 8 |

| FIGURE 4-6 TIME TABLE OF THE PROPOSED SOLUTION                                                                                | 0 |

| FIGURE 4-7 SIMPLIFIED SCHEMATIC OF OTA I                                                                                      | 2 |

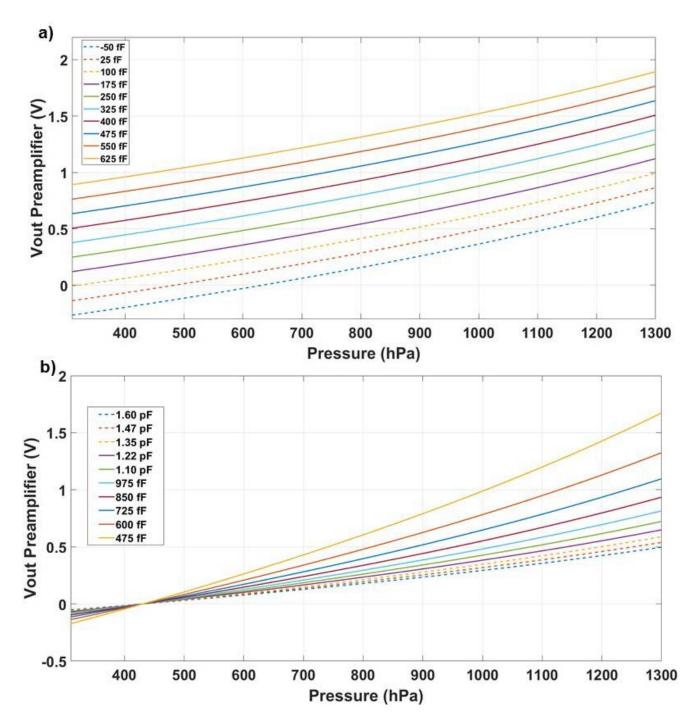

| FIGURE 4-8 PREAMPLIFIER OUTPUT VOLTAGE VS. PRESSURE FOR DIFFERENT TRIMMING OF COFFSET AND CGAIN                               | 3 |

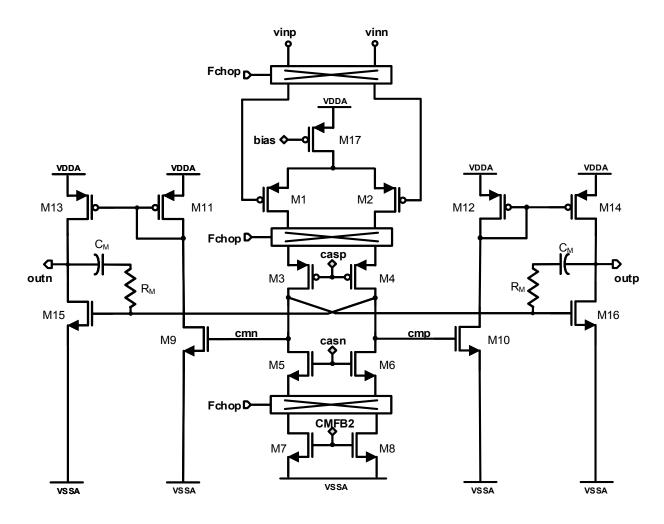

| FIGURE 4-9 SIMPLIFIED SCHEMATIC OF OTA II                                                                                     | 5 |

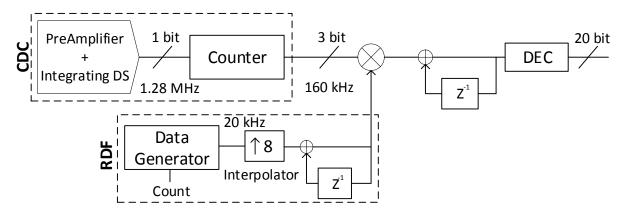

| FIGURE 4-10 BLOCK DIAGRAM OF DIGITAL PROCESSING PERFORM IN MATLAB                                                             | 6 |

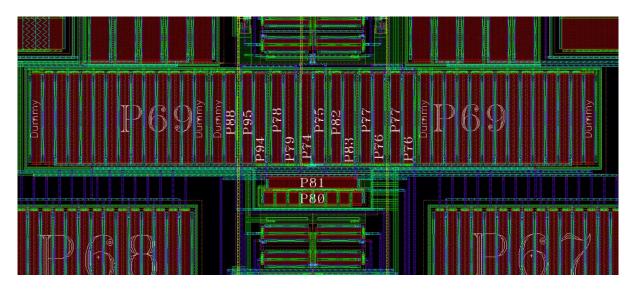

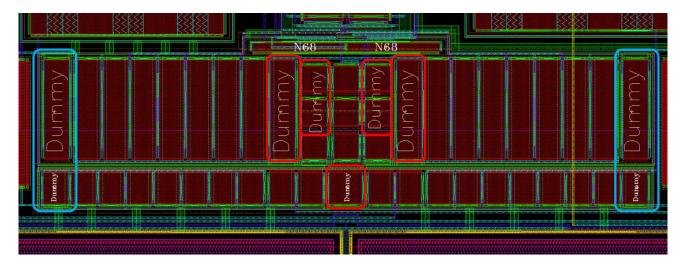

| FIGURE 4-11 LAYOUT VIEW OF PMOS TRANSISTORS OF THE FIRST STAGE IN OTA II.                                                     | 8 |

| FIGURE 4-12 LAYOUT VIEW WHERE DIFFERENT KIND OF DUMMY TRANSISTORS ARE USED                                                    | 0 |

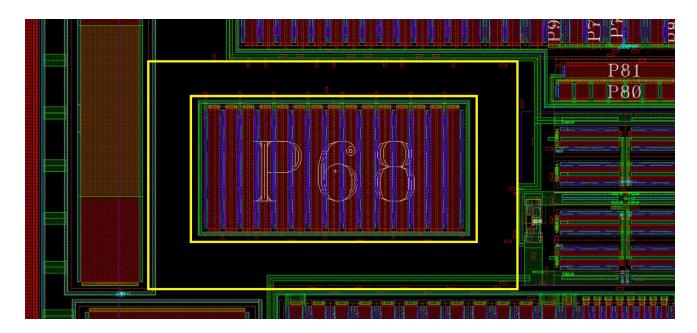

| FIGURE 4-13 LAYOUT VIEW OF A GUARD-RING SURROUNDING P68 AND ITS DEATH ZONE DUE DESIGN CONSTRAINS                              | 0 |

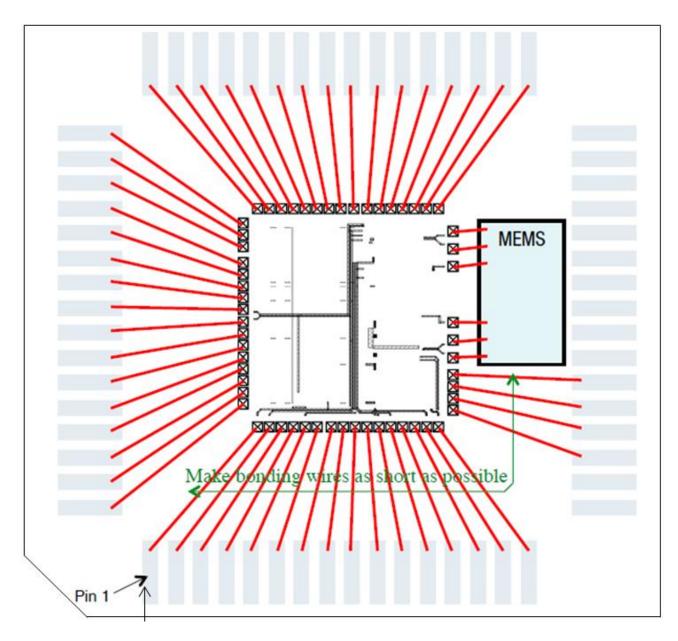

| FIGURE 4-14 BONDING SCHEME OF THE CDC IN CQFP64 PACKAGE                                                                       | 2 |

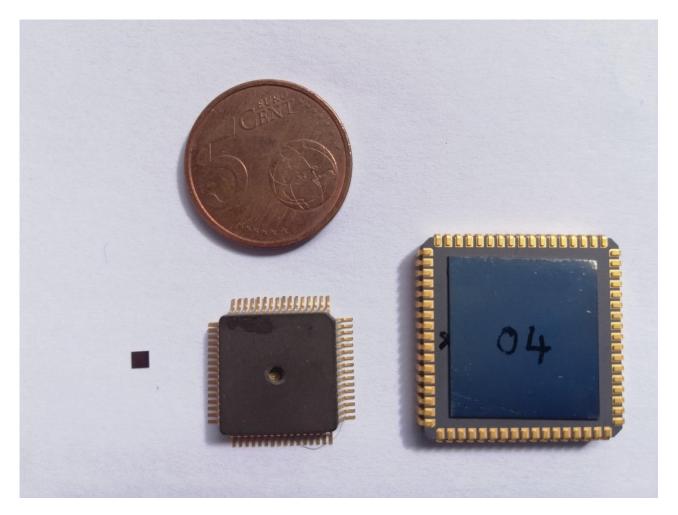

| FIGURE 4-15 COMPARISON OF SIZE BETWEEN SILICON AND DIFFERENT PACKAGE                                                          | 3 |

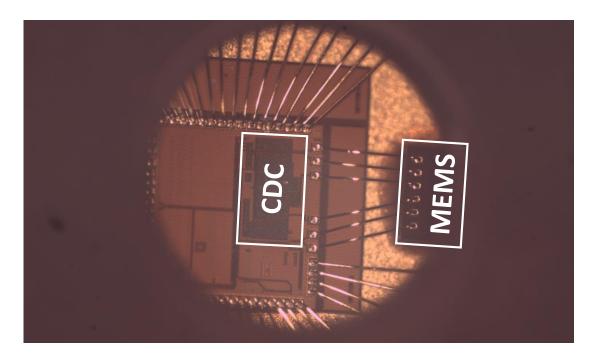

| FIGURE 5-1 DIE PHOTO OF THE MEMS SENSOR AND THE CDC BONDED TOGETHER IN A PACKAGE WITH A DRILL FOR PRESSURE CONTROL 7          | 9 |

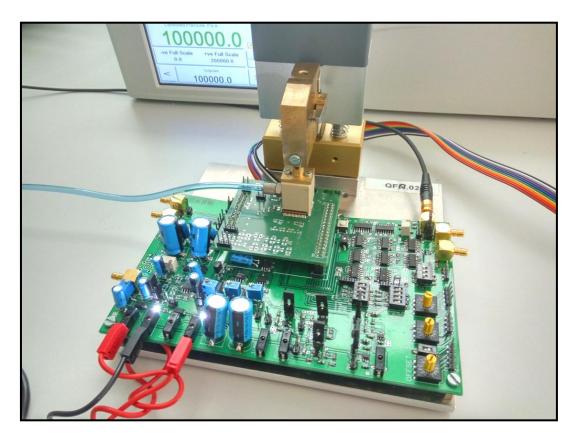

| FIGURE 5-2 TEST-CHIP WELDED AND WORKING CONNECTED TO THE TEST PCB AND PRESSURE CONTROLLER.                                    | 0 |

| FIGURE 5-3 HARDWARE USED TO MAKE ALL THE EXPERIMENTS OF THE TEST-CHIP                                                         | 0 |

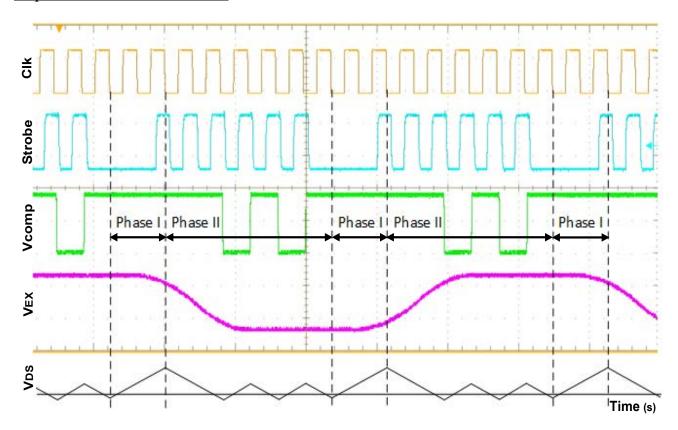

| FIGURE 5-4 TIME DIAGRAM OF THE SIGNALS THAT PROVES THE BEHAVIOR OF THE INTEGRATING DS MEASURED FROM THE TEST-CHIP             | 2 |

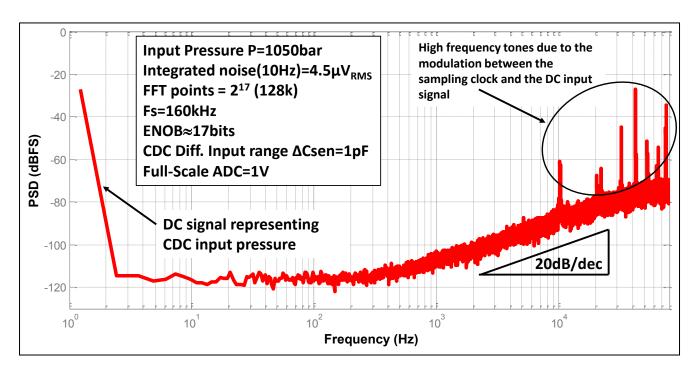

| FIGURE 5-5 FFT OF THE CDC FOR AN INPUT PRESSURE OF 1050MBAR                                                                   | 4 |

| FIGURE 5-6 DIGITAL OUTPUT CODE OF THE CDC VS INPUT PRESSURE IN DIFFERENTIAL MEASUREMENTS ANALYSIS                             | 4 |

| FIGURE 5-7 RAW DATA OUT OF THE TRANSFER FUNCTION MEASURED IN THE PROTOTYPE FOR DIFFERENT TEMPERATURES                         | 6 |

| FIGURE 5-8 ERROR OF RESOLUTION IN THE MEMS DEPENDING ON THE PRESSURE FOR EACH TEMPERATURE                                     | 7 |

| FIGURE 5-9 COMPENSATED TRANSFER FUNCTIONS AFTER TEMPERATURE, OFFSET AND GAIN ERROR FOR DIFFERENT TEMPERATURES                 | 7 |

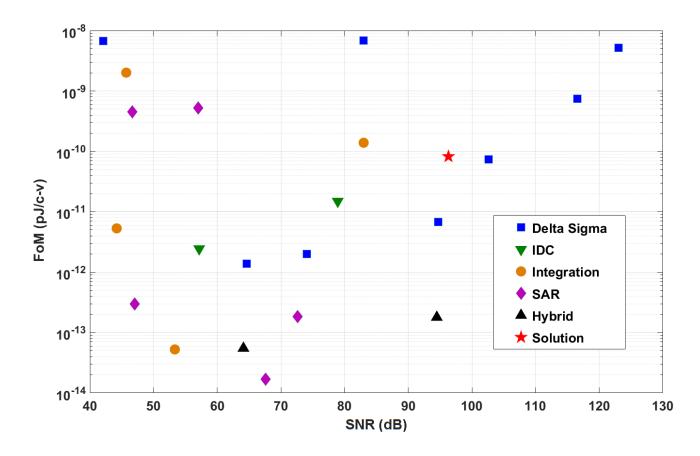

| FIGURE 5-10 STATE-OF-THE-ART PLOT. FIGURE OF MERIT (FOM) VS RESOLUTION                                                        | 0 |

## **List of Tables**

| Table 1 Comparative between Converters topology and their properties | . 30 |

|----------------------------------------------------------------------|------|

|                                                                      |      |

|                                                                      |      |

| Table 2 CDC state-of-the-art                                         | . 89 |

## List of Abbreviations

**ADC** analog-to-digital converter

**BW** bandwidth

**CCD** charge-coupled device

**CDC** capacitance-to-digital converter

**CDS** correlated double sampling

**CMOS** complementary metal-oxide-semiconductor

**DAC** digital-to-analog converter

**DS** dual slope

**EMC** electromagnetic compatibility

**ENOB** efficient number-of-bits

$f_{clk}$  clock frequency

**f**<sub>s</sub> sampling frequency

**FFT** fast Fourier transform

**IDC** incremental data converters

**IoT** internet-of-things

**LSB** least-significant bit

#### **List of Abbreviations**

MASH multistage noise-shaping

**MEMS** micro-electromechanical system

**NTF** noise transfer function

**OSR** oversampling ratio

**PVT** process-voltage-temperature

**SAR** successive approximation register

**SC** switched capacitors

**SNR** signal-to-noise ratio

**STF** signal transfer function

**VCO** voltage-controlled oscillator

V<sub>FS</sub> full-scale voltage

**ZCD** zero-crossing detector

## List of Publications and Biography

This thesis is based on work already published during the course of the doctoral research period, and therefore coincides partially with the following contributions:

- J. Pérez Sanjurjo, E. Prefasi, C. Buffa, and R. Gaggl, "A Capacitance-To-Digital Converter for MEMS Sensors for Smart Applications," Sensors, vol. 17, no. 6, p. 1312, Jun. 2017.

- Sanjurjo J.P., Prefasi E., Buffa C., Rogi C., Gaggl R. (2018) A High-Resolution Self-Oscillating Integrating Dual-Slope CDC for MEMS Sensors. In: Harpe P., Makinwa K., Baschirotto A. (eds) Hybrid ADCs, Smart Sensors for the IoT, and Sub-1V & Advanced Node Analog Circuit Design. Springer, Cham

#### **Papers in Journals**

• J. Pérez Sanjurjo, E. Prefasi, C. Buffa, and R. Gaggl, "A Capacitance-To-Digital Converter for MEMS Sensors for Smart Applications," Sensors, vol. 17, no. 6, p. 1312, Jun. 2017.

#### **Papers in Conference Proceedings**

• J. P. Sanjurjo, E. Prefasi, C. Buffa and R. Gaggl, "An energy-efficient 17-bit noise-shaping Dual-Slope Capacitance-to-Digital Converter for MEMS

- sensors," ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Lausanne, 2016.

- J. P. Sanjurjo and E. Prefasi, "A high-sensitivity reconfigurable integrating dual-slope CDC for MEMS capacitive sensors," 2015 11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Glasgow, 2015

- J. P. Sanjurjo, E. Prefasi and L. Hernandez, "A 1.2V low-power high-resolution noise-shaping ADC using multistage time encoding converters for biomedical applications," 2014 10th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Grenoble, 2014

#### **Chapters in Books**

Sanjurjo J.P., Prefasi E., Buffa C., Rogi C., Gaggl R. (2018) A High-Resolution Self-Oscillating Integrating Dual-Slope CDC for MEMS Sensors. In: Harpe P., Makinwa K., Baschirotto A. (eds) Hybrid ADCs, Smart Sensors for the IoT, and Sub-1V & Advanced Node Analog Circuit Design. Springer, Cham

#### **Patents**

Gaggl, Richard; Prefasi, Enrique; Perez Sanjurjo, Francisco Javier; Buffa,

Cesare, "Self-oscillating dual-slope integrating quantizer for sigma delta modulators"

#### Other publications of the author

J. P. Sanjurjo, E. Prefasi, L. Hernández, "Second-Order Noise-Shaping ADC using a Passive Integrating Quantizer for Biomedical Applications," DCIS Conference 2013: XXVIII edition of "Conference on Design of Circuits and Integrated Systems, Donosti, 2013.

#### **Biography**

Javier Pérez Sanjurjo was born in Madrid, Spain, in 1988. He obtained the B.S. degree in electrical engineering and the M.S. degree in Advanced Electronic Systems from Carlos III University of Madrid, Spain, in 2012 and 2014, respectively, where he is currently a student of the Ph.D. program in Electricity, Electronics and Automatic. He had worked for two years during his Ph.D. activity at Infineon Technologies in Villach, Austria. Nowadays, he is working as an analog designer for space applications in Video department at Airbus Defense & Space (ADS). His interest are readout circuits, sensors, environmental instrumentation systems and biomedical instrumentation systems.

## **Abstract**

This research activity has the purpose of open new possibilities in the design of capacitance-to-digital converters (CDCs) by developing a solution based on time domain conversion. This can be applied to applications related with the Internet-of-Things (IoT). These applications are present in any electronic devices where sensing is needed. To be able to reduce the area of the whole system with the required performance, micro-electromechanical systems (MEMS) sensors are used in these applications. We propose a new family of sensor readout electronics to be integrated with MEMS sensors.

Within the time domain converters, Dual Slope (DS) topology is very interesting to explore a new compromise between performances, area and power consumption. DS topology has been extensively used in instrumentation. The simplicity and robustness of the blocks inside classical DS converters it is the main advantage. However, they are not efficient for applications where higher bandwidth is required. To extend the bandwidth, DS converters have been introduced into  $\Delta\Sigma$  loops. This topology has been named as integrating converters. They increase the bandwidth compare to classical DS architecture but at the expense of higher complexity. In this work we propose the use of a new family of DS converters that keep the advantages of the classical architecture and introduce noise shaping. This way the bandwidth is increased without extra blocks. The Self-Compensated noise-shaped DS converter (the name given to the new topology) keeps the signal transfer function (STF) and the noise transfer function (NTF) of Integrating converters. However, we introduce a new arrangement in the core of the

#### **Abstract**

converter to do noise shaping without extra circuitry. This way the simplicity of the architecture is preserved.

We propose to use the Self-Compensated DS converter as a CDC for MEMS sensors. This work makes a study of the best possible integration of the two blocks to keep the signal integrity considering the electromechanical behavior of the sensor.

The purpose of this front-end is to be connected to any kind of capacitive MEMS sensor. However, to prove the concepts developed in this thesis the architecture has been connected to a pressure MEMS sensor.

An experimental prototype was implemented in 130-nm CMOS process using the architecture mentioned before. A peak SNR of 103.9 dB (equivalent to 1Pa) has been achieved within a time measurement of 20 ms. The final prototype has a power consumption of 220  $\mu$ W with an effective area of 0.317 mm<sup>2</sup>. The designed architecture shows good performance having competitive numbers against high resolution topologies in amplitude domain.

## Resumen

Esta actividad de investigación tiene el propósito de explorar nuevas posibilidades en el diseño de convertidores de capacitancia a digital (CDC) mediante el desarrollo de una solución basada en la conversión en el dominio del tiempo. Estos convertidores se pueden utilizar en aplicaciones relacionadas con el mercado del Internet-de-las-cosas (IoT). Hoy en día, estas aplicaciones están presentes en cualquier dispositivo electrónico donde se necesite sensar una magnitud. Para poder reducir el área de todo el sistema con el rendimiento requerido, se utilizan sensores de sistemas micro-electromecánicos (MEMS) en estas aplicaciones. Proponemos una nueva familia de electrónica de acondicionamiento para integrar con sensores MEMS.

Dentro de los convertidores de dominio de tiempo, la topología del doble-rampa (DS) es muy interesante para explorar un nuevo compromiso entre rendimiento, área y consumo de energía. La topología de DS se ha usado ampliamente en instrumentación. La simplicidad y la solidez de los bloques dentro de los convertidores DS clásicos es la principal ventaja. Sin embargo, no son eficientes para aplicaciones donde se requiere mayor ancho de banda. Para ampliar el ancho de banda, los convertidores DS se han introducido en bucles  $\Delta\Sigma$ . Esta topología ha sido nombrada como *Integrating converters*. Esta topología aumenta el ancho de banda en comparación con la arquitectura clásica de DS, pero a expensas de una mayor complejidad. En este trabajo, proponemos el uso de una nueva familia de convertidores DS que mantienen las ventajas de la arquitectura clásica e introducen la configuración del ruido. De esta forma, el ancho de banda aumenta sin bloques adicionales. El convertidor *Self-Compensated noise-shaped DS* (el nombre dado a la nueva topología) mantiene la función de

#### Resumen

transferencia de señal (STF) y la función de transferencia de ruido (NTF) de los *Integrating converters*. Sin embargo, presentamos una nueva topología en el núcleo del convertidor para conformar el ruido sin circuitos adicionales. De esta manera, se preserva la simplicidad de la arquitectura.

Proponemos utilizar el *Self-Compensated noise-shaped DS* como un CDC para sensores MEMS. Este trabajo hace un estudio de la mejor integración posible de los dos bloques para mantener la integridad de la señal considerando el comportamiento electromecánico del sensor.

El propósito de este circuito de acondicionamiento es conectarse a cualquier tipo de sensor MEMS capacitivo. Sin embargo, para demostrar los conceptos desarrollados en esta tesis, la arquitectura se ha conectado a un sensor MEMS de presión.

Se ha implementado dos prototipos experimentales en un proceso CMOS de 130-nm utilizando la arquitectura mencionada anteriormente. Se ha logrado una relación señal-ruido máxima de 103.9 dB (equivalente a 1 Pa) con un tiempo de medida de 20 ms. El prototipo final tiene un consumo de energía de 220 µW con un área efectiva de 0.317 mm2. La arquitectura diseñada muestra un buen rendimiento comparable con las arquitecturas en el dominio de la amplitud que muestran resoluciones equivalentes.

## Chapter 1.

## Introduction, motivation and objectives

#### 1.1. Introduction

Sensing a physical property has been one of the main field of investigation since a long time, sensing temperature or pressure have been possible since XVIII century. However, the world has change a lot since then, different kinds of sensors and connections between them have been developed. In fact, precision, size and connectivity have been the main goals of improvement. Nowadays, a new family of sensors have been used and tested all over the world. They are called Smart Sensors [1]. It is because they are able to calibrate, compensate and transmit data with microprocessor circuits, opening the possibilities of use the sensing data. The evolution of this kind devices has helped in the growing of a new market called, Internet-of-Things (IoT) [2] [3] [4]. In the market of IoT, all the devices are connected through the network, sharing all the information. In the past decade, the applications related with the Internet-of-Things (IoT) have grown exponentially. In this field, smart sensors for environmental measurements (humidity, pressure, temperature and gas) are one of the most demanded

#### Introduction, motivation and objectives

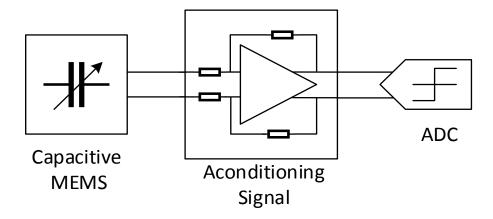

products. All the previous examples have in common the bandwidth that they share. Most of the variables to measure in IoT are in the low frequency domain. If the conversion is done with a high frequency converter, they can even be measured as DC (BW < 50 Hz). The main consequence is that most of the sensing activity will have similar readout outputs. This implies a big effort in developing new kinds of interfaces that are able to work with different type of sensors [5] [6] [7] [8]. To try to make as similar as possible the circuitry for different kind of sensors with a low-cost and energy efficient solution, Micro-Electro-Mechanical Systems (MEMS) sensors have arrived as the next generation of sensors for this purpose [9] [10] [11]. MEMS have the property of being very small in size keeping high performance. Also, they have a low cost per unit thanks to their process of manufacturing. For these reasons, MEMS are mainly used in IoT applications. Similar to a microelectronics component, MEMS are able to be produced in big. To try to make the output behavior similar between different sensing activities, capacitive MEMS are mostly used in IoT. This is one of the reasons why Capacitive-to-Digital Converters (CDC) are selected as one of the main readout topologies to be used in new sensors applications [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26]. They are able to digitize the signal of the MEMS with low power and high resolution which is the main interest in the market. A CDC is composed by an acconditioning signal circuit plus an analog-to-digital converter (ADC). Figure 1-1 shows the main blocks of interest:

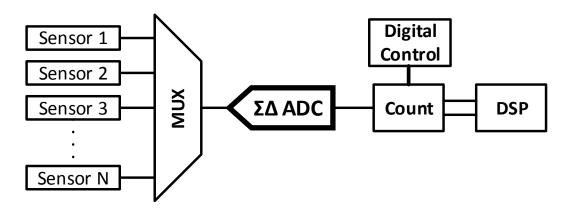

Figure 1-1 Block diagram of a CDC topology

In the open literature, different architectures have been tested as a possible solution for high-resolution CDCs. The typical approach is the use of charge transfer between capacitors to convert the sampled capacitance to voltage. Then this is used as an input for high order multi-bit switch-capacitor (SC) Sigma-Delta ( $\Delta\Sigma$ ) ADCs [16] [20] [25] [27] [28] [29] [30]. Its high resolution and linearity together with its intrinsic tolerance to analog non-ideal behavior make this option very popular for these applications. However, to reach the target resolution, large area and power demanding blocks are needed. In addition, when low voltage supplies are used, the performance of SC  $\Delta\Sigma$  converters is reduced. Other types of solutions have been also proposed: successive approximation register (SAR) converters are good for scaling the CDC [31] [32] [33], IDCs are simple and can reduce the power consumption [34] [35]. Alternative solutions also show different approaches (like period modulation [36], delay-chain discharge [24], voltage-controlled oscillator (VCO) [37] [38] [39], and DS [19]) to reduce area and power consumption even further. Hybrid converters (like SAR + Incremental) takes the properties of the previous topologies [12] [17] [40] [41].

To save power and area keeping the same performance of high resolution CDCs, this thesis explains the development of a topology that is able to detect small capacitance changes while reducing ADC complexity, which is, typically, a critical block area and power wise in the CDC. To be area and energy efficient the proposed ADC is based on the single-bit noise-Shaping Integrating DS converter [42] [43] [44] that maps the amplitude information into the time domain. Compared to traditional Dual-Slope ADCs [45], it introduces quantization error noise-shaping as in standard  $\Delta\Sigma$  ADCs. But it does not require multi-bit circuits (i.e.: flash quantizers or n-bit digital-to-analog converters (DACs)) to keep high resolution and performance; instead, it uses single-bit circuitry to exchange amplitude by time resolution allowing to use lower supplies voltages. In addition, this topology has an intrinsically small sensitivity to temperature and process variations. These properties were already shown in [42] [43] [44] [46].

#### Introduction, motivation and objectives

#### **1.2.** Motivation of the thesis

The main motivation of this work is to contribute to the research and development of CDC architectures compatible with MEMS sensors to improve the quality and possibilities of the applications that surround the market of IoT.

Devices are becoming smaller and smaller, introducing two main issues, area and power consumption. To keep the performance in designs with a power supply below 1.8 V, new architectures need to be developed that can cope with the resolution given by classic architectures [47].

Time resolution topology is selected as a good candidate to deal with the main constrains mentioned before. In this way, high resolution, low area and power consumption is achievable by architectures that works with single bit circuitry, and therefore doesn't suffer from low voltage supply.

A high number of applications need a lot of different kind of sensors. Develop a single CDC for every of them does not seem an intelligent solution. Specially taking into account that most of the sensors used for this application share the same technology, they are MEMS sensors. A topology that is able to adapt from one application to another with the most possible efficiency seems to be an interesting solution.

Find a solution that can keep the same performances of  $\Delta\Sigma$  converters but reducing the area and power consumption to adapt the CDC to new low power applications seems to be not efficient. To be able to deal with the characteristics of two different kind of converters, and hybrid solution that combine time resolution with noise shaping behavior from  $\Delta\Sigma$  converters seem to be the perfect solution.

Create a standard package with the properties commented in the previous point can reduce the price and the time to market of many applications, making them useful and efficient.

#### 1.3. Objectives of the thesis

To achieve all the goals that were commented in the motivation of this thesis the following objectives are defined.

- Study the electronic circuitry that has to be attached with the MEMS to create a proper readout topology. As said before, most of the MEMS used in these applications are capacitive MEMS, and therefore they have a measurable output in the capacitance domain. Because of that CDC seems to be the best candidate in readout circuits. In addition, the kind of variables that are going to be measured (gas, humidity, temperature or pressure), need a readout circuit that deals with low frequency source of noise must be selected.

- Taking into account the two outputs of the previous point (capacitance output and low frequency domain), it is not straight clear how to measure the output of the sensor. A study at system level is needed. To connect the sensor with the electronic of the CDC an AC modulation is needed. This modulation will make possible to take the info out of the capacitive sensor and give the data in the low frequency domain.

- Find a topology to use with AC modulation. How to optimize the whole design to make it robust and efficient. The different blocks of the CDC need to be design for the requirements that comes out of the previous study at system level. Making an acconditioning electronic block that is able to give a stable and precise analog signal and an ADC that can be connected with that.

- Develop the topology selected. Create a prototype that has connected the MEMS to the readout electronic, creating the whole CDC for measurement. Perform the research and activities needed to create a silicon solution that can be tested to compare with the State-of-the-Art (SoA) solutions. To achieve this goal, intermediate objectives need to be defined:

#### Introduction, motivation and objectives

- Create a synchronous architecture that deals with the resolution and noise to give expected performances

- Design at circuit level the main components that are going to be needed to have a CDC with all the specifications defined at system level.

- Implement a layout design that deals with non-ideal behavior and EMC.

- Build a setup to make the characterization of the prototype in silicon to compare with the SoA.

- Make the comparation with the SoA. Make a fair study and discussion between the main solutions performed with the different architectures mentioned before. See if the solution performed is useful and if it opens a new field for further investigation, and therefore, what would be the future investigation to keep going with the improvements for the applications.

#### 1.4. Document outline

We have split the work in three different parts. The first one intrudes all the theory of the previous works and the architecture proposed. The second part explain the building process of a prototype using the architecture proposed in the first. It includes the system, circuit, layout and packing considerations that have been considered for proper performances of the prototype. The third part presents the results obtained out of the measurements and compares the architecture with the other architectures used in similar applications and present the conclusions out of the work and a proposition of future activities.

#### Part I

**Chapter 2** present and introduction to the topic. It includes a brief introduction to the market of IoT and smart sensors. The basic knowledge of a capacitance-to-digital-converter (CDC) is presented. To conclude a presentation of the State-of-the-Art of the main topologies of converters used in these kinds of applications is presented with a comparative between them in order to select the topology that we think that fits better for our purpose.

In **Chapter 3** the selected architecture is explained. It includes a selection for the frontend circuitry considering the constrains of the application and the desire performances. It also includes the theoretical explanation of the architecture proposed inf this work. The evolution from the classic DS to the architecture developed during this process is presented with empirical demonstration of the new features and its implication in the transfer function.

#### Part II

The whole CDC architecture is presented in **Chapter 4**. An explanation of MEMS behavior is included, with special mention the one used for this prototype. The architecture of the CDC is presented at system level with an explanation of every phase of the whole conversion. The design at circuit level is also included with the main parameters selected to minimize the non-ideal effects and optimize the performances. Also, this chapter presents the details that have been taken into account for the layout and packing of the prototype.

#### Part III

The measurements of the prototypes are presented in **Chapter 5**. It includes an explanation of the setup used during the measurements. The measurements included are the ones that characterize the resolution of the prototype in the whole range. Also, the behavior of the prototype against Temperature is presented.

#### Introduction, motivation and objectives

In **Chapter 6** a comparison with the State-of-the-Art is presented. The conclusions achieved during the whole research are commented respect to the objectives already presented. The future work that would have to be done to continue con this research is also mentioned.

## Part I

Theoretical introduction to CDC for IoT applications and theory of the proposed architecture

# Chapter 2.

# **Sensors and Converters**

The purpose of this chapter is to give an introduction to the topic. Give a short introduction the environment, the market of IoT and how the sensors have evolved with that. Also, it will introduce the basic knowledge of a Capacitance to Digital Converter (CDC) and an overview of the state-of-the-art of readout circuits for smart sensors.

# 2.1. Applications

In the last years, the evolution of technology has changed our world completely. With the introduction of Internet of Thing and smart devices (IoT) a brand-new world for new applications have arrived. Nowadays there are many fields were new devices are required to satisfy new demands. For example, our homes are becoming more intelligent, they can give us information about the temperature outside, probability of rain, the status of the food inside the fridge, or the quality of the air in a certain room. However, this is not enough. With the idea of having all the information possible anytime, the market is evolving in the direction of solutions that are wearable. A watch, a pair of glasses, a smartphone, etc. All these examples have one thing in common, the small size. To be able to have a device that is providing all this information without affecting its size, new solutions need to be developed. The business under these

applications is growing exponentially, the main areas where is already taking a piece of the market are: IoT and Environmental Intelligence.

The concept of (IoT) comes out of the wireless interconnexion of items that surround us. Machines talking to each other and persons talking to machines. Within the last years sensors and networks (autonomous sensing systems) have gained new possibilities of control classical procedures in the human activity where it was not possible before due the spread of wireless networks and power consumption of the electronics. This is due the evolution of integrated circuits. The improvement in energy efficiency, performance and power consumption in the devices help to build an infrastructure much easier than before. There are many environmental parameters that need to be measured and controlled in different fields: home, automotive, energy management, industry, etc. [48]. An important new field needs to be mentioned, the quality in food and drinks. Avoid any possible contamination due a bad state of the food or detect products that have a carcinogenic effect is an important improvement hat will improve the quality of our health in the close future. The company Gartner says that 8.4 billion connected things will be used in 2017, a 31 % increase with the previous year. Also, it expected that by 2025 IoT nodes will connect most of the items in our day to day life [49]. To this goal will be achieved thanks to the development in smart sensors, nanotechnology and miniaturization of sensors. A common use of sensors is to use them to gather environmental information from different mediums. The importance of monitoring of the environmental can be reduced to two main topics, fresh water and fresh air, which are the main responsible of our health. There is the need of build sensors able to detect anything that mixes with the water and change it properties: organic matters, inorganic matters, radioactive waste. In special, plastic is considered major ocean pollutants, which causes severe harm in water properties. The same needs come from detecting the different toxic gases that contribute to air, like sulphur dioxide (SO2), or ozone (O3). The wide varieties of the sensors for the environment monitoring are needed, namely, temperature, humidity, light intensity, wind speed, pressure, salinity, oxygen, toxic gases, and many more.

IoT puts together all this information with the inter-connection of sensors machines and persons to share the information in the whole world. Its main purpose is to access different items of our daily life and controlled them as good as possible. However, connect people through internet implies a big cost in infrastructure, in special in remote areas. The introduction of Low-cost smart sensors nodes is easy in the applications and reduce this issue.

#### 2.2. Sensors and front-end solutions

As it was explained before, smart sensors are changing the intelligent systems. They provide new features that previously could not be performed by the common sensors, regarding economic or technical topics. Typical undesired characteristics of sensors like input offset, linearity, temperature effect can be automatically corrected by the digital part included in smart sensors. This feature helps to solve different technical and economic problems. As these operations are carried in software, no additional hardware is required. Therefore, it is possible to calibrate with digital control and there is no need to remove the sensor from its current environment or test fixture. For this reason, smart sensors are known for their standardized physical connection to enable the communication with the digital processor and therefore with the network. Also, smart sensors can perform different functions like sensing, self-calibration or ranging. These sensors can detect different parameters and change the programmability of the electronics in order to give precise data for different inputs.

Smart sensors open a new world of applications thanks to their properties. However, to go further in the integration of the sensor with the circuit there are physical constrains that are not possible to break. That is why a new generation of sensors have grown related with this market in the last years, the silicon-based sensors. Build sensors

in the same way of their Integrated Circuits front-ends helps to reduce the size, power consumption and price of the device. For example, complementary metal-oxide-semiconductor (CMOS) technology can be used. The CMOS charge-coupled device (CCD) [50] used in cameras are a good example of a mature sensor made in CMOS technology and it shows the possibility of integration and a high level of performance. However, there is a new kind of sensor that is becoming the more used of the integrated sensors. Its advantages of integration with the electronics plus the good performance are making MEMS (Micro-Electro-Mechanical Systems) sensors the new trend in front-end solutions.

## 2.3. Capacitance-to-Digital Converter

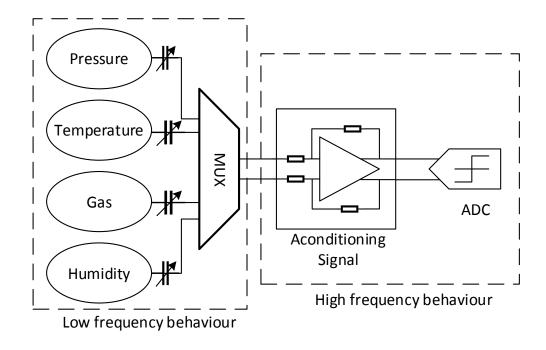

Capacitance-to-Digital Converter (CDC) [51] is the most used electrical circuitry with capacitance sensors. Any kind of sensor that has an output in the capacitance domain is a candidate to be used with this topology. However, the trend to create circuitry that is able to be connected with different interfaces (as can be seen in Figure 2-1) is the main reason of the upcoming interest in CDC topologies, specially inside the market of IoT. This is possible thanks to some constrains in the applications that were mentioned before. All the variables that are going to be measured of different applications have something in common. The bandwidth of all these signals is close to DC (BW < 50 Hz). It helps to target the bandwidth of interest to this value inside the CDC parameters of conversion and therefore to be able to measure all the different sources. To be able to work in an efficient way with multiple sensors, the CDC need to make some adjustments for every signal. To achieve this porpoise a configurable acconditioning step is included. Once the CDC is able to target different source of information, it needs to adapt the resolution specified for each application. This is one of the main advantages of use a CDC architecture with low BW input signals. Each sensing magnitude needs different level of precision in each application. Because of that the resolution in the CDC is given thanks to two different properties. The first one and

more obvious is the resolution of the ADC. The ADC is design to give certain resolution in a specific sample time.

Figure 2-1 Block diagram of an IDC converter

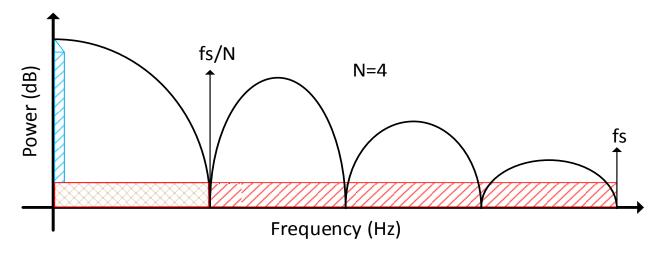

However, the resolution can be extended in these applications increasing the measuring time. Considering that the signals to convert have a frequency below 50 Hz, the CDC can be connected to one input signal and acquire a lot of samples for decimation that will increase the precision to the DC value. As it is explained in Figure 2-2, when more samples are taken for one input signal, the BW where the noise is integrated is smaller and therefore the Signal to Noise Ratio (SNR) increases.

Taking this property into account, a CDC for low bandwidth sensors signals scale the minimum resolution required with the resolution of the ADC and the signals that required more resolution use decimation technic. The resolution that is possible to increase depends on the time constrains of the system and the initial resolution of the ADC. The time constrains can be due the total physical time per conversion of all the

Figure 2-2 Relation between Signal and noise related with the sample frequency

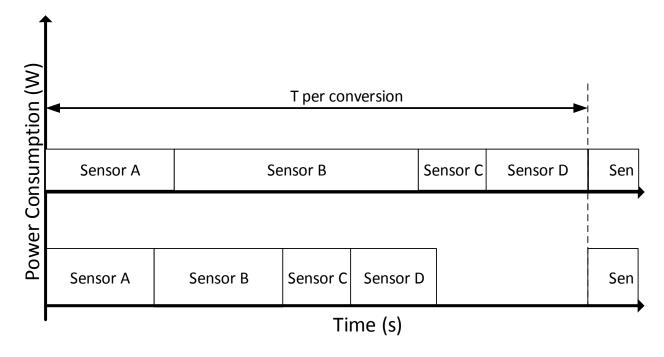

inputs (normally the data need to be updated every 0.1-1 second) or the ADC topology. Depends on the ADC, the N factor of Figure 2-2 can be only an integer (for Nyquist ADC) or taking into account the oversampling-ratio (OSR) ADCs can be split in smaller resolution requirements. However, to save power, some solutions use discontinuous measurement. The CDC is only switched on for each measurement and extra time the

Figure 2-3 Comparison of conversion period between continuous and discontinuous converters

deltas (N/OSR). There are two different methods to make the measurement to use the flexible measuring time. Both are represented in Figure 2-3. The first one is continuous measurement. The CDC is always on and the ADC is converting the whole time, therefore the total time for conversion is split between all the inputs considering their

CDC goes into sleep mode to save power. Systems that use this method normally uses ADCs that give higher resolution in order to avoid extra time in the conversion.

In the State-of-the-Art there are many different possibilities that uses one of the previous methods of measurement. In the next section the main families of converters are presented.

#### 2.4. State-of-the-Art of Converters

As mentioned in the previous section, there are a lot of different topologies of converters used in this type of applications. The amount of converter types is just a consequence of all the types of applications that demands different performances or with different level of relevance. The main constrains for IoT applications are: resolution, power consumption, area, flexibility, voltage power supply, complexity and robustness. Finding a solution that satisfy all of them with a high acceptance level is still out of the limits of the solutions developed. Nowadays, depending on the priority of each constrains, the designers choose a different topology to optimize their design. In this section the main topologies used are presented.

All the topologies can be organized inside two different groups. The ones that do the conversion continuously and the ones that do it discontinuous. It is important to mention that nowadays there is not a prove or understanding that one group or the other is better or worst. Each topology fit better in one of the groups due its architecture constrains.

#### 2.4.1. Continuous Converters

The main idea of continuous converters is that the converter is working all the time. It is not dependant on any system level constrains to start to perform the conversion or to stop to do it. It just needs a sampling time to take the sample from the input. The output data is always available for post-processing giving more flexibility in the measuring time. Inside continuous converters there mainly to different architectures that are used.  $\Sigma\Delta$  converters and Integration converters.

#### 2.4.1.1. $\Sigma\Delta$ converters

$\Sigma\Delta$  converters is the favourite candidate in the SoA when that main constrain of the design is the required resolution. This family of converters is well known as the high-resolution converters in the whole range of input frequencies. The two keys of the popularity of  $\Sigma\Delta$  are the effect of use an Over Sampling Ratio (OSR) and perform noise-shaping. As it is mentioned in [52] OSR is the ratio between the sampling frequency of the converter divided by two times the bandwidth of the input signal (fs/2\*BW). It is proven in [52] that the transfer function of a  $\Sigma\Delta$ , with OSR, doesn't affect the power of the input signal but have an attenuation effect on the in-band-noise. Therefore, every time that the OSR is doubled, the power of in-band-noise is divided by half, or what is the same, by 3 dB. This relation is explained by the Signal to Noise Ratio (SNR) classic equation of an oversampling converter:

$$SNR=6.02*N+1.76+10*log(OSR)$$

(1)

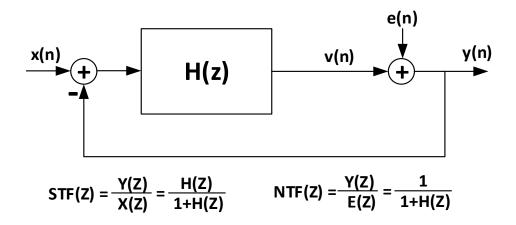

Where N is the number of bits in the quantizer. The noise shaping-behavior come out of the transfer function of the  $\Sigma\Delta$ . [52] explains that the noise transfer function (NTF) inside a  $\Sigma\Delta$  modulator is affected by a high-pass filter when the signal transfer function (STF) is a simple integrator, as it can be seen in Figure 2-4.

Figure 2-4 Block diagram and transfer function of a  $\Sigma\Delta$  modulator

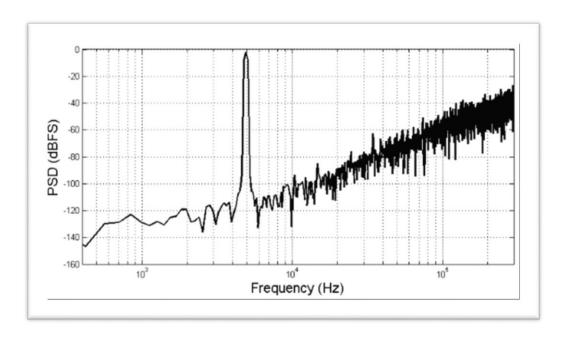

The properties that come out of the equations shows a big improvement of the previous SNR shown in equation (1). It is easy to understand the improvement of these two properties together, the combination of OSR (that moves to high frequencies the residual of the conversion) with the filter in the NTF thanks to the noise-shaping improves the SNR, as can be seen in equation (2), in the in-side-bandwidth of the converter as can be seen in Figure 2-5, where the fast Fourier transform (FFT) of a  $\Sigma\Delta$  converter output is presented.

$$SNR=6.02*N+1.76-5.17+30*log(OSR)$$

(2)

Figure 2-5 FFT of a  $\Sigma\Delta$  modulator with noise shaping

The stability of these converters is the main drawback. Having a high order  $\Sigma\Delta$ that can give the highest resolution of all the converter families, imply a design that needs to deal with the stability of a third, fourth or higher order loop, which is very sensitive to tolerances of the circuit. To deal with these issues, specific circuits that try to minimize the undesired effects in the loop are needed, making the  $\Sigma\Delta$  converters more complex and with a bigger area and power consumption. In addition, classic  $\Sigma\Delta$ normally use a Flash quantizer to maximize the resolution of the conversion, this type of quantizer is not possible to be used with low voltage supply. The same problem affects all the conversions that works in the amplitude domain. To fix the problem, single-bit  $\Sigma\Delta$  converters have been developed in the last years to cope with a resolution equal to their old brothers. To give the same level of resolution, single-bit  $\Sigma\Delta$  increase to loop order of the converter and the OSR. As mentioned before the loop order directly affects the stability of the conversion, and in combination with higher sampling frequency makes the design almost impossible to work under undesired effects. There is always a possibility to spend more power and area to stabilize the converter but then, the constrains of the IoT solutions push the design again. In addition to that, make all the extra circuitry to improve the stability of the converter only works for a specific

application, it means, the converter is focused on make the conversion of a specific sensors.

# 2.4.1.2. Integration converters

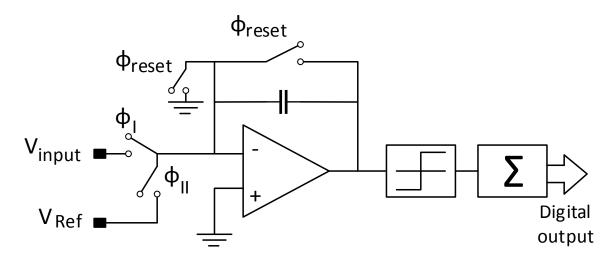

The integration converters family is well known in the SoA. It is considered a good candidate for low power converters in the low range of input bandwidth. Using simple circuitry, presented in Figure 2-6, the integration converters can cope with a good resolution. Inside the integration converters there are many different topologies. Period Modulation [36] or Current-Mode [18] are just some of the different way that this technic can be apply to converters. However, all of them have the same principle, the DS topology:

Figure 2-6 Block Diagram of Integration Converters

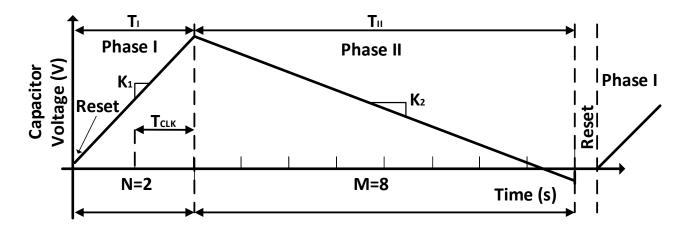

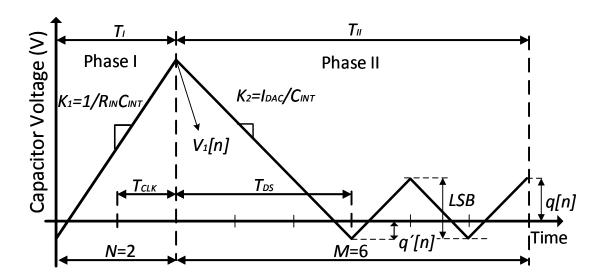

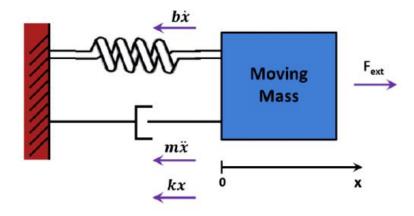

The behavior of this topology is simple. The conversion is based on charging a capacitor with a proportional voltage to the input value and then counts the time that takes to discharge the capacitor with a fixed current. It can be split in two phases and they are shown in Figure 2-7. In the first phase  $(T_I)$ , the DS ADC integrates the input value. The voltage stored in the capacitor will be then proportional to slope  $K_1 = V_{IN}/(R_{in} \cdot C_{INT})$ . This is only true if the input signal stays constant during  $T_I$ . To achieve this behavior the sampling frequency of the DS ADC  $(F_S=1/T_S=1/(T_I+T_{II}))$  is selected

much higher than the frequency of the input signal. In this way, the variation in the input signal during  $T_I$  will be negligible. This is one of the reasons why this topology fits good for low bandwidth applications. Use this solution for audio or video would lead to a clock in the DS ADC around GHz. In the second phase ( $T_{II}$ ), the DS ADC is connected to the fixed current that discharges the capacitor with a constant slope ( $K_2$ = $I_{DAC}/C_{INT}$ ). When the capacitor is full-discharged (a zero crossing is detected), the conversion is achieved and the voltage in the integrating capacitor is reset. To obtain the digital output of the conversion the number of clock cycles of the second phase are counted. The resolution achieved in this method is proportional to the number of clock cycles needed to discharge the full-scale input signal. This feature makes the topology flexible to adapt for different resolution with the root cost of frequency speed and therefore power consumption. The resolution (LSB) and number of bits can be calculated as is shown in equation (1) and equation (2).

$$LSB = \frac{V_{FS}}{M} \tag{1}$$

$$N_{bits} = log_2(M) (2)$$

Figure 2-7 Time table of an Integration Converter (DS)

Where  $V_{FS}$  is the maximum input level and M the number of clock cycles needed for the conversion. In the example of Figure 2-7, M=8 which lead to a  $N_{bits}$  = 3. To increase the resolution the frequency of the clock or the measuring time have to increase.

This topology fits perfectly for the principle of continuous measurement mentioned before. The measuring time of the conversion can be escalated depending on the resolution required by adjusting  $K_2$ . However, the resolution will be limited by the measuring time constrain of the application.

#### 2.4.2. Discontinuous Converters

In contrast with the previous converters, discontinuous converters switch off after the conversion in order to save power or just to make a reset in the design for future conversion. Making the conversion ins this way makes discontinuous converters ideal for multi input behavior. They use the switched off time of the converter to change the input to a new sensor without affecting the effective measuring time. Inside discontinuous converters there are three mainly types of architecture used in the SoA: Incremental Data Converters, SAR Converters and VCO Converters.

# 2.4.2.1. Incremental Data Converters (IDCs)

IDCs can be defined as the new generation for  $\Sigma\Delta$  or at least inside the IoT world [53]. An  $\Sigma\Delta$  IDCs is a  $\Sigma\Delta$  ADC that is reset periodically. They use a decimation filter which is much simpler than in the classic solution, it gives the conversion result between two reset clock-edges. The intermittent operation improves the sample to sample accuracy, makes a direct impact on the efficiency of power consumption and enables a single ADC to be connected to multiple channels, eliminating the need for more ADCs for each sensor, and therefore reducing the area needed drastically. Also, the latency from the analog input to the digital output is smaller than in a classic  $\Sigma\Delta$  converter, it is only a Nyquist conversion period. As it was mentioned before the power supply is one of the main constrains that affect the new topologies, that is why the IDCs normally use

a 1-bit comparator for the conversion. However, these converters suffer from having dead-zones around the thresholds of the quantizer, typically around zero, because of the two-level quantizer used in 1-bit circuitry due IoT constraints. In Figure 2-8 a diagram block of a typical  $\Sigma\Delta$  IDCs is presented. The Digital Signal Processing (DSP) is used to correct the gain and offset error of the  $\Sigma\Delta$  ADC. As explained before it is a  $\Sigma\Delta$  converter with the modifications needed to be efficient in IoT applications.

Figure 2-8 Block diagram of a  $\Sigma\Delta$  IDC

The main improvements of these kind of converters are: the direct reduction of power compared with classic  $\Sigma\Delta$  due uncontinuous conversions, the flexibility to deal with different sensor outputs, the reduction in area of the application thanks to the two previous characteristics. Only on ADC is needed in the solution.

However, these modifications have some drawbacks. Compared with classic  $\Sigma\Delta$  converters there is a degradation of performance due to the ability to multiplex between different inputs. Normally, due the reset pulse of each conversion the length of the impulse respond is limited, and it affects the SQNR. In addition,  $\Sigma\Delta$  IDCs still have some of the issues of classic  $\Sigma\Delta$  converters.  $\Sigma\Delta$  IDCs are implemented using 1-bit circuitry in the modulator to deal with source voltage issues. Because of that high frequencies and high loop orders are needed, increasing the risk of stability.

There are many different lines of investigation to trying to fix the issues mentioned before. One of the most used is the MASH IDCs [53]. MASH topologies are

a well-known architecture that has been used in  $\Sigma\Delta$  ADCs for a long time. The MASH architecture, also called cascade ADC, uses different low order modulator loops (1st or 2nd order) in cascade to increase the order of noise-shaping without increase the order of the loop (and therefore the instability). Also, the use of the cascade topology improves the energy efficiency. This is because less peripheral circuits are needed (simpler DACs and quantizers). However, the use of MASH converters implies an increase complexity in the digital part of the converter due the cancelation filters needed. The cancelation filters are the responsible of increase the order of noise-shaping making the perfect cancelation of the NTF of the first loop. The complexity of these filters depends on the order of each loop. Also, the opamp of the first loop needs to have a high DC gains to avoid SQNR degradation Therefore to obtain a high SNR it requires opamp DC gain similar to the one used in a  $\Sigma\Delta$  high order loop, which is difficult to achieve in a low-voltage design without any extra circuitry that kills the energy efficiency. On the other hand, MASH IDCs have much more relaxed requirements for the opamp gain and it has a much simpler filtering in the digital part, just implemented by decimation blocks [53].

# 2.4.2.2. Successive Approximation Register (SAR) Converters

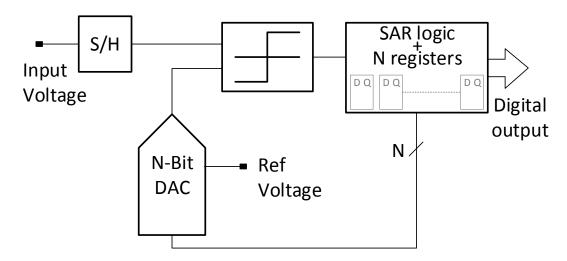

Successive-approximation-register (SAR) converters are used in a wide number of applications. The applications that use this topology are frequently the ones that have medium-to-high-resolution up to the range of MHz of input signal. The resolution of SAR converters is inside the range from 8 to 12 bits. One of the most attractive characteristic is their low power consumption. No amplifier is needed as it can be seen in Figure 2-9 where the main blocks of a SAR converter are presented. The analog input goes to a track and hold block and it is compared with successive level of voltage from a reference with a multi bit DAC. The output of each comparison goes to a register. At the end of the conversion the output of all the register makes the digital vale of the input.

Figure 2-9 Block diagram of a SAR converter

The evolution of the conversion is presented in Figure 2-10. As it was said before, successive comparations are done between the tracked input and the levels of reference. The amount levels of reference voltage are directly related with the resolution of the conversion. For example, a 12 bits SAR converter will create 12 levels of reference with a 12 bits DAC. Therefore, the limitation of resolution is directly dependent on the CMOS technology and the voltage supply. In the market of IoT, where the applications work with low voltage technologies, SAR converters are a good candidate for applications that doesn't need much resolution and need to have a fast conversion time or a very low power consumption.

Figure 2-10 Time table of a SAR conversion with 4 bits

# 2.4.2.3. Voltage Controlled Oscillator Converters

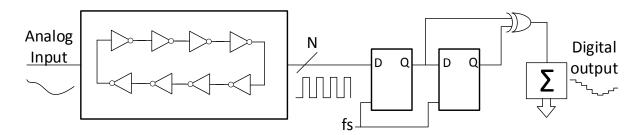

VCO Converters base they behavior in taking an analog input and transform it into the phase domain with a frequency proportional to the amplitude level of the input. The block schematic of the converter is shown in FIG. The oscillator will produce X number of transitions in the inverters of the chain between two periods of the system clock. The number of transitions is measured with a phase detector per inverter output (N in the example of Figure 2-11) and after the decimation of all the samples the digital number is obtained. This architecture has the property of being able to perform noiseshaping in the output without any feedback loop in the topology. This is possible thanks to the digital logic that creates the digital output. The outputs of the inverters of the oscillator have no reset between different samples of the converter. This means that the phase of each output stays constant between the end of one sample and the beginning of the next one. In other words, the phase error of the output n, is present in the output n+1. This property plus the no need of analog circuitry in the converter, gives the VCOs a very good relation between resolution and power consumption and area. Because of that, VCOs ADCs have grown significantly in the last years. The evolution of the CMOS technology into low voltage supply is normally a problem for many architectures of converters. On the other hand, for VCOs, this change plays as an ally. With the new CMOS technologies, the transition speed of the transistors has increase and therefore the frequency of oscillation can reach higher levels before modulation problems [54].

Figure 2-11 Block diagram of a VCO converter

However, there are some non-idealities that affect the VCOs:

- Sampling Clock jitter: VCO make the quantization in the time domain, therefor they use a fix amount of time as a reference, the sampling clock. Taking this into account, the jitter of this clock will produce a distortion in the results obtained. The sampling clock is not only used to start the conversion, it also gives the period of time of integration. Therefore, this non-ideality introduces two sources of error. The first one is the absolute jitter. It is produced because of the delta of time between the starting theoretical time and the rising edge of the system clock. This is common in any kind of ADCs and the effect doesn't differ from them. However, the change of integration period of time has a direct impact in the output, it can be seen as a change in the full-scale reference of the system, introducing a big distortion in data. To reduce this effect, the free running frequency of the VCO should be reduced. In this way the relative time that is added or subtracted in each measurement by the jitter is reduced.

- VCO phase Noise: This effect comes a as consequence of the oscillation frequency of the VCO. Ideally, the spectrum of a VCO is like a sine wave. And ideal tone at the frequency of oscillation and white noise in the rest of the bandwidth. However, the non-ideal behavior of the electronics (thermal and flicker noise) produce a modification in the oscillation frequency. In the spectrum can be seen as two slopes around the tone. Due aliasing effect, these tones moves into low frequency domain, increasing the noise floor with a 10 dB/dec behavior. To deal with this effect, the designer needs to apply some techniques to reduce the thermal and flicker noise inside the oscillator, and therefore the effect due aliasing in the in-band-noise.

- Nonlinearity of VCO: VCO has nonlinearity in its tuning curve. Therefore, harmonic peaks will appear like in voltage-based ADC with nonlinearity problems. There is no much to do with these sources of noise. It is one of the main constrains that VCOs have.

Inside the IoT market, VCO converters can be a good candidate. They have good numbers in area and power consumption. Basically, thanks to the digital blocks used. No power-hungry blocks are needed like amplifiers. Also, the scalability of this architecture is excellent. Just by digital tune it can change input bandwidth or its resolution. However, it will have a limit in resolution due the non-idealities mentioned before, especially in low bandwidth applications, were the oscillation frequency will be smaller and therefore the phase noise will dominate.

#### 2.4.3. SoA Analysis

The topologies presented in this section are the most used in applications for the market of IoT. The market is demanding solutions that can give high resolution data, normally, in the low-middle range of bandwidth. Also, the devices will try to measure all the possible environmental information. Therefore, IoT demand converters that can be connected to different kind of sensors. Also, the power consumption and area of the converter is an important constrain for application that will be inside small devices.

It is quite difficult to find a solution that works good in all the previous aspects. All the topologies described have their strength and weakness. Table I present a summary of all the main parameters need to be taken into account and all the topologies presented.  $\Sigma\Delta$  converters are able to give the highest resolution of all the converters in a wide range of input bandwidth, but this is achievable by architectures that uses power hungry blocks working at high frequencies. Also,  $\Sigma\Delta$  converters work in the amplitude domain. To give high resolution (N bits), a high voltage supply is needed in the quantizer to be able to create the N levels in the comparators. All these characteristics leads to a high area of silicon to perform the converter. Integration converters use one-bit circuitry and makes the conversion in the time domain, that is why they have a good power consumption that is scalable with low voltage technologies.

Table 1 Comparative between Converters topology and their properties

| Converties  | Resolution | Power<br>Consumption | Voltage<br>Supply | Area   | Speed  |

|-------------|------------|----------------------|-------------------|--------|--------|

| ΣΔ          | Very high  | Very high            | high              | high   | fast   |

| Integration | medium     | small                | small             | high   | slow   |

| IDC         | high       | medium               | high              | medium | fast   |

| vco         | low        | very small           | very small        | small  | fast   |

| SAR         | medium     | small                | high              | medium | medium |

However, the resolution is limited to the measuring time for each application because of the low speed of the architecture, not being able to give as much resolution as other solutions. The area is not as big as in  $\Sigma\Delta$  converters, but they also use some active components that are large in area compared with digital blocks. IDCs reduce the power consumption of  $\Sigma\Delta$  by reducing also the resolution. In addition, thanks to the possibility to be attached different inputs by a multiplexer, the average area and power are improved. However, IDCs also make the conversion in analog domain, having the same kind of problem with the source of voltage. VCO have the lowest power consumption of all the architectures presented (working in the low range of input frequency). The digital blocks of the architecture have low power consumption, don't need a high source of voltage (in fact they work better with low small technologies thanks to the increase in speed in the transitions of the transistors) and have a small area in silicon. Also, the can work with higher input signal frequency (by increasing also the power consumption). However, due the linearity issues the resolution is limited. SAR converters are very power efficient, avoiding any power-hungry block in the conversion and having a low duty time of conversion per period. As all the other converters that work in the amplitude domain they are directly affected with by the low supply voltage technologies. Having also a limitation in resolution because of this problem. The area in silicon is also good compare with some architectures, but not as good as in VCOs. The same happens with the speed of conversion.

Considering the scenario presented, there is no a clear solution. All of them have their pros and cons. That is the reason why a new kind of converters is demanded. A topology that can put together the benefits of the different solution already presented will give the market of IoT a flexible solution that will be able to work in more types of applications at the same time. The name that they received is Hybrid Converters. Many different lines of investigation are trying to mix the benefits of low power solution mixed with high resolution ( $\Sigma\Delta$  properties). Some of them are trying to replace the quantizer inside a  $\Sigma\Delta$  or an IDC by a low power converter (in amplitude or time domain) and others are using techniques to obtain noise-shaping in Nyquist topologies.

As an example, [55] presents a topology where IDC and SAR architecture are mixed. A second order topology is achieved by an IDC using zero-crossing detectors (ZCD) instead of classic OTA to save power and an energy-efficient noise-shaping SAR as a quantizer inside the IDC. Results show a resolution of 16 bits with a power consumption of  $0.24~\mu W$ .

Similar effect is also achievable in time domain. [41] presents an ADC of third order built just by digital blocks. It is just a combination of VCO and digital blocks. By the combination of them a continuous time sigma delta of third order is achieved. The problem of distortion inside the VCO is solved by digital calibration of the architecture. Pushing this effect below the noise level. The results show a very efficient in power ADC for an input frequency in the ranges of MHz. However, the application differs from the IoT. Theoretically, due its digital architecture; resolution, power and input bandwidth can be escalated to IoT requirements. It could be a good solution if the linearity problem and phase noise are still below quantization noise at low frequencies.

#### 2.5. Conclusion

After all the topologies presented in the SoA and their characteristics, pros and cons there are some conclusions that come out to select a topology for our application.

- Conversion in the time domain. Working in the new CMOS technologies for low power consumption affects directly the level of the power supply. This change in the specifications directly affects all the topologies that makes the conversion in the amplitude domain. Therefore, conversion in the time domain is mandatory for us in order to keep the efficiency of the topology when the new technologies that have to come to the market of IoT.

- Perform Noise shaping. In Table 1, the converters that are able to achieve high resolutions with the requirements of the IoT applications are architectures that are able to perform noise-shaping. This property affects directly the resolution by reducing the power of noise in the input bandwidth. The architecture that we want to implement need to include this feature.

- Use one-bit circuitry. It is needed that the applications are robust. They need to be independent from process, voltage and temperature (PVT) variations as much as possible. One-bit circuitry is less sensitive to these tolerances. Also, the design need to be as small as possible. One-bit circuitry save a lot of space compared with multibit solutions.

Considering all these conclusions and looking at the table there are only two possible candidate topologies of converter that can satisfy the requirements. DS (Integration Converters) is selected as the topology that can be optimized in a hybrid topology thanks to low power consumption, robustness and room of improvement in the time of conversion.

# Chapter 3.

# CDC with a Self-Compensated Dual Slope

There are multiple possible approaches to create a front-end circuit that take the values out of the capacitors from the MEMS and give a stable signal as an input for the digital conversion. This is the first concern of the study, find a solution that is able to take the data out of the input capacitors with enough resolution and using the needed techniques to reduce the noise in the process. This chapter presents the main front-ends solutions for capacitive sensors that are used and a study to select the one that fits better for our application.

To complete the CDC a converter is needed after the processed input. As it was mentioned in the previous chapter, the study performed to analyse the State-of-the-Art (SoA) give the conclusions of what type of architecture we wanted to study and develop. Thinking into future applications, conversion in the time domain looks more feasible considering the supply voltage that new CMOS technologies are using. Make a design that base the performances in a technic that depends directly in this variable will reduce the room of use of our application. In addition, the use of one-bit circuitry goes in the

#### CDC with a Self-Compensated Dual Slope

direction of the constrain already mentioned plus a reduction in power consumption and an improve in linearity. To conclude, he level of resolution, which is one of the main concerns in the applications that we target in this design is only achievable using techniques from  $\Sigma\Delta$  converters as noise-shaping. Therefore, an evolution in Classic Dual Slope is needed. This is also presented in this chapter with the topology that has been developed for this application, the Self-Compensated DS.

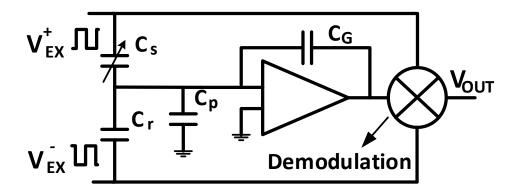

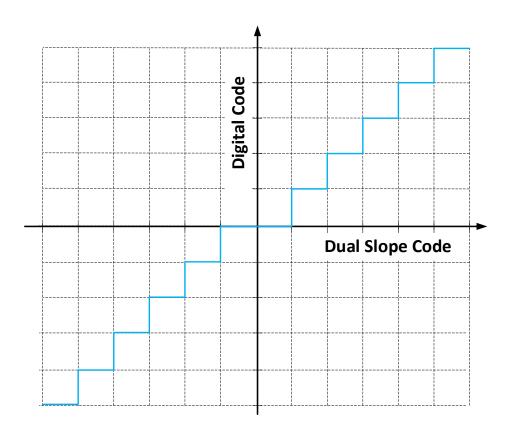

# 3.1. Front-end topology