## TESIS DOCTORAL

## Oversampled Analog-To-Digital Converter Architectures Based On Pulse Frequency Modulation

by

Eric Gutiérrez

PhD advisor: Luis Hernández

Electronics Technology Department Carlos III University of Madrid Leganés, December 2017

# TESIS DOCTORAL

# Oversampled Analog-To-Digital Converter Architectures Based On Pulse Frequency Modulation

|              | PhD author: E      | Cric Gutiérrez |        |

|--------------|--------------------|----------------|--------|

|              | PhD advisor: La    | uis Hernández  |        |

| Firma del T  | Tribunal Calificad | lor:           | Firmas |

| Presidente:  |                    |                |        |

| Vocal:       |                    |                |        |

| Secretario:  |                    |                |        |

| Calificación | :                  |                |        |

| Lega         | nés,               | de             | de     |

## Acknowledgments

I would like to express my gratitude to all the people who contributed somehow to the research work described in this document.

Thanks to the members of the Electronics Technology Department at Carlos III University who helped me to carry out this work. Many special thanks to my PhD advisor Luis Hernández, who let me work within his research group and devote these years to the field of signal processing and microelectronics. Thanks for the careful review made of this document too.

Thanks to all the members of the Connected Home Division in Intel Austria GmbH in Villach, Austria. I felt very welcome within your group. It was a pleasure learning analog and digital electronics design from you. Big thanks also for the economic support provided during my research period.

Thanks to the partners at university, who made me feel fine during lunch times and pushed me from the beginning to the end of my research period. Thanks to Carlos and Marcos, whose suggestions made this work look better.

As a non-optional social convention, dankzij Pieter Rombouts en de andere leden van de ELIS-groep (circuits en systemen) van de Universiteit Gent. Ik heb veel geleerd tijdens de maanden van mijn verblijf daar.

The most special thank you to my family. Thanks to my parents, who always support me, even when the craziest ideas come to my mind. Thanks to Edgar, who also reviewed this work and provided me very useful comments. I hope we can interchange the roles in the future.

Finally, many many thanks to Martuca, my awake dreamer partner. This work is also yours. Thanks for making me smile at bad moments, encouraging me during the working weekends and taking care of me. Thanks not only for staying with me in Gent, but also in Brussels, Antwerpen, Villers, Mechelen, Leuven, Brugge, Oostende, Ieper and De Panne. I have finished this research work because you spent that time abroad with me. I hope to be able to return you the favor.

Eric Gutiérrez

November 2017

# Contents

| 1      | Intr           | oducti           | ion                                                         | 1  |

|--------|----------------|------------------|-------------------------------------------------------------|----|

|        | 1.1            | Conte            | xt and motivation                                           | 1  |

|        | 1.2            | Scope            | of the dissertation                                         | 2  |

|        | 1.3            | Docum            | ment outline                                                | 3  |

|        |                |                  |                                                             |    |

| I<br>a |                |                  | tical modeling of VCO-based ADCs based on erpretation       | 5  |

| 2      | VC             | O-base           | ed ADCs: From the general to the specific                   | 7  |

|        | 2.1            | Analo            | g-to-digital conversion                                     | 7  |

|        | 2.2            | $\Delta\Sigma$ m | odulation                                                   | 12 |

|        | 2.3            | VCO-             | based ADCs                                                  | 14 |

|        |                | 2.3.1            | VCO-based integrator                                        | 15 |

|        |                | 2.3.2            | A digital voltage-controlled oscillator (VCO): the ring os- |    |

|        |                |                  | cillator                                                    | 16 |

|        |                | 2.3.3            | VCO-based configurations                                    | 16 |

|        |                |                  | 2.3.3.1 Open-loop configuration                             | 17 |

|        |                |                  | 2.3.3.2 Closed-loop configuration                           | 18 |

|        |                | 2.3.4            | VCO non-linearity                                           | 18 |

|        |                |                  | 2.3.4.1 Digital calibration                                 | 19 |

|        |                |                  | 2.3.4.2 Digital precoding                                   | 20 |

|        |                |                  | 2.3.4.3 Residue canceling                                   | 20 |

|        |                |                  | 2.3.4.4 Circuit-based solutions                             | 21 |

|        | 2.4            | Conclu           | usion                                                       | 21 |

| 3      | $\mathbf{Spe}$ | ctral a          | analysis of VCO-based ADCs based on pulse frequency         |    |

|        | mod            | dulatio          | $\mathbf{n}$                                                | 23 |

|        | 3.1            | An int           | troduction to the analysis of a VCO based on the pulse fre- |    |

|        |                | quenc            | y modulation theory                                         | 24 |

|        | 3.2            | Pulse            | frequency modulation: An alternative way to look at a VCO   | 25 |

|        |                | 3.2.1            | VCO – PFM Equivalence                                       | 25 |

|        |                | 3.2.2            | Discussion of the Modulation Spectra                        | 27 |

|        |                | 3.2.3            | Fundamental SNDR Limit of VCO-based coders                  | 28 |

|        | 3.3            | Direct           | construction of a VCO-based ADC using the PFM repre-        |    |

|        |                | sentat           |                                                             | 31 |

|        |                | 3 3 1            | Going from a PFM encoder to an ADC                          | 31 |

|   |     | 3.3.2        | Error analysis of the generic VCO-based ADC                    | 32           |

|---|-----|--------------|----------------------------------------------------------------|--------------|

|   |     | 3.3.3        | Implementation of a generic VCO-based ADC                      | 37           |

|   | 3.4 | Appro        | eximation of second order pulse shaping filters with a contin- |              |

|   |     |              | ime FIR filter                                                 | 41           |

|   | 3.5 | Detail       | ed analysis of the first-order VCO-based ADC structure         | 45           |

|   |     | 3.5.1        | First-order open-loop VCO-based analog-to-digital converter    |              |

|   |     |              | (ADC) architecture and pulse frequency modulation (PFM)        |              |

|   |     |              | equivalence                                                    | 46           |

|   |     |              | 3.5.1.1 Oscillator spectrum before sampling                    | 46           |

|   |     |              | 3.5.1.2 Sampled spectrum                                       | 47           |

|   |     |              | 3.5.1.3 signal-to-noise-and-distortion ratio (SNDR) prediction | 50           |

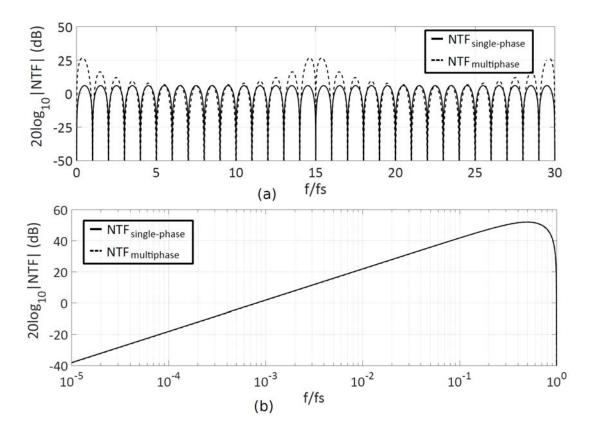

|   |     | 3.5.2        | Extension to first-order noise shaping architectures with      |              |

|   |     |              | multiphase VCOs                                                | 50           |

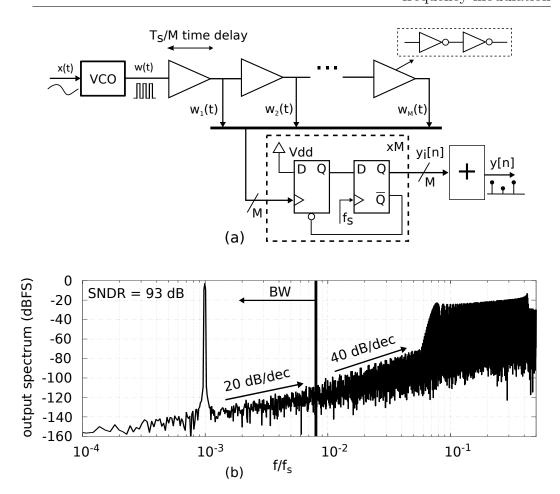

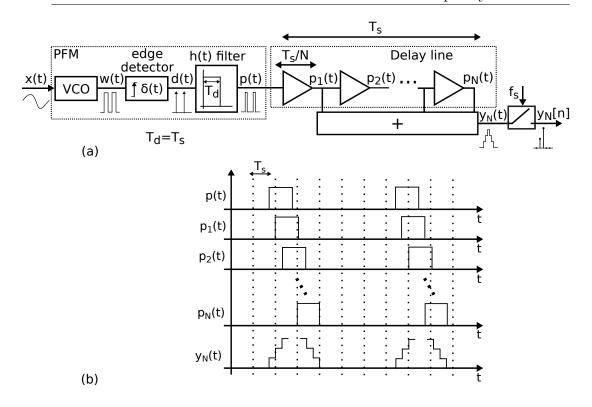

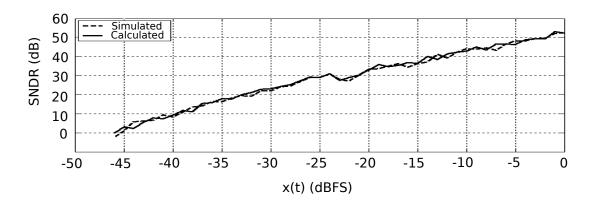

|   |     |              | 3.5.2.1 Multiphase ring oscillator based ADC                   | 51           |

|   |     |              | 3.5.2.2 Multiphase PFM-based ADC                               | 55           |

|   | 3.6 | Concl        | usion                                                          | 57           |

|   | _   |              | modulation                                                     | 59           |

| 4 |     |              | ed single stage architectures                                  | <b>61</b> 62 |

|   | 4.1 | Digita 4.1.1 | l precoding                                                    | 02           |

|   |     | 4.1.1        | lated precoding                                                | 62           |

|   |     | 4.1.2        | Conclusion                                                     | 67           |

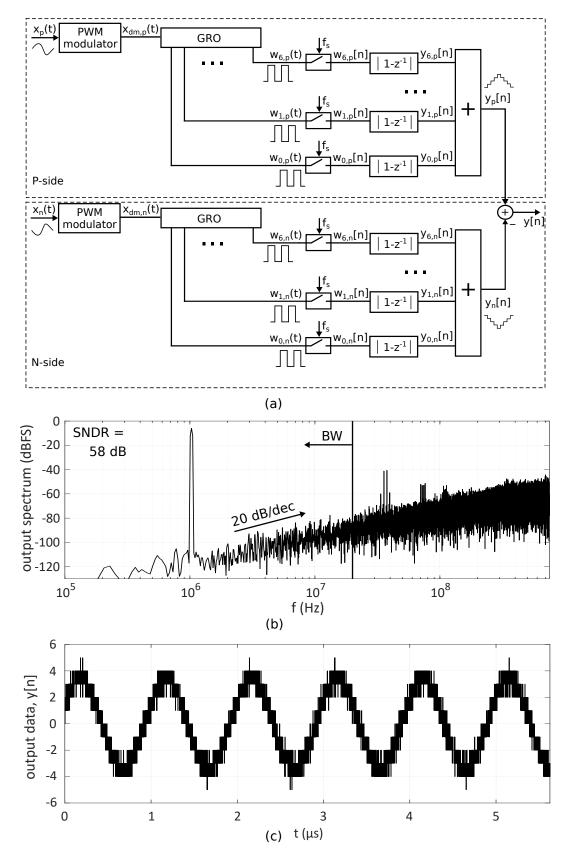

|   | 4.2 | ADC          | circuits based on an analog pulse frequency modulator          | 68           |

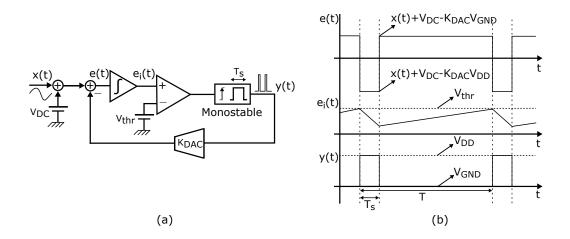

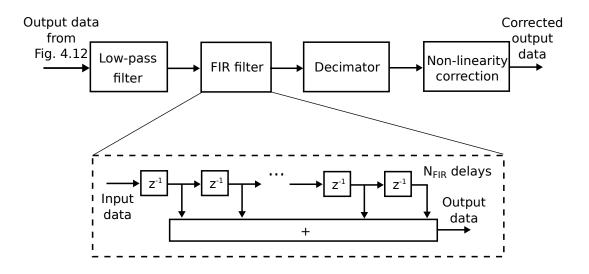

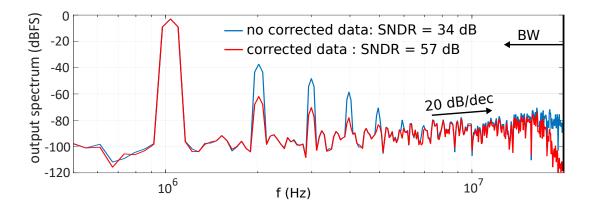

|   |     | 4.2.1        | An efficient ADC implemented with a pulse frequency modulator  | 69           |

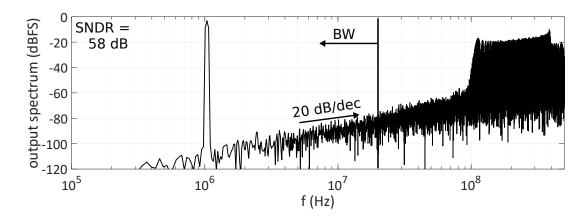

|   |     | 4.2.2        | PFM-based ADC with active integration                          | 72           |

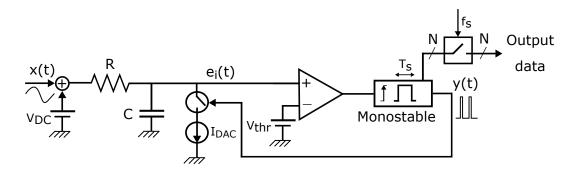

|   |     | 4.2.3        | Pulse frequency modulator with resistive input and digital     |              |

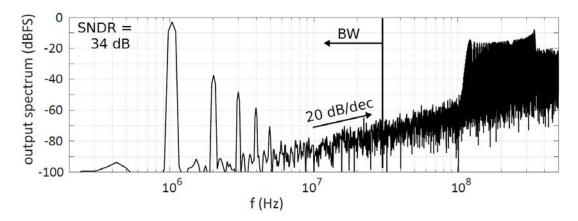

|   |     |              | correction of non-linearity                                    | 75           |

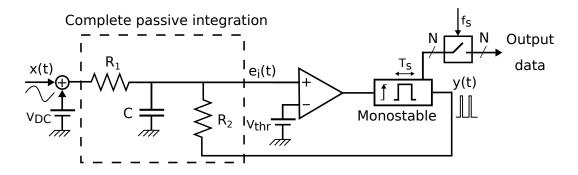

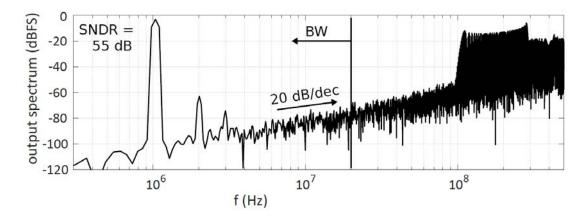

|   |     | 4.2.4        | Pulse frequency modulator with passive RC loop filter          | 78           |

|   |     | 4.2.5        | Conclusion                                                     | 80           |

|   | 4.3 |              | approach to the implementation of VCO-based closed-loop        |              |

|   |     |              | ectures                                                        | 81           |

|   |     | 4.3.1        | An "imperfect" integrator built with a VCO                     | 82           |

|   |     | 4.3.2        | Application examples                                           | 85           |

|   |     | 4.3.3        | Conclusion                                                     | 88           |

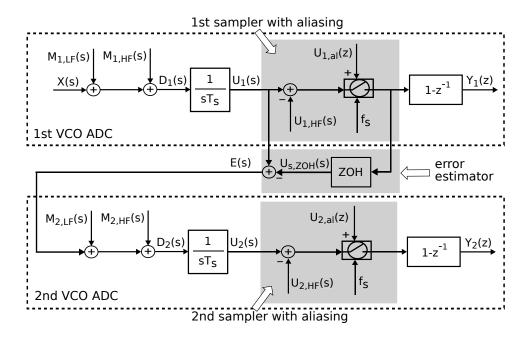

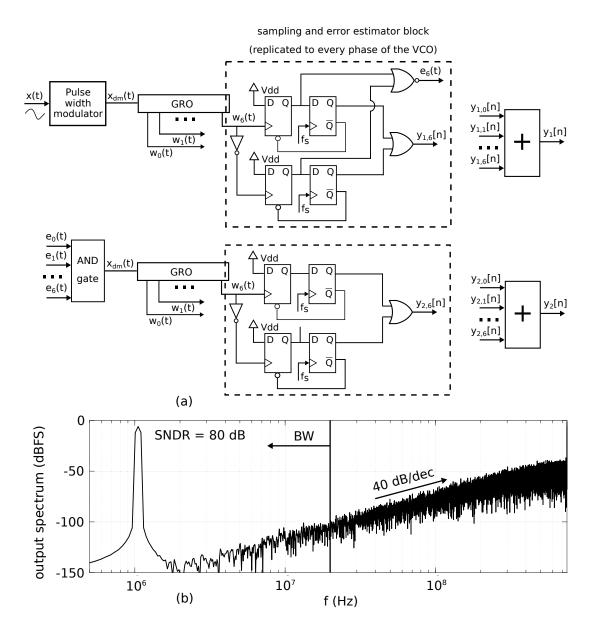

| 5 | VC  | O-bas€       | ed multistage noise shaping architectures                      | 91           |

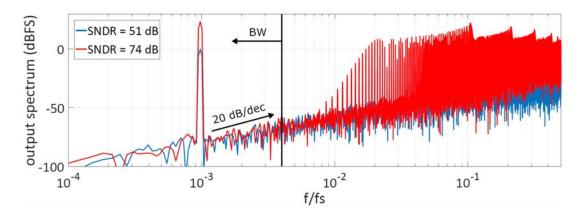

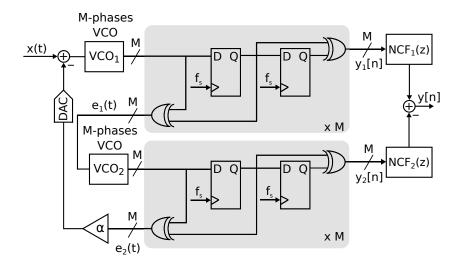

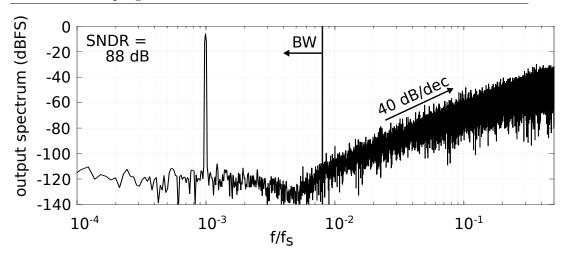

|   | 5.1 | Analy        | sis of MASH VCO-based ADC architectures using the PFM          |              |

|   |     | theory       | <sup>7</sup>                                                   | 92           |

|   |     | 5.1.1        | Practical implementation                                       | 94           |

|   |     | 5.1.2        | Finite interconnection bandwidth and gain mismatch             | 96           |

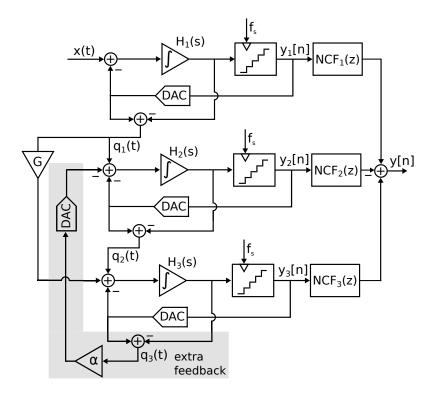

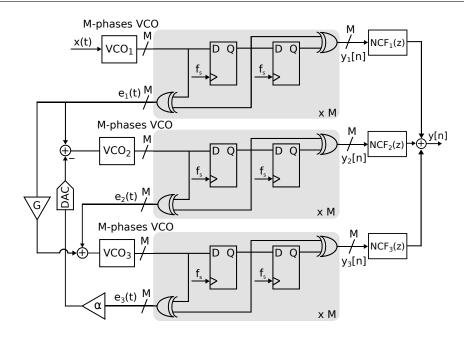

|   |     | 5.1.3        | Extension to higher order MASH architectures                   | 99           |

|     | 5.2        | 5.1.4 Conclusion                                                                                                                                  | <ul><li>100</li><li>101</li><li>101</li></ul> |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|     |            | <ul> <li>5.2.2 VCO-based 1-1 MASH with optimized NTF zeros</li> <li>5.2.3 1-1-1 continuous-time MASH modulator with optimized NTF zeros</li></ul> | <ul><li>103</li><li>104</li></ul>             |

|     |            | 5.2.4 VCO-based 1-1-1 MASH with optimized NTF zeros                                                                                               | 105                                           |

|     |            | 5.2.5 Conclusion                                                                                                                                  | 107                                           |

|     | 5.3        | Extension of the VCO-based structure with digital precoder to a MASH architecture                                                                 | 108                                           |

| ΙΙ  | Ιŀ         | Experimental results                                                                                                                              | 111                                           |

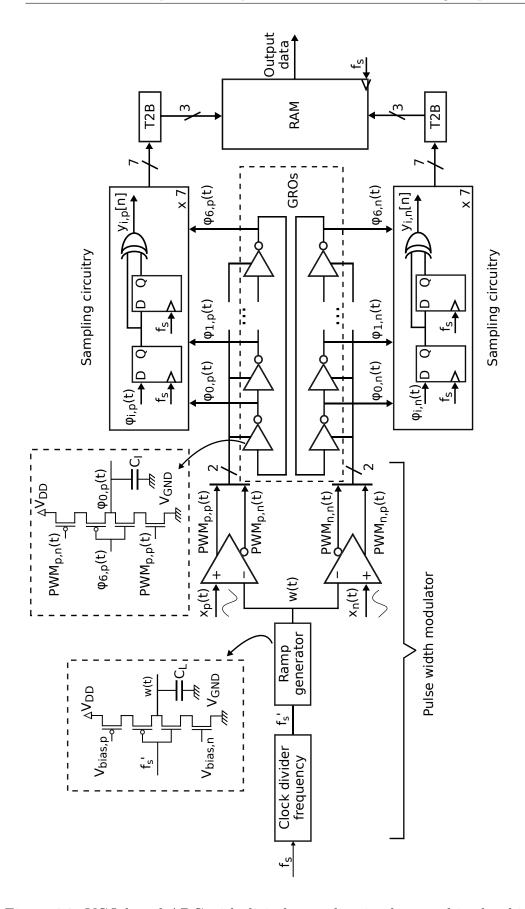

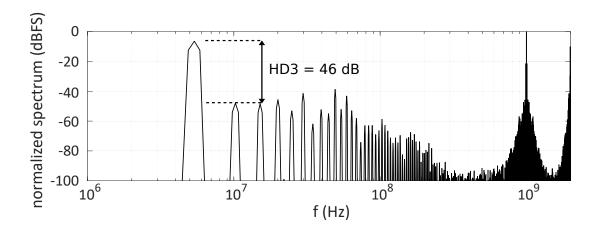

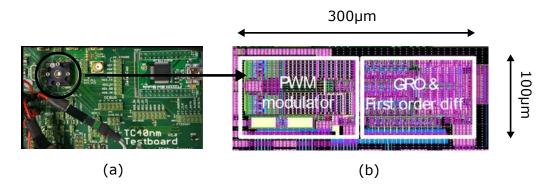

| 6   | Chi        | p I: VCO-based ADC with digital precoding                                                                                                         | 113                                           |

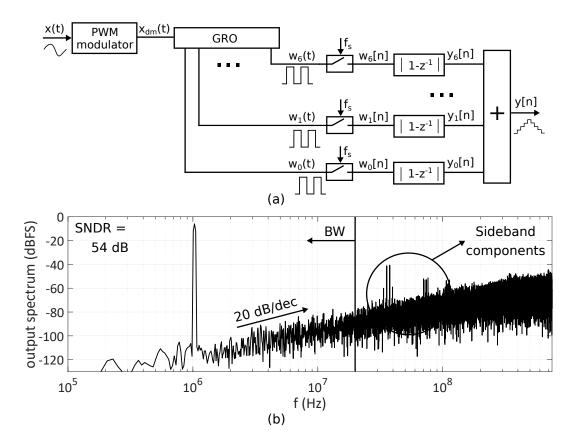

| Ū   | 6.1        | Implementation details                                                                                                                            | 113                                           |

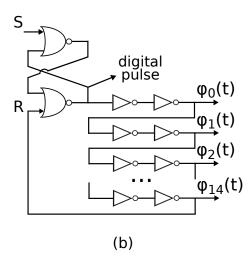

|     |            | 6.1.1 Pulse width modulator                                                                                                                       | 115                                           |

|     |            | 6.1.2 GRO                                                                                                                                         | 117                                           |

|     |            | 6.1.3 Digital logic                                                                                                                               | 117                                           |

|     | 6.2        | Experimental results                                                                                                                              | 118                                           |

|     | 6.3        | Conclusion                                                                                                                                        | 119                                           |

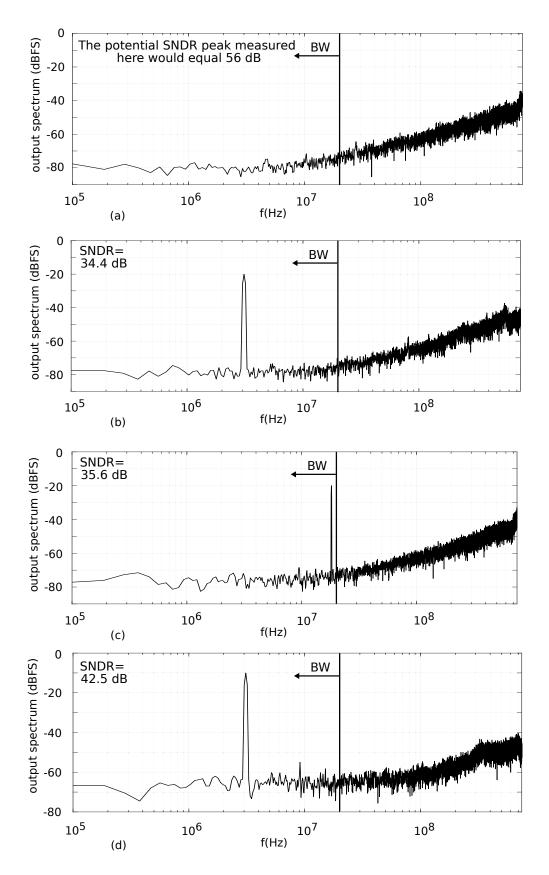

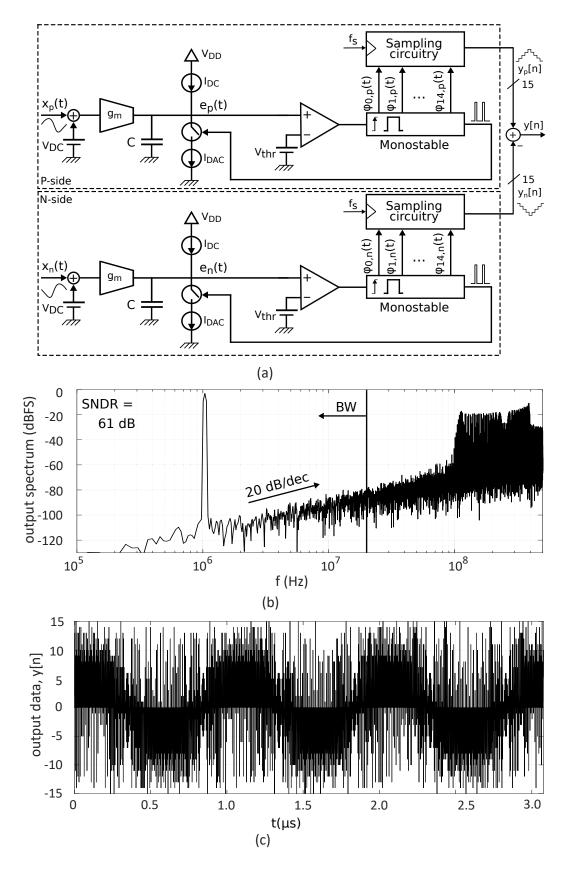

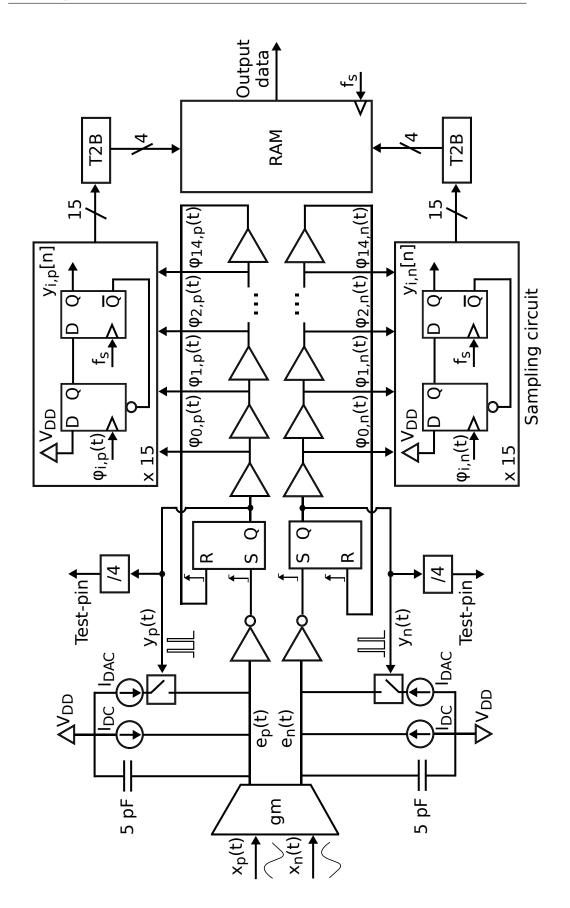

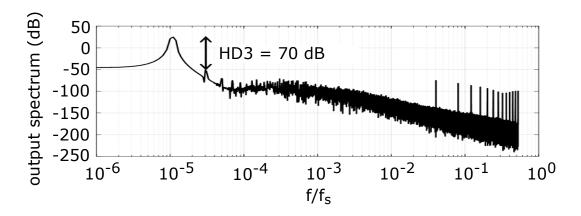

| 7   |            | p II: PFM-based ADC with active integration                                                                                                       | <b>123</b>                                    |

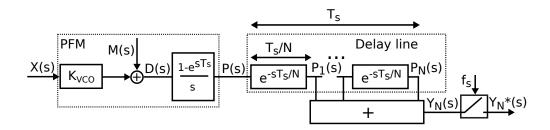

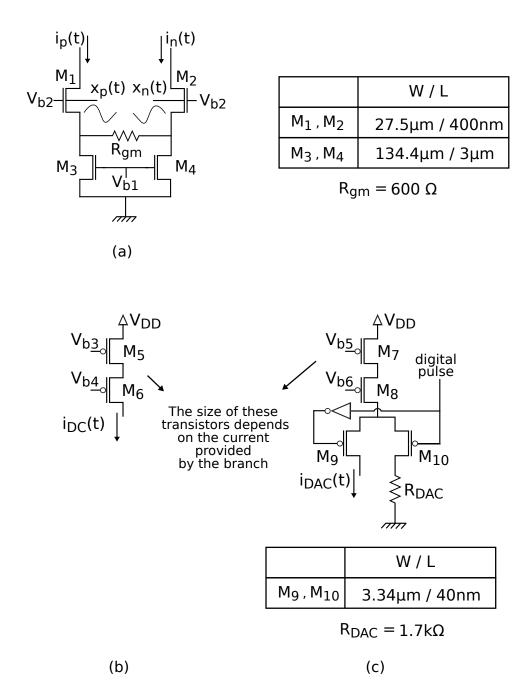

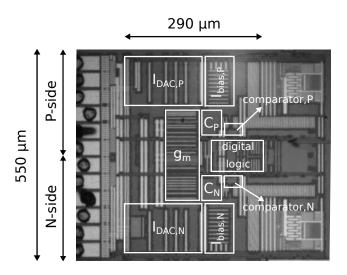

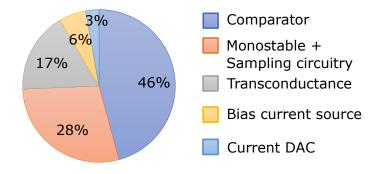

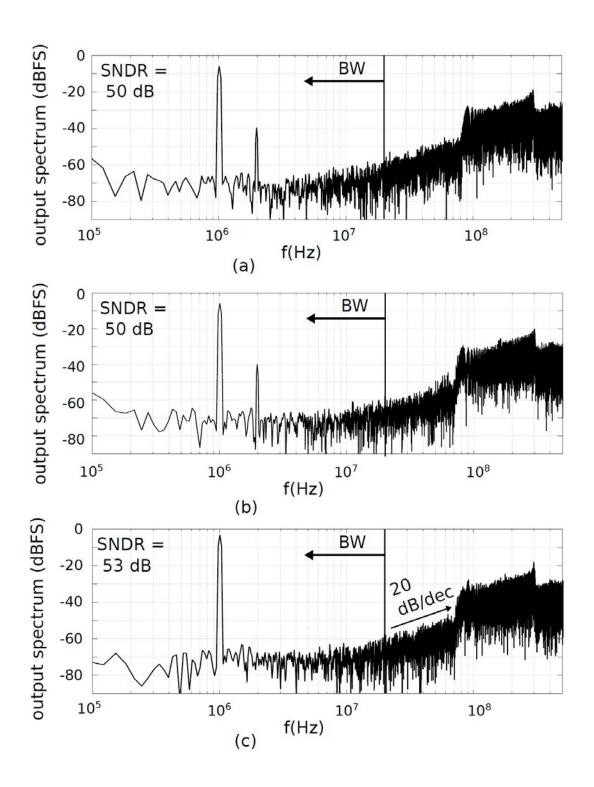

|     | 7.1        | Implementation details                                                                                                                            | 123                                           |

|     |            | 7.1.1 Bulk-driven transconductance                                                                                                                | 126                                           |

|     |            | 7.1.2 Bias current source and current DAC                                                                                                         | 127                                           |

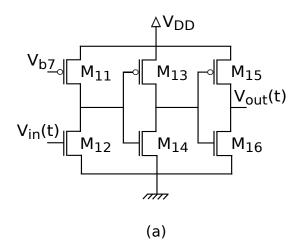

|     |            | 7.1.3 Comparator                                                                                                                                  | 127                                           |

|     |            | 7.1.4 Monostable and digital logic                                                                                                                | 128                                           |

|     |            | 7.1.5 LDO and circuit references                                                                                                                  | 128                                           |

|     | 7.0        | 7.1.6 Calculation of oscillation parameters                                                                                                       | 131                                           |

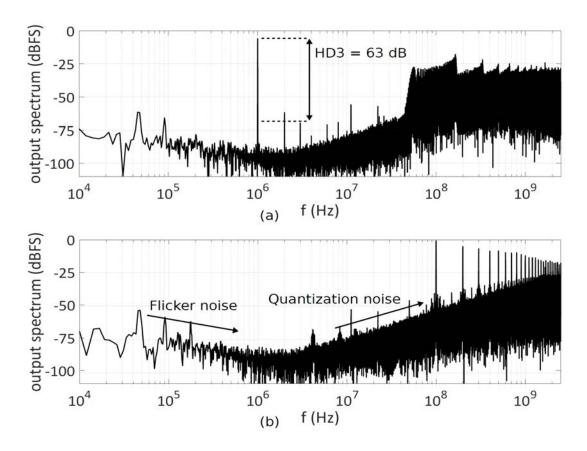

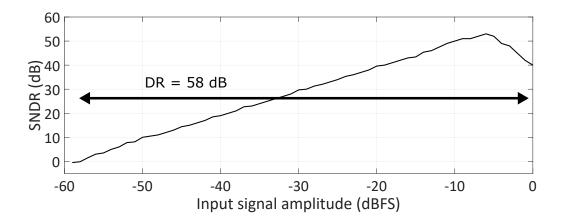

|     | 7.2<br>7.3 | Experimental results                                                                                                                              |                                               |

|     | 1.0        | Conclusion                                                                                                                                        | 194                                           |

| IJ  | <i>T</i> ( | Conclusion                                                                                                                                        | 137                                           |

| 8   | Con        | clusion                                                                                                                                           | 139                                           |

|     | 8.1        | Contributions                                                                                                                                     | 140                                           |

|     | 8.2        | Future work                                                                                                                                       | 142                                           |

| Co  | onclu      | siones                                                                                                                                            | 145                                           |

| Aı  | ppen       | dix                                                                                                                                               | 151                                           |

|     |            | graphy                                                                                                                                            | 153                                           |

| ٠,١ | ~1108      | o+ ~PJ                                                                                                                                            | ±00                                           |

# List of Figures

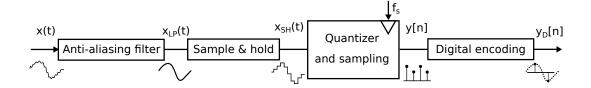

| 2.1  | Generic ADC diagram block                                                                                                     | 8    |

|------|-------------------------------------------------------------------------------------------------------------------------------|------|

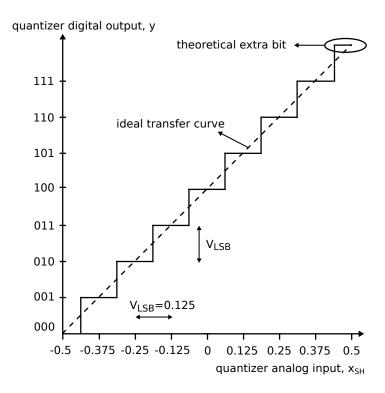

| 2.2  | Transfer function of a 3-bit quantizer                                                                                        | 9    |

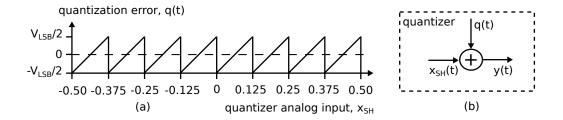

| 2.3  | (a) Quantization error associated to the quantizer of Fig. 2.2, and                                                           |      |

|      | (b) linear model of the quantization process                                                                                  | 9    |

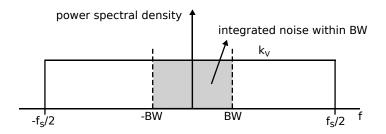

| 2.4  | Quantization noise power spectral density between $-f_s/2$ and $f_s/2$ .                                                      | 11   |

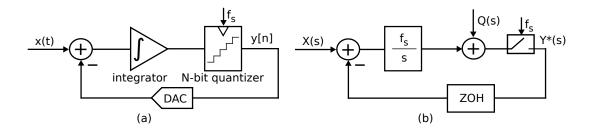

| 2.5  | (a) The simplest way of building a continuous-time $\Delta\Sigma$ modulator,                                                  |      |

|      | and (b) the equivalent linear model                                                                                           | 12   |

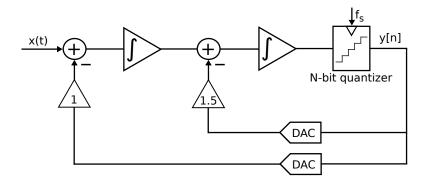

| 2.6  | Second-order continuous-time $\Delta\Sigma$ modulator architecture                                                            | 14   |

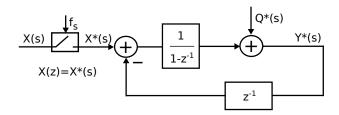

| 2.7  | First-order discrete-time $\Delta\Sigma$ modulator                                                                            | 14   |

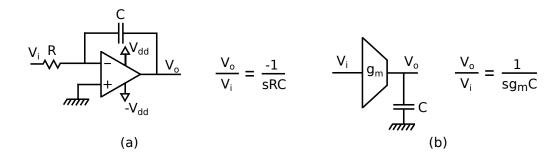

| 2.8  | (a) Opamp-based integrator, and (b) transconductance-based in-                                                                |      |

|      | tegrator                                                                                                                      | 15   |

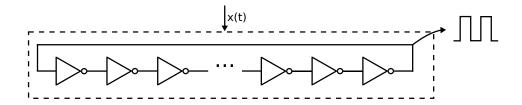

| 2.9  | Conventional diagram of a ring oscillator                                                                                     | 16   |

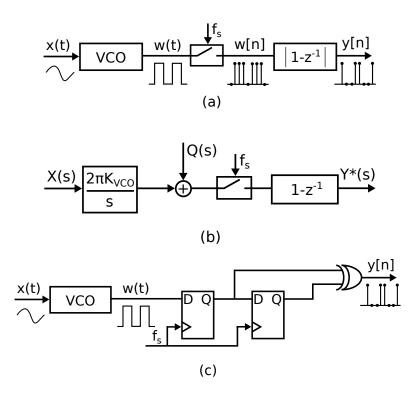

| 2.10 | (a) Open-loop configuration VCO-based ADC, (b) linear model of                                                                |      |

|      | the system, and (c) conventional architecture built with flip-flops                                                           |      |

|      | and XOR gate                                                                                                                  | 17   |

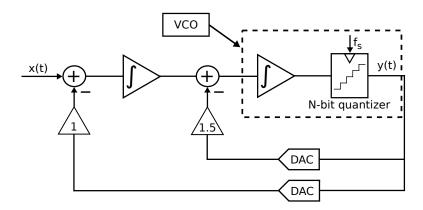

| 2.11 | Second-order continuous-time $\Delta\Sigma$ modulator with a VCO working                                                      |      |

|      | as the last integrator and the quantizer                                                                                      | 18   |

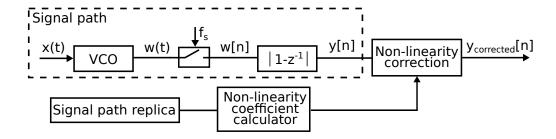

|      | VCO linearity correction by means of digital post-processing                                                                  | 19   |

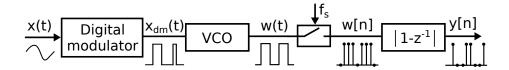

| 2.13 | Using a digital modulator to linearize the VCO                                                                                | 20   |

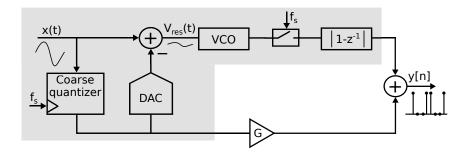

| 2.14 | Feeding the VCO to a low voltage input signal                                                                                 | 21   |

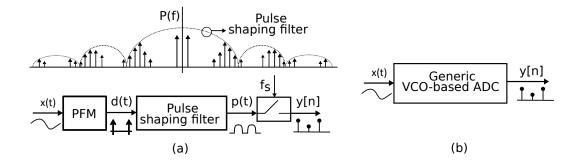

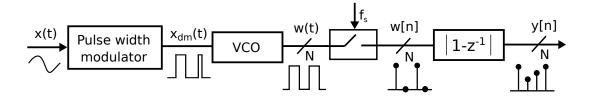

| 3.1  | Approach followed: from the (a) PFM + pulse shaping filter +                                                                  |      |

|      | sampler architecture to a (b) generic order VCO-based ADC struc-                                                              |      |

|      | ture                                                                                                                          | 25   |

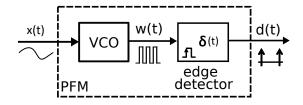

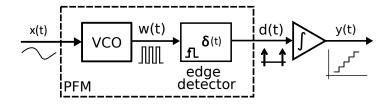

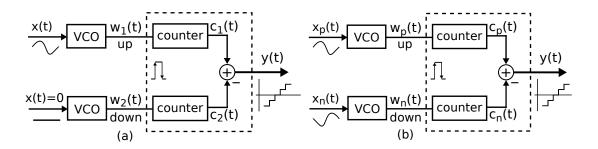

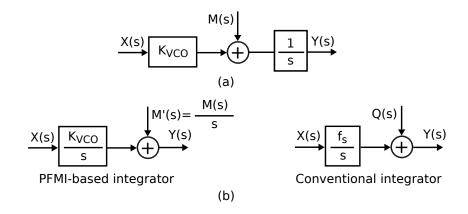

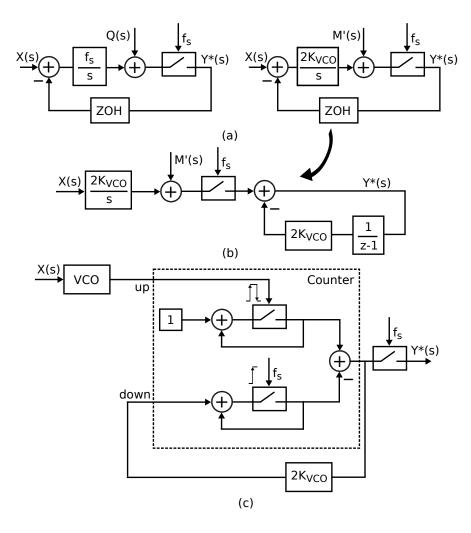

| 3.2  | VCO – PFM equivalence.                                                                                                        | 26   |

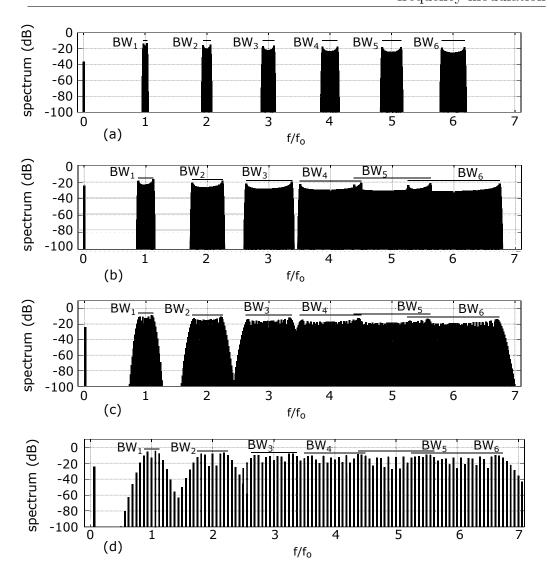

| 3.3  | Calculated spectrum according to (3.4) of the first six sidebands                                                             |      |

|      | for the case of an input signal with (a) a low input frequency $f_x =$                                                        |      |

|      | $f_{\rm o}/1024$ and a small input amplitude $AK_{\rm VCO}=f_{\rm o}/32$ , (b) again for                                      |      |

|      | a low input frequency $f_x = f_o/1024$ but a larger input amplitude                                                           |      |

|      | $AK_{\text{VCO}} = f_{\text{o}}/8$ , (c) for the same input amplitude $AK_{\text{VCO}} = f_{\text{o}}/8$                      |      |

|      | but now an intermediate input frequency $f_x = f_0/64$ and (d) for                                                            |      |

|      | again the same input amplitude $AK_{\text{VCO}} = f_{\text{o}}/8$ but now a rela-                                             | 00   |

|      | tively high input frequency $f = f/16$                                                                                        | -')× |

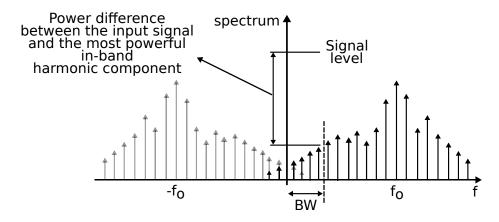

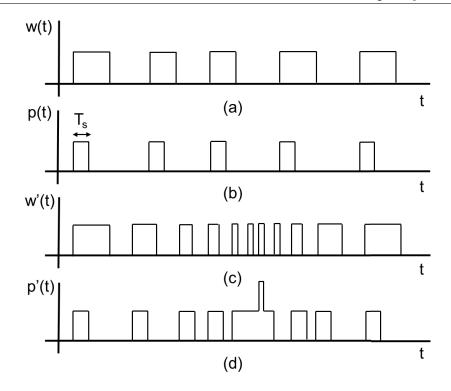

| 3.4  | tively high input frequency $f_x = f_o/16 \dots \dots$<br>Sketch of the signal integrity degradation due to spurious tones of | 28   |

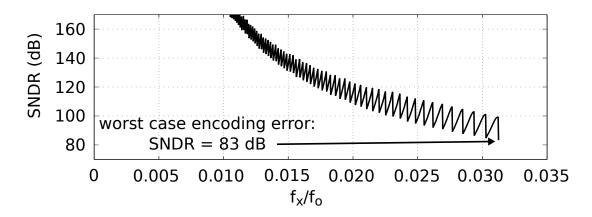

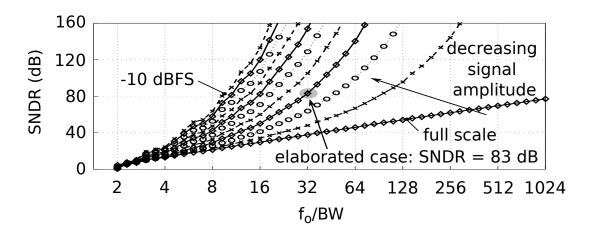

| 3.5  | SNDR due to to the encoding error calculated according to Eq. (3.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | vs. the input signal frequency $f_x$ for the case of an in input am-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | plitude of -3 dB <sub>FS</sub> for a fixed bandwidth equal to $f_{\rm o}/32$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

| 3.6  | Limiting SNDR for the case of an in band input tone vs the ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | $f_{\rm o}/BW$ for different values of the input signal magnitude (ranging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | from full scale to -10 dBFS in steps of 1 dB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

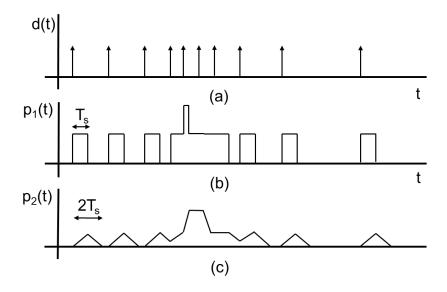

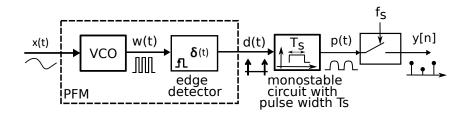

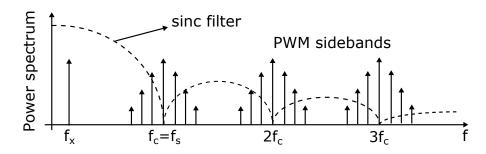

| 3.7  | Generic structure for a potential VCO-based ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32 |

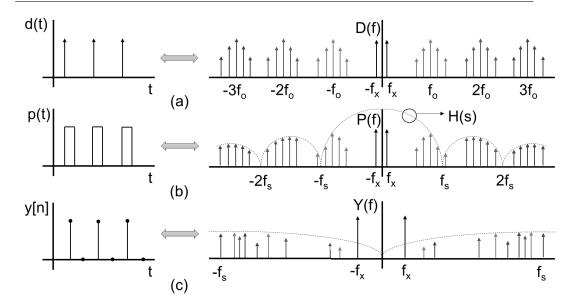

| 3.8  | Illustration of the effect of the lowpass filter $H(s)$ on the aliasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | of the modulation sidebands for the case of a single tone sinusoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | input signal, with a sketch of the time domain as well as the fre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | quency domain signals for (a) the signal $d(t)$ , (b) the filtered signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | p(t) and (c) the sampled overall output signal $y[n]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33 |

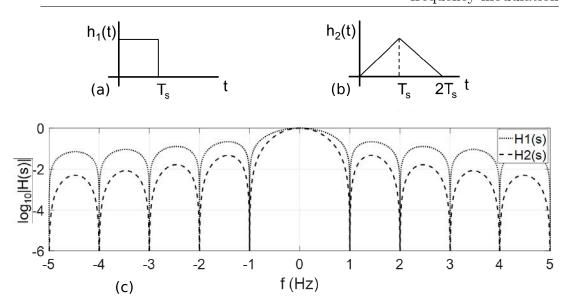

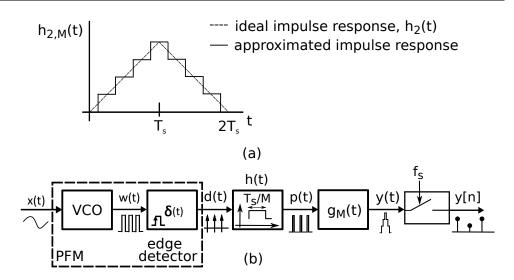

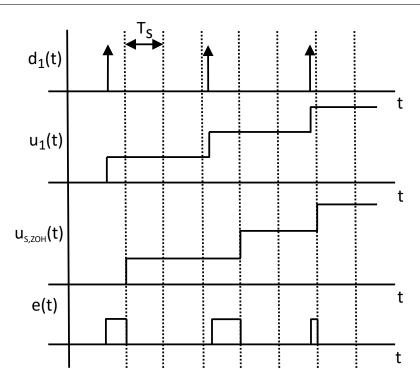

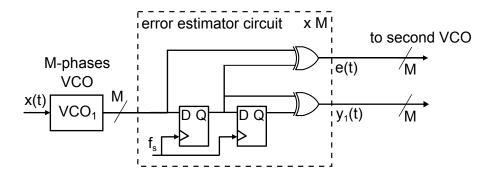

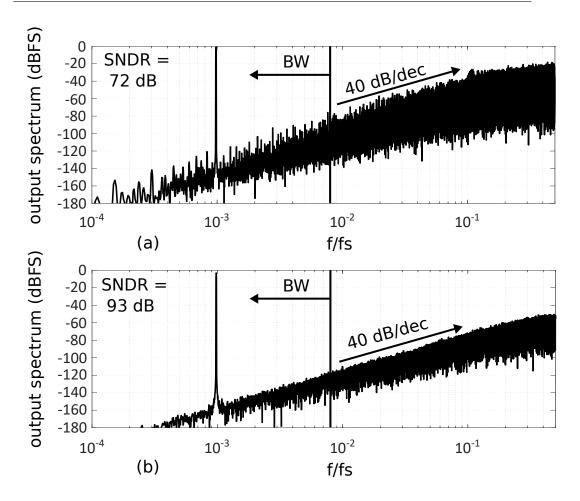

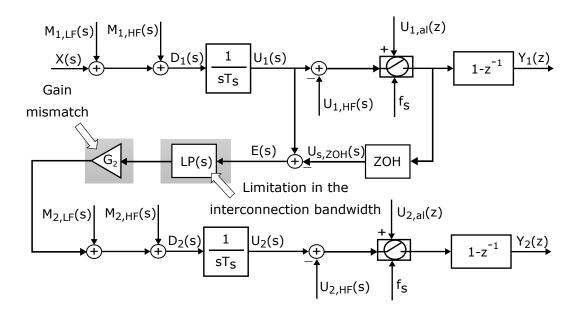

| 3.9  | Time domain impulse response of (a) the first order shaping pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | and and (b) the second order shaping pulse with (c) their respective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | frequency response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

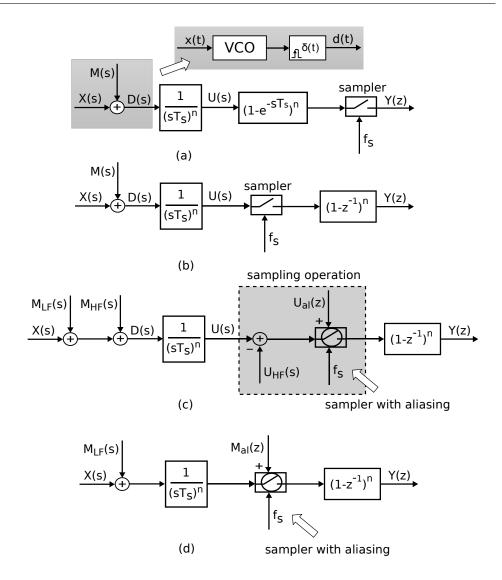

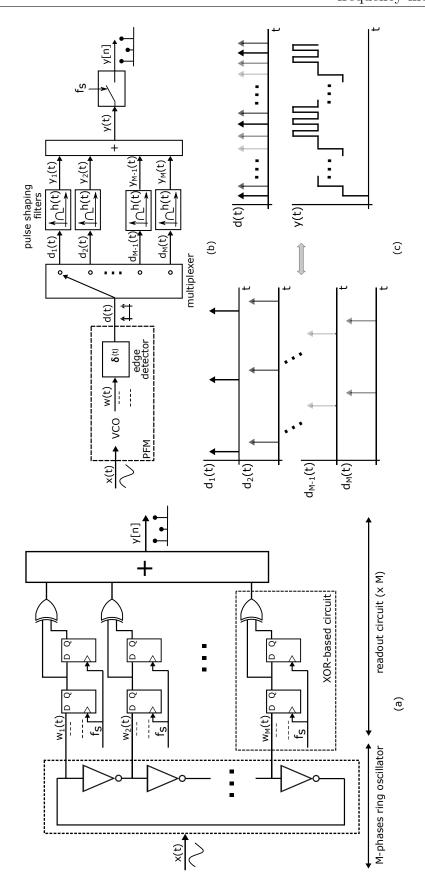

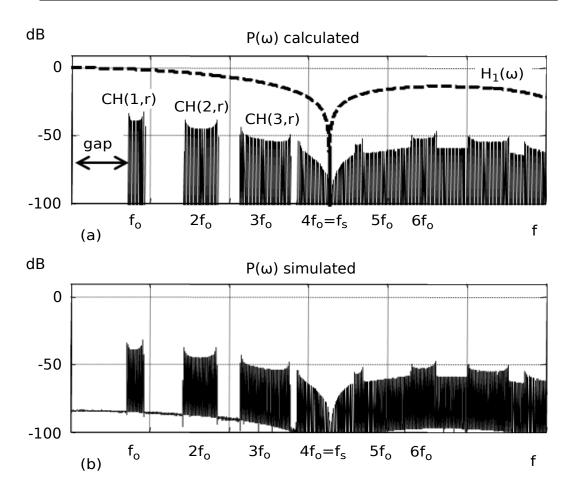

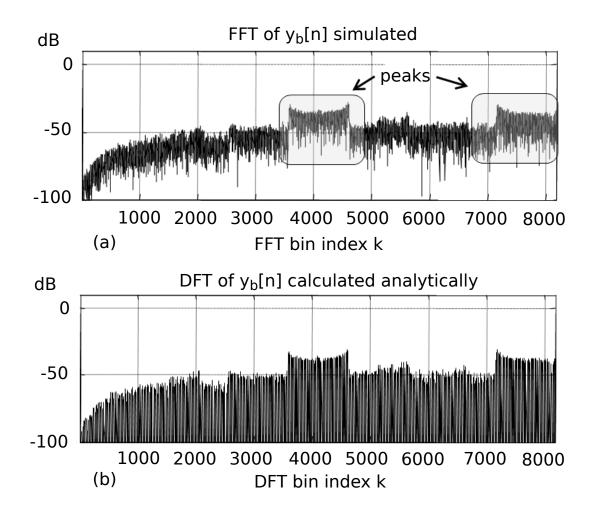

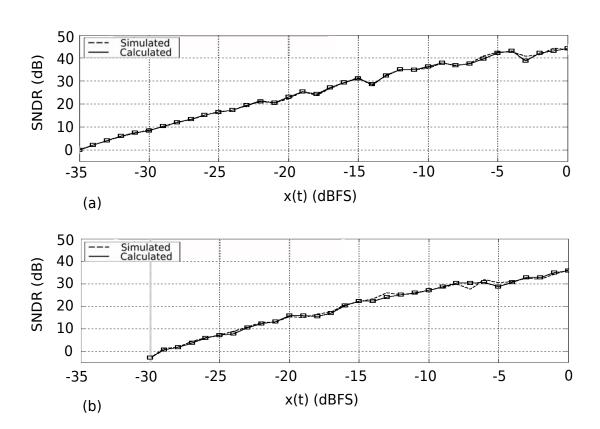

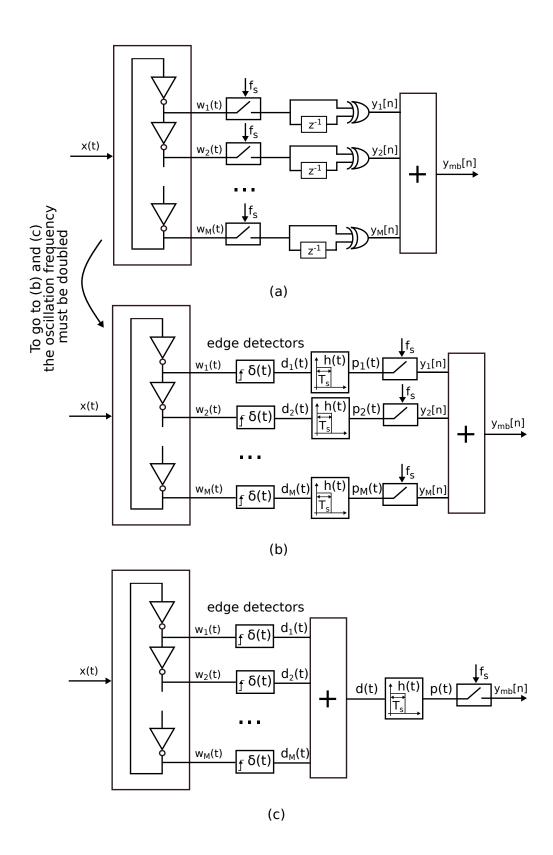

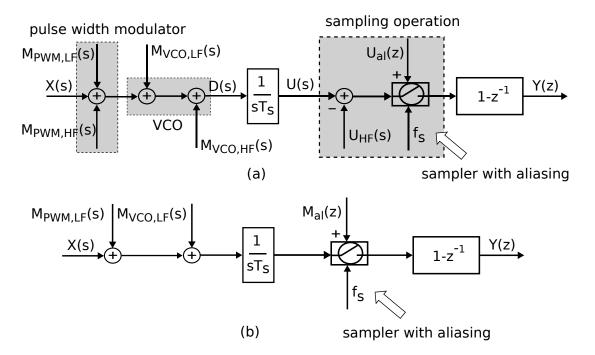

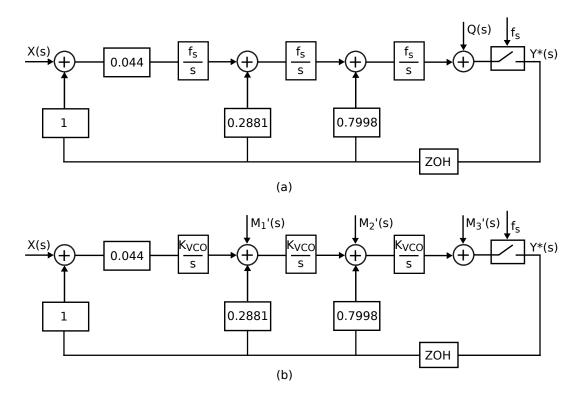

| 3.10 | Explanation of the spectral shaping in our generic VCO-ADC (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | generic VCO-ADC, (b) equivalent structure of our generic VCO-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | ADC, (c) equivalent structure with explicit indication of the errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | in the sampling process, (d) final equivalent model with the overall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | I/O behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

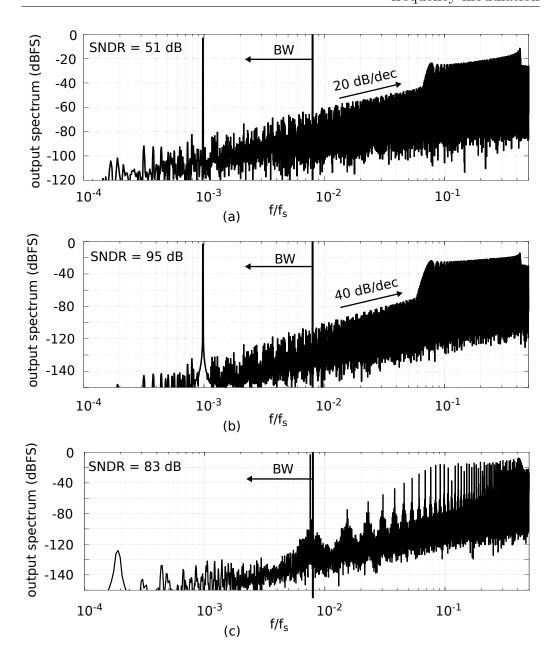

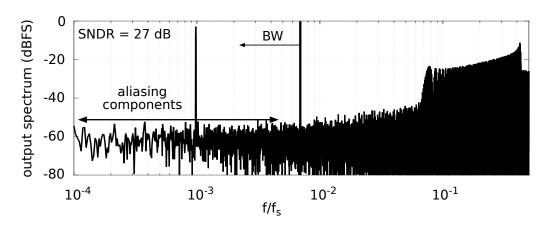

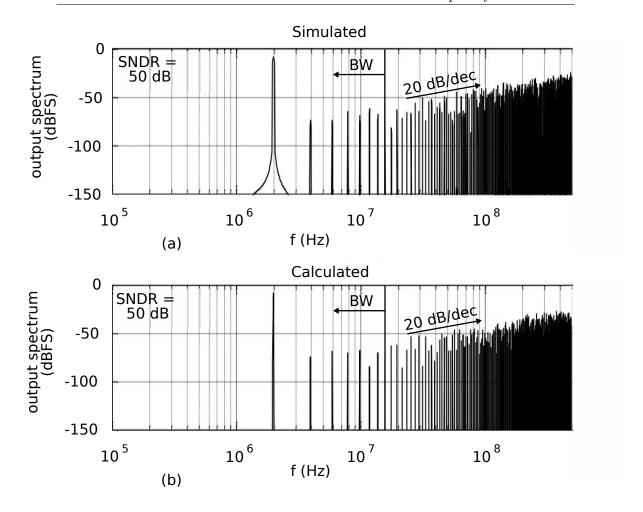

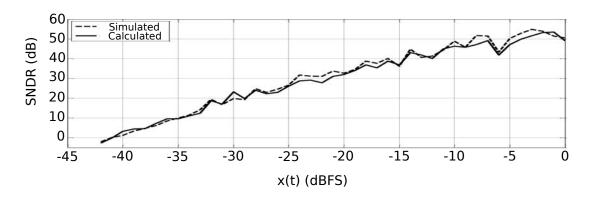

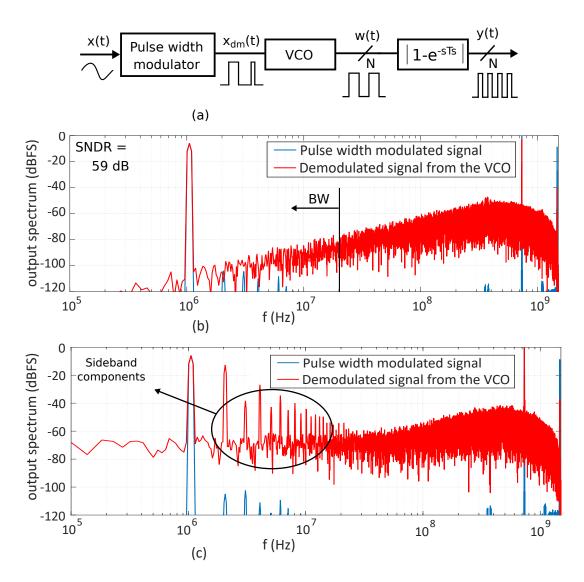

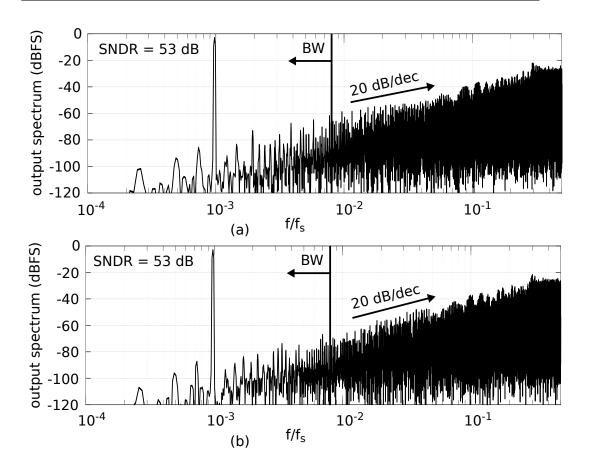

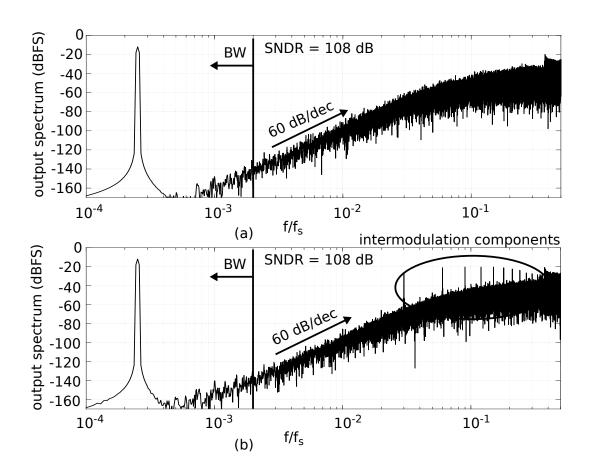

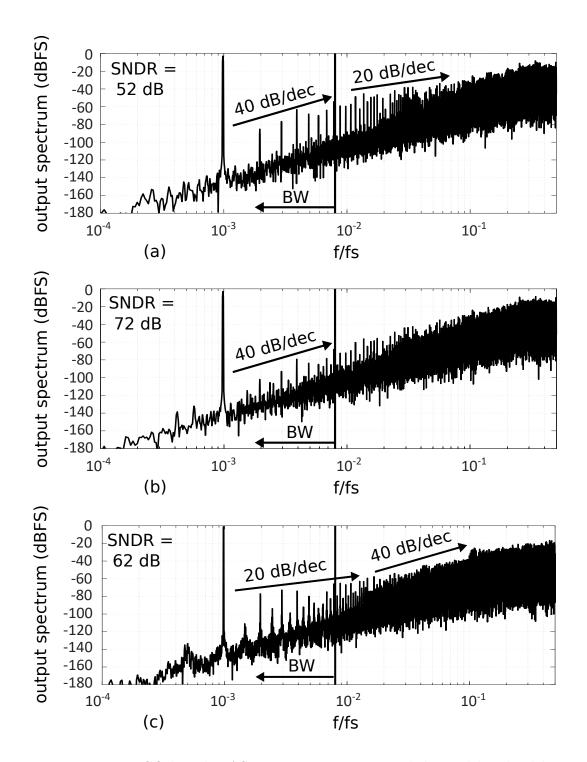

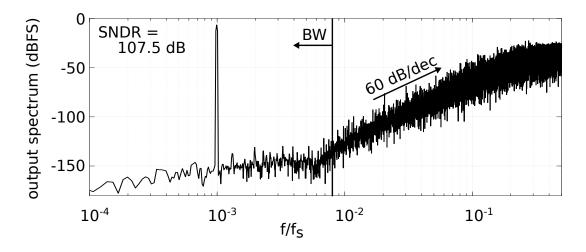

| 3.11 | Output spectra of the generic VCO-ADC architecture illustrating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | the spectral shaping of the aliasing error for the case of: (a) a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | first-order sinc filter, (b) a second-order sinc filter, and (c) a second-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | order sinc filter where the input frequency $f_x$ is chosen such that                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | the SNDR is limited to 83 dB by the fundamental PFM encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | error (i.e. $f_x \approx BW$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36 |