## University of Massachusetts Amherst

## ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

March 2020

# TRUSTWORTHY SYSTEMS AND PROTOCOLS FOR THE INTERNET OF THINGS

Arman Pouraghily University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Computer and Systems Architecture Commons, Hardware Systems Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Pouraghily, Arman, "TRUSTWORTHY SYSTEMS AND PROTOCOLS FOR THE INTERNET OF THINGS" (2020). *Doctoral Dissertations*. 1864.

https://scholarworks.umass.edu/dissertations\_2/1864

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# TRUSTWORTHY SYSTEMS AND PROTOCOLS FOR THE INTERNET OF THINGS

A Dissertation Presented

by

ARMAN POURAGHILY

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

February 2020

Department of Electrical and Computer Engineering

© Copyright by Arman Pouraghily 2020 All Rights Reserved

# TRUSTWORTHY SYSTEMS AND PROTOCOLS FOR THE INTERNET OF THINGS

A Dissertation Presented by  $\label{eq:decomposition} \operatorname{ARMAN\ POURAGHILY}$

| Approved as to style and content by: |   |  |

|--------------------------------------|---|--|

|                                      | _ |  |

| Tilman Wolf, Chair                   | - |  |

|                                      | _ |  |

| Wayne Burleson, Member               | - |  |

|                                      | _ |  |

| Brian Levine, Member                 |   |  |

|                                      | _ |  |

| Russell Tessier, Member              |   |  |

Christopher Hollot, Department Head Department of Electrical and Computer Engineering

## **DEDICATION**

To my mother and my father, Afsane and Akbar.

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my deepest appreciation to my advisor Prof. Tilman Wolf. Thank you for your support and mentorship throughout my entire journey as a Ph.D. student. I learned a lot from you both actively following your advice and passively watching you and learning from you as a role model in my personal and professional life.

I have to also thank professor Russell Tessier with whom I had the pleasure of working on multiple research projects. His knowledge and expertise in the subject matter, as well as his support and guidance all along the path of doing research, were always helpful, especially during the time of facing new challenges in our projects.

This work, without any doubts, would never be possible without the help and contributions of my colleagues and good friends at the Department of ECE. Firstly, I would like to thank Georgios Provelengios, one of the most knowledgable and most humble people I have ever had the opportunity of working with. We had a very successful collaboration only on one project but his knowledge and expertise were always helping me while working on this dissertation. I should also thank Tedy Thomas and Kekai Hu for their contributions and help in the earlier stages of this work.

I also had the pleasure of having wonderful teachers during my Ph.D. from whom I learned a lot. Without them, I would never be the person I am today and obviously, their influence is apparent in my work. It is a pleasure for me to thank Professors Maciej Ciesielski, Csaba Andras Moritz, Wayne Burleson, David Irwin, Michael Zink, and Brian Levine.

I also wish to thank Altera Corporation for the donation of the Quartus II software and DE4 board.

The work presented in this dissertation was also supported by National Science Foundation under Grant Numbers 1115999, 1617458, and 1551444.

### ABSTRACT

## TRUSTWORTHY SYSTEMS AND PROTOCOLS FOR THE INTERNET OF THINGS

FEBRUARY 2020

ARMAN POURAGHILY

B.Sc., UNIVERSITY OF TEHRAN

M.Sc., UNIVERSITY OF TEHRAN

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Tilman Wolf

Processor-based embedded systems are integrated into many aspects of everyday life such as industrial control, automotive systems, healthcare, the Internet of Things, etc. As Moore's law progresses, these embedded systems have moved from simple microcontrollers to full-scale embedded computing systems with multiple processor cores and operating systems support. At the same time, the security of these devices has also become a key concern.

Our main focus in this work is the security and privacy of the embedded systems used in IoT systems. In the first part of this work, we take a look at the security of embedded systems from a hardware point of view. We describe why we believe current security approaches fall short when it comes to securing modern embedded processors. We propose our hardware monitoring solution and expand it to cover a variety of embedded systems with different architectural specifications and applications.

vii

In the second part, we shift our focus from hardware to software and protocols involved in securing IoT systems and maintaining the privacy of the data they exchange. We argue why conventional financial mechanisms cannot be applied to this context when trying to monetize data sharing. We propose a financial mechanism based on blockchain technology and demonstrate how it can replace conventional methods. We discuss how the high processing demand of such protocols hinders widespread adoption on different IoT systems, mostly ones based on low-end embedded processors. To eliminate that barrier, we propose a novel, lightweight payment verification protocol that uses a hybrid IoT ecosystem based on low-end and mid-range embedded systems that can be horizontally integrated with other ecosystems and exchange data and assets with monetary values such as cryptocurrencies.

The last part of this work is the further expansion of the aforementioned hardware monitoring approach to enable it to secure high-end embedded systems. Using this new hardware monitoring system, we build a prototype IoT system that runs our proposed lightweight payment verification protocol to exchange data and money. By evaluating this system, we illustrate how our hardware and software approaches can be complementary to each other to safeguard IoT devices against remote attacks.

## TABLE OF CONTENTS

|              |                   |                                  | F                                                           | Page     |

|--------------|-------------------|----------------------------------|-------------------------------------------------------------|----------|

| A            | CKN               | OWL                              | EDGMENTS                                                    | <b>v</b> |

| $\mathbf{A}$ | BST:              | RACT                             | '                                                           | . vii    |

| LI           | ST (              | OF TA                            | BLES                                                        | . xiii   |

| LI           | ST (              | OF FIG                           | GURES                                                       | . xiv    |

|              |                   |                                  |                                                             |          |

| Cl           | HAP               | TER                              |                                                             |          |

| 1.           | INT               | ROD                              | UCTION                                                      | 1        |

|              | 1.1<br>1.2<br>1.3 | Horizo                           | vare Monitoring In Embedded Systems  ontally Integrated IoT | 5        |

| 2.           | WC                | RKLO                             | DAD MONITORING IN EMBEDDED SYSTEMS                          | 9        |

|              | 2.1<br>2.2        |                                  | ed Work                                                     |          |

|              |                   | 2.2.1<br>2.2.2                   | Secure Processing with Hardware Monitors                    |          |

|              |                   |                                  | 2.2.2.1 Security Requirements                               |          |

|              | 2.3               | Monit                            | for Design                                                  | 16       |

|              |                   | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | Task Management in the Operating System                     | 17<br>19 |

|              | 2.4               | Protot                           | type Implementation                                         | 22       |

|    |            | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5 | Monitor<br>Attack I<br>Monitor                      | Setup                                                               | 23<br>25       |

|----|------------|-------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------|----------------|

|    | 2.5        | Summ                                      |                                                     | Conclusions                                                         |                |

| 3. |            |                                           |                                                     | ULNERABILITIES IN THE OPERATING                                     | 20             |

|    | 3.1        |                                           |                                                     | toring in Low-End IoT Devices                                       |                |

|    |            | 3.1.1<br>3.1.2                            |                                                     | Workand Security Model                                              |                |

|    |            |                                           | 3.1.2.1<br>3.1.2.2<br>3.1.2.3                       | Monitoring Graph Construction                                       | 34             |

|    |            | 3.1.3                                     | Monitor                                             | Design                                                              | 36             |

|    |            |                                           | 3.1.3.1<br>3.1.3.2<br>3.1.3.3<br>3.1.3.4            | Operating System Task Management Multi-Task Hardware Monitor System | 38 $39$        |

|    |            | 3.1.4                                     | Prototyp                                            | pe Implementation                                                   | 41             |

|    |            |                                           | 3.1.4.1<br>3.1.4.2<br>3.1.4.3<br>3.1.4.4<br>3.1.4.5 | System Setup and Attack Scenario                                    | 42<br>42<br>43 |

|    | 3.2<br>3.3 |                                           |                                                     | toring in Mid-Range IoT Devices                                     |                |

| 4. | ]          | FOR B                                     | LOCKC                                               | T PAYMENT VERIFICATION PROTOCOL<br>HAIN TRANSACTIONS ON IOT         | 47             |

|    | 4.1<br>4.2 |                                           |                                                     | egrated IoT                                                         |                |

|    |            | 421                                       | The Nee                                             | d for Horizontal Integration                                        | 52             |

|    |            | 4.2.2                   | Economic Relationships and Systems                                                                                                             | 52 |

|----|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 4.3        | Currer                  | nt Blockchain-Based Solution                                                                                                                   | 53 |

|    |            | 4.3.1                   | Operation                                                                                                                                      | 53 |

|    |            |                         | 4.3.1.1Setting Up The Joint Account4.3.1.2Moving Funds4.3.1.3Closing the Account                                                               | 56 |

|    |            | 4.3.2                   | Drawbacks                                                                                                                                      | 57 |

|    | 4.4        | The T                   | Cicket-Based Verification Protocol                                                                                                             | 59 |

|    |            | 4.4.1<br>4.4.2<br>4.4.3 | Blockchain-Based and Blockchain-Agnostic Operations Separation of Contract Manager and Transaction Verifier Transactions using Tickets in TBVP | 59 |

|    | 4.5        | Imple                   | mentation and Evaluation                                                                                                                       | 62 |

|    |            | 4.5.1<br>4.5.2          | Experiment 1: Sharing Sensor Data                                                                                                              |    |

|    | 4.6        | Summ                    | ary and Conclusion                                                                                                                             | 64 |

| 5. | 7          | VALUI                   | NG THE EXCHANGE OF DATA AND MONETARY ES ON MODERN IOT DEVICES: A MULTI-LAYER OACH                                                              | 66 |

|    | 5.1<br>5.2 | Imple                   | ed Work                                                                                                                                        |    |

|    | 5.3        |                         | oring the TBVP on a Single-core Processor Running Linux                                                                                        |    |

|    |            | 5.3.1<br>5.3.2          | Attacks on Economic Transaction Protocols                                                                                                      |    |

|    |            |                         | 5.3.2.1 Security Vulnerabilities in Embedded Systems                                                                                           | 73 |

|    |            | 5.3.3                   | Hardware Monitor for IoT Protocols                                                                                                             | 74 |

|    |            |                         | 5.3.3.1 System Architecture                                                                                                                    |    |

|    |            |                         |                                                                                                                                                |    |

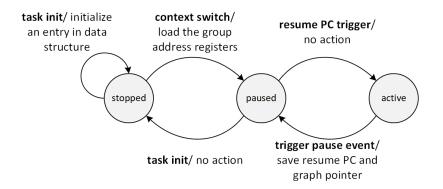

|    |            | 5.3.4                   | Hardware Monitor Data Structure and State Transition                                                                                           | 77 |

|        | 5.3.5 | Attack    | Scenario: Stack Smashing Attack                                             | 80   |

|--------|-------|-----------|-----------------------------------------------------------------------------|------|

|        | 5.3.6 | Attack    | Detection and Recovery                                                      | 81   |

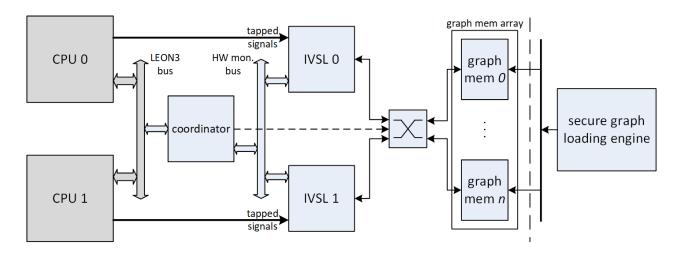

| 5.4    | Monit | oring the | TBVP on a Multi-core Processor                                              | 83   |

|        | 5.4.1 | System    | Architecture                                                                | 84   |

|        | 5.4.2 | Hardwa    | re Monitor Operation and Data Structure                                     | 85   |

|        |       | 5.4.2.1   | Task Initiation                                                             | 85   |

|        |       | 5.4.2.2   | Context Switch                                                              | 86   |

|        |       | 5.4.2.3   | Process Migration                                                           | 86   |

|        | 5.4.3 | Attack    | Detection and Recovery                                                      | 87   |

|        | 5.4.4 | Implem    | entation and Evaluation                                                     | 88   |

|        |       | 5.4.4.1   | Normal Execution on One Core                                                | 88   |

|        |       | 5.4.4.2   | Continuous Monitoring In Presence of Task                                   |      |

|        |       |           | Migration                                                                   | 89   |

|        |       | 5.4.4.3   | Attack Detection and Recovery                                               | 91   |

|        |       | 5.4.4.4   | Resource Utilization and Hardware Overhead of the Proposed Hardware Monitor | 91   |

|        |       | 5.4.4.5   | Performance Overhead                                                        |      |

| 6. CO  | NCLU  | SION A    | ND FUTURE DIRECTIONS                                                        | . 95 |

| DIDI I | OCR A | PHV       |                                                                             | ga   |

# LIST OF TABLES

| Table | Page                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1   | Resource use and power consumption on a Stratix IV FPGA 26                                                                                         |

| 3.1   | Qualitative comparison to related work                                                                                                             |

| 3.2   | Monitoring graph sizes for operating system and applications                                                                                       |

| 3.3   | Resource use on a Stratix IV FPGA                                                                                                                  |

| 4.1   | Number of Operations per Second Performed by Each Device in Different Roles in $\mu$ Raiden versus TBVP                                            |

| 5.1   | Related Work on Hardware Monitoring                                                                                                                |

| 5.2   | Data structure used by hardware monitor                                                                                                            |

| 5.3   | Data structure used by the coordinator                                                                                                             |

| 5.4   | FPGA resources consumed by different entities93                                                                                                    |

| 5.5   | Time spent in the user application versus the kernel when running different workloads for different system configurations. (values are in seconds) |

## LIST OF FIGURES

| Page                                                                                                                                                                                                                                                                              | Figure |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| IoT architecture to enable horizontal integration                                                                                                                                                                                                                                 | 1.1    |

| System architecture of Multi-Task Hardware Monitor System                                                                                                                                                                                                                         | 2.1    |

| Detailed view of multi-context monitoring system                                                                                                                                                                                                                                  | 2.2    |

| Console display during stack smashing23                                                                                                                                                                                                                                           | 2.3    |

| SignalTap waveforms showing the trigger for monitor context switch (Operation = 0x2), monitor switch finished (Done), and monitor restart monitoring when CPU ready (Enable)                                                                                                      | 2.4    |

| SignalTap waveforms showing the operations for monitor process creation (Operation = 0x1) and monitor update finished (Done)                                                                                                                                                      | 2.5    |

| SignalTap waveforms showing the successful identification of a stack smashing attack. Instruction hash values are checked against expected values stored in the monitor graph. When a mismatch occurs, a recovery signal is triggered indicating the process should be terminated | 2.6    |

| System architecture of embedded hardware monitoring system that can validate correct execution of applications and operating system                                                                                                                                               | 3.1    |

| Detailed view of multi-context monitoring system                                                                                                                                                                                                                                  | 3.2    |

| Context switch interactions between processor and monitor                                                                                                                                                                                                                         | 3.3    |

| Attack on processor system, which is detected by hardware monitor                                                                                                                                                                                                                 | 3.4    |

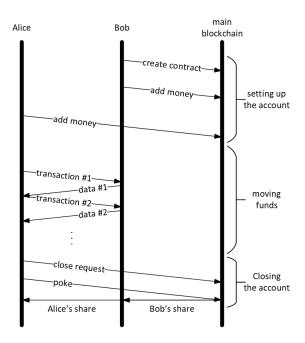

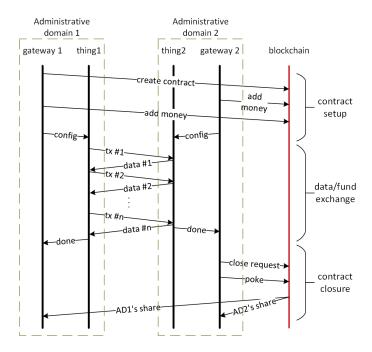

| Space-Time diagram for money and data exchange through payment channel as proposed by Poon et al. [54]                                                                                                                                                                            | 4.1    |

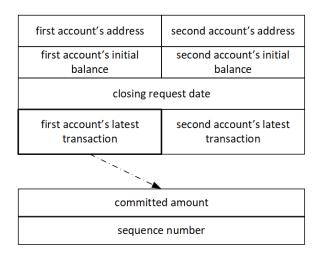

| 4.2  | Data structure used in the smart contract                                                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

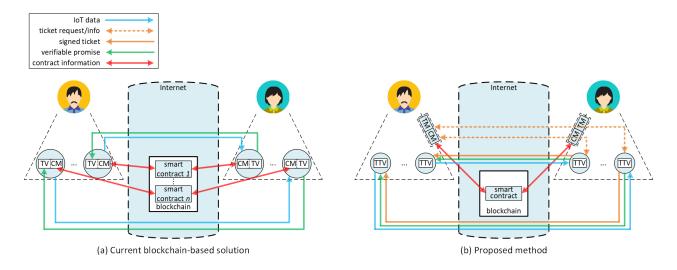

| 4.3  | Flow of information and money in (a) current blockchain-based solutions versus (b) our proposed Ticket-Based Verification Protocol              |

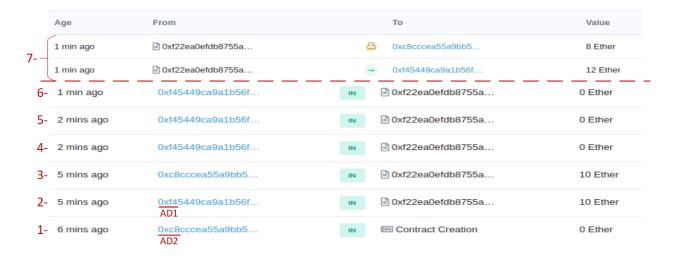

| 4.4  | Blockchain transaction details for experiment 1                                                                                                 |

| 5.1  | Space-Time diagram showing contract setup, data/economic-value exchange, and contract closure phases                                            |

| 5.2  | Blockchain transactions for selling 200 data samples                                                                                            |

| 5.3  | Proposed IoT system architecture with the monitoring system                                                                                     |

| 5.4  | Different states of the hardware monitor and transitions between them                                                                           |

| 5.5  | System console after being hijacked81                                                                                                           |

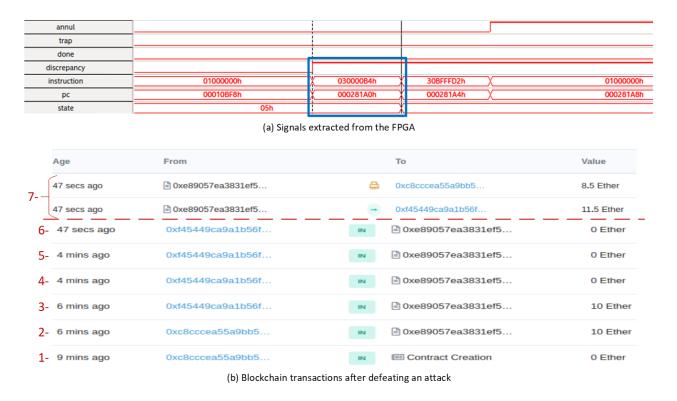

| 5.6  | (a) Signals extracted from the FPGA board showing the detection of the attack. (b) Resulting blockchain transactions after detecting the attack |

| 5.7  | Proposed system architecture for a multi-core LEON3 processor augmented with a hardware monitor84                                               |

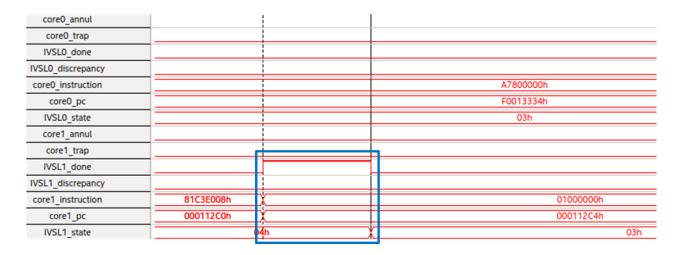

| 5.8  | Waveform extracted from the FPGA showing the Completion of a task on core 1                                                                     |

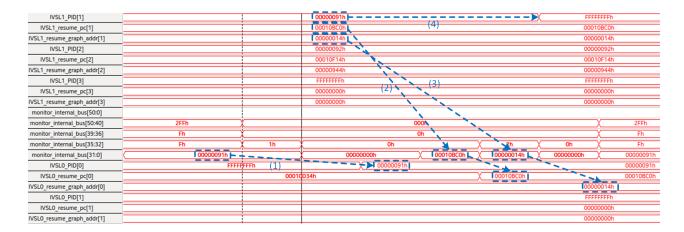

| 5.9  | Waveform extracted from the FPGA showing the successful transfer of monitoring state across two IVSLs                                           |

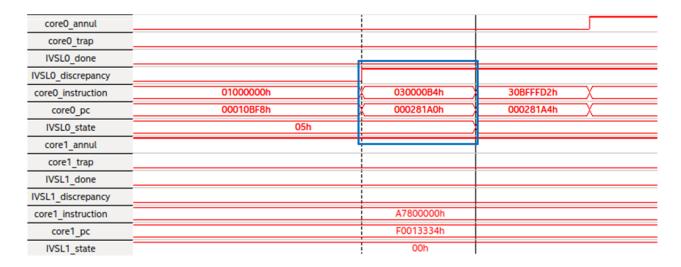

| 5.10 | Waveform extracted from the FPGA showing the detection of an attack on core 0                                                                   |

## CHAPTER 1

### INTRODUCTION

Over the past two decades, the idea of Cyber-Physical Systems (CPS) and their use in a broader network, known as the Internet of Things (IoT), has attracted a lot of attention as the technological foundation to address many important societal problems relating to the environment, health care, transportation, etc. [27,60,65,67, 80]. Today, we can see traces of IoT devices in many different aspects of our daily lives. According to Gartner, the number of IoT devices is expected to exceed 25 billion by 2020 [25], which shows how fast this new technology is finding its uses in different applications.

Fundamentally, IoT systems interconnect three types of components: sensors that detect or measure a physical property; computation that receives sensor data for processing and making control decisions; and actuators that act in the physical world in response. These three steps of sensing, computing, and acting can vary vastly in their implementation based on the IoT application and use case.

As the application of IoT systems become more prevalent, new challenges and concerns around their proper operation arise. Among those concerns, we can point to the privacy and integrity of the data throughout the whole cycle, from the sensor to the actuator, and the security of all the devices involved in the cycle with regard to potential external adversaries. In this work, our main focus is on enhancing the security of IoT systems and facilitating secure transactions between them while meeting the privacy requirements of the applications in which they are being used.

Since embedded systems are at the very core of sensing and actuation parts of any IoT system (sometimes even in the computation part), the security and privacy of the whole IoT system relies on the security and privacy of the underlying embedded systems. For that reason, our main focus throughout this work is on embedded systems and challenges around them.

In the first part of this work, we focus on enhancing the security of embedded systems as the underlying processing platform for IoT devices. We discuss the challenges of securing these devices and how to overcome those challenges.

The second part of this work is about the algorithms used at the software level and protocol level to ensure security and privacy of the information being exchanged between different IoT devices. In this part, we describe the idea of horizontal integration, which tries to facilitate the data exchange between different IoT ecosystems to pave the way for further use of IoT solutions in different new applications. As the basis of the idea of horizontal integration is incentivizing data sharing by adding monetary values to the data, having a robust and trustworthy financial mechanism is crucial. We then explain why we believe blockchain technology is a suitable platform for those financial transactions and how the current state of the art methods can be used in that model. At the same time, we discuss how those discussed methods are only applicable to mid-range and high-end embedded devices. As a big portion of IoT devices is based on low-end embedded devices, these approaches come short serving this group of IoT devices. We finally propose our lightweight payment verification protocol, which is based on blockchain technology to make it possible for all of the IoT devices to participate in horizontal integration.

The third part of this work is on joining the two approaches described in the first and second part of the work. In this part, first, we discuss how we plan to expand our hardware monitoring system to be applicable to yet another group of embedded systems which is the high-end embedded systems. We then describe how a secure IoT ecosystem can be built using a variety of embedded systems including a high-end, a mid-range, and a low-end IoT device, protected by our hardware monitoring approach and running our proposed lightweight payment verification protocol.

## 1.1 Hardware Monitoring In Embedded Systems

Embedded systems by definition are computing systems that are used in devices with main a functionality other than just computing. The term is usually used as a counterpart to general purpose computers, which are designed solely for computational purposes. Architecturally, embedded processors, which are the core processing elements of embedded systems, are no different than their general purpose counterparts. For example, Motorola 68000 [68], which was introduced in 1979 by Motorola Semiconductors [47], was designed as a high-end microprocessor for computational purposes. However, less than a decade after its introduction, in the early 1980s, it was begin used as an embedded processor inside automobile engines by car designers.

What happened to Motorola 68000 is a good example of how embedded systems' technology follows high performance computing. As the technology matures, processing power can be realized at a lower cost. This cost can be in terms of power consumption, area consumption, and actual monetary cost of production. As in the context of general purpose computers, security has been an active area of research since even before the actual processors came around and since embedded systems are following the footsteps are general purpose computers, one might think why the security of embedded systems should be any different from their predecessors? Why not apply the same techniques that are used in general purpose processors to embedded systems?

The answer to those questions is in the way embedded systems are being used. Although architecturally today's embedded systems are the same as yesterday's general purpose processors, they are different in the tasks they are fulfilling and the applications in which they are being used. Embedded systems are usually designed on a tight budget. This tight budget usually translates to limited cost, limited energy consumption (in battery operated devices), and limited processing power. These limitations make software-based solutions such as virus detection software and intrusion detection systems which are quite popular solutions in the context general purpose processor, very inefficient for embedded systems.

Another differentiating factor between embedded systems and general purpose computers is the use of them in real-time applications. The real-time nature of those applications paired with the limited processing resources available in the system makes the uncertainty imposed by the software solutions intolerable for these applications. Finally, in some applications such as IoT, the systems are deployed in remote environments which makes accessing them harder. This remote environment is not always a safe environment and in cases might be even hostile. The limited access to the devices and their higher exposure to adversarial parties make software-based solutions which are inherently reactive even less suitable for this type of embedded systems.

An alternative to software-based security solutions is hardware-based solutions. Hardware-based solutions vary from circuit level to architecture and system level. In this work, our focus is on hardware monitors which are hardware solutions at the system level. Hardware monitors are dedicated hardware modules which are located on the same system as the processor. They ideally do not require any changes to the architecture of the CPU and only require certain information extracted from the datapath of the processor. The main role of these hardware modules is to monitor the execution of the application on the processor core and compare that runtime behavior against a golden model of the application. The golden model which is extracted from the source of the application needs to be loaded into the hardware monitor before the application starts to run on the CPU. In the first part of this work, we discuss the details of hardware monitors and why we believe that hardware monitors are

more suitable security solutions than software-based approaches in the context of embedded systems. We then propose our novel hardware monitoring approach which expands the applicability of current hardware monitoring solutions to a wider range of embedded systems including more modern architectures.

## 1.2 Horizontally Integrated IoT

Deployment of IoT solutions can be expensive since sensors, actuators, and computation components are necessary. Traditionally, each application uses its own components. Switching from dedicated computation infrastructure to cloud-based computation platforms can reduce some of this cost. However, each application still needs to setup and maintain its own set of sensors and actuators in the environment. An alternative approach, which can make this investment more cost effective, is to share that platform with other IoT applications. To facilitate that resource sharing, the idea of horizontal integration of IoT components was proposed by Wolf et al. [78,79].

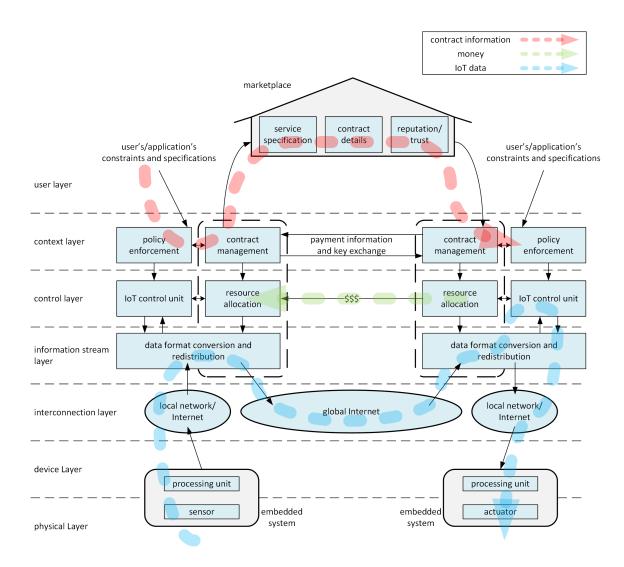

The system architecture we use in this work is based on the guidelines set in horizontal integrated IoT and is shown in Figure 1.1. The structure aligns with the layered IoT architecture presented by Wolf et al. in [78]. On the top layer, we have the users or applications controlling the system. The user/application needs to formulate and enter the constraints and specifications of the required IoT task. Those constraints and specifications include the functionality of the tasks and how much budget is allocated to this specific task (or how much the cost of using each module in the system is).

Below is the context layer. This layer which receives the constraints and specifications from the user level, forms and enforces the system policies. It is in this layer, where the system decides how much of the resources available in the lower layers are needed to perform the task and how much can be spared. We proposed the *contract management* unit in this layer to deal with leasing of extra resources.

Figure 1.1. IoT architecture to enable horizontal integration.

In case the available resources in the system are not sufficient to perform the task, this unit searches the marketplace to find other systems offering those resources. It then contacts those systems and leases those resources for the period of time they are needed. It is necessary for this unit to be tightly coupled with the *policy enforcement* unit to know about the specifications of the resources needed, the budget dedicated to acquiring them, and finally, about the time period those resources are needed for.

Another role of the contract management unit is to offer the excessive resources the system owns on the market. This role also requires a very close relationship to the policy enforcement unit as the contract management unit needs to exactly know which resources are idle for what time period and what the price of each resource should be in the market.

When acquiring extra resources, the contract management unit of the lessee inquires about the systems offering those resources on the marketplace. It then selects the one which meets the criteria set by the policy enforcement unit. The contract management unit then directly contacts its counterpart in the lessor system to exchange the information needed to establish a secure connection and also the account information to make future payments. The next step in leasing resources from outside systems is to pass this information to the *resource allocation* unit in the layer below.

Proposed resource allocation unit is co-located with the *IoT control* unit in the control layer. It receives the contract information from the contract management unit and coordinates with the IoT control unit to dedicate the resources accordingly. The resource allocation unit also sets the data format conversion parameters in the layer below and sets up the paths the data from each resource should traverse. This could be a path from the global Internet to the control unit in case of using external resources or it could be a path from the local resources to the information stream layer of another system in case of renting out internal resources. The resource allocation unit is also responsible for sending and receiving money once the contract is formed. By doing so, it makes sure the information channel formed between the two systems is up and running.

## 1.3 Organization and Contribution

The rest of this work is organized as follows:

In Chapter 2, we discuss the idea of hardware monitoring and challenges of securing embedded systems using hardware monitors in more details. We then describe how the current hardware monitoring solutions have fallen behind of the technology used in modern embedded systems and in this chapter we take the first step to bridge this gap by introducing our novel hardware monitoring system which can support multiple tasks running on top of a simple realtime operating system.

In Chapter 3, we show how operating systems which previously assumed to be secure entities can be vulnerable against remote attacks and be exploited. Then we show how our monitoring method proposed in Chapter 2 can be further extended to protect the whole system including the operating system itself. It is in this chapter that we discuss how middle-range embedded systems vary from low-end systems in terms of the processor architecture as well as the software running on top of them including the operating systems and how that difference impact the design of our hardware monitoring solution.

In Chapter 4, we shift our focus to horizontal integration of IoT systems and the challenges of securing IoT devices involved in this horizontal integration. In this chapter, we describe how current blockchain technology can be a good fit for this paradigm but at the same time too heavy weight in terms of processing demand to be used in low-end IoT devices. We then propose our lightweight payment verification protocol which is based on Ethereum blockchain technology. We describe how this lightweight protocol can be used even in low-end IoT devices which constitute a big portion of current IoT devices to enables them to horizontally integrate with other IoT systems without jeopardizing their security and privacy.

In Chapter 5, we describe our current plan to further expand our hardware monitoring approach to further cover high-end embedded devices as well as mid-range and low-end ones. We then show how an IoT system can be built using a variety of IoT devices including low-end devices and high-end devices where each of those devices can be secured using the hardware monitor at the hardware level. At the same time, using the protocol proposed in Chapter 4 they can participate in a horizontally integrated IoT ecosystem and securely exchange data and cryptocurrency.

### CHAPTER 2

## WORKLOAD MONITORING IN EMBEDDED SYSTEMS

Embedded processing systems are widely used and are a key technology for control systems, the Internet of Things, personal health monitoring, home automation, and many other application domains. Due to their wide use and the importance of their tasks, embedded systems need to be protected from hacking attacks. With an increasing number of embedded systems being connected to networks, one typical attack vector against embedded systems is through the global Internet.

Many embedded systems are based on general-purpose processing systems that are vulnerable to the same type of attacks as conventional desktop and server computers, albeit for a different set of applications. The National Vulnerability Database (NVD) [50] shows that around 10% of vulnerabilities (6,518 out of 66,399) in systems are related to overflows that can be exploited via a network. Many of these overflows then enable an attacker to execute malicious code. Thus, the first part of our work, which is presented in this chapter and the following chapter, focuses on protecting embedded systems from this important type of attack using a security-enhanced processor.

While desktop and server computers have the processing power to run malware detection software (e.g., virus scanner, intrusion detection system, etc.), embedded systems are typically not able to do so due to resource constraints (e.g., limited power budget, limited processing capacity, etc.). Instead, hardware-based protection mechanisms have been developed, in particular "hardware monitors", which track the operation of the processing system and aim to detect and suppress malicious activity.

A variety of different hardware-based solutions have been proposed to protect embedded processing systems. In general, there have been three shortcomings in existing work:

- Monitoring on systems with complex workloads is based on coarse indicators (e.g., function call sequence [64]). This approach leaves the system vulnerable to attacks that happen between indicators (e.g., within a function call).

- Fine-grained monitoring systems do not support multi-task workloads on operating systems. This constraint limits the applicability of this single-task monitoring to specialized domains (e.g., embedded control systems, network processors, etc.).

- Almost all of the existing work either target the very elementary embedded systems which do not run an operating system or in case of dealing with the embedded systems running an operating system, the OS is treated as a secure and trusted entity. This leaves the modern OS-based embedded systems vulnerable against attacks which target the operating system itself.

To make hardware monitors an effective protection mechanism for attacks on embedded systems in any application domain, it is critical to develop fine-grained monitoring on multi-task embedded systems. In this chapter, we present the design of a hardware monitoring system that coordinates with the task switching dynamics of an operating system to verify every instruction executed by applications. In the next chapter, we shift our focus to the operating system itself and how to address the vulnerabilities within the operating system.

The specific contributions of our work presented in this chapter are:

• Design of a Multi-Task Hardware Monitor System (MTHM) that supports multi-tasking contexts and that operates in sync with an embedded operating system (OS).

- Prototype implementation of a hardware monitoring system on an FPGA-based DE4 board.

- Evaluation of the prototype and a demonstration of system protection from a stack smashing attack.

This security enhancement for embedded processors allows for the simultaneous use of application-specific monitoring information for multiple applications [73]. The remainder of this chapter describes the design, operation, and implementation of our hardware monitoring system in more detail. In Section 2.1 we discuss other security approaches for embedded processors, including monitoring. Section 2.2 provides the security model and operation of our system while Section 2.3 describes the hardware details and protocols involved in task switching using monitoring. Experimental results are presented in Section 2.4. Section 2.5 concludes the chapter.

### 2.1 Related Work

Protection mechanisms for processing systems against code injection attacks are manifold. Network devices, such as firewalls [45] and intrusion-detection systems [46], can block malicious network traffic if packet payloads are not encrypted and if detection rules (e.g., Snort [62]) are updated quickly enough. Programming language extensions can generate code that is not vulnerable [37] if source code is available and can be transformed appropriately. Stack protection mechanisms in program code or in the operating system can defend against some attacks [15]. Memory protection mechanisms that separate instruction and data memory (e.g., Harvard architecture or No-eXecute (NX) bit) can avoid some attacks, but are still vulnerable [23]. A survey of these various techniques can be found in the article by Younan et al. [83].

The prevention of stack smashing attacks has been the focus of significant work, although most approaches require significant processor modifications and run-time execution slowdown. Dynamic instruction flow tracking (DIFT) [69] tags each incoming data value or its derivative with a one-bit tag to indicate that it should not influence program control flow. The approach can require an execution slowdown due to tag checking. CHERI [81] establishes a base and bounds for pointers, preventing illegal accesses to memory which can lead to buffer overflow attacks. This approach also involves data tagging and the use of a special-purpose capability processor and registers to dynamically assess tags. The Hardbound approach [19] includes hardware to check the address bounds of every pointer access to memory. A flexible software-only approach [48] introduces a compiler pass for each application to insert bounds checking operations in the code. Although flexible for a range of applications, an increase in code size and application slowdown make the approach limited for embedded applications.

One very effective protection mechanism is the use of hardware and software monitoring to track different aspects of program behavior. The granularity of such monitors ranges from a call sequence (e.g., [64]) to checksums over basic blocks (e.g., [6]) to per-instruction verification (e.g., [42]). Coarse monitoring granularity may not be able to detect attacks that require only a few instructions to execute (such as demonstrated for a denial-of-service attack in network processors [14]). Thus, our work focuses on monitors that perform per-instruction monitoring and can detect attacks immediately when program behavior changes. Due to the need for tight coupling, such monitors are implemented in hardware and co-located with the processor core.

Existing hardware monitors have been used to monitor processors with single-task workloads (e.g., [42]) or with a small number of tasks that are managed through a control processor (e.g., [32]). However, an increasing number of embedded systems use operating systems, where multiple tasks actively share the processor core and tasks are dynamically added and removed. Our work focuses on providing security

through instruction-level monitoring in such a highly dynamic workload controlled by an operating system.

## 2.2 System and Security Model

To provide the necessary context for the Multi-Task Hardware Monitor System design presented in Section 2.3, we briefly discuss the operation of MTHM and the security model for our work.

### 2.2.1 Secure Processing with Hardware Monitors

Hardware monitors are components that are co-located with processor cores to track the processing of software on that core. The objective is to assess the operation of the processor and determine when incorrect behavior is detected (which can be due to benign faults or malicious attacks). As discussed in related work, there are a number of different approaches to monitoring based on what information is communicated from the processor to the monitor and what information is used to determine if that behavior is "normal".

In our work, we use a hardware monitor that receives information about every instruction executed on the processor core and compares it to a "monitoring graph" that is based on the analysis of the processing binary (similar to [42]). Each instruction is represented by a 4-bit hash value (to reduce the size of the monitoring graph compared to the size of the binary) and state transitions correspond to possible control flow paths between instructions. We use a deterministic finite automaton (DFA) representation of the monitoring graph (as described in [12]).

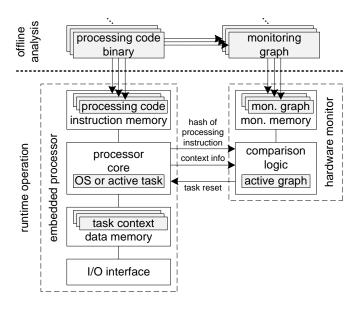

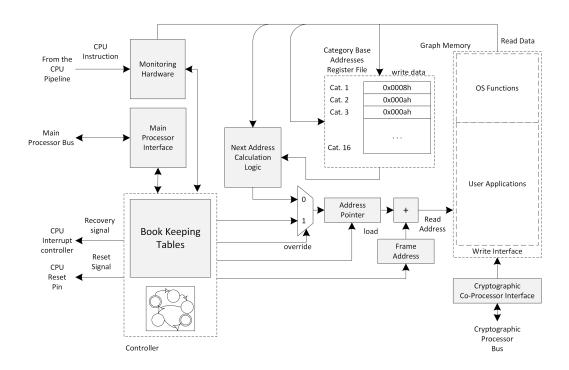

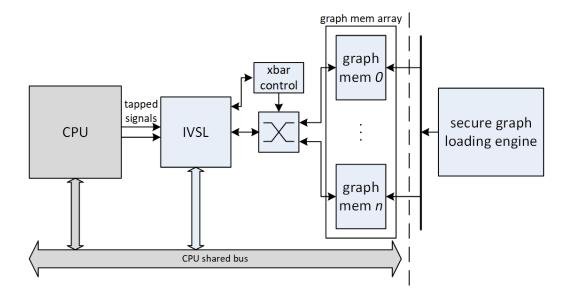

The system architecture of our Multi-Task Hardware Monitor System, which supports multiple tasks, is illustrated in Figure 2.1. The figure shows that application binaries are analyzed offline. During runtime, the comparison logic in MTHM matches the monitoring graph to the currently active task on the processor. To do the

Figure 2.1. System architecture of Multi-Task Hardware Monitor System.

operation, the OS-to-Monitor Interface (OMI) communicates the necessary context information between the processor and the monitor. When the processor execution does not match the expected behavior reflected in the monitoring graph of the current task, a recovery signal is sent from the monitor to the processor to terminate the current task. (More complex recovery and roll-back mechanisms could be implemented, but are not discussed here.)

It is important to note that the hardware monitoring system is isolated from the processor and thus cannot be tampered with remotely by the attacker (e.g., to change the monitoring graph to match an attack). Related work discusses how to achieve such isolation while still enabling dynamic installation of hardware monitoring graphs through the use of cryptographic mechanisms [34].

## 2.2.2 Security Model

To justify how our proposed system provides a secure processing environment, we briefly discuss the security model that is the basis for our work.

### 2.2.2.1 Security Requirements

We require that our system meets the following security requirements:

- SC1 The system should only allow execution of code as programmed in the executable binaries of each task.

- SC2 Secure processing should be provided for multiple, dynamically changing tasks.

- SC3 Malicious code execution in one task should not affect other tasks.

In addition to security, there are also practical performance requirements. As we show in our results, the hardware monitor does not reduce the performance of the embedded processor in any way. The only overhead is a few instructions (five for our experimentation) in the operating system code when switching tasks, which leads to a negligible reduction in processing speed.

## 2.2.2.2 Attacker Capabilities

We make the following assumptions about the capabilities of an attacker that tries to change the operation of the embedded system and/or tries to execute malicious code on the embedded system:

- AC1 An attacker can provide any input through input/output interfaces of the embedded system.

- AC2 An attacker can start and stop any task from an installed binary in the embedded system (within the limitations of a maximum number of active tasks).

- AC3 An attacker can tamper with any of the binaries.

In order to provide a practical solution for secure processing in an embedded system, we also require some reasonable constraints on attacker capabilities:

AC4 An attacker cannot tamper with the operating system itself.

AC5 An attacker cannot tamper with the hardware monitoring system (e.g., modifying monitoring graphs for installed executables).

As discussed above, we do not discuss the secure installation of monitoring graphs, which has been addressed in related work [34] in more detail.

## 2.3 Monitor Design

#### 2.3.1 Task Management in the Operating System

A key aspect of our monitoring system is its ability to fit seamlessly within the context switch operations of a typical operating system. As noted in Section 2.4, the time required to switch monitoring graphs for different tasks is significantly less than the typical time required for other activities in a context switch. In our implementation, graph switching is synchronized with other OS actions (e.g., register file save and restore) that occur during a context switch so that user tasks are protected at all times. Typical context switch activities for embedded operating systems, such as  $\mu$ C/OS-II<sup>1</sup> used for this work, include:

- 1. A timer or other OS event generates an interrupt triggering a context switch.

- 2. The OS scheduler determines the next process for execution. Our implementation uses a priority based scheme, although it can be replaced with a round-robin or any other scheduling algorithm if necessary.

- 3. The OS provides the process ID (PID) of the next process to the monitoring system, triggering a monitoring graph switch in the monitor. This switch includes monitor state saving for the process currently being monitored, and a restoration of monitoring state for the next process.

<sup>&</sup>lt;sup>1</sup>http://micrium.com/rtos/ucosii/overview/

- 4. Concurrently, the OS saves process state (registers, program counter, etc.) for the current task to main memory.

- 5. The OS retrieves process state for the next process from main memory and restores it to processor registers.

- 6. The OS checks the status of the monitoring system to confirm that the monitor for the next process is ready for use.

- 7. The OS sends a trigger to the monitoring system to start monitoring for the newly-loaded process.

After the context switch is completed, the processor sends every instruction executed for the process to the monitoring system. In the next section, we provide a detailed view of the monitoring system and how it interacts with the processor for steps 3, 5, and 6 above.

#### 2.3.2 Multi-Task Hardware Monitor System

A detailed view of our monitoring subsystem is shown in Figure 2.2. The portions of the monitoring system can be split into three parts: *monitoring hardware* (three boxes in upper left corner of the figure), which checks the per-instruction operation of the companion processor; *graph memory*, which stores state information about monitoring for each process, *controller*, and the *processor interface*.

The monitoring hardware checks each processor instruction using information from the monitoring graphs stored in graph memory. In the figure, graphs for four separate applications are stored in *slots* in the graph memory. Each graph includes one row per instruction, effectively representing expected program control flow as a state machine [12]. A *read address* pointer indicates the entry in the graph that corresponds to the instruction that has just completed execution. During the execution of an instruction, a multi-bit (in our case 4-bit) hash value of the instruction is generated and converted

Figure 2.2. Detailed view of multi-context monitoring system

to a one-hot representation. This one-hot encoding is compared against the expected next-instruction hash values (valid hash) that are stored in the graph entry for the previously executed instruction. Since branch instructions may have several possible next instructions, and, consequently, several possible valid hashes, multiple one-hot valid hash bits may be set per entry. A match of any of these hashes indicates a valid instruction. If no match occurs, an illegal instruction has been executed, leading to the generation of a recovery signal which alarms the processor and prevent the attack code from spreading or affecting the rest of the ecosystem. Our approach can handle dynamic branch targets by profiling the code to determine all branch targets for an application prior to graph generation. Entries for these targets are then added to the graph.

In the memory graph, states are grouped based on their fanin count and are placed in the memory with regard to their groups (i.e. states within the same group are located next to each other). base address registers cointains the base address of the group to which the current state belongs [12]. The next read address (memory row) in the monitoring graph is determined using next state information stored in the current entry, the matched hash value, and information stored in base address registers. These values are combined via addition and multiplication in the sequencing logic box in the figure. The resulting address is stored in the address pointer and subsequently added to the start address for the appropriate graph slot for the application. The implemented monitor requires only one memory lookup per instruction.

Effectively, the monitoring information for each process at any given point in execution is defined by the contents of the *address pointer*, the monitoring graph for the process and the contents of the *base address registers*. If a context switch is requested, these values must be updated to use values for the requested next process. The procedure required for a context switch inside the monitoring system is described next.

#### 2.3.3 OS-to-Monitor Interface for Context Switch

In case of a context switch, control information is exchanged between the processor and the monitoring system. The exchange of monitoring information (Step 3 in Section 2.3.1) starts when the processor writes the *PID* of the next process into the *PID* register in the *processor interface* of the monitoring system and sets a bit in the *Operation* register. The monitoring system *control FSM* then performs the following actions:

1. The *address pointer* for the currently executing process is saved in the *PID addresses* storage so that it can be restored for the next invocation of the process.

- 2. The graph ID (GID) associated with the next process is located in the PID to GID binding storage using the PID written to the processor interface.

- 3. If the graph ID of the next process differs from the ID of the previous one, the base address registers are loaded with values for the graph of the next process.

These values are loaded from the graph memory (e.g., Group 1 Addr, etc).

- 4. The GID is used to determine the frame address for the start of the appropriate monitoring graph in graph memory for the process. This information is stored in the GID to frame binding storage.

- 5. The *address pointer* value for the next process is restored from the *PID addresses* storage.

- 6. The *Done* bit is set in the *processor interface* indicating that the monitoring system is now ready to monitor the next process. This bit can be read by the processor.

- 7. Once all other context switch activity for the next process has concluded (e.g., processor registers are loaded), the processor sets an *Enable* bit in the *Operation* register of the processor interface, resuming monitoring. The processor waits until this bit set is successfully made, ensuring synchronization. Instructions of the newly-loaded process are then monitored.

In Section 2.4 we show that these steps can be performed in 17 clock cycles for our prototype system.

### 2.3.4 OS-to-Monitor Interface for Process Creation

When a new task is being created by the OS, it is assigned a unique *PID* and a *GID* by the operating system. Each known application has a predefined *GID* which is known to both the processor and hardware monitor. Since many processes of the

same application may exist, the *GID* may not be unique. The following steps are used to initialize the security monitor for the new process.

- 1. The two identifiers (GID and PID) are passed to the monitor via the processor interface. The monitor first searches for an empty slot in the PID addresses storage and PID to GID binding storage to insert the new bindings.

- 2. While making these associations, the *GID to frame binding* storage is searched to determine if the appropriate graph is already loaded. If it is available, the next step is skipped.

- 3. If the *GID* is not found in the *GID* to frame binding storage, the *GID* is inserted into the table. After a graph to remove is determined using a least recently used approach, the new graph is then loaded into graph memory using the DMA interface. Following graph loading, base addresses are updated.

- 4. The *Done* bit is set in the *processor interface* indicating that the monitoring system is now ready to monitor the next process. This bit can be read by the processor.

During system startup, monitoring graphs are loaded from an external memory graph pool for the new processes that will be executed by the processor. Concurrently, the processor performs a series of process creation operations including initialization of the process stack and control block (registers, etc.). In Section 2.4, it is noted that while process creation can require hundreds of cycles for the processor, if the appropriate monitoring graph is already in the monitoring system, monitoring information update for process creation requires less than 20 cycles for the monitoring system.

# 2.4 Prototype Implementation

# 2.4.1 System Setup

To verify the functionality of our monitoring system, we implemented an embedded NIOS II-based processing system plus monitoring system using a Stratix IV GX230 FPGA located on an Altera DE4 board. A single-core NIOS executing a  $\mu$ C/OS-II operating system was used for testing. Monitoring logic and memory were implemented in on-chip resources. Monitoring graphs were generated by passing code through a standard MIPS\_GCC compiler flow to generate assembly-level instructions [12]. The output of the compiler allows for the identification of branch instructions and their target addresses. This information was used to generate monitoring graphs for four MiBench<sup>2</sup> applications (bitcount, qsort, basicmath, and stringsearch) and malicious stack-smashing attack code. Our examination of all MiBench benchmarks determined that the target for all dynamic branches could be determined at compile time.

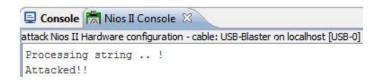

The attack code we use for our system is a C function which accepts a character string as its only argument and copies it to a buffer located on its local stack frame [66].

```

void process_input(char *stringpassed) {

char name[90];

strcpy(name,stringpassed);

printf("Processing string .. !\n");

return;

}

```

In this poorly designed code, no check is made to determine if the string **string-passed** is longer than the target buffer, so the return address of the function can be overwritten with an address which points into the user-provided input string. Instead

<sup>&</sup>lt;sup>2</sup>http://wwweb.eecs.umich.edu/mibench/

Figure 2.3. Console display during stack smashing

of characters, this "string" can contain processor instructions which repetitively print out "Attacked!!" on a terminal in a loop, although much more malicious behavior could be imagined. A monitor for the code is able to detect the unplanned control flow jump and stop the processor before the attack can perform this activity. The hash values stored in the monitoring graph for the application will not match the values for the malicious instructions as they are executed during the attack. As shown in Figure 2.3, we have confirmed that this attack will lead to unexpected results (an attack message) if monitoring is not used.

# 2.4.2 Monitor Context Management

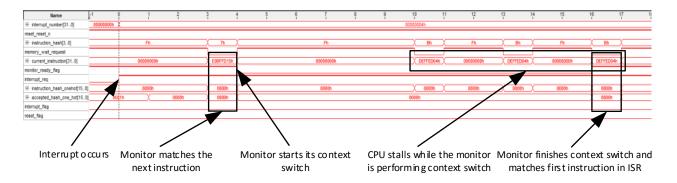

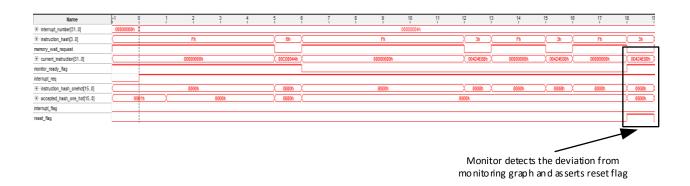

We have verified our ability to perform numerous context switches between multiple processes of the four monitored MiBench benchmarks both via simulation and in emulation hardware. This switch includes both standard process state used by the processor (e.g., register information, stack) and monitoring information using the mechanism outlined in Section 2.3.3. Altera SignalTap, a hardware debugger, was used to generate the waveforms shown in Figure 2.4.

The waveforms show the synchronization between the processor and the monitor as a result of the context switch. First, the processor notifies the monitoring system of the switch by writing the *PID* of the next process into the processor interface. The monitor switch is started by the processor writing into the *Operation* register of the interface. The value of the *address pointer* for the old process is stored and the value for the new process is restored to/from *PID* address storage immediately

**Figure 2.4.** SignalTap waveforms showing the trigger for monitor context switch (Operation = 0x2), monitor switch finished (Done), and monitor restart monitoring when CPU ready (Enable)

Figure 2.5. SignalTap waveforms showing the operations for monitor process creation (Operation = 0x1) and monitor update finished (Done)

after this trigger. The base address registers are then configured using the write\_data port shown in Figure 2.2. After the control FSM performs the monitor update, the Done signal is set in the processor interface indicating the monitor context switch is finished. Finally, after the processor finishes other context switch operations, it sets the Enable signal in the processor interface to restart monitoring. The processor waits a cycle until this write is complete. Monitoring for the new process starts with the first instruction received from the process.

Experiments in simulation and in the lab on FPGA hardware showed that the processor is able to process data for the MiBench benchmarks equally fast both with and without monitoring (e.g., no slowdown for monitoring). Context switch time is extended by 5 cycles versus no monitoring to allow for monitor context switches. This overhead accounts for the data exchanges between the processor and monitoring system for synchronization. Overall, we found that the number of cycles needed to perform a monitor context switch is 17 versus the 34 cycles needed for the processor to

**Figure 2.6.** SignalTap waveforms showing the successful identification of a stack smashing attack. Instruction hash values are checked against expected values stored in the monitor graph. When a mismatch occurs, a recovery signal is triggered indicating the process should be terminated.

save and restore registers (note that monitor and processor context switch operations occur in parallel).

The amount of time needed to create a new process in the OS is about 600 clock cycles versus 17 to create process information in the monitor (Figure 2.5). If a monitoring graph is loaded from main memory, the cycle count required for the monitor increases to include reading the number of rows in the monitoring graph for the new process into graph memory (about 80 for each of our applications).

#### 2.4.3 Attack Detection and Protection

We have verified in both simulation and in hardware that our monitoring system is able to detect the stack smashing attack described in Section 2.4.1 and notify the processor so that the malicious process can be terminated. SignalTap waveforms derived from observing hardware operation in system are shown in Figure 2.6. As described in Section 2.3.2, an attack is detected when the hash of the CPU instruction does not match the expected value stored in the monitoring graph for the application. In our system, the implemented hash function counts the number of ones in the instruction to form a four-bit hash value. The figure shows the four-bit hash value, a one-hot version of the hash value, and the retrieved, expected hash value for the instruction from the monitoring graph (read\_data[15:0]). In the waveforms, it can

|           | Available  | Nios II with  | HW monitor     |

|-----------|------------|---------------|----------------|

|           | on FPGA    | no HW monitor | and controller |

| LUTs      | 182,400    | 1,341         | 406            |

| FFs       | 182,400    | 1,166         | 522            |

| Mem. bits | 14,625,792 | 2,108,416     | 524,512        |

| Pwr (mW)  | -          | 105.97        | 41.83          |

Table 2.1. Resource use and power consumption on a Stratix IV FPGA

be seen that the correct hash value is matched twice, but the third hash value is incorrect, indicating a branch to an unexpected section of code. As a result of this detection, a recovery signal is generated, notifying the processor that the process should be terminated.

### 2.4.4 Monitoring System Resources

To provide some context regarding the amount of overhead required by the monitoring system relative to the processor, hardware results of the system reported by the Altera Quartus II tool are shown in Table 2.1. The lookup table (LUT), flip flop (FF), and memory resources required for the monitor are appropriate compared to the processor core. Dynamic power values are also shown in the table. These power numbers were generated using Altera PowerPlay.

# 2.4.5 Discussion of Security Properties

We argue that the system we have designed and prototyped achieves the security requirements we put forth in Section 2.2.2.

The key observation is that our hardware monitor can detect when a specific task executes code that is different from the binary. In such a case, the hash value that is reported from the processor core to the monitor does not match. There is a chance that the attacker is lucky and the hash matches by coincidence or the attacker is clever and aims to construct code that matches. This action, however, is very difficult to achieve in practice and can be defeated by hiding the hash function [34]. In Chapter

3, we introduce a technique to add diversity to hardware monitoring systems in a way that even a successful attack to a particular application on one system would fail on other systems. If the monitor detects deviation from the binary, then the processor is signaled to stop execution of the attacked task. Thus, SC1 (no execution of attack code) is achieved.

Our system supports multiple tasks that are switched dynamically by the operating system. The hardware monitor follows along in sync and associates the current task on the processor core with the correct monitoring graph. Thus, we achieve SC2 (secure processing for multiple tasks).

Finally, when an attack occurs, the hardware monitor informs the operating system about the attack and the targeted tasks are stopped using a conventional task termination mechanism (similar to the kill command). This mechanism is specifically designed to not affect other tasks. Thus, SC3 (isolation of attacked task) is achieved.

We rely on the limitations of attacker capabilities, such as AC4 and AC5 (no tampering of operating system or hardware monitor), to ensure that an attacker cannot circumvent the security mechanisms we have put in place.

# 2.5 Summary and Conclusions

In this chapter, we presented security hardware for embedded processors that execute multiple processes under the control of an operating system. Our monitoring approach allows the operation of each process to be tracked at the instruction execution level. If a deviation from the expected instruction execution sequence is detected, the monitor can quickly identify it and notify the processor to initiate process termination.

A significant contribution of the work is the inclusion of multi-context support in the monitoring system. Monitoring state for each process can be quickly saved during a process context switch and previously-stored state can be reloaded. We document the specific steps needed to ensure synchronization between the processor and monitor to ensure that each process is always protected during execution. Using prototyping, we show that our system is effective for multiple processes managed by an embedded OS. A stack smashing attack is identified and suppressed. The monitoring system does not impact application execution time.

In this chapter, we assumed that the operating system is a secure entity and the main vulnerable point of an embedded system, is the applications running on top of that operating system. In Chapter 3, we revisit this basic assumption that considers the operating systems secure. In two different scenarios, we show how both a real-time embedded operating system such as  $\mu$ C/OS-II and a full-scale general purpose operating system such as Linux can also be vulnerable against attacks. We also expand our hardware monitoring system accordingly in each scenario to ensure the security of the system in presence of external threats targeting those vulnerabilities.

# CHAPTER 3

# ADDRESSING VULNERABILITIES IN THE OPERATING SYSTEM

The Internet of Things (IoT) represents the convergence of cyber-physical systems (CPS), which control physical processes, and the Internet, which provides global interconnectivity for access to data systems. Embedded systems are at the core of any IoT solution as they provide the necessary computational power at the location where devices interact with the physical world. Due to their deployment in the environment, these embedded systems are typically constrained in their computational resources (performance and/or energy) but still connected to a network to interact with the other components of the IoT solution.

There are three aspects that are of particular importance when talking about the security of IoT devices. First, the IoT devices are connected to the Internet and thus vulnerable to remote attacks. Second, these embedded systems typically do not have the processing capacity or power budget to run software-based defense mechanisms, such as virus scanners or intrusion detection systems. Such software-based solutions, although very commonly used as security solutions in network-connected workstation and server computers, do not seem very suitable for IoT devices. Third, despite their limited processing capability, the collective power of IoT devices is enormous due to the big number of instances deployed in different environments and for a variety of applications. Therefore, in case they go rouge, the implications could be catastrophic.

As discussed in Chapter 2, an effective defense mechanism that has been developed in related work is "hardware monitors". These monitors are logic components that are co-located with the embedded system processor core and track the execution of software. Hardware monitors require no change or addition to the software that is run on the processing system.

Hardware monitors were initially introduced to protect embedded applications running on top of a bare metal or simple firmware-based embedded system. However, given the ever-changing nature of IoT applications and the recent advancements in the technology used in IoT devices, the assumption of having a single embedded application running on bare metal or a simple firmware does not fit the characteristics of these modern devices anymore.

In an attempt to bridge the gap between the security requirements of IoT devices and the available security solutions, in Chapter 2, we introduced a novel hardware monitoring system which had the capability of monitoring multiple tasks running on top of an embedded operating system. We showed how that monitoring system was able to stay in sync with the processor core throughout the core's entire processing cycle and during the context-related operations such as process creation, context switching, and process termination. We finally showed the effectiveness of this approach in defeating a buffer overflow attack in practice, using an FPGA prototype of the proposed method alongside an embedded processing system.

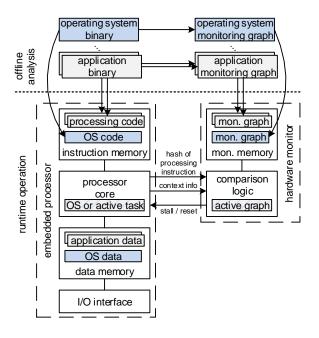

In this chapter, we further expand our proposed hardware monitoring approach to accommodate to yet another security need of today's IoT devices: the security of the system amid the vulnerabilities within the operating systems managing these devices. In This chapter we explore the challenges of securing a low-end IoT device managed by a simple real-time operating system. As an example, we use a NIOS II-based embedded system running  $\mu$ C/OS-II. We show how we can extend our hardware monitoring solution to not only protect the system while running user applications, but also continuously monitor the system while the processor switches from a user task

to the operating system or vice versa, and throughout the execution of the operating system itself.