# University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

March 2020

# EFFICIENT HARDWARE PRIMITIVES FOR SECURING LIGHTWEIGHT SYSTEMS

Siva Nishok Dhanuskodi

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Dhanuskodi, Siva Nishok, "EFFICIENT HARDWARE PRIMITIVES FOR SECURING LIGHTWEIGHT SYSTEMS" (2020). Doctoral Dissertations. 1821.

https://doi.org/10.7275/re76-xh53 https://scholarworks.umass.edu/dissertations\_2/1821

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# EFFICIENT HARDWARE PRIMITIVES FOR SECURING LIGHTWEIGHT SYSTEMS

A Dissertation Presented

by

SIVA NISHOK DHANUSKODI

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

February 2020

Electrical and Computer Engineering

© Copyright by Siva Nishok Dhanuskodi 2020 All Rights Reserved

# EFFICIENT HARDWARE PRIMITIVES FOR SECURING LIGHTWEIGHT SYSTEMS

# A Dissertation Presented $\label{eq:by}$ SIVA NISHOK DHANUSKODI

| Approved as to style and content by: |  |  |

|--------------------------------------|--|--|

|                                      |  |  |

| Daniel E. Holcomb, Chair             |  |  |

|                                      |  |  |

| Wayne P. Burleson, Member            |  |  |

|                                      |  |  |

| Russell G. Tessier, Member           |  |  |

|                                      |  |  |

| Charles Weems, Member                |  |  |

|                                      |  |  |

Christopher V. Hollot, Department Head Electrical and Computer Engineering

# **DEDICATION**

To my parents Dhanuskodi S. and Parvathi B.

## ACKNOWLEDGMENTS

I would like to first of all thank my advisor Professor Daniel Holcomb. His technical astuteness, patient guidance and unwavering support throughout my PhD have gone a long way in making this thesis happen. He has been always been willing to give a lot of his time and energy. The many interactions I have had with him have shaped my research goals as well as honed my technical skills. This thesis would not have been possible without his constant friendly support and encouragement.

I would like to thank the members of my thesis committee for their valuable feedback and time. A special thanks to Professor Burleson, Professor Kundu and Professor Koren for their guidance, discussions and critique in group meetings. Their personal interest and experience have helped me improve research quality. I would like to acknowledge the faculty at ECE department in general for an inspiring and conducive learning atmosphere.

It was great to work with several people all these years: Xiang Li, Shahrzad Keshavarz, Harshavardhan Ramanna, Vinay Patil, Arunkumar Vijayakumar and Raghavan Kumar. I really enjoyed our collaborations, technical discussions and thank you for your support at several stages of my graduate life. A special mention to some of my friends who always stood by me with encouragement and support: Arunachalam Annamalai, Sankara Narayanan Rajapandian, Meenakshi Sundaram Bhaskaran, Surendran Subramanian and Badri Krishna Kumar.

The list would not be complete without thanking my family for their selfless love, support and care. Their entire life has been an offering to my brother and I, more than I could ever ask for. Yoga has been a huge support in every aspect of my life, I would like to express my heartfelt gratitude to Sadhguru.

# ABSTRACT

# EFFICIENT HARDWARE PRIMITIVES FOR SECURING LIGHTWEIGHT SYSTEMS

#### FEBRUARY 2020

### SIVA NISHOK DHANUSKODI

B.E., ANNA UNIVERSITY - MADRAS INSTITUTE OF TECHNOLOGY

M.S., UNIVERSITY OF MASSACHUSETTS AMHERST

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Daniel E. Holcomb

In the era of IoT and ubiquitous computing, the collection and communication of sensitive data is increasingly being handled by lightweight Integrated Circuits. Efficient hardware implementations of crytographic primitives for resource constrained applications have become critical, especially block ciphers which perform fundamental operations such as encryption, decryption, and even hashing. We study the efficiency of block ciphers under different implementation styles. For low latency applications that use unrolled block cipher implementations, we design a glitch filter to reduce energy consumption. For lightweight applications, we design a novel architecture for the widely used AES cipher. The design eliminates inefficiencies in data movement and clock activity, thereby significantly improving energy efficiency over state-of-theart architectures. Apart from efficiency, vulnerability to implementation attacks are a concern, which we mitigate by our randomization capable lightweight AES architecture. We fabricate our designs in a commercial 16nm FinFET technology and

present measured testchip data on energy consumption and side channel resistance. Finally, we address the problem of supply chain security by using image processing techniques to extract fingerprints from surface texture of plastic IC packages for IC authentication and counterfeit prevention. Collectively these works present efficient and cost effective solutions to secure lightweight systems.

# TABLE OF CONTENTS

|                        |                        |                                  | Page                                                                                                                                                  |

|------------------------|------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC                     | CKN                    | IOWL                             | EDGMENTS v                                                                                                                                            |

| $\mathbf{A}\mathbf{B}$ | $\mathbf{ST}$          | RACT                             | 'vi                                                                                                                                                   |

| LIS                    | ST (                   | OF TA                            | BLES xii                                                                                                                                              |

| LIS                    | ST (                   | OF FI                            | GURES                                                                                                                                                 |

| СН                     | $\mathbf{AP}'$         | TER                              |                                                                                                                                                       |

| IN'                    | $\mathbf{T}\mathbf{R}$ | ODUC                             | TION 1                                                                                                                                                |

| 1.                     | $\mathbf{B}\mathbf{A}$ | CKGF                             | ROUND                                                                                                                                                 |

| 1                      | .1                     | Block                            | ciphers                                                                                                                                               |

|                        |                        | 1.1.1<br>1.1.2                   | AES                                                                                                                                                   |

|                        | .2                     |                                  | r efficiency in block ciphers implementations                                                                                                         |

|                        |                        | 1.3.1<br>1.3.2<br>1.3.3<br>1.3.4 | Differential Power Analysis and metrics.9Existing countermeasures.11Logic State Based Leakage Power Analysis.12Remote Side Channel Attack on FPGAs.14 |

| 1                      | .4                     | Supply                           | Chain Security19                                                                                                                                      |

| 2.                     | EF.                    | FICIE                            | NCY IN UNROLLED BLOCK CIPHERS 21                                                                                                                      |

| 2                      | 2.1<br>2.2<br>2.3      | Check                            | es and glitch filtering                                                                                                                               |

|                        |                        | 2.3.1                            | Methodology                                                                                                                                           |

|    |               | 2.3.2<br>2.3.3          | Comparison of Average Switching Rates                                                             |      |

|----|---------------|-------------------------|---------------------------------------------------------------------------------------------------|------|

|    |               |                         | 2.3.3.1 SIMON-128                                                                                 |      |

|    |               | 2.3.4<br>2.3.5          | Optimal Placement of Checkpoints for Glitch Filtering Checkpointing in Partially Unrolled Designs |      |

|    |               |                         | 2.3.5.1 SIMON-128                                                                                 |      |

|    |               | 2.3.6<br>2.3.7<br>2.3.8 | Area Cost of Checkpointing                                                                        | 38   |

|    | 2.4           | Summ                    | ary                                                                                               | 40   |

| 3. | EF            | FICIE                   | NCY IN LIGHTWEIGHT AES                                                                            | . 42 |

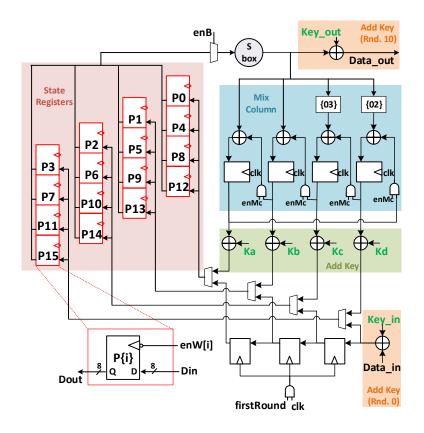

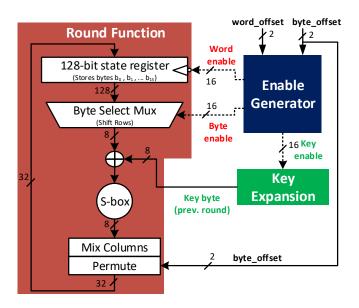

|    | 3.1           | Novel                   | architecture                                                                                      | 44   |

|    |               | 3.1.1<br>3.1.2<br>3.1.3 | Improved clocking                                                                                 | 45   |

|    | 3.2           | Microa                  | architectural Randomization                                                                       | 55   |

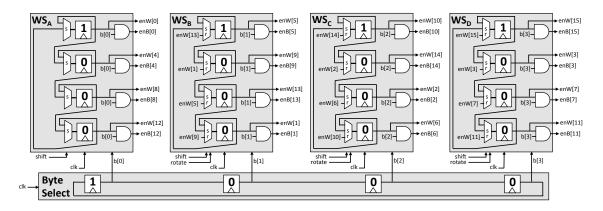

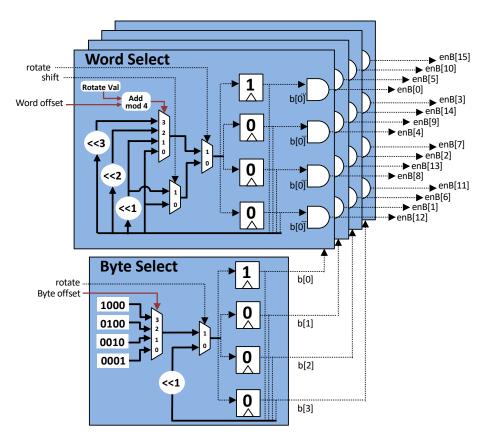

|    |               | 3.2.1<br>3.2.2<br>3.2.3 | Enable Generator design for Word and Byte shuffling                                               | 57   |

|    | 3.3           | Evalua                  | ation                                                                                             | 61   |

|    |               | 3.3.1<br>3.3.2          | Efficiency and overheads                                                                          |      |

|    | 3.4           | Summ                    | ary                                                                                               | 66   |

| 4. | $\mathbf{TE}$ | STCH                    | IP                                                                                                | . 68 |

|    | 4.1           | Design                  | methodology                                                                                       | 68   |

|    |               | 4.1.1                   | RTL design and synthesis                                                                          | 68   |

|    |               | 4.1.2                   | Physical design                                                                                   |      |

|    | 4.2        | Chip 7                                             | Testing                                                                                                                          | 75                |

|----|------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|

|    |            | 4.2.1<br>4.2.2                                     | Efficiency, power                                                                                                                |                   |

|    | 4.3        | Summ                                               | nary                                                                                                                             | 83                |

| 5. | PA         | CKAC                                               | GE IDENTIFICATION                                                                                                                | 85                |

|    | 5.1<br>5.2 |                                                    | fer Molding for IC packaging                                                                                                     |                   |

|    |            | 5.2.1<br>5.2.2<br>5.2.3                            | Enrollment                                                                                                                       | 91                |

|    | 5.3        | Image                                              | Processing and Analysis                                                                                                          | 95                |

|    |            | 5.3.1<br>5.3.2<br>5.3.3                            | Aruco marker labels and detection of ROI Feature Enrollment                                                                      | 96                |

|    |            |                                                    | 5.3.3.1 Feature matching and RANSAC based homography computation                                                                 |                   |

|    | 5.4        | Evalua                                             | ation                                                                                                                            | 100               |

|    |            | 5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6 | Package Authentication Runtime Practicality and Costs Algorithm Difference Camera Differences Varying Magnification and Lighting | 105<br>105<br>107 |

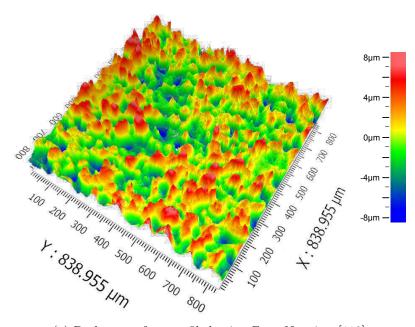

|    | 5.5        | Furthe                                             | er Investigation of Fingerprints                                                                                                 | 109               |

|    |            | 5.5.1<br>5.5.2                                     | Testing Resilience of Fingerprints                                                                                               | 110               |

|    |            | 5.5.3                                              | Additional Package Types                                                                                                         | 115               |

|    | 5.6        | Summ                                               | nary                                                                                                                             | 117               |

| 6. CONCLUSION        | . 118 |

|----------------------|-------|

| LIST OF PUBLICATIONS | . 119 |

| BIBLIOGRAPHY         | . 120 |

# LIST OF TABLES

| Table | Page                                                                                                                                                                                                                                                                                                                                        |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | Simulated Dynamic and static power consumption of a WDDL-AND gate                                                                                                                                                                                                                                                                           |

| 2.1   | Breakdown of $E_{enc}$ (pJ/bit) in fully unrolled SIMON-128. Glitch filters are added after every round in Round Gating and our checkpointing work                                                                                                                                                                                          |

| 2.2   | Breakdown of $E_{enc}$ (pJ/bit) in fully unrolled AES-128. Glitch filters are added after every round in Round Gating and our checkpointing work                                                                                                                                                                                            |

| 2.3   | $E_{enc}$ (pJ/bit) comparison in SIMON-128 between optimal checkpointing and the baseline design for various degrees of unrolling                                                                                                                                                                                                           |

| 2.4   | $E_{enc}$ (pJ/bit) comparison in AES-128 between optimal checkpointing and the baseline design for various degrees of unrolling                                                                                                                                                                                                             |

| 2.5   | Area penalty of proposed glitch filtering scheme in units of gate equivalents. Even in absolute terms, the area cost of checkpointing is significantly higher in SIMON-128 than in AES-128 because the larger number of rounds requires a larger number of checkpoints, even though the checkpoints are only applied at every second round. |

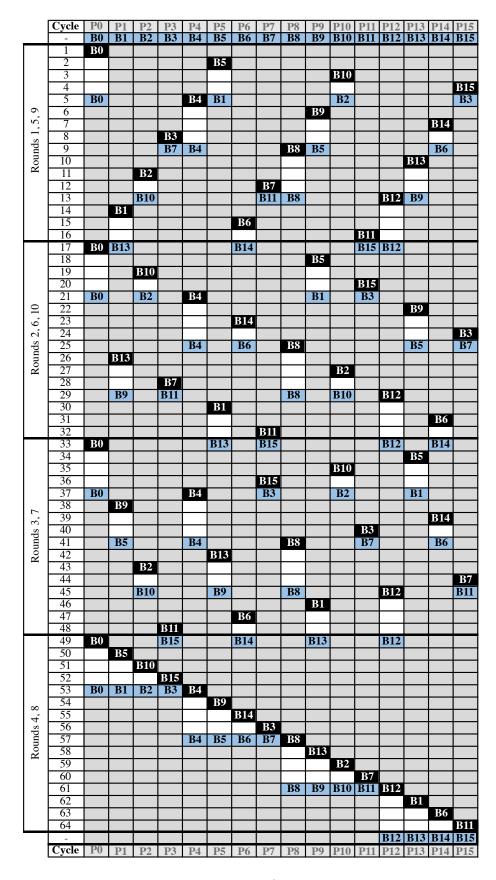

| 3.1   | Physical registers to be enabled in each clock cycle                                                                                                                                                                                                                                                                                        |

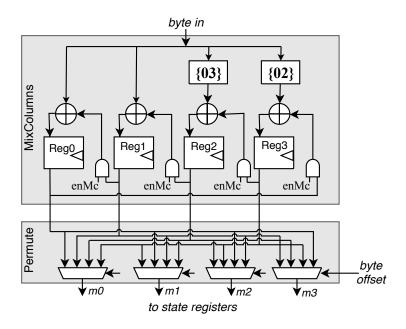

| 3.2   | Table illustrates the operation of the pipelined MixColumns (see Fig. 3.10) for two different orderings of the input bytes. At the end of the four cycles, the same values exist in the registers for both orderings, but their locations differ. The permutation step associates the appropriate register value to each output signal59    |

| 3.3   | Comparison of energy efficiency of four AES designs all implemented by us in the same 16nm technology                                                                                                                                                                                                                                       |

| 3.4 | Comparison of area of four AES designs all implemented by us in the same 16nm technology                                                                                                                                                 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5 | Comparison of performance. Throughput obtained at 300MHz clock                                                                                                                                                                           |

| 4.1 | Performance comparison of AES designs with testchip measurements obtained at 20MHz clock                                                                                                                                                 |

| 4.2 | Measurements to Disclosure using Hamming Distance DPA on the 8-bit AES designs                                                                                                                                                           |

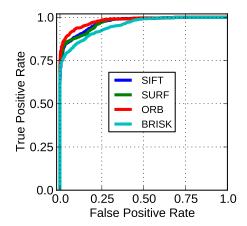

| 5.1 | Quantitative comparison of different feature-detecting methods. Plot at right shows the ROC plot from which the area-under-curve is computed. All four algorithms are configured to use $1,000$ keypoints per $mm^2$ for this comparison |

# LIST OF FIGURES

| Figure | Page                                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | Structure of AES round function                                                                                                               |

| 1.2    | Structure of AES 128-bit Key Expansion [87]                                                                                                   |

| 1.3    | SIMON round function and key schedule [13]                                                                                                    |

| 1.4    | Illustration of a DPA attack on AES                                                                                                           |

| 1.5    | Schematics for LLPA                                                                                                                           |

| 1.6    | A successful attack using LLPA                                                                                                                |

| 1.7    | FDPA Attack setup                                                                                                                             |

| 1.8    | FDPA in action                                                                                                                                |

| 2.1    | Schematic of latch-based checkpoints for glitch filtering                                                                                     |

| 2.2    | Timing diagram of glitch filter operation, annotated with the number of switching events happening at each point in the circuit for SIMON-128 |

| 2.3    | Increasing pulse width of enable signal to tolerate variations                                                                                |

| 2.4    | SIMON-128 energy per encryption histogram for 100 random inputs                                                                               |

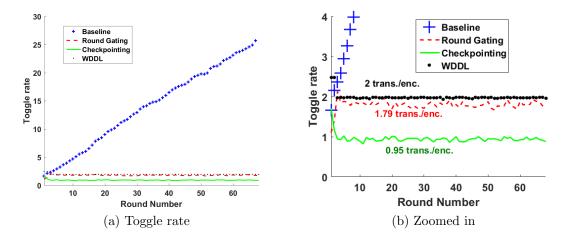

| 2.5    | Comparison of the average toggle rate of the output signals of each round of SIMON-128 for four different implementation styles29             |

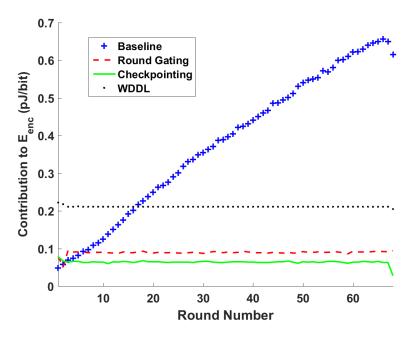

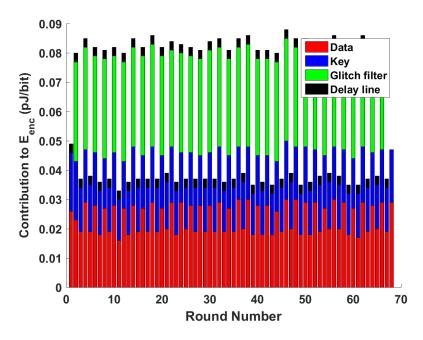

| 2.6    | Contribution of each round to the overall energy per encrypted bit in four different implementation styles of fully unrolled SIMON-128        |

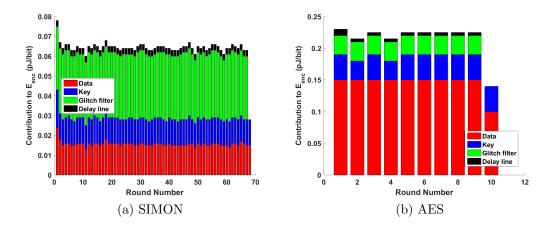

| 2.7    | Energy/encryption breakdown in fully unrolled implementations using checkpointing after every round                                           |

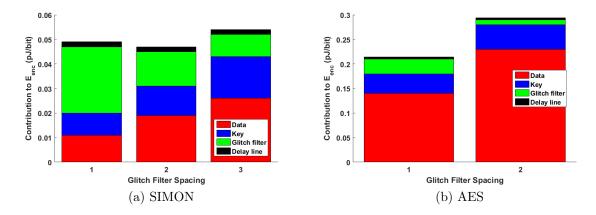

| 2.8  | Energy efficiency varies with the spacing between checkpoints in fully unrolled designs. Performing more computation between checkpoints reduces checkpointing energy, but allows more data switching to occur                              |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.9  | Energy breakdown of $E_{enc}$ for each round in fully unrolled SIMON-128 in the optimal configuration of checkpointing every second round                                                                                                   |

| 2.10 | Power gating to reduce leakage power consumption                                                                                                                                                                                            |

| 2.11 | Energy per encryption at different supply voltages in SIMON. Dotted lines represent leakage energy                                                                                                                                          |

| 3.1  | Proposed 8-bit architecture                                                                                                                                                                                                                 |

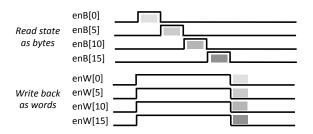

| 3.2  | Timing of control signals for a quarter of one round. $enB$ signals enable bytes to be read from physical registers into the datapath S-Box, and $enW$ signals allow round outputs to be written back to physical registers on falling edge |

| 3.3  | Illustration of register renaming                                                                                                                                                                                                           |

| 3.4  | Enable Generator                                                                                                                                                                                                                            |

| 3.5  | Schematic of Round Function                                                                                                                                                                                                                 |

| 3.6  | Schematic of Key Expansion                                                                                                                                                                                                                  |

| 3.7  | Randomization-capable 8-bit AES architecture. Additional details of redesigned Enable Generator and MixColumns circuits are shown in Figs. 3.9 and 3.10                                                                                     |

| 3.8  | Shuffled orders in which bytes can be processed in our architecture.  Depending on the value of the word offset and byte offset, each of the 16 state bytes could be processed in any of the 16 cycles of the round                         |

| 3.9  | Enable Generator for Randomized architecture (compare Fig. 3.4). Solid, dotted and red lines indicate 4-bit, 1-bit and 2-bit signals respectively                                                                                           |

| 3 10 | MixColumns for Randomized architecture                                                                                                                                                                                                      |

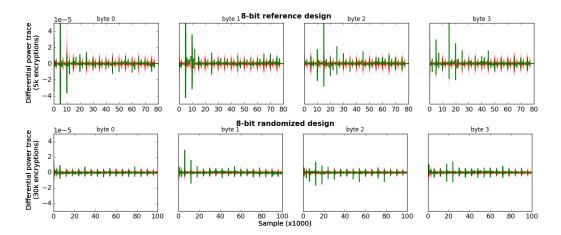

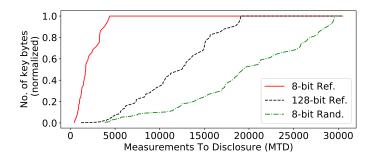

| 3.11 | Plots showing DPA attack on 4 key bytes for the 8-bit designs. Top plot shows differential power traces for the 8-bit renaming design and the bottom plot shows the same for the 8-bit randomized design. Green line corresponds to correct key guess and red lines correspond to incorrect key guesses |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.12 | CDF of MTD for the different designs                                                                                                                                                                                                                                                                    |

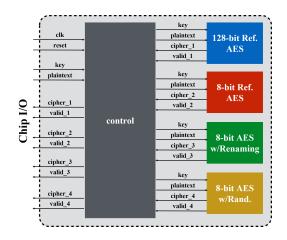

| 4.1  | Block level view of designs implemented on testchip 69                                                                                                                                                                                                                                                  |

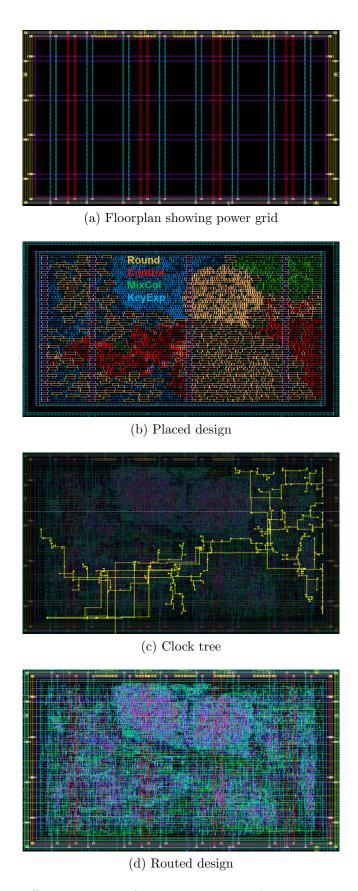

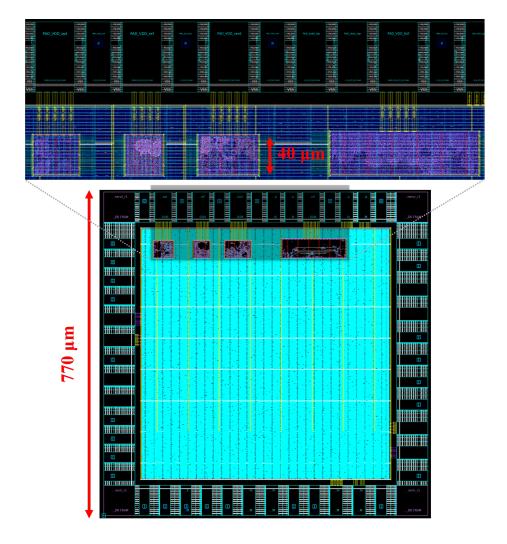

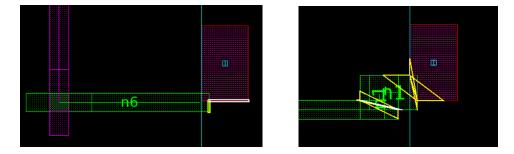

| 4.2  | Different stages of physical design of 8-bit Randomized AES                                                                                                                                                                                                                                             |

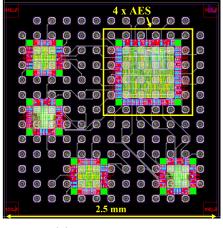

| 4.3  | Layout showing all four AES designs73                                                                                                                                                                                                                                                                   |

| 4.4  | Examples of sign-off DRC violations on finished design that were manually fixed                                                                                                                                                                                                                         |

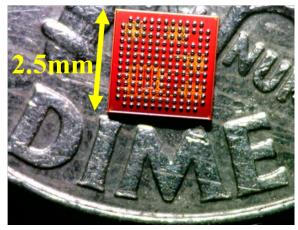

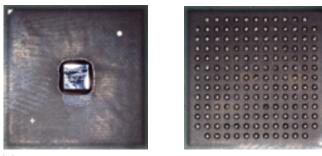

| 4.5  | Images of full chip with other designs from colleagues on same die.  All designs have isolated power domains                                                                                                                                                                                            |

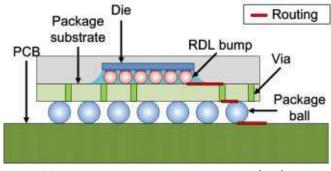

| 4.6  | Chip packaged in a Flip Chip Ball Grid Array                                                                                                                                                                                                                                                            |

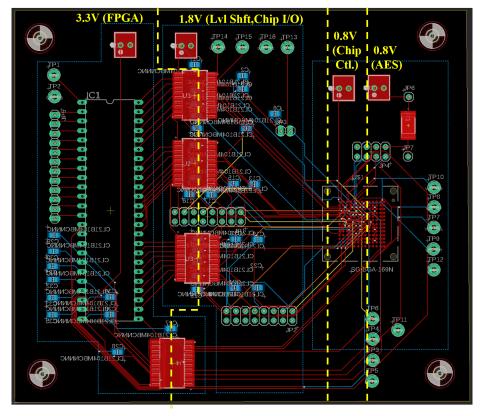

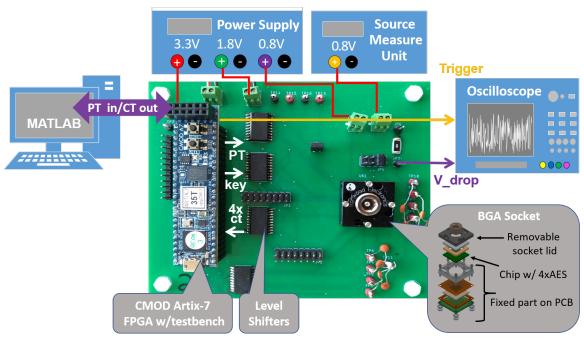

| 4.7  | AES chip test setup                                                                                                                                                                                                                                                                                     |

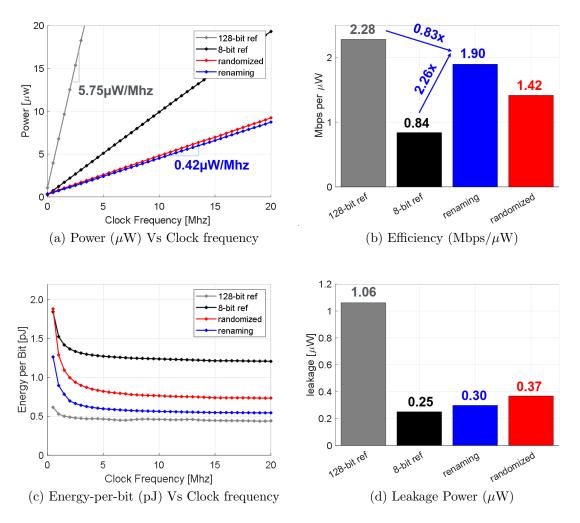

| 4.8  | Power and energy comparison of AES designs based on testchip measurements                                                                                                                                                                                                                               |

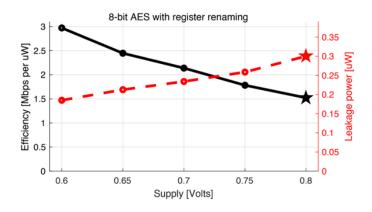

| 4.9  | Effect of voltage scaling on efficiency                                                                                                                                                                                                                                                                 |

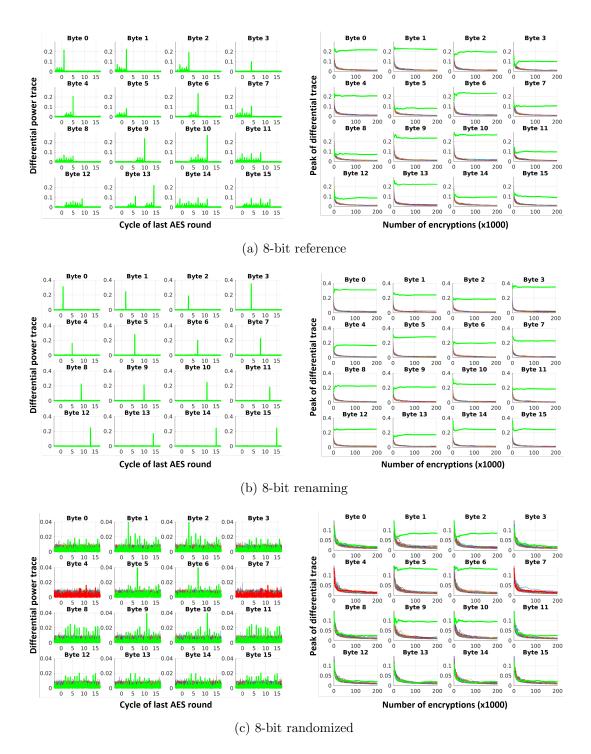

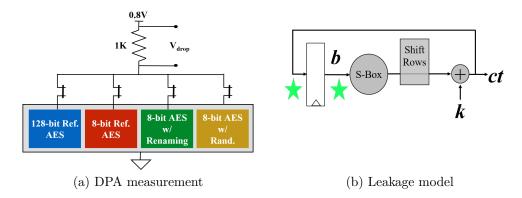

| 4.10 | Differential and DPA traces with Hamming distance leakage model                                                                                                                                                                                                                                         |

| 4.11 | Differential Power Analysis                                                                                                                                                                                                                                                                             |

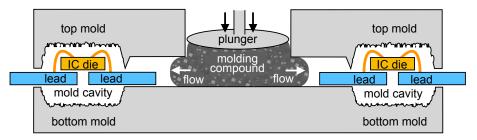

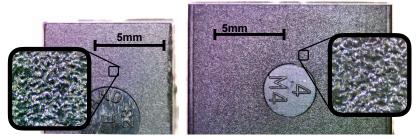

| 5.1  | Transfer molding is the mechanism used for packaging most high-volume microchips                                                                                                                                                                                                                        |

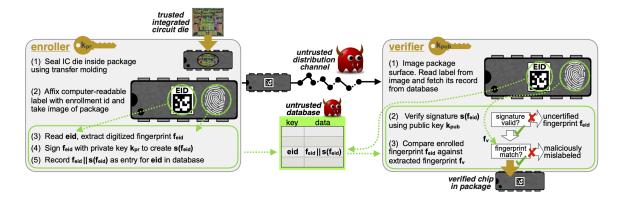

| 5.2  | Protocol for package fingerprinting. Trusted enroller labels each package and then enrolls it by extracting and then signing a set of keypoints associated with the package. Verifier compares the enrolled keypoints against the package to determine whether the package is consistent with its label |

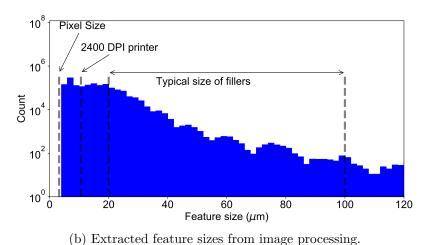

| 5.3  | Size of features extracted from images of package surfaces using OpenCV implementation of ORB algorithm as discussed in Sec. 5.3.2                                                                                                                                                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

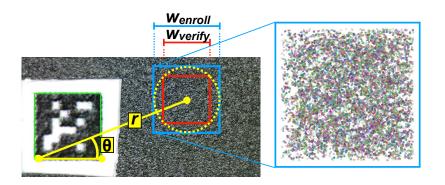

| 5.4  | Image of chip with affixed marker. The position of enrollment ROI is shown by the blue box, and the callout shows the keypoints extracted from the ROI. The ROI that would be used for verification is the smaller red box. The size and position of both ROIs are defined relative to the marker, as shown by annotations in yellow                                                |

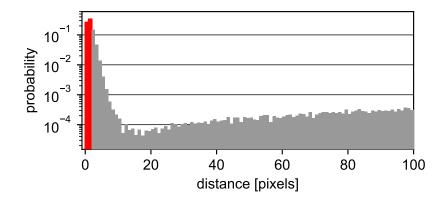

| 5.5  | Pixel distance between the expected location of a keypoint (according to homography) and the location of its nearest neighbor in feature space. The spike at left shows points for which the nearest neighbor is found in the expected location. The points that are sufficiently close to be counted as inliers are the ones colored red                                           |

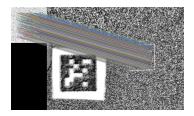

| 5.6  | Three examples of matching between enrollment keypoints (square in upper left) and verification image of the same chip package instance, where the verification image differs in zoom and orientation. White square on chip package is the identified region of interest for verification. Each line corresponds to a keypoint match from enrollment to verification (Sec. 5.3.3.2) |

| 5.7  | Experimental setup. Left side of workbench used for enrollment, right side used for verification. Separate camera are used for enrollment and verification. Middle of image shows the population of chips with labels affixed                                                                                                                                                       |

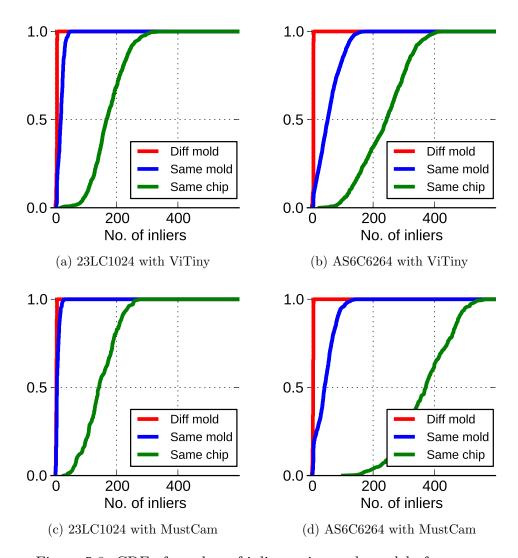

| 5.8  | CDF of number of inliers using each model of camera                                                                                                                                                                                                                                                                                                                                 |

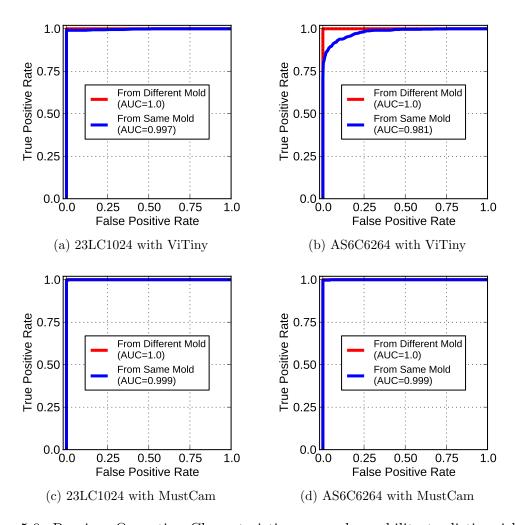

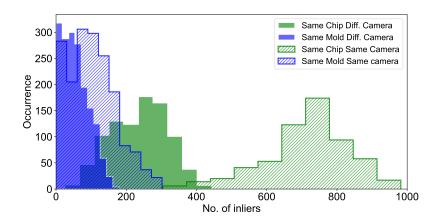

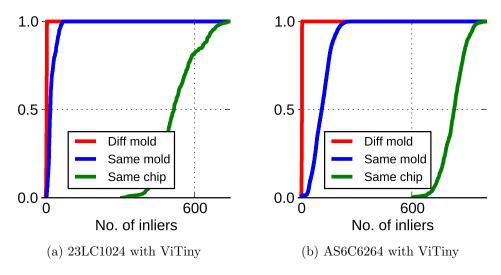

| 5.9  | Receiver Operating Characteristic curves show ability to distinguish enrolled chips from other chips created from a different mold than the enrolled chip, or from the same mold that produced the enrolled chip                                                                                                                                                                    |

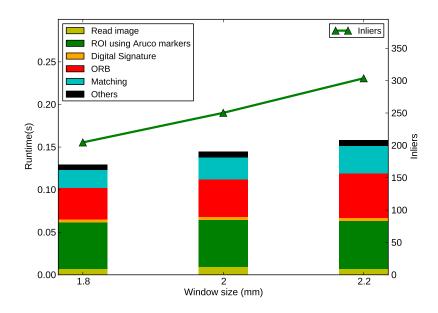

| 5.10 | Runtime of verification procedure, broken down by processing task, for different sizes of ROI. Keypoint density is held constant at $1,000/mm^2$ . The increase in keypoints for the larger ROI results in a higher runtime, but also increases the number of matching points that are found. Runtime can be traded against accuracy by adjusting the ROI size                      |

| 5.11 | SRAM when same ViTiny cameras are used for both enrollment and verification                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

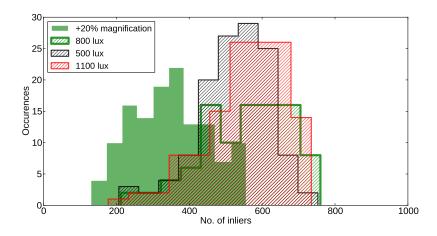

| 5.12 | Histogram of inliers in AS6C6264 SRAM under two alternative lighting intensities (nominal is 800 lux) and one alternative zoom                       |

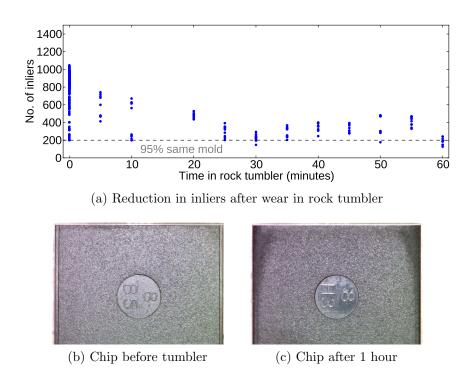

| 5.13 | Reduction in inliers for chip AS6C6264 after spending time in rock tumbler. Images of chip are included to give a sense of the amount of wear caused |

| 5.14 | Inlier CDFs for SRAMs under controlled alignment                                                                                                     |

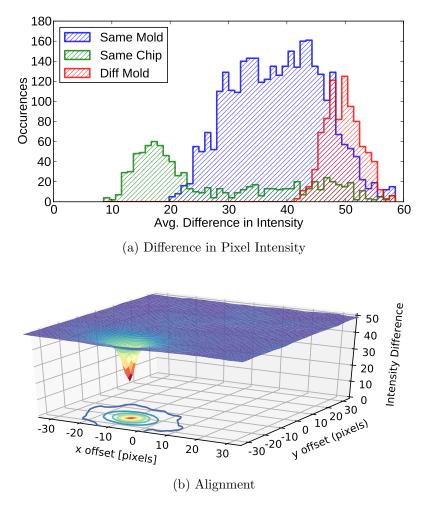

| 5.15 | PUF-like evaluation on raw pixel intensity data                                                                                                      |

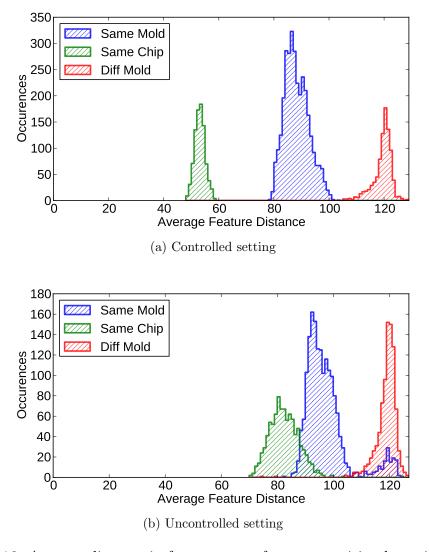

| 5.16 | Average distance in feature space for same-position keypoint pairs                                                                                   |

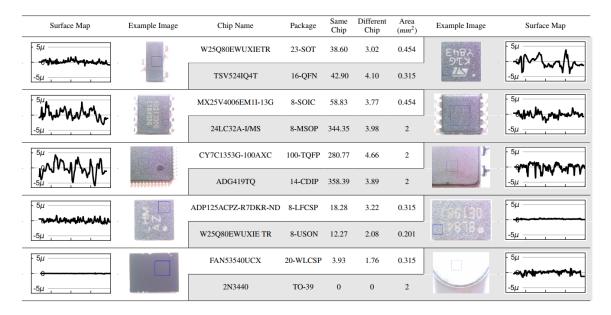

| 5.17 | Evaluation of package surface fingerprints across a range of package types                                                                           |

#### INTRODUCTION

Advances in the chip industry have enabled, at the time of this thesis, production of Integrated Circuits (ICs) with transistor channel lengths as small as a few nanometers. Miniaturization has opened avenues for ultra-lightweight systems such as the Internet-of-Things (IoT). Some of the multi-billion dollar [115] applications of IoT include smart homes and cities, operations and equipment optimization in factories, wearable/implantable medical devices and autonomous vehicles.

Ubiquitous computing often involves sharing personal and confidential data over the Internet. As a result security of IoT devices becomes important especially in critical applications like healthcare. Some of the unique challenges in IoT security include limited hardware resources, stringent power budgets, and cost constraints. Lightweight IoT devices like Radio Frequency Identification (RFID) tags and wireless sensor nodes are typically battery powered with energy budgets of less than a microjoule per bit of data processed [115]. Physically accessibility of these devices to an attacker opens a variety of security threats, both passive and active attacks.

The basic security services required of a cryptosystem are confidentiality, integrity, message authentication and nonrepudiation [87]. Block ciphers form an important building block in offering these services. Symmetric key encryption algorithms encrypt and authenticate data using a secret key. Advanced Encryption Standard (AES) is the most widely used symmetric key based block cipher. Dedicated hardware implementations of AES are used in millions of hardware chips worldwide to encrypt large blocks of data with better performance and power than can be achieved in software implementations.

Implementing cryptographic primitives such as AES for IoT systems is challenging due to cost constraints and power budgets. Designers exploit the symmetry in the operations of the AES algorithm to reduce the number of hardware units implemented and reuse them over time to save area. However block ciphers have data dependencies which these make lightweight implementations inefficient as a significant amount of energy is spent in moving data around to work around the dependencies.

Apart from efficiency concerns, AES can be vulnerable to *Side Channel Attacks* (SCAs) that target weaknesses of the hardware implementation to extract the secret key. Passive SCAs exploit correlation between computed data and the power consumption of hardware implementing AES to retrieve the secret key. Active attacks inject a fault in the AES computation and retrieve the secret key by comparing the outputs of faulty and faulty-free computations. Lightweight devices for IoT are especially susceptible to SCAs as they have low background noise power, are physically accessible to the attacker, and have low budget for defenses.

Besides the implementation weaknesses, the supply and distribution channels of ICs present a large, diverse and vulnerable attack surface. Counterfeit ICs such as phony parts, recycled, and remarked chips have made their way into critical defense and avionics systems. With ubiquitous computing, the problem of counterfeit parts becomes increasingly critical. IoT systems are often combining chips from different sources, and a single bad chip can compromise the entire system.

In this dissertation, we present a background to further understand some of the aforementioned problems, then provide novel and efficient solutions. The dissertation ranges on topics from silicon to package, covering the entire stack of a hardware system. We study the reasons for energy inefficiencies in state-of-the-art block ciphers and design micro-architectures that greatly mitigate inefficiencies under different scenarios. We support our claims with data from a testchip in an advanced commercial 16nm FinFET technology. We also present a novel IC authentication technique that

uses computer vision techniques to prevent counterfeits and can be deployed atop current infrastructure at almost no cost.

My specific contributions include:

- Developed glitch filtering techniques that allow partially and fully unrolled block ciphers to have an energy efficiency that is competitive with serialized implementations

- Designed a novel microarchitecture for lightweight AES implementations that minimizes data movement and clock activity to improve energy efficiency

- Enabled randomization of sub-round operations in lightweight AES architecture to mitigate side channel susceptibility

- Taped out AES designs in a commercial 16nm FinFET technology chip and tested efficiency and side channel resilience of the designs

- For the first time, showed that individual chip packages can be recognized and authenticated using intrinsic surface features extracted using low cost cameras and image processing

The remainder of the dissertation is structured as follows. Chapter 1 provides the necessary background about block ciphers, side channel attacks and supply chain security. Efficiency of unrolled block ciphers is addressed in chapter 2 through a new glitch filter design (published in Trans. on Computers 2017 [30]) enabling unrolled ciphers to be competitive with serialized designs but with the drawback of significant area costs. We next explore a novel lightweight AES architecture with side channel resilience in chapter 3. Our design significantly outperforms state-of-the-art and we published our work in ISLPED 2017 [32] and ISVLSI 2019 [31]. We further taped out our designs in 16nm FinFET technology and chapter 4 describes the design and evaluation of our testchip containing four AES designs. In chapter 5 we discuss our

novel IC package authentication methodology to verify provenance of ICs. We present concluding remarks in chapter 6.

## CHAPTER 1

# BACKGROUND

# 1.1 Block ciphers

Block ciphers are cryptographic primitives that encrypt and decrypt data, typically within a larger encryption mode of operation to help achieve security goals of confidentiality and authenticity for a cryptosystem. Block ciphers can also be used as part of hash functions. Typically, a block cipher algorithm iterates over a round function for a specified number of times using different round keys generated by the key schedule function. Substitution and permutation are two common operations found in the round functions of block ciphers. Symmetric key block ciphers such as DES and AES are used for data encryption due to their simple design and performance. Asymmetric algorithms such as RSA and ECC employ complex mathematical operations and are therefore used for key exchange and digital signatures. Now we describe the block ciphers AES and SIMON, as we will be using them in this thesis.

#### 1.1.1 AES

The Advanced Encryption Standard (AES) is a ubiquitous encryption standard [91] based on the Rijndael cipher. It was standardized by NIST in 2001 to replace DES following an open competition. AES uses a number of iterated rounds, 10 in the case of a 128-bit key strength, to transform a block of plaintext into a corresponding block of ciphertext. Each round (Fig. 1.1) operates on 128 bits of state, and uses a 128-bit round key to generate the next state from the current state. The major components of the round function are SubBytes, ShiftRows, MixColumns, and addition of the round key. The SubBytes function uses an S-Box circuit to apply the

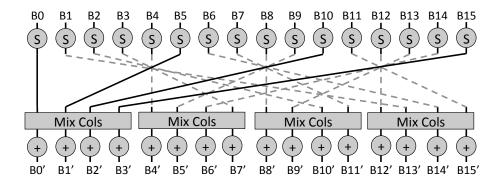

Figure 1.1: Structure of AES round function.

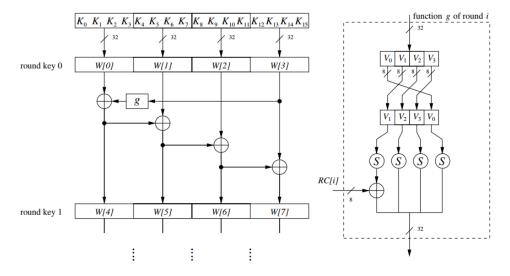

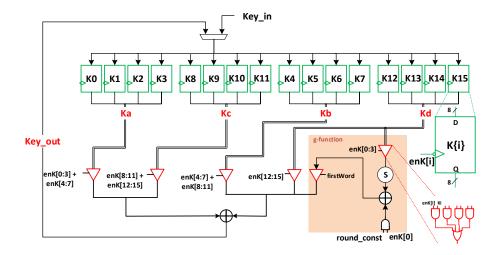

same byte-wise substitution function to each of the 16 state bytes. ShiftRows operation reorders the bytes. MixColumns operates on a 4-byte input  $\{s_3, s_2, s_1, s_0\}$  and produces a 4-byte output  $\{m_3, m_2, m_1, m_0\}$  as per Eq. 1.1. Finally the round key is added (XORed) to the output of MixColumns to create the next state that will be used as the input to the next round. The 128-bit round keys are expanded from a single 128-bit key input as shown in Fig. 1.2. Round key 0 is the input key and  $RC[i] = x^{i-1} mod(x^8 + x^4 + x^3 + x + 1)$  is the Round Constant of round i.

$$\begin{bmatrix}

m_0 \\

m_1 \\

m_2 \\

m_3

\end{bmatrix} = \begin{bmatrix}

2 & 3 & 1 & 1 \\

1 & 2 & 3 & 1 \\

1 & 1 & 2 & 3 \\

3 & 1 & 1 & 2

\end{bmatrix} \begin{bmatrix}

s_0 \\

s_1 \\

s_2 \\

s_3

\end{bmatrix}$$

(1.1)

# 1.1.2 **SIMON**

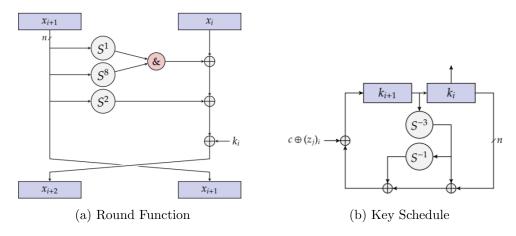

SIMON is a lightweight Feistel cipher suitable for resource constrained systems, and we use the SIMON-128 variant [13]. SIMON-128 uses a 128-bit key, 128-bit data, and requires 68 rounds for each encryption. A Feistel structure is symmetric in nature and offers the advantage of similarities in the encryption and decryption operations, which in turn reduces the required resources for a hardware implementation. The round function (Fig. 1.3a) is constructed to be extremely small in hardware and easy

Figure 1.2: Structure of AES 128-bit Key Expansion [87].

# 1.2 Energy efficiency in block ciphers implementations

Block ciphers are almost always implemented as components of a larger overall system-on-chip design, and this prevents the block cipher from being freely optimized independently of the other SoC components. For example, the block cipher will have to use the same fabrication process and supply voltage as the other components, and typically will share a common clock frequency to avoid clock generation and

Figure 1.3: SIMON round function and key schedule [13].

clock domain crossing. Therefore, any attempt at optimizing block ciphers may be constrained by these chip-scale implementation decisions.

Depending on the chip-scale requirements and constraints, the block cipher rounds can be implemented through sequential reuse of a single combinational block for each round, or they can be unrolled. If a design is serialized (no unrolling), one round function is computed in each clock cycle, and the number of cycles needed to encrypt a block is the same as the number of rounds in the block cipher algorithm. Yet at slow clock frequencies, the clock period may far exceed the critical path delay of a block cipher round. The latency of the block-cipher is then being increased unnecessarily due to the serialization of the round function. Unrolling has been explored in literature as a technique to instantiate multiple round functions per clock cycle and eliminate energy spent in loop control elements such as registers and multiplexers. However the energy savings are minimal and are offset by the increase in glitching power that comes with unrolling; we further explore this in Ch. 2.

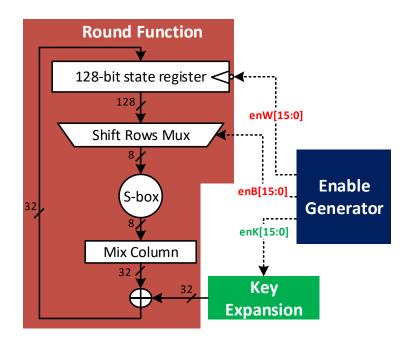

For resource constrained applications like IoT, lightweight implementations of block ciphers have been explored. Symmetry in sub-round operations has been leveraged by temporal reuse of limited hardware units to save area in ciphers such as AES [78, 47]. For example, if a single AES S-box (Fig. 1.1) is implemented in hardware

it can be reused to operate on different bytes across clock cycles. In this case one round is completed in 16 cycles. The increase in latency due to narrow datapath operation is acceptable in these non-performance critical applications. However, significant energy inefficiencies exist due to the storage of intermediate results and data movement which are explored and addressed in Ch. 3. Though lightweight ciphers such as SIMON have been proposed they are not used as extensively as AES.

# 1.3 Side Channel Attacks

Although encryption algorithms and protocols have been developed to provide security, hardware implementations can leak valuable information to an attacker. For example, data dependence in power consumption of a device can be exploited as a side-channel to extract its secret key. Such a security attack is termed a Side Channel Attack (SCA). Some examples of passive side-channels include encryption time, power consumption or electromagnetic radiation emanating from device that are correlated to the computed data [104]. Active attacks on the other hand inject faults into the computation by varying supply voltage, clock frequency, or exposing the device to lasers, and subsequently analyze faulty and fault-free outputs to retrieve the secret key [57, 104]. Combined active and passive attacks also exist [95].

## 1.3.1 Differential Power Analysis and metrics

Power side-channel attacks such as Simple Power Analysis (SPA) [64], Differential Power Analysis (DPA) [64] and Correlation Power Analysis (CPA) [22] leverage data dependency in power consumption to extract secret information. In a DPA attack, one would capture power traces  $T_0, T_1, ..., T_{m-1}$  while the encryption algorithm is running and record the corresponding ciphertexts  $C_0, C_1, ..., C_{m-1}$ . An internal node value b in the computation that is dependent on a few bits of round key and ciphertext is then chosen as a selection function. In AES, the attack is performed on values that

depend on only a single byte of round key at a time. Now the attacker guesses the key bits, and for each guess  $K_s$  he partitions the power traces  $T_0, T_1, ..., T_{m-1}$  based on the computed value of the selection function  $D(C_i, b, K_s)$ . The attacker then computes a differential trace  $\Delta_D$  as shown in Eq. 1.2. For the correct key guess, with enough power measurements a peak in the differential trace is observed at the time when the selection function is computed in hardware, due to the correlation between the predicted selection function and the differential average of power traces  $(\Delta_D)$ . For incorrect key guesses, a random partitioning of power traces results in a differential average that approaches zero with enough measurements.

$$\Delta_D[j] = \frac{\sum_{i=1}^m D(C_i, b, K_s) T_i[j]}{\sum_{i=1}^m D(C_i, b, K_s)} - \frac{\sum_{i=1}^m (1 - D(C_i, b, K_s)) T_i[j]}{\sum_{i=1}^m (1 - D(C_i, b, K_s))}$$

(1.2)

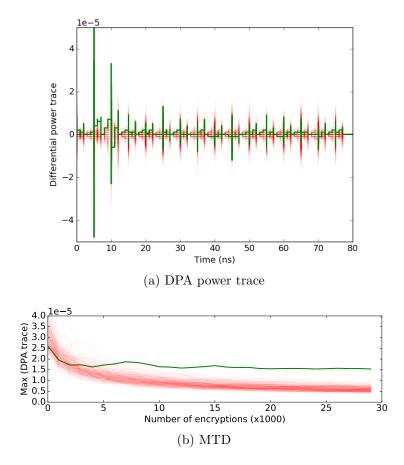

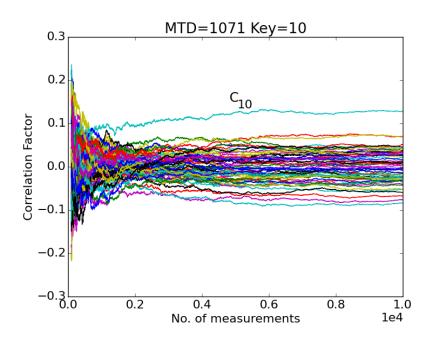

For example in a DPA attack on AES, by making power measurements the secret key of AES in a smart card is broken by using S-box input value as selection function. The attack works despite not being able to observe the S-box inputs. In Fig. 1.4a the differential power trace values for different key guesses are plotted. The correct key guess (green line) has a higher DPA peak than incorrect key guesses (red lines). With enough measurements only the correct key guess has a consistently high DPA peak as seen in Fig. 1.4b. **Measurements to Disclosure (MTD)** [107] is the number of measurements required to distinguish the correct key guess from incorrect ones. MTD is defined as the cross-over point between the differential peak of the correct key guess and the maximum differential peak of all the wrong key guesses. In Fig. 1.4b we see an MTD of about 13K encryptions. Even though we demonstrate DPA with AES, side-channel attacks can also break insecure implementations of other cryptographic algorithms such as RSA and DES [63].

Figure 1.4: Illustration of a DPA attack on AES.

#### 1.3.2 Existing countermeasures

A number of circuit-level countermeasures exist for side-channels. Circuit-level countermeasures are imperfect but can drastically decrease the signal-to-noise ratio of the information leaked through the side channel. One family of countermeasures tries to modify the power delivery system so that the power consumed by the encryption circuit will not be externally visible to the attacker. Switched-capacitor designs can isolate the sensitive computation from main power by sourcing its current from a capacitor and then discharging the capacitor to a fixed value before replenishing it [108]. On-chip low-dropout regulators [100] can also be used to obscure the power consumption of the sensitive circuit.

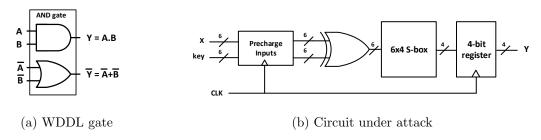

A second family of circuit-level countermeasures are modified logic styles that try to achieve a power consumption that is independent of the values being computed. SABL and WDDL [105] are differential logic styles that always compute both true and complement values of each node so that power consumption is unrelated to the computed value; these logic styles require careful routing to balance the loading on the differential signals, but given enough measurements can still be attacked due to unavoidable small imbalances in the differential routing [107]. Masked dual-rail precharge logics seek to avoid routing constraints by using a random mask to reduce correlation between power consumption and processed data [90, 89], but are costly in area.

Another approach to preventing side channel attacks, which can be complementary to circuit-level countermeasures, is hiding the timing of the computation from the attacker. An attacker that does not know when a certain key byte is processed will have difficulty aligning the power traces in the way that is required for DPA attacks. Timing randomization can easily be accomplished by inserting idle delays, but idle delays can be identified in the power trace and removed by the attacker. Randomly inserting dummy encryptions or dummy rounds between meaningful computations adds a delay that cannot easily be detected and removed in post-processing, but consumes significant power and latency and requires added complexity around the cipher. We further explore efficient timing randomization in Sec. 3.2.

#### 1.3.3 Logic State Based Leakage Power Analysis

Side-channel attacks have primarily focused on dynamic power as it has typically been assumed to be the main contributor of the power consumption. However with today's technology scaling, leakage power has become a significant contributor as well. While the countermeasures such as WDDL, SABL mitigate the information leakage

Table 1.1: Simulated Dynamic and static power consumption of a WDDL-AND gate.

| Input State | Absolute currents |                  | Normalized to state 00 |        |

|-------------|-------------------|------------------|------------------------|--------|

|             | Dynamic $(\mu A)$ | Static $(\mu A)$ | Dynamic                | Static |

| 00          | 9.83              | 0.174            | 1.00                   | 1.00   |

| 01          | 9.80              | 0.231            | 1.00                   | 1.33   |

| 10          | 9.73              | 0.206            | 0.99                   | 1.18   |

| 11          | 9.82              | 0.238            | 1.00                   | 1.37   |

through dynamic power consumption, the secret data can still be vulnerable through the analysis of leakage power.

Leakage Power Analysis (LPA) attacks are relatively new and have not been as thoroughly explored as dynamic power attacks. The overall leakage power of a cryptographic core is related to the secret data [43] and DPA techniques can be applied to leakage power in the presence of process variations [70]. Effectiveness of a Hamming Weight based LPA attack on cryptographic cores has been studied for various side-channel resistant logic styles in the presence of noise and process variations [6].

WDDL and other side-channel resistant logic styles offer resistance against dynamic power attacks. However, WDDL still has a significant data dependence in the static (leakage) power consumption (Tab. 1.1). Dynamic power can be made arbitrarily balanced (using SABL for instance) but static power cannot. We leverage the data dependence of static power to predict the total leakage power consumed by a circuit and from this extract secret information such as cryptographic keys. We name our scheme Logic state based Leakage Power Analysis (LLPA) [33].

We assume the attacker has knowledge of the circuit's implementation (in terms of logic gates) and is able to observe primary outputs and measure power consumption. Note that our assumption that an attacker knows the exact gates implemented inside of a design is increasingly a very practical assumption, as this technique has been employed in security research [86, 101], and one can even purchase this information commercially through companies such as Chipworks. Even if a design uses camou-

Figure 1.5: Schematics for LLPA.

flaged gates [92], the functionality of gates can often be extracted [77, 71]. Also, note that the internal state is unobservable in the attack model and is predicted with design knowledge and known data inputs.

To demonstrate our methodology, we choose to attack in simulation a 6x4 S-box used in DES and retrieve the secret key. The schematic of our circuit is shown in Fig. 1.5b. The static current of each gate type for every gate input combination is obtained in a pre-characterization step. For each data input the attacker guesses the key value  $K_j$  and computes the logical input state of each gate in the design. Under a key guess, state dependent static currents of all gates are summed up to compute a predicted static power  $P_j$  for the entire design. This is repeated for all key guesses j = 0, 1, ... 63 and the correlation  $C_j$  between static power predictions  $P_j$  and measurement M is computed per Eq. 1.3. With enough measurements only the correct key guess should have a consistently high correlation value. Fig. 1.6 shows a successful attack with an MTD of 1071 measurements.

$$C_j = \rho_{M,P_j} = \frac{covariance(M, P_j)}{\sigma_M \sigma_{P_j}}$$

(1.3)

#### 1.3.4 Remote Side Channel Attack on FPGAs

As part of my thesis, I collaborated with students from the Reconfigurable Computing Group at UMass to investigate a remote side channel attack on FPGAs which I describe in this section. The FPGA implementations described in this section were

Figure 1.6: A successful attack using LLPA.

done by my colleagues. I was responsible for developing the attack methodology and related software code. This work was published in 2018 [93].

Field Programmable Gate Arrays (FPGAs) are quickly growing in importance in a variety of computing spaces including cloud computing and embedded platforms (automotive, military, and aerospace). As FPGAs grow in size and complexity, it is apparent that numerous applications from independent users may simultaneously reside in a single FPGA device. This use of *multi-tenant* FPGAs opens the door to numerous potential attack vectors on unsuspecting co-located FPGA circuits. Although FPGA devices in cloud computing environments such as Microsoft Catapult [4] and Amazon EC2 F1 [1] are currently dedicated to a specific application, the growing capabilities of FPGAs makes it easy to envision single-FPGA platforms containing multiple independent applications created by completely separate entities.

The discovery of a covert communication channel between neighboring FPGA long wires (also called "long lines") has the potential to dramatically change the threat level of multi-tenant FPGAs. In a comprehensive set of experiments, Giechaskiel et

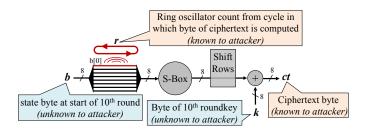

Figure 1.7: FDPA Attack setup

al. [42] showed that the logic value carried on a long wire influences the delay of both its immediate neighbor and a long wire in the same channel two wires away. When a logic 1 value is carried on a wire (the transmitter), the delay in the neighboring wire (the receiver) is reduced relative to when a logic 0 is transmitted. We leverage this information leakage by implementing a Ring Oscillator (RO) near a long wire (the victim), and use a binary counter to measure the RO's frequency: we increment a 32-bit count value at every positive edge of RO clock for a fixed time duration. The count values will depend on the data being transmitted on the victim wire.

Our Frequency DPA (FDPA) attack draws inspiration from DPA. As an example, we demonstrate the working of FDPA on AES to retrieve the secret key. The relevant portion of the AES final round circuit for attacking a key byte, using information leaked from a single wire, is shown in Fig. 1.7. Recall that the final round of the AES algorithm performs bytewise substitution (S-Box), shift rows, and key addition using XOR, but it omits the mix columns operation. The output of the final round is the ciphertext, which is public information. To set up the attack scenario for recovering a key byte, the attacker chooses as the victim any bit of S-Box input that is routed on a long wire; in Fig. 1.7, bit 0 of the S-Box input is chosen as the victim. The ring oscillator is then routed next to this signal so that its oscillation count in each clock cycle will depend slightly on the value of the S-Box input bit.

Using the ring oscillator as a sensor, the attacker monitors many encryptions to collect information for the side channel attack. For each of n encryptions performed,

the attacker records the ciphertext byte and the ring oscillator count during the cycle the ciphertext byte was produced; we denote these two quantities as  $ct_i$  and  $r_i$  respectively for the  $i^{th}$  encryption. After n encryptions, the attacker has a collection of measured oscillator count and ciphertext pairings  $(r_0, ct_0), (r_1, ct_1), \ldots, (r_{n-1}, ct_{n-1})$ . Among the 256 possible key byte values, the attacker correctly identifies the key byte used in the circuit based on side channel measurements as follows. For each key guess  $k_j$  (i.e.  $k_0 \ldots k_{255}$ ), the attacker computes an S-Box input value  $b_{i,j}$  for each of the  $i \in [0, n-1]$  measurements using Eq. 1.4 to invert the circuit's round key addition and S-Box computation.

$$b_{i,j} = S^{-1} \left( ct_i \oplus k_j \right) \tag{1.4}$$

By inverting the S-Box function under key guess  $k_j$ , the attacker now knows what S-Box input value would have induced ciphertext  $ct_i$  if the key byte was in fact  $k_j$ . For key guess  $k_j$ , the computed values at the S-Box input in the n encryptions would be denoted  $b_{0,j}, b_{1,j}, \ldots, b_{n-1,j}$ . The predicted S-Box inputs each contain a specific prediction on the value of the victim wire (bit 0 of the S-Box input), and we check for its effect on the oscillator counts to know whether  $k_j$  is the correct key byte value. The attacker next partitions the n measurements into two subsets according to whether the victim wire would have a 0 or 1 value under the key guess  $k_j$  – one subset contains all the measured RO counts  $(r_i)$  for encryptions when the victim would have a 1 value, and the other subset contains all the measured RO counts when the victim would have a 0 value. The attacker then uses the average RO counts of the two subsets to confirm or refute his guess that  $k_j$  is the key byte value as follows:

• If the key byte is in reality  $k_j$ , then partitioning according to key guess  $k_j$  is accurately partitioning the data based on whether the victim is 0 or 1. The average RO count will tend to be higher in the subset of encryptions that predict a 1-value for the victim wire, and lower in the subset of encryptions that predict

a 0-value. Observing a sufficient difference between the average RO counts in the two subsets confirms that the partition is meaningful, and thus supports the hypothesis that the correct key byte value is  $k_j$ .

• If the key byte is not in reality  $k_j$ , then partitioning according to key guess  $k_j$  is arbitrary and not correlated to the computation of the circuit. Because the partition is arbitrary, each subset will contain a similar proportion of RO counts taken when the victim wire is 0 and 1. In this case, the average RO count from each subset will be similar, and the difference between the average RO counts of the two sets will approach 0 with enough data. Observing no difference between the average RO counts of the two subsets therefore serves to refute the hypothesis that the key byte value is  $k_j$ .

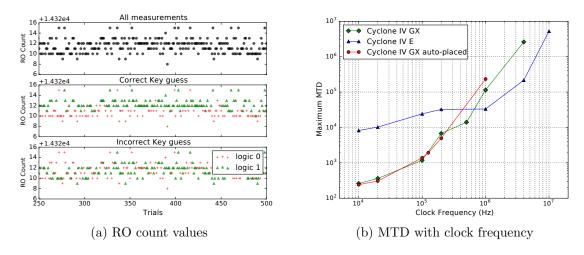

Fig. 1.8a shows graphically how a collection of RO counts can confirm or refute a key guess. The attacker in this case collects 500 RO counts and corresponding ciphertexts; the RO counts for the measurements are shown in the top plot of Fig. 1.8a. The middle plot shows which of the counts are predicted, according to the correct key guess, to occur when the victim wire is 1 and 0. We can see that, in measurements when the key guess predicts the victim wire to have a 1 value, the RO counts tend to be higher. The significant difference in average RO counts gives an attacker confidence that the key guess is correct. The lower plot of Fig. 1.8a uses an incorrect key guess to predict the 1 and 0 values of the victim wire. Using this key guess there is no difference between the average RO counts, indicating to an attacker that the key guess is not the correct one. Using this approach, with enough side channel data, the attacker will be able to identify the correct key byte guesses, even when the difference between the average RO counts is quite small. Successful attacks were performed on different FPGAs at clock frequencies upto 10MHz and the MTDs are shown in Fig. 1.8b.

Figure 1.8: FDPA in action.

# 1.4 Supply Chain Security

ICs take on critical roles in today's society, but the supply and distribution channels for ICs are vulnerable to a variety of security threats. One such threat is counterfeit parts, which are a significant and increasing threat to the reliability of electronic systems. Counterfeits are defined by the US Department of Defense as "unauthorized copies and previously used parts that are made to look new, and are sold as new" [94]. Misrepresented ICs such as speed binned parts that are remarked to a higher speed grade to increase selling price [88] can also be considered counterfeits. Prior research claims that recycled and remarked chips together make up 80% of all counterfeiting incidents [45]. These types of counterfeit parts are enabled by a lack of traceability through distribution channels as parts change hands through resellers and system integrators. DARPA notes that chain-of-custody solutions are unworkable for securing distribution due to components that may change hands 15 times before final installation [67]. Our work addresses this critical security problem by giving an approach for securing parts through distribution without chain-of-custody.

Estimates variously place the direct losses from electronics counterfeiting at \$3B-\$7.5B [55], and the potential risk due to counterfeiting at \$100B-\$200B [88, 84]. The

most commonly counterfeited electronics are said to be analog ICs, microprocessors, memories, programmable logic, and discrete transistors [52, 45]. Documented cases of counterfeit parts include purported microcontrollers that were found to be remarked voltage regulators [103], four instances of counterfeit parts in the Avionics Systems of C-27J aircraft [98], and refurbished flash memory devices in Terminal High-Altitude Area Defense (THAAD) mission computers that led to a recall of 50 systems [94]. Counterfeit parts such as these present clear security risks which we address in Ch. 5.

### CHAPTER 2

### EFFICIENCY IN UNROLLED BLOCK CIPHERS

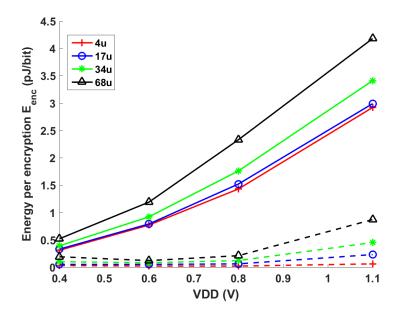

Unrolling a block cipher is the process of instantiating multiple rounds of the algorithm combinationally to be completed within each clock cycle. Unrolling allows the result to be computed in fewer cycles at the cost of increased area of the combinational circuit. Unrolling also saves some amount of register energy, as energy is not spent storing signals at the output of each round like the fully serialized case. The unrolling of block ciphers as an energy optimization technique has been explored in a number of recent works [58, 11]. Switching power, especially due to glitches, is a challenge in unrolled implementations of a block cipher. In this chapter we present an efficient latch-based glitch filter for unrolled designs that reduces energy per encryption by an order of magnitude over a straightforward unrolled implementation, and by 28-45% over the best existing glitch filtering schemes. We explore the optimal number of glitch filters to use for minimizing total energy, and provide estimates of the area cost. Power gating to reduce leakage power and reuse of computed key enable unrolled designs to be more efficient than serialized ones. We demonstrate our approach on the SIMON-128 and AES-128 block ciphers.

# 2.1 Glitches and glitch filtering

The limiting factor in energy minimization of block ciphers is switching energy.

This is especially true in unrolled block ciphers because combinational logic glitches at the input of each round diffuse through the round to cause more glitches at the output of the round. Leakage power is small relative to switching power for typical

clock periods and technologies used in low power designs [58]. Fundamentally, glitches occur because of mismatched arrival times of gate inputs. This causes the gate output to switch once when the first input arrives, and then switch again when the next input arrives. These two switching events then propagate to many other nodes and cause more switching events in a cascading fashion.

Several techniques to filter glitches have been proposed in literature. Pipelining [19, 114] stops glitches because they cannot propagate through a register, as a register can change its output value only once per clock cycle upon arrival of the clock transition. Gate-freezing [14] stalls the computation in a gate by using an NMOS footer transistor to filter 1-to-0 transitions. The stalled gate is allowed to compute only when its inputs have reached their final state. The scheme has a limitation in that it allows 0-to-1 transitions to pass through a stalled gate. Retiming [81] by moving or adding flip-flops in the datapath to high activity nodes that have a large fanout can reduce glitches and save power. Yet another approach is delay balancing to equalize input arrival times at a gate and reduce the number of output switching events [66, 51].

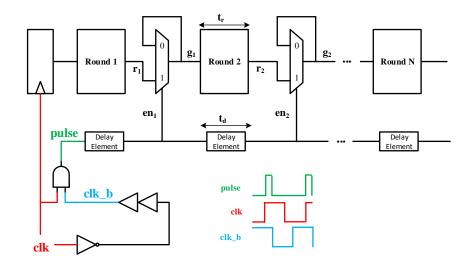

An AND gate based glitch filtering scheme (Round Gating) has recently been proposed in [9]. The output signals of each round in this scheme are gated by AND gates that wait on an enable signal. The enable signal is derived from a delayed clock such that it goes high to propagate the round outputs through the AND gates only after they have stopped glitching and become stable. A drawback of this scheme is that the enable signals must be reset low between the end of one computation and the start of the next in order to stop propagation of the glitches in the next operation. When the enable signals go low, waves of 0s propagate forward from the glitch filters and through the circuit to charge and discharge the nodes in the round functions similar to a normal computation of the round function. Effectively, resetting the glitch filters is thus causing a second, unnecessary, power-wasting computation to

occur. State-retaining barriers [83] provide a mechanism for preventing this power-wasting computation. The use of state-retaining elements is effective for reducing glitching in FPGAs [69, 27, 35].

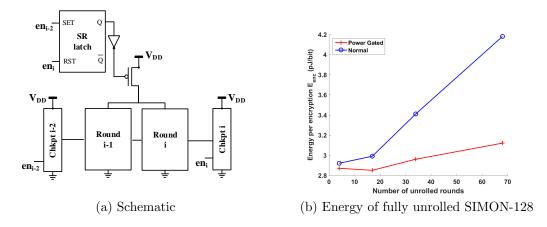

## 2.2 Checkpointing to improve energy efficiency

Combinational checkpointing is a microarchitectural technique to increase energy efficiency in a combinational circuit by filtering glitches. We propose a new standard-cell compatible glitch filtering mechanism [29, 30] as shown in Fig. 2.1. The topology is similar to that of round gating using AND gates [9], except that the glitch filtering element consists of a positive latch implemented using a multiplexer (MUX) at the output of the round function. The purpose of the filter is to make sure that any glitching activity from its input is not propagated to its output.

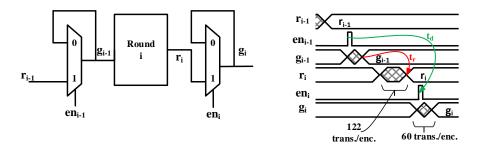

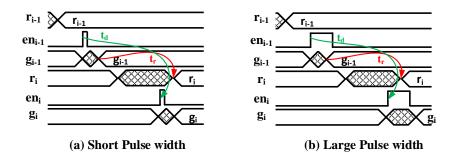

The operation of the filter is as follows. The MUX holds on to its previous output value when the enable (select) signal is low, and becomes transparent when enable is high. This causes the latch to be transparent only during the enable pulse. The enable pulse is generated at the rising edge of the clock as the AND of the clock signal and a delayed inverted version of clock. The enable pulse is propagated to the glitch filters combinationally with timing controlled by adding a delay element per round function. If the propagation delay of the delay element  $(t_d)$  is greater than the critical delay of a round function  $(t_r)$ , then round output  $r_i$  stabilizes before the rising edge of signal  $en_i$ , so the latches only become transparent after the glitching has stopped. Therefore, when this timing condition  $(t_d > t_r)$  is satisfied, glitches generated in round i do not propagate through the glitch filters to round i + 1. Because the latch stays open for the duration of the enable pulse, the circuit will function correctly as long as the round outputs stabilize before the falling edge of  $en_i$ , but the circuit will not filter any glitches that arrive when the latch is open, and the glitch filter will not have the intended effect.

The timing waveform for a single round of SIMON-128 is shown in Fig. 2.2. When the enable signal pulses at the first glitch filter, the stable outputs of round i-1 propagate through round i and cause a total of 122 transitions on the 128 round output signals. The round outputs wait for the enable signal to arrive at the second glitch filter, and upon its arrival, only 60 transitions occur on the inputs of round i+1; these 60 transitions are single transitions on 60 of the 128 signals, which is close to the expected number of bits that would differ between two uncorrelated 128-bit signals. In this case, the filter has prevented all the spurious glitches from propagating across rounds.

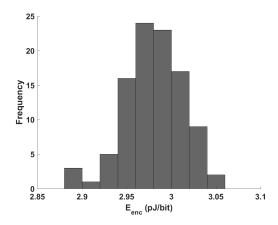

The propagation delay of the round function  $(t_r)$  can be determined through static timing analysis, and propagation delay of the delay element  $(t_d)$  can be configured to exceed  $t_r$  by a conservative 20% margin. This timing margin provides resilience against PVT variations and ensures that the enable signal always arrives after the round computation is complete. If the enable pulse arrives at a checkpoint before the round computation has completed, glitches will propagate through the open latch, but the computation can still be functionally correct as long as the round outputs stabilize before the falling edge of the enable pulse closes the latch. Correct functionality requires  $t_r < t_d + w$ , where w is the enable pulse width, and glitch free operation requires  $t_r < t_d$ . Therefore, a more aggressive  $t_d$  can be chosen by widening the enable pulse to tolerate variations as illustrated in Fig. 2.3. Widening the enable pulse allows performance improvements by paying a small (glitching) energy cost, and can be useful if only a few instances of the round function are slow due to process variations. The enable pulses can be made very wide as the input to a round function does not change until the next clock cycle, and the enable pulses can even be delayed versions of the clock signal.

Figure 2.1: Schematic of latch-based checkpoints for glitch filtering.

Figure 2.2: Timing diagram of glitch filter operation, annotated with the number of switching events happening at each point in the circuit for SIMON-128.

Figure 2.3: Increasing pulse width of enable signal to tolerate variations.

## 2.3 Evaluation of Checkpointing

### 2.3.1 Methodology

We use the SIMON and AES block ciphers to study the effectiveness of our glitch filtering scheme. SIMON is a lightweight Feistel cipher suitable for resource constrained systems, and we use SIMON-128 [13], which has a 128-bit key, 128-bit block size, and requires 68 rounds for each encryption. AES refers to three standardized variants [91] of the Rijndael cipher, based on a substitution-permutation network. Relative to SIMON, AES is a more complicated design, and we specifically use the widely used variant, AES-128; which has 128-bit block size, a 128-bit key, and requires 10 rounds per encryption. The RTL for both designs are written by us and validated for correctness against software implementations. To give an idea of the relative scales of the two ciphers, the round and key functions of fully unrolled SIMON require around 30,000 gates, whereas the round and key functions of fully unrolled AES are 4 times larger, requiring around 122,000 gates.