This is a repository copy of Avoiding diamonds in desynchronisation.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/158374/

Version: Accepted Version

## Article:

Beohar, H. orcid.org/0000-0001-5256-1334 and Cuijpers, P.J.L. (2014) Avoiding diamonds in desynchronisation. Science of Computer Programming, 91, Part A. pp. 45-69. ISSN 0167-6423

https://doi.org/10.1016/j.scico.2013.12.002

Article available under the terms of the CC-BY-NC-ND licence (https://creativecommons.org/licenses/by-nc-nd/4.0/).

## Reuse

This article is distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) licence. This licence only allows you to download this work and share it with others as long as you credit the authors, but you can't change the article in any way or use it commercially. More information and the full terms of the licence here: https://creativecommons.org/licenses/

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

eprints@whiterose.ac.uk https://eprints.whiterose.ac.uk/

# Avoiding Diamonds in Desynchronisation

H. Beohar<sup>a,\*</sup>, P. J. L. Cuijpers<sup>b</sup>

<sup>a</sup>Center for Research on Embedded Systems, Halmstad University, 301 18, Halmstad, Sweden

<sup>b</sup>Department of Mathematics and Computer science, Eindhoven University of Technology,

PO Box 513, 5600 MB, Eindhoven, The Netherlands

#### Abstract

The design of concurrent systems often assumes synchronous communication between different parts of a system. When system components are physically apart, this assumption becomes inappropriate. Desynchronisation is a technique that aims to implement a synchronous design in an asynchronous manner by placing buffers between the components of the synchronous design. When queues are used as buffers, the so-called 'diamond property' (among others) ensures correct operation of the desynchronised design. However, this property is difficult to establish in practice.

In this paper, we give sufficient and necessary conditions under which a concrete synchronous design (i.e., without the unobservable action) is equivalent to an asynchronous design and formally prove that the diamond property is no longer needed for desynchronisation when half-duplex queues are used as a communication buffer. Furthermore, we discuss how the half-duplex condition can be further relaxed when the diamond property can be partially guaranteed. To illustrate how this theory may be applied, we desynchronise the synchronous systems that are synthesised using supervisory control theory.

*Keywords:* Synchrony to Asynchrony, Desynchronisation, Branching Bisimulation, Equivalence Checking of Infinite State Systems

#### 1. Introduction

Message passing [1] is a programming paradigm in which software components send and receive messages either synchronously or asynchronously. In synchronous communication, components must be physically coupled making it possible to execute corresponding send and receive messages simultaneously. Asynchronous communication is used when components are placed physically apart. The corresponding send and receive messages are then decoupled and the messages travel via a buffer from a sender to its recipient.

A problem with asynchronous communication is that the presence of buffers makes ensuring the correctness of a system a non-trivial task. In general, if the buffers are modelled to have infinite capacity, analysing correctness of such systems is undecidable [2]. But also, if the buffers are modelled to have finite capacity, we may still face the state-space explosion problem.

It helps to separate concerns by first designing a correct synchronous system and then desynchronising it. The challenge is then to design the synchronous system in such a way that the addition of communication buffers does not alter its behaviour (in any relevant way) [3]. A synchronous system that is not altered by the addition of communication buffers is called *desynchronisable*.

In the context of web-services [4, 5], the focus is on effective analysis (like deadlock freedom, choreography analysis) of an asynchronous system by developing *synchronisability* techniques. Their idea is to make an asynchronous system synchronous, which is in contrast to desynchronisability, where a synchronous system is made asynchronous.

\*Corresponding author

Email addresses: harsh.beohar@hh.se (H. Beohar), P.J.L.Cuijpers@tue.nl (P.J.L.Cuijpers)

Thus, synchronisability techniques are applicable when the components of a system are designed under asynchronous communication from the start (for instance, in web-services), whereas desynchronisability techniques are applicable when the components of a system are designed under synchronous communication from the start (for instance, in supervisory control [6]).

Despite these differences both approaches aim to establish an equivalence between a synchronous system and its asynchronous version. In [4], the authors showed that the existence of a weak bisimulation relation between a deterministic synchronous system and its asynchronous system with one place queues is sufficient and necessary for synchronisability modulo weak bisimulation. Our work differs from [4] as we propose conditions for desynchronisability solely on a given (possibly nondeterministic) synchronous system.

In this paper, we show that the conditions *well-posedness*, *independence of external actions*, *input determinism*, and *diamond property* on a synchronous system are necessary and sufficient for desynchronisability. Intuitively,

- two communicating processes in a synchronous system are well-posed if both the processes are able to receive each other's requests.

- the external actions (i.e., actions that are not involved in synchronisation) are independent in a synchronous system if the communicating processes can always delay the execution of their own external actions in favour of receiving a sequence of messages, without any consequence on the future behaviour of the system.

- input determinism states that the communicating processes should not make nondeterministic choices upon the reception of messages.

- the essence of the diamond property is that when two components both wish to communicate a message, say  $\alpha$  and  $\beta$ , then communication of  $\alpha$  will not block communication of  $\beta$ , and vice versa. Furthermore, the order of communication will not influence the future behaviour of the system.

In previous research [3, 7–9], well-posedness and the diamond property were already present as sufficient conditions for desynchronisability, while the other two properties are new with respect to these references because external actions were not allowed in the specification of communicating processes and the equivalences studied in these papers were coarser than branching bisimulation<sup>1</sup>. Table 1 provides the list of buffers and equivalences studied previously in the context of desynchronisation.

| References              | Buffers | Equivalences           |

|-------------------------|---------|------------------------|

| Udding [9]              | Wires   | Trace equivalence      |

| Balemi [7]              | Queues  | Trace equivalence      |

| Fischer and Janssen [3] | Bags    | Failure equivalence    |

| Beohar and Cuijpers [8] | Bags    | Branching bisimulation |

Table 1: Buffers and equivalences studied previously in the context of desynchronisation.

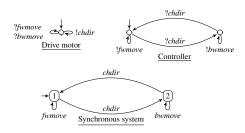

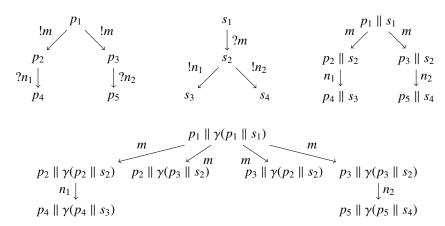

As it turns out, the diamond property is difficult to establish in practice, while in particular input determinism and independence of external actions can be easily obtained by construction, at least for supervisory control synthesis [6]. As an example why diamond property leads to practical problems, consider a simplified model of a controlled drive-motor [11]. The drive-motor can move in a forward direction '*fwmove*' or in a backward direction '*bwmove*', and it has a signal '*chdir*' indicating when it is safe to change this direction. A controller communicates with the drive-motor to ensure that the event '*chdir*' always executes before altering the direction of the motor. The models of the drive motor, the controller, and the synchronous system are shown in Figure 1, where !a (?*a*) denotes that an action *a* is sent (received) and *a* denotes the synchronization of !a and ?*a*.

Observe in the synchronous system of drive-motor that the execution of the event '*chdir*' from state 1 to state 2 disables the execution of the event '*fwmove*'; thus, violating the commutativity of the traces *chdir.fwmove* and

<sup>&</sup>lt;sup>1</sup>We claim that input determinism as a sufficient condition disappears when studying desynchronisability modulo any equivalence coarser than contra-simulation cf. [10, Chapter 4].

Figure 1: An illustration showing the impossibility of establishing the diamond property in certain synchronous systems.

*fwmove.chdir*. Similarly, the commutativity of the traces *chdir.bwmove* and *bwmove.chdir* is prohibited in this synchronous system. As a result, the synchronous system in Figure 1 does not satisfy the diamond property. In fact, the control requirement implicitly requires the diamond property to be broken. Therefore, it is impossible to desynchronise this system unless we adapt the model of plant or supervisor, or we adapt the way in which the desynchronisation is performed.

Studying the origin of the diamond property, we notice that it is caused by the type of buffer that is used for communication. The authors of [3, 7, 9] follow [2] in taking two unidirectional FIFO queues as a means of communication. In [3] a separate unidirectional FIFO queue is used for each type of message, which effectively leads to a *bag*-type of buffering (cf. [8]). Both types of buffer are useful abstractions of a physical communication layer with a protocol layer on top. For example, queues nicely represent the use of the TCP/IP protocol, while bags represent a UDP-like protocol [12]. Note that both approaches require the diamond property, essentially because both approaches allow the messages  $\alpha$  and  $\beta$  to be present in the buffer at the same time and arrive in arbitrary order.

Our research hypothesis is that it may be possible to find better desynchronisability conditions by changing the properties of the communication protocol. So far, research has focussed on the properties that the communicating components should have in order to ensure desynchronisability. The buffer is usually taken to be a queue or, incidentally, a bag. In this paper, we reconsider these properties, and alter them by changing the communication protocol if desired.

A first step in that direction is shown in this paper. We prove that the troublesome diamond property can be avoided by changing the type of buffer used for desynchronisation to so-called *half-duplex* communication (also used in [13] for model-checking asynchronous systems). In the context of two communicating processes, half-duplex communication means that a component is only allowed to send a message when its input buffer is empty. As a result, the buffering between the two processes alternates in each direction, having to become empty before alternating. We show that in this case a synchronous composition is desynchronisable if and only if it is *well-posed*, *independent of external actions*, and *input deterministic*.

These properties are generally weaker than the properties in [3, 7–9], and we are able to give a general method to adapt systems that are synthesised using supervisory control theory to satisfy these properties. In Section 4, we show how to obtain a well-posed supervisor for a given plant, whenever there exists a supervisor for the same plant. Our motivation in selecting supervisory control theory of Ramadge and Wonham [6] as our application domain is due to the inexact synchronisation problem, which prevents in applying this theory in practice (see [14]). The issue is that the existing supervisory control theory assumes synchronous interaction between a plant and its supervisor, whereas in practice the interactions between a plant and its supervisor are implemented asynchronously.

The use of half-duplex communication to restrict the behaviour of an asynchronous system is not new; see, for instance, [13, 15]. Furthermore, the authors of [13, 15] also gave conditions under which the behaviour of an asynchronous system is insensitive with the use of half-duplex or full-duplex queues. Intuitively, these conditions prevent the so-called *mixed states* (a state is mixed [13] if an input and output action is enabled from that state) in the specification of the communicating processes. Thus, this provides an alternative way to avoid diamonds in an asynchronous system. Nevertheless, we consider the prohibition of mixed states in a specification restrictive, at-least for control purposes [6], where the plants and their supervisors are allowed to have mixed states (for instance, see the case-study described in [11]). In addition, these mixed states also arise naturally when the communicating processes itself are composed with the parallel composition operator, which we do allow in our setup.

It is our hope that this paper will initiate discussion on the separation of concerns regarding desynchronisation. Our use of a half-duplex buffering strategy indicates that the communication protocol is essential in this separation. Admittedly, the choice for half-duplex communication is an odd one from the perspective of efficiency. The half-duplex protocol essentially makes components wait for each other, which makes communication slow. In Section 5, we sketch a first step to remedy this by recognising when actions are independent of each-other. Independent messages satisfy the diamond property and can therefore be processed in a full-duplex way. However, more research is needed to complete this claim and to find out when the half-duplex condition is in fact necessary for desynchronisability, and when it can be dropped for the sake of efficiency.

The methods we use for studying desynchronisability in this paper stem from process algebra and concurrency theory (see e.g. [16]). We do not fix a set of desirable properties a priori, but rather aim for desynchronisability modulo a behavioural equivalence that preserves a large set of possibly desirable properties. The desynchronisability question is therefore posed as: given two processes p and s, under which conditions are the synchronous composition and the asynchronous composition of p and s behaviourally equivalent? To be as general as possible, we take branching bisimulation as our behavioural equivalence of choice, which is the strongest equivalence used in interleaving semantics [17]. Note, that in many of the earlier works, weaker equivalences were used, but this did not lead to weaker desynchronisability conditions. Therefore, using a stronger equivalence does not pose a restriction here, while it does improve the applicability of the desynchronisation theorem.

In this paper, we show that our sufficient conditions for desynchronisability are also necessary for concrete (without silent steps) synchronous systems. To establish this result, we need to observe whether there are no more pending messages in a channel of an asynchronous system. We model this observation by a predicate, called *empty-buffer* predicate. Now by enriching the transfer condition of branching bisimilarity (just like how the termination predicate is handled in the definition of branching bisimulation; see [16]) we ensure that an asynchronous system constructed from a desynchronisable synchronous system has the following communication property: "every sent message is eventually received". Note that this property was already present in the previous works [3, 8, 9] on desynchronisability; although, it was never made explicit with the respective equivalences studied previously. For instance, the communication property was called *absence of computation interference* in [9]; while, [3] used *sender domination* to satisfy the above property. Thus, by making the communication property explicit in our setup we are able to show that our conditions are also necessary for desynchronisability, which was previously absent in [3, 7–9].

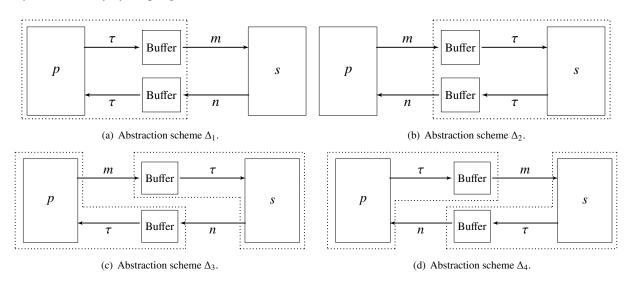

*Organisation of the paper.* In Section 2, we describe the mathematical notations and formal definitions required to define desynchronisability using two unidirectional FIFO buffers. Section 3 discusses necessary and sufficient conditions for desynchronisability, including the unwanted diamond property and show how it can be eliminated by using half-duplex buffers for desynchronisation. Section 4 considers how to apply desynchronisation in the context of supervisory control. Lastly, Section 5 motivates the choice of abstraction scheme used to construct asynchronous systems and discusses desynchronisation of non-concrete synchronous systems.

This article extends [18] in the following four aspects.

- First, this article contains proofs of all the lemmas and theorems, which were either sketched or left out in [18].

- Second, a new simplified sufficient condition for desynchronisability modulo branching bisimulation is given in Subsection 3.6, which is derived from the characterisation obtained in [18].

- Third, a more detailed account of desynchronisability for synchronous systems that are synthesised using supervisory control theory is given in Section 4. In contrast to [18], we allow external actions and nondeterminism in the specification of the supervisors.

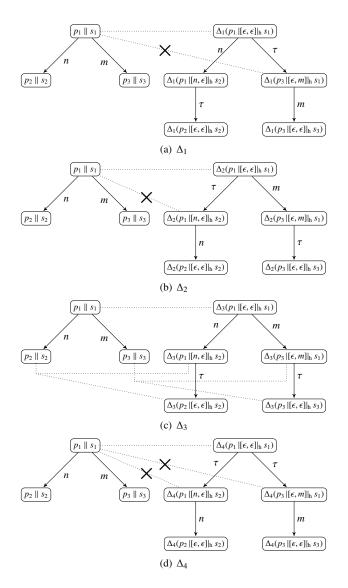

- Fourth, the different abstraction schemes of [8] are compared in Subsection 5.1 with the objective to find out the abstraction scheme that yields in weakest conditions for desynchronisation (modulo branching bisimulation) in the presence of (half-duplex) queues.

#### 2. Basic definitions

In this paper, we model the world as a single transition system in which all behaviour of interest is represented. Components of a system as well as their compositions are called *processes* and are represented by pointing out an *initial state*  $q \in \mathbb{P}$  in the labelled transition system. A *process* q is then formed by all reachable states from the initial state  $q \in \mathbb{P}$ .

**Definition 1.** A *labelled transition system* is a tuple  $(\mathbb{P}, A, \rightarrow, \sqcup)$ , where

- $\mathbb{P}$  is a set of states.

- A is a set of actions.

- $\rightarrow \subseteq \mathbb{P} \times (A \cup \{\tau\}) \times \mathbb{P}$  is a transition relation.

- ⊔ ⊆ ℙ is the empty-buffer predicate and its purpose is to observe the states of an asynchronous system in which all buffers are empty.

The notation  $q \xrightarrow{\alpha} q'$  denotes an element  $(q, \alpha, q') \in \rightarrow$ , the notation  $q \sqcup$  denotes that state q satisfies the empty-buffer predicate. For a given state  $q \in \mathbb{P}$ , the set of *reachable states*  $\Re(q)$  is defined as the smallest set such that:

- $q \in \Re(q)$ , and

- $\forall q_1, q_2 \in \mathbb{P}, \alpha \in A \cup \{\tau\}. \left[ \left( q_1 \in \Re(q) \land q_1 \xrightarrow{\alpha} q_2 \right) \Rightarrow q_2 \in \Re(q) \right].$

In what follows, the letter q and its decorations like  $q', q_1, q_2, \cdots$  are used to reason about arbitrary processes, whereas the letters p, s and their corresponding decorations are reserved to denote the communicating processes of a given synchronous system.

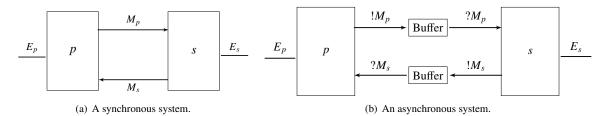

Figure 2: From Synchrony to Asynchrony.

Considering a synchronous system as depicted in Figure 2(a), we identify two components p, s, which we assume to be processes in our labelled transition system. These processes are composed into a synchronous process  $p \parallel s$ . The process  $p \parallel s$  can perform four kinds of events; namely, the *external* actions of p and s that belong to the sets  $E_p$  and  $E_s$ , respectively, and *messages* from p and s that belong to the sets  $M_p$  and  $M_s$ , respectively.

When the system is *desynchronised* we obtain an asynchronous system as depicted in Figure 2(b), consisting of the same processes p, s, which are now composed into an asynchronous process  $p | [\epsilon, \epsilon] | s$  (with  $\epsilon$  indicating initially empty buffer contents). In the asynchronous process, the external actions of p and s remain the same, but we now make a distinction between the sending of a message (i.e., the set  $!M_p = \{!m \mid m \in M_p\}$ ) and the receiving of a message from p sent by s (i.e., the set  $?M_s = \{?m \mid m \in M_s\}$ ). We assume that the so obtained sets of actions are all part of our alphabet and are all pairwise disjoint:  $E_p \uplus E_s \uplus M_p \uplus !M_p \uplus !M_s \uplus !M_s \uplus !M_s \subseteq A$ .

Assuming that the processes p and s are already part of our labelled transition system, where p makes use of the actions  $!M_p \uplus ?M_s \uplus E_p$  and s makes use of the actions  $!M_s \uplus ?M_p \uplus E_s$ , we can define the synchronous and asynchronous composition of p and s through Structural Operational Semantic (SOS) rules on the states of the transition system [19]. The premise of each rule states the assumption on the states of the composed processes, and the conclusion gives the resulting transition for the composed state.

In Table 2, we give the SOS rules for synchronous composition and asynchronous composition using two unidirectional lossless FIFO queues. The notation  $p \parallel s$  denotes the synchronous composition of processes p and s. Note that one can construct the synchronous composition of processes, say p' and  $p \parallel s$ , by renaming the synchronous interaction (e.g. the renaming operator from TCP process algebra [16]) of  $p \parallel s$  into a send message or receive message

$$\frac{p_1 \xrightarrow{!m} p_2, s_1 \xrightarrow{?m} s_2, m \in M_p}{p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_2} \quad \frac{p_1 \xrightarrow{?n} p_2, s_1 \xrightarrow{!n} s_2, n \in M_s}{p_1 \parallel s_1 \xrightarrow{n} p_2 \parallel s_2} \quad \frac{p_1 \xrightarrow{\alpha} p_2, \alpha \in E_p \cup \{\tau\}}{p_1 \parallel s_1 \xrightarrow{\alpha} p_2 \parallel s_1} \quad \frac{s_1 \xrightarrow{\alpha} s_2, \alpha \in E_s \cup \{\tau\}}{p_1 \parallel s_1 \xrightarrow{\alpha} p_1 \parallel s_2}$$

$$\frac{(p \parallel s) \sqcup}{(p \parallel s) \sqcup} \quad \frac{p \xrightarrow{!m} p', m \in M_p}{(p \parallel \mu, v \parallel s) \xrightarrow{!m} (p' \parallel \mu, v.m] \mid s)} \quad \frac{s \xrightarrow{!n} s', n \in M_s}{(p \parallel \mu, v \parallel s) \xrightarrow{!m} (p' \parallel \mu, v.m] \mid s)}$$

$$\frac{p \xrightarrow{?n} p', \mu = n \mu', n \in M_s}{(p \parallel \mu, v \parallel s) \xrightarrow{?m} (p' \parallel \mu, v \parallel s) \xrightarrow{?m} (p \parallel \mu, v \parallel s) \xrightarrow{?m} (p \parallel \mu, v \parallel s) \xrightarrow{!m} (p \parallel \mu, v \parallel s)}$$

$$\frac{p \xrightarrow{\alpha} p', \alpha \in E_p \cup \{\tau\}}{(p \parallel \mu, v \parallel s) \xrightarrow{\alpha} (p' \parallel \mu, v \parallel s)} \quad \frac{s \xrightarrow{\alpha} s', \alpha \in E_s \cup \{\tau\}}{(p \parallel \mu, v \parallel s) \xrightarrow{m} (p \parallel \mu, v \parallel s)}$$

depending on the architecture. The notation  $p | [\mu, \nu] | s$  denotes the asynchronous composition of processes p and s with sequences of messages  $\nu \in M_p^*, \mu \in M_s^*$  in the respective queues. Note how the empty-buffer predicate is always true for synchronous compositions, while it is only true for asynchronous compositions if both queues are empty.

As explained in the introduction, a composition  $p \parallel s$  is desynchronisable if it is equivalent to its asynchronous composition  $p \mid [\epsilon, \epsilon] \mid s$ . One problem with defining equivalence between the two is that asynchronous composition needs two actions for the communication of a message while synchronous composition only needs one. The usual process algebraic way to solve this issue is by defining an abstraction scheme, translating certain actions from the asynchronous system to actions from the synchronous system while hiding others.

In Table 3, we define the abstraction operator  $\Delta$ () that maps all the send-messages of the asynchronous system to communicated messages in the synchronous system, while the receive-messages are mapped to a so-called *internal action*, denoted by  $\tau$ . Subsequently, we define *branching bisimulation* (see [16, 17]) as an equivalence between processes that abstracts from internal actions. In Subsection 5.1, we discuss the impact of alternative choices of abstraction schemes on desynchronisability modulo branching bisimulation.

Table 3: SOS rules for the abstraction operator  $\Delta$ ().

$$\frac{q_1 \xrightarrow{!m} q_2, \ m \in M_p \cup M_s}{\Delta(q_1) \xrightarrow{m} \Delta(q_2)} \qquad \frac{q_1 \xrightarrow{e} q_2, \ e \in E_p \cup E_s}{\Delta(q_1) \xrightarrow{e} \Delta(q_2)} \qquad \frac{q_1 \xrightarrow{?m} q_2, \ m \in M_p \cup M_s}{\Delta(q_1) \xrightarrow{\tau} \Delta(q_2)} \qquad \frac{q \sqcup}{\Delta(q_1)}$$

**Definition 2.** The *reachability relation*  $\longrightarrow \subseteq \mathbb{P} \times A^* \times \mathbb{P}$  is derived from the transition relation  $\rightarrow$  as the *smallest* relation satisfying:

$$q_1 \xrightarrow{\epsilon} q_1$$

,  $\frac{q_1 \xrightarrow{w} q', q' \xrightarrow{\tau} q_2}{q_1 \xrightarrow{w} q_2}$ ,  $\frac{q_1 \xrightarrow{w} q', q' \xrightarrow{\alpha} q_2, \alpha \neq \tau}{q_1 \xrightarrow{w} q_2}$

Let  $x = x_p \uplus x_s$  and  $yM = yM_p \uplus yM_s$ , where  $x \in \{M, E\}$  and  $y \in \{!, ?\}$ . By abuse of notations, define two renaming functions  $! : (M \cup E)^* \to (!M \cup E)^*$ ,  $? : (M \cup E)^* \to ?M^*$ , and a projection function<sup>-</sup>:  $(M \cup E)^* \to M^*$  in the following way:

1.  $?\epsilon = \epsilon$ , ?(e.w) = w, ?(m.w) = ?m.?w, where  $e \in E$  and  $w \in (M \cup E)^*$ .

- 2.  $!\epsilon = \epsilon$ , !(e.w) = e.!w, !(m.w) = !m.!w, where  $e \in E$  and  $w \in (M \cup E)^*$ .

- 3.  $\bar{\epsilon} = \epsilon$ ,  $\overline{e.w} = \bar{w}$ , and  $\overline{m.w} = m.\bar{w}$ , where  $e \in E$  and  $w \in (M \cup E)^*$ .

Given a sequence of messages and external actions  $w \in (M \cup E)^*$ , then, w denotes a sequence of send messages and external actions, w denotes a sequence of receive messages, and  $\bar{w}$  denotes the projection of the sequence w onto the set of messages M.

**Proposition 1.** Let  $p \parallel s$  be a synchronous system.

1. If  $u \in (M_s \cup E_s)^*$  and  $p \parallel s \xrightarrow{u} p' \parallel s'$  then  $p \xrightarrow{?u} p' \wedge s \xrightarrow{!u} s'$ . 2. If  $v \in (M_p \cup E_p)^*$  and  $p \parallel s \xrightarrow{v} p' \parallel s'$  then  $s \xrightarrow{?v} s' \wedge p \xrightarrow{!v} p'$ .

*Proof.* Straightforward by induction on *u* and *v*, respectively.

**Definition 3.** A binary relation  $\mathcal{B} \subseteq \mathbb{P} \times \mathbb{P}$  on the states of the transition system is a *branching bisimulation* relation iff the following conditions are satisfied.

$$1. \ \forall q, q_1, q', \alpha. \left[ \left( (q, q') \in \mathcal{B} \land q \xrightarrow{\alpha} q_1 \right) \Rightarrow \left( \alpha = \tau \land (q_1, q') \in \mathcal{B} \right) \lor \\ \exists q'_1, q'_2 \cdot \left[ q' \xrightarrow{\epsilon} q'_1 \xrightarrow{\alpha} q'_2 \land (q, q'_1) \in \mathcal{B} \land (q_1, q'_2) \in \mathcal{B} \right] \right], \\ 2. \ \forall q, q'. \left[ \left( (q, q') \in \mathcal{B} \land q \sqcup \right) \Rightarrow \exists q''. \left[ q' \xrightarrow{\epsilon} q'' \land q'' \sqcup \land (q, q'') \in \mathcal{B} \right] \right], \\ 3. \ \forall q, q', q'_1, \alpha. \left[ \left( (q, q') \in \mathcal{B} \land q' \xrightarrow{\alpha} q'_1 \right) \Rightarrow \left( \alpha = \tau \land (q, q'_1) \in \mathcal{B} \right) \lor \\ \exists q_1, q_2 \cdot \left[ q \xrightarrow{\epsilon} q_1 \xrightarrow{\alpha} q_2 \land (q_1, q') \in \mathcal{B} \land (q_2, q'_1) \in \mathcal{B} \right] \right], \\ 4. \ \forall q, q'. \left[ \left( (q, q') \in \mathcal{B} \land q' \sqcup \right) \Rightarrow \exists q''. \left[ q \xrightarrow{\epsilon} q'' \land q'' \sqcup \land (q'', q') \in \mathcal{B} \right] \right]. \end{cases}$$

Two processes q and q' are said to be *branching bisimilar*, denoted  $q \leftrightarrow_{\mathbf{b}} q'$ , if there exists a branching bisimulation relation  $\mathcal{B}$  such that  $(q, q') \in \mathcal{B}$ .

Note that Conditions 1 and 3 are the conventional transfer properties of branching bisimulation, while Conditions 2 and 4 are reminiscent of the transfer properties involved with the termination predicate cf. [16]. Here, we interpret Condition 2 (likewise Condition 4) as follows: if two processes q, q' are branching bisimilar and q has empty buffer, then q' can empty its buffer contents by performing invisible actions and become branching bisimilar to q.

Now we have all the preliminaries that are necessary to define what desynchronisation formally means.

**Definition 4.** A synchronous system  $p \parallel s$  is desynchronisable if  $p \parallel s \Leftrightarrow_{\mathbf{b}} \Delta(p \mid [\epsilon, \epsilon] \mid s)$ .

#### 3. Properties of desynchronisable systems

In this section, we prove a number of properties of desynchronisable systems modulo branching bisimulation. In particular, Definition 5, Lemmas 1-2, and Theorem 1 are only required to establish the necessity of well-posedness, input-determinism, independence of external actions, and diamond property for desynchronisation. A new result (cf. [3, 7-9]) is that the observation of the empty-buffer predicate makes that these properties are necessary as well as sufficient for desynchronisability. A technical assumption used to show necessity in this case, is that the components p and s are *concrete*, meaning they do not have internal behavior themselves. Furthermore, in subsection 3.7, we show that by just dropping the diamond property from the general characterisation of desynchronisation results in the characterisation of desynchronisation when half-duplex queues are used to construct asynchronous systems.

**Definition 5.** A process  $q \in \mathbb{P}$  is *concrete* if  $\nexists q', q''. \left[q' \in \Re(q) \land q' \xrightarrow{\tau} q''\right]$ . A transition  $q_1 \xrightarrow{\tau} q_2$  is *inert* modulo  $\underset{\mathbf{p}_1}{\hookrightarrow} \inf q_1 \underset{\mathbf{p}_2}{\hookrightarrow} q_2$ .

Henceforth, due to the following proposition, we use strong bisimulation<sup>2</sup> equivalence  $\leftrightarrow$  in favour of branching bisimulation equivalence between any two concrete processes because of its simpler transfer properties.

**Proposition 2.** For any two concrete processes  $q, q' \in \mathbb{P}$ , we have  $q \leftrightarrow_{\mathbf{b}} q' \iff q \leftrightarrow q'$ .

**Lemma 1.** Let  $p \parallel s$  be a concrete and desynchronisable system. Then, all the  $\tau$ -transitions in  $\Delta(p \mid [\epsilon, \epsilon] \mid s)$  are inert modulo branching bisimulation.

*Proof.* Since  $p \parallel s$  is a concrete process, none of the  $\tau$ -transitions in the asynchronous system can be matched by any related state in the synchronous system. Thus, all  $\tau$ -transitions in the asynchronous system have to be inert [16].  $\Box$

A key step in understanding the necessary conditions for desynchronisability, is to see that any reachable state  $p' \parallel s' \in \Re(p \parallel s)$  of some desynchronisable system  $p \parallel s$  is desynchronisable itself. This property seems both desirable and trivial, but its proof turned out to be more involved than expected. In particular, the proof turns out to rely on the chosen abstraction scheme, the fact that p and s are concrete processes, disjointness of the message sets, and the fact that we observe the empty-buffer predicate.

**Lemma 2.** Let  $p_1, s_1, p_2, s_2$  be any four concrete processes. Then,

$$p_1 \parallel s_1 \nleftrightarrow_{\mathbf{b}} p_2 \parallel [\epsilon, \epsilon] \parallel s_2 \Rightarrow p_1 \parallel s_1 \nleftrightarrow_{\mathbf{b}} p_2 \parallel s_2 .$$

*Proof.* Due to Proposition 2, it is sufficient to show that the above implication holds w.r.t strong bisimulation  $\Leftrightarrow$ , i.e.,  $p_1 \parallel s_1 \Leftrightarrow p_2 \parallel (\epsilon, \epsilon) \parallel s_2 \Rightarrow p_1 \parallel s_1 \Leftrightarrow p_2 \parallel s_2$ . Define the following relation S:

$$\mathcal{S} = \left\{ (p_3 \parallel s_3, p_4 \parallel s_4) \mid p_3 \parallel s_3 \in \Re(p_1 \parallel s_1) \land p_4 \mid [\epsilon, \epsilon] \mid s_4 \in \Re(p_2 \mid [\epsilon, \epsilon] \mid s_2) \land p_3 \parallel s_3 \underset{\mathbf{b}}{\leftrightarrow} p_4 \mid [\epsilon, \epsilon] \mid s_4 \right\}$$

Next, we show that the relation S is indeed a strong bisimulation relation.

- 1. Let  $p_3 \parallel s_3 \xrightarrow{m} p_5 \parallel s_5$  and  $(p_3 \parallel s_3, p_4 \parallel s_4) \in S$  for some  $m \in M_p, p_5, s_5 \in \mathbb{P}$ . Then, by the construction of S we have  $p_3 \parallel s_3 \bigoplus_{\mathbf{b}} \Delta(p_4 \parallel [\epsilon, \epsilon] \mid s_4)$ . Applying the transfer conditions of branching bisimulation under the assumption of concrete processes and disjointness of sets  $M_p, M_s$  we get  $\Delta(p_4 \parallel [\epsilon, \epsilon] \mid s_4) \xrightarrow{m} \Delta(p_6 \parallel [\epsilon, m] \mid s_4)$  and  $p_5 \parallel s_5 \bigoplus_{\mathbf{b}} \Delta(p_6 \parallel [\epsilon, m] \mid s_4)$  for some  $p_6 \in \mathbb{P}$ . Since  $(p_5 \parallel s_5) \sqcup$ , branching bisimulation under concreteness assumption gives us  $\Delta(p_6 \parallel [\epsilon, m] \mid s_4) \xrightarrow{\tau} \Delta(p_6 \parallel [\epsilon, \epsilon] \mid s_6)$  and  $p_5 \parallel s_5 \bigoplus_{\mathbf{b}} \Delta(p_6 \parallel [\epsilon, \epsilon] \mid s_4)$ . Thus, we derive  $p_4 \xrightarrow{!m} p_6$  and  $s_4 \xrightarrow{?m} s_6$ ; hence,  $p_4 \parallel s_4 \xrightarrow{m} p_6 \parallel s_6$  and  $(p_5 \parallel s_5, p_6 \parallel s_6) \in S$ .

- 2. Let  $p_3 \parallel s_3 \xrightarrow{\alpha} p_5 \parallel s_5$  and  $(p_3 \parallel s_3, p_4 \parallel s_4) \in S$  for some  $\alpha \in E_p \cup E_s \cup M_s$ . Similar to the previous case.

- 3. Let  $p_4 \parallel s_4 \xrightarrow{m} p_6 \parallel s_6$  and  $(p_3 \parallel s_3, p_4 \parallel s_4) \in S$  for some  $m \in M_p, p_6, s_6 \in \mathbb{P}$ . Then, by the semantics we have  $p_4 \xrightarrow{!m} p_6$  and  $s_4 \xrightarrow{?m} s_6$ . Also, by the construction of S we have  $p_3 \parallel s_3 \Leftrightarrow_{\mathbf{b}} \Delta(p_4 \mid [\epsilon, \epsilon] \mid s_4)$ . Using the above transitions at the state  $\Delta(p_4 \mid [\epsilon, \epsilon] \mid s_4)$  we derive the following transitions:  $\Delta(p_4 \mid [\epsilon, \epsilon] \mid s_4) \xrightarrow{m} \Delta(p_6 \mid [\epsilon, m] \mid s_4) \xrightarrow{\tau} \Delta(p_6 \mid [\epsilon, \epsilon] \mid s_6)$ . Applying the transfer conditions of branching bisimulation under concreteness assumption we get  $\exists p_5, s_5. \left[ p_3 \parallel s_3 \xrightarrow{m} p_5 \parallel s_5 \land p_5 \parallel s_5 \Leftrightarrow_{\mathbf{b}} \Delta(p_6 \mid [\epsilon, \epsilon] \mid s_4) \right]$ . Now consider the transition  $\Delta(p_6 \mid [\epsilon, m] \mid s_4) \xrightarrow{\tau} \Delta(p_6 \mid [\epsilon, \epsilon] \mid s_6)$ . Note that the synchronous system  $p_1 \parallel s_1$  is concrete, thus this  $\tau$ -transition can be only mapped by zero  $\tau$ -steps from the state  $p_5 \parallel s_5$ . Thus,  $p_5 \parallel s_5 \Leftrightarrow_{\mathbf{b}} \Delta(p_6 \mid [\epsilon, \epsilon] \mid s_6)$ . Hence,  $(p_5 \parallel s_5, p_6 \parallel s_6) \in S$ .

- 4. Let  $p_4 \parallel s_4 \xrightarrow{\alpha} p_6 \parallel s_6$  and  $(p_3 \parallel s_3, p_4 \parallel s_4) \in S$  for some  $\alpha \in E_p \cup E_s \cup M_s$ . Similar to the previous case.

<sup>&</sup>lt;sup>2</sup>see [16] for a formal definition.

5. The transfer property for the empty buffer predicate ⊔ holds trivially because every state in the composition || satisfies the predicate ⊔ by definition. □

#### **Theorem 1.** Let $p \parallel s$ be concrete and desynchronisable, then any $p' \parallel s' \in \Re(p \parallel s)$ is desynchronisable.

*Proof.* As a base case, the initial state of  $p \parallel s$  is desynchronisable by assumption. By induction, assume that we have a reachable desynchronisable state  $p' \parallel s' \in \Re(p \parallel s)$  and consider any p'' and s'' with  $p' \parallel s' \xrightarrow{\alpha} p'' \parallel s''$ . Following the SOS rules, one of the following transitions must exist in the asynchronous process:

- 1. a transition  $\Delta(p' | [\epsilon, \epsilon] | s') \xrightarrow{\alpha} \Delta(p'' | [\epsilon, \alpha] | s')$  with  $\alpha \in M_p$  and a  $\tau$ -transition  $\Delta(p'' | [\epsilon, \alpha] | s') \xrightarrow{\tau} \Delta(p'' | [\epsilon, \epsilon] | s'')$ that is inert because p | | s is concrete, i.e.  $\Delta(p'' | [\epsilon, \alpha] | s') \xrightarrow{\leftarrow} \Delta(p'' | [\epsilon, \epsilon] | s'')$ ;

- 2. a transition  $\Delta(p' | [\epsilon, \epsilon] | s') \xrightarrow{\alpha} \Delta(p' | [\alpha, \epsilon] | s'')$  with  $\alpha \in M_s$ , and a  $\tau$ -transition  $\Delta(p' | [\alpha, \epsilon] | s'') \xrightarrow{\tau} \Delta(p'' | [\epsilon, \epsilon] | s'')$ that is inert because  $p \parallel s$  is concrete, i.e.  $\Delta(p' | [\alpha, \epsilon] | s') \xrightarrow{\leftarrow} \Delta(p'' | [\epsilon, \epsilon] | s'')$ ;

- 3. a transition  $\Delta(p' | [\epsilon, \epsilon] | s') \xrightarrow{e} \Delta(p'' | [\epsilon, \epsilon] | s'')$  with  $e \in E_p$ , in which case we find that s' = s''.

- 4. a transition  $\Delta(p' | [\epsilon, \epsilon] | s') \xrightarrow{e} \Delta(p'' | [\epsilon, \epsilon] | s'')$  with  $e \in E_s$ , in which case we find that p' = p''.

Because  $p' \parallel s' \underset{\mathbf{b}}{\hookrightarrow} \Delta(p' \mid [\epsilon, \epsilon] \mid s')$ , the properties of branching bisimulation (applied to concrete processes) dictate that we can relate those asynchronous transitions to synchronous transitions. I.e. there exist p''' and s''' such that  $p' \parallel s' \underset{\mathbf{b}}{\to} p''' \parallel s''' \underset{\mathbf{b}}{\hookrightarrow} \Delta(p'' \mid [\epsilon, \epsilon] \mid s'')$ . Furthermore, from Lemma 2 we get  $p'' \parallel s'' \underset{\mathbf{b}}{\hookrightarrow} p''' \parallel s'''$ . And by transitivity we conclude that  $p' \parallel s''$  is desynchronisable.

#### 3.1. Well-posedness

The first actual implication of desynchronisability that we would like to discuss, is that a desynchronisable system is always *well-posed*. This was already observed in [3] for desynchronisability modulo failure equivalence. Well-posedness means that whenever a process *p* would like to send a message, *s* should be willing to receive it and vice versa. In a synchronous composition such messages may be blocked, but in an asynchronous composition they lead to *orphans*, i.e., messages that remain forever in the buffer. In turn, orphans lead to deadlocking communication (except in a few pathological cases).

**Definition 6.** A binary relation  $\mathcal{W} \subseteq \mathbb{P} \times \mathbb{P}$  is called a *well-posedness* relation iff the following conditions are satisfied.

1.

$$\forall p_1, s_1, p_2, m. \left[ p_1 \xrightarrow{!m} p_2 \land (p_1, s_1) \in \mathcal{W} \Rightarrow \exists s_2. \left[ s_1 \xrightarrow{?m} s_2 \right] \land \forall s_2. \left[ s_1 \xrightarrow{?m} s_2 \Rightarrow (p_2, s_2) \in \mathcal{W} \right] \right],$$

2.  $\forall p_1, s_1, p_2, e \in E_p. \left[ p_1 \xrightarrow{e} p_2 \land (p_1, s_1) \in \mathcal{W} \Rightarrow (p_2, s_1) \in \mathcal{W} \right],$

3.  $\forall p_1, s_1, s_2, m. \left[ s_1 \xrightarrow{!m} s_2 \land (p_1, s_1) \in \mathcal{W} \Rightarrow \exists p_2. \left[ p_1 \xrightarrow{?m} p_2 \right] \land \forall p_2. \left[ p_1 \xrightarrow{?m} p_2 \Rightarrow (p_2, s_2) \in \mathcal{W} \right] \right],$

4.  $\forall p_1, s_1, s_2, e \in E_s. \left[ s_1 \xrightarrow{e} s_2 \land (p_1, s_1) \in \mathcal{W} \Rightarrow (p_1, s_2) \in \mathcal{W} \right].$

A composition  $p \parallel s$  is well-posed if there exists a well-posedness relation  $\mathcal{W}$  such that  $(p, s) \in \mathcal{W}$ .

**Proposition 3.** Let  $p \parallel s$  be a concrete and a well-posed synchronous system with W being the witnessing well-posedness relation, i.e.,  $(p, s) \in W$ . Then,

$$\forall p_1, s_1. [p_1 \parallel s_1 \in \Re(p \parallel s) \Rightarrow (p_1, s_1) \in \mathcal{W}].$$

Lemma 3 (Generalised well-posedness). Let p || s be a well-posed and concrete synchronous system.

1. If  $p_1 \parallel s_1 \in \Re(p \parallel s)$ ,  $u \in (M_s \cup E_s)^*$ , and  $s_1 \xrightarrow{!u} s_2$ , then  $\exists p_2. \left[ p_1 \parallel s_1 \xrightarrow{u} p_2 \parallel s_2 \right]$ . 2. If  $p_1 \parallel s_1 \in \Re(p \parallel s)$ ,  $v \in (M_p \cup E_p)^*$ , and  $p_1 \xrightarrow{!v} p_2$ , then  $\exists s_2. \left[ p_1 \parallel s_1 \xrightarrow{v} p_2 \parallel s_2 \right]$ .

### **Theorem 2.** If $p \parallel s$ is concrete and desynchronisable then it is well-posed.

*Proof.* Define a relation  $\mathcal{W} = \{(p_1, s_1) \mid \Delta(p_1 \mid [\epsilon, \epsilon] \mid s_1) \in \Re(\Delta(p \mid [\epsilon, \epsilon] \mid s))\}$ . To show that  $\mathcal{W}$  is a well-posedness relation, assume a transition  $p_1 \xrightarrow{\alpha} p_2$  and  $(p_1, s_1) \in \mathcal{W}$ , for some  $p_1, s_1, p_2 \in \mathbb{P}$ .

1. Let  $\alpha \in M_p$ . Then, by the construction of  $\mathcal{W}$  we have  $\Delta(p_1 | [\epsilon, \epsilon] | s_1) \in \Re(\Delta(p | [\epsilon, \epsilon] | s))$  and using  $p_1 \xrightarrow{!m} p_2$  we get  $\Delta(p_1 | [\epsilon, \epsilon] | s_1) \xrightarrow{m} \Delta(p_2 | [\epsilon, m] | s_1)$ . Since  $p \parallel s$  is desynchronisable, we know that there exists  $q \in \Re(p \parallel s)$  such that  $q \xrightarrow{\leftarrow} \Delta(p_2 | [\epsilon, m] | s_1)$ . Clearly, we have  $q \sqcup$ . Furthermore by the transfer property of branching bisimulation and under the assumption of concrete processes we get

$$\exists s_2. \left[ \Delta(p_2 | [\epsilon, m] | s_1) \xrightarrow{\tau} \Delta(p_2 | [\epsilon, \epsilon] | s_2) \land \Delta(p_2 | [\epsilon, \epsilon] | s_2) \sqcup \right].$$

Thus, we showed that there exists  $s_2$  such that  $s_1 \xrightarrow{?m} s_2$  and by the construction of  $\mathcal{W}$  it is clear that  $(p_2, s_2) \in \mathcal{W}$ .  $\mathcal{W}$ . But, well-posedness also asserts that for every  $s'_2$  such that  $s_1 \xrightarrow{?m} s'_2$  and  $(p_2, s'_2) \in \mathcal{W}$ . So pick a  $s'_2 \in \mathbb{P}$ such that  $s_1 \xrightarrow{?m} s'_2$ . Then we have  $\Delta(p_2 | [\epsilon, m] | s_1) \xrightarrow{\tau} \Delta(p_2 | [\epsilon, \epsilon] | s'_2)$ . Thus,  $(p_2, s'_2) \in \mathcal{W}$ . 2. Let  $\alpha \in E_p$ . Then, by the construction of  $\mathcal{W}$  we have  $\Delta(p_1 | [\epsilon, \epsilon] | s_1) \in \Re(\Delta(p | [\epsilon, \epsilon] | s))$  and using the

2. Let  $\alpha \in E_p$ . Then, by the construction of  $\mathcal{W}$  we have  $\Delta(p_1 | [\epsilon, \epsilon] | s_1) \in \Re(\Delta(p | [\epsilon, \epsilon] | s))$  and using the above transition we get  $\Delta(p_1 | [\epsilon, \epsilon] | s_1) \xrightarrow{e} \Delta(p_2 | [\epsilon, \epsilon] | s_1)$ . And, from the construction of  $\mathcal{W}$  we conclude that  $(p_2, s_1) \in \mathcal{W}$ .

Likewise, the symmetric case can be proved for the process  $s_1$ .

#### 3.2. Independence of external actions

The second implication of desynchronisability that we would like to discuss is *independence of external actions*. Intuitively, it means that a receiver can always delay the execution of its own external action e in favour of receiving a sequence of messages u from the other process, without any consequence on its future behaviour modulo  $\Delta_b$ , i.e., the traces e.u and u.e commute up to branching bisimulation. The reception of messages becomes *independent* of the external behaviour in this way.

In the following, we define independence on the composition  $p \parallel s$  rather than on the separate processes p and s because we aim for necessary conditions. The pathological case in which a process p is not independent in a part of its state-space that becomes unreachable when interacting with s has no effects on desynchronisability. Of course, independence of external actions of the separate processes would be a natural part of a sufficient condition for desynchronisability.

**Definition 7.** A synchronous system  $p \parallel s$  is *independent of external actions modulo*  $\underset{\mathbf{b}}{\leftrightarrow}_{\mathbf{b}}$  if the following conditions hold for every  $p_1 \parallel s_1 \in \Re(p \parallel s)$ .

$$1. \quad \forall p_2, p'_2, s_2, u, e. \left[ \left( e \in E_p \land u \in (M_s \cup E_s)^* \land p_1 \parallel s_1 \xrightarrow{e} p_2 \parallel s_1 \xrightarrow{u} p'_2 \parallel s_2 \right) \Rightarrow \\ \exists p_3, p'_3. \left[ p_1 \parallel s_1 \xrightarrow{u} p_3 \parallel s_2 \xrightarrow{e} p'_3 \parallel s_2 \land p'_2 \parallel s_2 \underbrace{\leftrightarrow}_{\mathbf{b}} p'_3 \parallel s_2 \right] \right].$$

$$2. \quad \forall p_2, s_2, s'_2, v, e. \left[ \left( e \in E_s \land v \in (M_p \cup E_p)^* \land p_1 \parallel s_1 \xrightarrow{e} p_1 \parallel s_2 \xrightarrow{v} p_2 \parallel s'_2 \right) \Rightarrow \\ \exists s_3, s'_3. \left[ p_1 \parallel s_1 \xrightarrow{v} p_2 \parallel s_3 \xrightarrow{e} p_2 \parallel s'_3 \land p_2 \parallel s'_2 \underbrace{\leftrightarrow}_{\mathbf{b}} p_2 \parallel s'_3 \right] \right].$$

**Theorem 3.** If  $p \parallel s$  is concrete and desynchronisable then it is independent of external actions modulo  $\underset{\mathbf{h}}{\leftrightarrow}_{\mathbf{h}}$ .

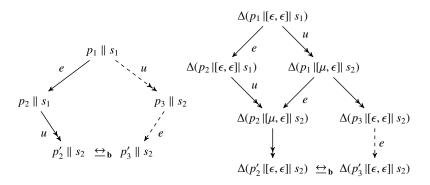

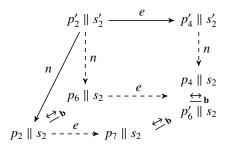

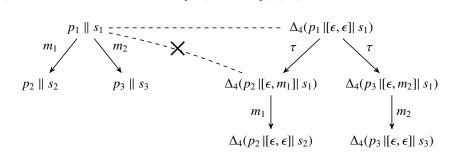

*Proof.* Assume we have a reachable and desynchronisable (Theorem 1) state  $p_1 || s_1 \in \Re(p || s)$  with solid transitions as in Figure 3, where  $e \in E_p$  and  $u \in (M_s \cup E_s)^*$ . From Proposition 1 we get  $p_1 \xrightarrow{e} p_2$ ,  $s_1 \xrightarrow{!u} s_2$ , and  $p_2 \xrightarrow{?u} p'_2$ . As well-posedness is necessary for desynchronisability, we may use it to obtain  $p_1 \xrightarrow{?u} p_3$  (for some  $p_3$ ) from Lemma 3. Using the SOS-rules we get  $p_1 || s_1 \xrightarrow{u} p_3 || s_2$  (dashed in Figure 3). From these transitions we then derive the transitions in the asynchronous system depicted as solid lines in Figure 3, where  $\bar{u} = \mu$ .

Figure 3: An illustration showing that an external action e by the process  $p_1$  can be delayed in favour of receiving the messages u such that the traces e.u and u.e commute up to branching bisimulation.

Since  $\tau$ -transitions are inert we have  $\Delta(p_1 | [\mu, \epsilon] | s_2) \xrightarrow{\leftrightarrow} \Delta(p_3 | [\epsilon, \epsilon] | s_2)$ . Branching bisimulation, under the assumption of concrete processes and disjointness of the sets  $E_p$  and  $E_s$ , gives us the existence of  $p'_3$  such that  $\Delta(p_3 | [\epsilon, \epsilon] | s_2) \xrightarrow{e} \Delta(p'_3 | [\epsilon, \epsilon] | s_2)$  and  $\Delta(p'_3 | [\epsilon, \epsilon] | s_2) \xrightarrow{\leftrightarrow} \Delta(p_2 | [\mu, \epsilon] | s_2)$ . By the SOS-rules we get  $p_3 \xrightarrow{e} p'_3$ , thus,  $p_3 | s_2 \xrightarrow{e} p'_3 | s_2$ . Next, we show that  $p'_2 | s_2 \xrightarrow{\leftrightarrow} p'_3 | s_2$ . From above we have  $\Delta(p'_3 | [\epsilon, \epsilon] | s_2) \xrightarrow{\leftrightarrow} \Delta(p_2 | [\mu, \epsilon] | s_2)$  and since  $\tau$ -transition are inert we have  $\Delta(p_2 | [\mu, \epsilon] | s_2) \xrightarrow{\leftrightarrow} \Delta(p'_2 | [\epsilon, \epsilon] | s_2)$ . By transitivity we get  $\Delta(p'_3 | [\epsilon, \epsilon] | s_2) \xrightarrow{\leftrightarrow} \Delta(p'_2 | [\epsilon, \epsilon] | s_2)$ . By Theorem 1 we have  $p'_3 | s_2 \xrightarrow{\leftarrow} \Delta(p'_3 | [\epsilon, \epsilon] | s_2)$  and  $p'_2 | s_2 \xrightarrow{\leftarrow} \Delta(p'_2 | [\epsilon, \epsilon] | s_2)$ , from which we ultimately conclude  $p'_2 | s_2 \xrightarrow{\leftarrow} p'_3 | s_2$ . Likewise, Condition 2 of Definition 7 can be proved.

#### 3.3. Input determinism

The next implication of desynchronisability, is that desynchronisable systems should be *input deterministic*. In other words, the synchronous system  $p \parallel s$  should not make non-deterministic choices upon the reception of messages. It may perform non-deterministic external behaviour, and it may also be non-deterministic when sending messages. The reason for this, is that desynchronisation *delays* any non-deterministic choice on the input.

Like in the case of independence of external actions, we define the condition input-determinism on the synchronous process  $p \parallel s$  rather than on the individual processes p and s (cf. [20]) because we are aiming for necessary conditions. As before, input-determinism of the individual processes would be a natural part of a sufficient condition for input-determinism of the composition.

**Definition 8.** A synchronous system  $p \parallel s$  is *input deterministic modulo*  $\leq_{\mathbf{b}}$  if every reachable state  $p_1 \parallel s_1 \in \Re(p \parallel s)$  satisfies the following conditions.

1.

$$\forall p_2, s_2, p_3, u. \left[ \left( p_1 \parallel s_1 \xrightarrow{u} p_2 \parallel s_2 \land p_1 \parallel s_1 \xrightarrow{u} p_3 \parallel s_2 \land u \in (M_s \cup E_s)^* \right) \Rightarrow p_2 \parallel s_2 \nleftrightarrow_{\mathbf{b}} p_3 \parallel s_2 \right].$$

2.  $\forall p_2, s_2, s_3, v. \left[ \left( p_1 \parallel s_1 \xrightarrow{v} p_2 \parallel s_2 \land p_1 \parallel s_1 \xrightarrow{v} p_2 \parallel s_3 \land v \in (M_p \cup E_p)^* \right) \Rightarrow p_2 \parallel s_2 \nleftrightarrow_{\mathbf{b}} p_2 \parallel s_3 \right].$

**Theorem 4.** Let  $p \parallel s$  be concrete and desynchronisable, then it is input deterministic modulo  $\underset{\mathbf{h}}{\hookrightarrow}_{\mathbf{h}}$ .

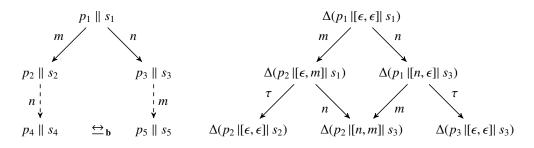

*Proof.* Pick a reachable state  $p_1 \parallel s_1 \in \Re(p \parallel s)$  such that  $p_1 \parallel s_1 \xrightarrow{u} p_2 \parallel s_2$  and  $p_1 \parallel s_1 \xrightarrow{u} p_3 \parallel s_2$ , for some  $u \in (M_s \cup E_s)^*, p_2, p_3, s_2 \in \mathbb{P}$  (see Figure 4). By Theorem 1 we have  $p_1 \parallel s_1 \leftrightarrow_b \Delta(p_1 \mid [\epsilon, \epsilon] \mid s_1)$ . Using the given

Figure 4: An illustration showing that nondeterministic reception of messages u in a desynchronisable synchronous system leads to branching bisimilar states  $p_2 || s_2, p_3 || s_2$ .

transitions in Proposition 1 we get  $s_1 \xrightarrow{!u} s_2$ ,  $p_1 \xrightarrow{?u} p_2$  and  $p_1 \xrightarrow{?u} p_3$ . For the asynchronous system we then find the transitions as shown in Figure 4, where  $\mu = \overline{u}$ .

As  $p \parallel s$  is concrete, all  $\tau$ -transitions in the asynchronous system are inert (Lemma 1), so we get  $\Delta(p_1 \parallel [\mu, \epsilon] \parallel s_2) \Leftrightarrow_{\mathbf{b}} \Delta(p_2 \parallel [\epsilon, \epsilon] \parallel s_2) \bigoplus_{\mathbf{b}} \Delta(p_3 \parallel [\epsilon, \epsilon] \parallel s_2)$ . Finally, using Theorem 1 twice we ultimately conclude that  $p_2 \parallel s_2 \bigoplus_{\mathbf{b}} p_3 \parallel s_2$ . Likewise, Condition 2 of Definition 8 can be proved.

#### 3.4. The diamond property

The final implication of desynchronisability that we would like is the *diamond property*. Intuitively, the diamond property says that sending a message from one component does not disable the sending of message from the other component. Moreover, any order of execution leads to behaviourally equivalent states.

**Definition 9.** A synchronous system  $p \parallel s$  has the diamond property modulo  $\Leftrightarrow_{\mathbf{b}}$  if for every reachable state  $p_1 \parallel s_1$ and transitions  $p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_2$  and  $p_1 \parallel s_1 \xrightarrow{n} p_3 \parallel s_3$  with  $m \in M_p$  and  $n \in M_s$  there exist transitions  $p_2 \parallel s_2 \xrightarrow{n} p_4 \parallel s_4$  and  $p_3 \parallel s_3 \xrightarrow{m} p_5 \parallel s_5$  with  $p_4 \parallel s_4 \Leftrightarrow_{\mathbf{b}} p_5 \parallel s_5$ .

**Lemma 4** (Generalised diamond property). Let  $p \parallel s$  be a concrete synchronous system such that it satisfies Definitions 6-9. If  $p_1 \parallel s_1 \in \Re(p \parallel s)$ ,  $u \in (M_s \cup E_s)^*$ ,  $v \in (M_p \cup E_p)^*$ ,  $p_1 \parallel s_1 \xrightarrow{u} p_2 \parallel s_2$ , and  $p_1 \parallel s_1 \xrightarrow{v} p_3 \parallel s_3$  then  $\exists p_4, s_4, p_5, s_5$ .  $\begin{bmatrix} p_2 \parallel s_2 \xrightarrow{v} p_4 \parallel s_4 \land p_3 \parallel s_3 \xrightarrow{u} p_5 \parallel s_5 \land p_4 \parallel s_4 \Leftrightarrow_{\mathbf{b}} p_5 \parallel s_5 \end{bmatrix}$ .

*Proof.* We first prove the following claim if  $p_1 \parallel s_1 \xrightarrow{u} p_2 \parallel s_2$ ,  $p_1 \parallel s_1 \xrightarrow{\alpha} p_3 \parallel s_3$ ,  $u \in (M_s \cup E_s)^*$ , and  $\alpha \in M_p \cup E_p$  then  $\exists p_4, s_4, p_5, s_5$ .  $\left[p_2 \parallel s_2 \xrightarrow{\alpha} p_4 \parallel s_4 \land p_3 \parallel s_3 \xrightarrow{u} p_5 \parallel s_5 \land p_4 \parallel s_4 \xleftarrow{b} p_5 \parallel s_5\right]$ . Without loss of

generality, assume that  $u = u' \cdot \alpha'$  and  $p_1 \parallel s_1 \xrightarrow{u'} p'_2 \parallel s'_2 \xrightarrow{\alpha'} p_2 \parallel s_2$ . Then, by induction hypothesis we have

$$\exists p'_4, s'_4, p'_5, s'_5. \left[ p'_2 \parallel s'_2 \xrightarrow{\alpha} p'_4 \parallel s'_4 \land p_3 \parallel s_3 \xrightarrow{u'} p'_5 \parallel s'_5 \land p'_4 \parallel s'_4 \underset{\mathbf{b}}{\leftrightarrow} p'_5 \parallel s'_5 \right].$$

We identify the following cases based on the types of  $\alpha, \alpha'$ .

- 1. Let  $\alpha = e$ , for some  $e \in E_p$ ,  $\alpha' = e'$ , for some  $e' \in E_s$ . Trivial.

- Let α = e, for some e ∈ E<sub>p</sub>, α' = n, for some n ∈ M<sub>s</sub>. The single step transitions from the above inductive hypothesis are shown as solid lines in Figure 5. Note that s'<sub>2</sub> = s'<sub>4</sub> because of Rule 2. From the transition p'<sub>2</sub> || s'<sub>2</sub> <sup>n</sup>→ p<sub>2</sub> || s<sub>2</sub> we have s'<sub>2</sub> <sup>!n</sup>→ s<sub>2</sub>. And from well-posedness (Definition 6) we get ∃p<sub>4</sub>. [p'<sub>4</sub> <sup>?n</sup>→ p<sub>4</sub>]. Thus, p'<sub>4</sub> || s'<sub>2</sub> <sup>n</sup>→ p<sub>4</sub> || s<sub>2</sub>.

Now, applying independence of external actions (Definition 7) at the state  $p'_2 \parallel s'_2$  we get (see Figure 5)

$$\exists p_6, p'_6. \left[ p'_2 \parallel s'_2 \xrightarrow{n} p_6 \parallel s_2 \xrightarrow{e} p'_6 \parallel s_2 \wedge p'_6 \parallel s_2 \nleftrightarrow_{\mathbf{b}} p_4 \parallel s_2 \right]$$

Figure 5: Case 2 in Lemma 4.

From input-determinism (Definition 8) we get  $p_2 \parallel s_2 \Leftrightarrow_{\mathbf{b}} p_6 \parallel s_2$ . And from transfer conditions of branching bisimulation under the assumption of concrete processes and disjointness of the sets  $E_p$ ,  $E_s$  we get

$$\exists p_7. \left[ p_2 \parallel s_2 \xrightarrow{e} p_7 \parallel s_2 \land p'_6 \parallel s_2 \nleftrightarrow p_7 \parallel s_2 \right].$$

Thus, by transitivity we get  $p_7 \parallel s_2 \Leftrightarrow_{\mathbf{b}} p_4 \parallel s_2$ . Recall from induction hypothesis that  $p'_4 \parallel s'_2 \Leftrightarrow_{\mathbf{b}} p'_5 \parallel s'_5$ . Again, from the transfer conditions of branching bisimulation under the assumption of concrete processes we get  $\exists p_5, s_5. \left[ p'_5 \parallel s'_5 \xrightarrow{n} p_5 \parallel s_5 \land p_4 \parallel s_2 \nleftrightarrow_{\mathbf{b}} p_5 \parallel s_5 \right]$ . Finally, by transitivity we have  $p_7 \parallel s_2 \nleftrightarrow_{\mathbf{b}} p_5 \parallel s_5$ . 3. Let  $\alpha = m$ , for some  $m \in M_p, \alpha' = e'$ , for some  $e' \in E_s$ . Similar to the previous case.

- 4. Let  $\alpha = m$ , for some  $m \in M_p$ ,  $\alpha' = n$ , for some  $n \in M_s$ . Similar to Case 2, use Definition 9 instead of Definition 7.

Likewise, the main statement can be proved by assuming  $v = v' \cdot \alpha$  for some  $\alpha \in E_p \cup M_p$ .

**Theorem 5.** Let  $p \parallel s$  be concrete and desynchronisable, then  $p \parallel s$  has the diamond property modulo  $\Leftrightarrow_{\mathbf{h}}$ .

*Proof.* Assume a state  $p_1 \parallel s_1 \in \Re(p \parallel s)$ ,  $p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_2$   $(m \in M_p)$  and  $p_1 \parallel s_1 \xrightarrow{n} p_3 \parallel s_3$   $(n \in M_s)$ , as depicted in Figure 6. From Theorem 1 we know that  $p_i \parallel s_i \nleftrightarrow_{\mathbf{b}} p_i \parallel (\epsilon, \epsilon) \parallel s_i$ , for  $i \in \{1, 2, 3\}$ . From the SOS rules we get  $p_1 \xrightarrow{!m} p_2$ ,  $s_1 \xrightarrow{?m} s_2$ ,  $p_1 \xrightarrow{?n} p_3$ , and  $s_1 \xrightarrow{!n} s_3$ . Using these transitions we find the transitions at the state  $\Delta(p_1 | [\epsilon, \epsilon] | s_1)$  as shown in Figure 6.

Figure 6: An illustration showing that the communication of two send messages m, n by different processes can be done in any order in a desynchronisable synchronous system.

Since  $\tau$ -transitions are inert we get  $\Delta(p_2 | [\epsilon, m] | s_1) \leftrightarrow_{\mathbf{b}} \Delta(p_3 | [\epsilon, \epsilon] | s_3)$ . And from Theorem 1 we get  $p_2 | | s_2 \leftrightarrow_{\mathbf{b}} \Delta(p_3 | [\epsilon, \epsilon] | s_3)$ .  $\Delta(p_2 | [\epsilon, \epsilon] | s_2)$ . Thus, by transitivity we have  $p_2 | | s_2 \Leftrightarrow_{\mathbf{b}} p_2 | [\epsilon, m] | s_1$ . And, the transfer conditions of branching bisimulation gives the dashed transition labelled *n* shown in Figure 6 with  $p_4 | | s_4 \Leftrightarrow_{\mathbf{b}} \Delta(p_2 | [n, m] | s_2)$ . Likewise we derive the dashed transition labelled m in Figure 6 with  $p_5 \parallel s_5 \leftrightarrow_{\mathbf{b}} p_2 \mid [n,m] \mid s_3$ . Finally, by transitivity we conclude that  $p_4 \parallel s_4 \nleftrightarrow_{\mathbf{b}} p_5 \parallel s_5$ .

#### 3.5. Sufficient conditions for desynchronisability

Conversely, the four necessary conditions that we discussed in the previous subsections, together form a sufficient condition for desynchronisability.

**Theorem 6.** Let  $p \parallel s$  be concrete, well-posed, independent of external actions modulo  $\underset{\mathbf{b}}{\leftrightarrow}_{\mathbf{b}}$ , input deterministic modulo  $\underset{\mathbf{b}}{\leftrightarrow}_{\mathbf{b}}$ , and satisfies the diamond property modulo  $\underset{\mathbf{b}}{\leftrightarrow}_{\mathbf{b}}$ , then  $p \parallel s \underset{\mathbf{b}}{\leftrightarrow}_{\mathbf{b}} \Delta(p \mid [\epsilon, \epsilon] \mid s)$ .

*Proof.* We define a relation  $\mathcal{B}$  in the following way:

$$\mathcal{B} = \left\{ (p_1 \parallel s_1, \Delta(p_2 \parallel [\mu, \nu] \parallel s_2)) \mid p_1 \parallel s_1 \in \Re(p \parallel s) \land \Delta(p_2 \parallel [\mu, \nu] \mid s_2) \in \Re(\Delta(p \parallel [\epsilon, \epsilon] \mid s)) \land \\ \exists p'_2, s'_2, q, q', u, \nu. \left[ u \in (M_s \cup E_s)^* \land \nu \in (M_p \cup E_p)^* \land \bar{u} = \mu \land \bar{\nu} = \nu \land p_2 \parallel s'_2 \in \Re(p \parallel s) \land \\ p'_2 \parallel s_2 \in \Re(p \parallel s) \land p_2 \parallel s'_2 \xrightarrow{u} q \nleftrightarrow p_1 \parallel s_1 \nleftrightarrow p' \xleftarrow{\nu} p'_2 \parallel s_2 \right\}.$$

Intuitively, two states  $p_1 \parallel s_1, \Delta(p_2 \mid [\mu, \nu] \mid s_2)$  are  $\mathcal{B}$ -related if

- 1. the above states are reachable from their respective initial states, i.e.,  $p_1 \parallel s_1 \in \Re(p \parallel s), \Delta(p_2 \mid [\mu, \nu] \mid s_2) \in \Re(\Delta(p \mid [\epsilon, \epsilon] \mid s); \text{ and}$

- 2. it is possible to read the contents of the input queues (because of the transitions  $p_2 \parallel s'_2 \xrightarrow{u} q, p'_2 \parallel s_2 \xrightarrow{v} q'$  in the construction of  $\mathcal{B}$ ) such that an asynchronous state  $\mathcal{B}$ -related to  $p_1 \parallel s_1$  is reached.

Next, we show that  $\mathcal{B}$  is a witnessing branching bisimulation. We first enumerate the cases that show every transition from the state  $p_1 \parallel s_1$  is simulated by the state  $\Delta(p_2 \mid [\mu, \nu] \mid s_2)$  when  $(p_1 \parallel s_1, \Delta(p_2 \mid [\mu, \nu] \mid s_2)) \in \mathcal{B}$ .

1. Let  $p_1 \parallel s_1 \xrightarrow{\alpha} p_3 \parallel s_3$ ,  $(p_1 \parallel s_1, \Delta(p_2 \mid [\mu, \nu] \mid s_2)) \in \mathcal{B}$ , and  $\alpha \in M_p$  (the case when  $\alpha \in M_s \cup E_s \cup E_p$  is similar). From the construction of  $\mathcal{B}$  we have  $p_1 \parallel s_1 \in \Re(p \parallel s)$  and there exists  $p'_2, s'_2, p_4, p'_4, s_4, s'_4, u, v$  such that

$$p_2 \parallel s'_2 \xrightarrow{u} p_4 \parallel s'_4 \nleftrightarrow_{\mathbf{b}} p_1 \parallel s_1 \nleftrightarrow_{\mathbf{b}} p'_4 \parallel s_4 \xleftarrow{v} p'_2 \parallel s_2.$$

(1)

Applying Proposition 1 we get  $p_2 \xrightarrow{?u} p_4$  and  $s_2 \xrightarrow{?v} s_4$ . Thus, we get  $\Delta(p_2 | [\mu, v] | s_2) \xrightarrow{\epsilon} \Delta(p_4 | [\epsilon, \epsilon] | s_4)$ . But from above we have  $p_4 || s'_4 \Leftrightarrow_{\mathbf{b}} p_1 || s_1 \leftrightarrow_{\mathbf{b}} p'_4 || s_4$ . Now instantiating transfer properties of branching bisimulation and since the processes p, s are concrete we get:

$$p_4 \parallel s'_4 \xrightarrow{m} p_5 \parallel s'_5 \underset{\mathbf{b}}{\leftrightarrow} p_3 \parallel s_3 \underset{\mathbf{b}}{\leftrightarrow} p'_5 \parallel s_5 \underset{\mathbf{c}}{\leftarrow} p'_4 \parallel s_4,$$

for some  $p_5, p'_5, s_5, s'_5 \in \mathbb{P}$ . Thus,  $\Delta(p_4 | [\epsilon, \epsilon] | s_4) \xrightarrow{m} \Delta(p_5 | [\epsilon, m] | s_4)$ . Finally, using the facts  $p_5 \parallel s'_5 \leftrightarrow_{\mathbf{b}} p_3 \parallel$  $s_5 \leftrightarrow_{\mathbf{b}} p' \parallel s_5$  and  $p' \parallel s_5 \xrightarrow{m} p' \parallel s_5$  in the construction of  $\mathcal{B}$  we conclude that  $(p_2 \parallel s_5, \Delta(p_5 \parallel \epsilon m) \mid s_5)) \in \mathcal{B}$

$s_{3} \underset{\mathbf{b}}{\hookrightarrow} p_{5}' \parallel s_{5} \text{ and } p_{4}' \parallel s_{4} \xrightarrow{m} p_{5}' \parallel s_{5} \text{ in the construction of } \mathcal{B} \text{ we conclude that } (p_{3} \parallel s_{3}, \Delta(p_{5} \mid [\epsilon, m] \mid s_{4})) \in \mathcal{B}.$ 2. Let  $(p_{1} \parallel s_{1}, \Delta(p_{2} \mid [\mu, \nu] \mid s_{2})) \in \mathcal{B}$  and  $(p_{1} \parallel s_{1}) \sqcup$ . By following the arguments of Case 1 we can derive  $\Delta(p_{2} \mid [\mu, \nu] \mid s_{2}) \xrightarrow{\epsilon} \Delta(p_{4} \mid [\epsilon, \epsilon] \mid s_{4}), \text{ for some } p_{4}, s_{4} \in \mathbb{P}.$  Clearly,  $(\Delta(p_{4} \mid [\epsilon, \epsilon] \mid s_{4})) \sqcup$ . Now using the facts  $p_{4} \parallel s_{4}' \underset{\mathbf{b}}{\leftrightarrow} p_{1} \parallel s_{1} \underset{\mathbf{b}}{\leftrightarrow} p_{4}' \parallel s_{4}$  from (1) in the construction of  $\mathcal{B}$  we get  $(p_{1} \parallel s_{1}, \Delta(p_{4} \mid [\epsilon, \epsilon] \mid s_{4})) \in \mathcal{B}.$

The proof for the other direction is an intricate one and we distinguish the following cases.

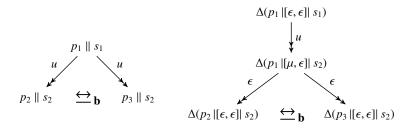

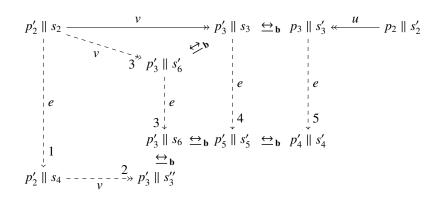

Let Δ(p<sub>2</sub> |[μ, ν]| s<sub>2</sub>) → Δ(p<sub>4</sub> |[μ', ν']| s<sub>4</sub>), (p<sub>1</sub> || s<sub>1</sub>, Δ(p<sub>2</sub> |[μ, ν]| s<sub>2</sub>)) ∈ B, and α ∈ E<sub>s</sub> (the case when α ∈ E<sub>p</sub> is symmetric). Then, by semantics we get p<sub>2</sub> = p<sub>4</sub>, s<sub>2</sub> → s<sub>4</sub>, μ' = μ, ν' = ν. From the construction of B we get the solid transitions depicted in Figure 7. Using the transition s<sub>2</sub> → s<sub>4</sub>, we get the dashed transition (1) in Figure 7. Consider the transition p'<sub>2</sub> || s<sub>2</sub> → p'<sub>3</sub> || s<sub>3</sub>. From Proposition 1 we have p'<sub>2</sub> → p'<sub>3</sub>. By generalised well-posedness we get the dashed transition (2) in Figure 7. By independence of external actions we get the two dashed transitions labelled as (3) in Figure 7. From input-determinism we get p'<sub>3</sub> || s'<sub>6</sub> ⇔<sub>b</sub> p'<sub>3</sub> || s<sub>3</sub>. And from the transfer conditions of branching bisimulation (under the concreteness assumption) we get the remaining dashed transitions (4) and (5).

Figure 7: Case 1 of Theorem 6.

Furthermore, from the construction of  $\mathcal{B}$  we have  $p_3 \parallel s'_3 \underset{\mathbf{b}}{\hookrightarrow} p_1 \parallel s_1$ . And, from the transfer conditions of a branching bisimulation (under concreteness assumption) we get there exists  $p'_1, s'_1$  such that  $p_1 \parallel s_1 \xrightarrow{e} p'_1 \parallel s'_1$  and  $p'_1 \parallel s'_1 \underset{\mathbf{b}}{\hookrightarrow} p'_4 \parallel s'_4$ . Finally, using the transitions  $p_2 \parallel s'_2 \xrightarrow{u.e} p'_4 \parallel s'_4$ ,  $p'_2 \parallel s_4 \xrightarrow{v} p'_3 \parallel s''_3$  and the fact that  $p'_3 \parallel s''_3 \underset{\mathbf{b}}{\hookrightarrow} p'_4 \parallel s'_4 \underset{\mathbf{b}}{\hookrightarrow} p'_1 \parallel s'_1$  in the construction of  $\mathcal{B}$  we conclude that  $(p'_1 \parallel s'_1, \Delta(p_2 \parallel \mu, \nu) \parallel s_4)) \in \mathcal{B}$ .

- 2. Let  $\Delta(p_2 | [\mu, \nu] | s_2) \xrightarrow{\alpha} \Delta(p_4 | [\mu', \nu'] | s_4)$ ,  $(p_1 || s_1, \Delta(p_2 | [\mu, \nu] | s_2)) \in \mathcal{B}$ , and  $\alpha \in M_s$  (the case when  $\alpha \in M_p$  is symmetric). Then,  $p_2 = p_4, \mu' = \mu.n, \nu' = \nu, s_2 \xrightarrow{!n} s_4$ , where  $\alpha = n$ , for  $n \in M_s$ . The remainder of the proof is similar to the previous case; except we use the diamond property instead of applying independence of external actions when both  $\mu$  and  $\nu$  are non-empty.

- 3. Let  $\Delta(p_2 | [\mu, \nu] | s_2) \xrightarrow{i} \Delta(p_4 | [\mu', \nu'] | s_4), (p_1 || s_1, \Delta(p_2 | [\mu, \nu] | s_2)) \in \mathcal{B}$ . Since the communicating components are concrete, the above transition is due to the removal of an element, either from  $\mu$  or from  $\nu$ . Thus,

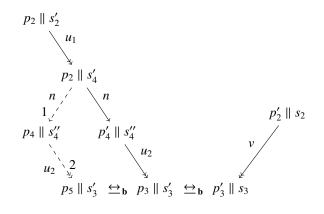

- (a) In case an element is removed from  $\mu$ , then,  $p_2 \xrightarrow{?n} p_4, \mu = n.\mu', \nu = \nu', s_2 = s_4$ , for some  $n \in M_s$ . From the construction of  $\mathcal{B}$  we have the transitions  $p_2 \parallel s'_2 \xrightarrow{u} p_3 \parallel s'_3$  and  $p'_2 \parallel s_2 \xrightarrow{\nu} p'_3 \parallel s_3$ . Since  $\bar{u} = \mu = n.\mu'$ , we can decompose the transition  $p_2 \parallel s'_2 \xrightarrow{u} p_3 \parallel s'_3$  as shown by the solid lines in Figure 8, where  $\bar{u}_1 = \epsilon$ , and  $\bar{u}_2 = \mu'$ . As  $p_2 \xrightarrow{?n} p_4$ , we get the dashed transition (1) in Figure 8. By generalised well-posedness, we get the dashed transition (2) in Figure 8, for some  $p_5 \in \mathbb{P}$ . And from input-determinism we get  $p_5 \parallel s'_3 \Leftrightarrow_{\mathbf{b}} p_3 \parallel s'_3$ . Finally, by using the transitions  $p_4 \parallel s''_4 \xrightarrow{u_2} p_5 \parallel s'_3$ ,  $p'_2 \parallel s_2 \xrightarrow{\nu} p'_3 \parallel s_3$  and the facts  $\bar{u}_2 = \mu'$  and  $p_5 \parallel s'_3 \leftrightarrow_{\mathbf{b}} p'_3 \parallel s_3 \leftrightarrow_{\mathbf{b}} p_1 \parallel s_1$  in the construction of  $\mathcal{B}$  we conclude that  $(p_1 \parallel s_1, \Delta(p_4 \parallel [\mu', \nu] \mid s_2)) \in \mathcal{B}$ .

- (b) In case an element is removed from  $\nu$ , the proof is symmetric.

- 4. Let  $(\Delta(p_2 | [\mu, \nu] | s_2)) \sqcup$  and  $(p_1 | | s_1, \Delta(p_2 | [\mu, \nu] | s_2)) \in \mathcal{B}$ . Trivial.

The next corollary states that substituting branching bisimulation equivalence by syntactical equivalence in the conditions of Theorem 6 does not affect the desynchronisability of a synchronous system.

**Corollary 1.** Let  $p \parallel s$  be concrete, well-posed, independent of external actions modulo =, input deterministic modulo =, and satisfies the diamond property modulo =, then  $p \parallel s \Leftrightarrow_{\mathbf{b}} \Delta(p \mid [\epsilon, \epsilon] \mid s)$ .

Note that the definition of the relation  $\mathcal{B}$  given in the proof of Theorem 6 is independent of the size of queues. This leads us to claim, without further proof, that the conditions of Theorem 6 are also sufficient in case we use lossless queues of finite size with back-pressure to construct our asynchronous system (just like the main theorems of [8]).

Figure 8: Case 3 of Theorem 6.

#### 3.6. A simplified sufficient condition for desynchronisability

In this subsection, we give an equivalent sufficient condition for desynchronisability which is much simpler to verify on a given synchronous system than the preconditions of Corollary 1. The motive is to find the equivalent formulations of independence of external actions (modulo =) and input determinism (modulo =) using the single step transition relation  $\rightarrow$ , instead of using the multiple steps transition relation  $\rightarrow$ .

**Definition 10.** A synchronous system  $p \parallel s$  is *locally* independent of external actions if the following conditions holds for every  $p_1 \parallel s_1 \in \Re(p \parallel s)$ .

1.

$$\forall p_2, p'_2, s_2, n, e.\left[\left(e \in E_p \land n \in M_s \land p_1 \parallel s_1 \xrightarrow{e} p_2 \parallel s_1 \xrightarrow{n} p'_2 \parallel s_2\right) \Rightarrow \exists p_3.\left[p_1 \parallel s_1 \xrightarrow{n} p_3 \parallel s_2 \xrightarrow{e} p'_2 \parallel s_2\right]\right].$$

2.  $\forall p_2, s_2, s'_2, m, e.\left[\left(e \in E_s \land m \in M_p \land p_1 \parallel s_1 \xrightarrow{e} p_1 \parallel s_2 \xrightarrow{m} p_2 \parallel s'_2\right) \Rightarrow \exists s_3.\left[p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_3 \xrightarrow{e} p_2 \parallel s'_2\right]\right].$

**Lemma 5.** A concrete synchronous system  $p \parallel s$  is locally independent of external actions iff it is independent of external actions modulo =.

*Proof.* The only-if part follows directly from Definition 7. To prove the *if* part, assume the transitions  $p_1 || s_1 \xrightarrow{e} p_2 || s_1 \xrightarrow{u} p'_2 || s_2$ , where  $p_1 || s_1 \in \Re(p || s)$ ,  $e \in E_p$ , and  $u \in (M_s \cup E_s)^*$ . We show by induction on *u* that there exists  $p_3$  such that  $p_1 || s_1 \xrightarrow{u} p_3 || s_2 \xrightarrow{e} p'_2 || s_2$ . Without loss of generality, assume  $u = u'.\alpha$  such that  $p_2 || s_1 \xrightarrow{u'} p'_3 || s'_2 \xrightarrow{\alpha} p'_2 || s_2$ , for some  $p'_3, s'_2 \in \mathbb{P}$  and  $u' \in (M_s \cup E_s)^*$  and  $\alpha \in M_s \cup E_s$ . Then, by induction hypothesis we have  $p_1 || s_1 \xrightarrow{u'} p_3 || s'_2 \xrightarrow{e} p'_3 || s'_2$ , for some  $p_3 \in \mathbb{P}$ . Now performing case distinction on  $\alpha$  we get the following cases.

- 1. Let  $\alpha = e'$  for some  $e' \in E_s$ . Then, by the semantics we have  $p'_3 = p'_2$  and  $s'_2 \xrightarrow{e'} s_2$ . Using this transition at the state  $p_3 \parallel s'_2$  we get  $p_3 \parallel s'_2 \xrightarrow{e'} p_3 \parallel s_2$ . But, from inductive hypothesis we have  $p_3 \xrightarrow{e} p'_2$ . Thus,  $p_3 \parallel s_2 \xrightarrow{e} p'_2 \parallel s_2$ ; hence,  $p_1 \parallel s_1 \xrightarrow{u} p_3 \parallel s_2 \xrightarrow{e} p'_2 \parallel s_2$  as required.

- 2. Let  $\alpha = n$  for some  $n \in M_s$ . Then, by applying Definition 10 we get  $p_3 \parallel s'_2 \xrightarrow{n} p_4 \parallel s_2 \xrightarrow{e} p'_2 \parallel s_2$ , for some  $p_4 \in \mathbb{P}$ . Thus,  $p_1 \parallel s_1 \xrightarrow{u} p_4 \parallel s_2 \xrightarrow{e} p'_2 \parallel s_2$  as required.

**Definition 11.** A synchronous system  $p \parallel s$  is *locally* input deterministic if every reachable state  $p_1 \parallel s_1 \in \Re(p \parallel s)$  satisfies the following conditions.

1.  $\forall p_2, s_2, p_3, n. \left[ \left( p_1 \parallel s_1 \xrightarrow{n} p_2 \parallel s_2 \land p_1 \parallel s_1 \xrightarrow{n} p_3 \parallel s_2 \land n \in M_s \right) \Rightarrow p_2 \parallel s_2 = p_3 \parallel s_2 \right].$

2.

$$\forall p_2, s_2, s_3, m.\left[\left(p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_2 \land p_1 \parallel s_1 \xrightarrow{m} p_2 \parallel s_3 \land m \in M_p\right) \Rightarrow p_2 \parallel s_2 = p_2 \parallel s_3\right].$$

**Lemma 6.** A concrete synchronous system  $p \parallel s$  is locally input deterministic iff it is input deterministic modulo =.

*Proof.* The *only-if* part follows directly from Definition 8. The *if* part follows by performing induction on sequences  $u \in (M_s \cup E_s)^*$  ( $v \in (M_p \cup E_p)^*$ ) and instantiating Definition 11.

Now, we are ready to prove the main result of this subsection.

**Theorem 7.** Let  $p \parallel s$  be concrete, well-posed, locally independent of external actions, locally input deterministic, and satisfies the diamond property modulo =, then  $p \parallel s \Leftrightarrow_{\mathbf{b}} \Delta(p \mid [\epsilon, \epsilon] \mid s)$ .

*Proof.* By Lemmas 5,6 and Corollary 1.

#### 3.7. Half-duplex communication eliminates the diamonds

In the previous subsections, we showed that the diamond property is a necessary condition for desynchronisability, while we expressed a desire in the introduction to desynchronise systems that do not possess this property as well. This leads us to rethink our model of desynchronisation.

Changing the notion of equivalence or the observation of the predicate is not likely to help. Previous research [3, 7] has been performed on weaker notions of equivalence, and although the diamond property was not identified as a necessary condition there, it did come up as a natural sufficient condition that the authors could not work around. This is why we decided to experiment with the properties of the buffer instead.

Inspired by the observation that the problem occurs when both communicating parties would like to send a message at the same time, we decided to see if *half-duplex communication*, in which only one party can communicate at a time, would give a solution. We model half-duplex communication between processes p and s as a process  $p |[\epsilon, \epsilon]|_h s$ , of which the structured operational semantics are given in Table 4. Observe that the rules are similar to those we used before, except that either the left or the right queue remains empty at all times.

Table 4: SOS rules for asynchronous systems with half-duplex queues.

| $p \xrightarrow{!m} p'$                                                                       | $s \xrightarrow{!n} s'$                                                                                                       |                                      |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| $(p \mid [\epsilon, \nu]]_{h} s) \xrightarrow{!m} (p' \mid [\epsilon, \nu]$                   | $[m] _{\mathrm{h}} s)  (p \mid [\mu, \epsilon] _{\mathrm{h}} s) \xrightarrow{!_{n}} (p \mid [\mu.n, \epsilon] _{\mathrm{h}})$ | s')                                  |

| $p \xrightarrow{?n} p', \ \mu = n.\mu', \ n \in P$                                            | $M_s \qquad s \xrightarrow{?m} s', \ v = m.v', \ m \in M_p$                                                                   |                                      |

| $(p \mid [\mu, \nu]]_{\mathrm{h}} s) \xrightarrow{?n} (p' \mid [\mu', \nu])$                  | $\overline{(p \mid [\mu, \nu]]_{h} s)}  \overline{(p \mid [\mu, \nu]]_{h} s)} \xrightarrow{?m} (p \mid [\mu, \nu']]_{h} s'$   | )                                    |

| $p \xrightarrow{\alpha} p', \ \alpha \in E_p \cup \{\tau\}$                                   | $s \xrightarrow{\alpha} s', \ \alpha \in E_s \cup \{\tau\}$                                                                   |                                      |

| $(p   [\mu, \nu] _{\mathfrak{h}} s) \xrightarrow{\alpha} (p'   [\mu, \nu] _{\mathfrak{h}} s)$ | $(p   [\mu, \nu] _{h} s) \xrightarrow{\alpha} (p   [\mu, \nu] _{h} s') \qquad (p   [\epsilon$                                 | $[\epsilon,\epsilon] _{h} s) \sqcup$ |

**Definition 12.** A synchronous system  $p \parallel s$  is half-duplex desynchronisable if  $p \parallel s \Leftrightarrow_{\mathbf{h}} \Delta(p \mid [\epsilon, \epsilon] \mid_{\mathbf{h}} s)$ .

Next, we find that the diamond property can be dropped from the necessary and sufficient conditions.

**Theorem 8.** Let  $p \parallel s$  be concrete and half-duplex desynchronisable, then it is well-posed, independent of external actions, and input deterministic.

*Proof.* Along the same lines as the proofs in the previous section.

# **Theorem 9.** Suppose a concrete process $p \parallel s$ is well-posed, independent of external actions, and input deterministic, then it is half-duplex desynchronisable.

*Proof.* Recall the relation  $\mathcal{B}$  from Theorem 6 and replace the full-duplex operator with our new half-duplex operator. This relation will serve as a witness for our theorem along the same lines set out in Theorem 6, except that in Case 2 we find for the queue contents that either  $\mu$  or  $\nu$  will be empty due to the half-duplex condition. As a result, the necessity of the diamond property in this proof disappears.

#### Relaxing the half-duplex condition

As already mentioned, the half-duplex mechanism leads to an inefficient design of an asynchronous system because a sender is not allowed to send messages while its input queue is non-empty. Furthermore, our only reason for wanting half-duplex communication is that we could not guarantee the diamond property for our synchronous system.