# Pilkington Library

| Author/Filing Title | KANE, A    |   |

|---------------------|------------|---|

| Accession/Copy No.  |            | ٠ |

| Vol. No             | Class Mark |   |

| - 2 NOV 2000        | LOAN CORY  |   |

| FOR :               |            |   |

| ·                   | -          | : |

2.54

040208554X

# AN INSTRUCTION SYSTOLIC ARRAY ARCHITECTURE FOR MULTIPLE NEURAL NETWORK TYPES

by Andrew Kane

September 1998

A doctoral thesis submitted in partial fulfilment of the requirements for the Degree of Doctor of Philosophy in

Department of Computer Studies,

Loughborough University

Loughborough, Leicestershire, LE11 3TU, UK

© by Andrew Kane, 1998

# To my darling wife

# Hilary

for her love, support and encouragement

| Lough<br>W Univer | Silv<br>Silv |

|-------------------|--------------|

| Dan Le            | 14           |

| Class             |              |

| Acc<br>No. 00208  | 554          |

|                   |              |

K0645010

j. 1

**ABSTRACT**

Modern electronic systems, especially sensor and imaging systems, are beginning to

incorporate their own neural network subsystems. In order for these neural systems to learn in

real-time they must be implemented using VLSI technology, with as much of the learning

processes incorporated on-chip as is possible. The majority of current VLSI implementations

literally implement a series of neural processing cells, which can be connected together in an

arbitrary fashion. Many do not perform the entire neural learning process on-chip, instead

relying on other external systems to carry out part of the computation requirements of the

algorithm.

The work presented here utilises two dimensional instruction systolic arrays in an attempt to

define a general neural architecture which is closer to the biological basis of neural networks - it

is the synapses themselves, rather than the neurons, that have dedicated processing units. A

unified architecture is described which can be programmed at the microcode level in order to

facilitate the processing of multiple neural network types.

An essential part of neural network processing is the neuron activation function, which can

range from a sequential algorithm to a discrete mathematical expression. The architecture

presented can easily carry out the sequential functions, and introduces a fast method of

mathematical approximation for the more complex functions. This can be evaluated on-chip,

thus implementing the entire neural process within a single system.

VHDL circuit descriptions for the chip have been generated, and the systolic processing

algorithms and associated microcode instruction set for three different neural paradigms have

been designed. A software simulator of the architecture has been written, giving results for

several common applications in the field.

Keywords: Systolic Array; Instruction Systolic Array; Systolic Algorithm Design; Parallel

Processing; Computer Architecture; Neural Networks; Backpropagation;

Kohonen; Counter-Propagation

i

## **ACKNOWLEDGEMENTS**

I would like to acknowledge the supervision and guidance given to me over the last few years by Professor D.J. Evans of the Department of Computer Studies at Loughborough University. His advice over the subjects that I choose to pursue during my studies was both stimulating and sincere, showing time and time again that he wished for me to get the very best out of my research, as well as managing to keep me motivated and interested in my subjects in spite of any problems that arose over my time at Loughborough. He also managed to keep me writing-up at a reasonable rate once I had left University to enter the world of work; when your industrial work is so unrelated to your studies it is often difficult to keep going and it is a credit to Professor Evans that I finally managed to complete my studies.

I would like to thank Professor S. Jones of the Department of Electrical Engineering at Loughborough University who, through the help of his staff, allowed me access to the resources so that I was able to carry out the microelectronic circuit designs that were vital to this work. It is only a shame that the funding was never available to actually fabricate the device that I designed.

I would like to thank those at Jasmin Simtec Ltd in Bulwell, Nottingham, for taking me on board even though I had not completed my studies. Many people there have given me encouragement in completing, as well as lending me the odd resource (especially time) to help me complete my research. It has been almost 18 months since I started at Jasmin and the studies are at an end - I hope it was worth the wait for them!

Finally, I would like to thank my wife, Hilary, for putting up with this for so long. Spending the first year of married life with me always saying "I'll just do another page or two" was not exactly the start in life together that we both anticipated. Her support in this work was invaluable and I doubt that I could have done it without her. Now that it is complete I hope we can go on now and begin to enjoy our lives together.

# **CONTENTS**

| 1. | INT | RODUCTION                                                 | 1  |

|----|-----|-----------------------------------------------------------|----|

|    | 1.1 | Introduction                                              | 1  |

|    | 1.2 | Evolution of Computing Machines                           | 3  |

|    |     | 1.2.1 What is a 'Computer'?                               | 3  |

|    |     | 1.2.2 Historical Development of Computers                 | 4  |

|    | 1.3 | Evolution of VLSI Technology                              | 9  |

|    |     | 1.3.1 Development of Integrated Circuit Technology        | 9  |

|    |     | 1.3.2 VLSI Scalability Constraints                        | 12 |

|    | 1.4 | Parallel Computer Architectures                           | 17 |

|    |     | 1.4.1 Historical Legacies                                 | 17 |

|    |     | 1.4.2 High-Level Parallel Architecture Classification     | 21 |

|    | 1.5 | Thesis Organisation                                       | 35 |

|    |     | 1.5.1 Part 1 - Introduction                               | 35 |

|    |     | 1.5.2 Part 2 - Systolic Array Architecture and Algorithms | 36 |

|    |     | 1.5.3 Part 3 - Software and Hardware Implementation       | 37 |

| 2. | BAC | CKGROUND TECHNOLOGY                                       | 38 |

|    | 2.1 | VLSI Fabrication Technology                               | 38 |

|    |     | 2.1.1 Silicon Semiconductor Technology                    | 38 |

|    |     | 2.1.2 Standard p-Well Fabrication Process                 | 41 |

|    |     | 2.1.3 Other Fabrication Processes                         | 46 |

|    | 2.2 | Digital Logic Testing Techniques                          | 51 |

|    |     | 2.2.1 Introduction to Digital Logic Testing               | 51 |

|    |     | 2.2.2 Combination and Sequential Logic Test Strategies    | 55 |

|    | 2.3 | Systolic Array Architectures                              | 60 |

|    |     | 2.3.1 Introduction                                        | 60 |

|    |     | 2.3.2 Systolic Architecture Definitions                   | 62 |

|    |     | 2.3.3 Linear Connected Systolic Array                     | 65 |

|    |     | 2.3.4 Dense Matrix Systolic Arrays                        | 69 |

| 3. | ART | TIFICIAL NEURAL NETWORKS                                  | 77 |

|    | 3.1 | Neural Network Overview                                   | 77 |

|    |     | 3.1.1 What are Neural Networks?                           | 77 |

|    |     | 3.1.2 Biological and Physiological Background             | 78 |

|    |     | 3.1.3 Historical Perspective of Neural Networks           | 81 |

|    |     |                                                           |    |

|    | 3.2  | Commo   | on Neural Network Learning Methodologies                | 84  |

|----|------|---------|---------------------------------------------------------|-----|

|    |      | 3.2.1   | Perceptron Learning                                     | 84  |

|    |      | 3.2.2   | Backpropagation Learning                                | 87  |

|    | •    | 3.2.3   | Kohonen Self-Organised Learning                         | 94  |

|    | 3.3  | Alterna | tive Neural Network Learning Methodologies              | 98  |

|    |      | 3.3.1   | Counter Propagation Learning                            | 98  |

|    |      | 3.3.2   | Hopfield Learning                                       | 101 |

|    |      | 3.3.3   | Adaptive Resonance Theory                               | 107 |

| 4. | IMP  | LEME    | NTATION OF NEURAL NETWORKS                              | 113 |

|    | 4.1  | VLSIN   | Neural Network Systems                                  | 113 |

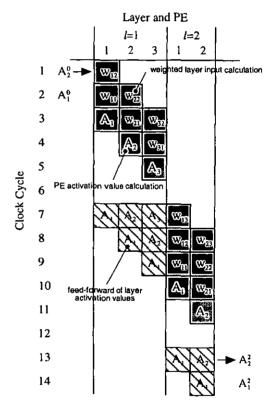

|    |      | 4.1.1   | Backpropagation in Linear Arrays                        | 113 |

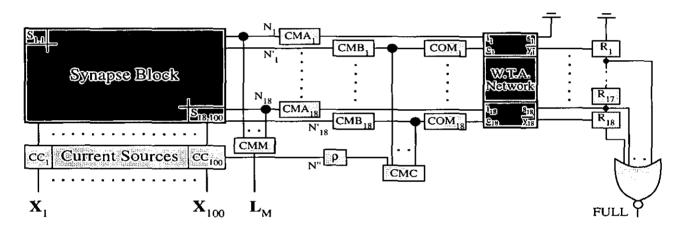

|    |      | 4.1.2   | Real-Time Clustering Neural Engine                      | 118 |

|    | 4.2  | Neural  | Network Applications                                    | 123 |

|    |      | 4.2.1   | Traffic Management of a Satellite Communication Network | 123 |

|    |      | 4.2.2   | Prediction of a Continuous Stirred Tank Reactor         | 130 |

| 5. | PRO  | POSE    | D ARCHITECTURAL DESIGN                                  | 136 |

|    | 5.1  | Archite | ectural Overview                                        | 136 |

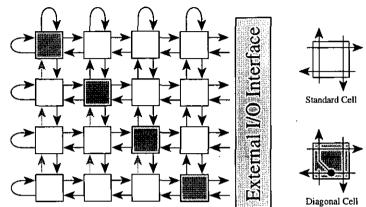

|    |      | 5.1.1   | Array Structure                                         | 136 |

|    |      | 5.1.2   | Instruction Systolic Array Processing                   | 138 |

|    |      | 5.1.3   | Array I/O Requirements and Processing                   | 139 |

|    |      | 5.1.4   | Data Format and Precision                               | 141 |

|    |      | 5.1.5   | Processing Element Structure                            | 143 |

|    | 5.2  |         | Network Hardware Features                               |     |

|    |      | 5.2.1   | On-Chip Learning Methodology                            | 144 |

|    |      | 5.2.2   | Reconfigurable Instruction Set                          | 145 |

|    |      | 5.2.3   | Activation Function Approximation                       | 151 |

|    | 5.3  | Hardw   | are Design and Implementation                           | 159 |

|    |      | 5.3.1   | Miscellaneous Circuits                                  | 159 |

|    |      | 5.3.2   | Register Units                                          | 164 |

|    |      | 5.3.3   | Instruction Set Memory                                  | 165 |

|    |      | 5.3.4   | Addition Unit                                           | 167 |

|    |      | 5.3.5   | Multiplier Unit                                         | 170 |

| 6. | SYS' | TOLIC   | C NEURAL ALGORITHMS                                     | 173 |

|    | 6.1  |         | ropagation Learning Algorithm                           | 173 |

|    |      | 6.1.1   | Introduction                                            |     |

|    |      |         |                                                         |     |

|    |     |        | Counter Propagation Timings                      |     |

|----|-----|--------|--------------------------------------------------|-----|

| 7. | NEU | JRAL   | NETWORK SOFTWARE SIMULATION                      | 206 |

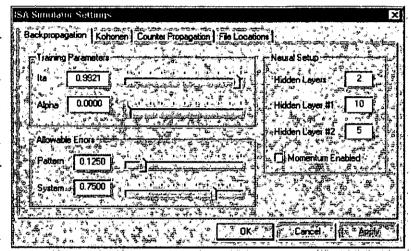

|    | 7.1 | Soft S | ystolic Simulator                                | 206 |

|    |     | 7.1.1  | Simulator Overview                               | 206 |

|    |     | 7.1.2  | Simulator Data Definitions                       | 208 |

|    | 7.2 | Backp  | ropagation Learning Applications                 | 210 |

|    |     | 7.2.1  | Exclusive-Or Problem                             | 210 |

|    |     | 7.2.2  | Parity Problem                                   | 212 |

|    |     | 7.2.3  | Simple Pattern Recognition                       | 215 |

|    | 7.3 | Kohon  | nen Application - Pattern Recognition            | 217 |

|    |     | 7.3.1  | Problems Associated with Kohonen Learning        |     |

|    |     | 7.3.2  | Simulation Strategy                              |     |

|    |     | 7.3.3  | Network Structure                                |     |

|    |     | 7.3.4  | Simulation Run                                   |     |

|    | 7.4 | Count  | er Propagation Application - Pattern Recognition |     |

|    |     | 7.4.1  | Application Overview                             |     |

|    |     | 7.4.2  | Network Structure                                |     |

|    |     | 7.3.3  | Kohonen Simulation Run                           |     |

|    |     |        | Counter Propagation Simulation Run               |     |

|     |             | 8.1.1   | Increasing Computational Capacity          | 223 |

|-----|-------------|---------|--------------------------------------------|-----|

|     |             | 8.1.2   | Hardware Implementation of Neural Networks | 225 |

|     |             | 8.1.3   | Practical Advantages of Study              | 226 |

|     | 8.2         | Further | r Work                                     | 229 |

|     |             | 8.2.1   | Increased Micro-code Capacity              | 229 |

|     |             | 8.2.2   | Index Registers                            | 230 |

|     |             | 8.2.3   | Conditional Instructions                   | 231 |

|     |             | 8.2.4   | Multiple Processing Paths                  | 232 |

|     | 8.3         | Final C | Comments                                   | 233 |

|     |             |         |                                            |     |

| Α.  | CIRC        | CUIT    | DESIGNS AND VHDL CODE                      | 234 |

|     | <b>A</b> .1 | Basic ( | Circuit Elements                           | 234 |

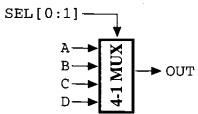

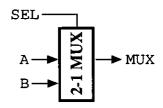

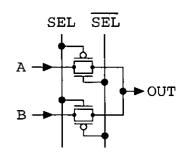

|     |             | A.1.1   | 2-to-1 Multiplexor                         | 234 |

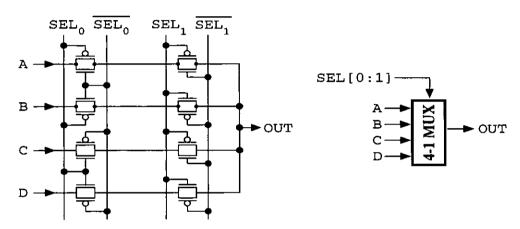

|     |             | A.1.2   | 4-to-1 Multiplexor                         | 235 |

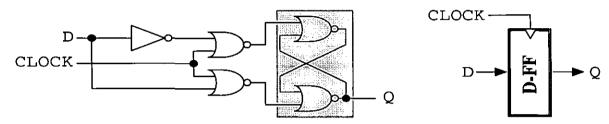

|     |             | A.1.3   | D-Type Flip-Flop                           | 236 |

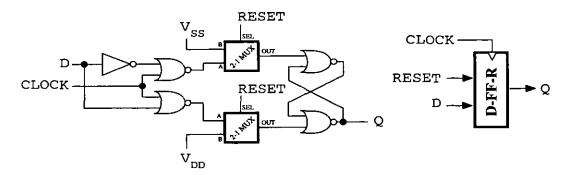

|     |             | A.1.4   | D-Type Flip-Flop with Reset                | 236 |

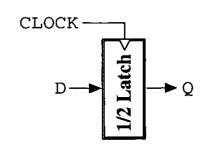

|     |             | A.1.5   | Half Latch                                 | 237 |

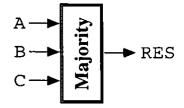

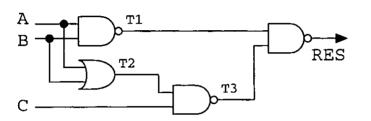

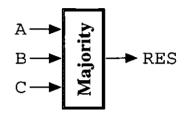

|     |             | A.1.6   | 3-Input Majority Function                  | 238 |

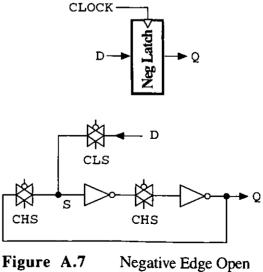

|     |             | A.1.7   | Negative Clock Open Latch                  | 239 |

|     | A.2         | Data S  | torage Units                               | 240 |

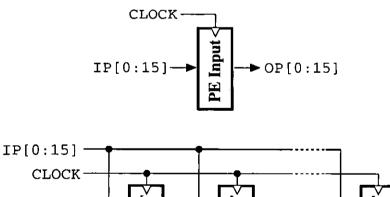

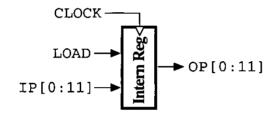

|     |             | A.2.1   | PE Input Register                          | 240 |

|     |             | A.2.2   | PE Output Register                         | 241 |

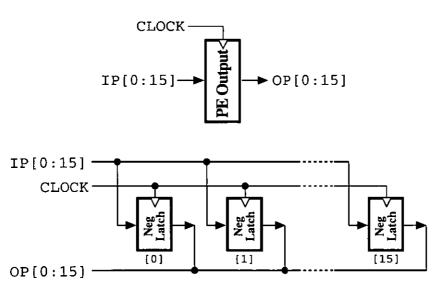

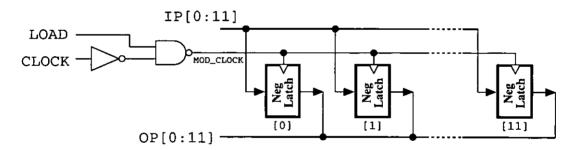

|     |             | A.2.3   | PE Internal Register Block                 | 242 |

|     | A.3         | Instruc | ction Set Storage                          | 248 |

|     |             | A.3.1   | Memory Read/Write Generator                | 248 |

|     |             | A.3.2   | Opcode Lock Unit                           | 250 |

|     |             | A.3.3   | Additional Control Signal Store            | 253 |

|     |             | A.3.4   | Instruction Set RAM Unit                   | 255 |

|     |             | A.3.5   | Complete Instruction Set Store             | 263 |

|     | A.4         | Mathe   | matical Units                              | 265 |

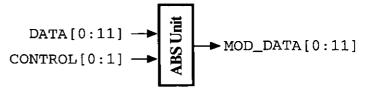

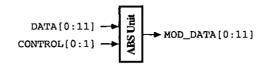

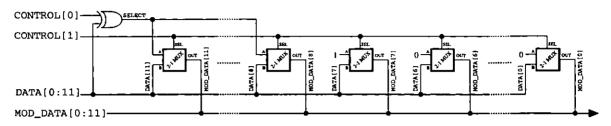

|     |             | A.4.1   | ABS Unit                                   | 265 |

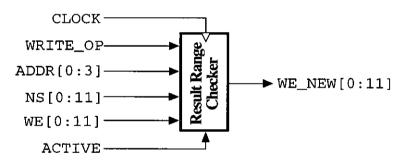

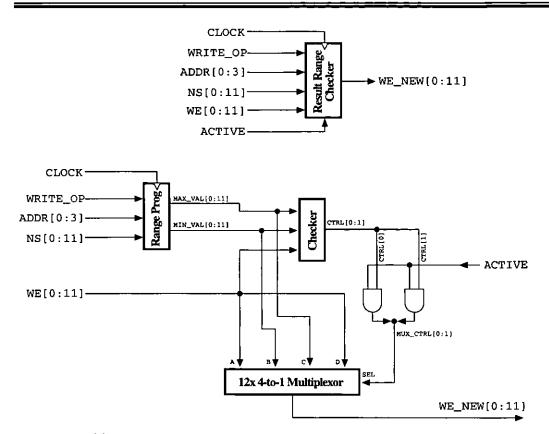

|     |             | A.4.2   | Result Range Limiter                       | 266 |

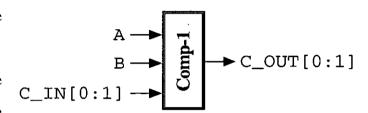

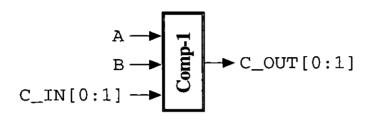

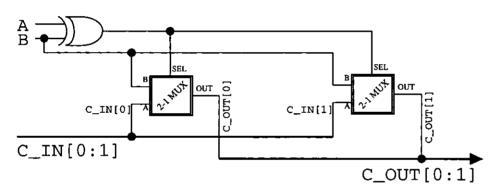

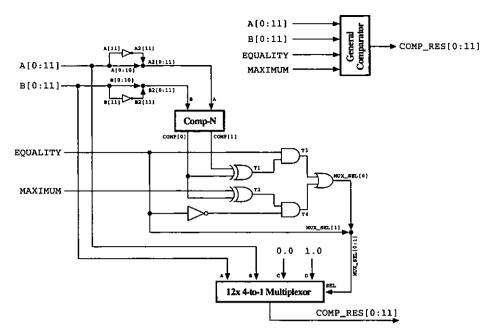

|     |             | A.4.3   | General Purpose Comparator                 | 273 |

|     |             | A.4.4   | Fixed-Point Adder Unit                     | 275 |

|     |             | A.4.5   | Fixed Point Multiplier Unit                | 284 |

|     |             |         |                                            |     |

| REE | EREN        | ICES    |                                            | 290 |

# LIST OF FIGURES

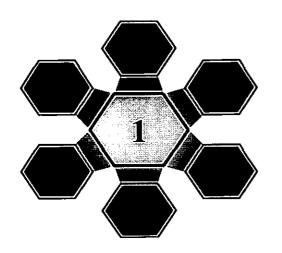

| Figure 1.1  | Wafer-Scale Integration Lattice                          | 12 |

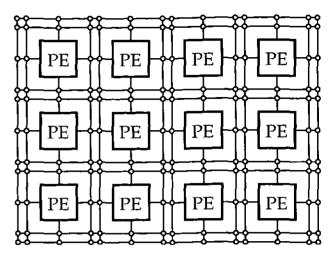

|-------------|----------------------------------------------------------|----|

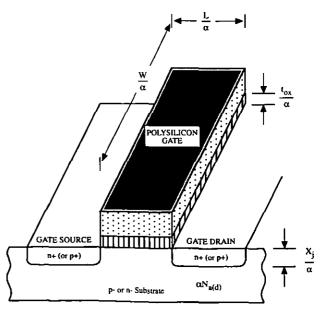

| Figure 1.2  | Scaled MOS device                                        | 13 |

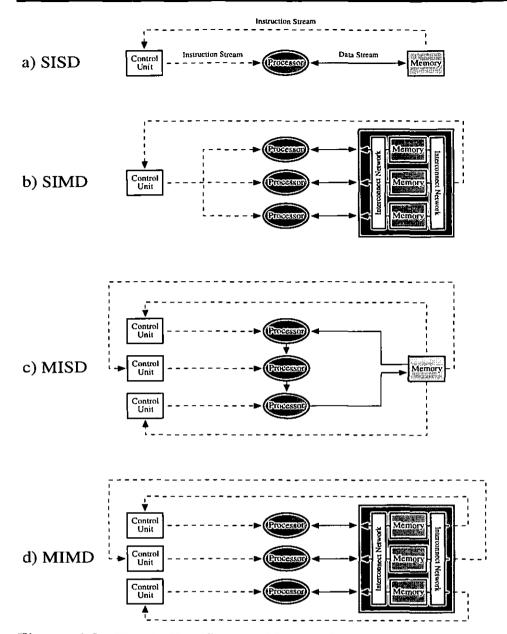

| Figure 1.3  | Flynn's Classification of Parallel Computer Architecture | 18 |

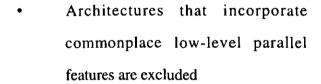

| Figure 1.4  | Duncan's Classifications                                 | 22 |

| Figure 1.5  | Vector Processor Dataflow                                | 23 |

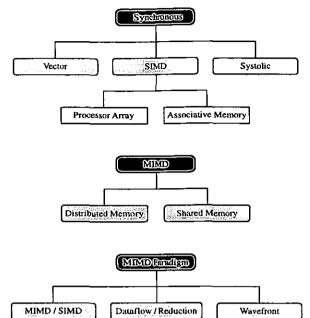

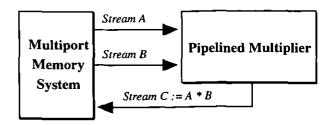

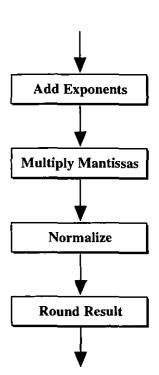

| Figure 1.6  | Multiplier Pipeline                                      | 23 |

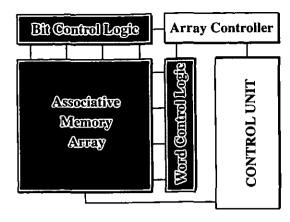

| Figure 1.7  | Associative Memory Schematic                             | 25 |

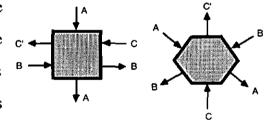

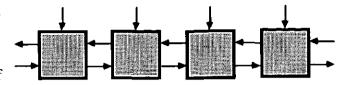

| Figure 1.8  | Basic Concept of Systolic Arrays                         | 26 |

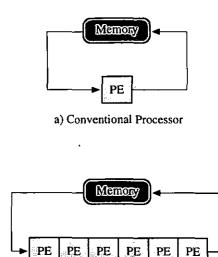

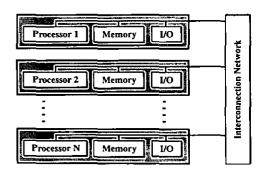

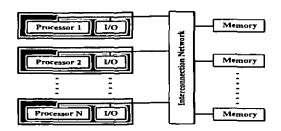

| Figure 1.9  | Distributed Memory Architecture                          | 27 |

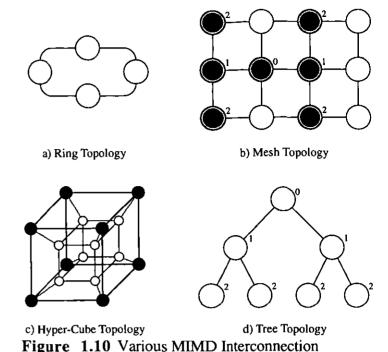

| Figure 1.10 | Various MIMD Interconnection Topologies                  | 28 |

| Figure 1.11 | Shared Memory Architecture                               | 30 |

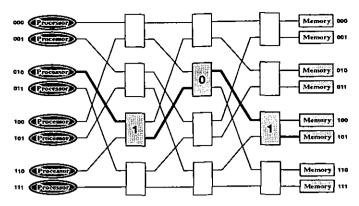

| Figure 1.12 | Shuffle-Exchange Network                                 | 31 |

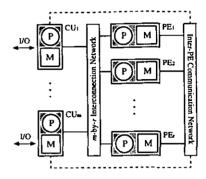

| Figure 1.13 | MIMD/SIMD Architecture                                   | 33 |

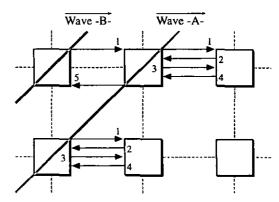

| Figure 1.14 | Wavefront Array Architecture                             | 34 |

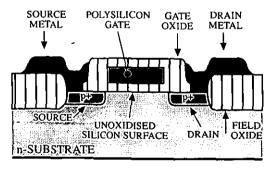

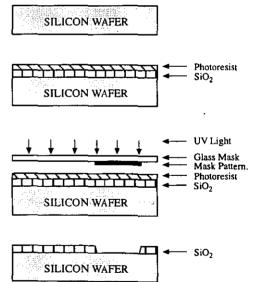

| Figure 2.1  | Field Oxide Growth                                       | 39 |

| Figure 2.2  | Patterning of SiO <sub>2</sub>                           | 40 |

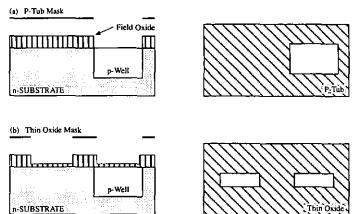

| Figure 2.3  | Well and ThinOx Deposition                               | 41 |

| Figure 2.4  | Gate Definition                                          | 42 |

| Figure 2.5  | Gate Metallisation                                       | 42 |

| Figure 2.6  | Inverter Layout and Schematic                            | 43 |

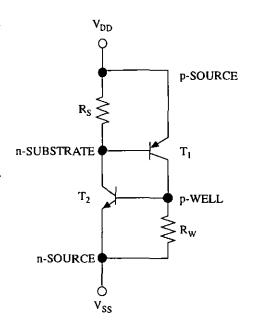

| Figure 2.7  | Parasitic Latch-Up Equivalent Circuit                    | 44 |

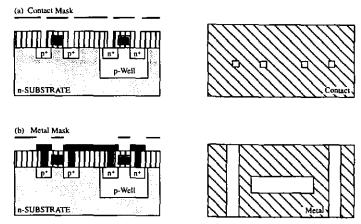

| Figure 2.8  | Substrate Contacts                                       | 45 |

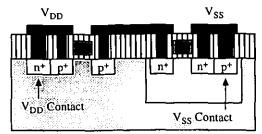

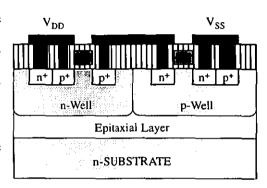

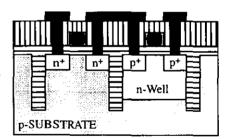

| Figure 2.9  | Twin-Tub Process Cross-Section                           | 47 |

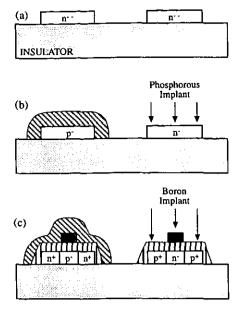

| Figure 2.10 | Selection of SOI Process Steps                           | 48 |

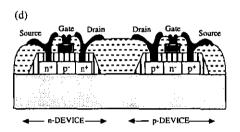

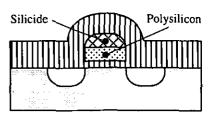

| Figure 2.11 | Silicide Gate                                            | 49 |

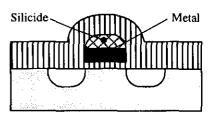

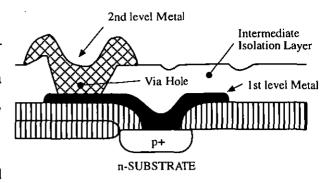

| Figure 2.12 | Second Level Metal                                       | 50 |

| Figure 2.13 | Trench Isolation Cross Section                           | 50 |

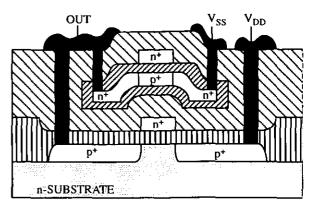

| Figure 2.14 | 3-D CMOS Cross Section                                   | 51 |

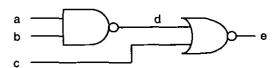

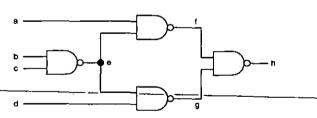

| Figure 2.15 | Simple Function Schematic                                | 56 |

| Figure 2.16 | Reconvergent Fan-Out                                     | 57 |

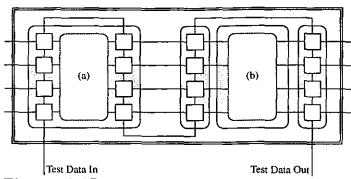

| Figure 2.17 | Outline of Boundary Scan Structure                       | 59 |

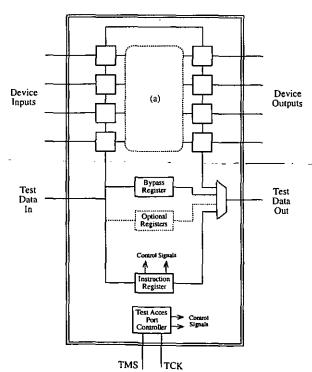

| Figure 2.18 | JTAG Device Architecture                                 | 59 |

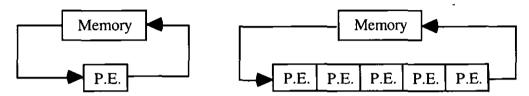

| Figure 2.19 | Von Neuman .v. Systolic Array Architecture               | 61 |

| Figure 2.20 | Geometry for IPS Processors                              | 64 |

| -           | •                                                        |    |

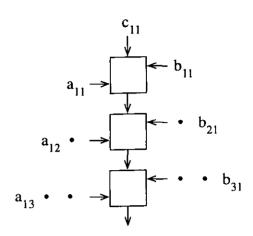

| Figure 2.21 | Linearly Connected Systolic Array                        | 65  |

|-------------|----------------------------------------------------------|-----|

| Figure 2.22 | Bi-Directional Systolic Array for Convolution            | 66  |

| Figure 2.23 | Matrix-Vector Multiplication Problem Data                | 67  |

| Figure 2.24 | Data Connection Map for Matrix-Vector Multiplication     | 67  |

| Figure 2.25 | Initial Cycles of Matrix-Vector Multiplication           | 69  |

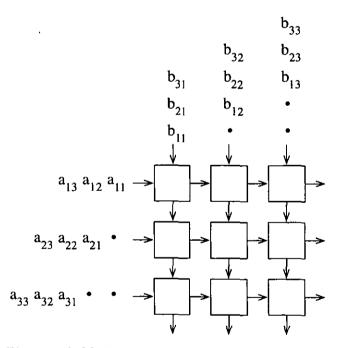

| Figure 2.26 | Rectangular Array for Scalar Products                    | 70  |

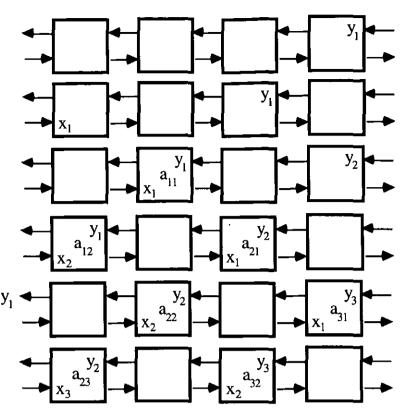

| Figure 2.27 | Full Rectangular Array for 3x3 Scalar Products           | 70  |

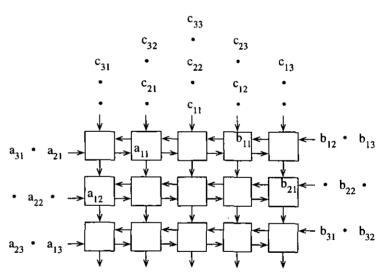

| Figure 2.28 | Square Array MAC Cell Configuration                      | 71  |

| Figure 2.29 | Full Square Array for 3x3 Scalar Products                | 71  |

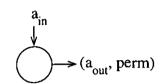

| Figure 2.30 | Triangular System Cells                                  | 73  |

| Figure 2.31 | Triangular System Linear Array                           | 73  |

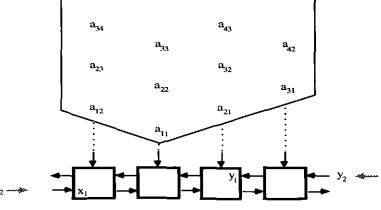

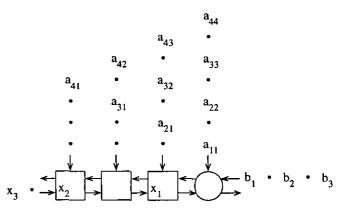

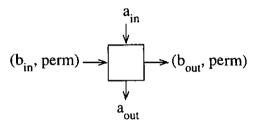

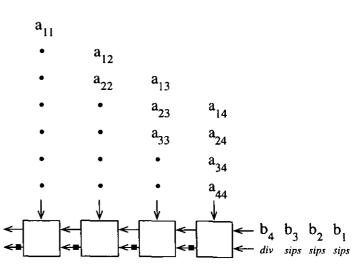

| Figure 2.32 | Cell Topology for Gaussian Elimination                   | 75  |

| Figure 2.33 | Triangularisation of a Dense Matrix (n=4)                | 76  |

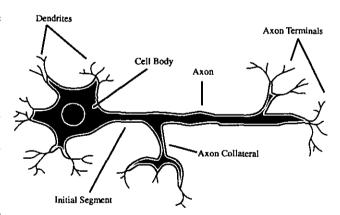

| Figure 3.1  | Diagrammatic Representation of a Biological Neuron       | 78  |

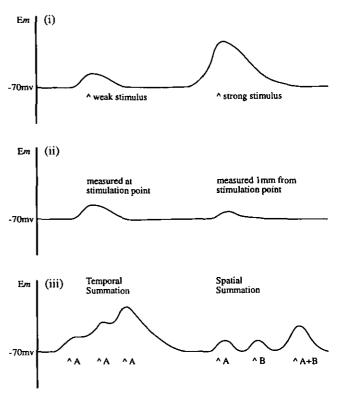

| Figure 3.2  | Graded Potential Possibilities                           | 80  |

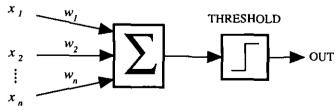

| Figure 3.3  | Perceptron Neuron Structure                              | 84  |

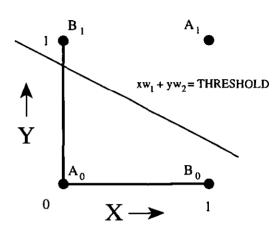

| Figure 3.4  | Exclusive-Or Threshold on the X-Y Plane                  | 86  |

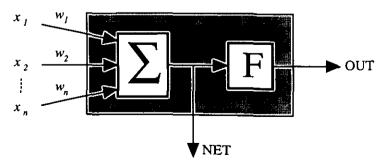

| Figure 3.5  | Backpropagation Neuron Schematic                         | 87  |

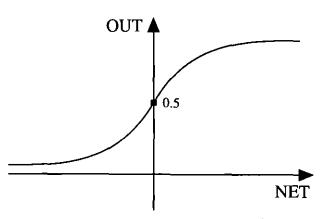

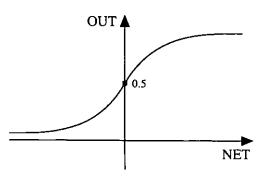

| Figure 3.6  | Backpropagation Activation Sigmoid Function              | 88  |

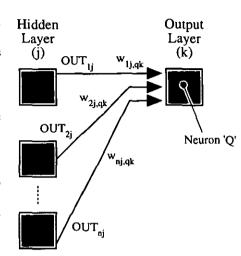

| Figure 3.7  | Connections for Output Layer Training                    | 91  |

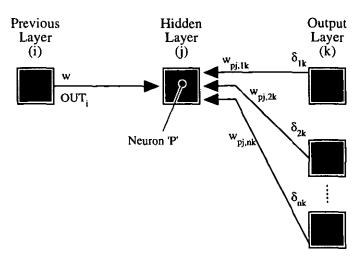

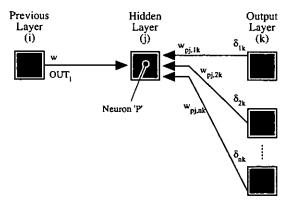

| Figure 3.8  | Connections for Hidden Layer Training                    | 92  |

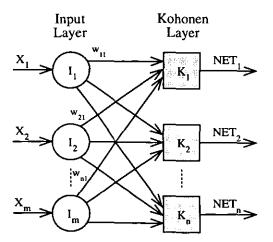

| Figure 3.9  | Kohonen Neural Network Layer                             | 94  |

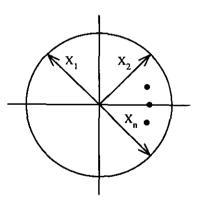

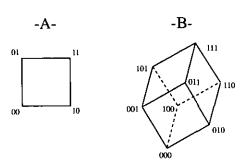

| Figure 3.10 | Unit Length Vectors                                      | 95  |

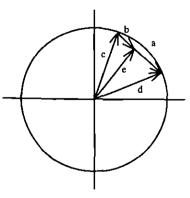

| Figure 3.11 | Kohonen Weight Changes                                   | 96  |

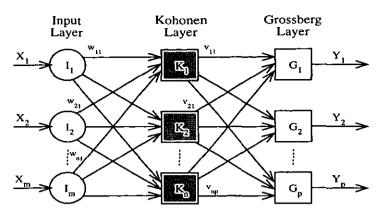

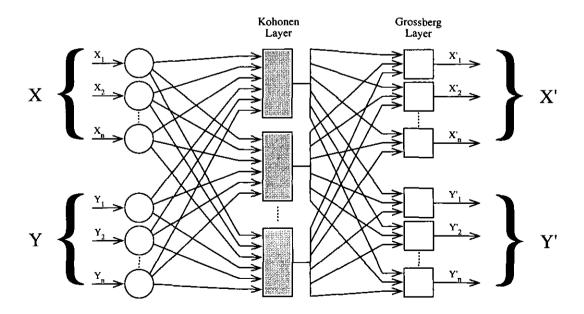

| Figure 3.12 | Counter Propagation Network                              | 99  |

| Figure 3.13 | Full Counter Propagation Network                         | 100 |

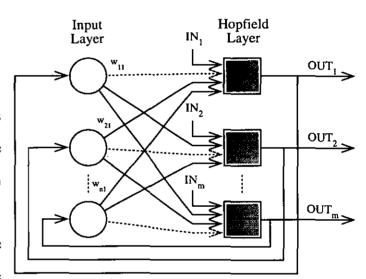

| Figure 3.14 | Single Layer Recurrent Network                           | 102 |

| Figure 3.15 | Hopfield Network State Space                             | 103 |

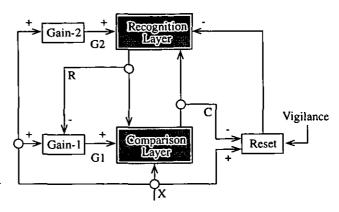

| Figure 3.16 | Simplified ART Architecture                              | 109 |

| Figure 4.1  | Feed Forward Mode                                        | 114 |

| Figure 4.2  | Feed Back Mode                                           | 114 |

| Figure 4.3  | Recall Timing Graph                                      | 115 |

| Figure 4.4  | Calculation Timing Graph                                 | 116 |

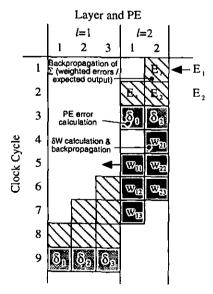

| Figure 4.5  | Update Timing Graph                                      | 117 |

| Figure 4.6  | Hardware Block Diagram for VLSI-Friendly ART-1 Algorithm | 121 |

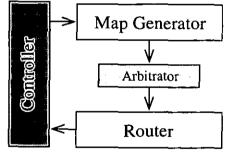

| Figure 4.7  | Network System Model                                     | 124 |

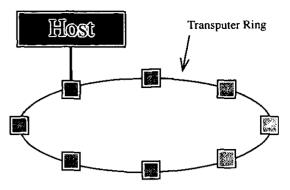

| Figure 4.8  | Transputer Ring Network                                   | 132 |

|-------------|-----------------------------------------------------------|-----|

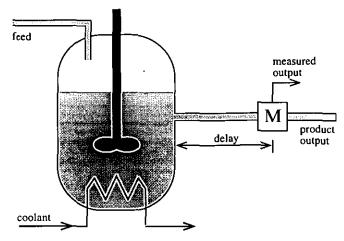

| Figure 4.9  | Continuous Stirred Tank Reactor                           | 133 |

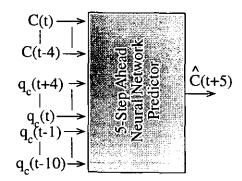

| Figure 4.10 | CSTR Plant Neural Predictor                               | 133 |

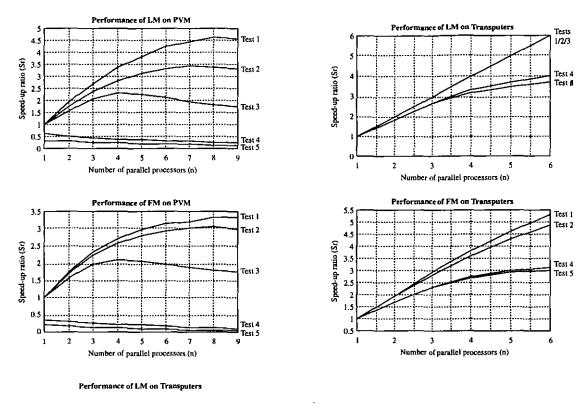

| Figure 4.11 | Algorithm Performance                                     | 135 |

| Figure 5.1  | Neural VLSI Array Architecture                            | 137 |

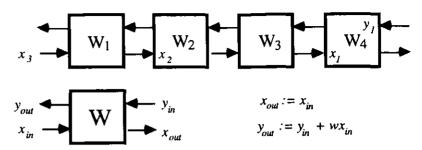

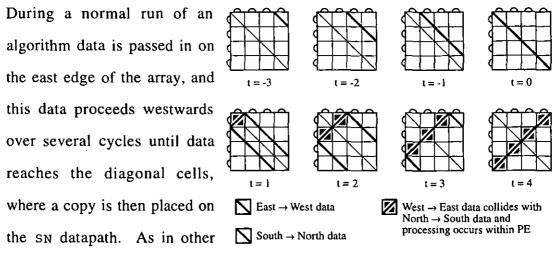

| Figure 5.2  | Back Substitution using Instruction Systolic Arrays       | 138 |

| Figure 5.3  | Internal Datapath Timings                                 | 140 |

| Figure 5.4  | Data Format                                               | 141 |

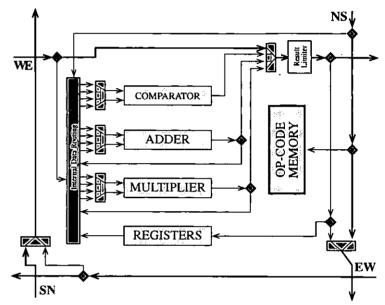

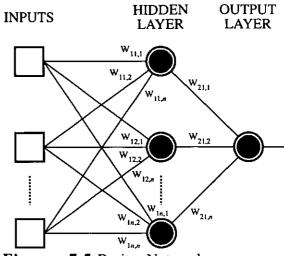

| Figure 5.5  | Processing Element Schematic                              | 143 |

| Figure 5.6  | Opcode ROM Bit-Slice                                      | 146 |

| Figure 5.7  | Sigmoidal Activation Function                             | 151 |

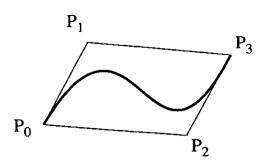

| Figure 5.8  | Bézier Curve Segment                                      | 156 |

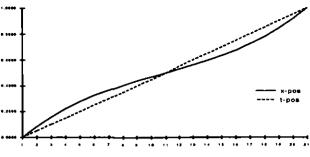

| Figure 5.9  | X-pos and t-pos Relationship                              | 158 |

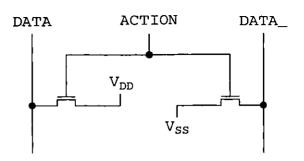

| Figure 5.10 | Multiplexor Schematics                                    | 159 |

| Figure 5.11 | ABS Unit Schematic                                        | 160 |

| Figure 5.12 | Majority Function Schematic                               | 160 |

| Figure 5.13 | Result Range Limiter Schematic                            | 161 |

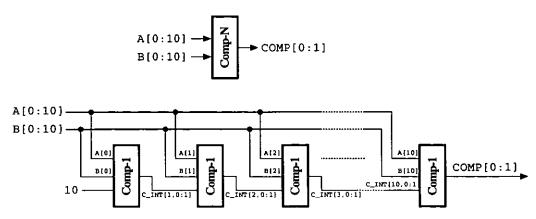

| Figure 5.14 | 1-Bit Comparator Schematic                                | 162 |

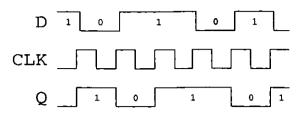

| Figure 5.15 | Flip-Flop Timing Diagram                                  | 164 |

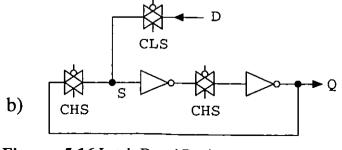

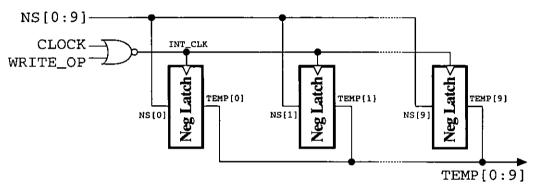

| Figure 5.16 | Latch-Based Register                                      | 164 |

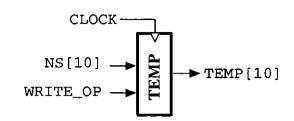

| Figure 5.17 | Instruction Set Store Schematic                           | 165 |

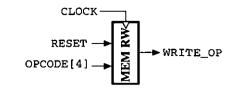

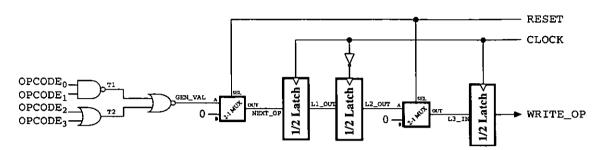

| Figure 5.18 | Read/Write Schematic                                      | 166 |

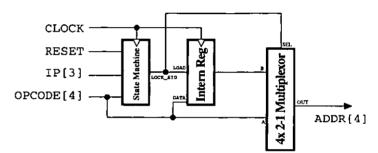

| Figure 5.19 | Opcode Lock Schematic                                     | 167 |

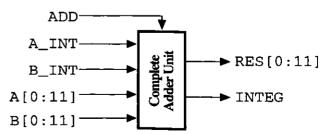

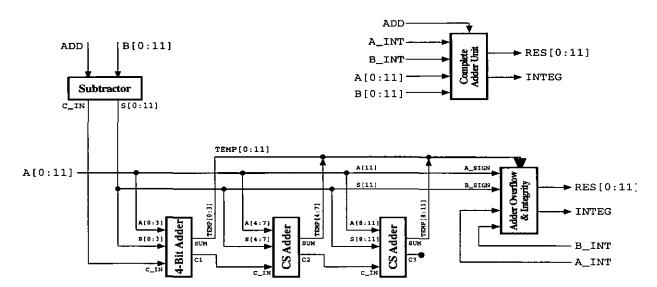

| Figure 5.20 | Complete Adder Unit Schematic                             | 167 |

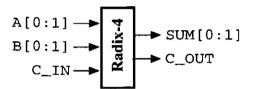

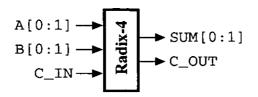

| Figure 5.21 | Radix-4 Adder Schematic                                   | 168 |

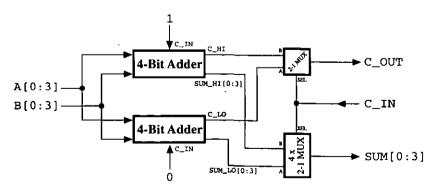

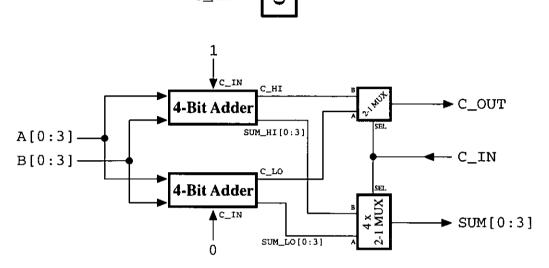

| Figure 5.22 | Carry Select Adder Block                                  | 168 |

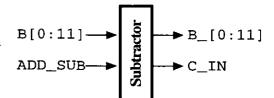

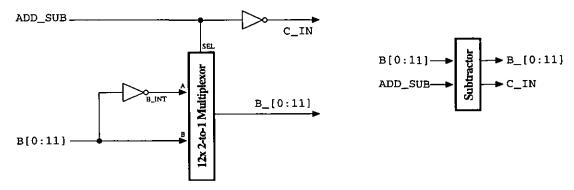

| Figure 5.23 | Subtraction Control Schematic                             | 169 |

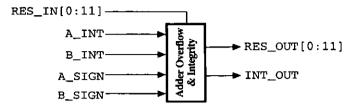

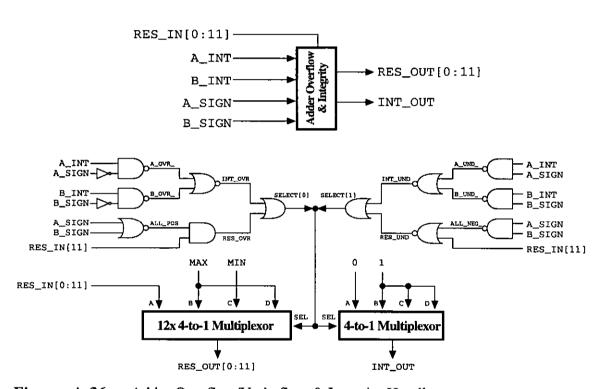

| Figure 5.24 | Adder Overflow Schematic                                  | 170 |

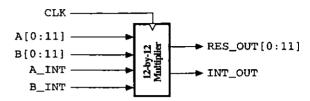

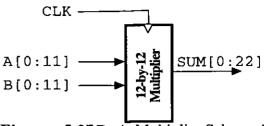

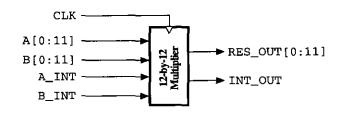

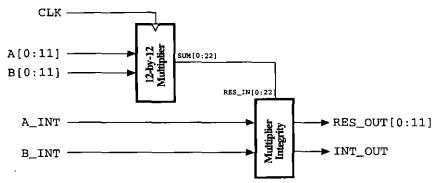

| Figure 5.25 | Complete Multiplier Unit Schematic                        | 171 |

| Figure 5.26 | Booth Multiplier Functional Overview                      | 171 |

| Figure 5.27 | Basic Multiplier Schematic                                | 172 |

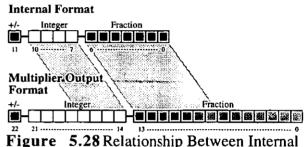

| Figure 5.28 | Relationship Between Internal and Multiplier Data Formats | 172 |

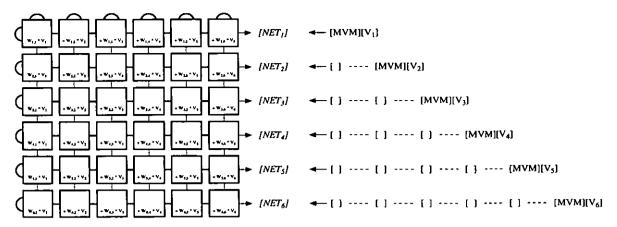

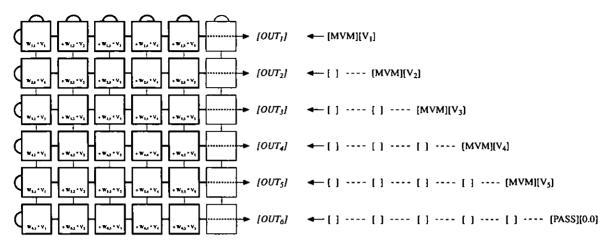

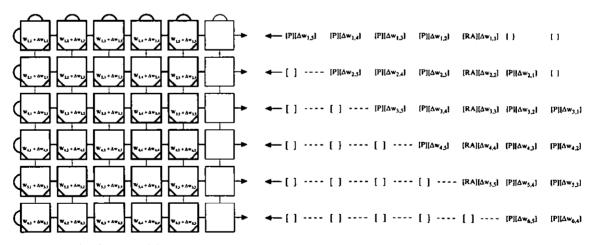

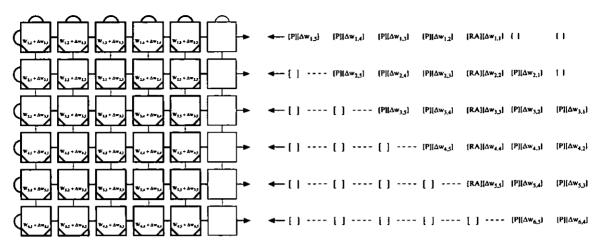

| Figure 6.1  | Algorithm for NET Value Calculation                       | 176 |

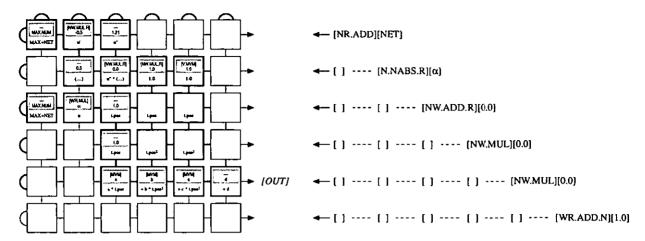

| Figure 6.2  | Algorithm for Bézier F(NET) Approximation                 | 178 |

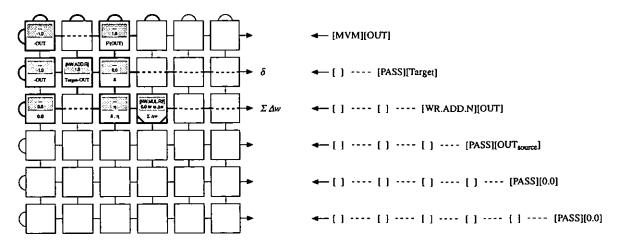

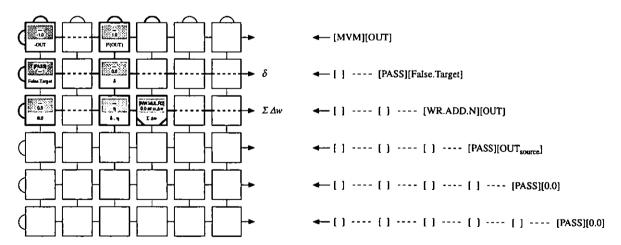

| Figure 6.3  | Algorithm for Output Layer Weight Adjustments             | 180 |

| Figure 6.4  | Connections for Hidden Layer Training                     | 180 |

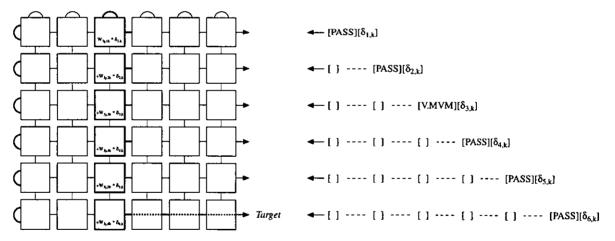

| Figure 6.5  | Algorithm for False Target Generation                  | 181 |

|-------------|--------------------------------------------------------|-----|

| Figure 6.6  | Algorithm for Hidden Layer Weight Adjustment           | 182 |

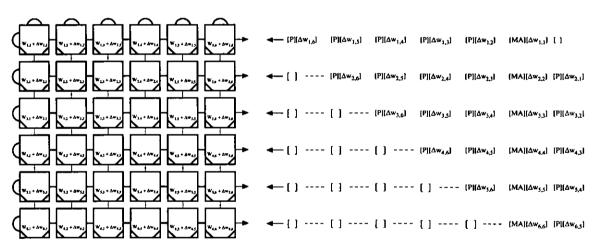

| Figure 6.7  | Algorithm for Weight Update                            | 183 |

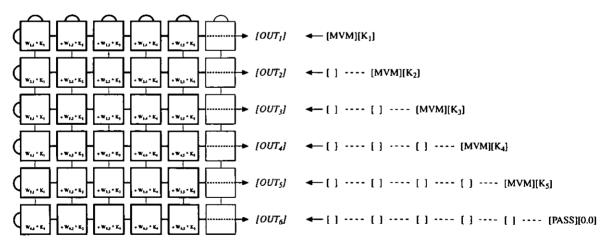

| Figure 6.8  | Algorithm for OUT Value Calculation                    | 189 |

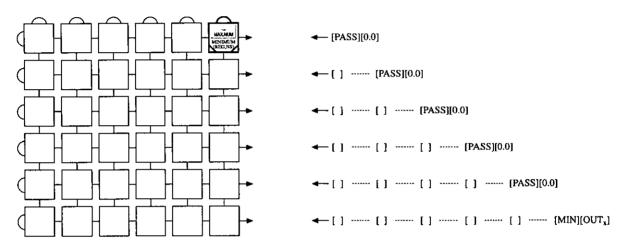

| Figure 6.9  | Algorithm for Minimum OUT Search                       | 190 |

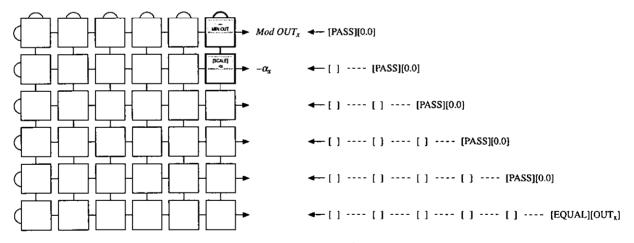

| Figure 6.10 | Algorithm for Modified OUT Generation                  | 190 |

| Figure 6.11 | Algorithm for Weight Adjustment Calculation            | 191 |

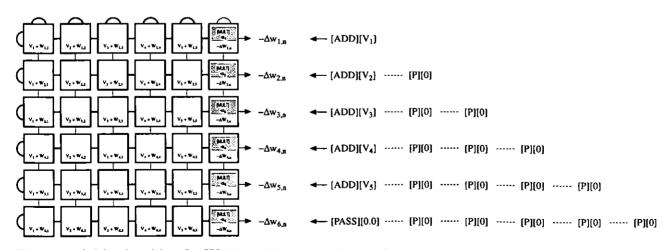

| Figure 6.12 | Algorithm for Weight Update                            | 192 |

| Figure 6.13 | Algorithm for OUT Value Calculation                    | 198 |

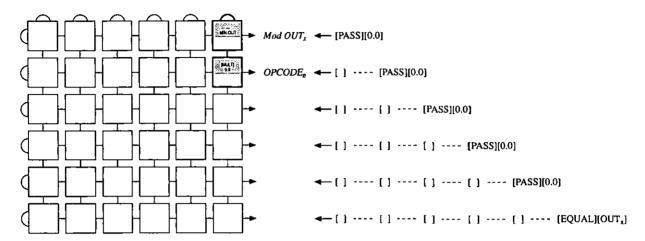

| Figure 6.14 | Modified Algorithm for Kohonen Modified OUT Generation | 200 |

| Figure 6.15 | Algorithm for Weight Adjustment Calculation            | 200 |

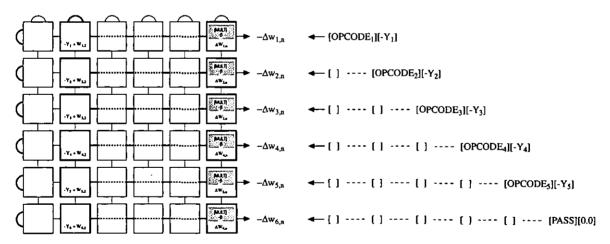

| Figure 6.16 | Algorithm for Weight Update                            | 201 |

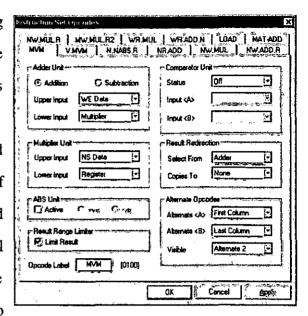

| Figure 7.1  | Opcode Definition Dialog                               | 208 |

| Figure 7.2  | Neural Parameter Definition Dialog                     | 209 |

| Figure 7.3  | Exclusive-Or Network                                   | 211 |

| Figure 7.4  | Exclusive-Or Training Run Progress                     | 212 |

| Figure 7.5  | Parity Network                                         | 213 |

| Figure 7.6  | Parity Training Run Progress (whole set)               | 214 |

| Figure 7.7  | Parity Training Run Progress (limited set)             | 215 |

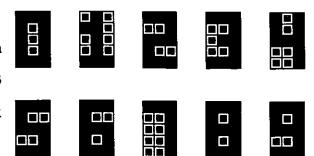

| Figure 7.8  | Pattern Recognition Training Set Images                | 215 |

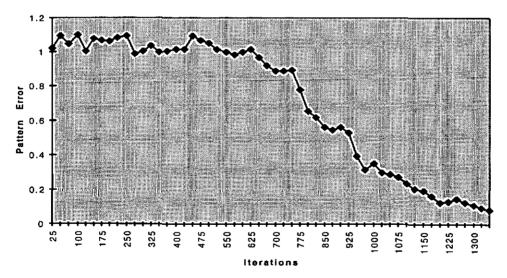

| Figure 7.9  | Pattern Recognition Training Run Progress              | 217 |

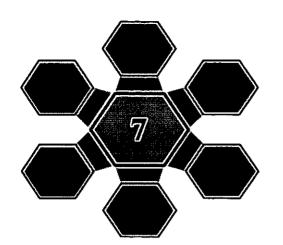

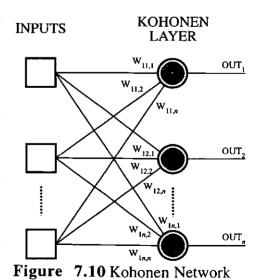

| Figure 7.10 | Kohonen Network                                        | 218 |

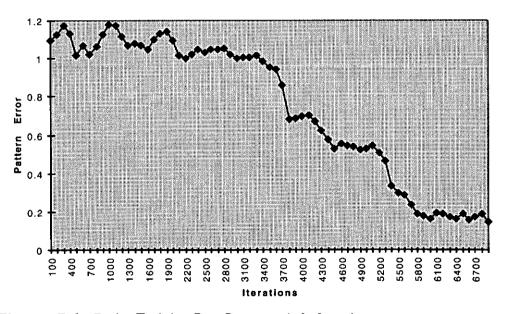

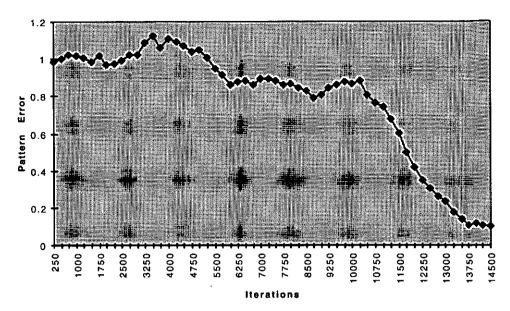

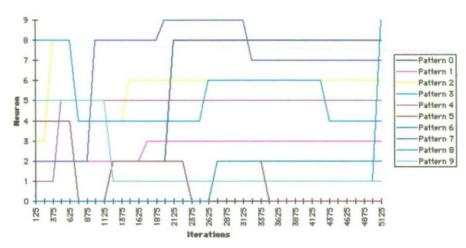

| Figure 7.11 | Kohonen Training Run Progress                          | 219 |

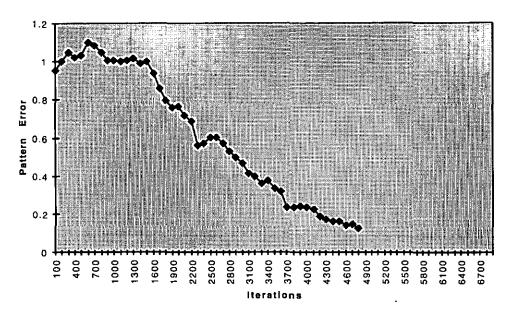

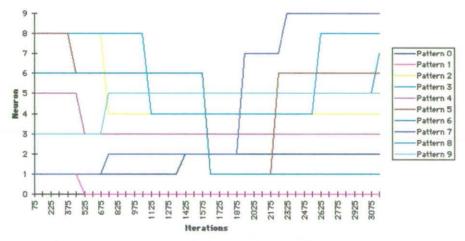

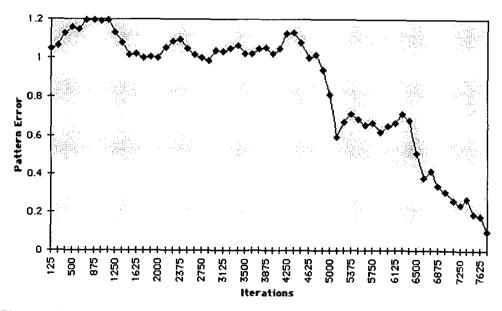

| Figure 7.12 | Counter Propagation Kohonen Layer Progress             | 222 |

| Figure 7.13 | Counter Propagation Grossberg Layer Progress           | 223 |

| Figure A.1  | 2-to-1 Multiplexor                                     | 234 |

| Figure A.2  | 4-to-1 Multiplexor                                     | 235 |

| Figure A.3  | D-Type Flip-Flop                                       | 236 |

| Figure A.4  | D-Type Flip-Flop with Instant Reset                    | 237 |

| Figure A.5  | Half Latch                                             | 238 |

| Figure A.6  | 3-Input Majority Function                              | 239 |

| Figure A.7  | Negative Edge Open Latch                               | 239 |

| Figure A.8  | PE Input Register                                      | 240 |

| Figure A.9  | PE Output Register                                     | 241 |

| Figure A.10 | Register Block Internal Register                       | 243 |

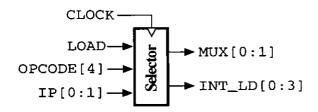

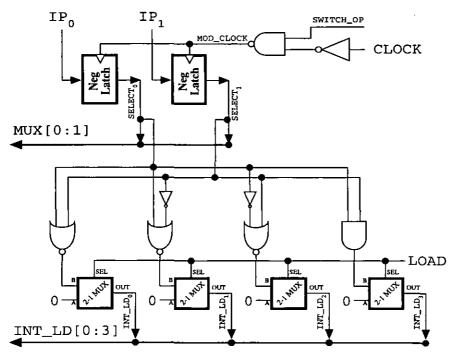

| Figure A.11 | Register Block 'Active' Selector                       | 245 |

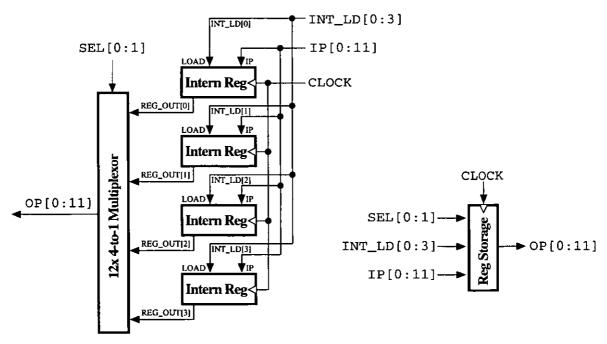

| Figure A.12 | Register Block Storage                       | 247 |

|-------------|----------------------------------------------|-----|

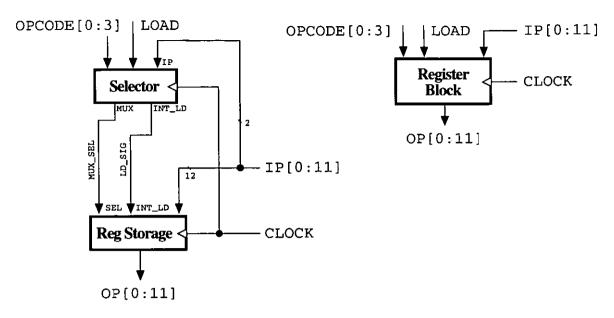

| Figure A.13 | Entire Internal Register Block               | 248 |

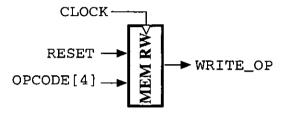

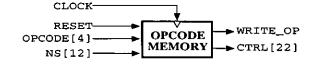

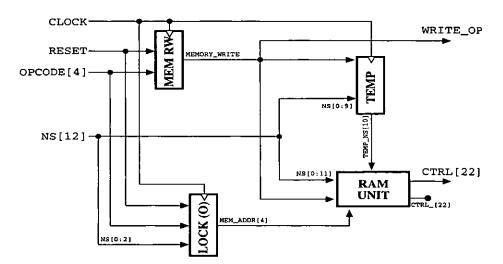

| Figure A.14 | Opcode Memory Read/Write Generator           | 250 |

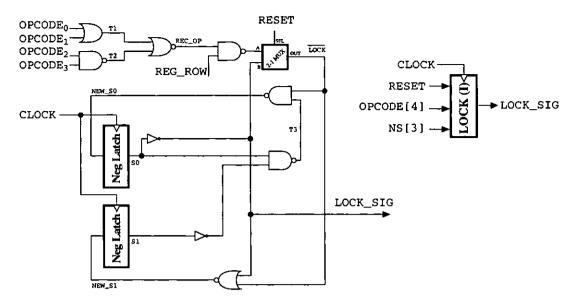

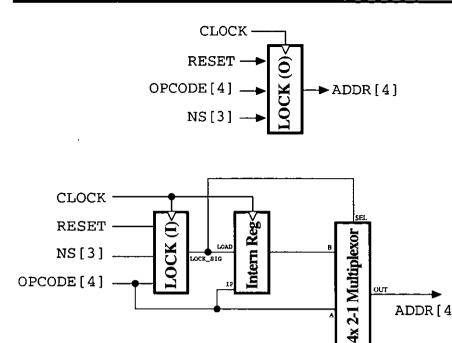

| Figure A.15 | Opcode Lock Inner Block                      | 251 |

| Figure A.16 | Opcode Lock Outer Block                      | 253 |

| Figure A.17 | Control Signal Temporary Storage             | 254 |

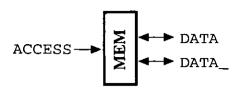

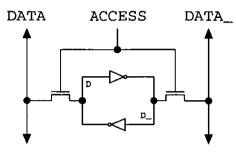

| Figure A.18 | Base Memory Cell                             | 255 |

| Figure A.19 | Constant Memory Cell                         | 256 |

| Figure A.20 | Memory Address Decoder                       | 258 |

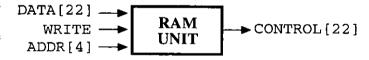

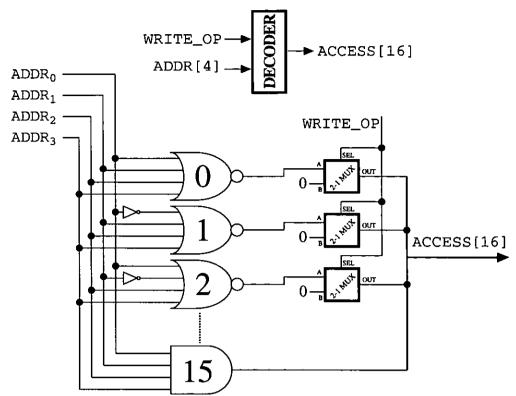

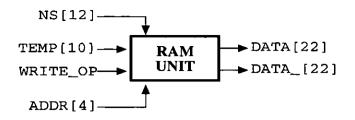

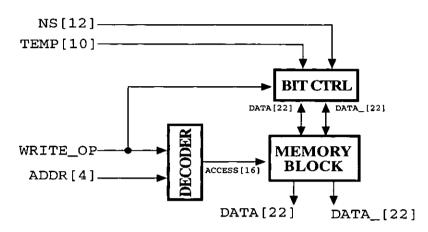

| Figure A.21 | RAM Unit Bit Control Logic                   | 260 |

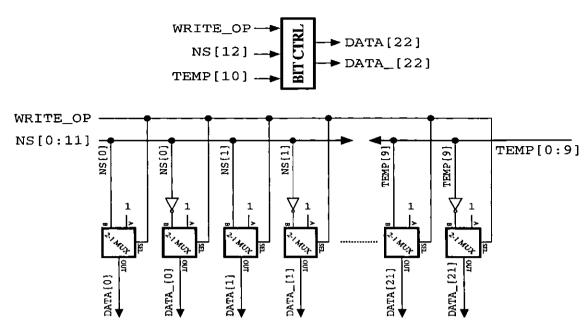

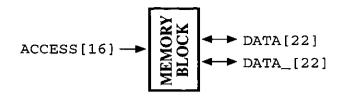

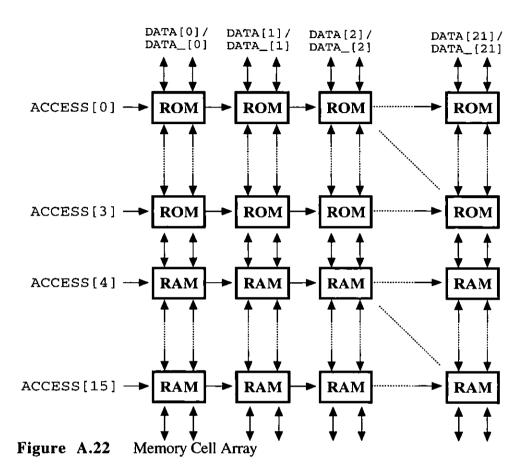

| Figure A.22 | Memory Cell Array                            | 261 |

| Figure A.23 | Enitre RAM Unit                              | 263 |

| Figure A.24 | Complete Instruction Set Memory              | 264 |

| Figure A.25 | ABS Unit                                     | 266 |

| Figure A.26 | Range Limit Data Stores                      | 267 |

| Figure A.27 | 1-Bit Comparator                             | 268 |

| Figure A.28 | N-Bit Comparator                             | 270 |

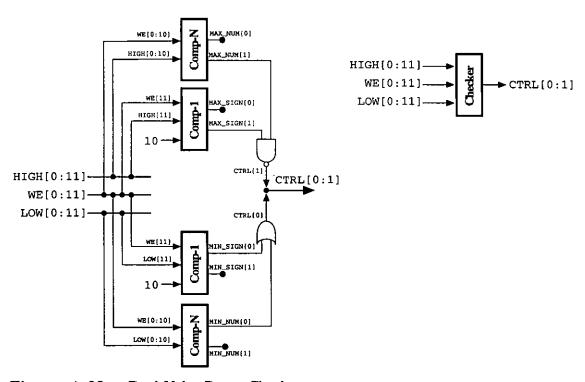

| Figure A.29 | Dual-Value Range Checker                     | 270 |

| Figure A.30 | Complete Result Range Checker Unit           | 273 |

| Figure A.31 | General Purpose Comparator Unit              | 274 |

| Figure A.32 | Radix-4 Adder                                | 276 |

| Figure A.33 | 4-Bit Basic Adder Block                      | 277 |

| Figure A.34 | Carry-Select Adder 4-Bit Block               | 279 |

| Figure A.35 | Subtraction Control Unit                     | 280 |

| Figure A.36 | Adder Overflow/Underflow & Integrity Handler | 281 |

| Figure A.37 | Complete Adder Unit                          | 283 |

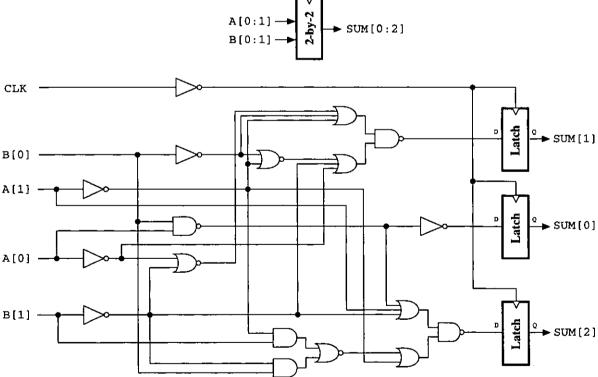

| Figure A.38 | 2x2 Optimised Booth Multiplier               | 286 |

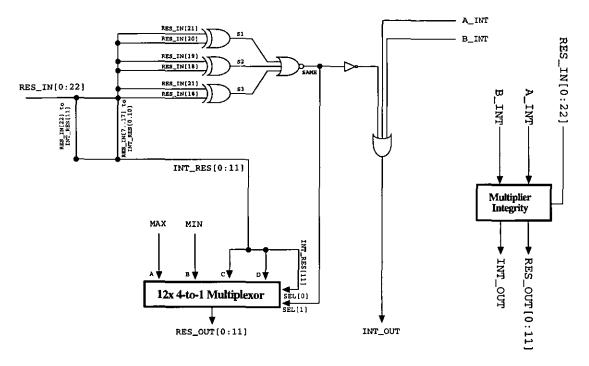

| Figure A.39 | Multiplier Integrity Checker                 | 287 |

| Figure A.40 | Complete 12x12 Parallel Multiplier           | 289 |

|             |                                              |     |

|             |                                              |     |

| LIST O      | F TABLES                                     |     |

| Table 1.1   | IC Complexity                                | 10  |

| Table 1.2   | Influence of first-order MOS scaling         | 14  |

| Table 1.3   | Scaling of interconnect media                | 15  |

| Table 1.4   | Feng's Computer System Classifications       | 21  |

|             |                                              |     |

| Linearly Separable Functions                  | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G1 Calculation                                | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Annealing Simulation Results                  | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dimensions of Test Problems                   | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Instructions fixed in ROM                     | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Possible Mathematical Operations              | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Comparator Data                               | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ABS Unit Logic                                | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Result Destinations                           | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Summary of instruction-based control signals  | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instruction Combinations                      | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Iterative Reciprocal Calculation Errors       | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Initial Bézier Control Points                 | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Final Bézier Control Points                   | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Multiplexor Control                           | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ABS Unit Control                              | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Majority Function Control                     | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Range Limiter Multiplexor Control             | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Comparator Input Control Values               | 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C_OUT Transfer Function                       | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Comparison Example                            | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instruction Set Store Operations              | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Possible PE Lock States                       | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Overflow Possibilities                        | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Backpropagation Instruction Set               | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bézier Approximation Constants                | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bézier Approximation Workings                 | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Backpropagation Example Neural Network Setups | 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6x6 Array Timing (using non-optimal network)  | 185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6x6 Array Timing (using optimal network)      | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 24x24 Array Timing                            | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Final Backpropagation Timings                 | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Kohonen Instruction Set                       | 187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Kohonen Example Neural Network Setups         | 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6x6 Array Timing (small network)              | 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               | G1 Calculation  Annealing Simulation Results Dimensions of Test Problems  Instructions fixed in ROM Possible Mathematical Operations Comparator Data ABS Unit Logic Result Destinations Summary of instruction-based control signals Instruction Combinations Iterative Reciprocal Calculation Errors Initial Bézier Control Points Final Bézier Control Points Multiplexor Control ABS Unit Control Majority Function Control Range Limiter Multiplexor Control Comparator Input Control Values C_OUT Transfer Function Comparison Example Instruction Set Store Operations Possible PE Lock States Overflow Possibilities  Backpropagation Instruction Set Bézier Approximation Workings Backpropagation Example Neural Network Setups 6x6 Array Timing (using non-optimal network) 6x6 Array Timing (using optimal network) 24x24 Array Timing Final Backpropagation Timings Kohonen Instruction Set Kohonen Example Neural Network Setups |

| Table 6.12 | 6x6 Array Timing (large network)                        | 194 |

|------------|---------------------------------------------------------|-----|

| Table 6.13 | 12x12 Array Timing (small network)                      | 195 |

| Table 6.14 | 12x12 Array Timing (large network)                      | 195 |

| Table 6.15 | Final Kohonen Timings                                   | 196 |

| Table 6.16 | Counter Propagation Instruction Set                     | 197 |

| Table 6.17 | 6x6 Array Timing (small network)                        | 202 |

| Table 6.18 | 6x6 Array Timing (large network)                        | 202 |

| Table 6.19 | 12x12 Array Timing (small network)                      | 203 |

| Table 6.20 | 12x12 Array Timing (small network)                      | 203 |

| Table 6.21 | Final Grossberg Timings                                 | 203 |

| Table 6.22 | Counter Propagation Single Pattern Timings              | 205 |

| Table 6.23 | Counter Propagation Batch Pattern Timings               | 205 |

| Table 7.1  | Exclusive-Or Training Set                               | 211 |

| Table 7.2  | Exclusive-Or Training Parameters                        |     |

| Table 7.3  | Parity Training Parameters                              |     |

| Table 7.4  | Pattern Recognition Training Set Targets                |     |

| Table 7.5  | Pattern Recognition Training Parameters                 | 216 |

| Table 7.6  | Kohonen Training Parameters                             |     |

| Table 7.7  | Counter Propagation Network Structure                   |     |

| Table 7.8  | Counter Propagation Kohonen Layer Training Parameters   |     |

| Table 7.0  | Counter Propagation Groscherg Layer Training Parameters | 222 |

# INTRODUCTION

#### 1.1 Introduction

Modern electronic systems, especially sensor and imaging systems, are beginning to incorporate their own neural network sub-systems. One of the major advantages of neural networks is that they have the capacity to extract the essential characteristics of input data, which may well contain much irrelevant data [Wass89]. This, coupled with their ability to generalize from previous examples to new ones, makes their use in real-time image-processing and sensor applications very attractive. However, the response times of such applications necessitate that the neural systems be implemented in hardware rather than software, and in order to maximize their performance application-specific integrated circuits (ASIC) would have to be designed rather than use standard general-purpose components [MeCo80].

In many existing hardware neural network systems [Nayl94] [KuHw89] [Hamm91] the processing elements (PE) within an ASIC perform the majority of the neural processing, with each PE being mapped on to a physical neuron in the network. With a large network there can be a tremendous number of communication channels, due to the number of connection combinations, and managing such channels can take up a large proportion of the available processing time. This can make the hardware implementation of neural networks either rather slow or limited in scope, with the former being especially true if the ASIC is to be 'general purpose' and allow conceivably any inter-neuron connection strategy.

Chapter 1 Introduction

There is little work [Lehm93] which focuses on using the synapses within a neuron as the main PE's of a hardware system; such systems compute partial results on each of the synapses and combine them all on a parallel pipeline. This is a perfect example as to the benefits of using systolic array structures: they can utilize the inherent parallelism present in neural networks for very few overheads and, thus, solve the communication problem through the extensive use of concurrency [KungHT82].

Very large scale integration (VLSI) allows for many millions of transistors per IC. Although such large devices can be expensive to fabricate they actually make array processors financially viable, as the single IC could hold a large number of individual PE's. A systems architect can then re-cast basic algorithms into a form more suitable for processing, as well as partitioning the algorithm in new ways in order to reduce the amount of working memory required on-chip. This allows for a single IC to have high performance even though it consists of multiple instances of cheap low performance units - there can often be an advantage in using inexpensive technology in seeking high performance.

Algorithms in many areas are well understood and are not expected to be improved upon in the near future; e.g. the fields of mathematical floating-point division and data sorting. However, the systems architect may be limited in computational units and may have to implement algorithms in a non-standard fashion. For instance, if the VLSI device has only fixed-point adders and multipliers how can complex expressions such as  $x = \ln(n+1)^2$  be calculated? The architect is forced to re-engineer such expressions, devising equivalent functions based upon the mathematical units available. These equivalent functions will be optimised for the parallel architecture that has been designed and will often be faster and more efficiently than the original expression would have been on a more mathematically-capable serial processor.

The work to devise a VLSI architecture suitable for real-time learning of neural networks can be seen to be into three distinct areas; parallel architecture design, parallel algorithm design and

Chapter 1 Introduction

mathematical approximation of functions. All areas need to be worked upon with efficiency in mind, as if one stage is inefficient then any gains from the other stages will be lost.

This introductory chapter begins with a brief overview of the evolution of computing machines, followed by the descriptions of the advances made in IC technology. The chapter concludes with a survey of parallel computer architectures and an outline of the structure of the thesis. This introductory chapter, therefore, sets the technological background from which the work presented in the remainder of the thesis was based upon.

## 1.2 Evolution of Computing Machines

#### 1.2.1 What is a 'Computer'?

There are two fairly standard definitions of the term 'computer' [OUP90]:

- 1. a usually electronic device for storing and processing data (usually in binary form), according to instructions given to it in a variable program

- 2. a person who computes or makes calculations

The latter definition has fallen out of use since the 1950's, when the former definition became the only one of everyday importance. Until this time the latter definition was a common term, especially within military circles, for people who could perform complex calculations with or without the use of mechanical aids.

The definition given for a computer being a data processing machine makes no preconceptions about the type of machine, nor does it attempt to qualify the type of data that it deals with - the computer could be electronic or mechanical by design, although mechanical computers have been made redundant through technological advances in electronics throughout this century. Computers tend to be either analogue or digital in nature - the latter operates on continuous data values whilst the former uses discrete data values.

Analogue computers can measure precisely the values of physical quantities, such as current and temperature, which makes their use in simulator equipment desirable. Digital computers cannot cope with exact numbers, save where only integer values are required, but their increased speed over their analogue counterparts makes up for their deficiency in accuracy. This lack of accuracy in digital computers has become a moot point, however, as they are accurate to approximately  $\pm 1/2^{n-1}$ , with  $n \ge 64$  becoming commonplace [IEEE85].

Hybrid computers have recently been developed, which incorporate both analogue and digital components, in an attempt to make a computer both speedy and exact in it's calculations. An example of such a VLSI device is discussed further in section 4.1.2.

#### 1.2.2 Historical Development of Computers

#### 1.2.2.1 The Early Years