# Fault Management via Dynamic Reconfiguration for Integrated Modular Avionics

by

Peter David Hubbard

A Doctoral Thesis submitted in partial fulfilment of the requirements

for the award of Doctor of Philosophy of

Loughborough University

May 2015

© by Peter David Hubbard 2015

### i. Abstract

The purpose of this research is to investigate fault management methodologies within Integrated Modular Avionics (IMA) systems, and develop techniques by which the use of dynamic reconfiguration can be implemented to restore higher levels of systems redundancy in the event of a systems fault.

A proposed concept of dynamic configuration has been implemented on a test facility that allows controlled injection of common faults to a representative IMA system. This facility allows not only the observation of the response of the system management activities to manage the fault, but also analysis of real time data across the network to ensure distributed control activities is maintained.

IMS technologies have evolved as a feasible direction for the next generation of avionic systems. Although federated systems are logical to design, certify and implement, they have some inherent limitations that are not cost beneficial to the customer over long lifecycles of complex systems, and hence the fundamental modular design, i.e. common processors running modular software functions, provides a flexibility in terms of configuration, implementation and upgradability that cannot be matched by well-established federated avionic system architectures. For example, rapid advances of computing technology means that dedicated hardware can become outmoded by component obsolescence which almost inevitably makes replacements unavailable during normal life-cycles of most avionic systems. To replace the obsolete part with a newer design involves a costly re-design and re-certification of any relevant or interacting functions with this unit. As such, aircraft are often known to go through expensive mid-life updates to upgrade all avionics systems. In contrast, a higher frequency of small capability upgrades would maximise the product performance, including cost of development and procurement, in constantly changing platform deployment environments.

IMA is by no means a new concept and work has been carried out globally in order to mature the capability. There are even examples where this technology has been

implemented as subsystems on service aircraft. However, IMA flexible configuration properties are yet to be exploited to their full extent; it is feasible that identification of faults or failures within the system would lead to the exploitation of these properties in order to dynamically reconfigure and maintain high levels of redundancy in the event of component failure. It is also conceivable to install redundant components such that an IMS can go through a process of graceful degradation, whereby the system accommodates a number of active failures, but can still maintain appropriate levels of reliability and service. This property extends the average maintenance-free operating period, ensuring that the platform has considerably less unscheduled down time and therefore increased availability.

The content of this research work involved a number of key activities in order to investigate the feasibility of the issues outlined above. The first was the creation of a representative IMA system and the development of a systems management capability that performs the required configuration controls. The second aspect was the development of hardware test rig in order to facilitate a tangible demonstration of the IMA capability.

A representative IMA was created using LabVIEW Embedded Tool Suit (ETS) real time operating system for minimal PC systems. Although this required further code written to perform IMS middleware functions and does not match up to the stringent air safety requirements, it provided a suitable test bed to demonstrate systems management capabilities.

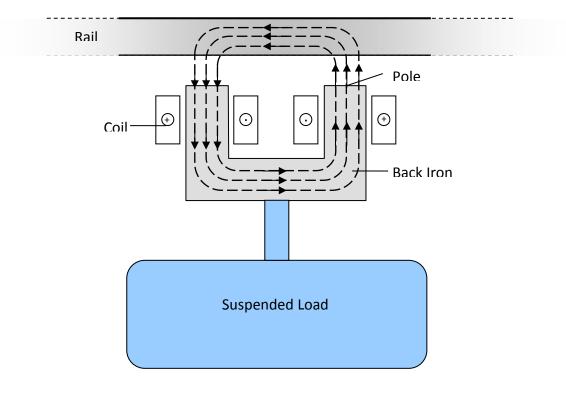

The overall IMA was demonstrated with a 100kg scale 'Maglev' vehicle as a test subject. This platform provides a challenging real-time control problem, analogous to an aircraft flight control system, requiring the calculation of parallel control loops at a high sampling rate in order to maintain magnetic suspension. Although the dynamic properties of the test rig are not as complex as a modern aircraft, it has much less stringent operating requirements and therefore substantially less risk associated with failure to provide service.

The main research contributions for the PhD are:

- A solution for the dynamic reconfiguration problem for assigning required systems functions (namely a distributed, real-time control function with redundant processing channels) to available computing resources whilst protecting the functional concurrency and time critical needs of the control actions.

- A systems management strategy that utilises the dynamic reconfiguration properties of an IMA to restore high levels of redundancy in the presence of failures.

- A Demonstration of the operation of points 1 & 2 on a representative system, showing that dynamic configuration can occur whilst the service provision (i.e. realtime control action) is maintained.

The conclusion summarises the level of success of the implemented system in terms of an appropriate dynamic reconfiguration to the response of a fault signal. In addition, it highlights the issues with using an IMA to as a solution to operational goals of the target hardware, in terms of design and build complexity, overhead and resources.

For those who say 'about time', this is for you:

But most of all, for my Wife and Daughter.

### i. Acknowledgements

I would like to thank both EPSRC and BAE Systems for funding this research activity. I also extend my thanks to my industrial supervisor, Matt Mapleston, and to my Academic supervisors Roger Goodall and Roger Dixon for supporting me through to the bitter end. Their support has gone above and beyond the expectations of supervisors and I hope I do your efforts service. Thanks also to my examiners for taking the time to read and critique this work in order to scientifically validate the findings.

Thanks to the support from my friends and family, both to those that 'got it' and to those that still don't really understand! I thank you all the same and I'm glad you are there. I'd like to thank my Wife, Ella, who has been through this with me from the start and offered her support throughout (with varying amounts of patience!), and I'm also going to thank my daughter, Elsie, even though she's just turned up.

And finally, thanks to Rekha Patel, for providing a solution that no one else knew.

Pete.

## iii. Contents

| i.   | Abs  | stract      |                                         | ii  |

|------|------|-------------|-----------------------------------------|-----|

| ii.  | Ack  | now         | ledgements                              | v   |

| iii. | Cor  | ntent       | S                                       | vii |

| iv.  | List | of Fi       | gures                                   | xii |

| ٧.   | List | of Ta       | ables                                   | xv  |

| 1.   | Inti | roduc       | ction                                   | 1   |

| 1    | .1.  | Back        | ground                                  | 2   |

| 1    | .2.  | Prob        | lem Statement                           | 3   |

| 1    | .3.  | Cont        | ributions                               | 4   |

| 1    | .4.  | Obje        | ctives                                  | 5   |

| 1    | .5.  | Publi       | ications                                | 5   |

| 1    | .6.  | Thes        | is Overview                             | 6   |

| 2.   | Lite | eratu       | re Review                               | 7   |

| 2    | .1.  | The D       | Developing Need for Improved Avionics   | 9   |

|      | 2.1. | 1.          | Digital Revolution in Aircraft Systems  | 9   |

|      | 2.1. | 2.          | The Development of Avionics Integration | 10  |

|      | 2.1. | 3.          | Future Needs for Avionics Systems       | 14  |

|      | 2.1. | <b>4.</b> . | Summary of Future Avionic Requirements  | 18  |

| 2    | .2.  | Integ       | rated Modular System Concepts           | 19  |

|      | 2.2. | 1.          | Introduction to IMS                     | 19  |

|      | 2.   | 2.1.1.      | Modular Hardware/Software Integration   | 20  |

|      | 2.   | 2.1.2.      | Why Use IMS?                            | 24  |

|      | 2.2. | 2.          | IMS Research Areas                      | 26  |

|      | 2.   | 2.2.1.      | Standards                               | 26  |

|      | 2.   | 2.2.2.      | System Design and Certification         | 30  |

|      | 2    | 223         | Hardware                                | 33  |

|                                                  | 2.2.2.4.                                                                           | Partitioning                                                                                                                                                                                                                                | 35               |

|--------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                                  | 2.2.2.5.                                                                           | Configuration                                                                                                                                                                                                                               | 37               |

|                                                  | 2.2.2.6.                                                                           | Reconfiguration                                                                                                                                                                                                                             | 38               |

|                                                  | 2.2.2.7.                                                                           | Network Requirements                                                                                                                                                                                                                        | 41               |

| •                                                | 2.2.2.8.                                                                           | Distributed Control                                                                                                                                                                                                                         | 42               |

| 2                                                | 2.3. F                                                                             | ault Management in IMS                                                                                                                                                                                                                      | 45               |

|                                                  | 2.2.3.1.                                                                           | Fault Avoidance and Removal                                                                                                                                                                                                                 | 48               |

|                                                  | 2.2.3.2.                                                                           | Fault Tolerance                                                                                                                                                                                                                             | 50               |

| •                                                | 2.2.3.3.                                                                           | Fault Treatment                                                                                                                                                                                                                             | 57               |

| 2.3.                                             | Examp                                                                              | oles of IMS implementation                                                                                                                                                                                                                  | 58               |

| 2                                                | 3.1.                                                                               | Genesis IMA                                                                                                                                                                                                                                 | 58               |

| 2                                                | 3.2. N                                                                             | Modular Avionics Operating System (MAOS)                                                                                                                                                                                                    | 60               |

| 2.4.                                             | Literat                                                                            | ure Review Summary                                                                                                                                                                                                                          | 61               |

|                                                  |                                                                                    |                                                                                                                                                                                                                                             |                  |

| 3 IV                                             | 11 Dan                                                                             | a anatystay Custom Daguiyanaants                                                                                                                                                                                                            | 64               |

| J. 111                                           | ia Deli                                                                            | nonstrator System Requirements                                                                                                                                                                                                              | 04               |

| 3.1.                                             |                                                                                    | duction                                                                                                                                                                                                                                     |                  |

|                                                  | Intro                                                                              | •                                                                                                                                                                                                                                           | 65               |

| 3.1.                                             | Introd<br>Top L                                                                    | duction                                                                                                                                                                                                                                     | 65               |

| <ul><li>3.1.</li><li>3.2.</li><li>3.3.</li></ul> | Introd<br>Top L<br>IMA                                                             | ductionevel System                                                                                                                                                                                                                          | 65<br>65         |

| 3.1.<br>3.2.<br>3.3.                             | Introd Top L IMA                                                                   | evel System                                                                                                                                                                                                                                 | 65<br>65<br>68   |

| 3.1.<br>3.2.<br>3.3.<br>3                        | Introd Top L IMA                                                                   | ductionevel System                                                                                                                                                                                                                          | 65656871         |

| 3.1.<br>3.2.<br>3.3.<br>3                        | Introd<br>Top L<br>IMA<br>3.1. /.                                                  | ductionevel System                                                                                                                                                                                                                          | 65657172         |

| 3.1.<br>3.2.<br>3.3.<br>3                        | Introd<br>Top L<br>IMA<br>3.1. //<br>3.2. //<br>3.3.2.1.                           | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources                                                                                                                   | 6565717274       |

| 3.1.<br>3.2.<br>3.3.<br>3                        | Introd Top L IMA 3.1. II 3.2. II 3.3.2.1. 3.3.2.2. 3.3.2.3.                        | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources  Configuration Management                                                                                         | 656571727475     |

| 3.1.<br>3.2.<br>3.3.<br>3                        | Introd Top L IMA 3.1. II 3.2. II 3.3.2.1. 3.3.2.2. 3.3.2.2.                        | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources  Configuration Management  Fault Management                                                                       | 656571727475     |

| 3.1.<br>3.2.<br>3.3.<br>3<br>3                   | Introd Top L IMA 3.1. I. 3.2. I. 3.3.2.1. 3.3.2.2. 3.3.2.3. 3.3.2.4.               | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources  Configuration Management  Fault Management  Communications Management                                            | 65657172757678   |

| 3.1.<br>3.2.<br>3.3.<br>3<br>3                   | Introd Top L IMA 3.1. I. 3.2. I. 3.3.2.1. 3.3.2.2. 3.3.2.3. 3.3.2.4. 3.3.2.4.      | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources  Configuration Management  Fault Management  Communications Management                                            | 65657172757678   |

| 3.1.<br>3.2.<br>3.3.<br>3<br>3                   | Introd Top L IMA 3.1. I. 3.2. I. 3.3.2.1. 3.3.2.2. 3.3.2.3. 3.3.2.4. 3.3. I. Magle | duction  evel System                                                                                                                                                                                                                        | 6565717275767879 |

| 3.1.<br>3.2.<br>3.3.<br>3<br>3<br>3              | Introd Top L IMA 3.1. I. 3.2. I. 3.3.2.1. 3.3.2.2. 3.3.2.3. 3.3.2.4. 3.3. I. Magle | duction  evel System  MA Hardware  MA Middleware/Operating System  Management of Application Access to Hardware Resources  Configuration Management  Fault Management  Communications Management  MA Applications  Graphical User Interface | 6565717275767879 |

| 4.1. Top  | o Level Design                                                        | 86  |

|-----------|-----------------------------------------------------------------------|-----|

| 4.2. Sys  | tems Management                                                       | 88  |

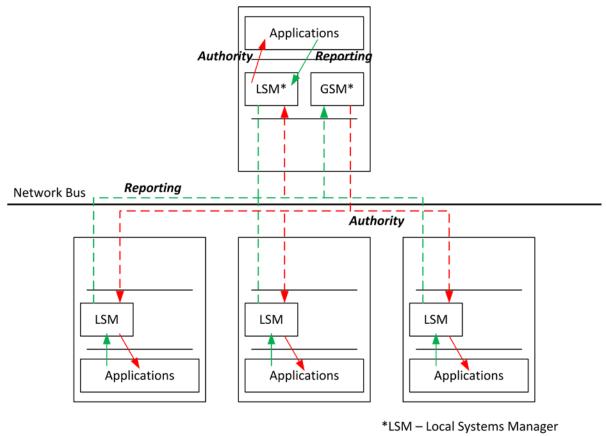

| 4.2.1.    | Systems Management Reporting Structure                                | 88  |

| 4.2.2.    | Timing and Synchronisation                                            | 90  |

| 4.2.3.    | Redundancy in Systems Management                                      | 91  |

| 4.3. Ap   | plication Design                                                      | 93  |

| 4.3.1.    | Application specification example                                     | 95  |

| 4.4. Co   | nfiguration/Re-configuration                                          | 96  |

| 4.4.1.    | Configuration Example                                                 | 99  |

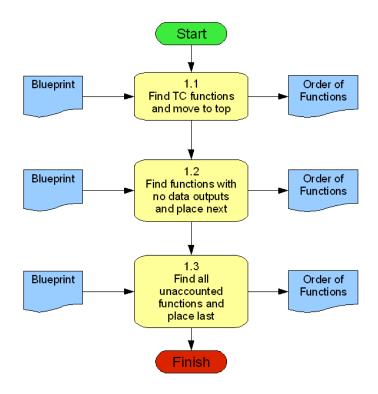

| 4.4.1.    | 1. Process 1: Order Functions by Criticality (and Identify Resources) | 101 |

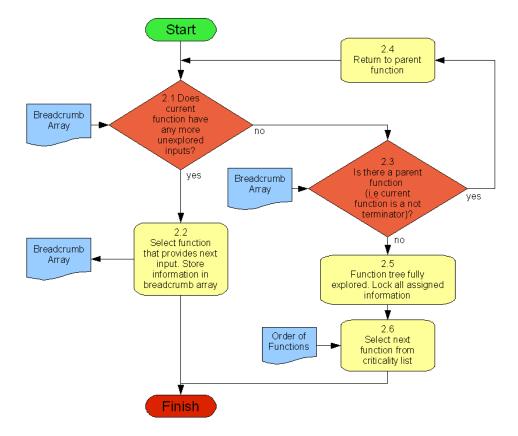

| 4.4.1.    | 2. Process 2: Select Next Function                                    | 103 |

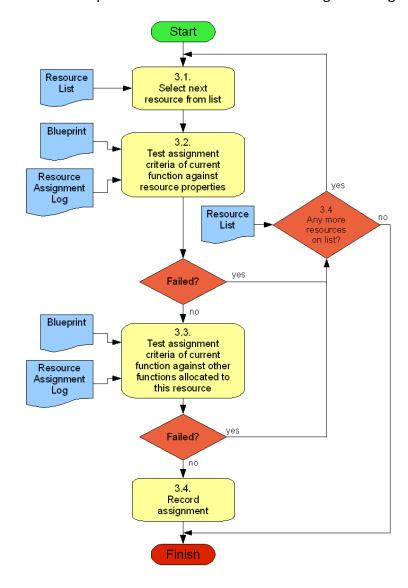

| 4.4.1.    | 3. Process 3: Placing Function on Resources                           | 104 |

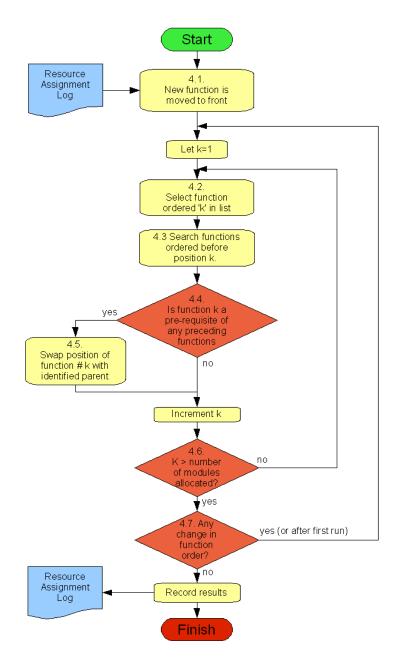

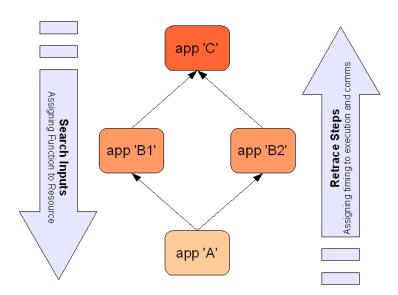

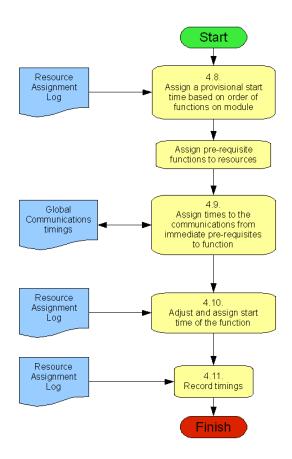

| 4.4.1.    | 4. Process 4: Schedule of Application Execution and Communications    | 105 |

| 4.4.1.    | 5. Process 5: Record all Details in Blueprint                         | 110 |

| 4.4.2.    | Start Up Procedures                                                   | 110 |

| 4.4.3.    | Using this Algorithm for Reconfiguration                              | 111 |

| 4.4.4.    | Configuration Summary                                                 | 113 |

| 4.5. Syr  | nchronisation and Communications                                      | 114 |

| 4.5.1.    | Synchronisation of Modules                                            | 115 |

| 4.5.2.    | Synchronisation of Applications                                       | 116 |

| 4.5.3.    | Synchronisation of Communications                                     | 116 |

| 4.5.3.    | 1. Collision Avoidance                                                | 117 |

| 4.5.3.    | 2. Managing Time Critical and Non-Time Critical Data                  | 118 |

| 4.6. Err  | or Recovery                                                           | 119 |

| 4.6.1.    | Processing module failure                                             | 120 |

| 4.6.2.    | Application Failure                                                   | 121 |

| 4.6.3.    | Summary                                                               | 121 |

| 5. Config | uration and Real-Time Robustness Testing                              | 123 |

|           | lidation of the Configuration Algorithm                               |     |

|           | Sinale Sensor. Sinale Process and Sinale Actuator                     |     |

| 5.1.2.                                     | Single Sensor, Duplex Processing, Single Actuator          | 128                      |

|--------------------------------------------|------------------------------------------------------------|--------------------------|

| 5.1.3.                                     | Single Sensor, Triplex Processing, Single Actuator         | 130                      |

| 5.1.4.                                     | Dual Sensors, Triplex Processing, Dual Actuator            | 132                      |

| 5.1.5.                                     | Dual I/O, Triplex processing and parallel function         | 134                      |

| 5.1.6.                                     | Summary                                                    | 137                      |

| 5.2. IN                                    | 1S as a Distributed Real Time System                       | 138                      |

| 5.2.1.                                     | Real time attributes testing                               | 138                      |

| 5.2.1                                      | .1. Communication time: 3 ms                               | 141                      |

| 5.2.1                                      | .2. Communication time: 2 ms                               | 143                      |

| 5.2.1                                      | .3. Communication time: 1 ms                               | 145                      |

| 5.2.1                                      | .4. Summary                                                | 147                      |

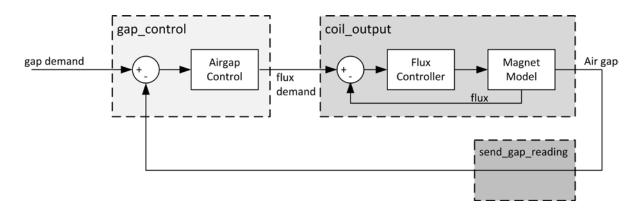

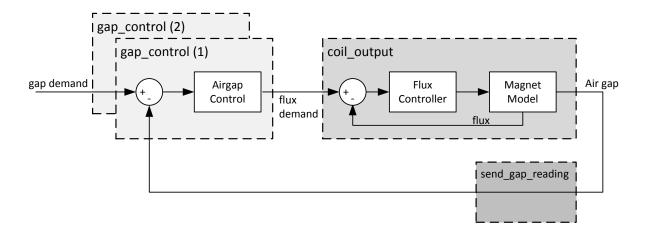

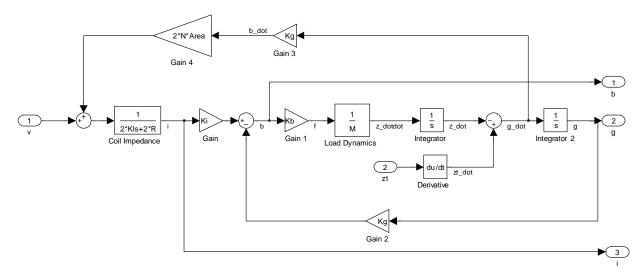

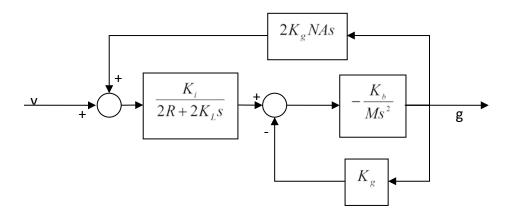

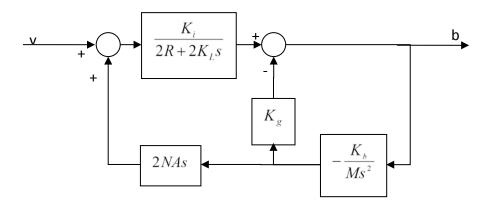

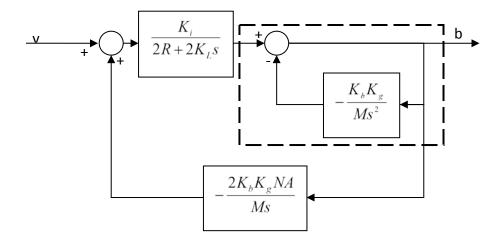

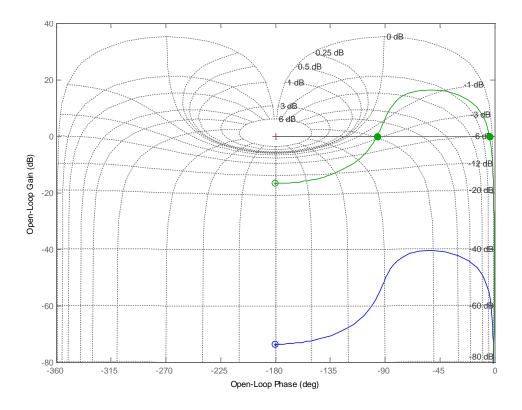

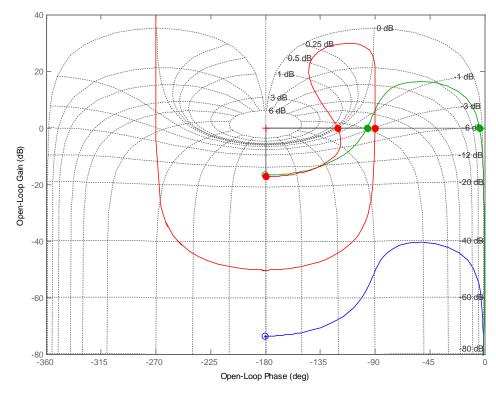

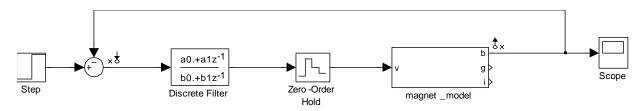

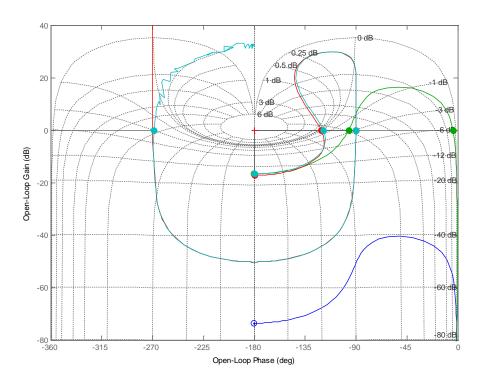

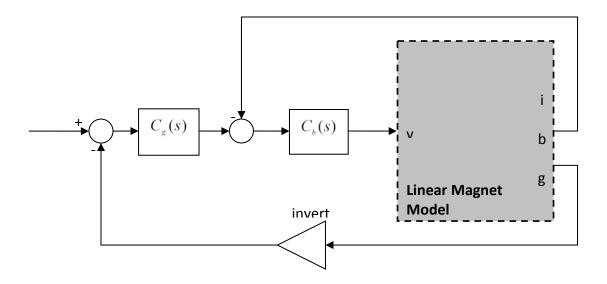

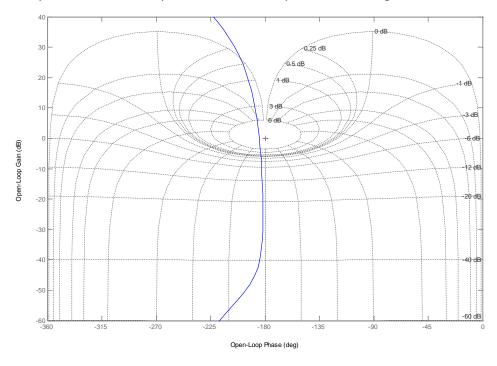

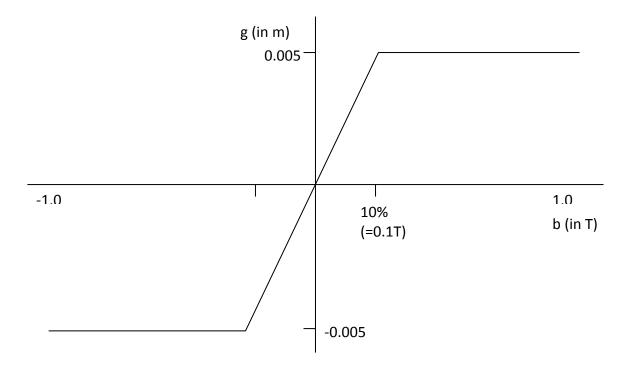

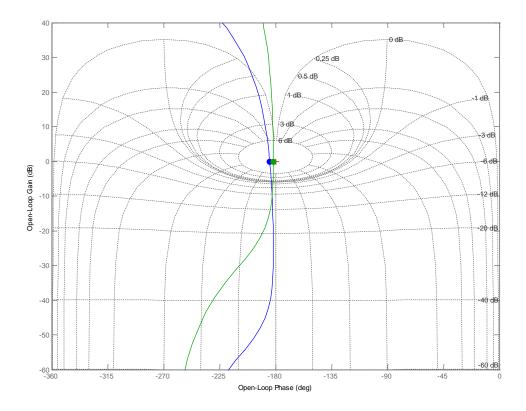

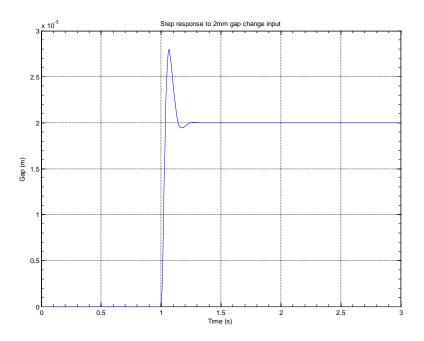

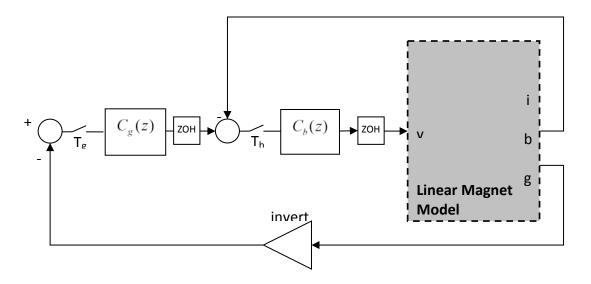

| 5.2.2.                                     | Air Gap control                                            | 149                      |

| 5.2.2                                      | .1. Application Design                                     | 149                      |

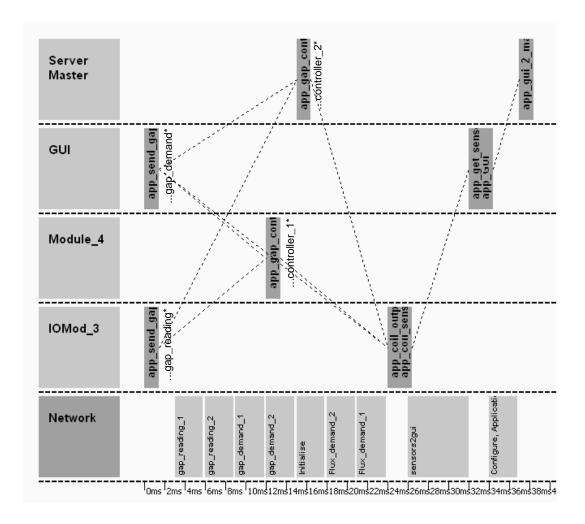

| 5.2.2                                      | .2. IMA Implementation of Distributed Gap Control          | 151                      |

| 5.2.2                                      | .3. Results of Gap Control Implementation                  | 151                      |

| 5.2.2                                      | .4. Distributed Gap Control Summary                        | 152                      |

| C Fault                                    |                                                            | 454                      |

|                                            | Management within IMA                                      |                          |

|                                            | seline System Initial Configuration                        |                          |

| _                                          | stem Response to a Single Fault                            |                          |

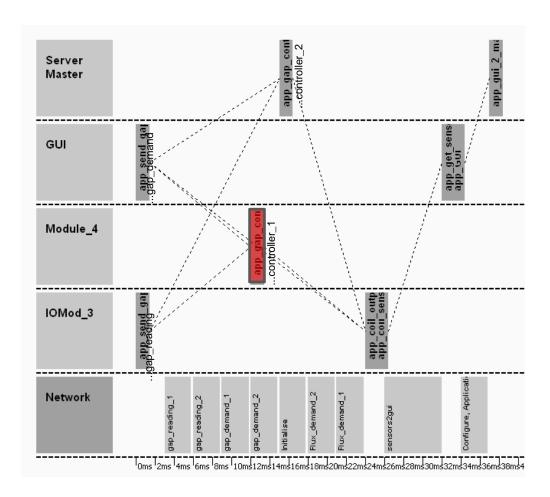

| 6.2.1.                                     | Simulation of an Application Failure                       | 161                      |

| 621                                        |                                                            |                          |

| 0.2.1                                      | .1. Fault Injection                                        |                          |

| 6.2.1                                      | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163                      |

|                                            | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163<br>165               |

| 6.2.1                                      | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163<br>165<br>166        |

| 6.2.1<br>6.2.1                             | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163<br>165<br>166        |

| 6.2.1<br>6.2.1<br>6.2.2.                   | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163<br>165<br>166<br>168 |

| 6.2.1<br>6.2.2.<br>6.2.2<br>6.2.2<br>6.2.2 | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163165166168             |

| 6.2.1<br>6.2.2.<br>6.2.2<br>6.2.2<br>6.2.2 | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163165166168             |

| 6.2.1<br>6.2.2.<br>6.2.2<br>6.2.2<br>6.2.2 | .2. Reconfiguration to Restore Higher Levels of Redundancy | 163165166168170          |

|      | 6.3.3 | 3.   | Fault 3 of 3: Application Failure of gap_controller_1    | 175    |

|------|-------|------|----------------------------------------------------------|--------|

|      | 6.3.4 | 4.   | Evaluation of Series of Failures                         | 176    |

| 6    | .4.   | Sum  | mary                                                     | 177    |

|      |       |      |                                                          |        |

| 7.   | Con   | clus | ion                                                      | 179    |

| 7    | .1.   | Asse | essment of Objectives                                    | 180    |

| 7    | .2.   | Asse | essment of Contributions                                 | 185    |

| 7    | .3.   | Futu | re Work and Recommendations                              | 188    |

|      | 7.3.2 | 1.   | Identified Areas of Good Practice for Reconfigurable IMA | 188    |

|      | 7.3.2 | 2.   | Certification                                            | 189    |

|      | 7.3.3 | 3.   | Quantification of Potential Savings                      | 189    |

|      | 7.3.4 | 4.   | Controller Lag Approximations                            | 190    |

|      | 7.3.5 | 5.   | Configuration Optimisation                               | 190    |

|      |       |      |                                                          |        |

| ٧.   | Ref   | eren | ces                                                      | xvi    |

| vi.  | App   | end  | ix A: Maglev Controller Development                      | xxiii  |

| vii. | Арр   | end  | ix B: Requirements Compliance                            | lxxxvi |

| viii | .Арр  | end  | ix C: Magnetic Levitation Experimental Rig               | xcii   |

| ix.  | App   | end  | ix D: Psuedo Code of Configuration Algorithm             | civ    |

# iv. List of Figures

| Figure 2-1 Research Topics                                                          | 8     |

|-------------------------------------------------------------------------------------|-------|

| Figure 2-2 Historical Analysis of Moore's Law                                       | 10    |

| Figure 2-3 ARINC 429 Example                                                        | 12    |

| Figure 2-4 Multiplex databus system architecture (Moir & Seabridge, 2008)           | 13    |

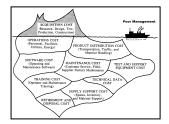

| Figure 2-5 Aircraft System Lifecycle Cost (Mapleston, 2006b)                        | 15    |

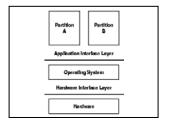

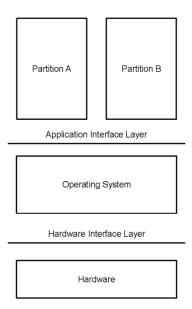

| Figure 2-6 'Three Layer Stack' Model                                                | 21    |

| Figure 2-7 Possible IMA architecture based on ARINC 651 architecture C (Joh         | nson, |

| Omiecinski 1998)                                                                    | 28    |

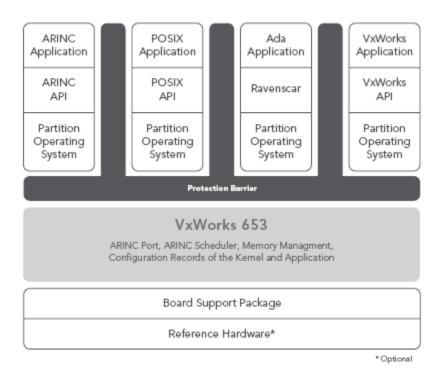

| Figure 2-8 ARINC 653 System Architecture (Prisaznuk, 2008)                          | 29    |

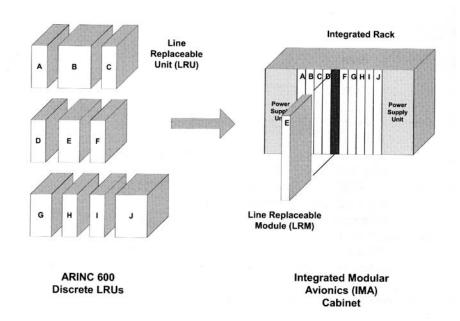

| Figure 2-9 Integrated Modular Cabinet Comparison (Moir et al., 2006)                | 33    |

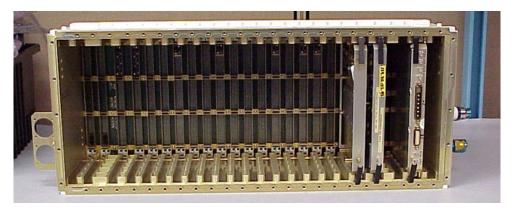

| Figure 2-10 High Density Packaging/Avionics Rack Example (Sutterfield et al., 2008) | 34    |

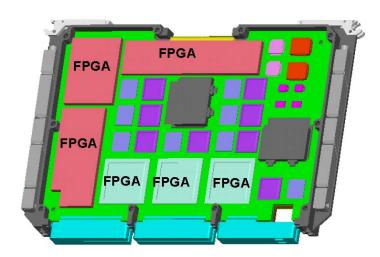

| Figure 2-11 FPGA Standard Module for Processing (Sutterfield et al., 2008)          | 34    |

| Figure 2-12 Partitioning Scheme for a Core module (Parkinson 2006)                  | 35    |

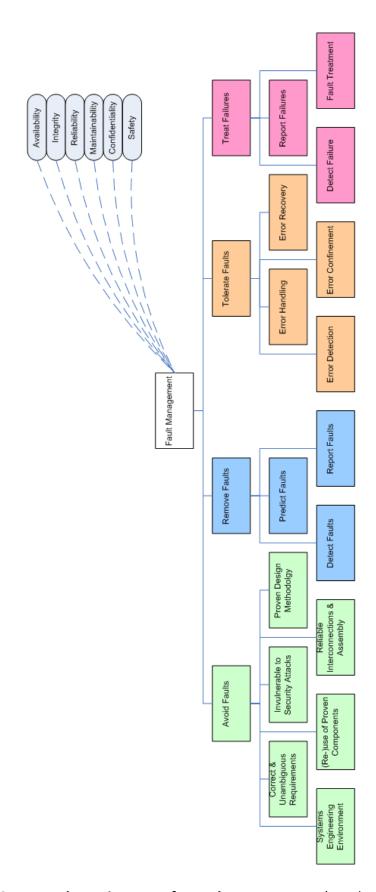

| Figure 2-13 Structured Requirements for Fault Management (Mapleston, 2006a)         | 46    |

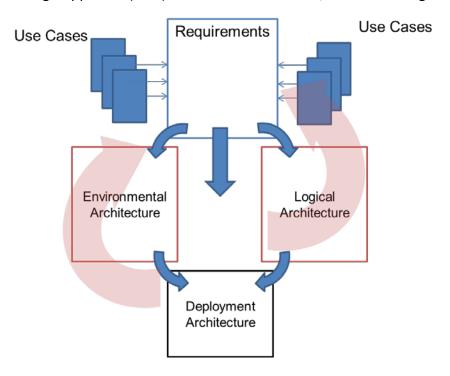

| Figure 2-14 Architectural Design Approach (Mapleston, 2006a)                        | 48    |

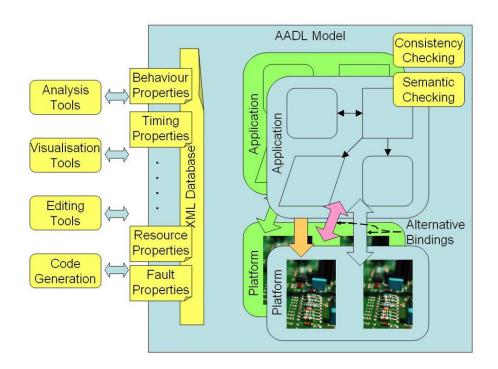

| Figure 2-15 AADL Overview (Mapleston, 2006b)                                        | 49    |

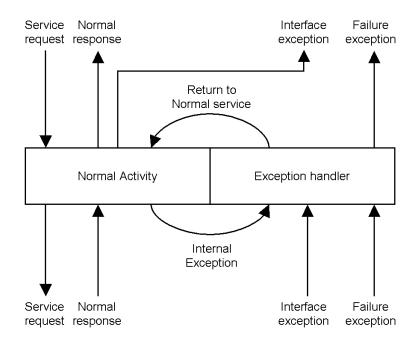

| Figure 2-16 Ideal Fault Tolerant Component (Burns & Wellings, 2001)                 | 52    |

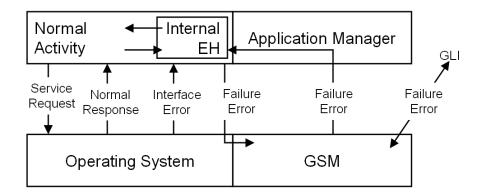

| Figure 2-17 IMS Environment Error Handling (Mapleston, 2006a)                       | 53    |

| Figure 2-18 IMS Internal Error Handling (Mapleston, 2006a)                          | 53    |

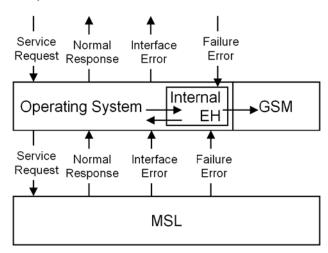

| Figure 2-19 Atomic Actions Examples (Mapleston, 2006b)                              | 54    |

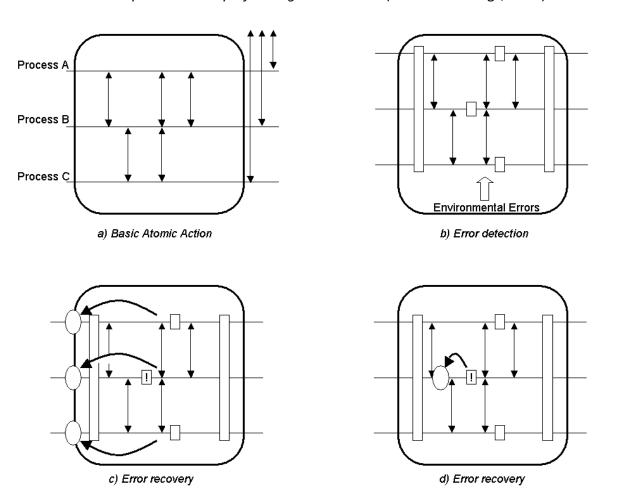

| Figure 2-20 Implementing Replication in IMS (Mapleston, 2006a)                      | 56    |

| Figure 2-21 Future Fault Treatment Model (Mapleston, 2006a)                         | 57    |

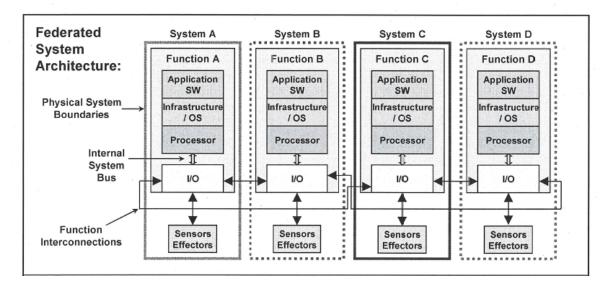

| Figure 2-22 Federated Systems Architecture (Watkins, 2006)                          | 59    |

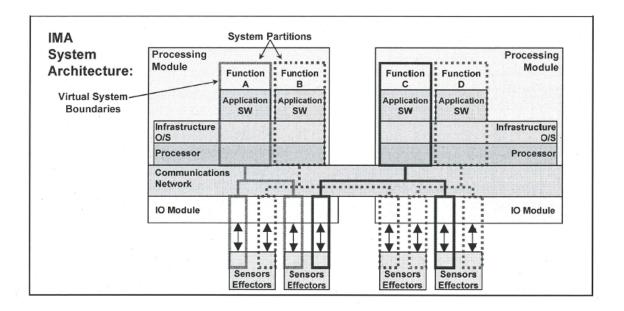

| Figure 2-23 IMA System Architecture (Watkins, 2006)                                 | 59    |

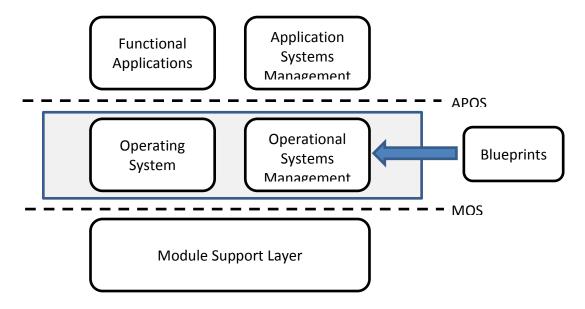

| Figure 2-24 IMA Software Model (Grigg et al., 1999)                                 | 60    |

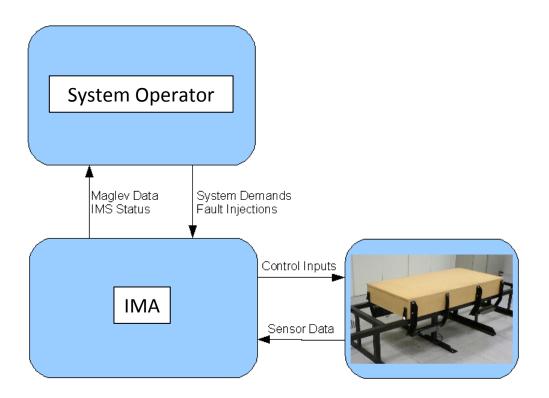

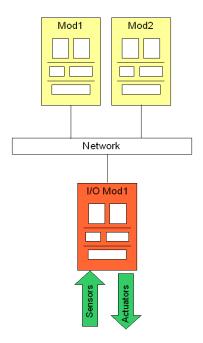

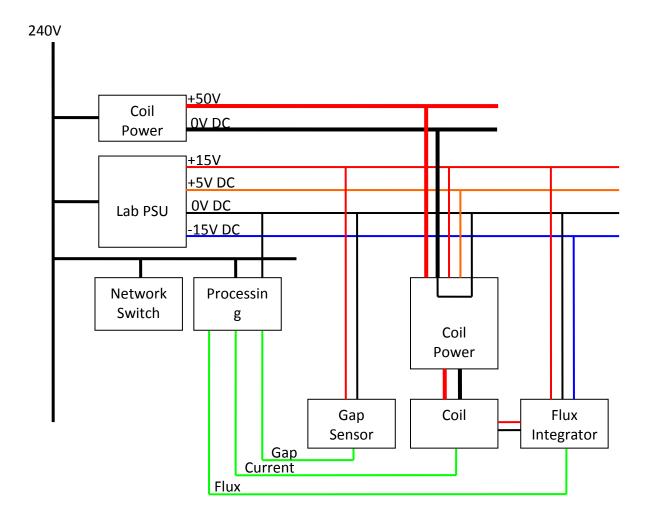

| Figure 3-1 Top Level Systems Diagram                                                | 66    |

| Figure 3-2 Three Layer Stack                                                        | 68    |

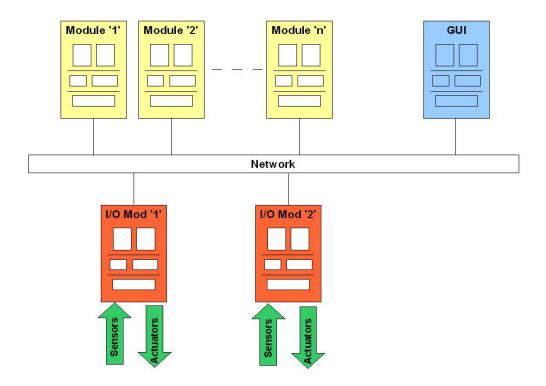

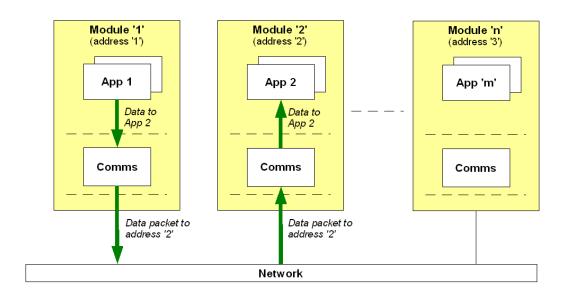

| Figure 3-3 IMA Module Integration                                                   | 70    |

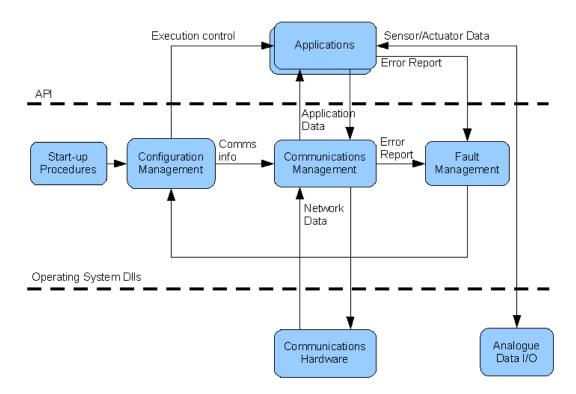

| Figure 3-4 IMA Middleware Architecture                                              | 72    |

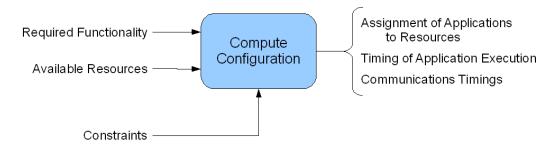

| Figure 3-5 Configuration Manager                                                        | 75      |

|-----------------------------------------------------------------------------------------|---------|

| Figure 3-6 Application Data Exchange Example                                            | 78      |

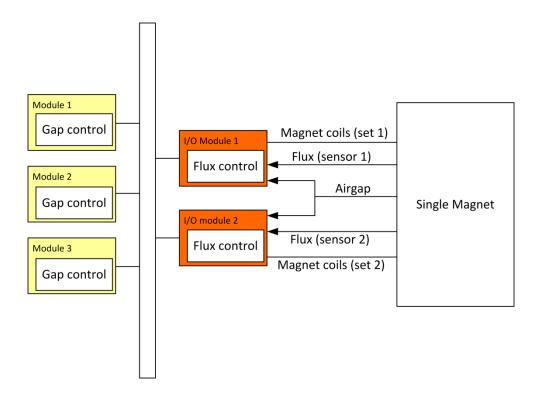

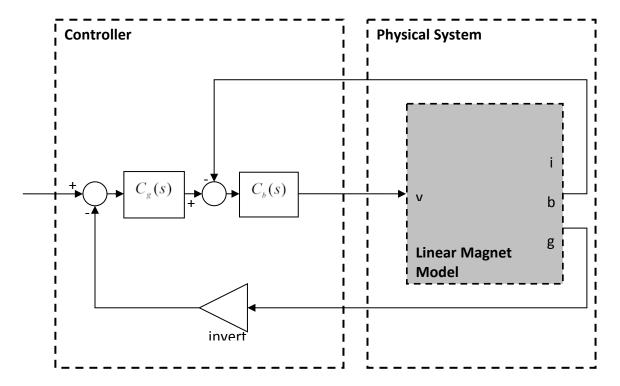

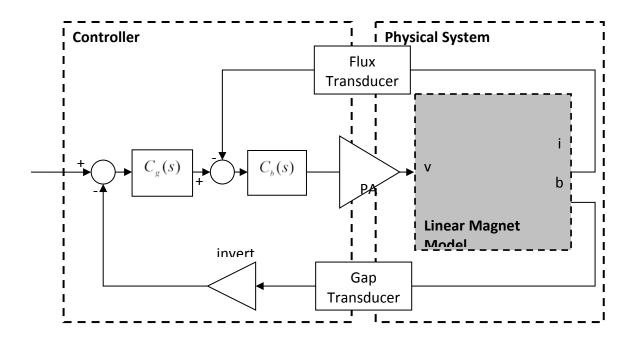

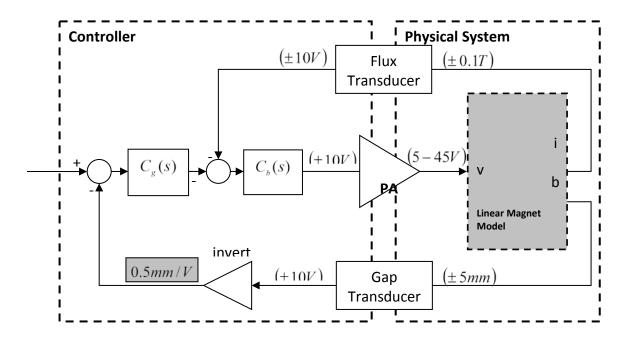

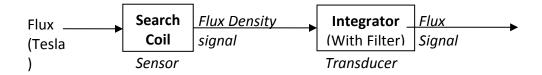

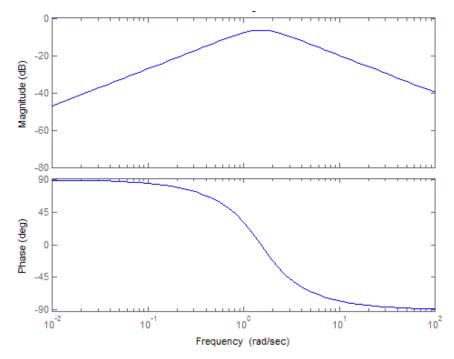

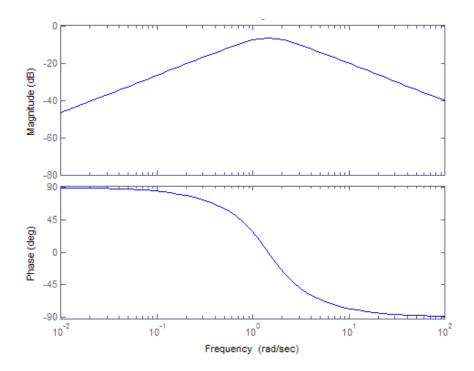

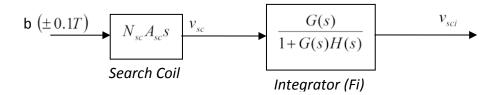

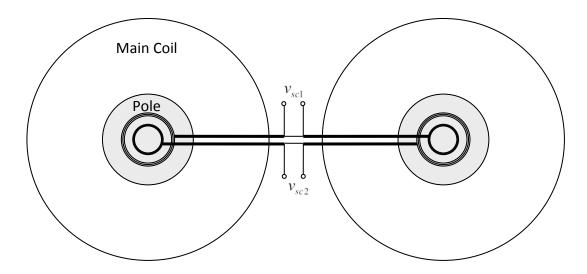

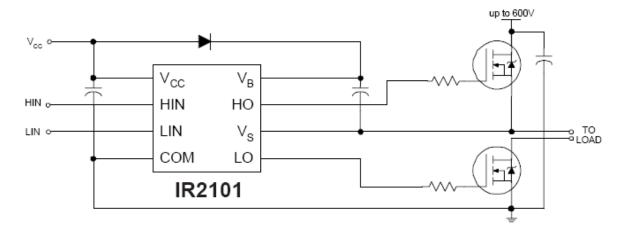

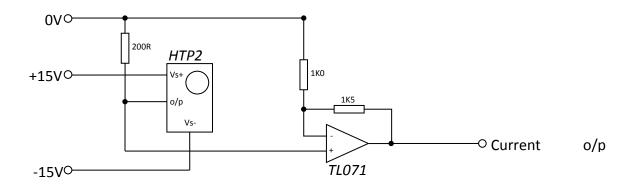

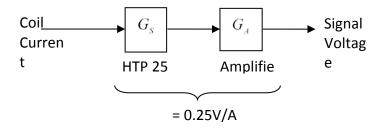

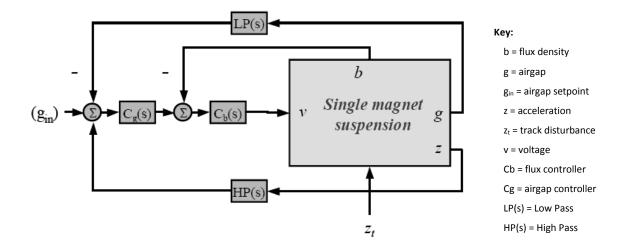

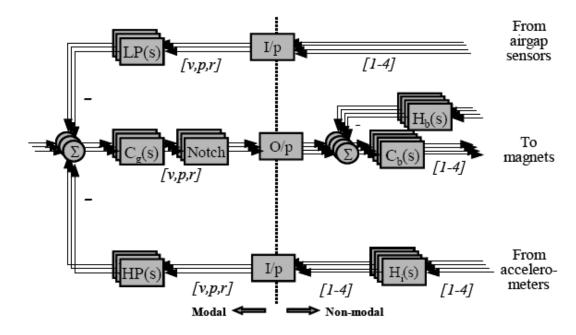

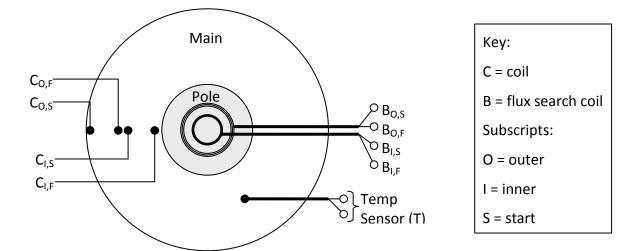

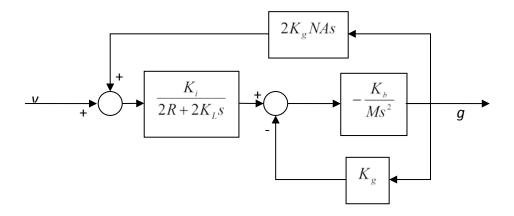

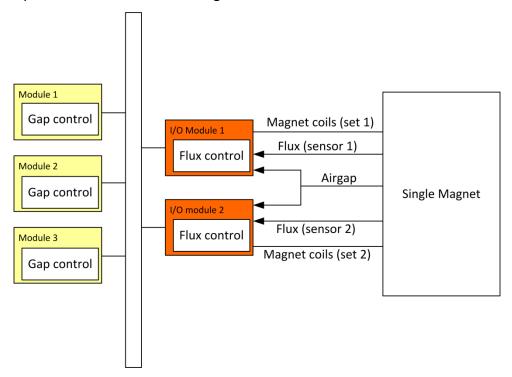

| Figure 3-7 Suggested sensor interface between IMA and Magnet                            | 83      |

| Figure 4-1 Practical Implementation of IMA                                              | 87      |

| Figure 4-2 Systems Management Hierarchy                                                 | 89      |

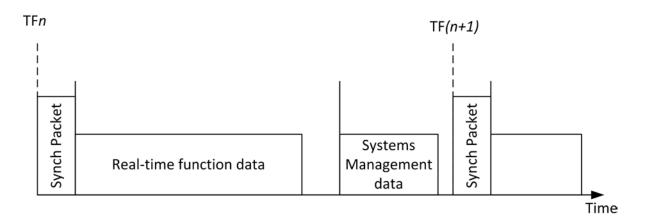

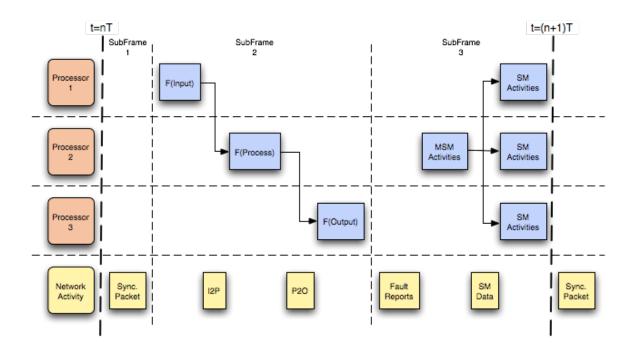

| Figure 4-3 Time Partitioning of Network Bus using Segmented Time Frames (TF)            | 91      |

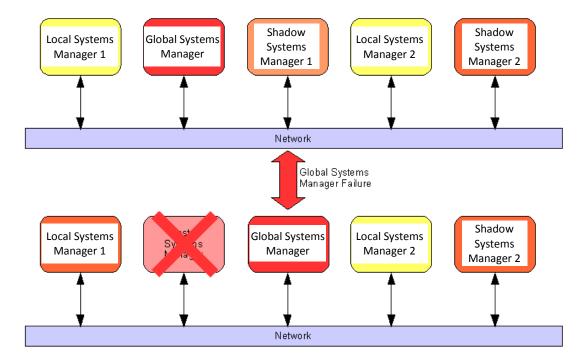

| Figure 4-4 Systems Management Tolerating Failure                                        | 92      |

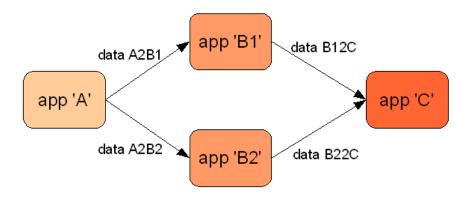

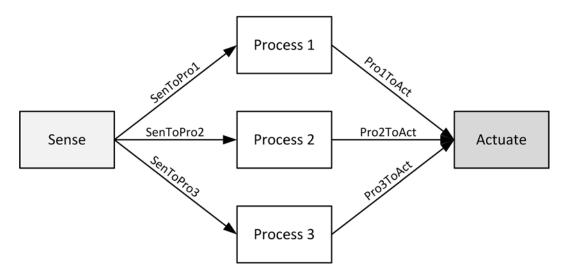

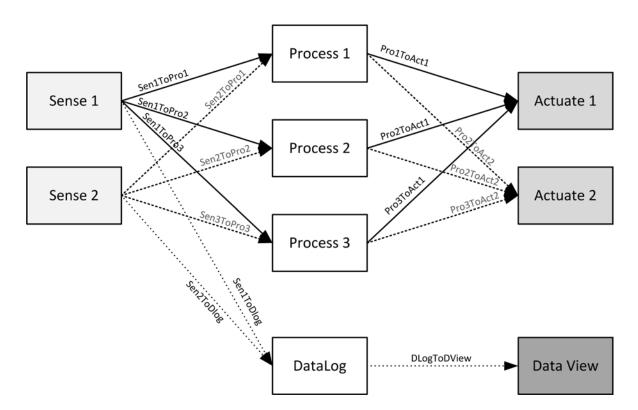

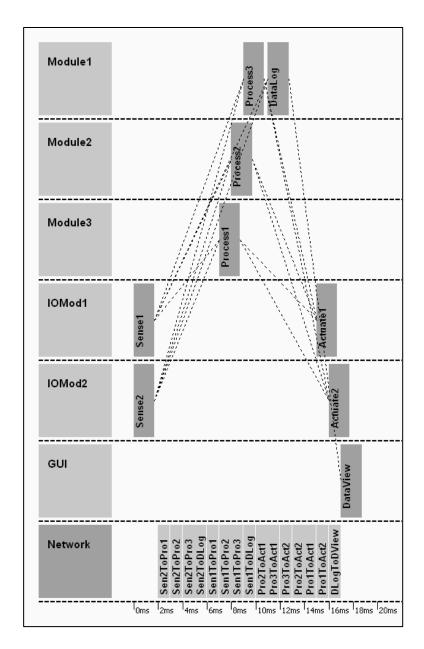

| Figure 4-5 A Simple Network of Functions                                                | 95      |

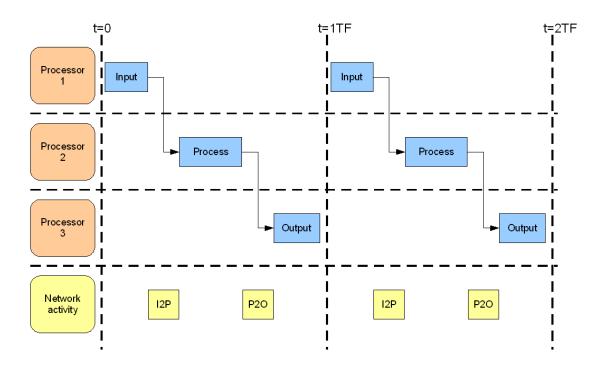

| Figure 4-6 Organising a Real Time Distributed Control System                            | 97      |

| Figure 4-7 Simple Network of IMA Resources                                              | 99      |

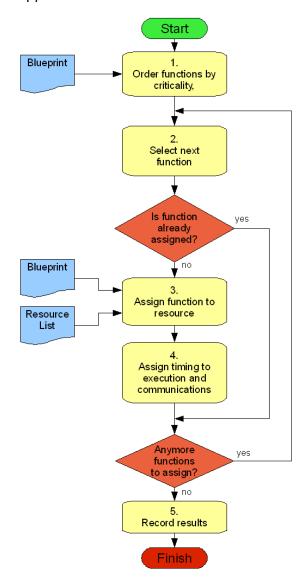

| Figure 4-8 Recursive Placement Algorithm Process Flow                                   | 100     |

| Figure 4-9 Order Functions by Criticality                                               | 102     |

| Figure 4-10 Find Next Function to Place                                                 | 103     |

| Figure 4-11 Assign Function to Resource                                                 | 104     |

| Figure 4-12 Order Function on Module                                                    | 106     |

| Figure 4-13 Relationship between search direction and function                          | 108     |

| Figure 4-14 Process to Assign Timings to Communications and Execution                   | 109     |

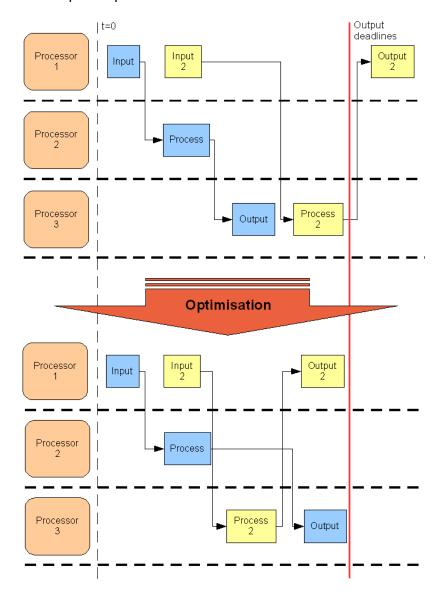

| Figure 4-15 Benefits of Optimisation                                                    | 114     |

| Figure 4-16 Subdivision of Time Frame                                                   | 119     |

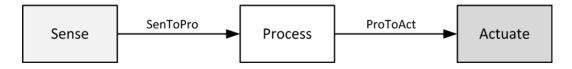

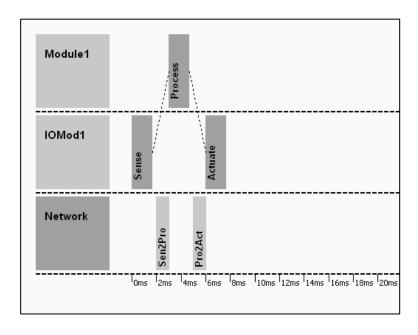

| Figure 5-1 Single Sense, Process and Actuation                                          | 125     |

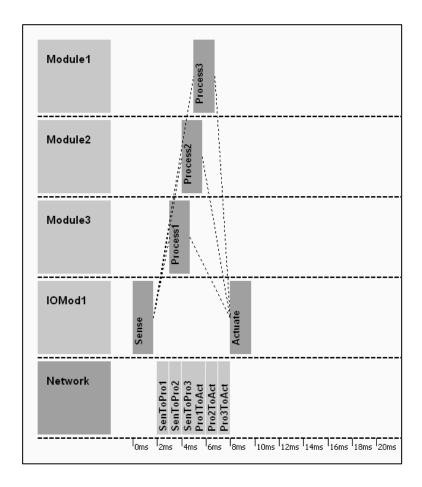

| Figure 5-2 Allocation results of Single Sensor, Single Process and Single Actuator      | 127     |

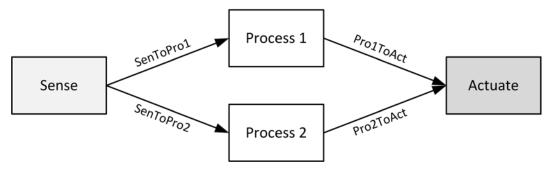

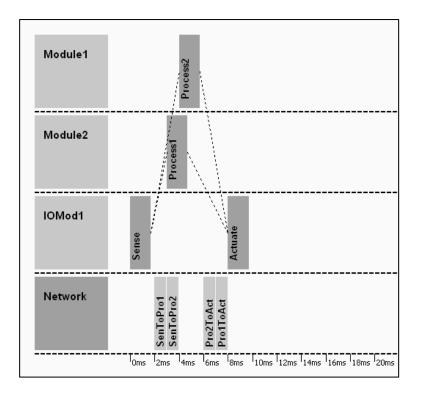

| Figure 5-3 Single sensor, duplex processing, single actuation                           | 128     |

| Figure 5-4 - Single Sensor, Duplex Processing, Single Actuator                          | 129     |

| Figure 5-5 Single sensor, Triplex processing, single actuator                           | 130     |

| Figure 5-6 Allocation Results of Single Sensor, Triplex Processing, Single Actuator     | 131     |

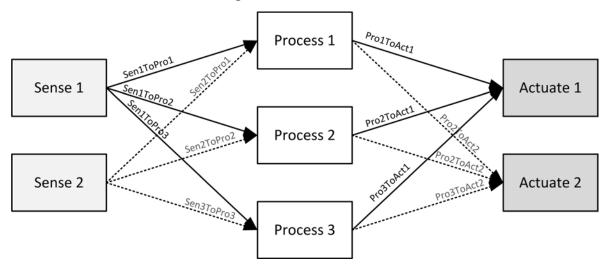

| Figure 5-7 Dual sensors, triplex processing, dual actuation                             | 132     |

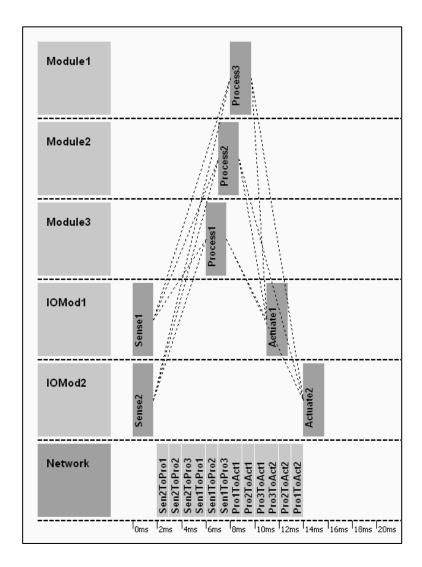

| Figure 5-8 Allocation Results of Dual sensors, triplex processing, dual actuation       | 133     |

| Figure 5-9 Dual sensing, triplex processing, dual actuation plus non-critical functions | 134     |

| Figure 5-10 Allocation Results of Dual Sensing, Triplex Processing, Dual Actuation ar   | nd Data |

| log                                                                                     | 136     |

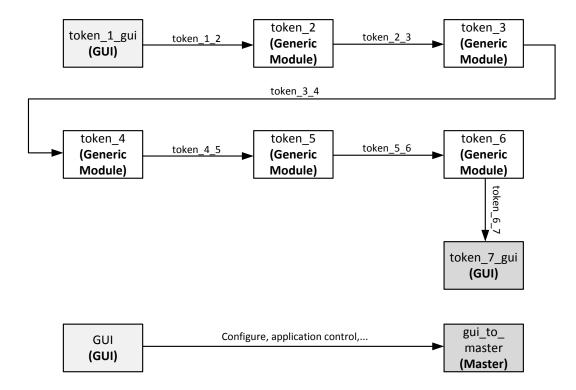

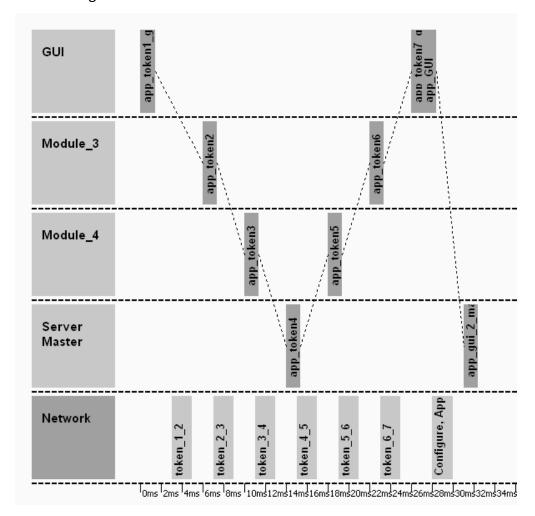

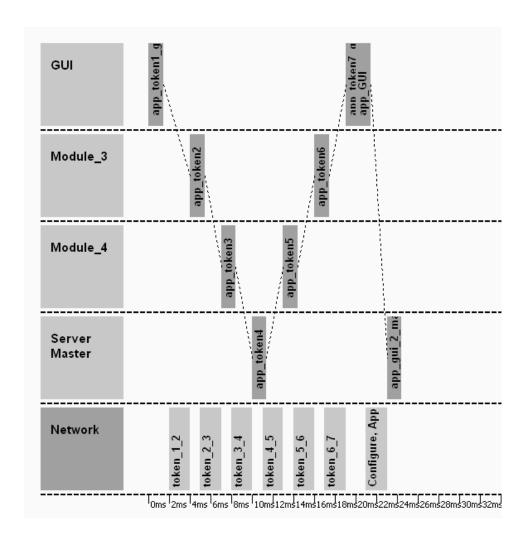

| Figure 5-11 Function Network Design for Token Passing Exercise                          | 138     |

| Figure 5-12 Allocation of Token Passing Functions to IMA (3 ms communication       | time |

|------------------------------------------------------------------------------------|------|

| allowed)                                                                           | 139  |

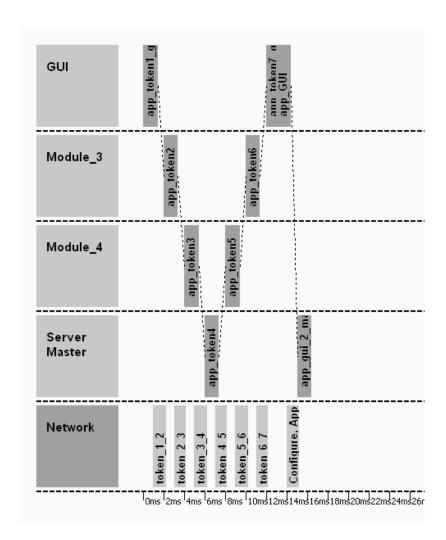

| Figure 5-13 Allocation of Token Passing Functions to IMA (2 ms communication       | time |

| allowed)                                                                           | 144  |

| Figure 5-14 Allocation of Token Passing Functions to IMA (1 ms communication       | time |

| allowed)                                                                           | 146  |

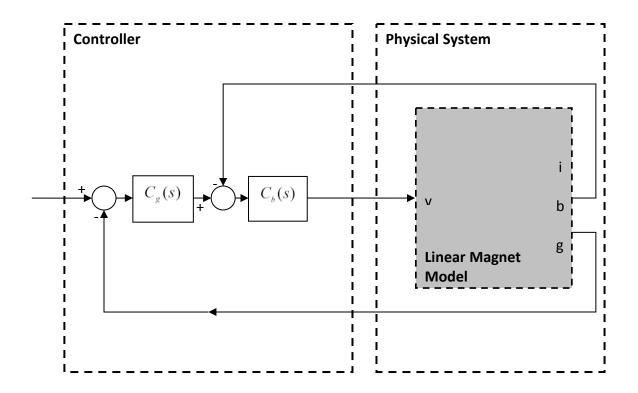

| Figure 5-15 Air gap control schematic                                              | 149  |

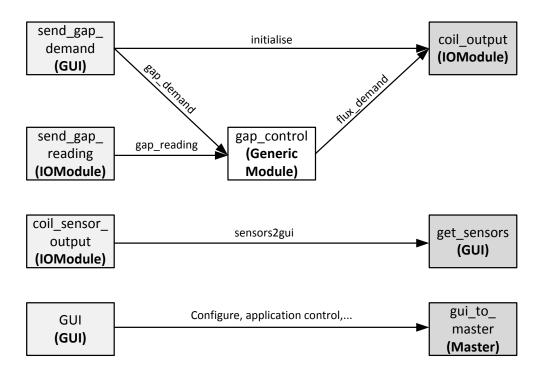

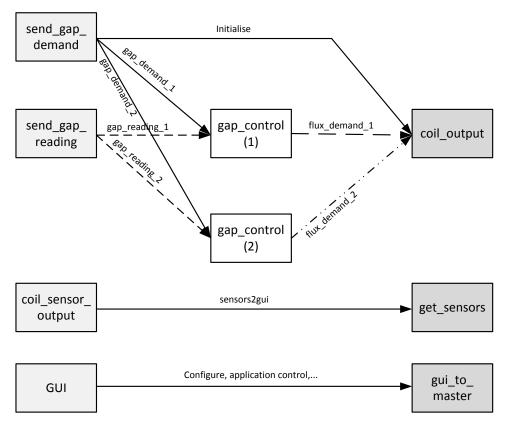

| Figure 5-16 Function Network for Gap Control Structure                             | 150  |

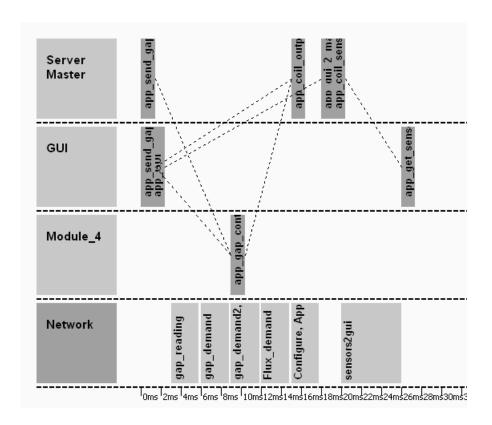

| Figure 5-17 IMA Implementation of Gap Control Functional Network                   | 151  |

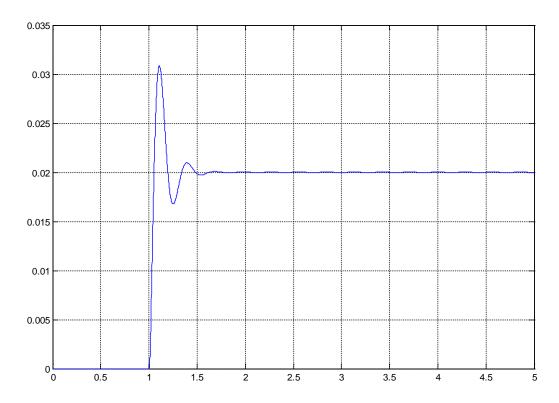

| Figure 5-18 Time Response of Simulated Air Gap to Step Input                       | 152  |

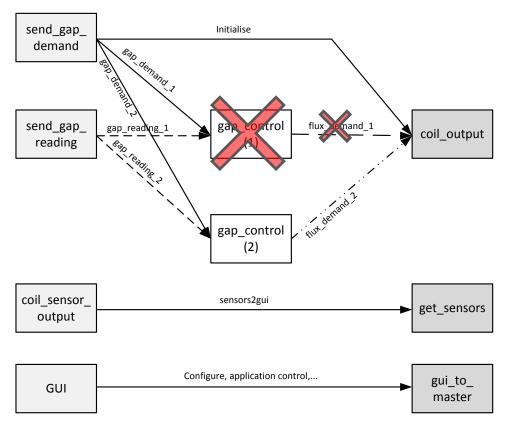

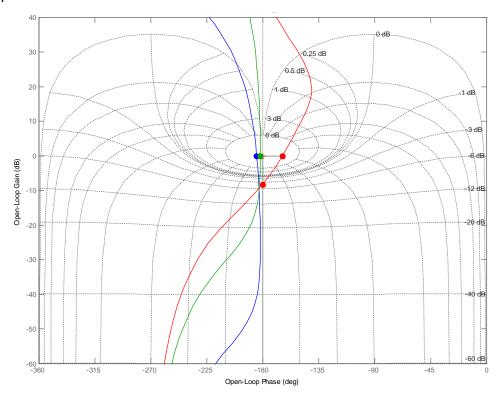

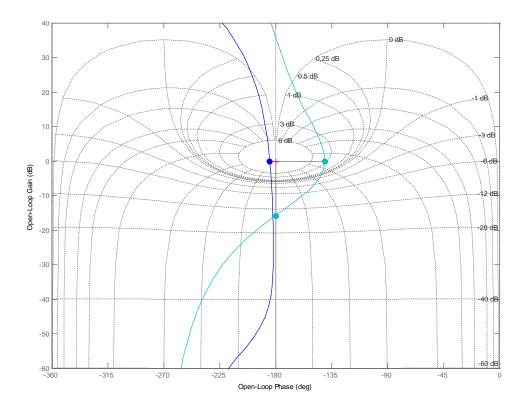

| Figure 6-1 Control Loop Realisation for Airgap control                             | 155  |

| Figure 6-2 Network of Air Gap Control Functions                                    | 156  |

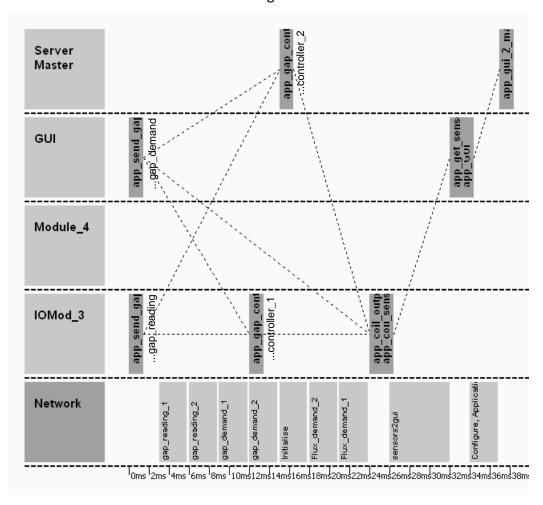

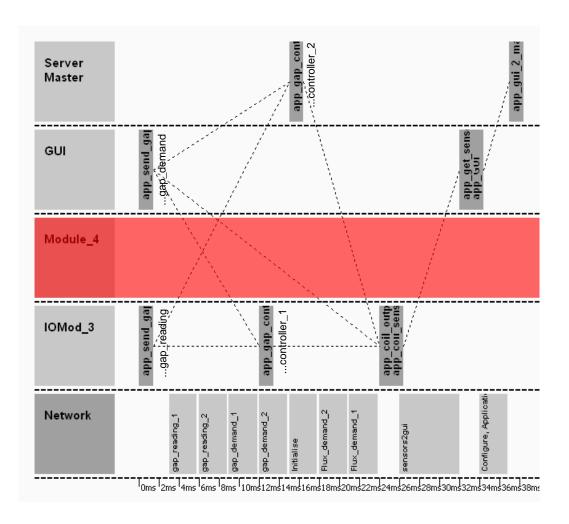

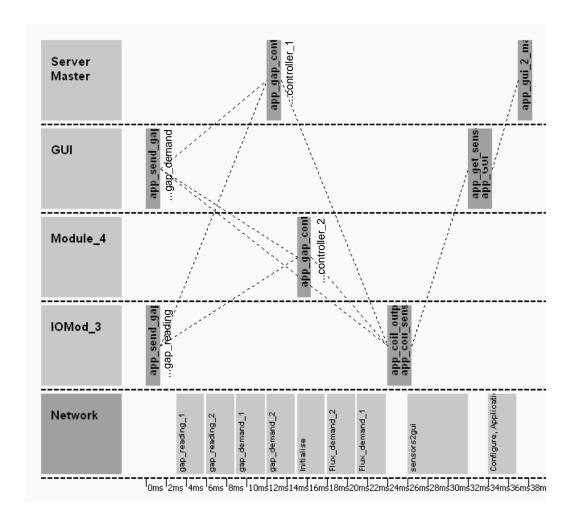

| Figure 6-3 Assignment of functions to resources For duplex gap controller          | 160  |

| Figure 6-4 Application failure introduced to 'gap_controller_1'                    | 162  |

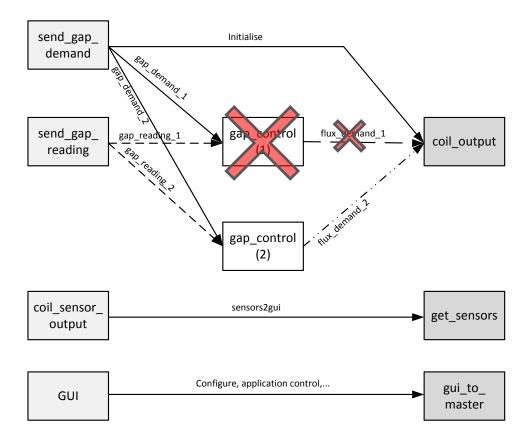

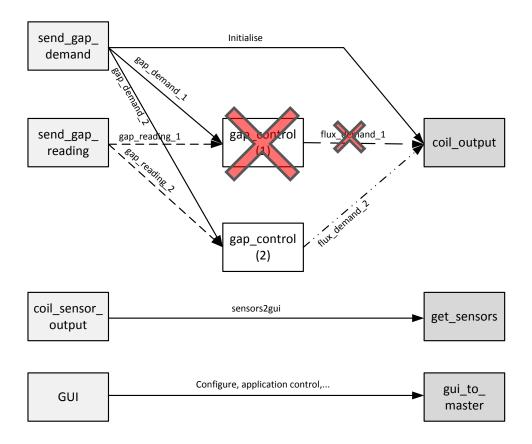

| Figure 6-5 Effect of failure on the functional network                             | 163  |

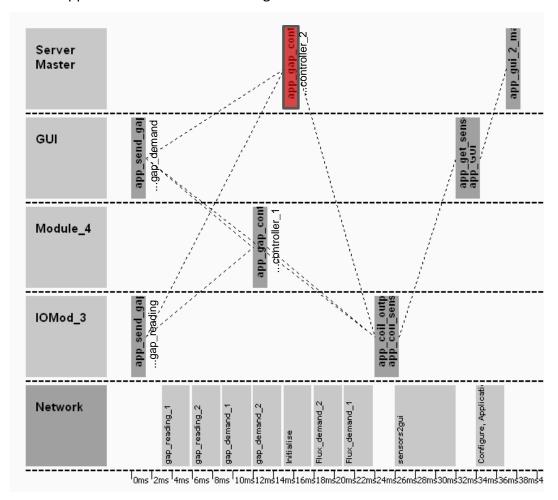

| Figure 6-6 Allocation of functions as a result of reconfiguration                  | 164  |

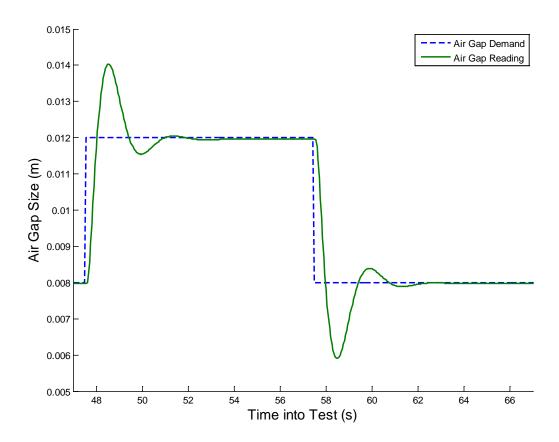

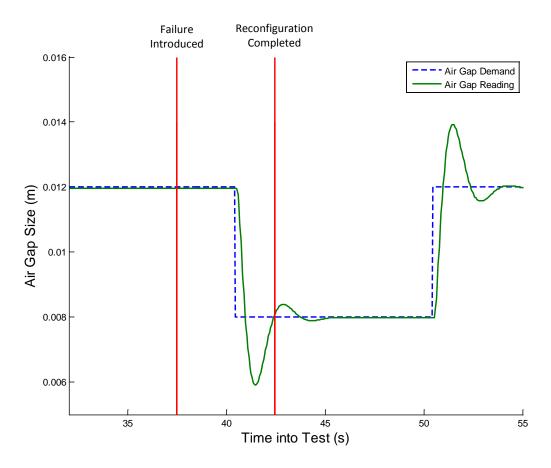

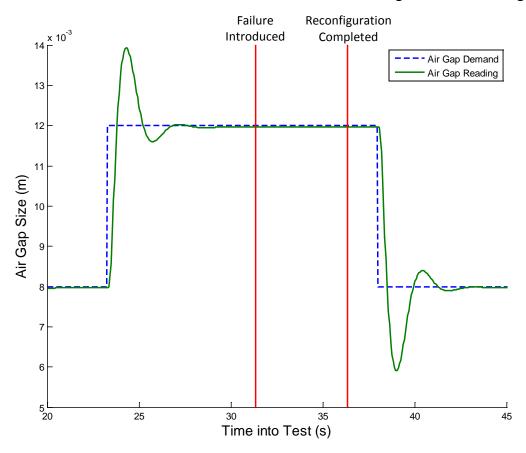

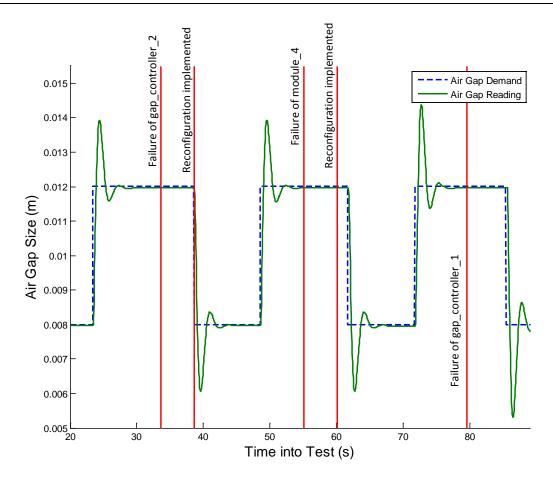

| Figure 6-7 Airgap response during reconfiguration activity                         | 165  |

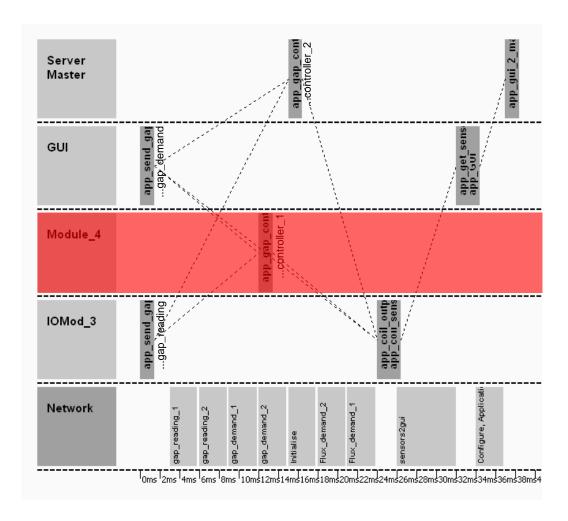

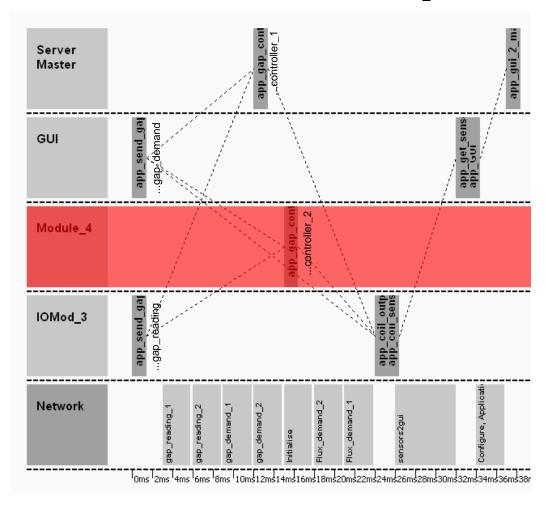

| Figure 6-8 Module failure introduced to module 4                                   | 167  |

| Figure 6-9 Effect of Module4 failure on the functional network                     | 168  |

| Figure 6-10 Allocation of functions as a result of reconfiguration                 | 169  |

| Figure 6-11 Airgap response during reconfiguration activity                        | 170  |

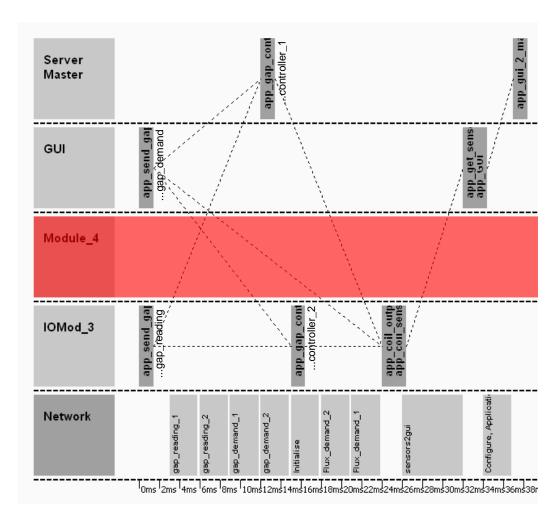

| Figure 6-12 Application failure introduced to 'gap_controller_2'                   | 171  |

| Figure 6-13 Reconfiguration following the failure of the gap_control_2 application | 172  |

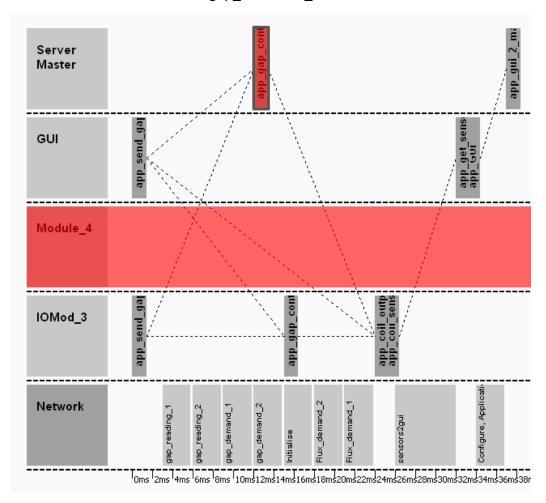

| Figure 6-14 Failure of module_4                                                    | 173  |

| Figure 6-15 Configuration as a result of failing module_4                          | 174  |

| Figure 6-16 Failure of gap_controller_1                                            | 175  |

| Figure 6-17 Effect on functional network of three failures                         | 176  |

| Figure 6-18 Time response of airgap during series failures                         | 177  |

### v. List of Tables

| Table 2-1 Comparison of IMS Capabilities to Highlighted Requirements                 | 25   |

|--------------------------------------------------------------------------------------|------|

| Table 2-2 ARINC 653 content summary (Prisaznuk, 2008)                                | 29   |

| Table 3-1 Component Composition of Top Level System                                  | 66   |

| Table 3-2 Maglev Rig Sensor Descriptions                                             | 82   |

| Table 4-1 Analysis of LabVIEW implementation of IMA style middleware                 | 88   |

| Table 4-2 IMA Blueprint Outline                                                      | 94   |

| Table 4-3 Example Capture of Application Information                                 | 96   |

| Table 5-1 Assignment Criteria                                                        | .127 |

| Table 5-2 Assignment criteria for duplex processing                                  | .129 |

| Table 5-3 Assignment criteria for triplex processing                                 | .130 |

| Table 5-4 Assignment criteria for triplex processing and dual I/O                    | .133 |

| Table 5-5 Assignment Criteria for Dual Sensing, Triplex Processing, Dual Actuation   | and  |

| Datalog                                                                              | .135 |

| Table 5-6 Sample Communication Data from a Single Time-frame                         | .141 |

| Table 5-7 Communication timing results $-3$ ms communication time (824 time frames). | .143 |

| Table 5-8 Communication timing results $-2$ ms communication time (902 time frames). | .145 |

| Table 5-9 Communication timing results - 1 ms communication time (828 time frames) . | .147 |

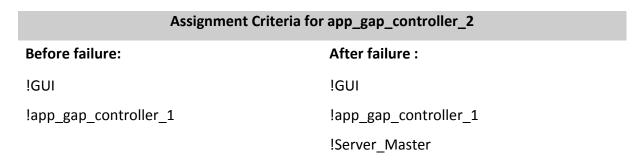

| Table 6-1 Change in Assignment Criteria as a result of Fault Injection               | .164 |

| Table 6-2 Change in available modules as a result of failure                         | .169 |

| Table 6-3 Change in assignment criteria as a result of failure                       | .172 |

| Table 6-4 Change in available modules as a result of failure                         | .174 |

| Table 6-5 Change in assignment criteria as a result of failure                       | .175 |

# Fault Management via Dynamic Reconfiguration for IMA

**CHAPTER 1:**

Introduction

### 1. Introduction

This thesis addresses the concept of using dynamic reconfiguration within an avionic system to maintain high levels of redundancy in the presence of faults.

The concepts presented are based on the modern avionics architecture known as Integrated Modular Avionics (IMA). This solution to on-board computing requirements is designed to be flexible by specifying generic hardware resources for which 3<sup>rd</sup> party avionic applications can be developed. Compared to traditional avionics design, IMA reduces the complexity and cost of avionics systems by commonality of modules, flexible configuration options, and incremental update possibilities.

A further opportunity of IMA is exploiting the flexible configuration to extend operating periods of aircraft, even in the presence of failures. By optimising configuration using healthy parts of the system; sufficient levels of reliability could be maintained to retain operational performance. This thesis considers managing faults at the point of occurrence using dynamic reconfiguration (i.e. automatically re-configuring at run-time) to tolerate component failures.

### 1.1. Background

Future generations of avionics are transitioning from a traditional 'federated' design to flexible architectures that exploit benefits of modularity. These benefits are realised through potential savings in spares (via savings due to commonality of design), extended operating periods between maintenance (via abilities to 'gracefully degrade' and tolerate faults) and ease of upgradeability (via a software layering mechanism that removes dependency between hardware and software components).

A concept proposed and defined for the civilian sector by the standard ARINC 653 (ARINC, 2006), and in the military sector in DEF-STAN-00-78 (MOD, 2005), is that of Integrated Modular Avionics (IMA). The fundamental principle of IMA is that bespoke hardware and

software design for a specific function is replaced by generic processing units capable of delivering the same functionality by executing software 'applications'.

This format has the potential to be implemented using conventional systems design in that a configuration of hardware resources and software applications can be defined, with communications protocols and execution scheduling such that real-time task execution can be performed deterministically. This offers benefits over a federated design in that the hardware processing resources across the network can be similar, significantly reducing the spares and servicing requirements to maintain system availability.

To achieve further benefits of IMA, the flexible architecture can be exploited to reconfigure the system when failures occur. This benefit can be realised off-line (between operations) or on-line (during operation). In an off-line sense, a new configuration could be defined at the point of front-line servicing to extend operation between maintenance intervals. If reconfiguration could occur during run time, the system could adapt in order to maintain high levels of safety critical operation in the presence of failures.

### 1.2. Problem Statement

The introduction of IMA presents a number of opportunities, as previously highlighted, but also brings with it a number of challenges. Aircraft systems have to be certified to an incredibly high standard of reliability. This is a complex task that requires complete systems understanding to prove that common failure modes are not safety-critical or mission-critical. As such, the system design is 'frozen' early in the system lifecycle as changes to part of the infrastructure can lead to costly re-certification of the whole system whole. This makes the concept of reconfiguration (even in an off-line sense) a difficult one to introduce to the aviation industry. Current philosophies follow the idea of a 'multi-static' configuration, whereby a number of system configurations are designed and certified prior to operation. Such an approach enables some of the benefits of IMA to be seen, and allows some flexibility within the system configuration. IMA systems in service currently utilise this approach.

To achievement the full benefits of the flexible nature of an IMA, system configuration needs to be automatic. In such a case, the system would be capable of continually identifying the most effective allocation of applications to resources. This enables the restoration of high levels of operational capability shortly after the occurrence of a failure and a graceful degradation of the system such that reliability levels can be maintained by reconfiguration in the presence of component failure. Such an automatic configuration method would have to be robust (such that it does not implement bad configurations) and intelligent (such that functional and reliability requirements are not jeopardised by the configuration defined).

There are two fundamental principles that are evident when considering the problem of assigning avionic functions to system resource; that of assigning functions to specific resources (e.g. information input/output points), and that of ensuring point failures are not created by assigning redundant processing streams to the same physical resource. Alongside this is the temporal configuration problem, in that real-time control or data processing tasks need to occur concurrently such that the latest available data is used in calculations. Mismanagement of this can have implications such as reducing expected closed-loop performance specifications.

### 1.3. Contributions

Further to the problem analysis in the previous section, the main research contributions for this PhD are to:

- A solution for the dynamic reconfiguration problem for assigning required systems functions (namely a distributed, real-time control function with redundant processing channels) to available computing resources whilst protecting the functional concurrency and time critical needs of the control actions.

- A systems management strategy that utilises the dynamic reconfiguration properties of an IMA to restore high levels of redundancy in the presence of failures.

### 1.4. Objectives

In order to validate the contributions outlined in section 1.3, the following objectives have to be met:

- Investigate relevant literature to determine current state-of-the-art in areas such

as; IMA implementation, Fault management strategies within IMA, and methods for

assigning avionic functionality to an IMA hardware installation.

- Develop a method of automatic configuration/reconfiguration of required avionic applications to distributed process resources.

- Design and develop a hardware test bed (i.e. a representative IMA system with appropriate 'middleware' and real-time communication strategy) to enable implementation of the automatic configuration/reconfiguration method.

- 4. Validate that the IMA implementation is capable of facilitating distributed real-time control operations with a range of functional topologies.

- 5. Verify the ability of the configuration method to appropriately assign avionic applications to available resources using a range of functional topologies and available modules.

- 6. Verify the ability of the IMA system to reconfigure a distributed real-time control functional set (following a fault injection) to an allocation that tolerates component failure.

### 1.5. Publications

The following are publications as a result of the work detailed within this thesis.

- Hubbard, P., Goodall, R., Dixon, R., & Mapleston, M. (2008). Integrated Modular Systems for Maglev Vehicle Control. In *The 20th International Conference on Magnetically Levitated Systems and Linear Drives (MAGLEV 2008)*. San Diego, USA.

- Hubbard, P., Mapleston, M., Goodall, R., & Dixon, R. (2008). Integrated Modular Processing for High Performance, High Integrity Control (IMPPIC). In *EDCC-7 Seventh European Dependable Computing Conference*. Kaunas, Lithuania.

### 1.6. Thesis Overview

This thesis details the key findings and results from the objectives listed in section 1.4. Chapter 2 contains a review of appropriate literature to identify the current capability of fault management within IMA, and other appropriate technologies and methods of similar areas that may have useful input to the study. Chapter 3 considers the findings of Chapter 2 and defines requirements in order to enable validation of the developed system and ensures tests are appropriate for proving the research objectives. Chapter 4 presents the real-time task control task (namely air-gap control of a Maglev vehicle) that will be the subject of the IMA. The purpose of this is to provide a complex control problem of an open-loop unstable system that should remain controlled in the presence of IMA component failure. Chapter 5 details the development of the IMA system, including the method used for configuring and reconfiguring avionics applications to available processing resources. Chapter 6 presents validation of the configuration method by analysing a series of configuration tasks and testing the timing properties of the system to ensure distributed real-time processing is occurring. Chapter 7 includes the results of a series of laboratory tests to observe the system response to IMA component failures. The goal of these tests is to show that after an occurrence of a failure, the system can reconfigure to regain previous reliability levels, whilst maintaining service provision. Chapter 8 documents the conclusions and main findings of the thesis.

# Fault Management via Dynamic Reconfiguration for IMA

**CHAPTER 2:**

# Literature Review

### 2. Literature Review

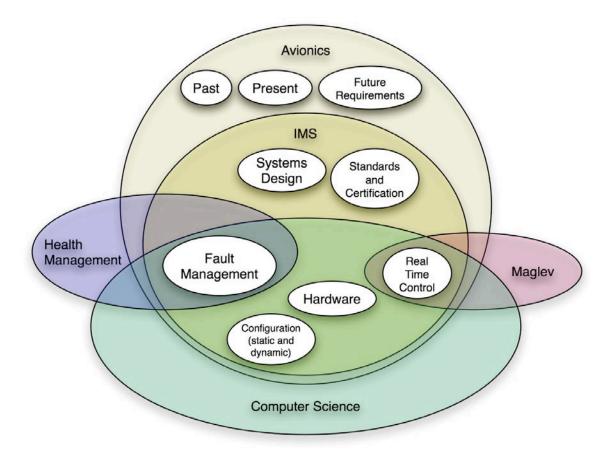

IMA is a large topic branching into different disciplines and areas of interests resulting in a potentially large and diverse reading area. Figure 2-1 below shows the major areas of research undertaken and how they overlap to form common ground. Although this figure represents the main areas of study, it is not a definitive list of topics.

Figure 2-1 Research Topics

The following sections are the findings taken from academic publications, text books, journal articles and other sources of open information that are pertinent to the above topics.

### 2.1. The Developing Need for Improved Avionics

Over the past few decades, aircraft avionics systems have developed at a staggering rate into highly capable, costly and complex systems. This development has been fuelled by an end user requirement to exploit the potential capability offered by digital electronic devices and by a desire to constantly reduce the cost of maintaining a complex aircraft system throughout its lifecycle.

This section outlines these drivers and summarise the related future needs of aircraft systems.

### 2.1.1. Digital Revolution in Aircraft Systems

The rapid development in avionic system capability has been fuelled by the explosion of digital technology throughout the latter half of 20<sup>th</sup> century and to the current day. This fundamental relationship has been highlighted in a number of texts (Collinson, 2011; Moir, Seabridge, & Jukes, 2003, 2006; Moir & Seabridge, 2008).

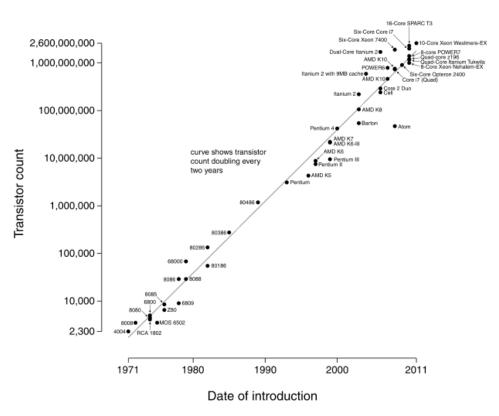

World War II provided the first major drive for electronics to be embedded on board aircraft. These first systems were analogue based and relied on linear relationships for communication and processing of data throughout the system. Due to the extreme environment of an aircraft, these systems were subject to large amounts of drift and non-linearities. The alternative to these systems evolved during the 1950s and 1960s as the transistor replaced the thermionic valve which eventually led to the widespread use of digital electronics in the 1970s. The advent of micro-electronics and the capabilities that subsequent digital avionics systems could offer finally proved to be a better solution to providing the capabilities required for aircraft. As integrated circuits continue to follow development trends as highlighted with 'rules of thumb' such as Moore's Law (Moore, 2006), highlighted in Figure 2-2, we can expect to see aircraft systems continue to provide increasing performance and capability.

### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 2-2 Historical Analysis of Moore's Law

In the current day, high performance digital technology not only offers the means to perform increasingly complex tasks within each individual subsystem, but to integrate avionic subsystems effectively creating the capacity to perform even more capable and complex functions.

#### 2.1.2. The Development of Avionics Integration

The following is a summary of the work done by Zhang, Moir and Collinson (Collinson, 2011; Moir et al., 2006; Zhang, Pervez, & Sharma, 2003) who have all produced extensive works with regards to the development of avionics technologies.

Avionics have the potential to be integrated in different ways to yield different benefits. In the 1970s, a non-profit making organisation called Aeronautical Radio Inc. (ARINC) suggested that avionics units should have commonality in terms of form, fit and functionality – commonly known as F<sup>3</sup>. The critical aspect of this standardisation is that a

Line Replaceable Units (LRU) that meets the F<sup>3</sup> specification can be directly replaced by another even if the replacement has different interior electronic implementation, or even manufactured by a different company. This specification lead to the terminology of Line LRUs or LRIs (Line Replaceable Items) which refers to modules that conform to the F<sup>3</sup> criteria. The benefits of this standardisation are widespread. It allowed for an open market place to exist for avionic components as well as simplifying the way spare units are managed.

In addition to the integration of the physical aspects of LRUs, it was widely recognised that passing data between aircraft systems would be a powerful capability. The sharing and fusion of data from different sources allows information to be inferred that may not be directly available from a single source. A classic example of this is the use of multiple sensors for object tracking (Varshney, 1997). In order to manage the sharing of data, it became clear that a standard was required for the data interaction of avionics.

During the early phase of this development, items were connected by a single source, single sink (or point to point, hard wired) connection wherever a communications channel was required. Although effective and logical to a degree, this format found limitations as the required amount of data passing between avionics functions increased to meet demands for more complex capabilities.

In order to address this issue and to provide consistency across the aerospace community, a number of standardised formats of connectivity between LRUs were defined. This section will look at three examples of these methods, namely ARINC 429, MIL-STD 1553 and the ARINC 629 specifications.

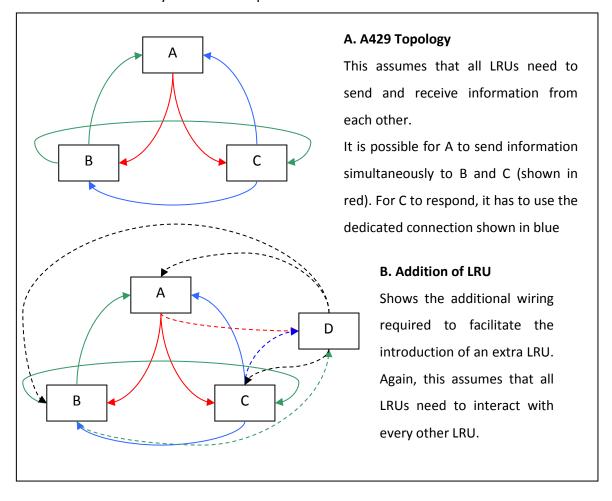

The ARINC 429 databus is a single source, multiple sink (SSMS) communication concept. The fundamental concept of a SSMS is that one node can send data to a number of recipient equipments via a digital serial link. This solution was adopted in aircraft such as the Boeing 757, 767 and the Airbus A300 and A310

The main limitation of the ARINC 429 databus is that it is a half-duplex design via a point to point communication strategy. In this topology each communication link requires dedicated hardware at both the source and sink of the transmission plus a dedicated cable to transfer the message. A difficulty with this system is that this set of components can only facilitate the transfer of a message in a single direction. For a reply signal to be sent, a second communication link inclusive of a duplicate set of hardware is required.

As systems using this topology grew in complexity and more information was required to be shared, the length and weight of cabling to facilitate these transfers grew substantially. For example, the Boeing 767-200ER contains approximately 90 miles (145km) of electrical wiring, clearly a huge maintenance issue. Furthermore, if the requirements of a system such as this were to change and extra LRUs are required, the redesign, refit and recertification of the system is a complex task.

Figure 2-3 ARINC 429 Example

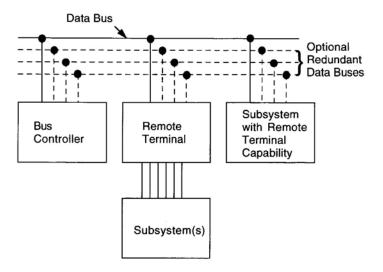

An alternative developed to this communications methodology in the military avionics domain is the MIL-STD (Military Standard) 1553 databus. Although the specification for the MIL-STD 1553 occurred slightly before the ARINC 429, its design has stood the test of time and is still widely popular in military avionic systems.

The MIL-STD 1553 is a true data bus. It is a half-duplex system, which means that although communication can occur in both directions along the same communication channel, they can only be sent one direction at a time. The advantage the 1553 bus has over the ARINC 429 is that this is a Multiple Source Multiple Sink (MSMS) method meaning that each node can send a message to a number of nodes connected to the bus. The general bus structure of the MIL-STD 1553 is shown in Figure 2-4 below.

Figure 2-4 Multiplex databus system architecture (Moir & Seabridge, 2008)

The 1553 communications is controlled from a single node called the bus controller. The communication strategy in terms of data size, sender, recipient and timing for each data package for the particular avionics configuration implemented is predetermined and uploaded onto the controller. This preparation allows each configuration to be tested and verified before implementation via the use of software tools to ensure the communication meets concurrency and timing criticality requirements.

A further feature of the MIL-STD 1553 is the concept of multiplexing. In Figure 2-4, it can be seen that there is an option to include parallel channels of identical capability for redundancy purposes.

The ARINC 629 data bus is similar in concept to the MIL-STD 1553 bus as it is a true data bus, i.e. half duplex and MSMS. It is however of newer specification than the 1553 and offers more benefits, such as the capacity for 131 terminals against the 1553's 31 and a data transfer rate of 10 Mbit/sec compared to 1Mbit/sec. This particular system has been largely brought into popularity by the Boing 777 aircraft.

The main advantage the MIL-STD 1553 and the ARINC 629 architecture have over the ARINC 429 is the relative ease of adding new components. As mentioned before, for the ARINC 429, this requires a great deal more connections to satisfy the communication criteria. However for the true data buses another component can simply be added onto the length of the bus. This is certainly an advantage when it comes to modifying or reworking the system but does not remove all the complications with regards to re-testing and re-certifying.

### 2.1.3. Future Needs for Avionics Systems

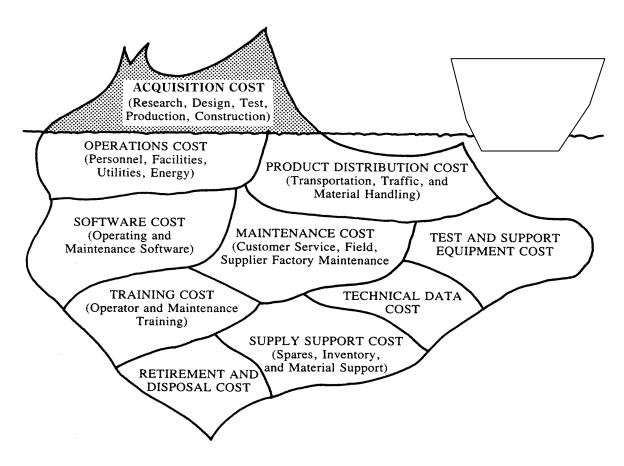

There is a continuing drive from the aerospace industry to improve the quality and cost effectiveness of avionics across the entire systems lifecycle, inclusive of design, maintenance and upgrade costs. Avionics in general account for 30% of the cost of a new aircraft (Collinson, 2011) and carry a further burden with the rest of the lifecycle costs in terms of maintenance during operation, the resolution of faults and the cost of recertification should an upgrade be required. Figure 2-5 highlights the overall lifecycle cost of an aircraft in the form of an iceberg. Although not to scale, it shows how the acquisition cost of the aircraft is merely the 'tip of the iceberg' and the real cost lies in the support required to keep the platform available for use for as much time as possible. It can be inferred from here how the development, maintenance, support and upgrade of avionics systems relate to many of the different areas highlight in the diagram.

Figure 2-5 Aircraft System Lifecycle Cost (Mapleston, 2006b)

Aerospace companies are therefore seeking to identify the causes for the high cost of avionics, and find ways of reducing this.

One of the causes of high avionics cost is that as customers request incremental change to existing designs or products to exploit new technology, bespoke platform specific solutions are developed to meet this need (Johnson & Omiecinski, 1998). As a result, there is little commonality between different aircraft types, resulting in spiralling costs associated with avionics equipment. To drive down this cost a requirement for commonality between systems and subsystems exists to allow the re-use of components.

A further contributing factor is identified as the early stages in the project at which aircraft design is fixed (Little, 1991). As part of certification, avionics systems designs are frozen at an early stage of the procurement cycle. This defines purchasing schemes, system designs, etc, that allow the system build to commence. As mentioned previously, by the time the

system is in service the requirements have usually changed. In addition to this, the technology available to build the system will have progressed and be more capable. The inherent problem of attempting to introduce new requirements and technologies, however beneficial they may be, is that the systems design, purchasing schemes and certification stages may no longer be valid and have to be repeated in order to clear the aircraft to fly. In addition to new technology or capability requirements posing problems to designs, the problem of component obsolescence is also a substantial issue. The lifecycle of an aircraft from initial design to retirement can be the order of 50 years. Even during the period from the initial design to manufacture, electronic parts often become outdated and stop being produced. This causes problems with the purchase of spare parts for the aircraft further down the lifecycle.

It is suggested (Johnson & Omiecinski, 1998; Little, 1991) that a modular approach to avionics design offers inherent solutions to these problems. The idea of a common processing unit, capable of executing a number of aircraft functions, would solve a number of issues. Firstly, if a generic processing module is implemented as a replacement to bespoke LRUs, these can be a common component not only throughout a single aircraft system but across all aircraft in the fleet, or potentially across all military and civil platforms. Clearly the knowledge base required to sustain these component would be drastically reduced, simplifying the complexity of maintenance. Secondly, if the software is suitably decoupled from the hardware, the software could be re-implemented quite simply on upgraded hardware, or vice versa. This removes some problems with obsolescence and upgradeability throughout the lifecycle. In addition, life cycle cost will be minimized by functional integration as it reduces the amount of duplication of hardware and software elements (Morgan, 1991). In line with this theory, Line Replaceable Modules (LRMs) are becoming increasingly popular with avionics design as a replacement to LRUs. LRMs are designed to provide a solution to the modularity paradigms that LRUs are unable to. This modular concept of design is studied in detail in section 2.2.2.3.

The potential cost benefits of implementing a modular system is highlighted by Little (Little, 1991):

"It has been estimate that if LRMs were substituted for today's black boxes or LRUs in a wing of 72 F-16 A/B fighter aircraft, a 50% reduction in the flight line avionics maintenance personnel could be made together with the elimination of the intermediate workshops. This represents a total manpower saving of 109 personnel, a reduction from 180 to 71. The same analysis showed a reduction in spares types from 437 to 43 and an increase in avionic system MTBF from 7.3 hours to 35 hours."

The key elements identified in the quote above are:

- 1. The quoted time for MTBF (Mean Time Between Failure). Having aircraft available to fly rather than sitting dormant in a hanger is a key capability for military situations and a huge cost benefit to civil aircraft. This increase in reliability of the system makes the solution better value to the customer.

- The reduction of intermediate workshops results in more availability of the aircraft

in that the system can be service and repaired on the front line. This means that the

unit does not have to return back to a main headquarters to be repaired and made

available.

- 3. The reduction of spares not only simplifies repair jobs, but reduces the logistic complexity of taking a military system to the front line, or maintaining a civil aircraft away from main base. The support infrastructure can be reduced resulting in another potential cost saving to the customer.

It is also suggested (Little, 1991) that military customers more specifically have three main requirements to utilise the opportunity for modular architectures:

- a) They must provide the desired mission capability. In particular they must allow the myriad datastreams obtained from the platform sensors to be more effectively integrated for the pilot to improve their situational awareness. Moreover, the avionics must be adaptive not only to accommodate new technology when appropriate but also more importantly to cope with a rapidly changing threat.

- b) They must be affordable. In particular life-cycle costs must be a design driver from initial concept through to, and including, operational service.

c) They must exhibit improved reliability, maintainability and availability. This is directly related to life-cycle costs which currently are dominated by maintenance costs, and the operational need for a flexible but sustained maintenance response remote from main operating bases.

A solution to the one or two of the above requirements can be found using conventional methods, but only a modulated solution can provide a solution to all three.

### 2.1.4. Summary of Future Avionic Requirements

The top level needs for future avionics systems have been highlighted from two main sources (Little, 1991; Sutterfield, Hoschette, & Anton, 2008). The first requirement set suggested (Little, 1991) are:

- Adaptive technology in order to meet changing mission requirements or changing technology

- Affordable through the lifecycle

- Exhibit improved reliability, maintainability and availability

In order to facilitate the growing capability desires of the customer, and to facilitate the overall needs highlighted, the expected technology requirements are to be (Sutterfield et al., 2008):

- Modular hardware operating at processing speeds more than two orders of magnitude great than today

- Dense multiplexing buses

- Multi-core modular processors

- Conform to open standards (F<sup>3</sup>)

The methods by which these capabilities can be implemented, associated with the design challenges involved, are discussed in the following sections.

### 2.2. Integrated Modular System Concepts

Integrated Modular Systems (IMS) have been identified as a potential concept that can meet the requirements of future avionics systems as highlighted in the previous section. The overall design principle is to utilise modularity throughout the system in order to move away from the tightly coupled/federated systems design of previous years.

This section aims to introduce the concepts of IMS and describe the work done to date in the development of systems

#### 2.2.1. Introduction to IMS

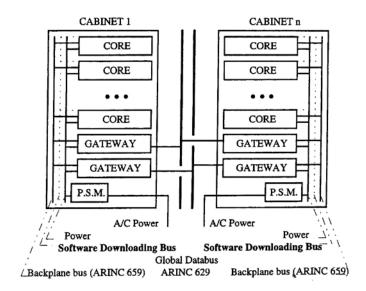

IMS can is also referred to as Integrated Modular Avionics (IMA), or Integrated Modular Architectures (also IMA). These systems offer conceptual solutions for future architectures for many aerospace programmes, with some limited IMS architectures already implemented (such as the Airbus A350 and the Boeing 777). IMS concepts are replacing current avionics systems as they have the potential to overcome many issues highlighted in the previous sections.

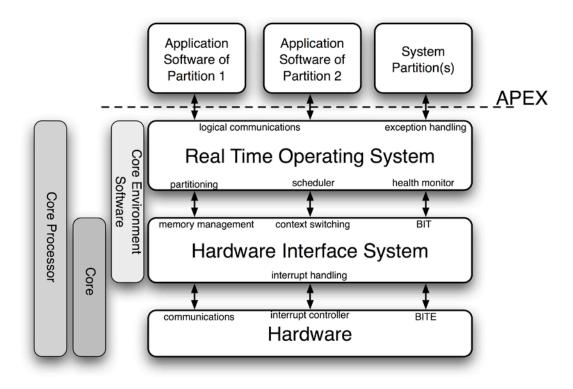

The concept of IMS was formalised in ARINC report 651 entitled "Design Guidance for Integrated Modular Architecture". The concept is one formed around using powerful computing modules that provide resource for the independent processing of application software (Prisaznuk, 1992). This is facilitated by an appropriate operating system that allows different applications to operate side by side on a single module.

Conmy (Conmy, 2006) provides a good introduction to the IMA concept. In this reference, the term Integrated Modular Avionics is introduced as:

"...a blanket term used to describe a distributed real-time computer network aboard an aircraft. This network should consist of a number of computing modules capable of supporting numerous applications of differing safety criticality levels."

These sources highlight the idea of a distributed yet integrated modular architecture, a statement which at first appears to contradict itself. However, the processing modules can

be connected throughout the aircraft by high speed databuses (such as ARINC 629), then the functionality of the different processes can be functionally integrated, albeit physically distributed (Jolliffe, 2005; Prisaznuk, 1992; Watkins, 2006).

One of the fundamental benefits of IMA is the modularity with which the system can be designed, built and maintained. The idea is that a system can be built to a functional specification using or re-using generic building blocks. This applies to the software applications as well as the hardware component. It is suggested (Field et al., 1997) that IMA consists of 5 'building blocks' that could be used to create any sized architecture, namely:

- Software the software architecture

- Hardware/Modules the hardware architecture

- Packaging the environmental conditions of the hardware, the cooling and the power conditioning

- Data transmission the communication network

- Low and Medium bandwidth interfacing to sensors/effectors

In summary, IMS provides a capability for interchangeable software and hardware components with interfaces well specified by open standards. IMS provides a good option to quickly reconfigure the allocation of functions either statically to meet new or changed deployment requirements or dynamically to restore higher levels of redundancy should faults occur.

The current state of the art IMA enables multiple unrelated applications, with different criticalities, to share the same computational platform without interference. The design challenge remains to map platform system and subsystem level constraints in timing, safety and security. (Gaska, Watkin, & Chen, 2015)

### 2.2.1.1. Modular Hardware/Software Integration

An important aspect of IMS is to remove the closely coupled nature of hardware and software which has been a part of avionics for a long time (Collinson, 2011; Field et al.,

1997; Morgan, 1991). The applications still require appropriate hardware to execute the software commands and fulfil function, but it is necessary to make the relationship loosely coupled.

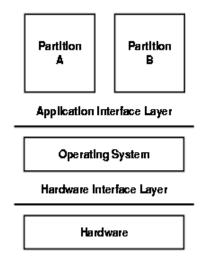

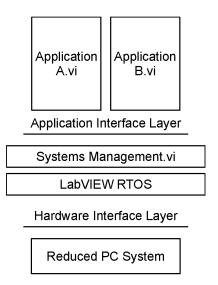

The generally agreed solution to this is to use a software architecture known as the 'three layer stack', which is a simplified version of that found in (Prisaznuk, 1992).

Figure 2-6 'Three Layer Stack' Model

The three layer stack is a fundamental principle for IMS as it provides the mechanism for the implementation of modular software upon modular hardware by facilitating well defined interface layers between the two. If this interface layer between hardware and software can be adequately implemented, the development of software can be performed without any direct knowledge of the hardware component. The hardware then becomes an unseen service provider of resource, such as facilitating communication or execution of functions. This is termed 'hardware transparency' (Conmy, 2006).

As applications are intended to be hardware transparent, the underlying hardware can theoretically be upgraded or replaced without affecting the design and source code of the application software. Conversely, an application can be upgraded or incrementally changed without directly affecting other applications, or requiring a hardware change. Furthermore, different companies will be capable of the production of parts of the system promoting

ease of development and competition for provision. Currently any changes to hardware or software require requalification of the system.

The arrangement of software functionality to hardware resources possible with IMS means that resource redundancy can be managed in new ways (Prisaznuk, 1992). For example, secondary redundancy in resource can be incorporated at component level or the system can be reconfigured by moving required software functions to available spare processing units. This may be done statically (during system down time) (Little, 1991) or dynamically (during operation).

In addition to providing for the hardware/software interface, the three layer stack provides a method of defining how to run multiple applications, or avionics functions, on shared resources such as processing and memory. If left unchecked this would present a problem as there is potential for a number of different safety critical avionics functions, all with their own real time constraints to function on shared resources (Lee, Kim, Younis, Zhou, & McElroy, 2000). In this situation, the safety case for the aircraft would be compromised and a potentially disastrous scenario could arise should one function hog a shared resource and delay the execution of another. To avoid this, a robust partitioning mechanism including processing resource scheduling needs to be implemented that prevents applications interfering with one another.

In terms of the production of an IMS, the final system should display the following properties (Conmy, 2006):

- Technology Transparency The underlying hardware should not have any impact on an application either during development or execution

- Scheduled Maintenance The system should have inbuilt capability to operate in the presence of failures so that Maintenance Free Operating Periods (MFOPS) can be achieved and only scheduled maintenance need occur.

- Incremental Update The system should be designed such that applications can be inserted/altered with minimum impact on other applications and on the supporting safety case

Another way of expressing some of the above properties is to say that an IMS should be designed as 'future proof', i.e. designed with technology transparency and with the capacity for incremental update. A future proof system can be described as (Edwards, 1997):

"A future proof system remains viable in terms of capability and affordability throughout its life cycle, despite the evolution of the technology that it embodies. Evolution of technology presents two major challenges to a system: obsolescence and capability growth."

A manner in which this can be achieved is to design a truly 'open' system architecture. An open system is one where no proprietary interface specifications exits that prevent outside agencies designing and building components capable of being integrated. It is likely that all components will have a specification following a so called F<sup>3</sup>I guideline (Form, Fit, Functionality and Interface). This F<sup>3</sup>I is a development of the F<sup>3</sup> idea introduced by ARINC for LRUs. These specifications will exist in the public domain.

In order to test the openness of a system, BAE SYSTEMS have 7 tests (Edwards, 2001):

- a) Information published & publicly available open access

- b) Sufficient information provided to allow independent implementation

- c) No royalties open exploitation

- d) Not dependant on proprietary components or processes

- e) Standards and essential components not restricted by export controls

- f) Possible to create special-to-type items which conform to the interfaces defined by the open standards and are interoperable with other items which conform to the standards (in modular systems this means that the system builder is not constrained to use only the standard modules)

- g) Open to technology growth & system growth technology transparent. In other words, open over a long period of time.

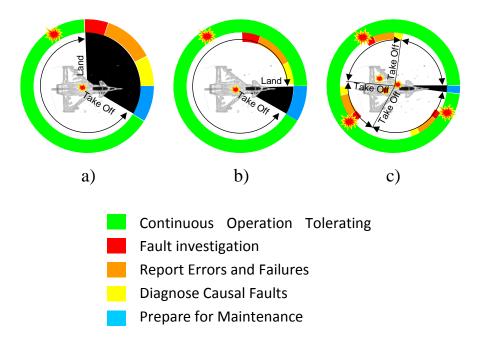

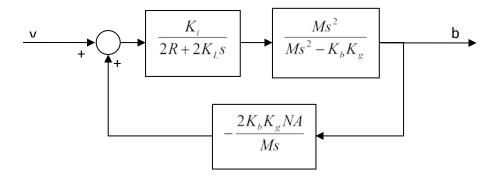

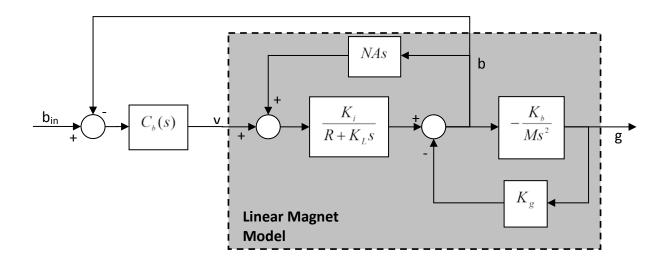

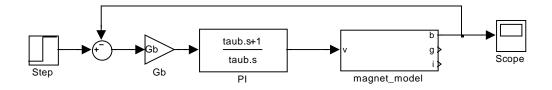

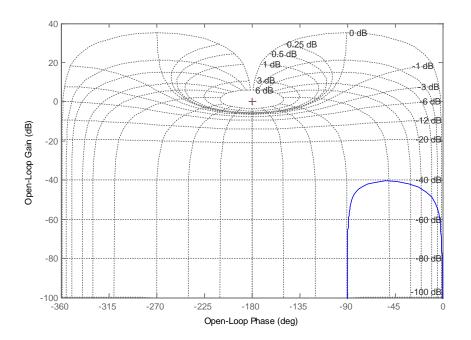

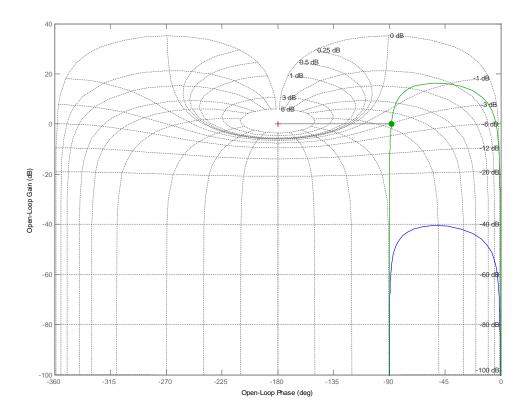

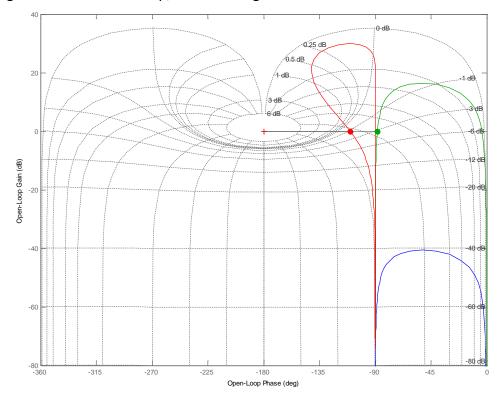

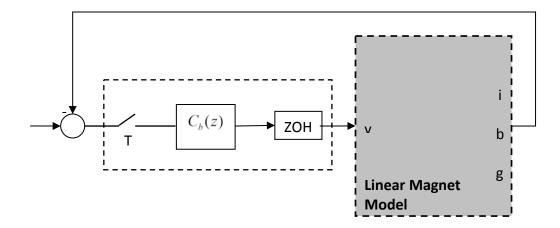

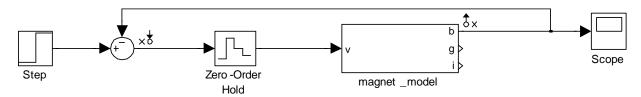

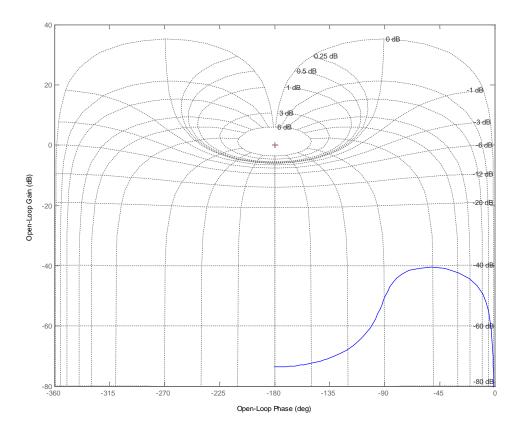

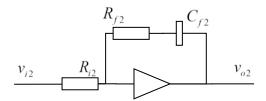

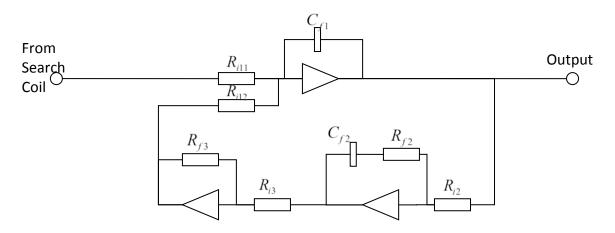

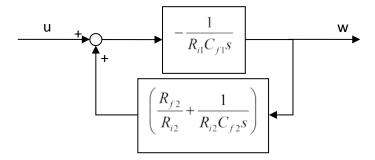

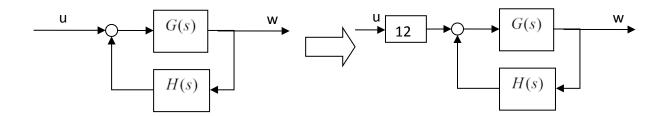

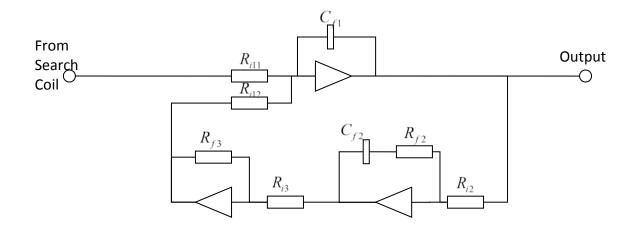

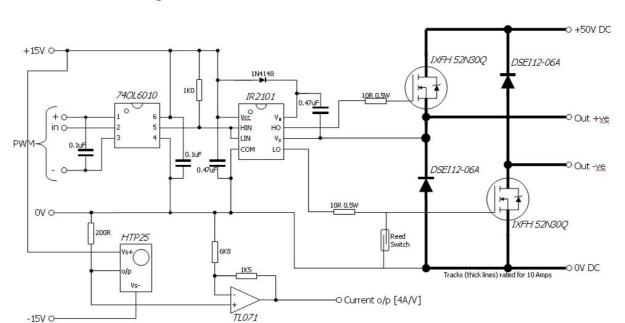

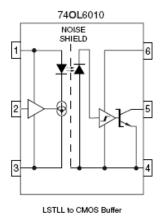

# 2.2.1.2. Why Use IMS?