# LOUGHBOROUGH UNIVERSITY OF TECHNOLOGY LIBRARY

| AUTHOR/FILING  | TITLE          |     |

|----------------|----------------|-----|

| Σ              | HANG, J        |     |

|                | <del>-</del>   | ·   |

| ACCESSION/COP  | Y NO.          |     |

|                | 03600031       | 9   |

| VOL. NO.       | CLASS MARK     |     |

|                |                |     |

| - 1 MAR 1993   | LOBA COPY      |     |

| - 4 1 MIL 1000 |                | e e |

| = 1; JUL 1994  | 30 Jt 1995     |     |

| · A SIGN COND  | 2 8 JUN 1998   |     |

| 11 KOV 1333    | 1              | ·   |

| - 1-177 199    | 4 2 5 JUN 1999 |     |

| 0 7-8CT 1994   |                | •   |

| n c 11th 1000  |                |     |

| 2 6 JUN 1998   |                |     |

| •              | 1              |     |

# ON FLEXIBLY INTEGRATING MACHINE VISION INSPECTION SYSTEMS IN PCB MANUFACTURE

by

# JINGBING ZHANG

A Doctoral Thesis

Submitted in partial fulfillment of the requirements

for the award of

Doctor of Philosophy

of the Loughborough University of Technology

Loughborough University

Department of Manufacturing Engineering

March 1992

© by Jingbing Zhang

| _        | borough University |

|----------|--------------------|

| C maga   | Any 92             |

| C (a) () | 036000319          |

w9921256

My Parents and My Wife

#### **ACKNOWLEDGEMENTS**

The author wishes to thank:

Professor R. H. Weston for his kind supervision, encouragement and support.

Mr. J. M. Edwards, Mr. I. S. Murgatroyd, Mr. I. A. Coutts, Mr. J. D. Gascoigne, Mr. P. Clements, Mr. G. P. Charles, Mr. D. Walters for their interest, technical support and friendship.

Mr. X. D. Chen, Mr. J. Wang, Mrs. Y. Gu, Mr. X. T. Yan, Mrs. Y. H. Li, Mr. Y. Zhang, Mr. X. Z. Ren, Mr. J. H. Zhao, Mrs. J. Zhang, Mr. A. S. Goh, Mr. C. B. Wong, Mrs. H. Jiao, Miss F. Zheng, Miss G. H. Li, Dr. J. S. Pu for their friendship.

Mrs. M. E. Carden and all the staff from the Department for their kindness and administrative work.

Finally, my motherland, the People's Republic of China, and the British Council for providing financial support.

#### **SYNOPSIS**

The objective of this research is to advance computer vision techniques and their applications in the electronics manufacturing industry. The research has been carried out with specific reference to the design of automatic optical inspection (AOI) systems and their role in the manufacture of printed circuit boards (PCBs).

To achieve this objective, application areas of AOI systems in PCB manufacture have been examined. As a result, a requirement for enhanced performance characteristics has been identified and novel approaches and image processing algorithms have been evolved which can be used within next generation of AOI systems. The approaches are based on gaining an understanding of ways in which manufacturing information can be used to support AOI operations. Through providing information support, an AOI system has access to product models and associated information which can be used to enhance the execution of visual inspection tasks. Manufacturing systems integration, or more accurately controlled access to electronic information, is the key to the approaches. Also in the thesis methods are proposed to achieve the flexible integration of AOI systems (and computer vision systems in general) within their host PCB manufacturing environment. Furthermore, potential applications of information supported AOI systems at various stages of PCB manufacturing have been studied.

It is envisaged that more efficient and cost-effective applications of AOI can be attained through adopting the flexible integration methods proposed, since AOI-generated information can now be accessed and utilized by other processes.

# **CONTENTS**

| Declaration |                         |                                                                                                                                                                        | i                                      |  |

|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Acknowledg  | ements                  |                                                                                                                                                                        | ii                                     |  |

| Synopsis    |                         |                                                                                                                                                                        | iii                                    |  |

| Contents    |                         |                                                                                                                                                                        | iv                                     |  |

| Chapter 1   | Introduction            | en.                                                                                                                                                                    | 1                                      |  |

| Chapter 2   | Literature              | Survey                                                                                                                                                                 | 3                                      |  |

| 2.1         | Introduction            | 1                                                                                                                                                                      | 3                                      |  |

| 2.2         | 2.2.1 Uses              | Computers in Manufacturing Industries s of Computers in Manufacturing Industries Need for Integrating Manufacturing Systems                                            | 3<br>3<br>5                            |  |

| 2.3         | Modelling o             | of Manufacturing Systems                                                                                                                                               | 6                                      |  |

| 2.4         | Computer In             | Computer Integrated Manufacture                                                                                                                                        |                                        |  |

| 2.5         |                         | d Tools for Manufacturing Systems Integration working and Communication Standards ISO/OSI Standards and the ISO/OSI Reference Model IEEE 802.X Standards MAP/TOP SNA   | 12<br>12<br>13<br>14<br>14             |  |

|             | A.<br>B.                | Information Handling Information Administration Systems Standards for Information Representation IGES PDES and STEP EDIF Eufacturing Systems Integration Architectures | 19<br>19<br>21<br>22<br>22<br>24<br>24 |  |

|             | A.<br>B.                | Three architectures ESPRIT CIM-OSA                                                                                                                                     | 24<br>28                               |  |

| 2.6         | Manufactur<br>2.6.1 The | Vision Technology and Its Applications in ing Building Elements of a Computer Vision System Image Processing and Analysis Techniques Preprocessing Segmentation        | 28<br>31<br>32<br>35<br>37             |  |

|                | C. Feature Extraction                                            | 41       |

|----------------|------------------------------------------------------------------|----------|

|                | D. Recognition                                                   | 41       |

|                | 2.6.3 3-D Computer Vision Techniques                             | 43       |

|                | 2.6.4 Industrial Applications of Computer Vision                 | 43       |

|                | A. Inspection                                                    | 44       |

|                | B. Guidance                                                      | 44       |

| 2.7            | Applications of Computer Vision in Electronics                   |          |

|                | Manufacturing Industry                                           | 45       |

|                | 2.7.1 Automatic Optical Inspection                               | 46       |

|                | 2.7.2 AOI Techniques and Their Applications in PCB               | 40       |

|                | Product Inspection                                               | 46       |

|                | A. Reference Based Techniques  B. Non-Reference Based Techniques | 48<br>49 |

|                | <b>1</b> · · ·                                                   |          |

| 2.8            | Summary                                                          | 50       |

| Chapter 3      | The Requirement for Integrated Machine Vision                    |          |

|                | Application in PCB Manufacture                                   | 53       |

| 3.1            | Introduction                                                     | 53       |

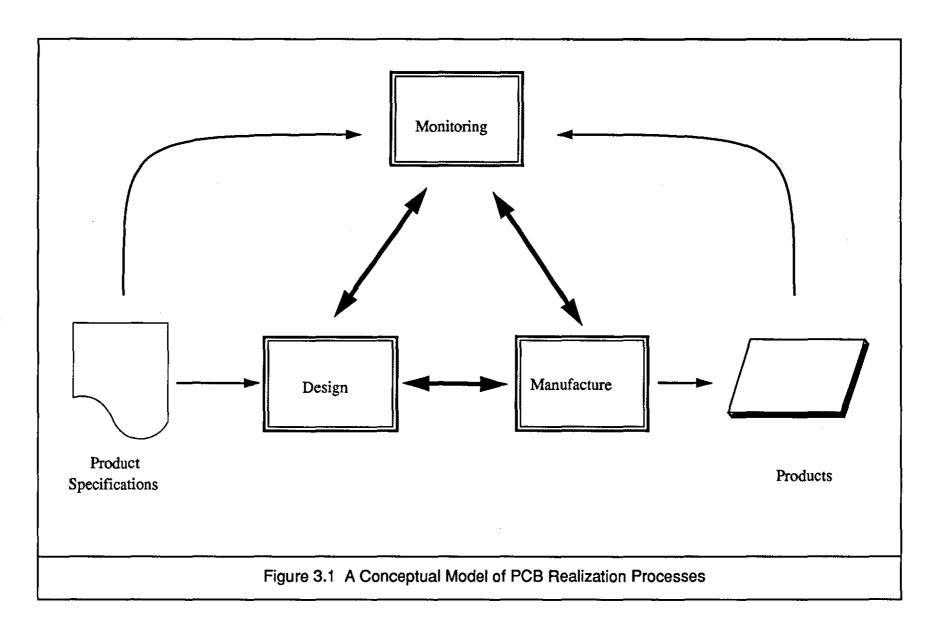

| 3.2            | A Conceptual Model of PCB Manufacturing Industry                 | 55       |

|                | 3.2.1 Design                                                     | 55       |

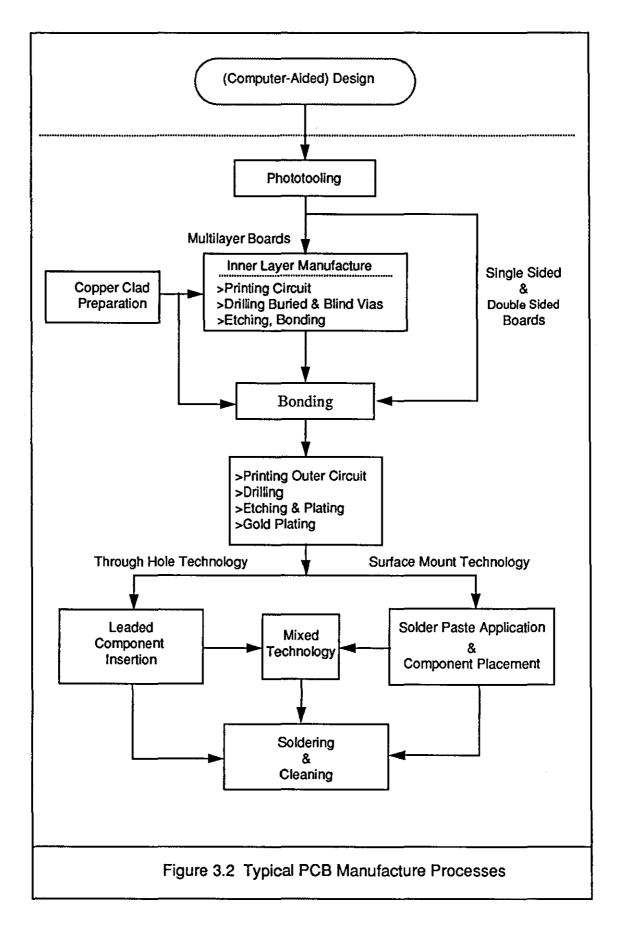

|                | 3.2.2 Manufacture                                                | 57       |

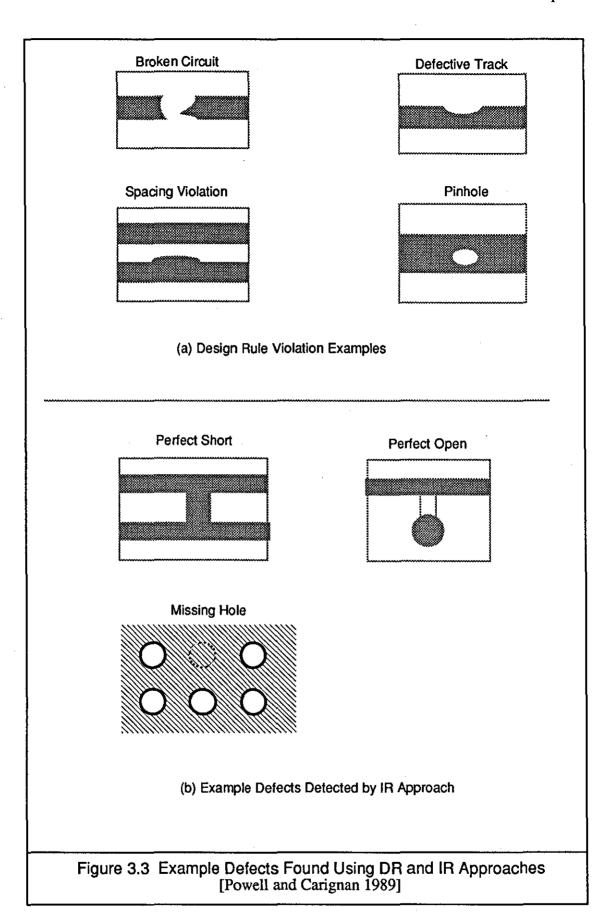

|                | 3.2.3 Monitoring                                                 | 59       |

| 3.3            | Automatic Optical Inspection and Its Role in PCB                 |          |

|                | Manufacturing                                                    | 60       |

|                | 3.3.1 A Comparison between AOI and ATE                           | 62       |

| 3.4            | Present Generation AOI                                           | 63       |

|                | 3.4.1 Limitations of Present Generation AOI systems              | 66       |

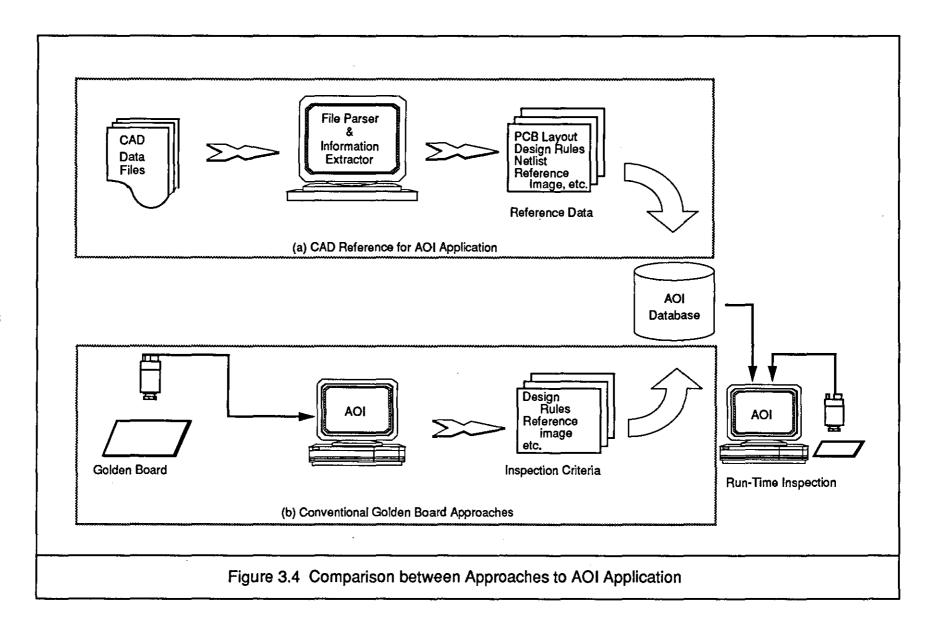

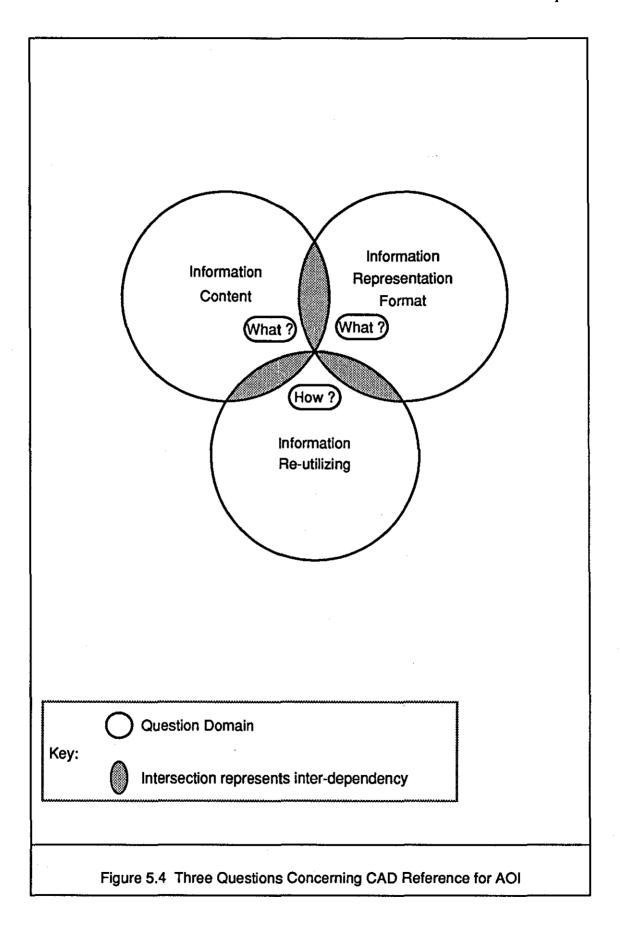

| 3.5            | CAD Reference for AOI                                            | 67       |

|                | 3.5.1 Benefits of CAD Data Reference                             | 69       |

|                | 3.5.2 Problems Associated with CAD Reference                     | 70       |

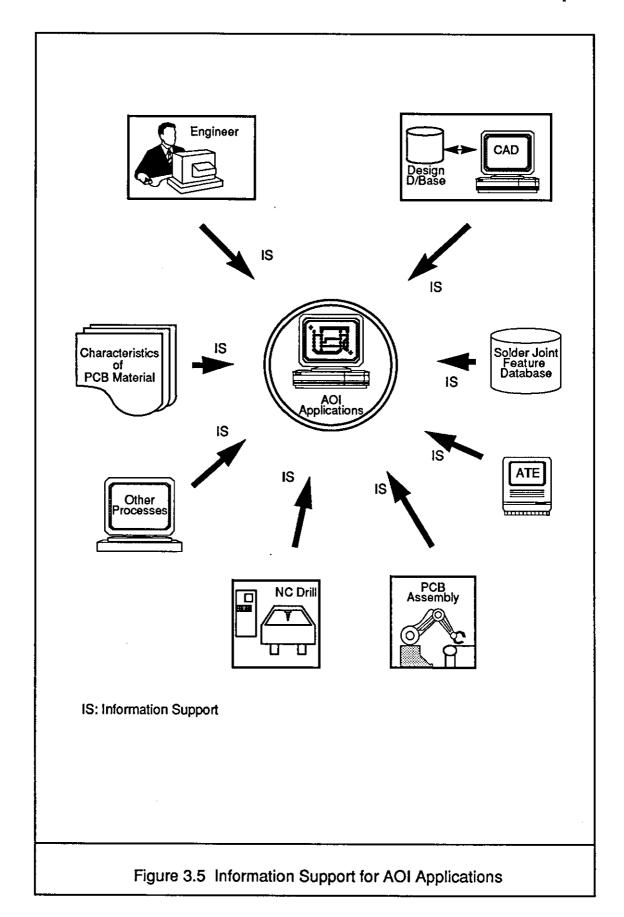

| 3.6            | Information Support for AOI                                      | 71       |

|                | 3.6.1 Specifications of a New Generation AOI system              | 72       |

| 3.7            | Summary                                                          | 74       |

| Chapter 4      | The Integration of Machine Vision and Robotic Systems            | 76       |

| 4.1            | Introduction                                                     | 76       |

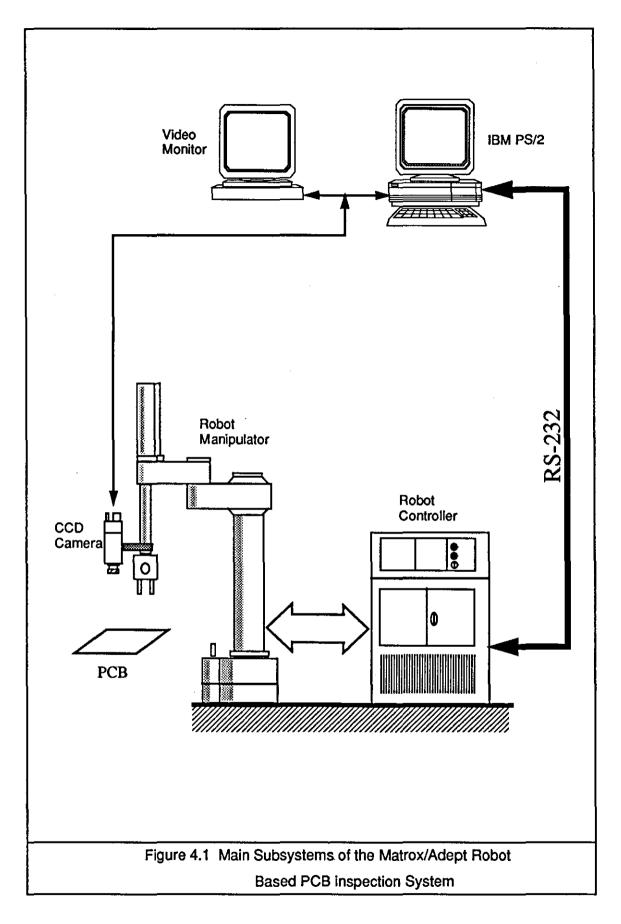

| 4.2            | Description of the Facilities Used                               | 77       |

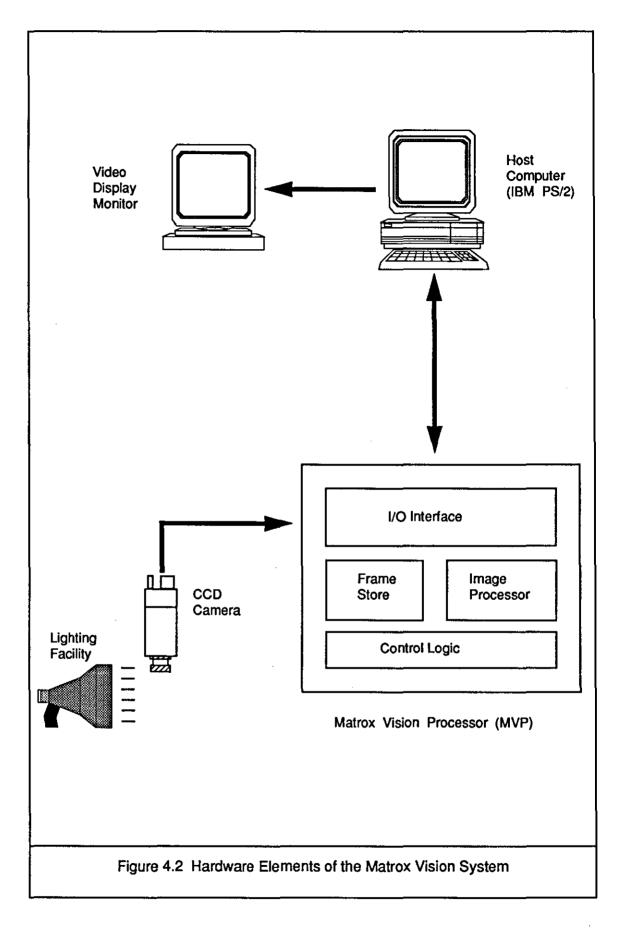

| -3 <b>, 26</b> | 4.2.1 The Matrox Machine Vision System (MVS)                     | 77       |

|           | 4.2.2 The AdeptOne Robot Manipulator System                                                                                                                                                                                                                       | 80                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.3       | Vision-Robot Communication 4.3.1 Overview 4.3.2 Specific Constraints 4.3.3 Description of the Approach Adopted 4.3.4 The Information Requirements of the Two Systems A. PCB Inspection B. Vision Guidance for Robot 4.3.5 Information Representation Format (IRF) | 81<br>82<br>83<br>85<br>85<br>86<br>88 |

| 4.4       | An Example Application of the Integrated System                                                                                                                                                                                                                   | 91                                     |

| 4.5       | Discussions                                                                                                                                                                                                                                                       | 94                                     |

| 4.6       | Summary                                                                                                                                                                                                                                                           | 97                                     |

| Chapter 5 | Using CAD Information to Support AOI Operations                                                                                                                                                                                                                   | 98                                     |

| 5.1       | Introduction                                                                                                                                                                                                                                                      | 98                                     |

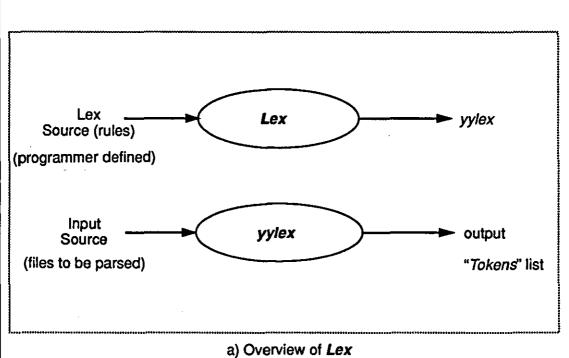

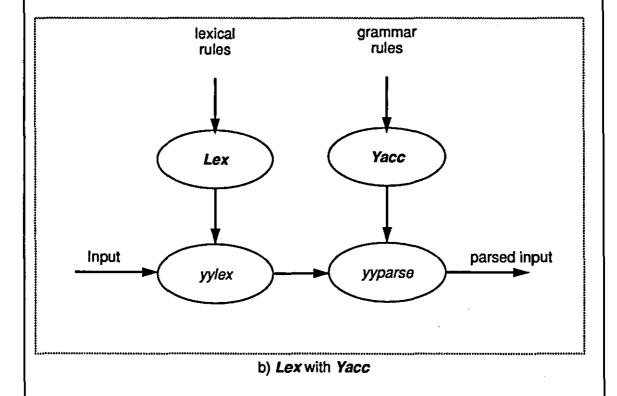

| 5.2       | Systems/Tools Utilized 5.2.1 The P-CAD System 5.2.2 The Matrox Machine Vision System 5.2.3 SUN Workstation and the LEX/YACC Tools                                                                                                                                 | 99<br>101<br>103<br>104                |

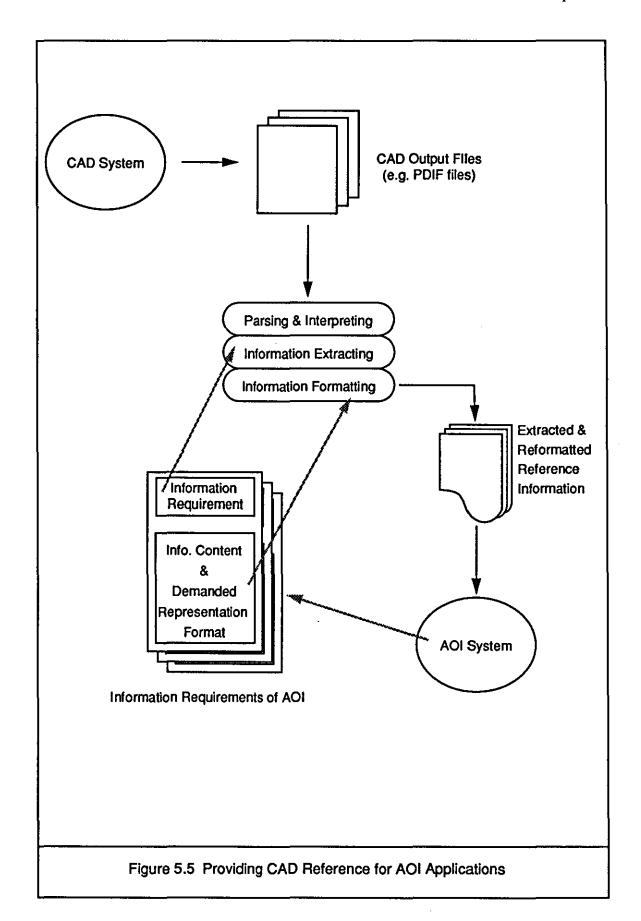

| 5.3       | General Issues of CAD Information Support for AOI Applications                                                                                                                                                                                                    | 106                                    |

| 5.4       | Designing of a Software Information Generator Using LEX/YACC                                                                                                                                                                                                      | 110                                    |

| 5.5       | The Utilization of the CAD Information                                                                                                                                                                                                                            | 111                                    |

| 5.6       | Discussions                                                                                                                                                                                                                                                       | 116                                    |

| 5.7       | Summary                                                                                                                                                                                                                                                           | 118                                    |

| Chapter 6 | A Product Model Based Approach to Integrating Vision Systems in the CIM of PCB                                                                                                                                                                                    | 120                                    |

| 6.1       | Introduction                                                                                                                                                                                                                                                      | 120                                    |

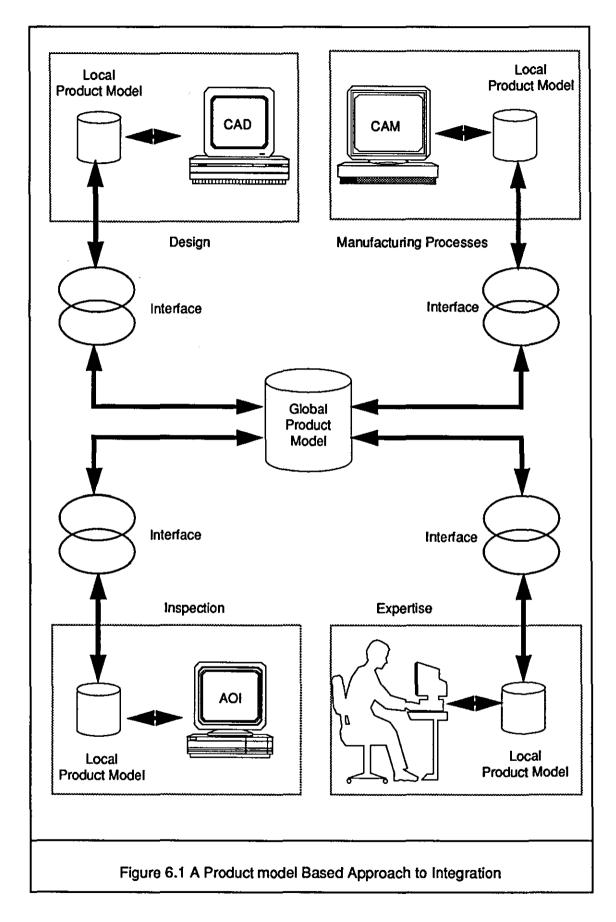

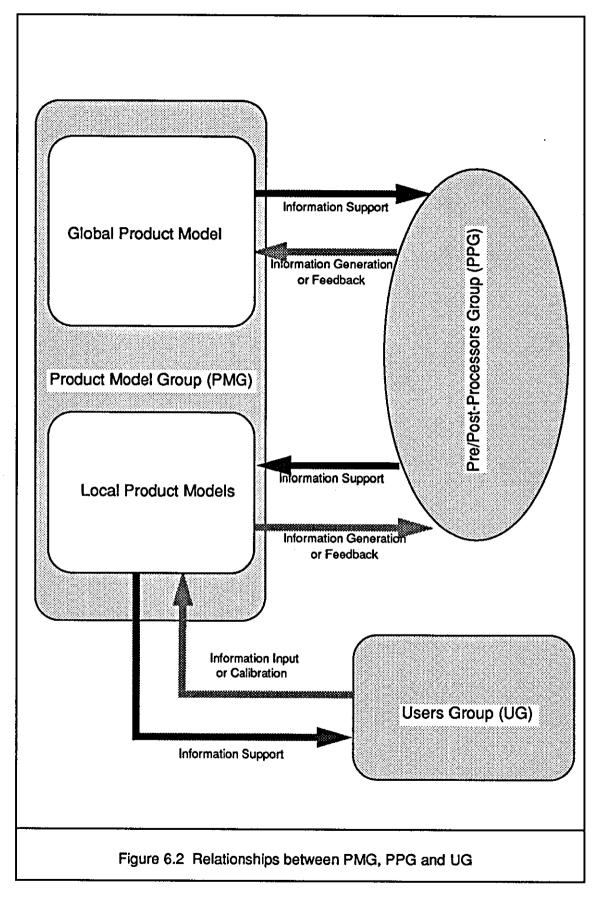

| 6.2       | Notion Relating to a Product Model Based Approach 6.2.1 Use of Terminology 6.2.2 A Proposed Product Model Based Approach                                                                                                                                          | 121<br>121<br>124                      |

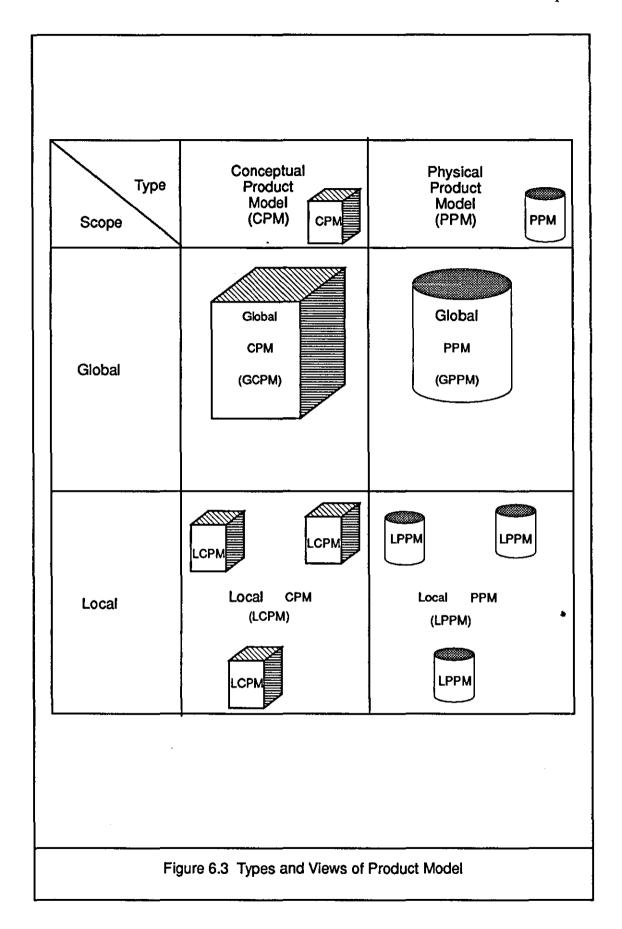

| 6.3       | Some Issues Relating to Product Model  6.3.1 Two Types of PCB Product Models  A) The Conceptual Product Model  B) The Physical Product Model                                                                                                                      | 128<br>129<br>129                      |

|           | 6.3.2           | Two V<br>A) | Views of the Product Models  Global Conceptual and Physical Product                        | 132  |

|-----------|-----------------|-------------|--------------------------------------------------------------------------------------------|------|

|           |                 | •           | Models                                                                                     | 132  |

|           |                 | B)          | Local Conceptual and Physical Product Models                                               | 133  |

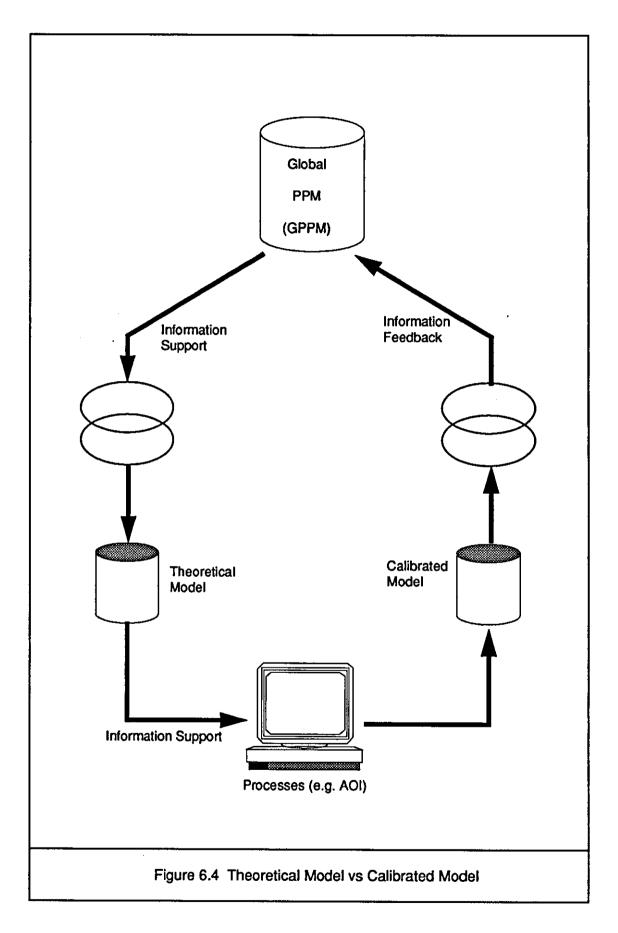

|           | 6.3.3           | Theore      | etical Model vs Calibrated Model                                                           | 134  |

| 6.4       | Pre- ar         | nd Post-    | processors                                                                                 | 136  |

|           | 6.4.1           | Pre-pr      | ocessors                                                                                   | 137  |

|           | 6.4.2           | Post-p      | rocessors                                                                                  | 137  |

| 6.5       | Summ            | ary         |                                                                                            | 138  |

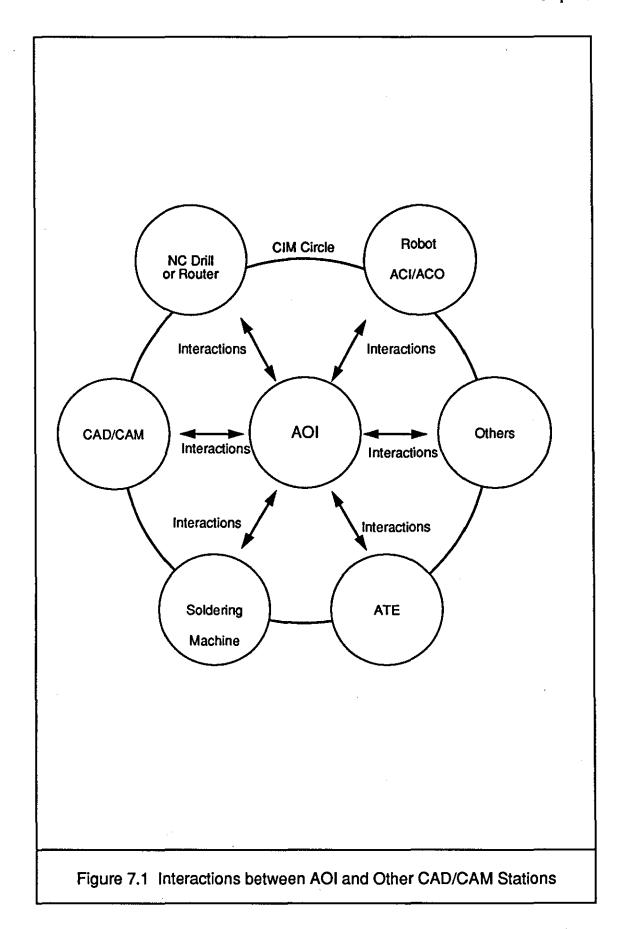

| Chapter 7 | Sugge           | sted Ar     | chitectural Design of an AOI System                                                        | 139  |

| 7.1       | Introd          | uction 1    |                                                                                            | 139  |

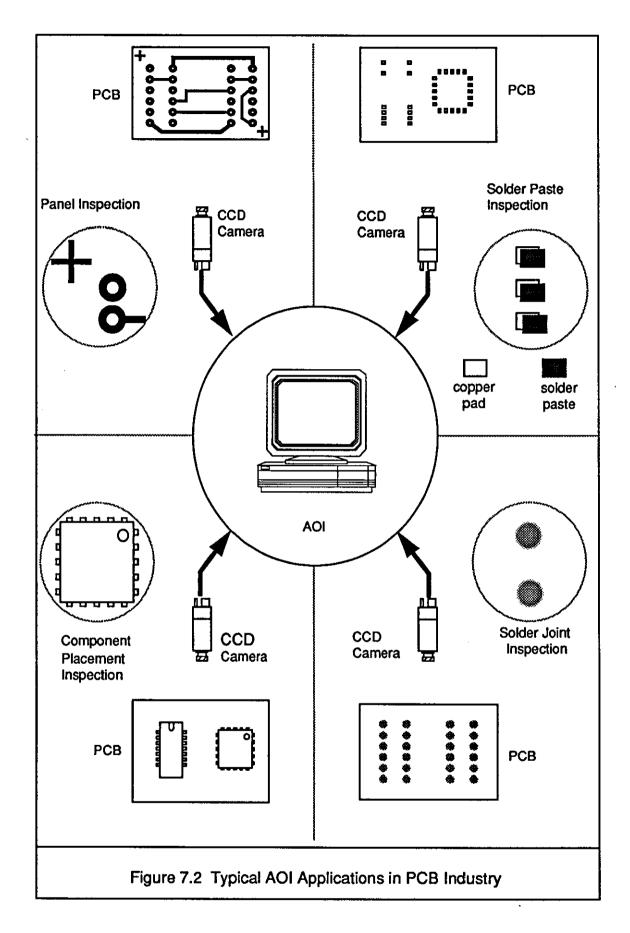

| 7.2       | Charac<br>7.2.1 | Furthe      | g Typical AOI Applications in PCB Manufacture er Examination of AOI Applications and Their | 141  |

|           |                 | Gener       | ic Characteristics                                                                         | 144  |

|           |                 | A.          | Panel Inspection (PI)                                                                      | 144  |

|           |                 | В.          | Solder Paste Application Inspection (SPAI)                                                 | 145  |

|           |                 | C.          | Component Placement Inspection (CPI)                                                       | 147  |

|           |                 | D.          | Solder Joint Inspection (SJI)                                                              | 149  |

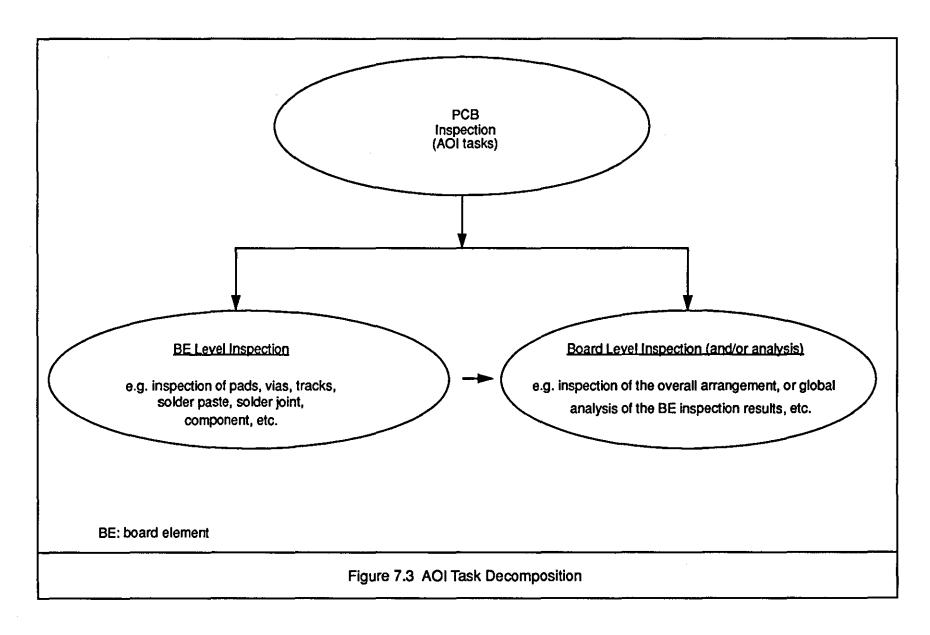

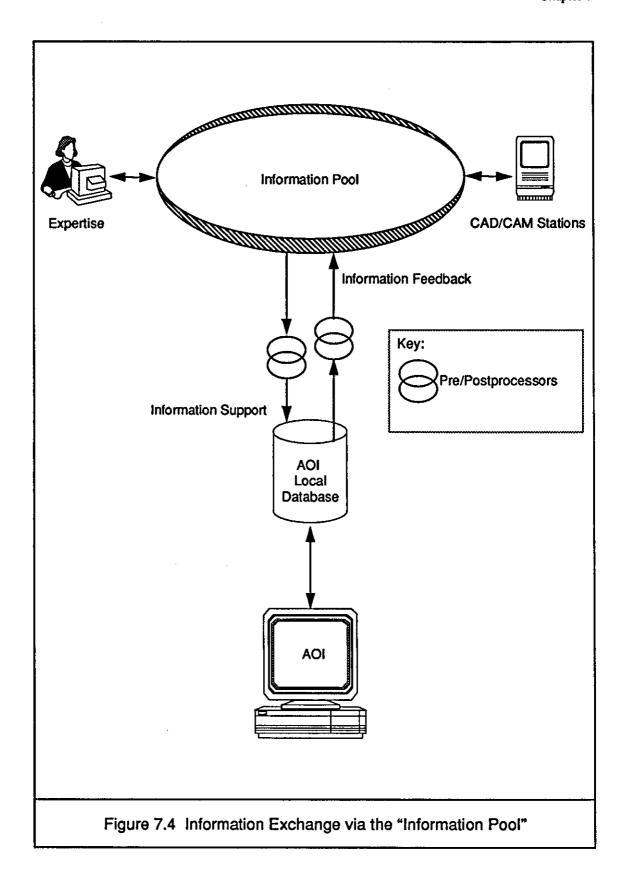

| 7.3       | AOI T           | ask Dec     | composition                                                                                | 152  |

|           | 7.3.1           | Decon       | nposing General AOI Tasks                                                                  | 153  |

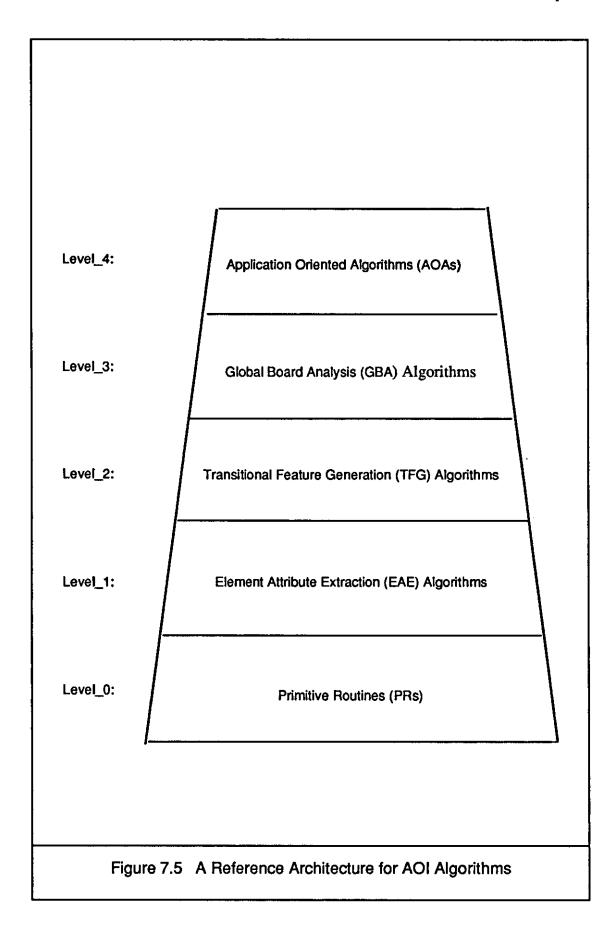

| 7.4       | Hierar          | chical I    | Design of AOI Algorithms                                                                   | 157  |

|           | 7.4.1           | The pr      | oposed Hierarchical Reference Architecture                                                 | 157  |

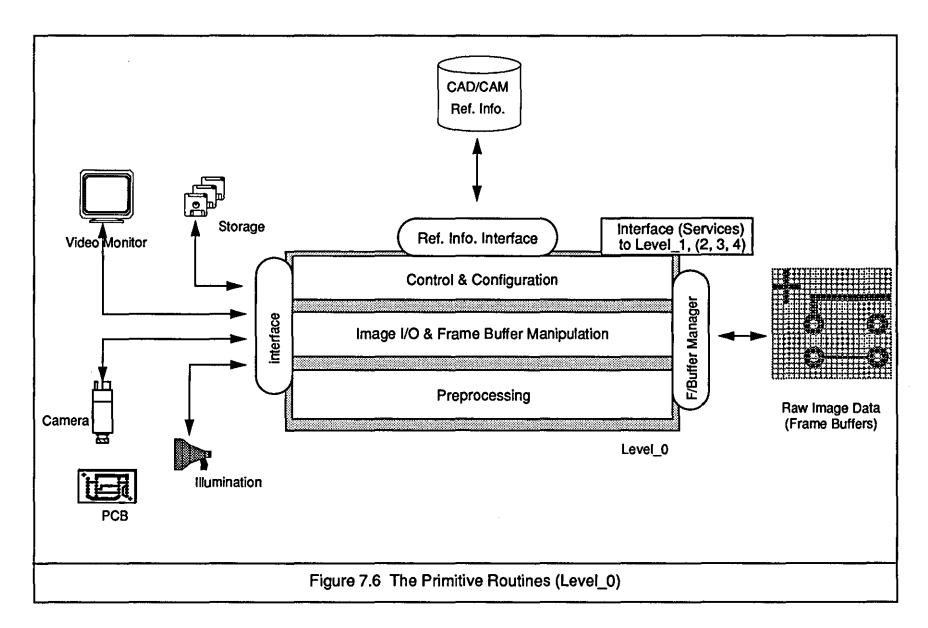

|           |                 | A.          | Level_0: The Primitive Routines (PRs)                                                      | 160  |

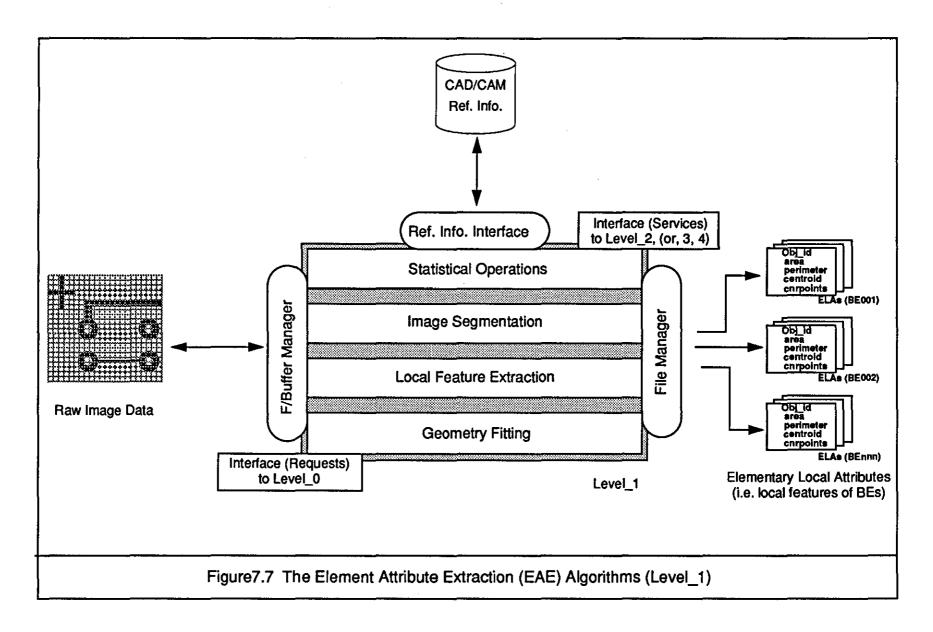

|           | •               | В.          | Level_1: Element Attribute Extraction (EAE)                                                |      |

|           |                 | _           | Algorithms                                                                                 | 162  |

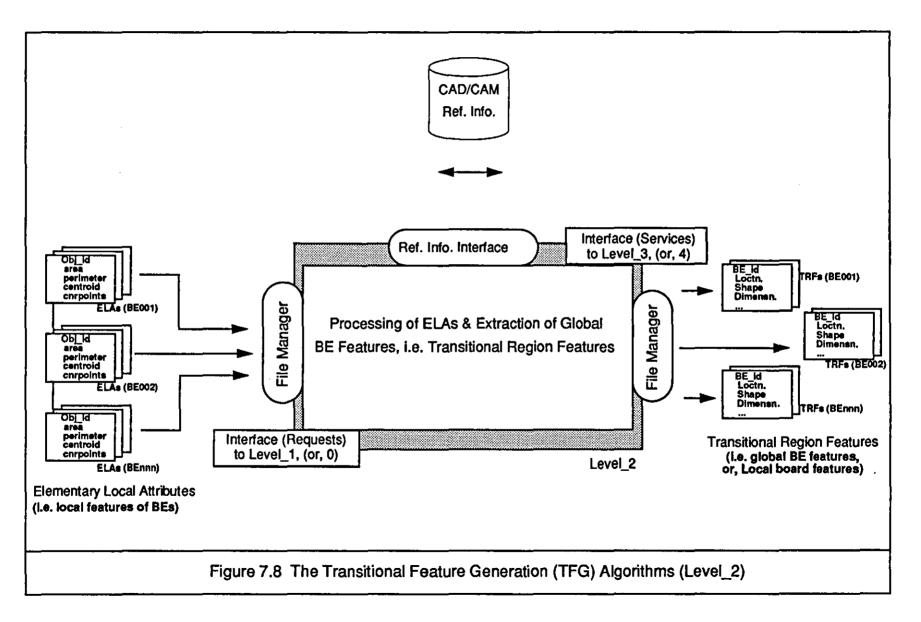

|           |                 | C.          | Level_2: Transitional Feature Generation                                                   |      |

|           |                 | -           | (TFG) Algorithms                                                                           | 164  |

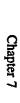

|           |                 | D.          | Level_3: Global Board Analysis (GBA)                                                       | 1.00 |

|           | •               | 177         | Algorithms                                                                                 | 167  |

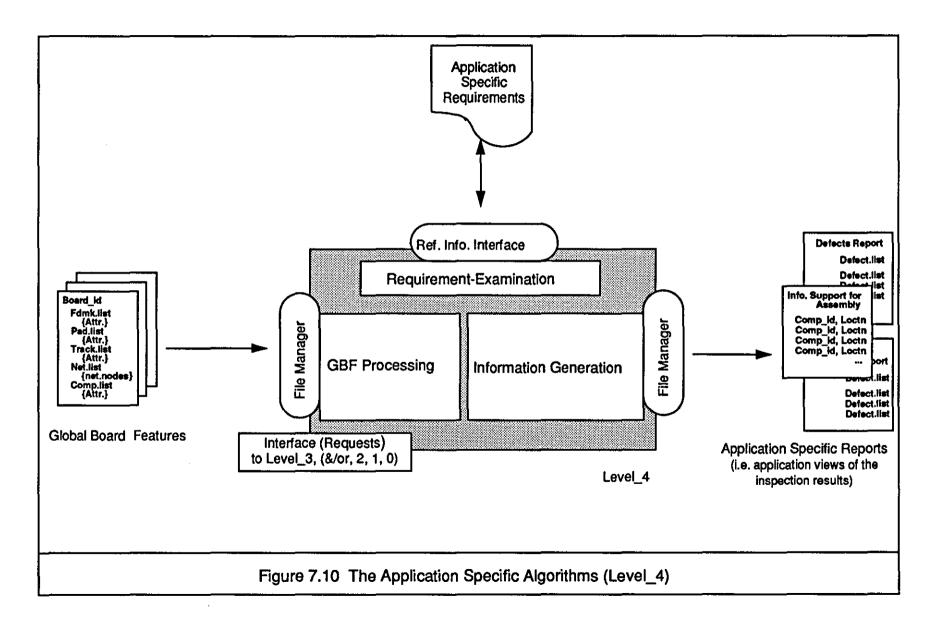

|           |                 | E.          | Level_4: Application Oriented Algorithms                                                   | 1.00 |

|           |                 |             | (AOAs)                                                                                     | 169  |

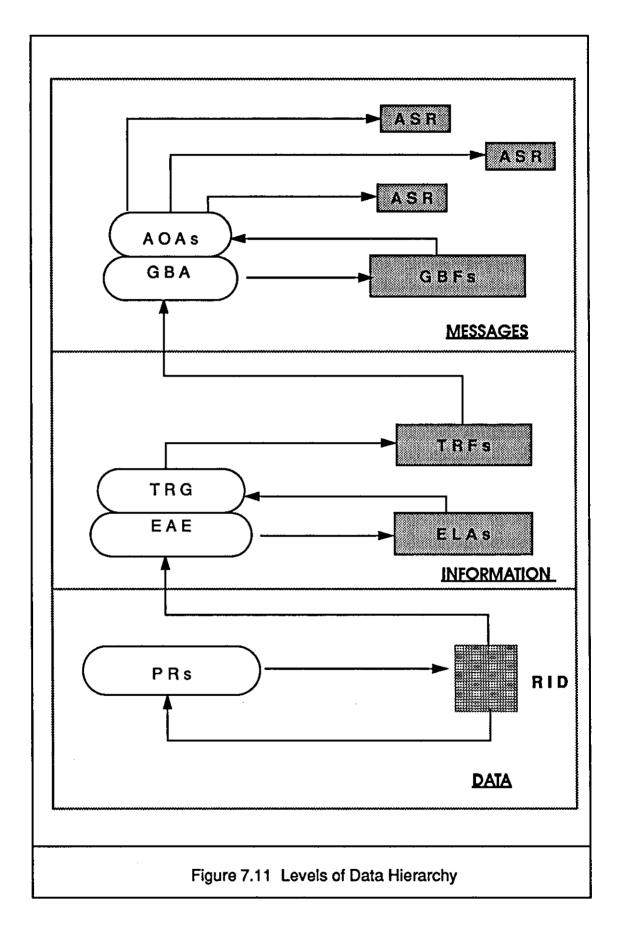

| 7.5       | The D           |             | w Hierarchy                                                                                | 171  |

|           |                 | <b>A</b> .  | The Raw Image Data (RID)                                                                   | 171  |

|           | ,               | В.          | The Elementary Local Attributes (ELAs) and                                                 | 1=0  |

|           |                 |             | the Transitional Region Features (TRFs)                                                    | 172  |

|           |                 | C.          | Global Board Features (GBFs) and Application-                                              | 172  |

|           | _               |             | Specific Reports (ASRs)                                                                    | 173  |

| 7.6       | Summ            | iary        |                                                                                            | 175  |

| Chapter 8  | Description Of A Prototype Information Supported  Machine Vision System                                                                                                                                                                                                              | 177                                    |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| 8.1        | Introduction                                                                                                                                                                                                                                                                         |                                        |  |

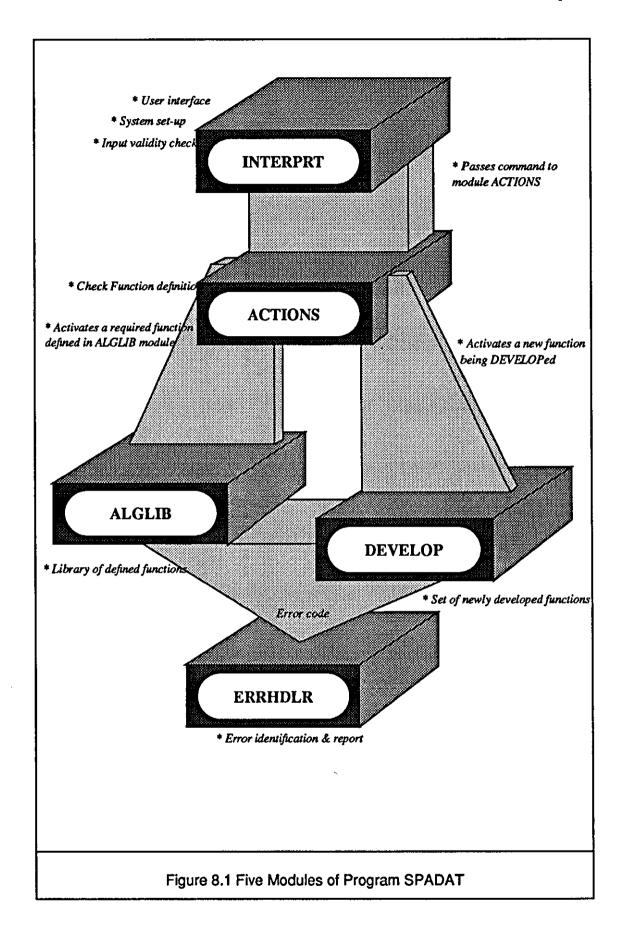

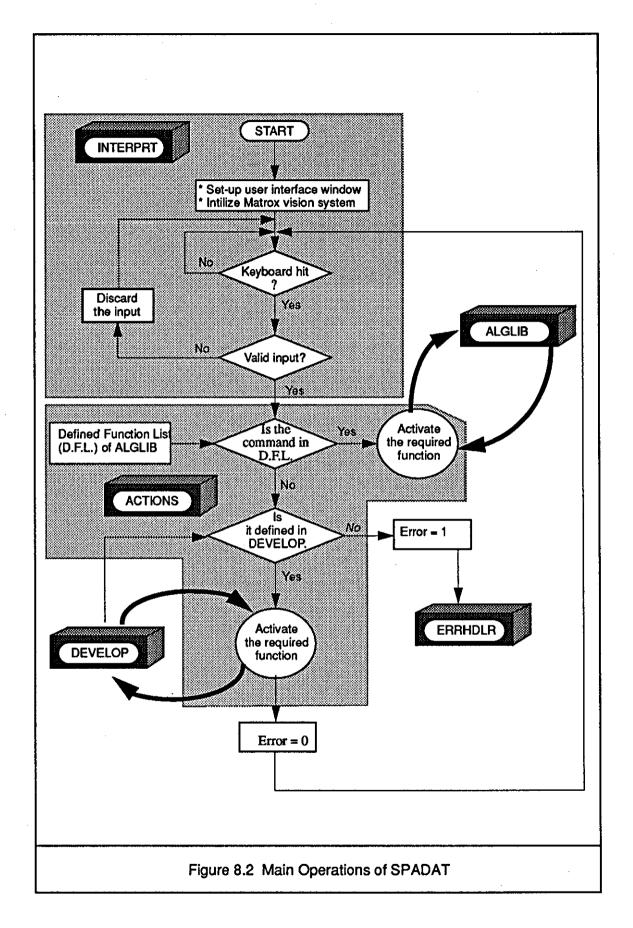

| 8.2        | Description of the Software Platform SPADAT                                                                                                                                                                                                                                          |                                        |  |

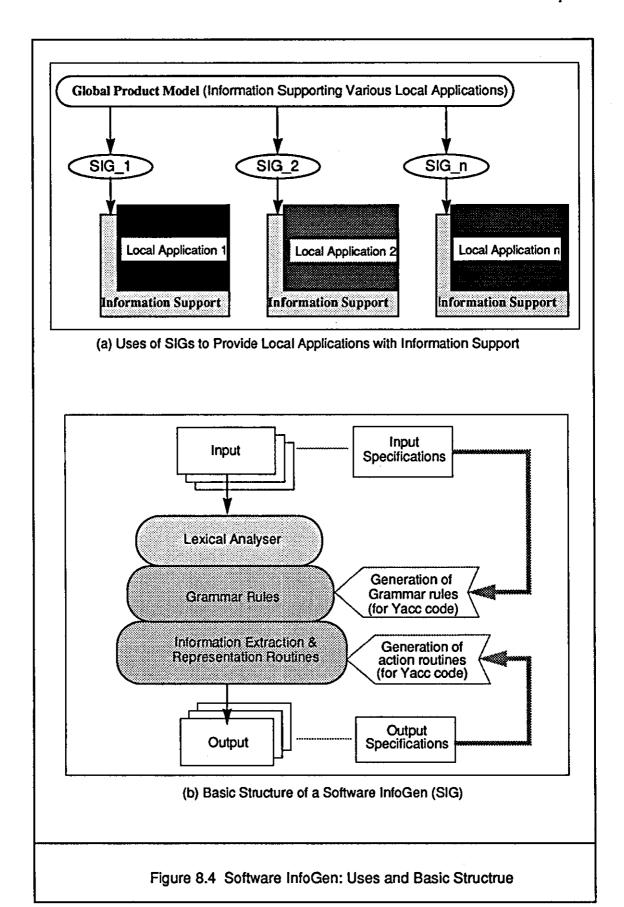

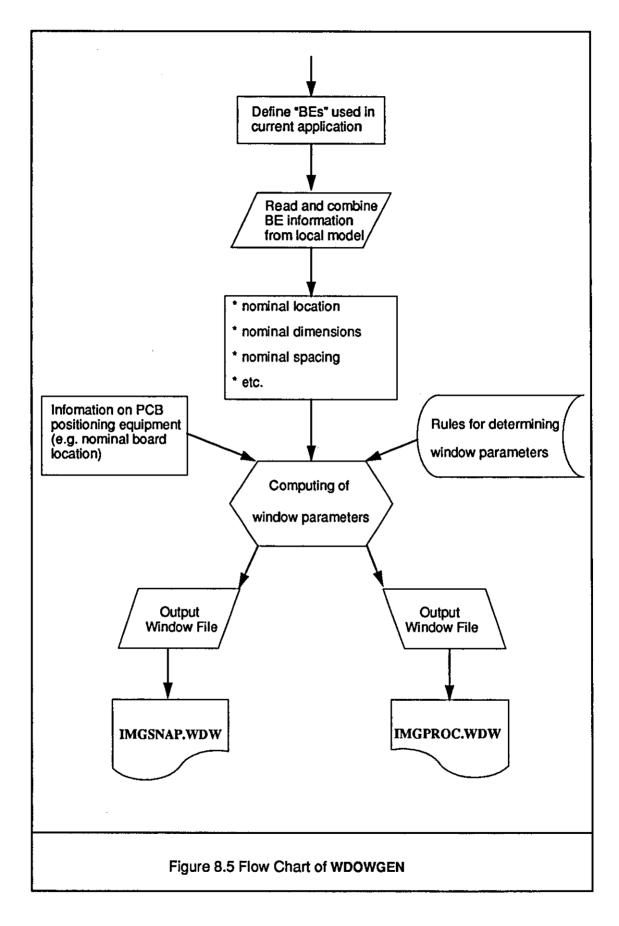

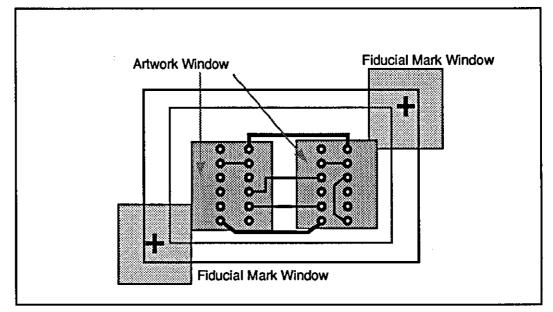

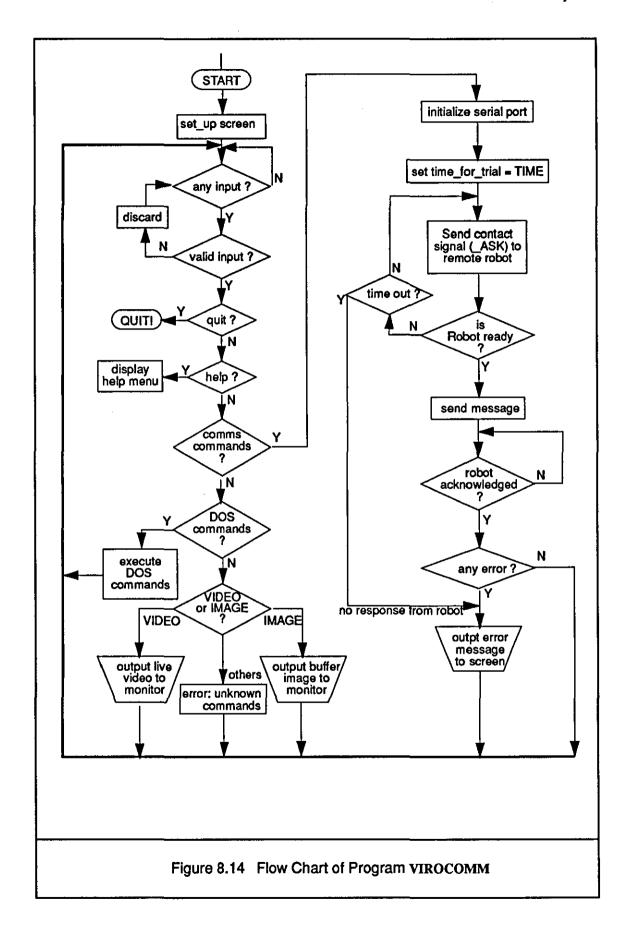

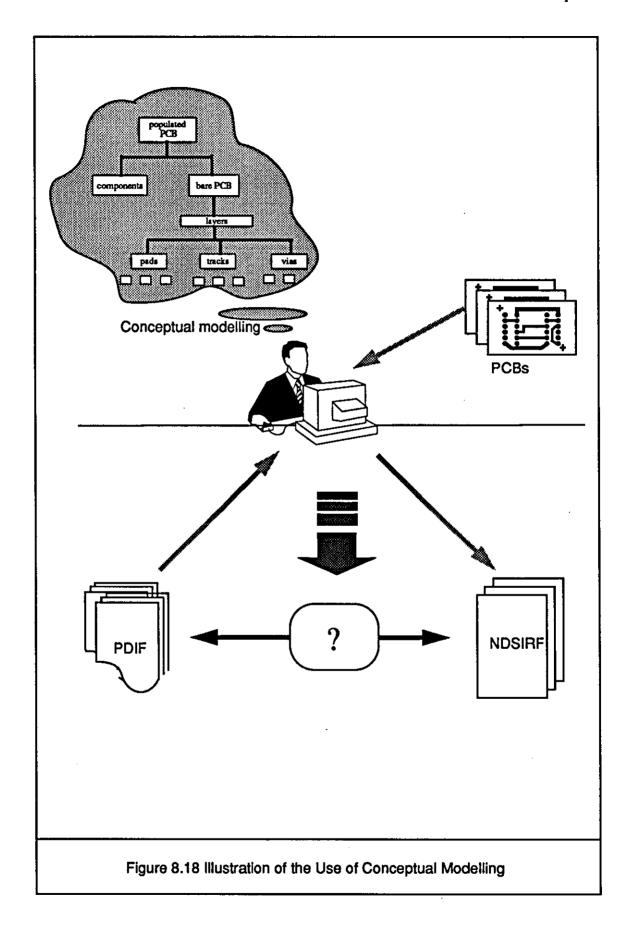

| 8.3        | Towards Achieving Flexible Information Support for AOI 8.3.1 Implementing a Global Physical Product Model 8.3.2 Software Development A. Software to Extract Global Information from a CAD Database B. Software to Provide Information Support for Local Applications                 | 181<br>183<br>185<br>185               |  |

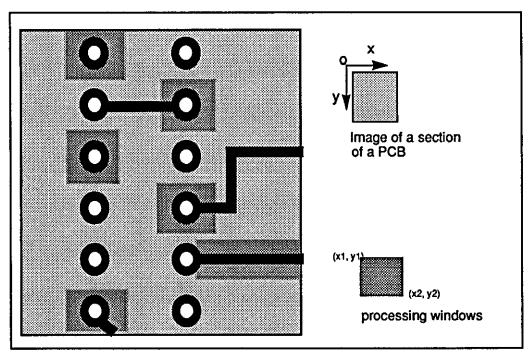

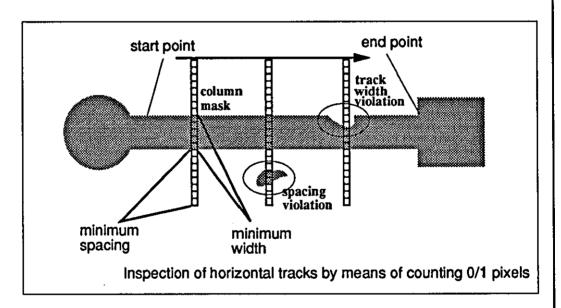

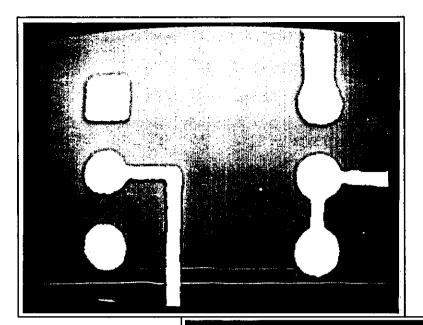

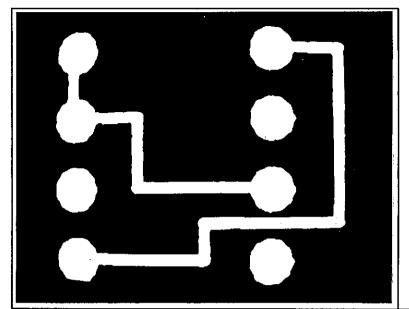

| 8.4        | Implementation of the AOI Reference Architecture 8.4.1. The Primitive Routines 8.4.2. The Element Attribute Extraction (EAE) and Transitional Feature Generation (TFG) Algorithms 8.4.3 The Global Board Analysis (GBA) Algorithms and Application Oriented Algorithms (AOAs)        | 187<br>189<br>194<br>202               |  |

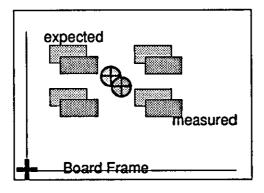

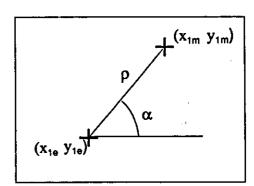

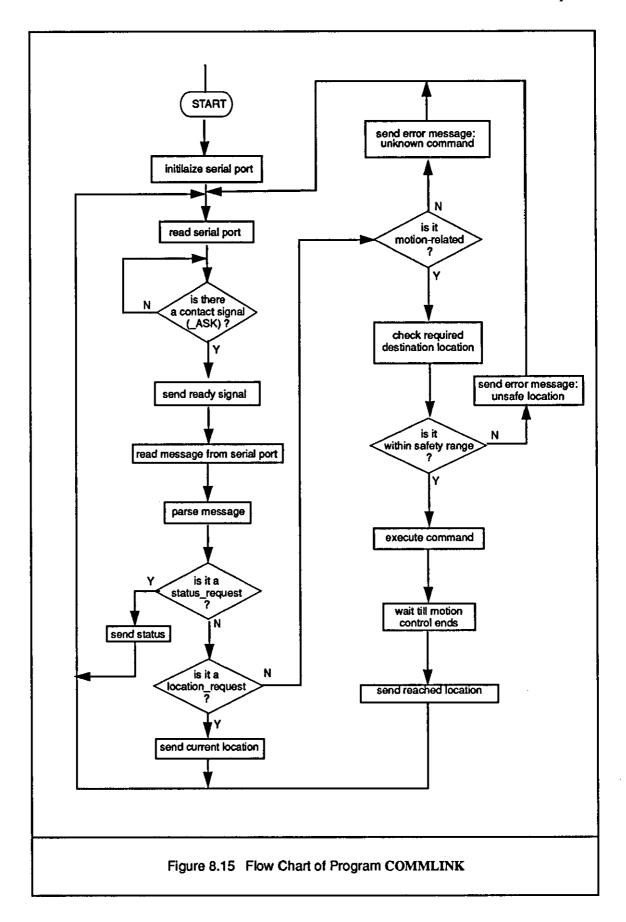

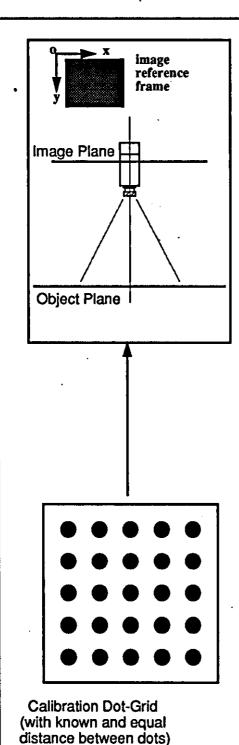

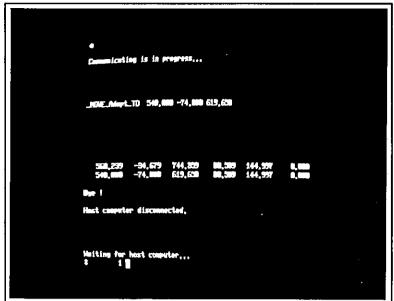

| 8.5        | The Vision-Robot Integrated System and its Calibration 8.5.1 The Communication Link for the Vision-Robot System 8.5.2 Calibration of the Vision-Robot System                                                                                                                         | 206<br>206<br>209                      |  |

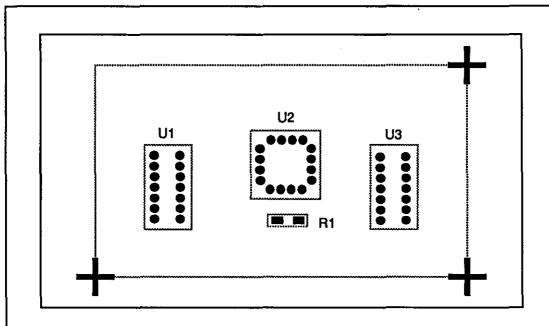

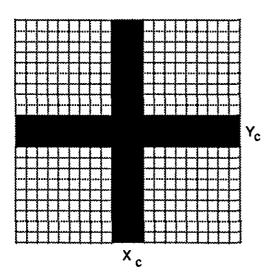

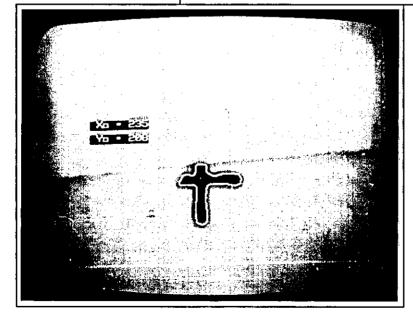

| 8.6        | Experimental Results: A Case Study 8.6.1 Introduction 8.6.2 System Configuration 8.6.3 Inspection/Location of Fiducial Marks 8.6.4 Inspection of Pads 8.6.5 Problems of Noise in the Inspection Process 8.6.6 The Role of the Proposed AOI Reference Architecture in This Case Study | 211<br>211<br>213<br>213<br>215<br>216 |  |

| 8.7        | Summary                                                                                                                                                                                                                                                                              | 218                                    |  |

| Chapter 9  | Conclusions and Recommendations                                                                                                                                                                                                                                                      | 229                                    |  |

| 9.1        | Conclusions and Contributions to Knowledge                                                                                                                                                                                                                                           | 229                                    |  |

| 9.2        | Contribution to Knowledge 9.2.1 The Product Model Based Approach 9.2.2 A Proposed AOI Reference Architecture and Its Partial Implementation                                                                                                                                          | 230<br>230<br>236                      |  |

| 9.3        | Recommendations for Future Work                                                                                                                                                                                                                                                      | 240                                    |  |

| References |                                                                                                                                                                                                                                                                                      | 242                                    |  |

| Appendix A   | List of Routines Implemented                  | 262 |

|--------------|-----------------------------------------------|-----|

| Appendix B.1 | An Example of PDIF Files                      | 266 |

| Appendix B.2 | YACC Code for Software Information Generators | 279 |

**CONTENTS**

# Chapter 1

# Introduction

This thesis is concerned with advancing studies and applications of machine vision technology/systems in PCB (printed circuit board) manufacture. More specifically, it is concerned with evolving methods of achieving better AOI (automatic optical inspection) performance by means of providing information support through flexibly integrating the operations of AOI systems with those of other relevant product realisation processes/systems involved at various stages of PCB manufacture.

A prerequisite of research in this field requires a good understanding of background concepts and available knowledge in the areas of systems integration and computer vision technology. Thus chapter 2 reviews literature on computers applications in manufacture and more specifically computer vision techniques. Further detailed discussions on the potential role and application areas of machine vision systems in PCB product inspection is discussed in chapter 3. A growing range of applications of AOI systems, especially at critical processing stages in PCB manufacturing, have been identified which are important to the success and survival of modern PCB manufacturing organisations in markets where competition is fierce. Information supported AOI is considered by the author to be the right way forward.

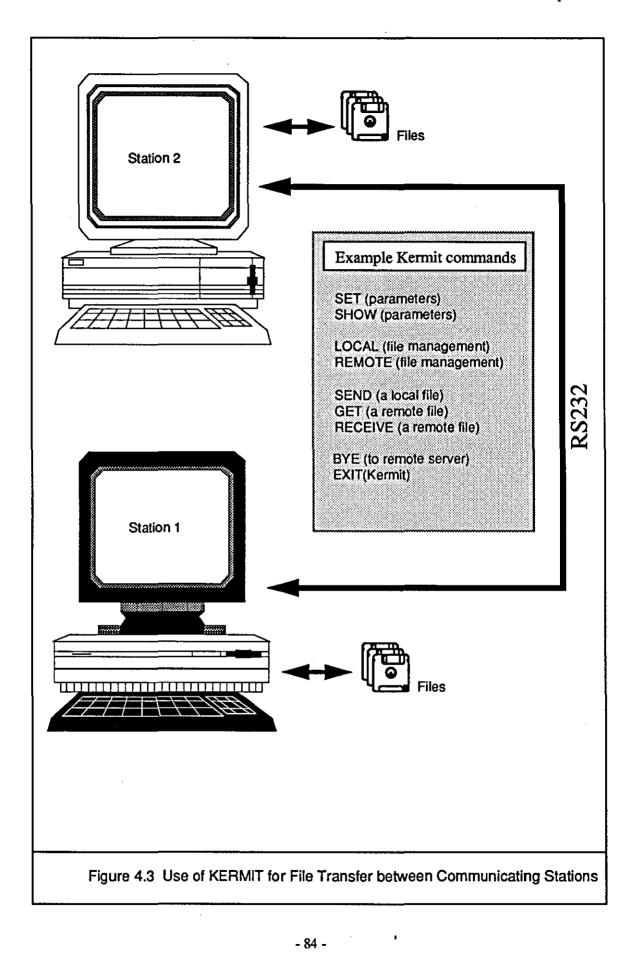

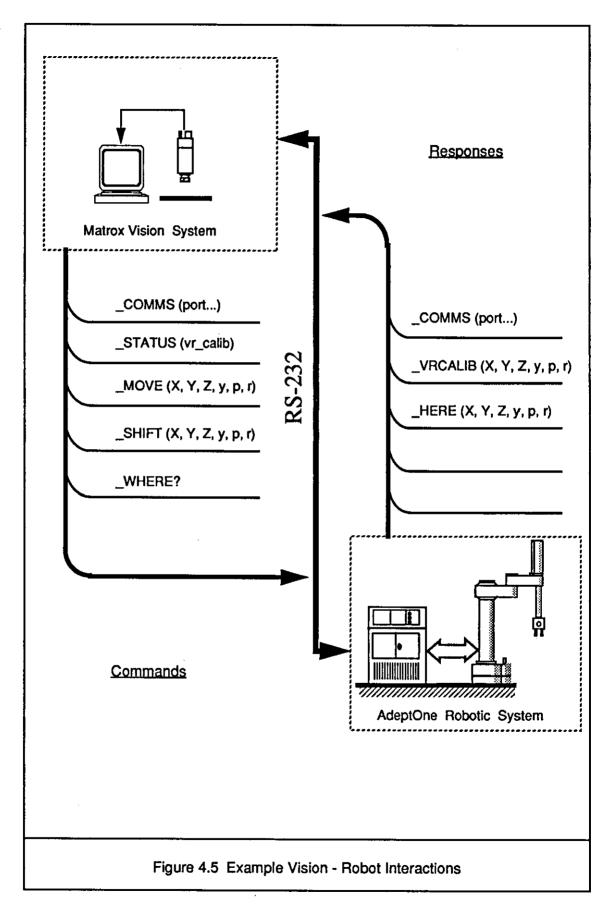

Chapter 4 describes the author's study of interaction between a Matrox vision system and an AdeptOne robot manipulator system, and subsequent integrated operations of the two systems. The approach used to integrating these two systems is of a bespoke nature, i.e. customized communication protocols are deployed for the data and information interchange between the two systems. In addition, custom designed data structure and information representational format was specified which satisfies requirements of the two end systems.

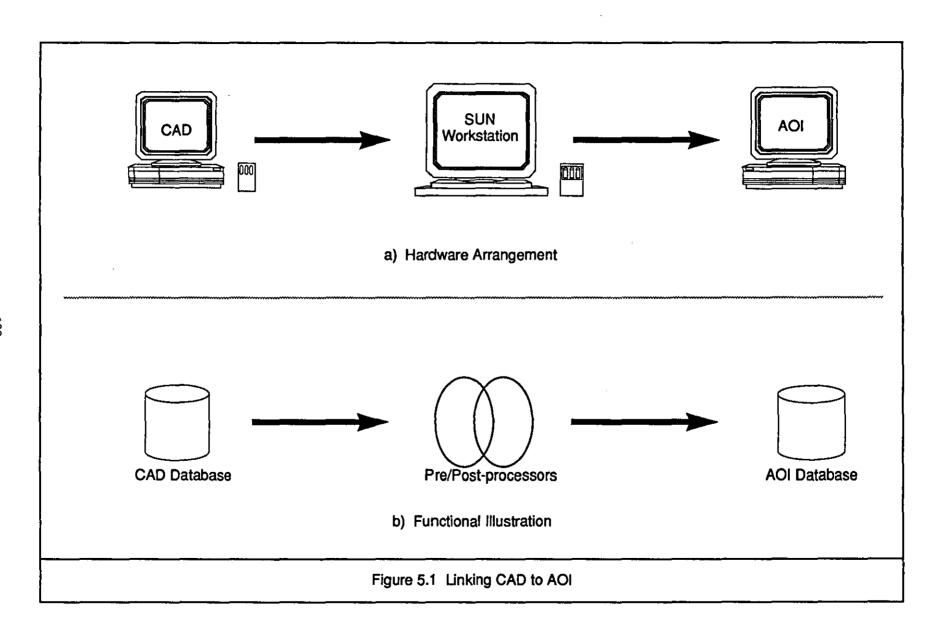

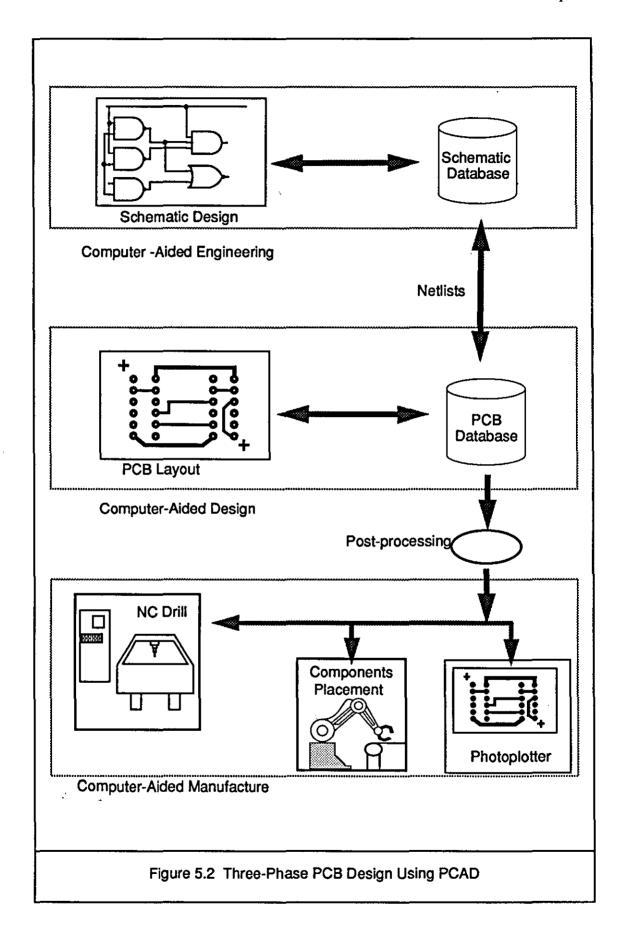

Chapter 5 presents the author's work of integrating a CAD (computer aided design) system and a vision machine. The main issue addressed is the re-utilisation by an AOI system of CAD generated reference information during inspection of PCB products. Other issues such as information parsing and translating are considered and recommendations made in regard to the extraction of suitable information. Thus a methodology is proposed by the author for reusing CAD reference data to support AOI applications which may be an important step forward towards achieving full information supported AOI application in the domain of PCB manufacture.

Chapter 6 describes a proposal of a product model based approach to achieving flexible integration of AOI systems within the wider computer integrated manufacturing (CIM) environment. Here, product models are considered as a means of providing a comprehensive product definition and of representing manufacturing information which can be used to support many manufacturing operations; including product inspection using AOI systems.

Chapter 7 proposes an architectural framework which can be used to structure the design and implementation of software algorithms for building the next generation AOI systems that can make better use of information available from CAD/CAM (computer aided design/manufacture) systems. The design focus comes from aiming to address the question, "given the availability of CAD/CAM created and other product-realization-related information, how should AOI systems be structured to make the best use of manufacturing information which can be used to support its operations".

Finally, chapter 8 describes a prototype software implementation of the suggested AOI system reference architecture and the proposed product model based approach to system integration. This is followed by concluding remarks in chapter 9 which outlines the major conclusions drawn from this research, the contributions to knowledge made and recommendations for future work.

# Chapter 2

# **Literature Survey**

#### 2.1 Introduction

The literature to be reviewed in this chapter is divided up into two major parts. The first part reviews literature on the broad issue of computer applications in manufacturing: including computer based tools and methods of achieving systems integration. This serves to set up the broad frame of reference wherein all computerized manufacturing devices including computer vision systems are hosted.

The second part of this chapter reviews background concepts and knowledge about computer vision including basic techniques for digital image processing. Emphasis is placed on automatic optical inspection (AOI), which represent one specific application area of computer vision technology.

#### 2.2 The Role of Computers in Manufacturing Industries

#### 2.2.1 Uses of Computers in Manufacturing Industries

Computers have now become invaluable tools which are increasingly used in the operations of many different types of manufacturing industries [Powers, Jr. 1987]. Examples of computer applications can be easily found; e.g. programmable logic controllers (PLCs) [Pessen and Hübl 1979], computerised numerical control (CNC) of machine tools [Koren 1983] [Seames 1990], computer-aided design

and manufacturing (CAD/CAM) [Groover and Zimmers Jr. 1984] [Besant and Lui 1986], robotics [Craig 1986] [Fu et al 1987], computer vision [Ballard and Brown 1982], computer-based process control (e.g. control of process variables such as temperature, pressure, flow, etc.) [Holland 1983], and so on.

Along with this process of computerization of manufacturing systems/ processes, the nature of modern manufacturing industry is tending to evolve into a blend of data-driven operations [Kutcher 1983]. As new and more sophisticated computer-based technologies are being continuously introduced and employed in a greater range of manufacturing processes, and as more stringent customer demands are applied to marketable products, manufacturing operations are becoming increasingly more complex [Pao 1984]. Thus the data and information required in completing shop-floor manufacturing operations in a competitive manner (as well as management and decision-making) have increased substantially to the point that computers must be used to handle it [Powers, Jr. 1987] [Charif 1986]. Consequently, the use of computer-based equipment and computer software to manipulate huge quantities of information, stored in a digital form, becomes a common feature of contemporary manufacturing enterprises [Solberg and Heim 1989].

As in many other manufacturing industries, the computerisation of electronic manufacturing industry, in particular the PCB manufacturing industry, is, on the one hand, "pulled" by market demand and strict customer requirement for delivering high quality product on time and at low cost [Wearden 1990]. On the other hand, this process of computerization is also "pushed" by technological development in computers and other related domain technology and the increasing availability of computerized equipment to automate shop-floor manufacture [Riley 1988]. Such equipment can be classified into the following broader categories, viz:

- Computer aided engineering and design (CAE/CAD) systems [Du Feu 1988] [Riley 1988] [Hansohn 1990],

- Computer aided manufacturing (CAM) systems: including for

example NC drilling machines, automatic component insertion/onsertion (ACI/ACO) and automated assembly machines [Du Feu 1988], automated test equipment (ATE) and automated inspection stations (e.g. an AOI system), computerised process control (e.g. soldering [Cox 1988] [Spitz 1988], etching and plating [Makstein 1988a], etc.), and

Computer-aided process planning and control (PP&C), integrated tooling and engineering control (ITEC) and management information system (MIS) [Balius 1990].

# 2.2.2 The Need for Integrating Manufacturing Systems

The widespread application of computers and computer-based equipment in manufacturing industries has indeed promoted productivity of various industry sectors: in terms of more efficient manufacturing operations, shortened time-to-market of products, reduced unit product costs and in terms of improved product quality [Powers, Jr. 1987].

However, since the process of computerization has been a gradual process (mirroring but lagging behind developments in computer technology), many segmented "islands of automation" have been created [Llewelyn 1989] [Harhalakis et al 1991]. As a result of these step-wise enhancements, segments of product realisation have also advanced in a stand-alone manner, meaning that they only perform a well defined range of tasks of limited scope with little assistance of other devices [Weston et al 1988]. One way of viewing this is that they are not designed to interact or share information with other segments [Hansohn 1990]. As a result, achieving synergism (i.e. greater functionality from the whole than a summation of functionality of individual parts) has traditionally been very limited. In other words, the realisation of the synergy inherent among these sub-systems may be achieved only through a full integration of these "islands of automation" [Graves et al 1988].

As manufacturing industry takes on a new data-driven (programmable) nature, tasks of data manipulation and information handling have become a common feature [Weston et al 1988] of any computerised manufacturing system. Effective and efficient processing and utilisation of all relevant manufacturing information is becoming one of the prerequisites of many industrial sectors to maintain competitive edge or even to survive in modern world of industry [Kutcher and Gorin 1983].

In view of the limitations of "islands of automation" approach to computerized-manufacturing, researchers worldwide have strived to evolve suitable means of integrating relevant activities of various sectors of manufacturing, with a view to maximising the utilization of computerised manufacturing devices [Hemond 1986] and especially the information stored in and manipulated by these devices [PE Staff Report 1986] so as to improve efficiency of factory operations and to achieve more rapid response to new marketing demands [Weston 1991a].

## 2.3 Modelling of Manufacturing Systems

Manufacturing systems, which often comprise many components (such as people, work stations, robots, tools, conveyer, storage, AGVs (automatic guided vehicles), etc.) [Chow et al 1985], are inherently complex systems, particularly so as their size increases; therefore in order to achieve an appropriate level of integration of the operations (processes) involved in such complex systems, it is necessary in the first place to have a good understanding of the fundamental concepts, functions and information requirements of systems and their constituent parts [Hitomi 1990].

For these reasons the modelling of manufacturing operations has become an important area of interest and research, which is expected to promote a "uniform understanding" of functions, information requirements, system necessary resources, structural organization, operational behaviours, etc. of the manufacturing enterprise [Mertins and Sussenguth 1991]. Research activities in this area have led

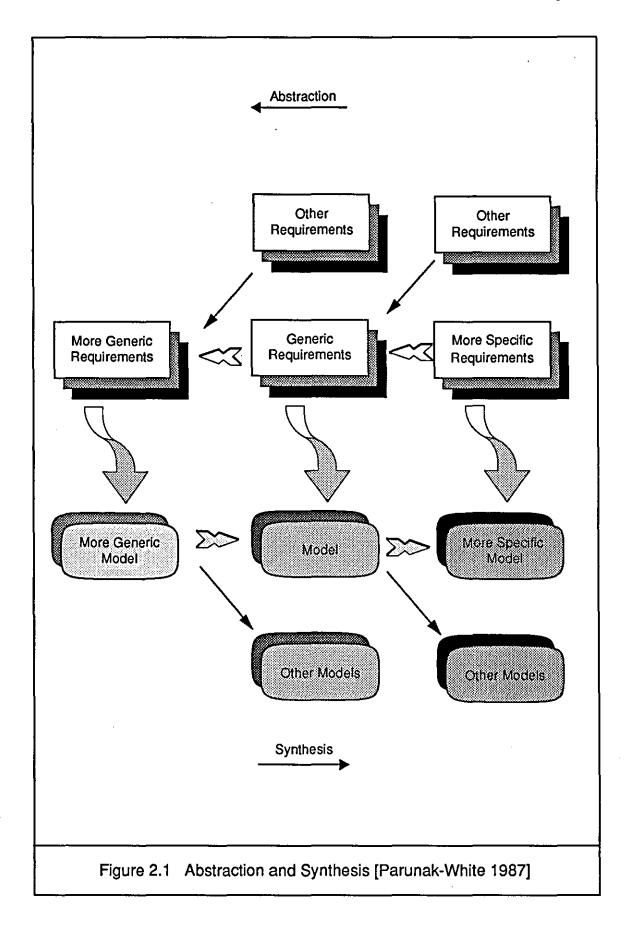

to a number of proposed models of manufacturing which describe manufacturing operations from various viewpoints, providing to some level of abstraction a description of real world manufacturing systems. Some examples of these models are CAM\*I [CAMI 1983] [Boylin 1990], ISO [ISO 1986] [Shorter 1990], CIM-OSA [Beechman 1989] [Kosanke 1991] [Panse 1990], CIM-BIOSYS [Leech et al 1991].

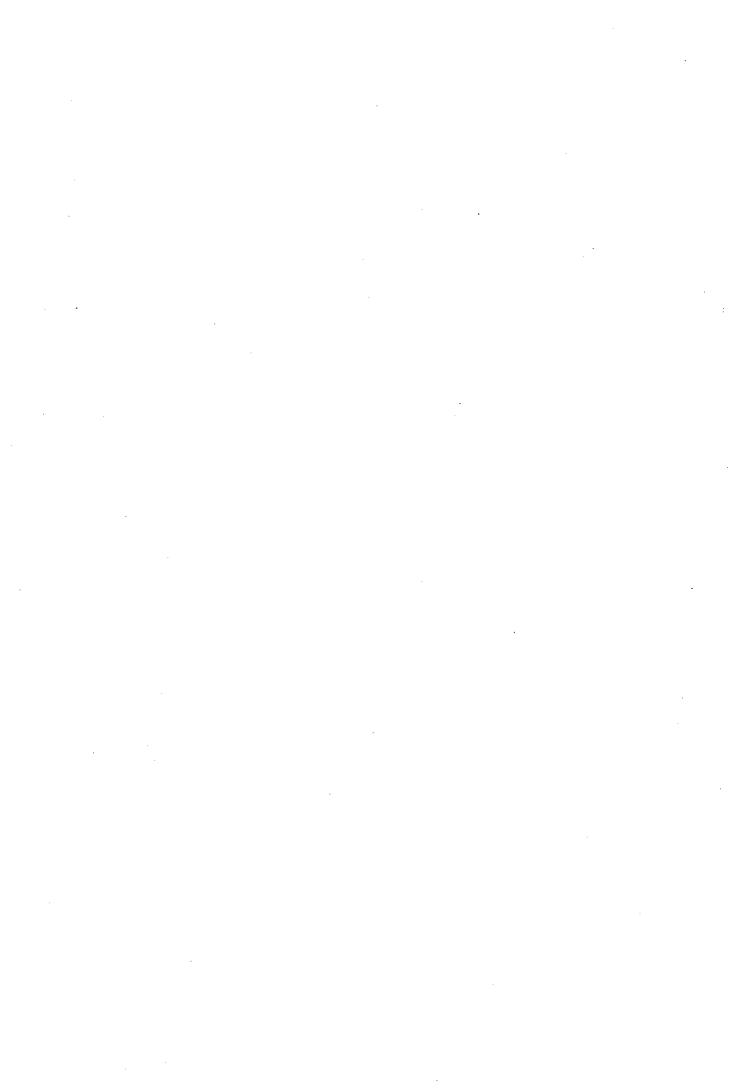

While it is common and reasonable that different viewpoints are adopted when modelling particular problems of interest, the existence of an array of non-conforming conceptual models does not naturally lead to well designed manufacturing systems from a global perspective. Certainly, it is not a straight forward matter to agree on the functionality of each hierarchical layer typically found within these models or indeed even the number of hierarchical layers that typically exist. However, it is necessary and important to have a conceptual model which is generic enough to be applied to any systems with little modification. Such a universally applicable generic model could greatly assist human understanding of manufacturing systems [Dooner 1989]. Furthermore, conceptual models can also be used to provide guidelines for the design and implementation of complex manufacturing systems [Jorysz and Vernadat 1990a]. The existence of such a generic model (which is likely to be of a hierarchical nature although heterarchical models of manufacturing systems have also been specified [Solberg and Heim 1989]) relies on the fact that generic requirements are common to all manufacturing areas [Anderson et al 1990l, and that every manufacturing system exhibits much the same characteristics (though different in details). A recognition of generic similarities (and underlying commonality) in all manufacturing systems can be identified and more generic solutions be sorted out through classification and analysis of typical cases [Parunak and White 1987]. This process is illustrated in Figure 2.1.

However, it has not yet been demonstrated that such a model can be identified without either being so abstract that it is not very useful or too prescriptive so that it only represents reality in a very narrow application domain [Haren and Williams 1990] [Böhms and Tolman 1990]. Nonetheless, it is worth noting that

among the various proposed models, the hierarchical factory reference model adopted by the international standards organisation (ISO) has gained wide international acceptance [Shorter 1990]. This model which serves to define the hierarchical operational levels within a manufacturing enterprise is illustrated in Figure 2.2.

## 2.4 Computer Integrated Manufacturing

Research activity in modelling manufacturing systems has advanced an understanding of fundamental concepts and requirements involved in manufacturing organizations. This enhanced understanding of manufacturing has led to a realization of the need and the importance of systems integration. Information is a valuable resource within manufacturing and the management and control of manufacturing information on an enterprise-wide basis has been considered central to the concept of computer integrated manufacturing (CIM) [Murray 1988] [Harhalakis et al 1991].

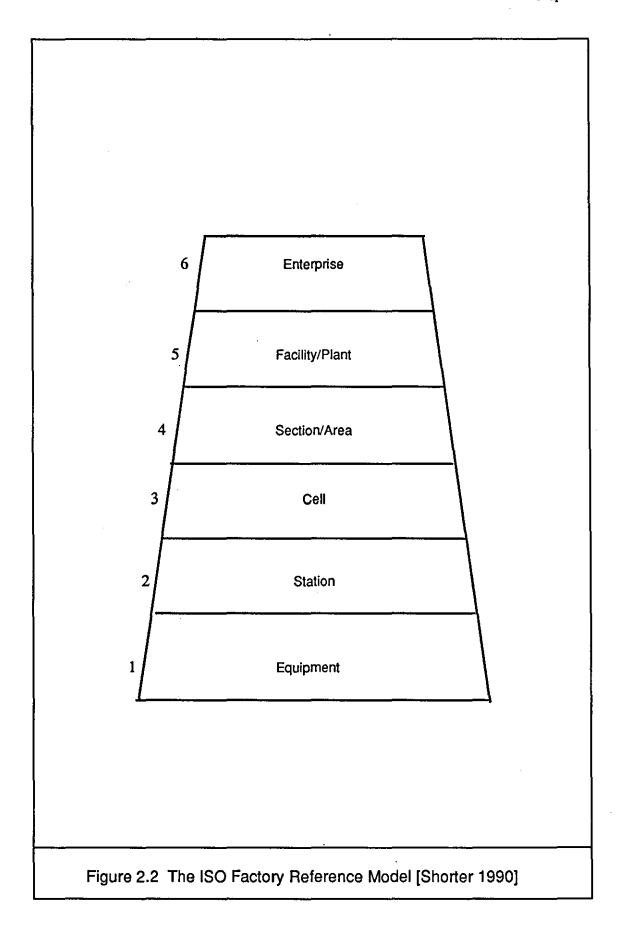

CIM aims at the complete integration of all activities and subsystems of a manufacturing organization; from the receipt of customer orders, through product specifications, product design and modification, product manufacturing and quality control (testing and inspection), to product delivery and after-sale services [Groover 1987]. See Figure 2.3. In reality, various turnkey (stand-alone) computerized subsystems, devices and tools are involved in this cycle of production, assisting with product design, development and manufacturing, as well as with organizational management. These devices and tools are building elements for CIM and are required to be interconnected or integrated in order to exploit CIM [Hemond 1986] [Foong and Hoang 1991]. Typically, such CIM elements would include: computer-aided design (CAD) systems, robots, material requirement planning (MRP), computer-aided manufacturing (CAM) stations such as NC (numerical control) drill, CNC (computer numerical control) machines, automatic optical inspection (AOI) systems, automated test equipment (ATE), etc. The trend is towards multi-vendor manufacturing, implying that for each type of devices there will be a group of suppliers; there-

fore no conformity is guaranteed for even the same type devices supplied by different suppliers, nor by the same supplier at different time frame.

## 2.5 Methods and Tools for Manufacturing Systems Integration

The challenge and the potential benefits of CIM have greatly stimulated world-wide interest and research activities in developing appropriate methods and tools to assist in achieving an integration of manufacturing systems. Out of these various research activities and project initiatives, a number of useful tools and underlying methodologies have emerged. Such tools and methods will be reviewed in this subsection, especially with respect to the following areas, viz:

- (1) Netwoking and communication standards,

- (2) Manufacturing information handling: administration systems and representation format standards, and

- (3) Architectures for manufacturing systems integration.

## 2.5.1 Networking and Communication Standards

A fundamental requirement of CIM is to provide means by which the physical flow of fragments of information can be realised between systems which need to communicate [Scheer and Hars 1991]. Through electronic information transfer, information sharing and interaction between manufacturing sub-systems can be enabled to allow more timely and effective decision making [Mills et al 1991]. However, in reality this physical link can be established either as a manual delivery mechanism (e.g. using manually delivered floppy disks, magnetic tapes, etc.), or as an electrical connection between communicating systems so as to facilitate electronic data interchange (EDI) [Low and Chee 1991]; e.g. using RS-232 serial transfer, or via local area networks.

The use of suitable local area network (LAN) [Maria 1986] for intercomputer communications has been proven to be an effective means of delivering

information quickly and accurately [Stix 1990]. However, as has been acknowledged, data communication over LANs has only partially solved the problem, as

"data transfer is one matter but information transfer is another completely" [Weston

et al 1988]. Furthermore, there still exists a lack of conformity between the subsystems wishing to communicate and indeed various LAN implementations which can

be used to enable communication. As a result, systems built with differing LAN

interfaces (i.e. different protocols) are still unable to transfer data between them

[Voelcker 1986].

Until recently, proprietary architectures and customised protocols have been the underlying basis for almost all factory networks [Jasany 1986] [Busby et al 1990]. The need for communications standards, to allow direct exchange of information between communicating systems, has stimulated the research activities in the area of communication standardization [Kaminski 1986] [Farowich 1986] [Hansohn 1990] [Frenkel 1990]. Here only a few of very important research projects in communication standards are reviewed.

#### A. ISO/OSI Standards and the ISO/OSI Reference Model

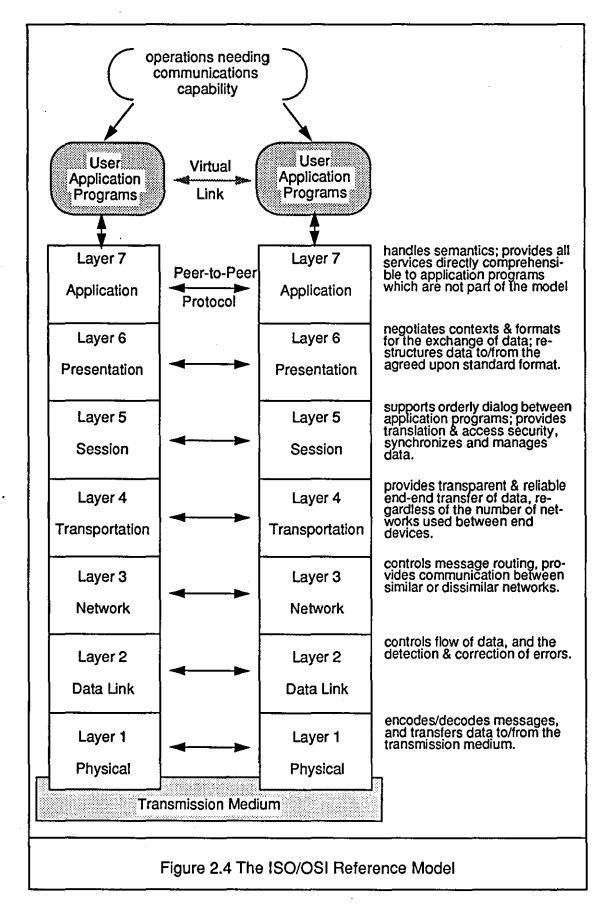

In 1970 the International Standards Organization (ISO) began work on series of communications standards with a number of international projects initiated under the Open System Interconnection (OSI) banner [Crowder 1985]. In 1977 a reference model for Open System Interconnection, i.e. the ISO/OSI reference model, was made public and gained international acceptance as a framework for LAN development in both the factory and the office environment [Welch Jr. 1986]. The ISO/OSI reference model functionally segments the general communication task a LAN must perform into seven different layers [Maira 1986] [Gray 1991]; therefore this reference model is also known as the "seven-layer OSI model" (see Figure 2.4). The

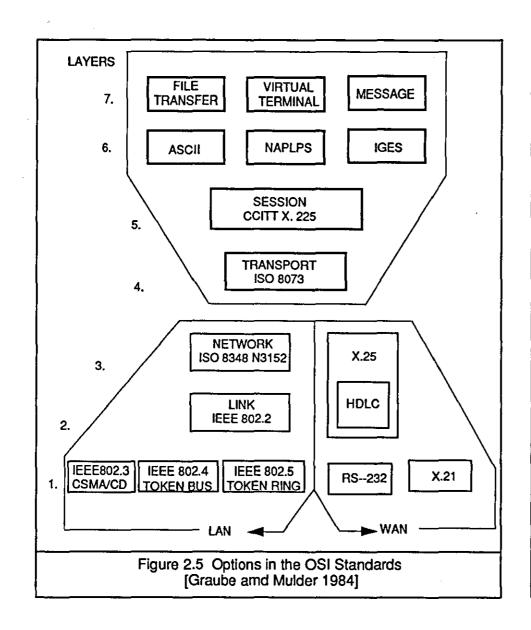

ISO/OSI model is an abstract model; it only provides a blueprint [Amam 1986], but does not specify how the functionality at each layer should be implemented [Day and Zimmermann 1983], i.e. it does not specify what protocol standards should be used at which layer. In order to accommodate the wide variety of applications, there are a number of options within the OSI standards for each of the layers [Graube and Mulder 1984]. See Figure 2.5. However, this in turn gives rise to the possibility of incompatibility between different implementation based on the same reference model [Gray 1991].

#### B. IEEE 802.X Standards

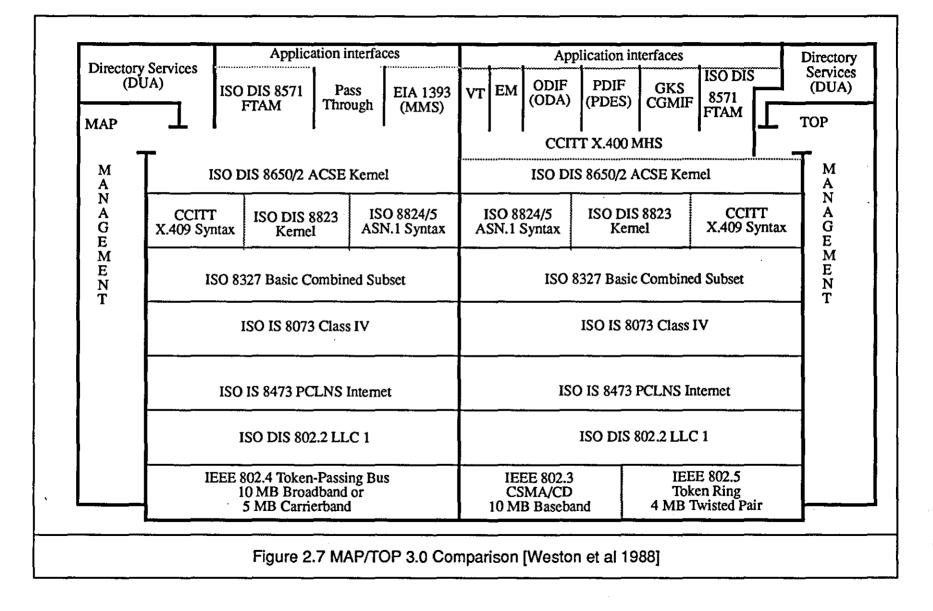

In 1980 the Institute of Electrical and Electronic Engineer (IEEE) formed the Project 802 committee to work on specific standards for local area networks [Maira 1986]. The results of this project is a series of LAN standards which are now gaining international acceptance [Amam 1986]. See Figure 2.6. In fact, some of the IEEE standards are chosen as standard protocols which are being included in the MAP/TOP specifications (at the lowest two layers, see Figure 2.7).

#### C. MAP/TOP

Manufacturing Automation Protocol (MAP) [Kaminski 1986] and Technical Office Protocol (TOP) [Farowich 1986] are two specific implementations of the ISO/OSI model developed and evolved during the last decade. Both MAP and TOP are based on ISO/OSI reference model and are committed to take the best of existing standards where available and specify new protocols where necessary [Moon 1985] [Weston et al 1988] [Breeze 1990]. For example, both MAP and TOP take ISO, IEEE, and DIS (Draft international Standards) standards for the lower layers, and specify their own protocols for the application layer (layer 7), e.g. the Manufacturing Message Specification (MMS) used in MAP 3.0. However, while MAP is intended for factory floor automation where the guaranteed delivery of messages is

#### **IEEE 802.1**

Local Area Networks Glossary, Interworking and Management

**IEEE 802.2**

Local Area Networks, Logical Link Control

**IEEE 802.3**

Local Area Networks, Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifica-

**IEEE 802.4**

Local Area Networks, Token-Passing Bus Access Method and Physical Layer Specifications

**IEEE 802.5**

Local Area Networks, Token-Ring Access Method and Physical Layer Specifications

Figure 2.6 IEEE 802 Standards [Amam 1986]

critical (e.g. for real time control), TOP is intended for technical office automation where data traffic tends to involve bursts of large blocks of data but guaranteed delivery within a short time frame is not critical [Amam 1986]; therefore at certain layers different protocols have been adopted in MAP and TOP specifications. See Figure 2.7. The difference between MAP and TOP specifications reflects the reality that communications solutions must address a variety of business applications and each of these applications may require its own coordinated suite of protocols. Moreover, as stressed in [Crowder 1985], the differences between those protocol suites will primarily lie in the lowest and highest level of the OSI reference model.

The development of MAP as the basis for rapid evolution of non-proprietary factory floor communications has received wide attention worldwide, and MAP is evolving standard messages and message handling facilities (e.g. MMS) primarily for shop floor control devices [Weston et al 1988]. However, MAP and TOP again only provide a physical data communication link between computers and computer-controlled programmable devices [Amam 1986]. In other words, MAP (based on the ISO/OSI model) serves to provide two classes of services to applications, namely, interconnection (or networking) and interworking (or interoperation) [Moon 1985] [Gray 1991].

#### D. SNA

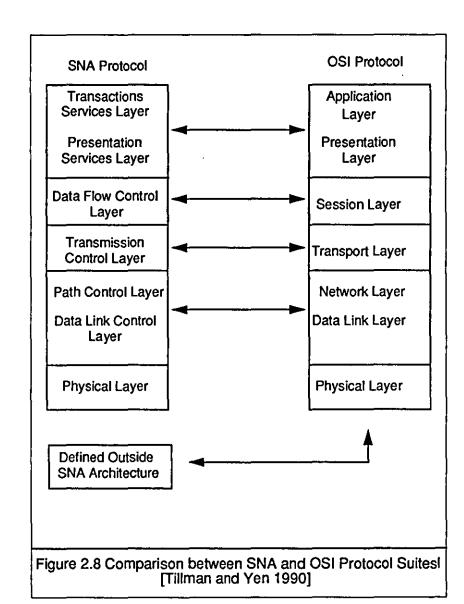

Systems Network Architecture (SNA) [Corr and Neal 1979] was announced in September 1974 by IBM as a seven-layer, hierarchical and single-host network structure [Jarema and Sussengüth 1981]. Since then, the original set of functions has been enhanced to support multiple-host networking [Ahuja 1979].

SNA was designed as a proprietary communication product mainly for the purpose of allowing IBM's own computers to communicate with each other [Gray and McNeill 1979], and has for sometime been widely used as a *de facto* data communication standard, especially among IBM users [Gray 1991]. Although both

SNA and the ISO/OSI reference architecture are seven-layer hierarchical structures, the layers in SNA and OSI model have no mutual conformance. This is due to the fact that SNA proceeded OSI, yet IBM were unwilling to give control of its SNA specifications and its further development to the public standard-making body [Gray 1991]. A comparison of the function of each layer in the two architectures is given in Figure 2.8, whereas Figure 2.9 lists the advantages/disadvantages of each protocol suite [Tillman and Yen 1990].

## 2.5.2 Manufacturing Information Handling

#### A. Information Administration Systems

The US Air Force ICAM programme has specified and advanced an Integrated Information Support System (I<sup>2</sup>S<sup>2</sup>) which is intended to address the problem of information sharing [Weston et al 1988] and to provide mechanisms for managing and controlling information shared between networked computers [Amam 1986].

Furthermore, a three-schema distributed database architecture is incorporated in the Integrated Manufacturing Data Administration System (IMDAS) which has evolved from the work in the Automated Manufacturing Research Facility (AMRF), established by the National Bureau of Standards (NBS) [Libes and Barkmeyer 1988].

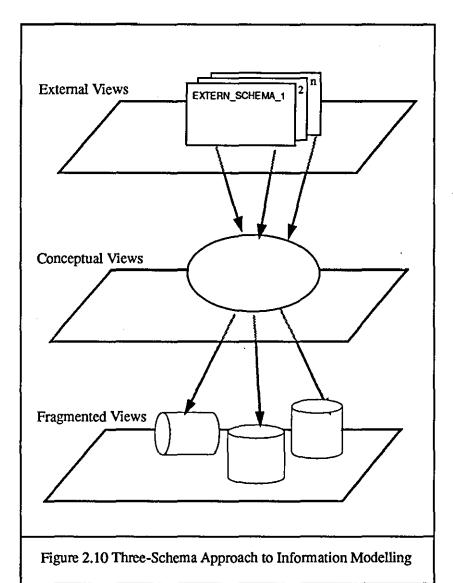

As shown in Figure 2.10 the 3-schema information architecture identifies three types of views of a database, namely, 1) a number of external views, 2) a global conceptual view, and 3) a number of fragmented views [Date 1986] [Beyon 1990]. An external view is the view of the database as seen by the individual user, and is therefore also known as the "user" view or "application" view [Kent 1978]. The global conceptual view represents the entire information content of the integrated database and therefore is a combined view of all necessary data required to manage the whole CIM system, which the database is intended to serve. A frag-

#### Advantages

#### SNA

- \* High-installed base

- Excellent vendor and thirdparty support

- de facto industry standard for long-distance data communication

- \* Good connectivity with other proprietary networks

#### OSI

- \* International connectivity

- Modularity allows for ease of update for each layer without affecting other protocols

- \* Not hardware or program dependent

#### Disadvantages

#### **SNA**

- \* Little connectivity with open system networks

- \* Slow in adapting to distributed network environment

- Design constraints make it difficult to update network

- \*Applications are H/W and S/W dependent

#### OSI

- \* Suite not fully defined

- \* Security (interception, alteration, interruption) is tough to maintain

- Network management is difficult in open systems

Figure 2.9 Advantages and Disadvantages of SNA and OSI [Tillman and Yen 1990]

mented view of the database represents the physical portioning, storage and multiple occurrences of the conceptual data objects across the sub-systems of a CIM system [Weston et al 1988]. The use of three schema information architecture is deemed appropriate for information integration in a manufacturing environment as a means of managing change in manufacturing environments where fragments of information may reside on various storage media—and where the location, content and even structure of that information may need to be regularly changed [Weston et al 1989d].

#### B. Standards for Information Representation

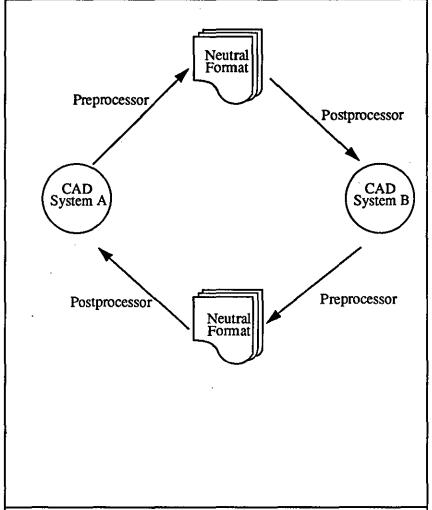

As previously stated, the major functionality of the MAP/TOP specification can be viewed as providing two classes of services to application programs, namely interconnection and interworking [Gray 1991]. However in reality these two classes of services have not been developed evenly, meaning that on the one hand the interconnection services tend to be mature, the interworking services on the other hand are still underdeveloped. This is partially due to the fact that the development and specification of standards for the lower layers of the communication paradigm are relatively less dependent on particular applications, whereas the specification of the higher layers are largely application-specific [Murphy 1990]. For example, the communication needs of file manipulation are quite different from that of real-time control as required by factory floor automation. In other words, the services provided by higher layers are geared more towards the semantics than the syntactic of the communication. This would require the inclusion of protocols for encapsulating production definition data, graphical data, virtual terminal access and office documents [Weston et al 1988]. In this area, a number of standardization initiatives have been focused on evolving standard (or neutral) information representation to facilitate exchange of design intent between dissimilar CAD/CAM systems [Bloor and Owen 1991]. The primary goal of all these initiatives is to facilitate the two-way transfer of data between two or more CAD systems without any loss of information [Brandli and Mittelstaedt 1989], where the neutral format acts as the

"intermediate transfer format" (Figure 2.11). The following few subsections give a brief review of some of the more important initiatives in this area together with a description of important features of resulting standards (many of which are still evolving).

#### **IGES**

The IGES (Initial Graphics Exchange Specification) represents an early approach to establishing a neutral format [Owen and Bloor 1987] [Brandli and Mittelstaedt 1989] for describing and transmitting product design and manufacturing information. It is intended to facilitate the meaningful exchange of data which has been created and stored in a CAD/CAM system in a computer readable format. The IGES initiative started in the late 1970s supported by the US Air Force ICAM (Integrated Computer Aided Manufacturing) programme, involving ground work by the Boeing Co. and General Electric Co. [Murphy 1990].

#### PDES and STEP

PDES (Product Data Exchange Specification) was developed by a third project under the US Air Force programme. Drawing on the IGES, PDDI (Product Definition Data Interface), and XBF (Experimental Boundary File) work, it was developed as a successor to IGES [Owen and Bloor 1987]. It is proposed that PDES should include all product data necessary for the design and manufacture of a product [Weston et al 1988].

STEP (Standard for the Exchange of Product Model Data), first proposed in 1984, was developed under the ESPRIT CAD\*I (CAD Interfaces) project which is to define a specification for the capture and exchange of surface, solid and finite element modelling data so as to support a complete representation of a product through its life-cycle [Bloor and Owen 1991]. A three-layer architecture is incorporated in STEP: the application layer, the logical layer and the physical layer.

Figure 2.11 Using Neutral Format as Intermediate Transfer Format

As has been reported in literature, STEP will be the future standard in exchanging of product model data including complete product definition data and product life cycle data [Brandli and Mittelstaedt 1989] [Bloor and Owen 1991].

### **EDIF**

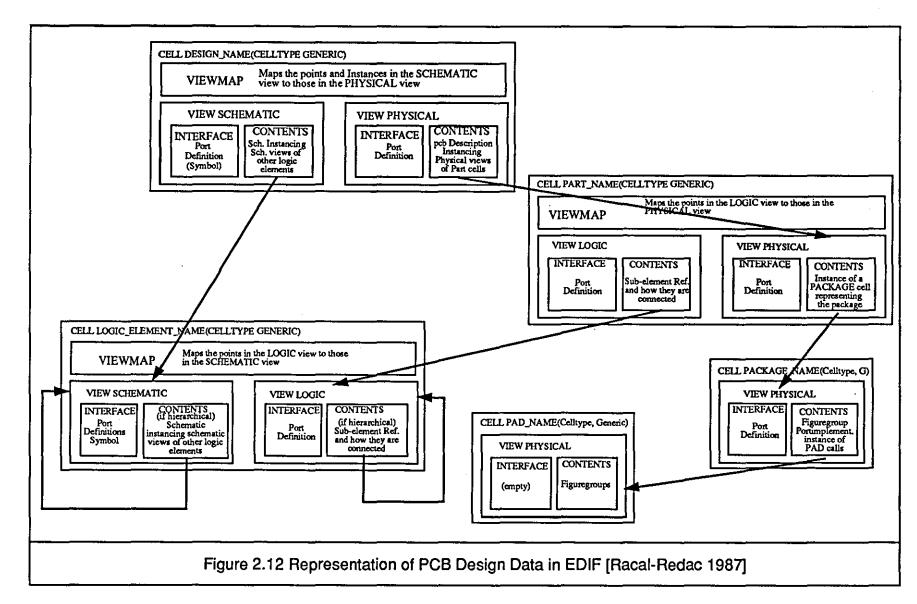

The Electronic Design Interchange Format (EDIF) was originally developed by six large electronics companies in the US; with support from it European representations, it is rapidly becoming a de facto standard for the exchange of electronic CAD design data [Owen and Bloor 1987]. EDIF is designed for representing IC (integrated circuit) design data in a standard format which can facilitate information transfer from design to fabrication environment [Murphy 1990], and thus EDIF has been welcomed by many electronics companies [Eurich and Roth 1990].

Compared with IGES/PDES, EDIF uses a well defined LISP-like language for data definition. The latest EDIF version 2.0.0 was released in 1987, which has already been used to establish "links" between design and manufacturing of VLSI (very large scale integration) [Burson 1987]. Attempts were made to use the original EDIF 2.0.0 syntax (which is mainly intended for representing VLSI design data) for describing PCB layout [Racal-Redac 1987]. See Figure 2.12. However, it was found later on that this was unsuccessful due to the limitations of the EDIF 2.0.0 syntax; those triggering the research into conceptual modelling of PCB layout by the EDIF committee which has been focused on expanding EDIF syntax to include provision for describing PCB layouts [EDIF-PCB-TSC 1990].

### 2.5.3 Manufacturing Systems Integration Architectures

### A. Three architectures

The need for separate integration architectures to enable the creation of highly configurable, visible and maintainable CIM system was identified by the Sys-

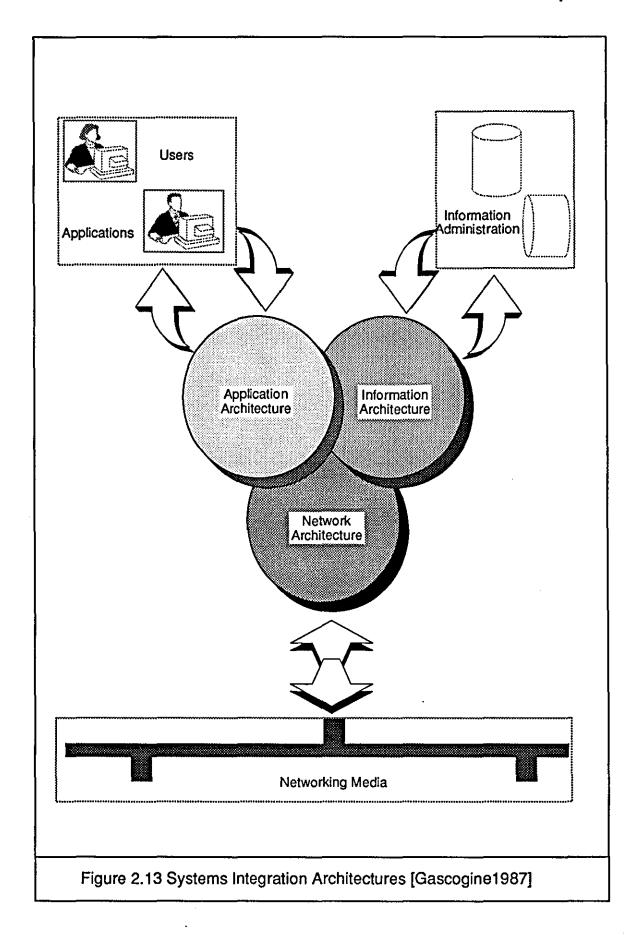

tems Integration Group at Loughborough University of Technology (SIG/LUT). This identification has led to the notion of three integration architectures [Gascoigne 1987] [Weston et al 1989a] [Weston et al 1989c] as depicted in Figure 2.13.

According to Sumpter [Sumpter et al 1987] and Weston [Weston et al 1989a] [Weston et al 1989b], the "network architecture" is to support information exchange (sharing); the "information architecture" is to provide, e.g. by means of database technology, the required information to support various applications; the "application architecture" is to implement system management and supervisory functions, i.e. concerns with the administration of applications (or manufacturing actions) which normally involves defining, building, debugging and running manufacturing applications [Weston et al 1989a]. As such, the development in communication protocol standards (e.g. OSI standards, IEEE standards, MAP/TOP specifications, etc.) can be considered as only providing networking tools/services which can be utilized to form the "communication (network) architecture", whereas development in information administration systems (IAS) such as I<sup>2</sup>S<sup>2</sup> and IMDAS concepts providing methodologies/tools required to form the "information architecture" [Weston et al 1988].

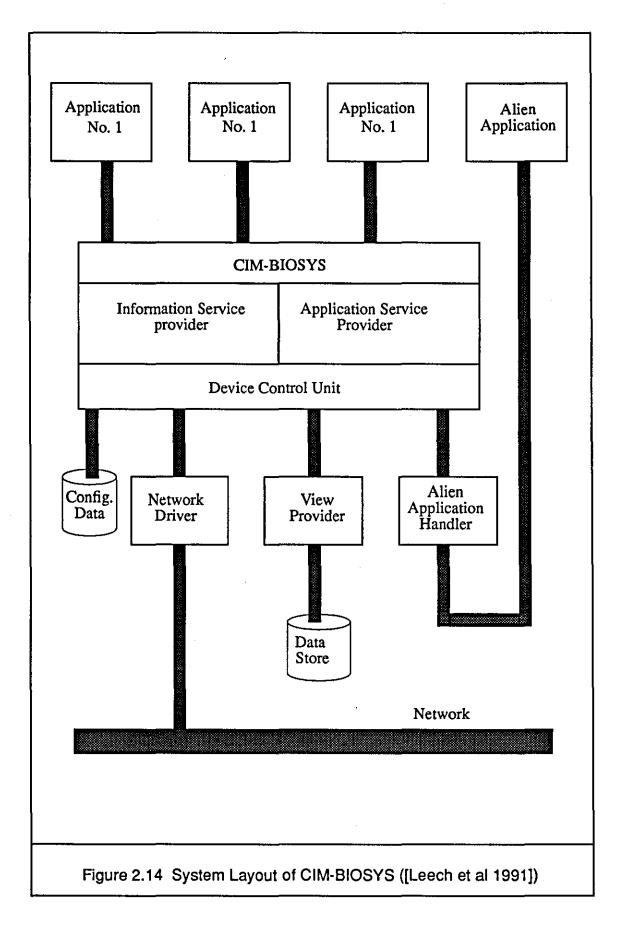

Recent development by the group is the notion of "soft integration platform" called CIM-BIOSYS (CIM-Building Integrated Open SYStem) [Weston et al 1990] which includes a set of configuration tools that can be used to produce, run and maintain soft integrated manufacturing systems. In other words, it provides a set of integration services which support the operation of (and interactions between) open application processes [Weston 1991b]. The platform allows conformant manufacturing devices to be "plugged" in and non-conformant devices to be connected by means of "temporary bridges" known as "alien application handlers". It also allows the manufacturing applications to be distributed and run across a network of computers and machines [Leech et al 1991]. Software services (i.e. communications, information, control and administration) are provided by the platform to all devices plugged in or connected to it. The above-mentioned three integration architectures

are reflected in CIM-BIOSYS by the three main sections of the platform, namely, application service provider, information services provider and device control unit. The system layout of the CIM-BIOSYS is illustrated in Figure 2.14

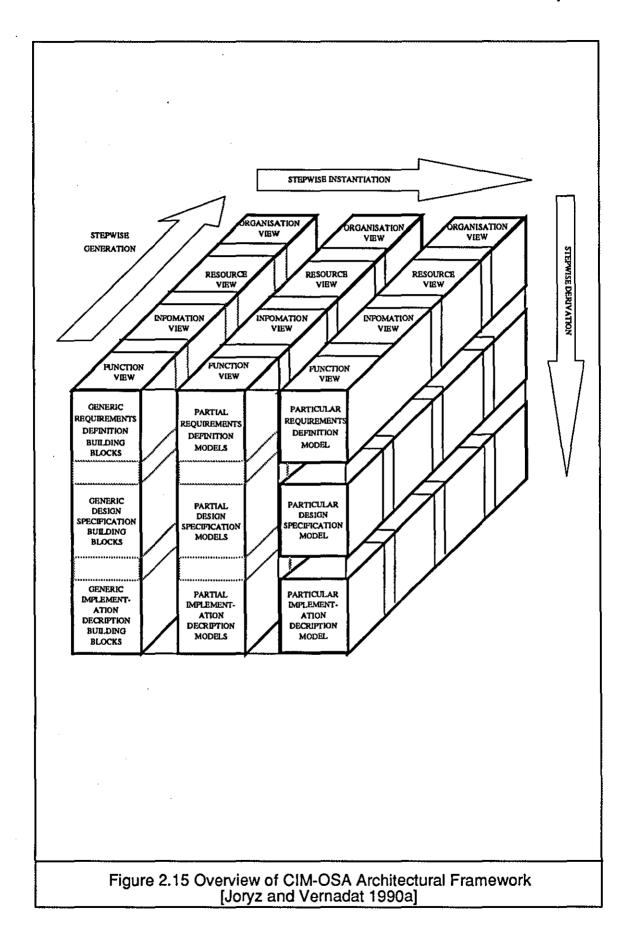

### B. ESPRIT CIM-OSA

The European Strategic Programme for Research and Development in Information Technology (ESPRIT) was launched in 1984 [Jorysz and Vernadat 1990a], of which CIM is a key area of research. The aim of the ESPRIT CIM programme is to develop standards and technology for multi-vendor systems, with the technical goal being to develop (i) a generic CIM reference architecture for the creation and execution of enterprise models, i.e a "modelling framework" [Panse 1990] [Jorysz and Vernadat 1990a] [Jorysz and Vernadat 1990b], and (ii) a set of rules for building CIM systems based on the architecture, i.e. an "integrating infrastructure" [Klittich 1990] that can support model engineering within heterogeneous manufacturing and information technology environments [Kosanke 1991]. The Computer-Integrated Manufacturing Open Systems Architecture (CIM-OSA) thus resulted. See Figure 2.15.

### 2.6 Computer Vision Technology and Its Applications in Manufacturing

Computer vision (or machine vision) is a multi-disciplinary area of study, involving electronics, optics and sensing, computer science, vision algorithms, image processing, pattern recognition and artificial intelligence [Sanz 1988]. It can be viewed as an area of pattern recognition which deals with the analysis of images and scenes, and is mainly concerned with enabling computers to handle visual (or pictorial) input data [Fu and Rosenfeld 1984]. As far as industrial application is concerned, computer vision systems can be applied in almost all manufacturing processes to provide invaluable data and information for supporting the realisation

- 30 -

of computer integrated manufacturing [Zuech and Miller 1989], and adding a high level of flexibility to factory automation [Kent and Shneier 1986].

### 2.6.1 The Building Elements of a Computer Vision System

There are potentially many ways in which a computer vision system can be applied industrially [Dunbar 1986]. However, despite the fact that varying applications may have varying requirements specifying different physical configuration of the vision system hardware and software [Welsh 1991], the underlying composition and concepts of contemporary computer vision systems are essentially similar. Moreover, in almost all cases, the generic goal of a computer vision system is to derive a description of a scene by analysing one or more images of the scene [Rosenfeld 1987], or to construct an explicit and meaningful description of physical objects from images [Ballard and Brown 1982], though apparently the content and format of the description may vary from one application to another.

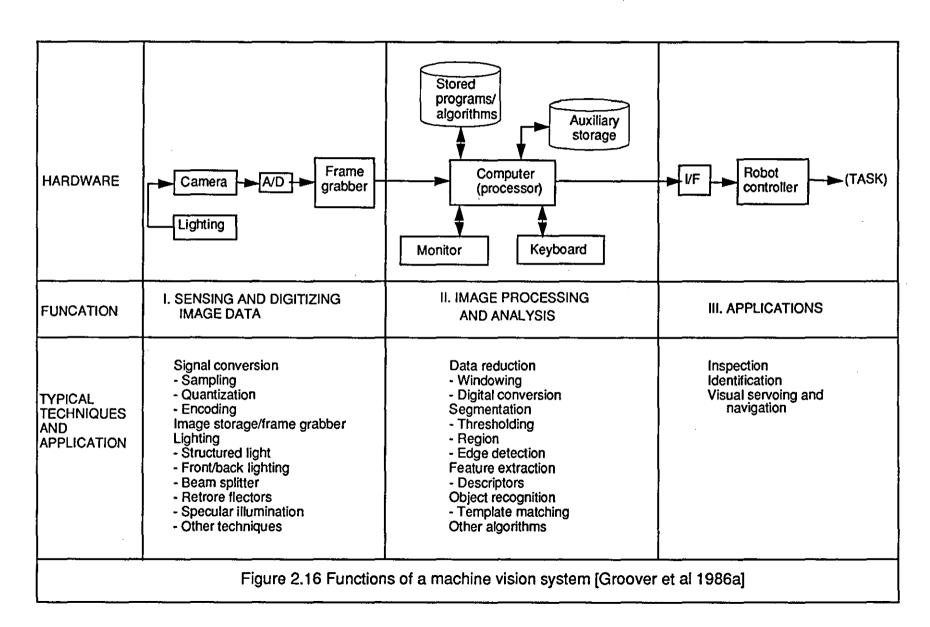

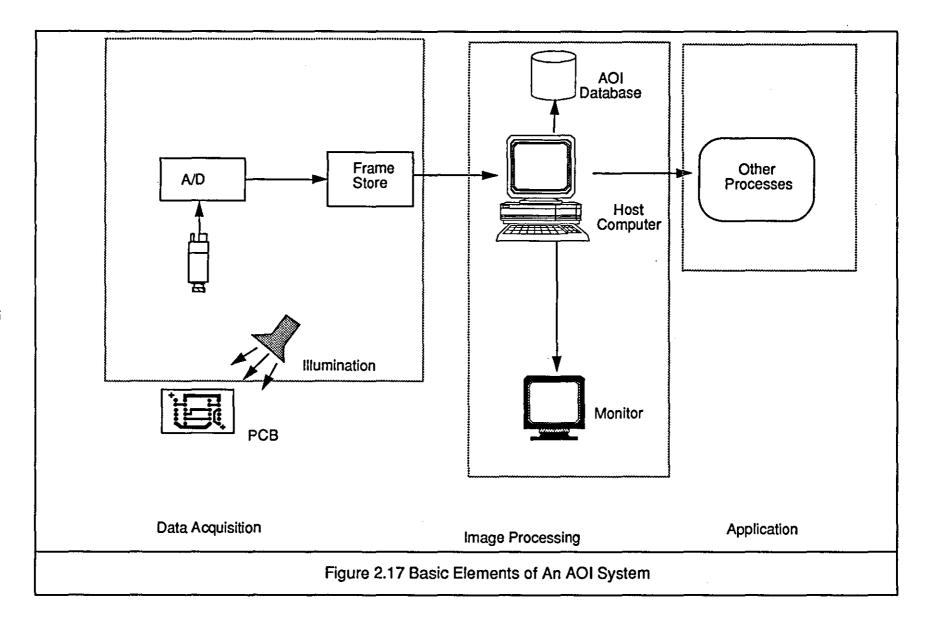

Conceptually, from the system composition point of view, regardless the context of application, a computer vision system will typically include an input (sensing) device (e.g. a camera or a scanner, and an appropriate frame store), a host computer and a set of image processing algorithms and application software [Hollingum 1984]. However, from a research point of view, the heart of a computer vision is its software [Rossol 1983]. The primary operations of a typical vision system comprise three functions (see Figure 2.16) [Groover et al 1986a] [Vernon 1991] [Braggins and Hollingum 1986], viz:

- (1) Sensing and digitizing of the incoming data describing a scene, i.e. image formation and acquisition,

- (2) Image processing and analysis, and

- (3) Image interpretation, and application-specific action-activating and/or decision-making, based on the information generated by

function 2).

In the following subsections, literature concerning issues (2) and (3) listed above are reviewed, as these are closely related to the objective of this research. A good review of techniques concerning the issue of illumination, sensing and image acquisition techniques can be found in [Batchelor 1985a].

Although the real world is geometrically three dimensional, there are many application situations where the scene under examination is itself essentially of a two-dimensional (2-D) nature [Rosenfeld 1987] [Vernon 1991]; for example, a bare PCB or a master film under inspection, a flat part laying on a flat background (e.g a conveyer belt), and so on. Furthermore, in a computer vision system, almost all the images processed are in nature two-dimensional, typically comprising of digitized values arranged in a 2-D array. Not surprisingly, 2-D image processing techniques are relatively well-developed and form fundamental building blocks of some of the 3-D computer vision techniques.

### 2.6.2 2-D Image Processing and Analysis Techniques

Generally, computer vision systems are capable of dealing with 2-D images much more easily than with 3-D images. However, even with a 2-D computer vision there are still many problems which remain as bottlenecks to the development of computer vision, and thus have stimulated great interests and effort in research.

One such problem is related to the sheer amount of data to be processed by a vision machine; for example, an image with 512 by 512 pixels with 8-bit grey levels will give a total of 2,097,152 bits of data which have to be processed by the vision system in say 1/30 second (obviously the time will be dependent on the requirements of a given application). In order to reduce the amount of data to a manageable level, various techniques have evolved. The two main techniques for image

data reduction are digital conversion and windowing [Groover et al 1986a]. The former involves representing an image with a smaller number of bits (less grey levels), with the extreme being binary representation; the latter involves using only a portion of the total image.

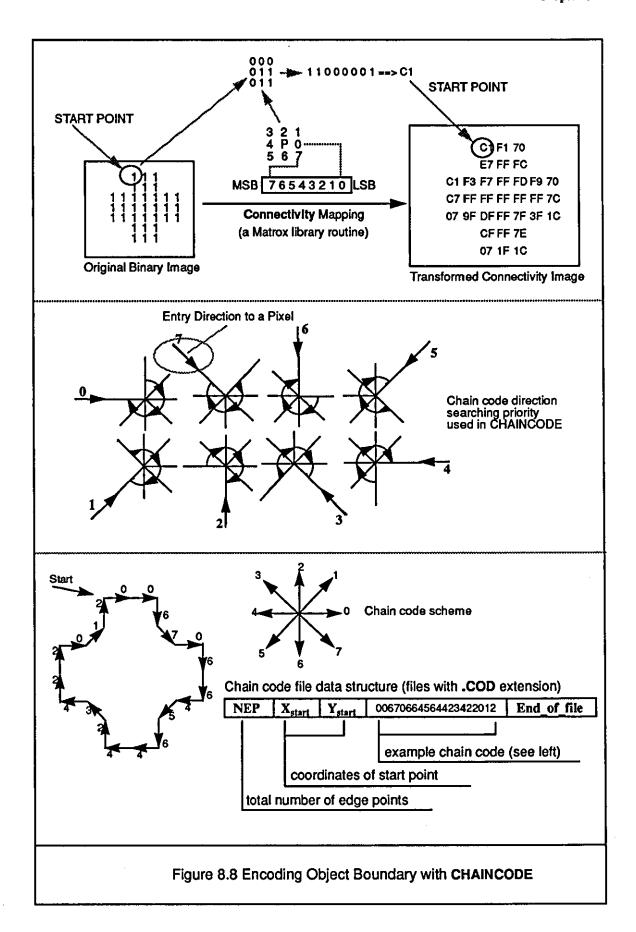

Another class of data reduction techniques incorporate the structural transformation of the image data being processed; for example, representing an image in a more compact string-like data structure instead of the original matrix. Chain codes [Fairhurst 1988] are widely used to encode boundaries of objects in a binary image. This approach is attractive because it uses only eight numerical digits to represent the eight possible directions along the boundary of an object, yet the resultant representation not only reduces the amount of data representing the image, but also makes the process of extracting certain features (e.g. area, perimeter, moments, etc.) fairly straightforward. Another useful data reduction method in this class is the so-called run-length codes [Batchelor 1985b], which in fact adopts a line-by-line scanning approach. However, there exists an additional problem inherent in this approach, namely, that of relating one scan line to the next; therefore analysing the line-to-line relationship is much more difficult [Tanimoto 1980] with run-length codes than with the original arrays.

Traditionally, 2-D image processing techniques can be classified loosely according to the stages at which computer vision task is performed; these being:

- (a) preprocessing,

- (b) segmentation,

- (c) feature extraction, and

- (d) recognition.

### A. Preprocessing

In a computer vision system, the first task starts with acquisition of an image of the scene (e.g. the natural outdoor scene, an industrial assembly, a printed circuit board, etc., depending on the application concerned). This is usually done utilizing sensors which transform the real world three-dimensional scene into two-dimensional arrays of digitized image data. For this purpose, two basic types of video cameras [Dunbar 1986] are usually utilized, namely 1) the vidicon, which is based on vacuum-tube technology, and 2) solid-sate camera, which is based on the semi-conductor technology. Often, with either technology, the resultant image data is, to a certain extent, degraded by electronic noise and/or other types of distortions (e.g. optical distortions) introduced during this process of image acquisition [Ballard and Brown 1982] [Ruocco 1987].

As a result, it is often desirable that certain preliminary operations be performed on the digital image data (though in application this process may not necessarily distinctly be isolated from the succeeding stages of image processing) with a view to removing as much the noise as possible and correcting the distortions, or to enhancing certain features (e.g. the grey-level intensity uniformity [Benhabib et al 1988]) of the image so as to improve its "quality" [Rosenfeld 1969]. Such operations are generally referred to as preprocessing [Ruocco 1987], or early processing [Ballard and Brown 1982], or image enhancement [Rosenfeld 1969] [Castan 1977] [Galbiati Jr. 1990]. Arguably, these operations should not remove critical information contained in the original image [Benhabib et al 1988]. Operations for such purposes are usually considered to be at the lowest level of image processing hierarchy [Offen 1985], and are performed mainly on a pixel-by-pixel basis. In fact, most of the image pre-processing techniques are based on digital filtering techniques, which is a general term given to a class of operations transforming the image intensity values so as to enhance or depress certain features of the image [Ballard and Brown 1982]. Two classes of digital filters can be further distinguished, i.e. linear and nonlinear filters.

Linear filters are usually realised by means of convolving the image with some defined "masks" [Vernon 1991]. As the convolution is being performed, a weighting factor, represented individually by a mask value, will be applied to each corresponding pixel of the image, and the resultant weighted sum will be assigned as the new grey-level of the pixel of the image which corresponds to the centre of the mask. For example, a low-pass-filter can be realised by convolving the image with an "averaging-mask", which serves to suppress noises with high spatial frequency, and the image is thus "smoothed". However, the noise reduction is done at the expense of bandwidth [Svetkoff et al 1987], causing the image to blur and thus the edge transition is inevitably degraded.

Equally important in the class of linear filters, are the so-called "high-pass-filters". These are again realised by convolution, but serve to highlight intensity discontinuity of the image, resulting in a "sharpened" image; therefore it can be used as a means of enhancing the image before edge detectors are applied.

Non-linear filters are also frequently used for noise reduction and image enhancement. A good example is given as the median filtering [Castan 1977] whereby the grey-level of a pixel is replaced with the median of the pixel values in some local neighbourhood (e.g. a 3 x 3 window). Median filters can be used for noise reduction, whereas at the same time preserving sharp intensity discontinuity as normally found on edge transitions [Svetkoff et al 1987], and hence preserving certain edge shapes [Schalkoff 1989]. Thus in general, median filters are superior to the above-mentioned linear mean filters (e.g. low-pass-filters) in that image blurring is kept at minimum [Vernon 1991]. However, inherently, median filters are computationally expensive, as it requires in the first place a substantial sorting operation [Low 1991]. Moreover, serious size and shape distortions can be resulted from the use of median filters; therefore, as commented by Davies, median filters should not be applied especially in situations (e.g. industrial inspection) where precise measurements are required [Davies 1989c]. Thus median filters tend not to be used much in industrial machine vision applications [Vernon 1991].

### B. Segmentation

Image segmentation is a general term applied to a variety of techniques used to extract subsets of an image that (hopefully) correspond to the relevant parts of the scene under consideration [Rosenfeld 1987]. Although a great number of techniques are available, they are almost all *ad hoc* in nature; there are no general algorithms which work for all images [Fu and Mui 1981], or, as Haralick put it, "there is no theory of image segmentation" [Haralick 1983]. The various techniques can be categorized into three classes [Fu and Mui 19981] [Groover 1986a] [Rosenfeld 1987] [Vernon 1991], namely, 1) thresholding, 2) edge detection, and 3) region growing (extraction).

Thresholding is a very popular technique which is most widely used to segment an image by means of grey-level transformation [Fu and Mui 1981] [Rosenfeld 1983] [Vernon 1991]. It is essentially a binary conversion method of which the main operation is to set all the grey levels below a certain pre-defined level (i.e. the threshold) to zero, and those above to a maximum brightness level (say 255) [Groover et al 1986a] [Low 1991]. Many preprocessing techniques (e.g. smoothing, image sharpening, etc.) can be applied prior to thresholding so as to obtain a thresholded image where certain features in the original image are highlighted or suppressed [Rosenfeld 1969]. For example, smoothing followed by thresholding [Davis et al 1975] will yield a binarized image containing less "noise points".

A crucial problem in using thresholding-based image segmentation methods is how to select the threshold. In practice, a histogram (representing the statistical frequency distribution of grey levels in the image) is often employed to guide the selection of a proper threshold value. Where appropriate, a global threshold can be applied to the entire image, based on grey level histogram, or local properties [Fu and Mui 1981]. However, one should not assume that this will always be the case. On the contrary, there are many cases of industrial applications where it is not possible or not appropriate to use a single threshold for the whole image, necessitat-

ing the adoption of a more flexible "varying threshold" scheme [Rosenfeld 1987], or "adaptive binarization" [Castan 1977], or "adaptive thresholding" [Ruocco 1987], so as to properly segment the image. A review of threshold selection techniques is given by [Weszka 1978]; and in [Vernon 1991], these techniques are summarised as being falling into one of the following three classes, viz:

- 1) Global thresholding, in which the threshold operation is dependent only on the gray-level of the point.

- 2) Local thresholding, in which the threshold operation is dependent on the neighbourhood property of the point (e.g. the average gray-level) and on the grey-level of the point.

- Dynamic thresholding, in which the threshold operation is dependent on the point coordinates (i.e. position-variant thresholding), a neighbourhood property and the grey-level of the point.

Edge detection is an image segmentation technique based on the detection of discontinuity in image intensity [Fu and Mui 1981], assuming that sharp changes in grey level (intensity) occur in pixels which lie on the boundary or edges of an object. This approach has been motivated by the following factors [Rosenfeld and Kak 1976], namely (i) most of the information of an image lies on the boundaries (or contours) between different regions [Niemann 1979], and (ii) biological visual systems appear to make use of edge detection, but not of thresholding. Edge detection operations can be further broken down into two steps, namely a) edge-element extraction and b) edge-element combination.

In step a), various local edge operators [Levialdi 1983] are utilized to extract edge elements (e.g. an edge point) from the original image by means of measuring any local discontinuity in intensity or its gradient [Ballard and Brown 1982], and a large number of operators have been proposed. For example, linear operators such as Laplacian [Pratt 1978], and non-linear operators such as Sobel

[Duda and Hart 1973], Roberts [Galbiati 1990], Prewitt and Kirsch operators [Ballard and Brown 1982], are commonly used.