# Performance characterisation of photovoltaic devices: Managing the effects of high capacitance and metastability

By Alexander Eeles

**Doctoral Thesis**

Submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of Loughborough University

June 2016

© by Alexander Eeles 2016

### <u>Abstract</u>

It is essential to make performance measurements of photovoltaics modules in order to quantify the power they will produce under operational conditions. Performance measurements are fundamental throughout the photovoltaic industry, from product development to quality control in manufacturing and installation in the field. Rapid and economic evaluation of photovoltaic performance requires measurements using pulsed illumination solar simulators. However some devices have characteristics which can cause difficulties making these measurements. The aim of this thesis is to overcome these measurement problems focusing particularly on two of the most prevalent and pressing of these problematic characteristics: high capacitance and metastability.

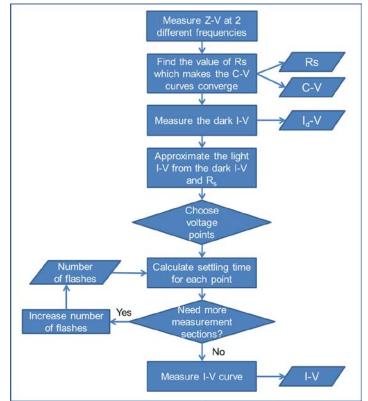

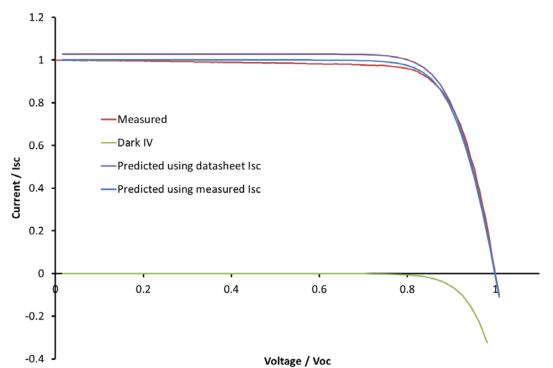

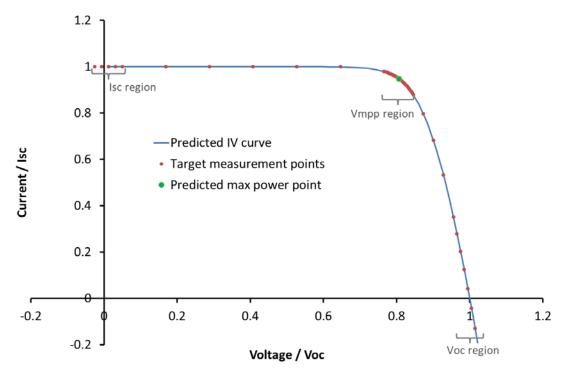

A new method for measuring high capacitance modules in a pulsed simulator, based on tailor made voltage ramps, was developed. The voltage ramp is tailor made such that the measurement time is minimised while maintaining high accuracy (0.5 %), allowing the measurement of high capacitance modules in a single 10ms illumination pulse. The necessary inputs for this method are the capacitance and dark current as a function of voltage for each module. In order to make these measurements, at the high forward bias voltages required, a new system was developed. The tailored voltage ramp can be created individually for each module, since the process is rapid an automatic. This makes the method applicable to a production line or to test house measurements. In addition to their use as inputs for the voltage ramp design, the capacitance and dark current also contain other valuable information, including effective minority carrier lifetime.

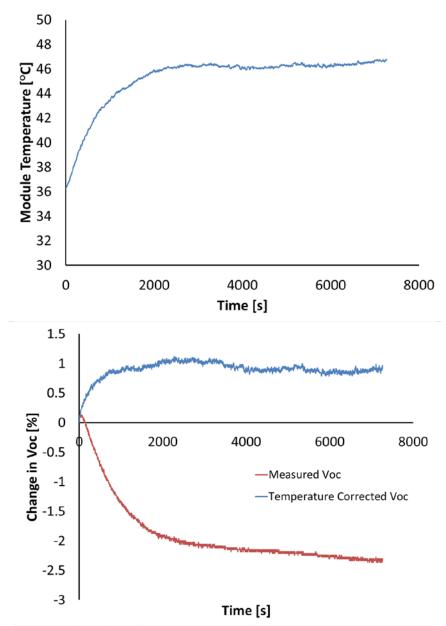

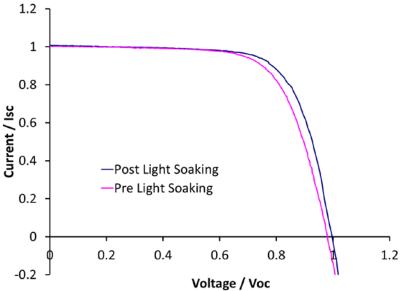

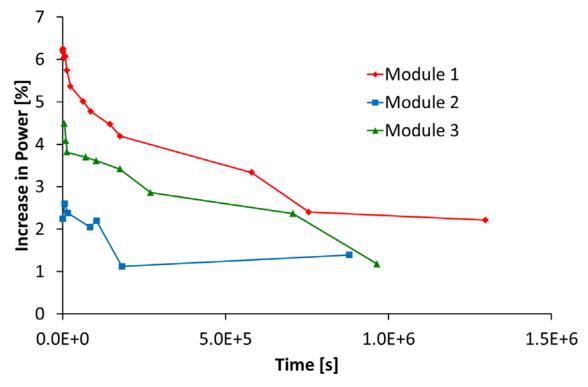

In several thin film technologies, such as CIGS, the efficiency is not a fixed value, rather the module is metastable and the efficiency changes depending on the previous exposure /preconditioning of the device. Preconditioning is normally applied to these devices before measurement in order to put them in a specific state that is repeatable and representative of outdoor operation. Improved preconditioning practices are vital for performance measurements in CIGS modules. Therefore the preconditioning behaviour of a variety of CIGS modules from different manufacturers was investigated. The effect of preconditioning varied for different modules, commonly the fill factor improved substantially, but often changes in open circuit voltage were also seen and in some cases also substantial changes in short circuit current. The rates of

iv

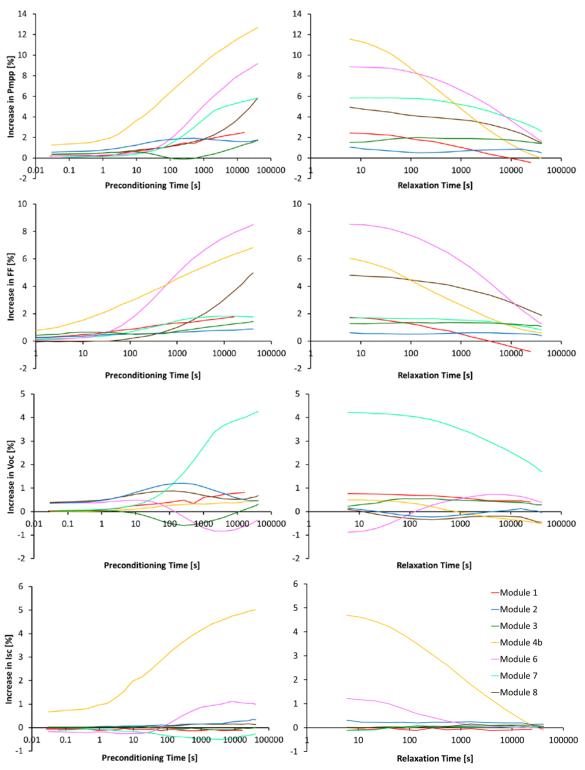

preconditioning and relaxation were found to follow stretched exponential behaviour, such that the changes occur linearly on a logarithmic timescale over several orders of magnitude in time. The total time for performance stabilisation was found to vary significantly between different types of module. Because of this stretched exponential behaviour, even though the module took days to fully relax to the dark state, there was significant relaxation within the tens of minutes that it would normally take a module to cool down after light soaking before it could be measured. The major implication of observed kinetics is that in order to achieve repeatable measurement the timing in each element of a preconditioning routine should be controlled such that the fractional error in the duration of each step is small. During the investigation an unexpectedly short timescale preconditioning effect was observed, which occurs on a millisecond timescale and relaxes in seconds. It was shown that the measurement artefacts introduced using this method can be eliminated by using electrical forward bias until immediately before the measurement.

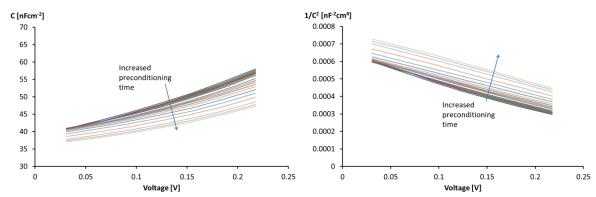

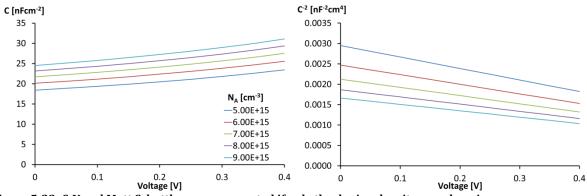

Another measurement system was developed to track the dark current and C-V characteristic of the modules during electrical bias preconditioning and subsequent relaxation. These measurements demonstrate that more than one process involved during preconditioning in CIGS. Changes occur both in the doping in the bulk of the absorber and also in charge accumulation occurring near to the absorber / buffer interface. The theoretical models for preconditioning in CIGS were reviewed and compared to the experimental results. A rate model was developed based on the theory of the metastable  $V_{Se}$ - $V_{Cu}$  defect. This model was shown to correspond well to the rates of preconditioning and relaxation in CIGS. The non-exponential behaviour was shown to be compatible with a distribution of activation energies for the transition between different defect states. The difference in the time taken for modules to stabilise is explained by differences in doping density and the density of  $V_{Se}$ - $V_{Cu}$  defects.

The work presented facilitates more accurate, economical performance measurements for high capacitance devices and CIGS devices, thereby contributing to the large scale implementation of photovoltaics as power source.

# **Acknowledgments**

Many people gave me huge amounts of help during my time completing this thesis and without that help it would not have been possible.

My academic supervisors Tom Betts and Ralph Gottschalg provided excellent support both technical and also in the softer aspects. In regard to those softer aspects tom in particular has been the most caring supervisor one could wish for. Thank you both for believing in me and providing me with many opportunities.

I have had several industrial supervisors / points of contact from TATA steel and associated groups during this thesis - Paul Jones, Rodney Rice, Paul Bates, Martyn Hussey, Andy Thein, Ben Wilkinson. Despite significant turbulence that occurred with the structure and aims of TATA steels solar research activities they continued to give me support, which was very much appreciated. There were also many others from TATA steel, Dyesol, BIPVco and SPECIFC who provided valuable help. Thank you to you all.

Everyone at CREST has helped to create a fantastic, dynamic, stimulating environment to work. Many of you have become close friends. Thanks for all the thought provoking discussions, both technical and otherwise. There is not space to mention you all by name but I am very grateful to you all. In particular I would like to note Bianca Maria Maniscalco, for being an excellent friend and housemate who proof red my thesis, cooked me many meals while I was working on it and provided a huge amount of moral support.

Without question I would not have made it this far without the support of my parents who taught me to achieve the most that I can.

Finally I would like to mention my wonderful wife to be Ana Isabel Barbosa. The huge amount of support and understanding she gave me was amazing.

# **Contents**

| Ab | stract       |                                                    | iv |

|----|--------------|----------------------------------------------------|----|

| Ac | knowledg     | gments                                             | vi |

| 1  | Introduction |                                                    |    |

| 2  | Princip      | les of Photovoltaics                               | 6  |

|    | 2.1 Op       | eration                                            | 6  |

|    | 2.1.1        | Basic operation principle                          | 6  |

|    | 2.1.2        | Solar Resource                                     | 9  |

|    | 2.1.3        | Band diagrams                                      | 11 |

|    | 2.1.4        | Transport equations                                | 14 |

|    | 2.1.5        | Recombination mechanisms                           | 16 |

|    | 2.1.6        | Depletion approximation                            |    |

|    | 2.1.7        | Defects                                            | 20 |

|    | 2.1.8        | Equivalent circuits                                | 23 |

|    | 2.2 Dif      | ferent PV technologies                             | 26 |

|    | 2.2.1        | CIGS                                               | 26 |

|    | 2.2.2        | High efficiency Si concepts                        | 27 |

|    | 2.3 Per      | formance measurements                              | 29 |

|    | 2.3.1        | Standard Test Conditions                           | 29 |

|    | 2.3.2        | Other performance measurement conditions           |    |

|    | 2.3.3        | Apparatus                                          |    |

| 3  | Factors      | s affecting Performance measurements of PV devices | 35 |

|    | 3.1 Cap      | pacitance                                          | 35 |

|    | 3.1.1        | Effects of capacitance on performance measurements | 35 |

|    | 3.1.2        | Definition of capacitance                          | 37 |

|    | 3.1.3        | Mechanisms of charge storage in solar cells        | 37 |

|    | 3.1.4        | Dynamic equivalent circuit models.                 |    |

|    |     | 3.1.5   | C-V profiling                                                        | 41 |

|----|-----|---------|----------------------------------------------------------------------|----|

|    | 3.2 | 2 Pre   | conditioning in CIGS                                                 | 43 |

|    |     | 3.2.1   | Effects on performance measurements                                  | 43 |

|    |     | 3.2.2   | Other observable device metastabilities                              | 45 |

|    |     | 3.2.3   | Microscopic origins of preconditioning                               | 47 |

| 4  |     | Capacit | ance                                                                 | 50 |

|    | 4.1 | 1 Int   | roduction                                                            | 50 |

|    | 4.2 | 2 Mo    | dule impedance and I-V measurement system                            | 50 |

|    |     | 4.2.1   | Measurement system setup                                             | 50 |

|    |     | 4.2.2   | Correction factors for the impedance measurements                    | 52 |

|    |     | 4.2.3   | Module C-V measurements                                              | 55 |

|    |     | 4.2.4   | Validation of the impedance measurement system                       | 56 |

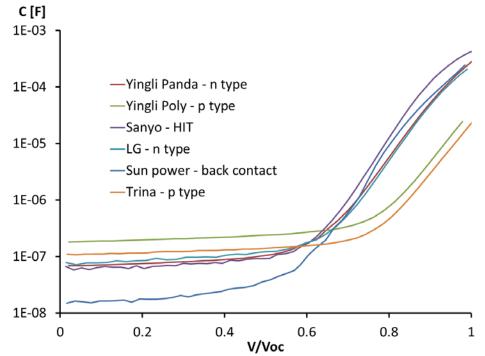

|    |     | 4.2.5   | Comparison of different module C-V characteristics                   | 57 |

|    | 4.3 | 3 Tai   | lored sweep design based on dark I-V and C-V measurements            | 59 |

|    |     | 4.3.1   | Concept                                                              | 59 |

|    |     | 4.3.2   | Review of existing performance measurement protocols                 | 59 |

|    |     | 4.3.3   | Estimating the light I-V                                             | 61 |

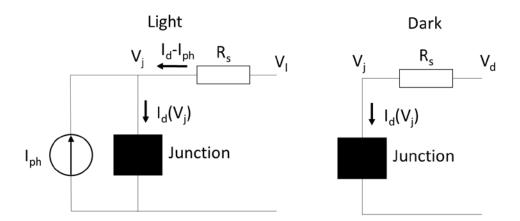

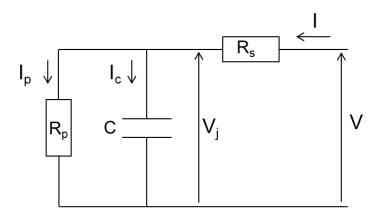

|    |     | 4.3.4   | Modelling a small voltage step                                       | 63 |

|    |     | 4.3.5   | Error between I-V curves                                             | 65 |

|    |     | 4.3.6   | Results of the tailored sweep design                                 | 66 |

|    |     | 4.3.7   | Comparison of measurement protocols                                  | 71 |

|    | 4.4 | 4 Ext   | racting device information                                           | 73 |

|    |     | 4.4.1   | Carrier density                                                      | 73 |

|    |     | 4.4.2   | Carrier lifetime measurements                                        | 74 |

|    | 4.5 | 5 Cor   | nclusions                                                            | 76 |

| Сс | onc | clusion | of the problem of high capacitance and link to metastability in CIGS | 78 |

| 5  |     | Quantif | fication of Preconditioning in CIGS                                  | 79 |

|   | 5.1 | I     | Introduction                                                          | 79     |

|---|-----|-------|-----------------------------------------------------------------------|--------|

|   | 5.2 | 2 I   | Light soaking in modules                                              | 81     |

|   | !   | 5.2.1 | 1 Method                                                              | 81     |

|   | !   | 5.2.2 | 2 Results                                                             | 82     |

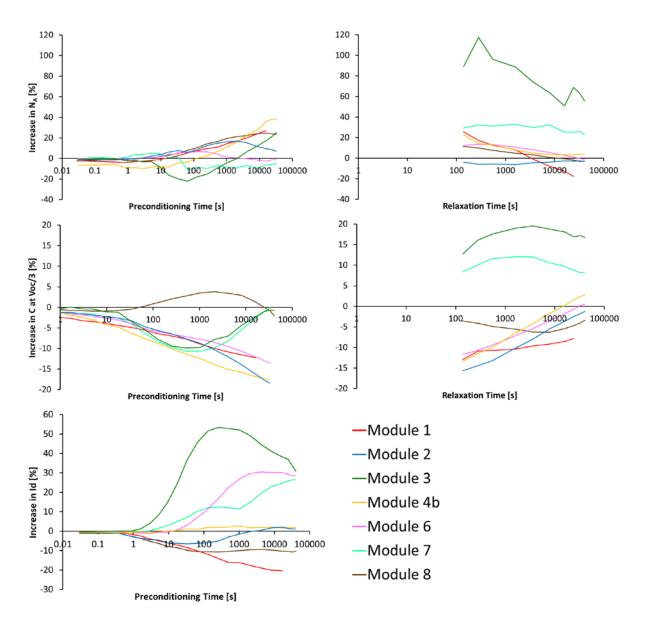

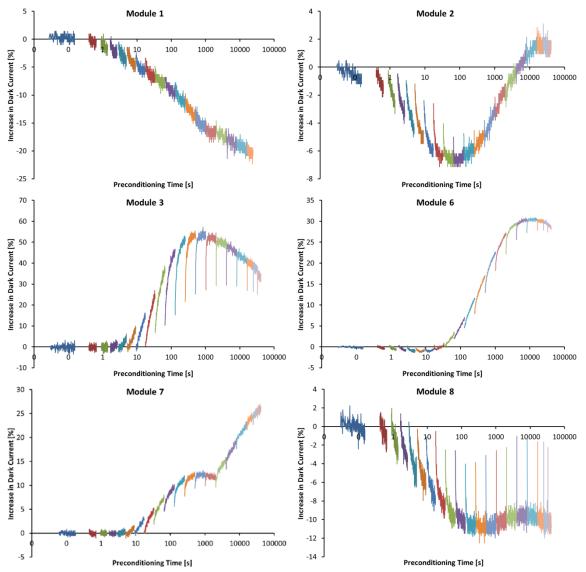

|   | 5.3 | 8 I   | Electrical bias preconditioning in modules                            | 86     |

|   | !   | 5.3.1 | 1 Experimental setup                                                  | 87     |

|   | !   | 5.3.2 | 2 Results                                                             | 88     |

|   | 5.4 | 4 5   | Spectral Response of CIGS modules                                     | 89     |

|   | !   | 5.4.1 | 1 Details of the spectral response measurement system                 | 90     |

|   | !   | 5.4.2 | 2 Results                                                             | 92     |

|   | 5.5 | 5 I   | Millisecond timescale preconditioning                                 | 93     |

|   | !   | 5.5.1 | 1 Module measurements                                                 | 93     |

|   | !   | 5.5.2 | 2 Single Cell Measurements                                            | 95     |

|   | 5.6 | 5 A   | Automated electrical bias preconditioning with I-V, C-V and dar       | ·k I-V |

|   | mc  | onito | oring                                                                 | 100    |

|   | !   | 5.6.1 | 1 Method                                                              | 100    |

|   | !   | 5.6.2 | 2 Results                                                             | 101    |

|   | 5.7 | 7 (   | Conclusions                                                           | 110    |

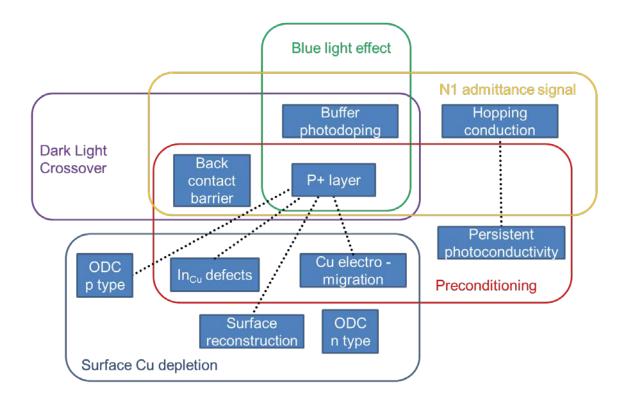

| 6 | (   | Caus  | ses of preconditioning in CIGS                                        | 111    |

|   | 6.1 | I     | Introduction                                                          | 111    |

|   | 6.2 | 2 F   | Electronic properties of CIGS devices                                 | 111    |

|   | (   | 6.2.1 | 1 N1 admittance signal                                                | 112    |

|   | (   | 6.2.2 | 2 Cross over of dark and light I-Vs                                   | 116    |

|   | (   | 6.2.3 | 3 Origin of the Copper depleted surface region                        | 117    |

|   | 6.3 | 3 (   | Origins of performance change                                         | 118    |

|   | (   | 6.3.1 | 1 Electronic transport mechanisms potentially causing metastabilities | 119    |

|   | (   | 6.3.2 | 2 Microscopic causes of preconditioning                               | 122    |

| 6.4             | 6.4 Metastable defects in CIGS |                                          |  |

|-----------------|--------------------------------|------------------------------------------|--|

| 6.4             | 4.1                            | Se-Cu di-vacancy ( $V_{Se}$ - $V_{Cu}$ ) |  |

| 6.4             | 4.2                            | III <sub>Cu</sub> defect                 |  |

| 6.5             | Kin                            | etics                                    |  |

| 6.5             | 5.1                            | Metastable defects kinetics              |  |

| 6.5             | 5.2                            | Cu-Se di-vacancy kinetics                |  |

| 6.5             | 5.3                            | III <sub>Cu</sub> defect kinetics        |  |

| 6.6             | Imp                            | plications for preconditioning138        |  |

| 6.7             | Cor                            | nclusions                                |  |

| 7 Co            | onclus                         | sions                                    |  |

| Bibliography146 |                                |                                          |  |

## 1 Introduction

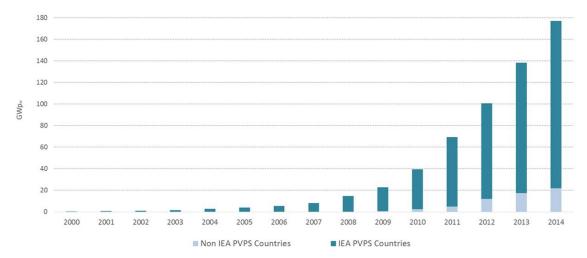

The need to produce usable energy in an environmentally sustainable manner is one of the biggest challenges of our time. Photovoltaic energy is a beautifully elegant solution to this problem. It has no moving parts, and a panel can simply be left outside and it will directly transform into electricity the solar radiation that falls on it for free every day. The lure of this abundant renewable energy source has fuelled impressive technological improvements and cost reduction over the past decades. PV system price has declined by 75% in less than 10 years [1] and uptake of PV technology has been accelerating rapidly as can be seen from the evolution of installed photovoltaic capacity in Figure 1-1. Currently there is approximately 178GW of installed photovoltaic capacity worldwide which produces roughly 1% of global electricity production. It is predicted that 540GW of installed capacity could be reached by 2019 [1,2]. It is an exciting time for solar photovoltaics as the technology rapidly approaches the inflection point where energy produced in this way becomes cheaper than conventional energy even without subsidies. This point will begin a self-sustaining explosion in the use of photovoltaics and herald a new age of renewable energy where we can finally leave the fossils in the past from which they came.

Figure 1-1: The evolution of installed photovoltaic capacity. Source IEA snapshot of global PV markets 2014 [2]. The strong exponential like growth can be taken as a reason for great optimism.

New generations of photovoltaic technology continue to provide the improvements necessary for the growth of the industry, however they often also provide fresh challenges. One of the challenges that they present is how to measure their performance under different conditions in order to predict the energy that they will produce when mounted in any particular location. For a variety of reasons this is often not a trivial task and this challenge is the overarching theme of this thesis.

Performance measurement of PV devices is an essential component of the photovoltaics industry. During manufacturing the performance of each module is measured as a quality control measure. Modules are then often sorted according to their power output with the higher performing modules achieving a higher price. Sorting of the modules also helps to improve the overall efficiency of an installed system, since low power modules in a series string will bring down the output of all the other modules in that string. Installers rely on performance measurements to compare different potential products and to model the energy yield, and therefore financial payback of solar installations. These financial models are extremely important for large installations in order to attract investment and get funding. Overall when there is a problem with performance measurements for a particular photovoltaic technology, it is a big problem.

There are a number of different technology options available for photovoltaic modules, and some of these present unique measurement challenges. Photovoltaic technologies are often categorised into crystalline silicon based vs thin film technologies, but both of these categories have an increasing number of subdivisions. Crystalline silicon is the most established technology and currently represents around 90% of the photovoltaic market [3]. Thin film technologies however are an exciting prospect for the future because they have very strong potential for cost reduction, efficiency improvement and also novel applications such as flexible modules. Within the heading thin film technologies are many different material systems, but only three main options have reached significant commercial production at present. These technologies are in order of current market size: CdTe, Cu(In,Ga)Se<sub>2</sub> (CIGS) and amorphous silicon (a-Si). While a-Si was the first thin film technology to gain a significant market share it has struggled more recently and it appears unlikely that it will be able to achieve the efficiency required to compete with other technologies. CdTe and CIGS however have both demonstrated single cell efficiencies of 22% or over, which demonstrates that modules of these technologies should be able to reach at least similar efficiencies to c-Si based technologies if not eventually surpassing them.

In order to characterise the performance of a photovoltaic device it is necessary to measure its current output as a function of the applied voltage while the cell is under illumination. This is known as the I-V curve and will also depend on the intensity and spectrum of the light illuminating the device and the temperature of the device. In order to aid comparison of devices the standard IEC 61853-1 [4] was created and is used throughout the PV community. In this standard the device temperature is 25°C and the irradiance on the device is 1000Wm<sup>-2</sup> with a defined spectrum known as AM1.5G which is based on the spectrum of solar irradiation received at sea-level when the sun is at an angle such that the light travels through 1.5 times more air mass than it would if the sun were directly overhead.

The intensity of 1000Wm<sup>-2</sup> specified in the standard is close to the maximum intensity ever received from the sun. In general is it difficult and expensive to continuously and uniformly illuminate a large area with such a high intensity, especially with a good spectral match to AM1.5. Additionally, a PV module illuminated at such high intensity will rapidly heat up to well over the 25°C specified in the standard. However, these conditions are relatively easy to achieve using a pulsed solar simulator, where the I-V curve is measured during a short flash often of around 10ms duration. Pulsed simulators are by far the most common method for indoor performance measurements of photovoltaic modules.

One of the problems for performance measurement that is often encountered is that of highly capacitive modules. This problem limits the rate at which the I-V curve can be measured without distortion, and presents a problem for using short pulse simulators to characterise devices. Large capacitance is a problem particularly prevalent in high efficiency modules, for example Panasonic HIT modules, Sunpower back-contact modules and Yingli PANDA bulk n-type modules. It is therefore a problem that is quite likely to persist and become even more troublesome in the future. There are a number of solutions to this problem, including longer pulse simulators, and measuring the I-V curve in sections using several illumination pulses. Other methods try to reduce the measurement time using non-linear voltage ramps. In this thesis the problem of quickly measuring high capacitance modules is addressed and a new method is presented that uses direct measurement of the module capacitance to calculate the fastest rate the voltage can be swept for a given desired accuracy of the measurement.

For many of the thin film PV technologies one of the biggest characterisation problems is that their measured efficiency is not a constant value but varies during the course of normal operation depending of the exposure history of the modules. In a-Si this problem manifests itself as a seasonal variation in efficiency due to the Staebler-Wronski effect [5]. This type of module gradually reduces in efficiency with light exposure, however the effect is reversed by heating. The Staebler-Wronski effect has been well studied and is now relatively well understood at a material level [6]. A related phenomenon In CIGS, normally called the "light soaking effect" or "preconditioning", has also been extensively studied but is contrastingly less well understood. The effects of light exposure are more favourable in CIGS than in amorphous silicon and it is usually observed that the efficiency improves during light exposure. The performance differences between measurements of CIGS modules made immediately after dark storage and those made after light soaking vary significantly depending on the particular module but can be quite large, improvements in efficiency of over 10% are not uncommon. The preconditioning state of the module therefore has a high impact of the measured efficiency.

A common procedure aiming for consistent measurement is to light soak the modules, wait for them to cool down and then measure them in a standard pulsed simulator. The justification for this procedure is the modules are often seen to increase in efficiency much more quickly than they relax, so that in normal operation the modules will operate for the majority of the time at the increased efficiency observed after light soaking. However the procedure is not well defined, with many manufacturers suggesting different details for the preconditioning routines and measured values often depending strongly on those precise details in a seemingly inexplicable manner. One of the main reasons for the confusion is a basic lack of understanding of the causes of the effect. Despite the fact that metastabilities in CIGS have been extensively studied, there is no universally accepted model for the cause of preconditioning in CIGS. Experimental observations of metastabilities in CIGS produce a variety of different behaviours depending on the fabrication of the device, which is undoubtedly part of the reason for the lack of agreement in the literature. Another reason is because of a lack of measurement possibilities that directly test one theory over another, so that the same experimental results can be interpreted in a variety of different ways. Nevertheless, there are some theories that have gained a significant amount of backing.

Developing a repeatable measurement routine for CIGS modules forms a major theme of this thesis. The effect of preconditioning applied either by light soaking or voltage bias is measured for a variety of CIGS devices and the rates at which the preconditioning occurs and subsequently relaxes are also measured. During the observations an unexpected, additional preconditioning effect was discovered which occurs and relaxes on a much faster timescale than usual. The effect was investigated further and appears be of a different origin from the previously known preconditioning effect, however the effects are not independent.

The theoretical models for the causes of preconditioning in CIGS are numerous and related in a complicated manner to many other controversial aspects of device physics in CIGS. In the final chapter these theories are explored in detail, and discussed in relation to the problem measurement problem. In particular a rate model for the preconditioning is created and observed to represent the observed data. The further implications of this model for device preconditioning and measurement are explored.

# 2 Principles of Photovoltaics

This chapter introduces the basic principles of photovoltaics. These principles are the fundamental understandings that lay the foundation for the work in this thesis. The operation of photovoltaics will be described followed by details of the specific technologies relevant to this thesis. Finally performance measurements for photovoltaics will be discussed.

### 2.1 Operation

#### 2.1.1 Basic operation principle

The basic principle of any photovoltaic device is to take energy from incident light falling on the device and turn it directly into electrical energy. Photons of electromagnetic energy are absorbed by electrons in a material increasing the potential energy of those electrons and creating a potential difference / voltage between the excited electron and the empty states they previously occupied. The electrons are then physically separated from the empty states. When an external circuit is provided for the electron to relax back to their initial state, the potential energy of the electrons creates a voltage across the external circuit which causes current to flow. The voltage and current can then be used in the external circuit to do useful work, for example making a cup of tea.

The most successful photovoltaic devices to date are based on PN junctions of inorganic semiconductors. In semiconductors there are two continuous bands of allowable energy levels for electrons separated by a forbidden energy gap known as the band gap. The energy states of the lower energy (valence) band are mostly full of electrons whereas the higher energy (conduction) band is mostly empty. The empty energy states in the valence band take on the properties of new particles, known as holes, which can be considered instead of trying to deal with the enormous number of electrons. When nearly fill the valence band. The holes have the opposite charge to electrons. When photons of sufficient energy are incident on the semiconductor they can be absorbed and excite electrons from the valence band to the conduction band, leaving a hole in the valence band. The hole and the electron are both free to move in the semiconductor and are physically separated in space by the effect of the PN junction.

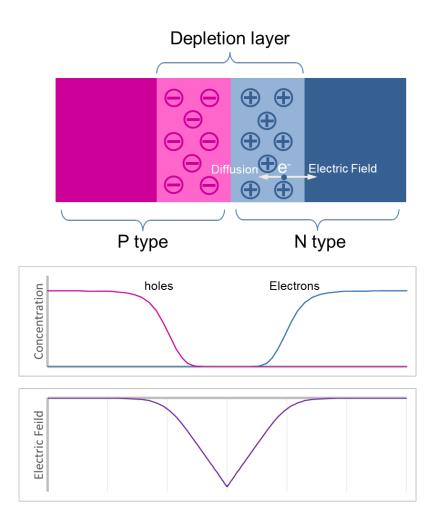

A PN junction is created by connecting an electron rich (n type) semiconductor directly to a hole (rich p) type semiconductor. When this happens the electrons from the n type region diffuse into the p type region and holes from the p type region diffuse into the n type region. When the electrons and holes diffuse they leave behind a net charge, which creates an electric field opposing further diffusion of holes so that equilibrium is reached between the diffusion of the carriers and the electric field as shown in Figure 2-1. When a photon is absorbed it creates an electron hole pair at the point of absorption, disrupting the equilibrium. The minority carrier from the pair is pushed by the electric field to the other side of the junction separating the electronic charges. When an external circuit is connected to opposite sides of the junction the excess carriers flow around the external circuit.

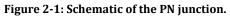

Because of the band gap in semiconductors, incoming photons can only excite carriers from one band to another if they have energy greater than the band gap. After a carrier is excited by an incoming photon it rapidly loses energy until it reaches an energy close to the band edge and comes into a quasi-thermal equilibrium with the other excited carriers. This process is called thermalisation and it occurs very rapidly, on the order of picoseconds [7]. Under these conditions the carriers are not in equilibrium, but there can be considered to be a quasi-equilibrium separately within each band because the processes of generation and recombination between the bands are much slower than the thermalisation within the bands. Any energy of an absorbed photon greater than the bandgap of the semiconductor is lost to thermalisation and the energy of photons with lower energy than the band gap is lost because they never create an electron hole pair. The other unavoidable loss mechanism is radiative recombination which cannot be avoided because it is the reverse of the absorption process. For a continuous spectrum of incident irradiance, increasing the bandgap increases the voltage of the cell but reduce its current because fewer photons have sufficient energy to excite electrons. This trade off means that single bandgap photovoltaic cells operating under the sun have a maximum efficiency which depends on the bandgap of the device. This maximum was first calculated by Shockley and Queisser and is hence known as the Shockley-Queisser limit [8]. Figure 2-2 show the graph of efficiency Vs bandgap for the standard solar spectrum. There are two peaks in efficiency of roughly 33.5% at 1.15eV and 1.4eV. In real devices there are other losses which prevent the Shockley-Queisser limit being reached in practice. These non-ideal losses can be grouped into optical losses which are due to incomplete absorption of the incoming radiation, and electrical losses due to recombination of photo-generated electrons and holes, or voltage drops due to series resistance.

Figure 2-2: Cell efficiency Vs bandgap.

#### 2.1.2 Solar Resource

The sun irradiates the earth with 175,000 TW of light. It drives the weather systems and provides the energy which sustains the bountiful life on our planet. Through photovoltaics it is possible to harness this power to provide for our energy needs as well.

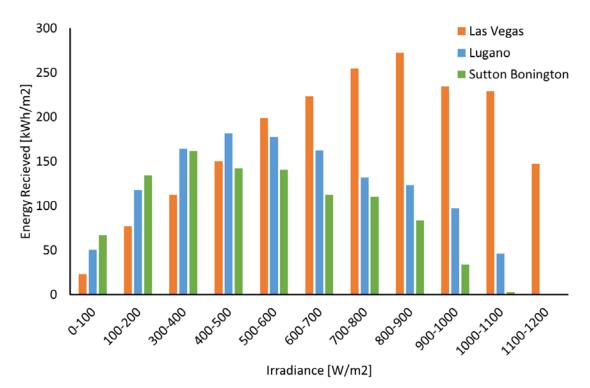

The intensity of the sunlight arriving at the earth is highly variable. There is a highly predictable geometrical component to this variability caused by the orbit and rotation of the earth. These variations cause the cycles of day and night, summer and winter. There is also a much less predictable component to the variation caused by weather. The maximum intensity of sunlight at ground level on a clear sky day is roughly equal to 1000Wm<sup>-2</sup>. This conveniently round number is referred to as 1 sun illumination and is the intensity used for standard performance test measurements of photovoltaic devices. Statically mounted photovoltaics only receive this intensity of illumination for a very small percentage of the time and are usually operating at lower intensities. Figure 2-3 shows the distribution of annual solar irradiation at different intensities in three different locations. It can be seen that location has a strong impact, which is a combination of the effect of different latitude and different climatic conditions.

Figure 2-3: The distribution for the fraction of power received on a horizontal plane for different irradiances in: Sutton Bonington, UK; Las Vegas; USA; and Lugano, Switzerland. Data is taken from Meteonorm.

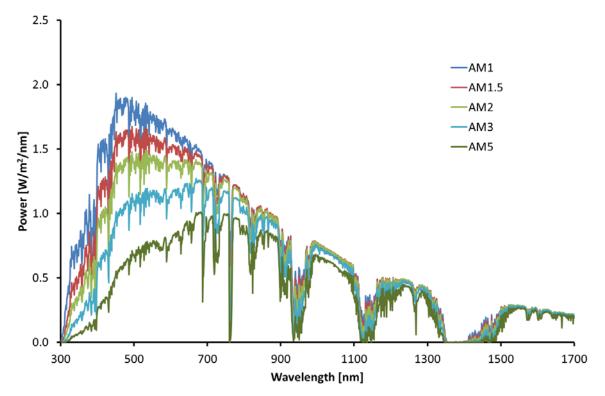

The surface of the sun is a plasma consisting of mainly of hydrogen and helium with a temperature of approximately 6000K. The spectrum of the irradiance emitted by the sun is matched closely to the theoretical black body radiation for 6000K. This is the spectrum of irradiation on satellites, but for terrestrial photovoltaics the spectrum is considerably altered by absorption and scattering in the atmosphere. The inclination of the sun has a large impact on the irradiation arriving at the ground level because it changes the path length of the light through the atmosphere so more light is absorbed. Because of this and other atmospheric factors the spectrum of solar irradiation is not constant and varies throughout the day. The path length of the light through the atmosphere is usually described in terms of the air mass number (AM), which is the mass of air travelled through relative to that when the sun is directly overhead. Examples of typical clear sky spectra at different air mass are shown in Figure 2-4. For performance measurements, an AM1.5 spectrum is used, this corresponds to the spectrum for a panel with a 37° tilt and a sun elevation of 41.8° (IEC 60904-3). It was constructed to be roughly representative of the average spectrum over the whole of the US over the course of a year.

Figure 2-4: The direct incidence solar spectrum at different air mass values, calculated using SMARTS [9]

#### 2.1.3 Band diagrams

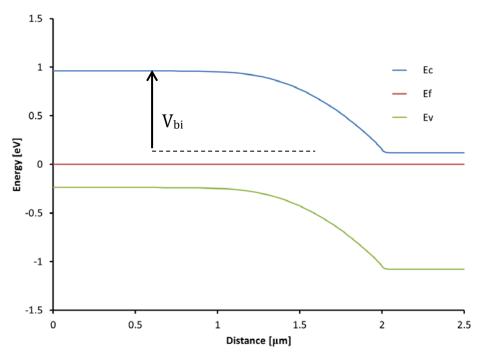

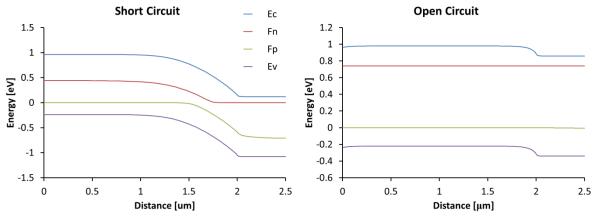

Band diagrams are the easiest way to visualise what is happening in solar cells. The band diagram displays the energy level of the conduction and valence band edges and the Fermi levels as a function of the distance through the device. The Fermi level ( $E_f$ ) represents the average electrochemical potential energy of the charge carriers (electrons and holes). Variation in the Fermi level would represent a driving force for carriers through the device so in equilibrium the Fermi level is flat. As previously discussed, outside of equilibrium the electrons and holes can be considered to form two separate quasi equilibrium populations. There are then separate quasi Fermi levels for the electrons ( $E_{fn}$ ) and holes ( $E_{fp}$ ). The closer the Fermi level is to the relevant band the higher the number of carriers is, as described by the Fermi-Dirac distribution. Electrons move in the direction of decreasing  $E_{fn}$  whereas holes move in the direction of increasing  $E_{Fp}$ . The band diagrams in this section were all created using the photovoltaic device simulation package SCAPS [10].

Figure 2-5: Band diagram of a PN junction in equilibrium.

In the dark at zero bias a photovoltaic cell is in equilibrium. Figure 2-5 shows the band diagram of a PN junction in these conditions. The carriers are in equilibrium between the bands as well as within the bands so there is only one Fermi level and it is flat. The device in the diagram is more heavily doped on the n type side. Since the charge on both sides of the junction must balance, the depleted area on the lightly doped side is much

wider and the result is that the majority of the band bending occurs on the p type side of the junction. The built in voltage is an important quantity which is also illustrated.

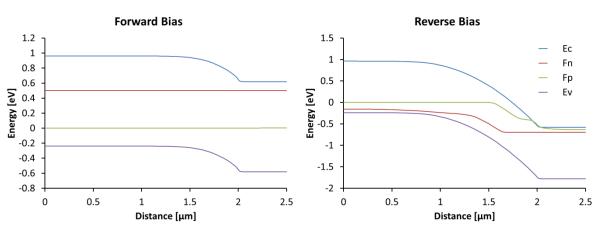

Figure 2-6 band diagram of PN junction in the dark under forward and reverse bias

When an external bias is applied to the cell, charge flows and there is no longer equilibrium in the device, so the Fermi levels split. The bias for a device is dictated by the difference in the majority carrier Fermi level at the two contacts. That is, the difference between the  $E_{Fn}$  on the n side contact and  $E_{Fp}$  on the p side contact. The Fermi level at the contacts follows the majority carrier Fermi level in the semiconductor at that contact. Forward bias reduces the band bending in the device until the bias is equal to the built in voltage, when there is no band banding as shown in Figure 2-6.

Illumination causes generation of carriers and massively increases the concentration of minority carriers. This moves the minority carrier Fermi levels significantly towards the relevant bands. Figure 2-7 shows the illuminated PN junction under different bias conditions. At short circuit the Fermi level of the contacts is the same on both sides of the device. In the junction region there is a significant gradient of the quasi Fermi levels which shows there is a strong force on the carriers which generates the short circuit

current. The increase in minority carriers has reduced the diffusion gradient without reducing the electric field so the carriers now move in the direction dictated by the built in field.

At open circuit there is no current flow. The Fermi level difference between the contacts increases and the band bending flattens out until the quasi Fermi levels are virtually flat. They may in fact slope gradually in opposite directions such that the currents from each carrier type cancel out. This is due to the generation and recombination profiles not matching. For example most of the carriers are generated near the front of the device where the light is incident, but there may be higher recombination at the back contact which causes movement of both carrier types towards the back.

In between the extremes of the open circuit and short circuit conditions there is a voltage difference across and a current flow around the external circuit. The amount of power dissipated by the external circuit depends on the voltage and reaches the maximum power point ( $P_{mpp}$ ) at the voltage  $V_{mpp}$  and current  $I_{mpp}$ .

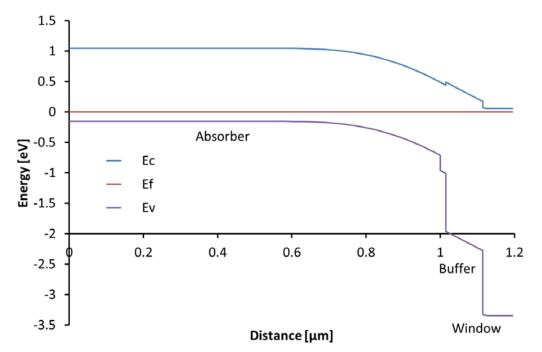

Figure 2-8: Band diagram of an absorber-buffer-window hetero-junction solar cell

Up to now the band diagrams displayed have been homo-junction devices, meaning the semiconductor on both sides of the junction is the same material with different doping. This device structure is typical of Si and GaAs solar cells. Heterojunctions can also be formed between different semiconductors. A common architecture for thin film devices is the absorber-buffer-window structure shown in Figure 2-8. In particular this is the

structure of CIGS devices, which feature prominently in this thesis. In a heterojunction device the band gap of the different semiconductors is not the same so there is a discontinuity known as a band offset at each of the interfaces.

Light enters the cell through the window layer which is a transparent conductor. Light is primarily absorbed in the absorber layer where the majority of the photocurrent generation occurs. The buffer layer improves device efficiency through a number of mechanisms including, improving band alignment, reducing surface recombination and refractive index matching.

#### 2.1.4 Transport equations

In order to quantitatively understand photovoltaic cells we need equations for the movement of charge carriers within the cell, these are called the transport equations.

As was mentioned previously, the carriers within each band can be considered to be in a thermal equilibrium within the band. This means that the probability of carriers occupying an energy level of energy E follows the Fermi-Dirac distribution

$$f(E, E_f, T) = \frac{1}{1 + \exp((E - E_f)/kT)}$$

2.1

Where  $E_f$  is the fermi level which represents the average electrochemical energy of the carriers within the band. In general there are two Fermi levels, one for electrons in the conduction band ( $E_{f_n}$ ) and one for holes in the valence band ( $E_{f_p}$ ). In the dark and at zero bias there is equilibrium between the bands as well as within the bands and the Fermi levels are the same. The number of carriers is related to the Fermi level by the equations

$$n(E_{Fn},T) = \int_{E_C}^{\infty} g(E)f(E,E_{Fn},T)dE$$

$$p(E_{Fp},T) = \int_{-\infty}^{E_V} g(E)f(E,E_{Fp},T)dE$$

2.2

Where g(E) is the density of states, and  $E_c$ ,  $E_v$  are the conduction and valence band edge energies respectively. When the Fermi level is further than kT from the band edge the Fermi Dirac distribution can be approximated very well by the Boltzmann distribution

$$f(E, E_f, T) = \exp((E_f - E)/kT)$$

2.3

And since only the states very close to the band edge are occupied the density of states at the conduction band can usually be approximated by an effective density of states at the band edge energies. This allows the integrals in 2.2 to be easily solved and gives the carrier concentrations as a function of the Fermi levels and the temperature

$$n(E_{f_n}, T) = N_c \exp((E_{f_n} - E_c)/kT)$$

$$p(E_{f_p}, T) = N_v \exp((E_v - E_{f_p})/kT)$$

2.4

Where  $N_c$  and  $N_v$  are the effective conduction band and valence band density of states. A useful relation can be found by taking the product of these two equations at equilibrium

$$np = n_i^2 = N_c N_v \exp\left(-E_g/kT\right)$$

2.5

Where  $n_i$  is the intrinsic carrier density. This relation shows that at equilibrium the product of the carrier densities is a constant throughout each semiconductor layer. It is independent of the position relative to the junction and it is even independent of the doping level. Outside of equilibrium the product becomes

$$np = n_i^2 \exp(\Delta E_f / kT)$$

2.6

Where  $\Delta E_f$  is the separation between the Fermi levels.

The gradient of the electrochemical potential is the driving force for the movement of the carriers. The currents of the carriers can be expressed as

$$j_n = \mu_n n \nabla E_{f_n}$$

$$j_p = \mu_p p \nabla E_{f_p}$$

2.7

Where  $\mu_n$ ,  $\mu_p$  are the mobilities of electrons and holes. The gradients of the Fermi levels can be found from taking the gradient of equation 2.4

$$j_n = \mu_n (n \nabla E_c - nkT \nabla \ln(N_c)) + q D_n \nabla n$$

$$j_p = \mu_p (p \nabla E_v + pkT \nabla \ln(N_v)) - q D_p \nabla p$$

2.8

Where the Einstein relation has been used to replace the mobility with the diffusion constant D. In compositionally invariant materials the band energies depend only on the electric field (F) as  $\nabla E_c = \nabla E_v = qF$  and the conduction band density of states is constant. In this case

$$j_n = q\mu_n Fn + qD_n \nabla n$$

$$j_p = q\mu_p Fp - qD_p \nabla p$$

2.9

The first term in these equations is known as drift. It comes from the action of the electric field on the carriers. The second term is the diffusion term that comes from the concentration gradient of the carriers. For materials that vary in composition there are additional effective force fields caused by variations in bandgap, electron affinity and band edge density of states. These effective forces can be utilised in devices, for example some devices deliberately widen the bandgap of the absorber layer near the back contact to create an effective field which reduces recombination at the back surface.

In quasi thermal equilibrium the carrier densities are constant which gives the continuity equations

$$1/q\nabla \cdot j_n + G - R = 0$$

-1/q\nabla \cdot j\_p + G - R = 0

2.10

Where G and R are the net generation and recombination rates. These combine with the current equations 2.9 to give

$$D_n \nabla^2 n + \mu_n n \nabla \cdot F + \mu_n F \nabla \cdot n + G - R = 0$$

$$D_p \nabla^2 p - \mu_p p \nabla \cdot F - \mu_p F \nabla \cdot p + G - R = 0$$

2.11

There are several different mechanisms for recombination that are discussed in the next section. The main generation comes from optical excitation.

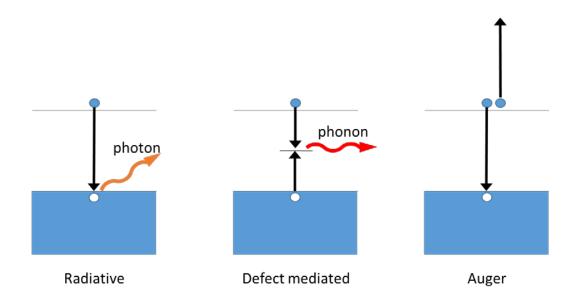

#### 2.1.5 Recombination mechanisms

In real solar cells the separation of excited electrons and holes is not perfect and some recombine in the device instead of travelling around the external circuit, reducing the current and voltage that the device can produce. In a perfect device the only recombination mechanism is radiative, which is the reverse process by which the photons were absorbed. In real devices there are other recombination mechanisms that limit the device before the radiative recombination limit.

Recombination mechanisms can be classified according to where the excess energy is transferred. In the case of radiative recombination the energy is transferred to a photon. There are two more cases which are the energy being transferred to another carrier (Auger recombination) or the energy being transferred to a vibration of the crystal lattice (a phonon) through defect recombination. These three recombination mechanisms are illustrated schematically in Figure 2-9. In most devices defect related

recombination is the dominant mechanism, although in some high efficiency devices Auger recombination is dominant.

#### Figure 2-9: Schematic of different recombination mechanisms

If a defect introduces a localised state with an energy level in the band gap then that energy level provides an intermediate step for the relaxation of the electron by absorbing alternately electrons and then holes. After a carrier is captured by the localised state it can either be re emitted, in which case recombination has not occurred, or a carrier of the opposite type can be captured and recombination has occurred. This type of recombination is known as Shockley Read Hall (SRH) recombination. The net rate for SRH recombination is given by the equation [7]

$$R = \frac{np - n_i^2}{\tau_{n,SRH}(p + p^*) + \tau_{p,SRH}(n + n^*)}$$

2.12

Where  $\tau_{n,SRH}$ ,  $\tau_{p,SRH}$  are the SRH lifetimes for electrons and holes. n\* and p\* are the auxiliary carrier densities, they are the carrier densities that would be realised if the Fermi level were at the trap level. The auxiliary carrier densities are high when the trap level is close the band edge, so from equation 2.12 we can see that in this case the recombination rate are slow. Physically this is because when a defect level has an energy close to the band edge the activation energy for a trapped carrier to be reemitted from the defect back to the nearby band becomes small and so the probability of that occurring becomes large, much larger than the probability of the carrier being annihilated by a carrier of the opposite type. Thus defects with an energy level close to

the band edges are known as trap states because they continuously trap and re-emit carriers but do not act as efficient recombination centres. Defects with energy levels near the middle of the bandgap on the other hand are efficient at causing recombination and are known as recombination centres [7].

Radiative recombination is the direct recombination of an electron and a hole, with the emission of a photon. This reverse process is always be present and is the limiting process in an optimum device. Its rate is given by

$$R = B(np - n_i^2) \tag{2.13}$$

Where B is the radiative recombination constant.

Auger recombination is a three carrier process where the energy from the annihilation of an electron hole pair is transferred to extra kinetic energy for the third carrier. Because it involves the collision of two carriers of the same type the rate depends strongly on the density of the majority carrier, and for very high doping the rate can become high. This eventually counteracts the beneficial increase in built in potential which also comes from increasing the doping. The rate for auger recombination is

$$R = C_n(n^2p - n_0^2p_0) + C_p(p^2n - p_0^2n_0)$$

2.14

Where  $C_n$ ,  $C_p$  are the auger coefficients. The first term is for the case where the excess energy is transferred to an electron (as in Figure 2-9) and the second term is for the case where the energy is transferred to a hole. In p type materials the first term is negligible and for n type materials the second term is negligible.

#### 2.1.6 Depletion approximation

The equations 2.11 and 2.12 can be solved numerically in device simulation packages and this is the most accurate way to proceed. However by making an approximation, known as the depletion approximation, the equations can be solved analytically. In this way a better understanding of the devices can be developed along with some useful equations.

The depletion approximation states that for the purpose of calculating the electric field in a region near the junction the semiconductor is completely depleted of carriers. The net charge in this region is equal to the doping density. This is called the space charge region (SCR). The region outside of this is called the quasi neutral region (QNR), and it is approximated to be completely neutral of charge and have no electric field. Using this approximation along with Poisson's equation the size of the depletion region on each side of the junction can be found

$$w_n = \sqrt{\frac{2\varepsilon_p \varepsilon_n N_A V_{bi}}{q N_D (\varepsilon_p N_A + \varepsilon_n N_D)}}$$

2.15

And

$$w_p = \sqrt{\frac{2\varepsilon_p \varepsilon_n N_D V_{bi}}{q N_A (\varepsilon_p N_A + \varepsilon_n N_D)}}$$

2.16

Where  $w_n$ ,  $w_p$  are the depletion widths of the n and p sides of the junction respectively,  $N_D / N_A$  are the doping densities of the n / p sides and  $\varepsilon_n$ ,  $\varepsilon_p$  are the permittivity on the n/p side of the junction. For a one sided junction, where one side of the junction is much more heavily doped than the other, the depletion width on the lightly doped side is much larger and most of the voltage drops on this side. For an n<sup>+</sup>-p device the total width of the space charge region ( $w_{scr}$ ) becomes

$$w_{scr} = w_p = \sqrt{\frac{2\varepsilon_p V_{bi}}{qN_A}}$$

2.17

When a bias V is applied to the device the band bending and width of the space charge region changes according to

$$w_{scr} \approx \sqrt{\frac{2\varepsilon_p (V_{bi} - V)}{qN_A}}$$

2.18

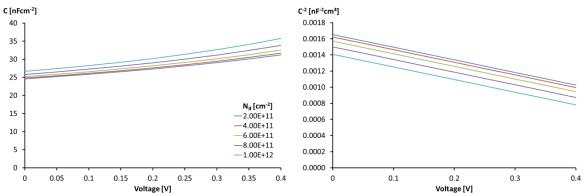

The change in the depletion width with voltage creates a stored charge and gives rise to a capacitance. This mechanism of charge storage in photovoltaic devices is known as the junction capacitance and it can be a useful way to determine the doping density  $N_D$ ,  $N_A$  as discussed further in section 3.1.

The depletion approximation can be used to solve for the current through the device. It is found that the current is given by

$$j = j_0 \left( \exp\left(\frac{qV_j}{AkT}\right) - 1 \right) - J_{ph}$$

2.19

Where  $J_{ph}$  is the photocurrent; A is an ideality factor which depends of the dominant recombination mechanism and  $j_0$  is given by

$$j_0 = j_{00} \exp\left(\frac{E_a}{AkT}\right)$$

2.20

Where  $J_{00}$  is a constant and Ea is the activation energy of the dominant recombination mechanism, which will often be equal to the bandgap energy.

The ideality factors for different recombination mechanisms are shown in Table 2-1.

| Dominant recombination mechanism | Ideality factor |

|----------------------------------|-----------------|

| SRH recombination in the SCR     | 2               |

| SRH recombination in the QNR     | 1               |

| Interface recombination          | 1               |

| Auger recombination              | 2/3             |

| Radiative recombination          | 1               |

Table 2-1: Ideality factor for different dominant recombination mechanisms

Often the dominant recombination mechanism is different at low and high voltages. For example at low voltages SRH recombination in the space charge region can dominate giving an ideality factor of 2, and then at higher voltages SRH recombination in the quasi neutral region can become dominant since with an ideality factor of 1 it has a stronger voltage dependence.

#### 2.1.7 Defects

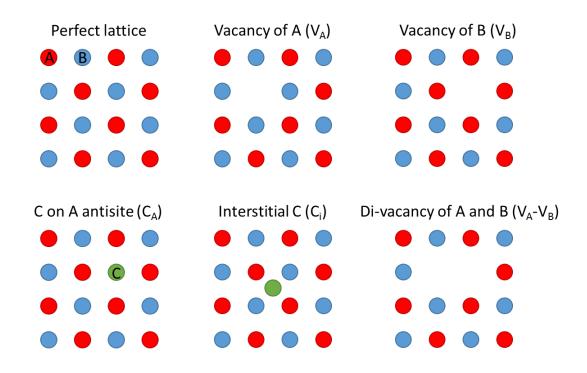

Shockley Read Hall recombination via defects was discussed in section 2.1.5. The defects through which this occurs are now discussed in more detail. There are many different types of possible defect and they cover a large range of scales. Point defects are the smallest, they are atomic level defects in the periodicity of the lattice, caused by displaced or missing atoms, or incorporation of impurity atoms. There are also larger defects, which extend over a larger number of dimensions: 1D Line defects and 2D surface or grain boundary defects. Finally there are defects of the device rather than material defects, such as cracks or shunt pathways where a layer is missing in a small region. All of these defects have very important implications for device operation, however the discussion here is restricted to point defects, knowledge of which becomes necessary in chapter 5.

Figure 2-10 is a schematic of some of the different types of point defect, along with the notation used to denote them.

Figure 2-10: Schematic of different types of point defect in the fictional lattice composed of atoms of A and B. The element C is an extrinsic impurity.

The most basic point defects are vacancies, anti-sites and interstitials which are respectively missing atoms, atoms on the wrong site, and atoms inserted between normal lattice points. Complexes can form from combination of the basic defects, the  $V_{A}$ - $V_{B}$  defect from Figure 2-10 is an example of a defect complex where two vacancies are paired together. Point defects can be intrinsic, meaning that they contain only atoms native to the lattice, as in the case of the examples  $V_{A}$ ,  $V_{B}$ , and  $V_{A}$ - $V_{B}$  in Figure 2-10. Alternatively if a defect contains impurity atoms not normally found in the lattice it is called an extrinsic defect.  $C_{A}$  and  $C_{i}$  are both examples of extrinsic defects. Point defects can introduce localised electronic levels within the bandgap of a semiconductor and depending on where within the bandgap the energy level lies they can act either as dopants, trap states or recombination centres.

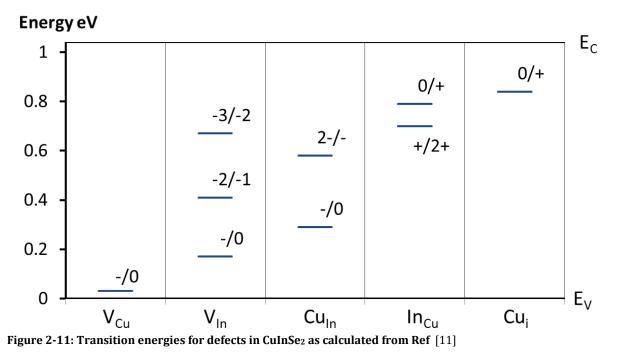

The transition energy of a defect is the energy level of the Fermi level when there is equal probability of the defect having either of two charge states. These defect transitions are often depicted as in Figure 2-11 which shows the example defect transition energy levels calculated for CIGS [11].

The transition energy is often called the energy level of the defect and considered to be the energy of an electron that occupies the electronic state. However this is not really true since often when the electron occupies the state it then interacts with the lattice causing the atoms to move and relax to a lower energy positions. This in turn changes the energy of the electronic state [12]. This effect is usually known as lattice relaxation. In the common situation where the lattice relaxation is negligible, then the transition energy of the defect can be considered as the energy level for the electron occupying the localised state. Lattice relaxation can be observed for example in the difference between the energy of absorption and luminescence from a defect [12]. When the lattice relaxation is large the character of the defect can completely change, for example changing from a shallow to deep, or donor to acceptor. These types of defect can also exist in a metastable condition where they are thermodynamically less stable than an alternative configuration, due to an activation barrier of transition between the two different states. An example of this kind of metastable defect is the DX centre in AlGaAs, which is one of the best studied cases. Metastable defects have also been observed in several of the materials relevant to CIGS photovoltaic devices: MoSe<sub>2</sub> [13], ZnO [14] and also the CIGS absorber itself [15,16]. This type of defect appears to be at least partly responsible for the metastable behaviour of device performance observed in CIGS based photovoltaics.

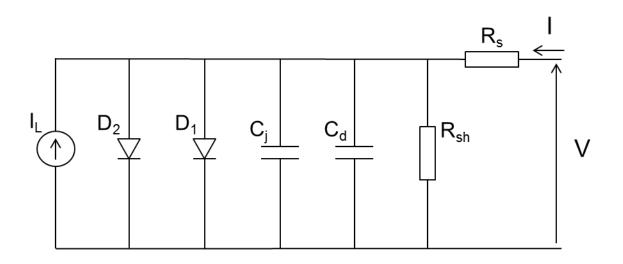

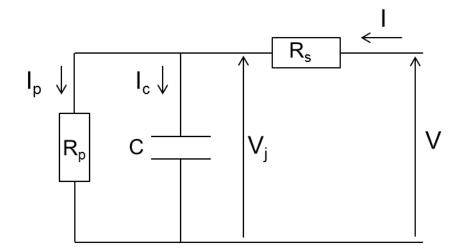

#### 2.1.8 Equivalent circuits

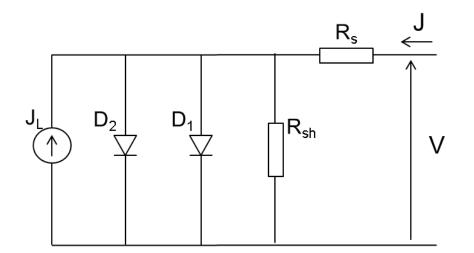

Equivalent circuits are representations of the electrical properties of a photovoltaic device using standard electrical components. They are a very useful tool for modelling and analysing I-V curves. A typical equivalent circuit is shown in Figure 2-12. In this circuit there is a constant current source which represents the generation of carriers by the incident light. In parallel with this there are two diodes, which represent different types of recombination. One diode has an ideality factor close to 1 and the other has an ideality factor close to 2. The diode with ideality factor 2 represents SCR recombination and also interface recombination. The diode with ideality factor 1 represents QNR recombination. In general these are the largest recombination pathways, but if Auger recombination is significant a diode with ideality factor of 2/3 should be included in the equivalent circuit model. Often, to make the model fit I-V measurement data of real solar cells, ideality factors slightly different from the theoretical values of 1 or 2 are used. Sometimes the same diode dominates over the whole range of interest and then it is possible to successfully model the device using a circuit with only 1 diode. The remaining elements are the series and shunt resistances. The series resistance  $(R_s)$ represents ohmic losses, for example at the contacts of the device. The shunt resistance  $(R_{sh})$  represents the effects of ohmic defects, for example a small pinhole in the device allowing contact between the front and rear contacts.

Figure 2-12: Two diode equivalent circuit diagram of a solar cell

From the diode model we get an implicit equation for the solar cell current. In the case that one diode dominates the recombination current we get

$$J(V) = -J_{ph} + J_0 \left( \exp\left(-\frac{q(V+JR_s)}{AkT}\right) - 1 \right) - \frac{V+JR_s}{R_{sh}}$$

2.21

This equation can be solved numerically to show the dependence of a device on irradiance, temperature, series resistance and shunt resistance. In the special case of the open circuit voltage, and when the shunt resistance is high, the equation has a simple explicit solution.

$$V_{oc} = -\frac{AkT}{q} ln \left(\frac{j_{ph}}{j_0} + 1\right)$$

2.22

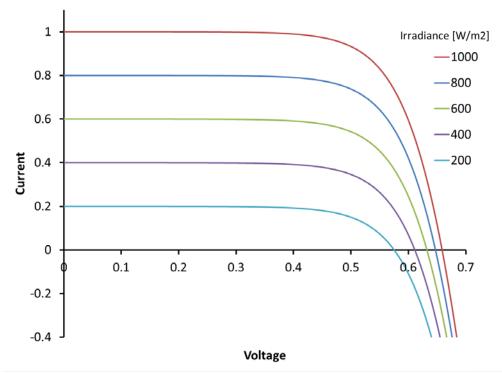

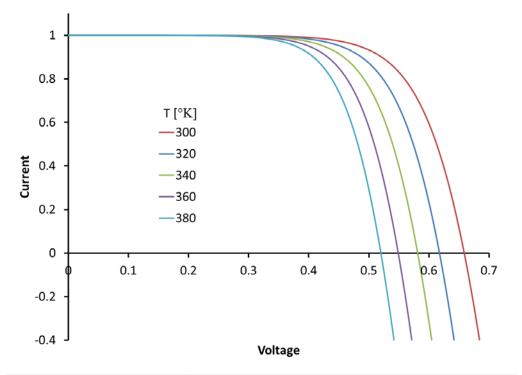

Figure 2-13 shows the I-V curve for different irradiance values, the photocurrent generated in a solar cell is linearly proportional to the incident irradiance, but the open circuit voltage also increases logarithmically with the irradiance. Figure 2-14 shows the variation of the I-V curve with temperature. The main effect is a linear decrease of Voc with temperature. There is in fact a very slight increase in current with temperature which is not evident from equation 2.22 and is caused by a slight narrowing of the bandgap with increasing temperature. For many purposes this change is small enough that Isc can be considered to be constant with temperature. For silicon the bandgap at 0°C is 1.13eV which decreases to 1.10eV at 100°C, corresponding to a 6% increase in short circuit current[17,18].

Figure 2-13: I-V curves at different irradiance values.

Figure 2-14: I-V curves at different temperatures.

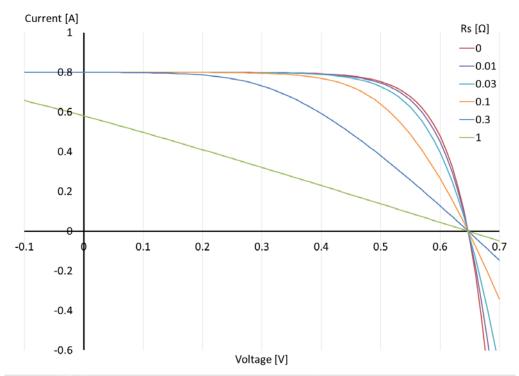

The series and shunt resistances both mainly affect the fill factor of the device but in slightly different ways. The series resistance causes a voltage drop in the device which is larger at higher currents. As the series resistance increases it reduces the slope of the I-V curve at the Voc as seen in Figure 2-15.

Figure 2-15: Effects of series resistance on I-V curves

Figure 2-16: Effects of shunt resistance on I-V curves

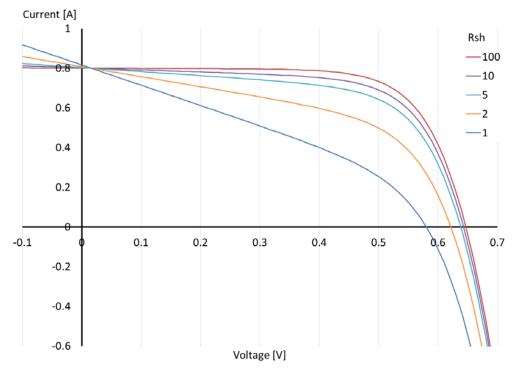

The shunt resistance works in the opposite way, a more shunted device has a lower shunt resistance, which increases the slope of the I-V curve at the Isc point. Figure 2-16 shows the effect of varying shunt resistance on the I-V curve.

#### 2.2 Different PV technologies

The first photovoltaic cell was created by Becquerel in 1839 more than 175 years ago, so it is unsurprising that since then a whole host of variations on the technology have been explored and developed. Silicon solar cells are by far the market leaders but thin film technologies based on CdTe and Cu(In,Ga)Se<sub>2</sub> absorbers also have a significant market share. Within the umbrella of Si solar cells there are many variations, including whether the cell is mono- or multi- crystalline; whether the base is p type or n type and many more. The device structures which will be relevant in the work of this thesis are the high efficiency silicon technologies, which are relevant because of their high capacitance, and the thin film CIGS technology, which is relevant because of its metastable behaviour. These relevant device structures are presented here.

#### 2.2.1 CIGS

Thin film photovoltaics are a promising technology for several reasons. They have the potential to reduce the production cost and energy payback time of photovoltaics, they can be made flexible which is an advantage for some applications and finally, because of

potentially more optimum bandgap energies, they have higher potential maximum efficiencies than silicon based devices. This is a point which has become more relevant recently as the record efficiency of thin film devices has increased rapidly over that last few years. The record at the time of writing of May 2016 stands at 22.3% for a CIGS device, which is above the record for multi-crystalline silicon at 21.3% and starting to approach the 25.6% efficiency record for a Si heterostructure device[19]. The structure of a typical CIGS solar cell is shown in Figure 2-17.

| AZO Window layer    | ~0.3µm  |

|---------------------|---------|

| i-ZnO               | ~0.05µm |

| CdS buffer layer    | ~0.05µm |

| CIGS absorber layer | ~2µm    |

| Mo back contact     | ~1µm    |

| Glass               |         |

|                     |         |

#### Figure 2-17: CIGS device structure.

In the language of thin film photovoltaics, the CIGS layer is the absorber. It is an intrinsically p type polycrystalline semiconductor  $Cu(In_x,Ga_{1-x})(Se_{2y},S_{2-2y})$  with a variable bandgap depending on the relative ratio of In/In+Ga and S/S+Se. The bandgap of the absorber layer can be varied across the range 1.0eV to 1.7eV, although in practice the best devices are made with a bandgap of around 1.15eV. The window layer is a transparent conductor, usually ZnO:Al (AZO). It acts both as the n-type part of the junction and also to conduct current laterally out of the device. The buffer layer is not completely necessary to form a pn junction but it significantly improves the performance of the device. Various different materials can be used for the buffer layer, the most common is CdS but many other options are available [20]. There are a many different variables in CIGS device construction which is reflected in the way that many of the devices have very different characteristics, as will be seen later in the sections on preconditioning in these devices.

#### 2.2.2 High efficiency Si concepts

Heterojunction with Intrinsic Thin layer (HIT) photovoltaics are a high efficiency Si device structure. In this device structure a thin layer of intrinsic a-Si:H is placed

between the n and the p sides of the junction as shown in Figure 2-18. The intrinsic layer provides excellent surface passivation.

| Front Grid       |        |

|------------------|--------|

| ITO Window layer | ~80nm  |

| a-Si (p+)        | ~5nm   |

| a-Si (i)         | ~5nm   |

| c-Si (n)         | ~200µm |

| a-Si (i)         | ~5nm   |

| a-Si (n+)        | ~15nm  |

| Al Back contact  |        |

#### Figure 2-18: HIT device structure.

N type device solar cells are another way to achieve higher efficiencies. The reason is that the Boron used for p type material combines with Oxygen impurities and the resulting Boron-Oxygen defect acts as a recombination centre. Using an n type base material it is possible to get wafers with fewer recombination centres and consequently higher minority carrier lifetimes and higher efficiencies.

Interestingly, the Boron-Oxygen defect is another example of a metastable defect and is responsible for the light induced degradation observed in p type Silicon solar cells [21]. Light induced degradation occurs in the first hours of light exposure and can be reversed by thermal annealing.

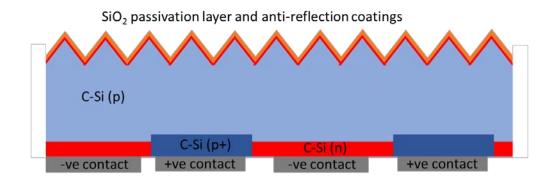

Figure 2-19: Back contact solar cell

Back contact solar cells are another concept to achieve high efficiencies where the contacts are moved to the back of the device, so no shading losses from the metallisation grid occur. In order to achieve a junction on the back of the device high diffusion lengths / minority carrier lifetimes are necessary.

### **2.3 Performance measurements**

### 2.3.1 Standard Test Conditions

The standard test conditions (STC) for reporting the efficiency of solar cells is defined in IEC 61583 [22] and is by far the most common set of conditions used for reporting photovoltaic device performance. The conditions are a device temperature of 25°C with 1000Wm<sup>-2</sup> irradiance at normal incidence and a spectrum matching the AM1.5G standard spectrum. Periods of such high irradiance usually heat the module to temperatures significantly above 25°C, however this temperature is convenient for indoor measurements because it is an easily achievable ambient temperature, and therefore device temperature. By only illuminating the module for a short period during the measurement it does not heat up significantly.

In reality, it is often not possible to achieve these conditions sufficiently closely and in particular it can be difficult to match the spectrum. Corrections should be made to account for differences between the actual measurement conditions and the reporting conditions. For small temperature deviations linear interpolation for the values of Isc, Voc, Pmpp and FF can be made. For irradiance deviations a linear correction can be made for Isc but a logarithmic interpolation should be made for Voc and a polynomial interpolation should be used for Pmpp. Another standard IEC 60891 [23] provides correction procedures for the whole I-V curve. For deviations from the standard spectrum there are two possible ways to proceed. If the reference device used to set / measure the intensity of the illumination has the same spectral response as the device under test then the spectral difference has exactly the same effect on the reference device as it has on the device under test and the spectral deviation can be ignored. An alternative option is to use spectral response measurements of the device under test and the monitor device, along with the measurement spectrum to calculate a correction factor, known as the spectral mismatch factor.

$$MMF = \frac{\int d\lambda G_{sim}(\lambda) SR_{DUT}(\lambda) \int d\lambda G_{STC}(\lambda) SR_{ref}(\lambda)}{\int d\lambda G_{STC}(\lambda) SR_{DUT}(\lambda) \int d\lambda G_{sim}(\lambda) SR_{ref}(\lambda)}$$

2.23

Where the G is the irradiance of the simulator (sim) or AM1.5 spectrum (STC); SR is the spectral response of the device under test (DUT) or the reference device (ref). It can be difficult to make absolute measurements of spectral response and often an absolute factor multiplies the result. Due to the construction of the MMF these factors in the measured spectral response cancel.

### 2.3.2 Other performance measurement conditions

Standard test conditions are useful for comparison between devices because the performance of most devices is reported at these conditions. However, for predicting the actual outdoor performance of devices the performance at STC can provide only a basic first order approximation, since the outdoor operating environment spans a wide range of conditions and the temperature and irradiance dependence is not the same in different devices. The solution given within the standard [22] is to measure the device at different conditions. Table 2-2 shows the different conditions defined for reporting, although the measurements are made over a full matrix of irradiance and temperature conditions. The NOCT (Nominal Operating Cell Temperature) condition is an attempt to include information about the amount of heating that occurs in the module when it is operating. It is defined as the temperature that the cells of the module operate at when the module is exposed to 20°C air temperature, 800Wm<sup>-2</sup> irradiance and 1ms<sup>-1</sup> wind speed. In practice other aspects such as how the module is mounted and the wind direction can also make a considerable difference to the operating temperature so this condition is not strongly defined [24]. The temperature of the module during operation can be approximated by the equation.

$$T = T_{air} + (NOCT - 20)G/800$$

2.24

Which is useful for predicting energy yields.

| Condition        | Temperature [°C] | Irradiance [Wm <sup>-2</sup> ] |

|------------------|------------------|--------------------------------|

| STC              | 25               | 1000                           |

| NOCT             | 20 (ambient)     | 800                            |

| Low Irradiance   | 25               | 200                            |

| High Temperature | 75               | 1000                           |

| Low Temperature  | 15               | 500                            |

Table 2-2: Set conditions for the reporting of photovoltaic module efficiency, as defined in IEC

While it is convenient to measure at a single condition, or a limited number of set conditions it is more representative of outdoor operating conditions to measure the energy generated over a set time period with varying conditions. Standards for this reporting including the creation of standard days are under discussion and will eventually form the standards IEC 61853-3 and 61853-4 [25].

### 2.3.3 Apparatus

The most obvious way to measure the performance of a photovoltaic device is to leave it outside in the sun and monitor its output. Outdoor performance measurements of this type have many advantages and are indispensable as the only true measurement for the operation of a photovoltaic device in its final environment. However for STC measurements there is a huge drawback to using outdoor measurements in terms of practicality since they rely on waiting for the right time of day, the right time of year and the right weather conditions. For comparison of large numbers of devices this is simply not an option and measurements must be made using a solar simulator. The brief of a solar simulator is to illuminate a photovoltaic device with light which is comparable to that of the sun. Normally the solar simulator is used for STC measurements and therefore the light output is expected to be close to that of STC.

The illumination from the simulator can be pulsed or steady state. For large areas, such as full sized modules, pulsed simulators are normally used due to excessive power requirements and thermal management of steady state simulators. The pulse length in pulsed simulators varies quite widely but is typically in the range 1 to 30ms. It is easier to control the temperature of the device under test using pulsed simulators because the illumination pulse is usually short enough that it does not induce any significant heating in the device. For small area devices it is easier to use a light source that runs continuously in a steady state and this type of simulators reduce the complication of measurement of individual cells. Steady state simulators reduce the complication of measuring the I-V curve in a short time, which can cause problems for highly capacitive devices and devices with short timescale preconditioning effects.

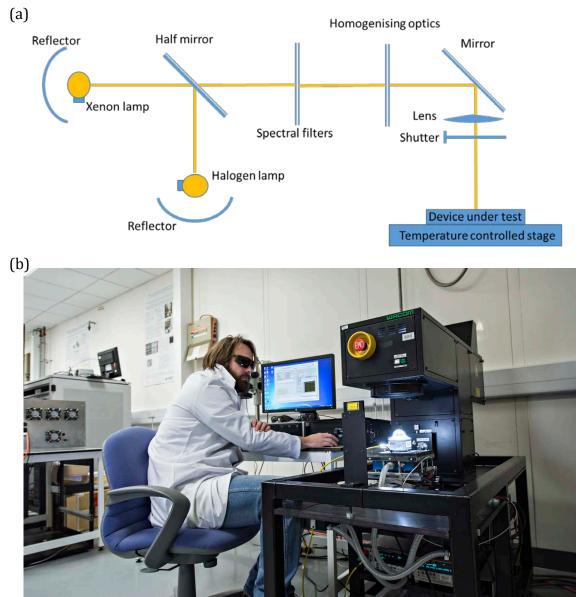

Figure 2-20 show a schematic of a steady state simulator as well as a photo of one of the best steady state simulators at CREST. The irradiance is set before the measurement using a reference device. The device under test is then placed on top of a temperature

controlled stage. A shutter is used to prevent unnecessarily long light exposure and hence heating of the device.

Figure 2-20: a) schematic of steady state solar simulator. b) Photo of the Wacom steady state simulator at CREST

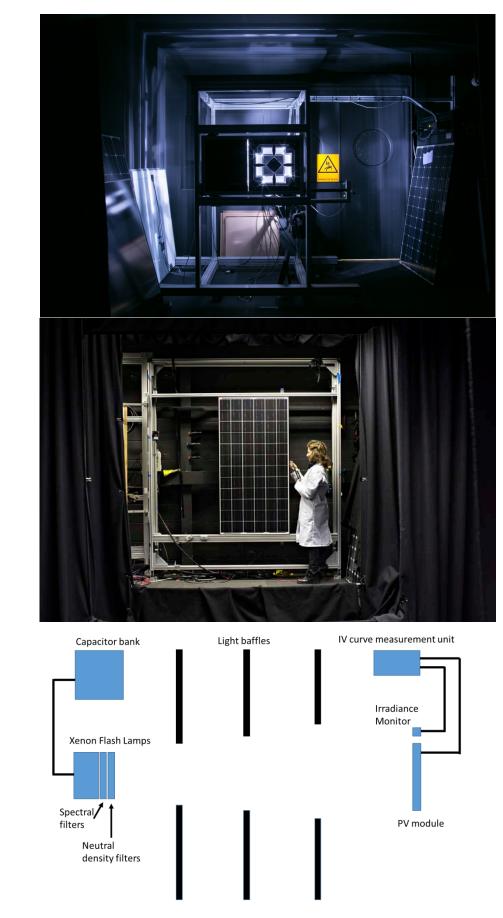

Figure 2-21 shows a schematic of a typical pulsed solar simulator along with a photo of the PASAN IIIb simulator at CREST. The simulator has a 10ms stable (flat-top) illumination pulse. During the pulse the intensity is monitored using a diode on the edge of the illuminated area. The maximum illumination area is over 2x2m which is very difficult to illuminate using a steady state simulator, although a few large area steady state simulators do exist, for example the Apollo simulator at the European Solar Test Institute.

(c)

Figure 2-21: Photos and schematic of the PASAN IIIb simulator at CREST. (a) The flash lamps from the module rack. (b) The module rack from the flash lamps. (c) Schematic.

The important parameters for the simulator are the uniformity and stability of the illumination as well as its spectral match to AM1.5. An international standard IEC 60904-9 [26] classifies the quality of simulators according to these parameters, with a grade from A to C for each aspect. High grade simulators are very important for high accuracy measurements, but it can be difficult and expensive to achieve high grade pulsed simulators with long duration pulses for example over 100ms. Sometimes using a pulsed simulator as opposed to continuous light can cause other measurement problems, which will be discussed in the ensuing chapter.

# 3 <u>Factors affecting Performance measurements of PV</u> <u>devices</u>

# 3.1 Capacitance

A capacitor is an electrical element that stores charge when a voltage is applied to it. Having capacitors in parallel with other elements does not affect the current or voltage values for a steady applied voltage (DC), but when the applied voltage is changing then the amount of charge that the capacitor can store also changes and a current flows to charge/discharge the capacitor. Solar cells are not intended to be capacitors but they do have an internal capacitance. This capacitance puts a limit to the maximum speed that an I-V curve can be measured because at high voltage ramp rates the charging current is large and the measured current of the device does not represent the steady state operating value. This is a particular problem for measurements of many of the newer, high efficiency technologies since, for reasons that are discussed below, they tend to have higher capacitance than the traditional technologies. In these cases the solar simulator pulse length required to measure the devices using conventional methods becomes longer, typically exceeding 100ms [27], which is more than the pulse length of most commercial solar simulators. Long pulse lengths can be achieved but are technically more challenging and hence more expensive. The other main problem with long pulse lengths is that they can induce heating in the cells, reducing the accuracy of the measurement in a different way. In commercial use, long pulse lengths can become a bottleneck on the production line.

Despite being a potential measurement problem, the capacitance of solar cells can also be a useful feature. This is because it can be easily measured and its dependence on other parameters such as temperature, frequency and voltage gives valuable information about the device. An important example is the extraction of the carrier density and built in voltage from the voltage dependence of the capacitance.

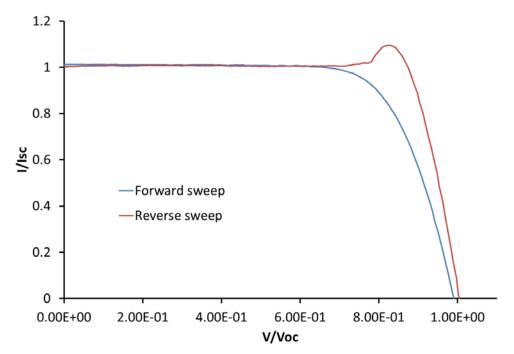

## 3.1.1 Effects of capacitance on performance measurements

The effect of capacitance on I-V curve measurements depends on the direction of the voltage ramp. If the voltage is ramped from low to high it is referred to as a forward sweep, if the voltage is ramped from high to low it is referred to as a reverse sweep. In a forward sweep the voltage on the device is increasing during the measurement so the capacitance of the device charges up as the voltage increases. The charging of the

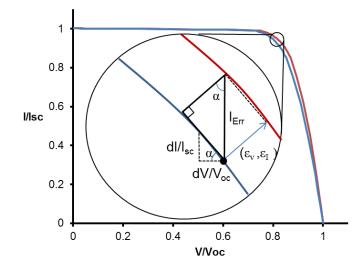

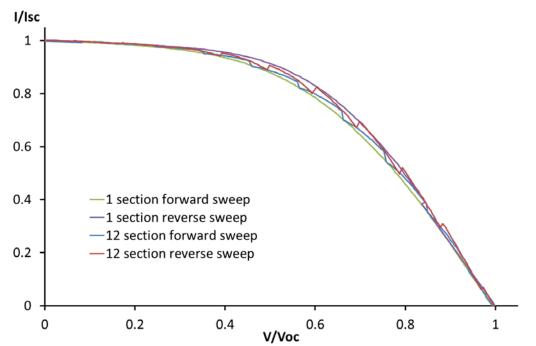

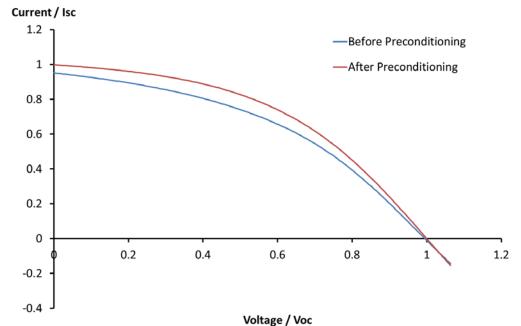

capacitance takes some of the photo current that would otherwise have been output by the device, so if the device is measured too quickly the performance is underestimated, this normally manifests itself mainly as a reduction in fill factor with a smaller reduction in Voc as seen in the example in Figure 3-1. Reverse sweep measurements are also shown in the figure. In this case the capacitance of the device is fully charged at the starting voltage and discharges during the measurement, resulting in an overestimation in performance. Again this usually manifests mainly in the fill factor but also a smaller amount in the open circuit voltage. If the reverse sweep measurement is sufficiently fast the rapid discharging can leads to a pronounced hump in the I-V curve as seen in the figure.

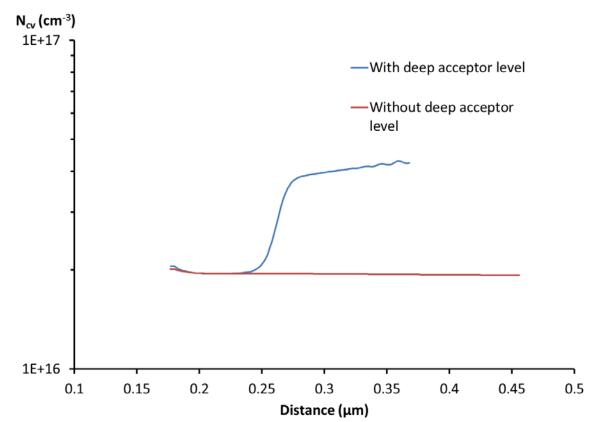

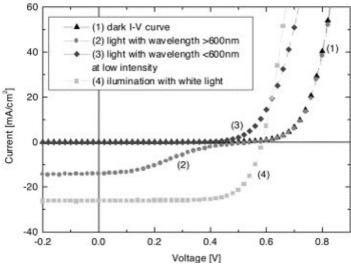

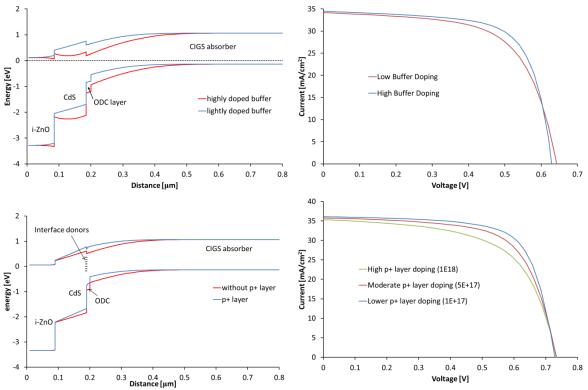

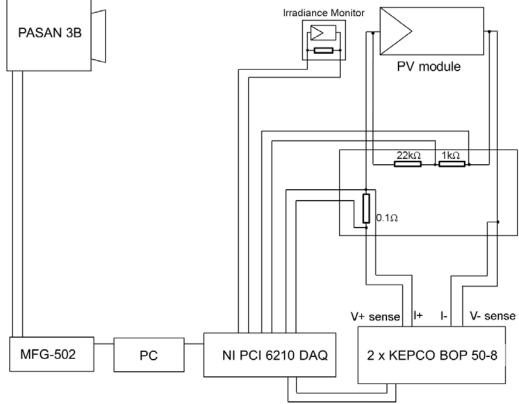

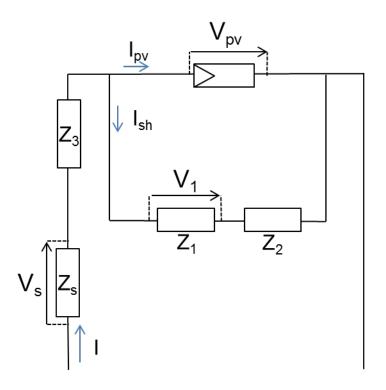

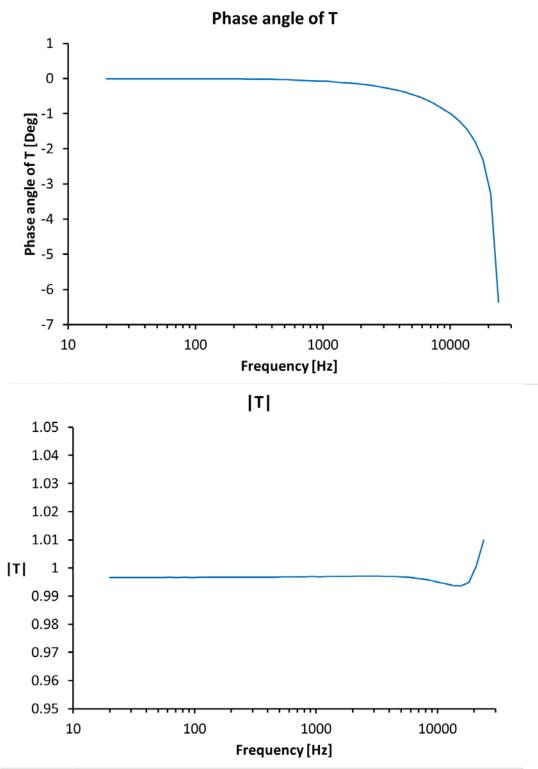

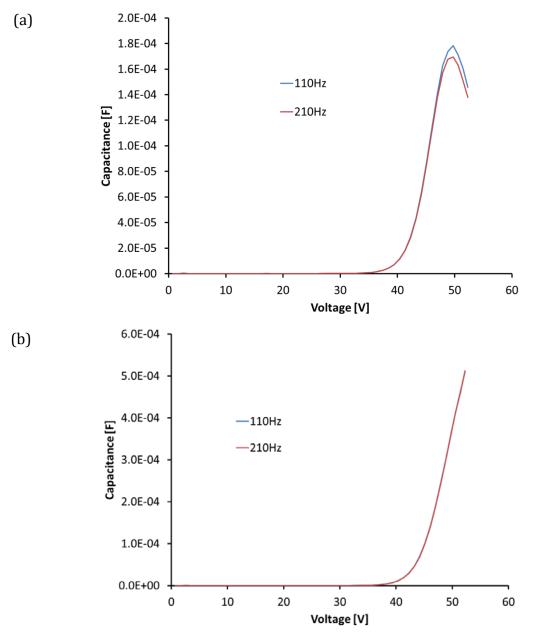

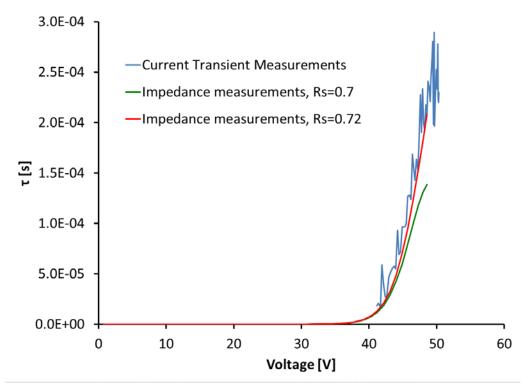

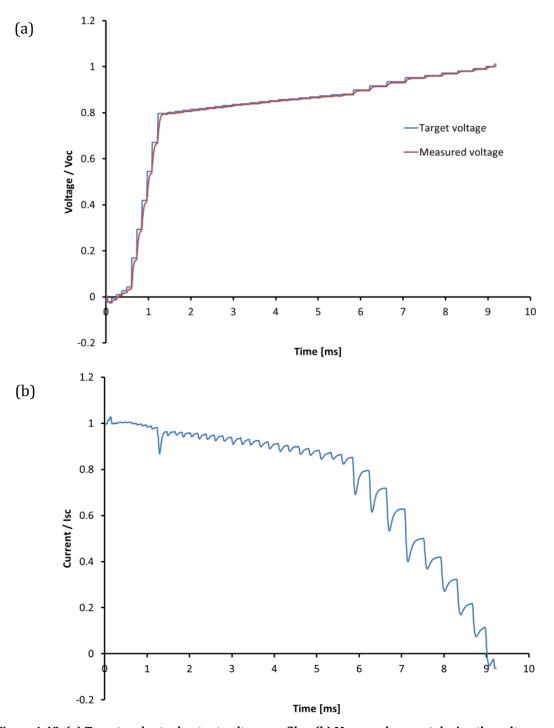

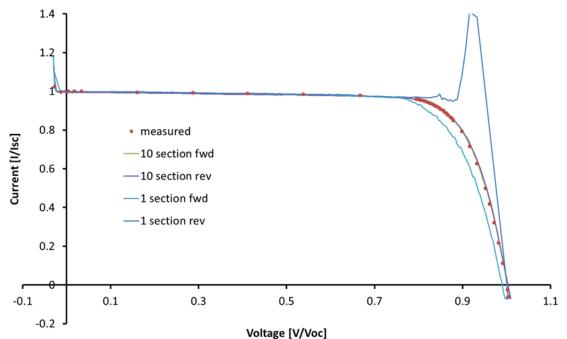

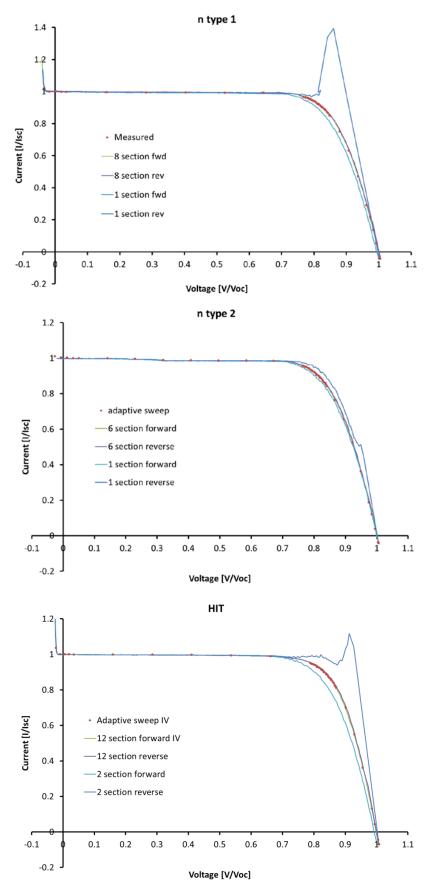

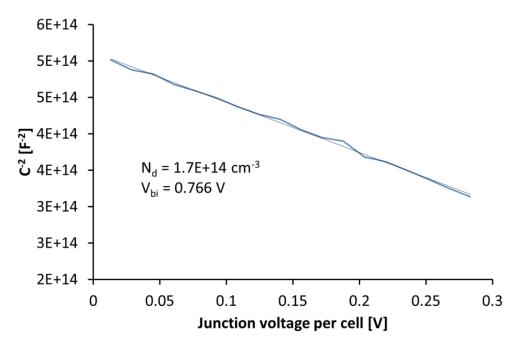

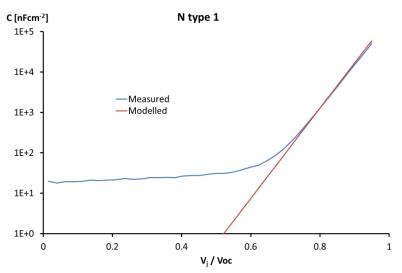

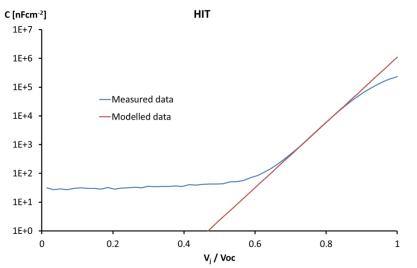

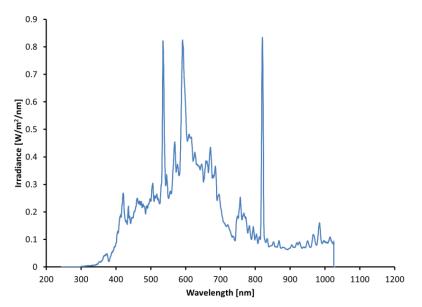

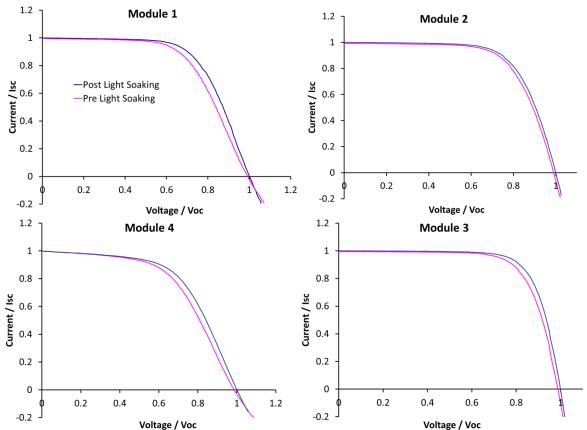

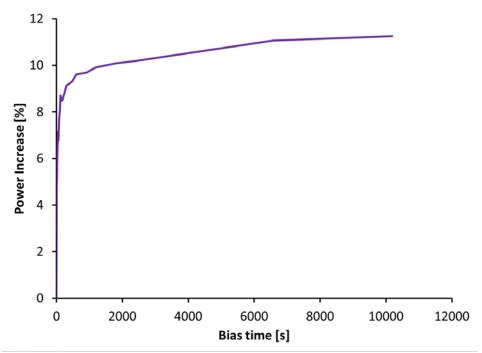

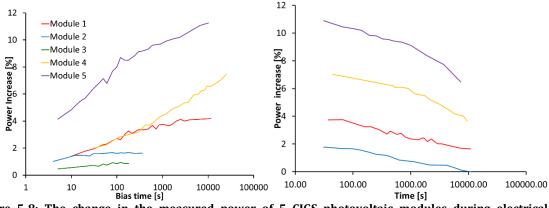

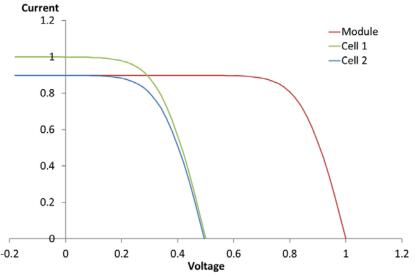

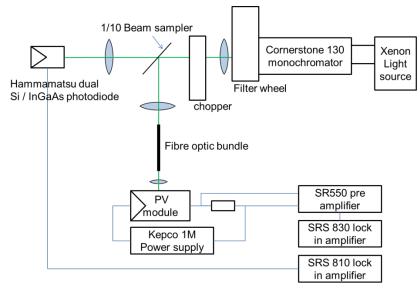

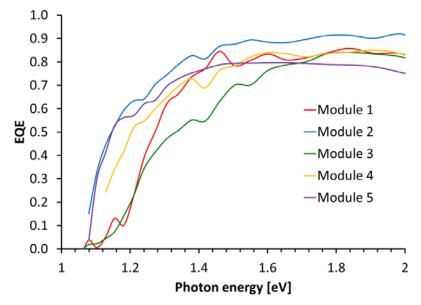

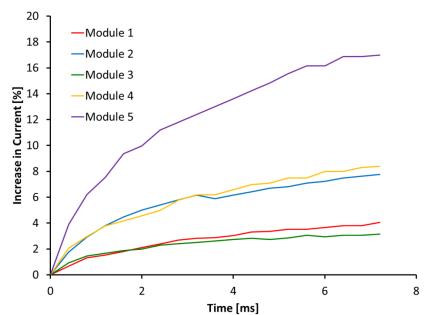

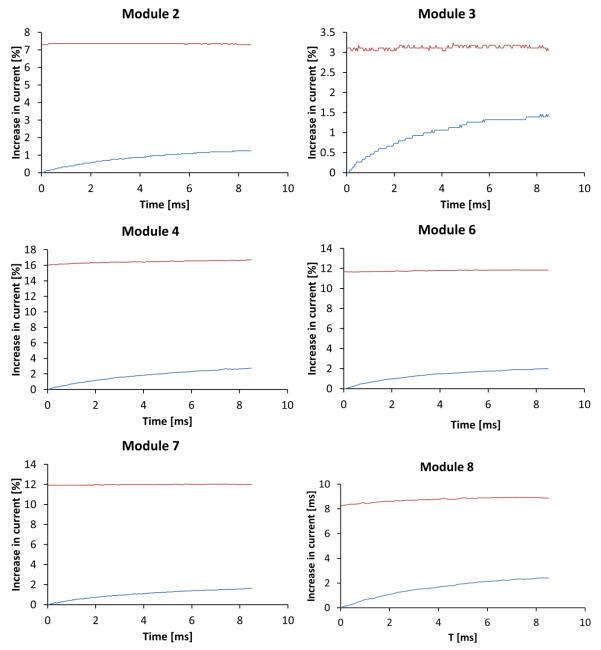

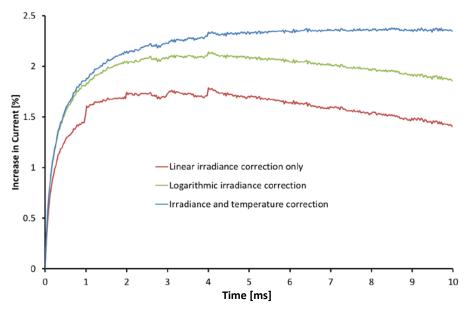

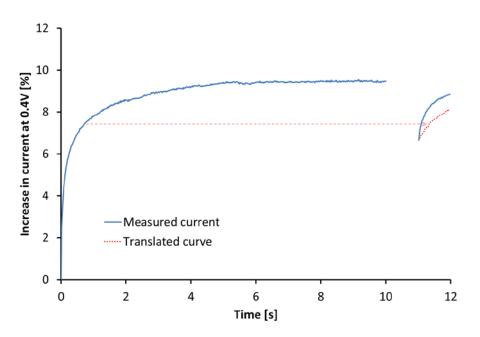

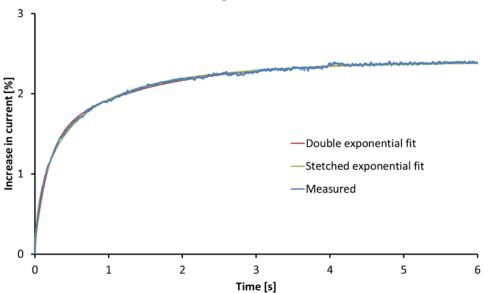

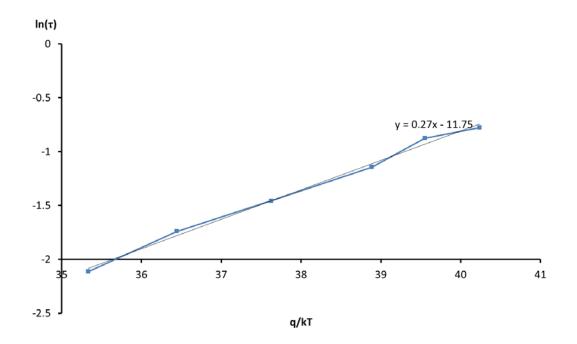

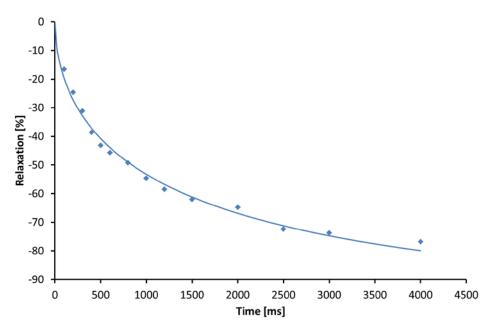

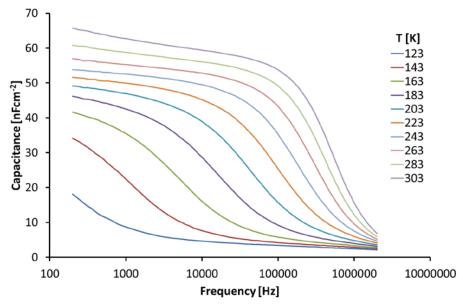

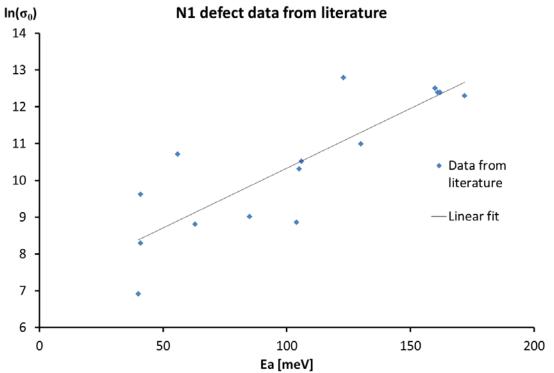

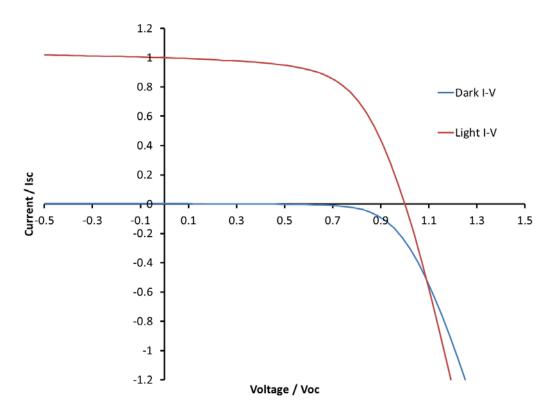

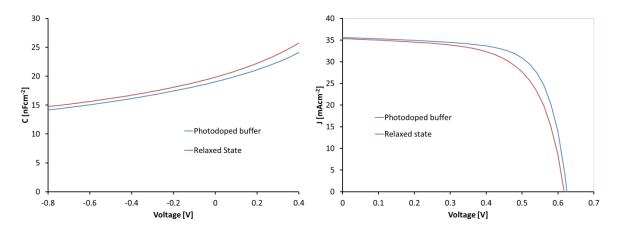

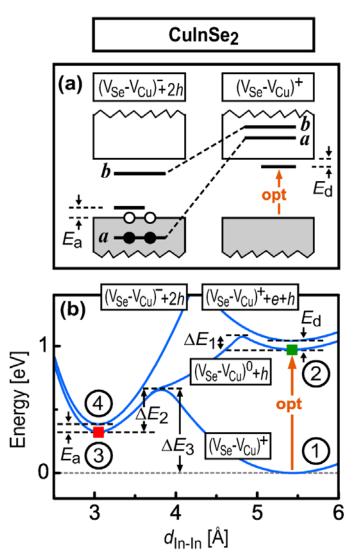

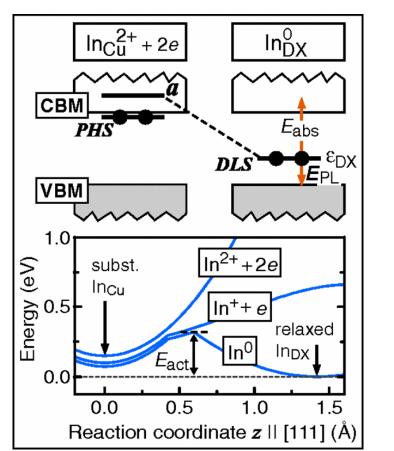

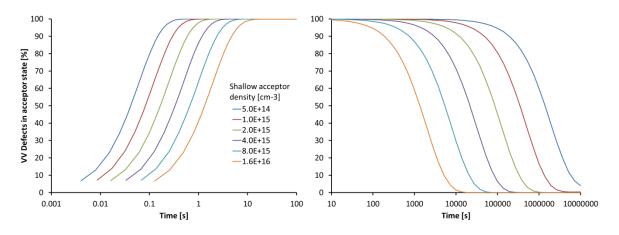

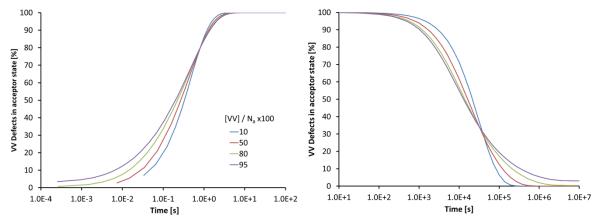

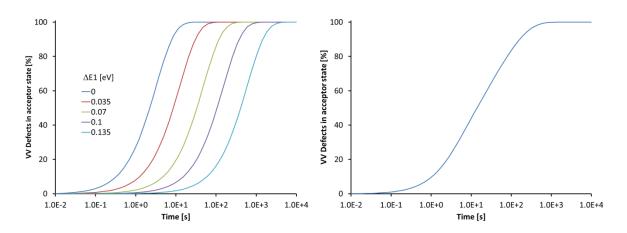

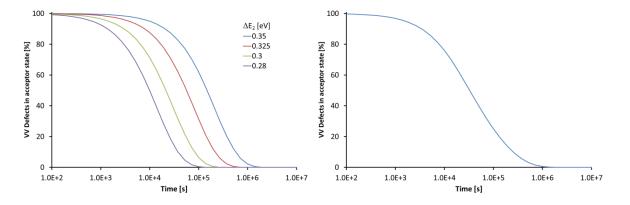

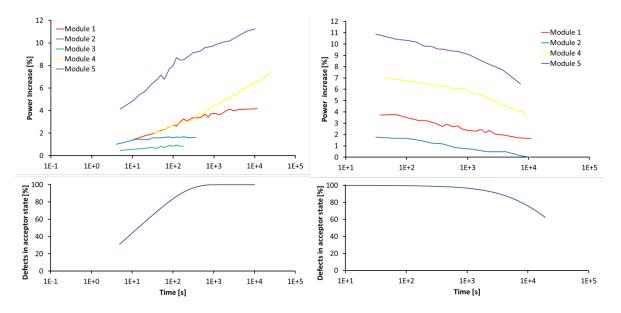

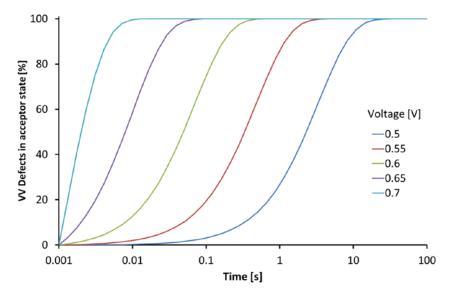

Figure 3-1: The effect of capacitance on I-V curve measurements.