## Microstructural and Mechanical Characteristics of Micro-Scale Intermetallic Compounds Interconnections

By

Liping Mo

A Doctoral Thesis Submitted in Partial Fulfilment of the Requirements For the Award of Doctor of Philosophy of Loughborough University

December 2016

© Liping Mo (2016)

# LOUGHBOROUGH UNIVERSITY WOLFSON SCHOOL OF MECHANICAL AND MANUFACTURING ENGINEERING

Dated: December 2016

First Supervisor:

Changqing Liu

Second Supervisor:

## Abstract

Following the continually increasing demand for high-density interconnection and multilayer packaging for chips, solder bump size has decreased significantly over the years, this has led to some challenges in the reliability of interconnects. This thesis presents research into the resulting effects of miniaturization on the interconnection with Sn-solder, especially focusing on the full intermetallics (IMCs) micro-joints which appear in the 3D IC stacking packaging. Thereby, systematic studies have been conducted to study the microstructural evolution and reliability issues of Cu-Sn and Cu-Sn-Ni IMCs micro-joints.

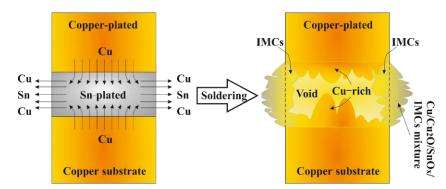

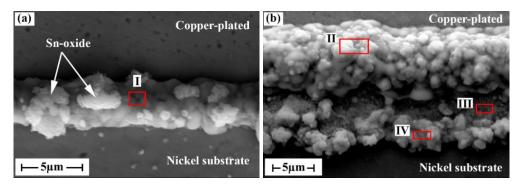

(1) Phenomenon of IMCs planar growth: The planar IMCs interlayer was asymmetric and composed of  $(Cu,Ni)_6Sn_5$  mainly in Ni/Sn (2.5~5 µm)/Cu interconnect. Meanwhile, it was symmetric two-layer structure in Cu/Sn (2.5~5 µm)/Cu interconnect with the Cu<sub>3</sub>Sn fine grains underneath Cu<sub>6</sub>Sn<sub>5</sub> cobblestone-shape-like grains for each IMCs layer. Besides, it is worth noticing that the appearance of Cu-rich whiskers (the mixture of Cu/Cu<sub>2</sub>O/SnO<sub>x</sub>/Cu<sub>6</sub>Sn<sub>5</sub>) could potentially lead to short-circuit in the cases of ultra-fine (<10 µm pitch) interconnects for the miniaturization of electronics devices.

(2) Microstructural evolution process of Cu-Sn IMCs micro-joint: The simultaneous solidification of IMCs interlayer supressed the scalloped growth of  $Cu_6Sn_5$  grains in  $Cu/Sn (2.5 \ \mu m)/Cu$  interconnect during the transient liquid phase (TLP) soldering process. The growth factor of  $Cu_3Sn$  was in the range of  $0.29 \sim 0.48$  in  $Cu-Cu_6Sn_5$  diffusion couple at 240~290 °C, which was impacted significantly by the type of substrates. And the subsequent homogenization process of  $Cu_3Sn$  grains was found to be consistent with the description of flux-driven ripening (FDR) theory. Moreover, Kirkendall voids appeared only in the  $Cu_3Sn$  layer adjacent to Cu-plated substrate, and this porous  $Cu_3Sn$  micro-joint was mechanically robust during the shear test.

(3) Microstructural evolution of Cu-Sn-Ni IMCs micro-joint: There was obvious inter-reaction between the interfacial reactions in Ni/Sn (1.5  $\mu$ m)/Cu interconnect. The growth factor of (Cu,Ni)<sub>3</sub>Sn on Cu side was about 0.36 at 240 °C, and the reaction product on Ni side was changed from Ni<sub>3</sub>Sn<sub>4</sub> into (Cu,Ni)<sub>6</sub>Sn<sub>5</sub> with the increase of soldering temperature. In particular, the segregation of Ni atoms occurred along with phase transformation at 290 °C and thereby stabilized the (Cu,Ni)<sub>6</sub>Sn<sub>5</sub> phase for the high Ni content of 20 at.%.

(4) Micro-mechanical characteristics of Cu-Sn-Ni IMCs micro-joint: The Young's modulus and hardness of Cu-Sn-Ni IMCs were measured by nanoindentation test, such as  $160.6\pm3.1$  GPa/ $7.34\pm0.14$  GPa for (Cu,Ni)<sub>6</sub>Sn<sub>5</sub> and  $183.7\pm4.0$  GPa/ $7.38\pm0.46$  GPa for (Cu,Ni)<sub>3</sub>Sn, respectively. Besides, in-situ nano-compression tests have been conducted on IMCs micro-cantilevers, the fracture strength turns out to be 2.46 GPa. And also, the ultimate tensile stress was calculated to be  $2.3\pm0.7$  GPa from in-situ micro-bending tests, which is not sensitive with the microstructural change of IMCs after dwelling at 290 °C.

Keywords: Intermetallics, Microstructure, Phase transformation, Electron backscatter diffraction (EBSD), Insitu micro-mechanical test

## **Publications**

- 1. <u>L. Mo</u>, F. Wu, and C. Liu, "Microstructural evolution and *in-situ* nanomechanical testing on Cu-Sn-Ni IMCs microjoints," 2016, **pending**

- 2. <u>L. Mo</u>, F. Wu, and C. Liu, "Planar growth of intermetallics in micro-scale Cu/Sn/Cu structure," 2016, pending

- 3. <u>L. Mo</u>, Z. Chen, F. Wu, and C. Liu, "An investigation of Cu-Sn intermetallic joints on isothermal evolution of microstructure and mechanical property," *Intermetallics*, 2015, Vol.66, pp. 13-21.

- L. Mo, F. Wu, and C. Liu, "Growth kinetics of IMCs in full Cu-Sn intermetallic joints during isothermal soldering process," *in Proceeding of the 64<sup>th</sup> Electronic Components and Technology Conference (ECTC)*, 2015, pp. 1854-1858.

- L. Mo, F. Wu, C. Liu and W. Xia, "The size dependency of full IMC solder joint for 3D interconnection," in Proceeding of the 62<sup>nd</sup> Electronic Components and Technology Conference (ECTC), 2012, pp. 839-843.

- J. Zou, <u>L. Mo</u>, F. Wu and B. Wang, "Effect of Cu substrate and solder alloy on the formation of Kirkendall voids in the solder joints during thermal aging," *in Proceeding of the 11<sup>th</sup> Electronic Packaging Technology & High Density Packaging (ICEPT-HDP)*, 2010, pp. 944-948.

- B. Wang, F. Wu, Y. Wu, <u>L. Mo</u> and W. Xia, "Microstructural evolution of the intermetallic compounds in the high density solder interconnects with reduced stand-off heights," *Soldering & Surface Mount Technology*, 2011, vol. 23, pp. 229-234.

## Acknowledgements

This research is funded through LU-HUST joint research degree program, and financially supported by a Marie Curie International Research Staff Exchange Scheme Project within the 7th European Community Framework Program, No. PIRSES-GA-2010-269113, entitled "Micro-Multi-Material Manufacture to Enable Multifunctional Miniaturized Devices (M6)" and a China-European Union technology cooperation project, No. 1110.

I would like to acknowledge both of my supervisors, Prof. Changqing Liu from Loughborough University and Prof. Fengshun Wu from Huazhong University of Science and Technology, for their guidance and help in my study. They are always patient and left a thinking space to me, which is beneficial to improve my capability as a real researcher. And, it is very grateful that I have been involved in the cooperative project, then I could take the great opportunity to experience a different life in UK.

Many thanks are given to the all technicians. Their support are important for the carrying out of my experiments. Especially, I appreciated that the demonstration and supervision I have received from Geoff West and Keith Yendall in Loughborough Materials Characterisation Centre (LMCC), which enabled me to operate FIB and FEG-SEM. Meanwhile, it is also thankful to conduct the in-situ micro-testing within the help from Dr. Chaowei Guo in the Center for Advancing Materials Performance from the Nanoscale, Xi'an Jiaotong University.

Finally, I would like to express the thanks to all my friends and colleagues for their kind company and help to cheer me up in the difficulties during the period of my PhD study. And the most importance is the free and unreserved supports from my families in economic and spirit. Their love makes me here.

Liping Mo

## Contents

| Abstract              |                                                                                        | I    |

|-----------------------|----------------------------------------------------------------------------------------|------|

| Publications          |                                                                                        | II   |

| Acknowledge           | ments                                                                                  | III  |

| Contents              |                                                                                        | IV   |

| List of Tables        |                                                                                        | .VII |

|                       | s                                                                                      |      |

| U                     | viations                                                                               |      |

|                       |                                                                                        |      |

| Chapter 1             | Introduction                                                                           |      |

|                       | kground                                                                                |      |

| 1.1.1                 | Flip-chip technology in chip-level packages                                            |      |

| 1.1.2<br>1.2 Prot     | Copper pillar bump bonding in 3D integration<br>blem statement and research motivation |      |

|                       | earch aims and objectives                                                              |      |

|                       | -                                                                                      |      |

|                       | ement of main innovation and contributions                                             |      |

|                       | sis structure                                                                          |      |

| -                     | Development of Solder Micro-interconnection Technology                                 |      |

| 2.1 Sold              | ler bump bonding                                                                       | 7    |

| 2.1.1                 | Stencil printing technology                                                            |      |

| 2.1.2                 | Micro-C4 technology                                                                    |      |

|                       | per Pillar Bump Bonding                                                                |      |

| 2.3 Inter             | rmetallic Compounds Interconnections                                                   | 10   |

| 2.3.1                 | Reaction and Formation of IMCs                                                         |      |

| 2.3.2                 | Properties of Intermetallic Compounds                                                  |      |

| 2.3.3<br>2.4 Sum      | Reliability analysis                                                                   |      |

|                       | •                                                                                      |      |

| Chapter 3<br>3.1 Prer | Experiment and Methodology                                                             |      |

|                       |                                                                                        |      |

| 3.1.1<br>3.1.2        | Electroplating tin and copper<br>Transient liquid phase (TLP) bonding                  |      |

| 3.1.2                 | Formation of IMCs interconnection                                                      |      |

|                       | allographic observation and analysis                                                   |      |

| 3.2.1                 | Metallographic sample preparation                                                      | 22   |

| 3.2.2                 | Microstructural characterization and analysis                                          |      |

| 3.3 Mea               | surement of IMCs mechanical properties                                                 | 23   |

| 3.  | 4   | Mic   | ro-mechanical testing                                           | 24      |

|-----|-----|-------|-----------------------------------------------------------------|---------|

|     | 3.  | 4.1   | Fabrication of micro-cantilever by FIB                          | 24      |

|     | 3.  | 4.2   | Micro-mechanical tests                                          | 25      |

| Cha | pte | er 4  | Planar Growth of IMCs in Cu/Sn/Cu and Ni/Sn/Cu Sandwich Struc   | tures27 |

| 4.  | 1   | Intro | oduction                                                        | 27      |

| 4.  | 2   | Exp   | erimental procedures                                            | 27      |

|     | 4.  | 2.1   | Sample preparation                                              | 27      |

|     | 4.  | 2.2   | Testing and analysis                                            | 28      |

| 4.  | 3   | Resu  | ults and discussion based on Cu/Sn/Cu structure                 | 28      |

|     | 4.  | 3.1   | Macro-scale planar growth of IMCs                               | 28      |

|     | 4.  | 3.2   | Micro-scale planar growth of IMCs                               | 31      |

|     | 4.  | 3.3   | Mechanical testing by nano-indentation                          | 32      |

| 4.  | 4   | Mac   | cro-scale planar growth of IMCs in Ni/Cu/Sn structure           | 33      |

| 4.  | 5   | Sum   | ımary                                                           | 34      |

| Cha | pte | er 5  | Perpendicular Phase Transformation of IMCs in Cu/Sn/Cu Structur | re 35   |

| 5.  | 1   | Intro | oduction                                                        | 35      |

| 5.  | 2   | Exp   | erimental procedures                                            | 35      |

| 5.  | 3   | Mic   | rostructural observation on the micro-IMCs-joints               |         |

|     | 5.  | 3.1   | Formation process of micro-IMCs-joints                          |         |

|     |     | 3.2   | Effect of substrates on the microstructure                      |         |

|     | 5.  | 3.3   | Effect of temperature on the microstructure                     |         |

| 5.  | 4   | Kine  | etics study on the growth of Cu-Sn IMCs                         | 41      |

| 5.  | 5   | Disc  | cussion on the Kirkendall phenomenon in micro-IMCs-joints       | 45      |

| 5.  | 6   | Sum   | ımary                                                           | 45      |

| Cha | pte | er 6  | Homogenizing and Mechanical Property of Cu <sub>3</sub> Sn IMC  | Micro-  |

|     | 1   |       | interconnection                                                 |         |

| 6.  | 1   | Intro | oduction                                                        |         |

| 6.  | 2   | Exp   | erimental procedures                                            | 47      |

|     | 6.  | 2.1   | Preparation of Cu/IMCs/Cu test structure                        | 47      |

|     |     | 2.2   | Microstructural analysis of IMCs                                |         |

|     | 6.  | 2.3   | Micro-mechanical testing                                        | 48      |

| 6.  | 3   | Hon   | nogenizing process of Cu <sub>3</sub> Sn in micro-joints        | 48      |

|     | 6.  | 3.1   | EBSD analysis of Cu/IMCs/Cu interconnects                       | 48      |

|     | 6.  | 3.2   | Kinetic analysis on IMC grains in micro-joints                  |         |

| 6.  | 4   | Mec   | chanism of microstructural evolution in the IMCs micro-joints   | 54      |

| 6.  | 5   | Mec   | chanical property of Cu <sub>3</sub> Sn IMC micro-joints        | 56      |

| 6.  | 6   | Sum   | 1mary                                                           | 58      |

| Chapter 7  | Microstructural Evolution and Mechanical Property of        | Cu-Sn-Ni IMCs |

|------------|-------------------------------------------------------------|---------------|

|            | Micro-interconnection                                       | 59            |

| 7.1 Intr   | oduction                                                    | 59            |

| 7.2 Exp    | perimental procedures                                       | 59            |

| 7.3 Mic    | crostructural evolution of Cu-Sn-Ni IMCs micro-joints       | 59            |

| 7.3.1      | Formation process of Cu-Sn-Ni IMCs micro-joints             | 59            |

| 7.3.2      | Diffusion and growth behaviour in micro-joints              | 61            |

| 7.3.3      | Effects of temperature and dwell time on microstructure     | 66            |

| 7.3.4      | Evolution process of Cu-Sn-Ni IMCs micro-joints             | 70            |

| 7.4 Me     | chanical properties of Cu-Sn-Ni IMCs                        | 73            |

| 7.5 In-s   | itu mechanical testing on Cu-Sn-Ni IMCs                     | 77            |

| 7.5.1      | Nano-compression test                                       | 77            |

| 7.5.2      | Nano-bending test                                           | 80            |

| 7.6 Sun    | nmary                                                       | 84            |

| Chapter 8  | Conclusions and Future Work                                 |               |

| 8.1 Ma     | in conclusions                                              | 86            |

| 8.1.1      | Planar growth of IMCs in micro-interconnect                 | 86            |

| 8.1.2      | Microstructure and reliability of Cu-Sn IMCs micro-joint    | 86            |

| 8.1.3      | Microstructure and reliability of Cu-Sn-Ni IMCs micro-joint | 87            |

| 8.2 Rec    | commendations for future work                               |               |

| References |                                                             |               |

## List of Tables

| Table 2-1 application characteristics of solder bump and copper pillar bump interconnection [9]            | 9  |

|------------------------------------------------------------------------------------------------------------|----|

| Table 2-2 the growth factor (n) of IMCs in different diffusing structures                                  | 11 |

| Table 2-3 material properties of some typical IMCs                                                         | 15 |

| Table 3-1 solution make up for electroplating tin                                                          | 18 |

| Table 3-2 solution make up for electroplating copper                                                       | 20 |

| Table 3-3 characteristics and corresponding application of the micro-mechanical testing equipment          | 26 |

| Table 4-1 the EDX results for some certain locations in Figure 4-5(a)                                      | 30 |

| Table 4-2 the EDX results for certain area in soldered Ni/Sn/Cu structure                                  | 34 |

| Table 7-1 EDX results from FEG-SEM observation on IMCs interlayer formed at 240 °C                         | 62 |

| Table 7-2 EDX results from FEG-SEM observation on IMCs interlayer formed at 260 °C                         | 67 |

| Table 7-3 EDX results from FEG-SEM observation on IMCs interlayer formed at 290 °C                         | 68 |

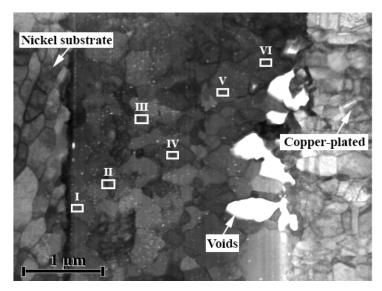

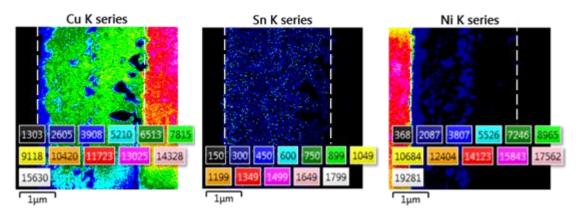

| Table 7-4 EDX results from TEM observation on IMCs interlayer formed at 290 °C                             | 70 |

| <b>Table 7-5</b> parameters of IMCs (0 min) micro-cantilevers and the calculated results of $\sigma_{max}$ | 82 |

| Table 7-6 parameters of IMCs (25 mins) micro-cantilevers and the calculated results of $\sigma_{max}$      | 84 |

## List of Figures

| Figure 1-1 schematic images of primary interconnection technologies for chip-level packages: (a) wire bonding,         (b) tape-automated bonding, and (c) flip-chip bonding                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 schematic image of the traditional under bump metal (UBM) structure1                                                                                                                                                                                                    |

| <b>Figure 1-3</b> silicon integration roadmap from board-level integration to 3D chip integration (SCM- single chip module; MCM- multichip module; LGA- land grid array; BGA- ball grid array; CGA- column grid array; MLC- multilayer ceramic; SLC- surface laminar circuit) [15] |

| Figure 1-4 comparison between two bonding structures (a) solder bump, and (b) copper pillar bump (H-Interconnected Height, SOH-Stand-off Height)                                                                                                                                   |

| Figure 1-5 microstructural evolution within solder joint scaling [21]4                                                                                                                                                                                                             |

| Figure 1-6 the blueprint for the whole thesis                                                                                                                                                                                                                                      |

| Figure 2-1 diagram of stencil printing process to make solder bump7                                                                                                                                                                                                                |

| Figure 2-2 fabrication process of solder bump by micro-C4 technology [9]8                                                                                                                                                                                                          |

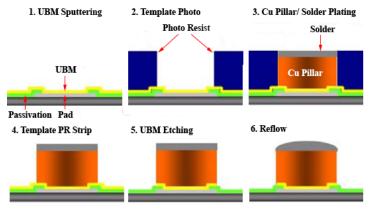

| Figure 2-3 process flow for making Cu pillar bump [9]8                                                                                                                                                                                                                             |

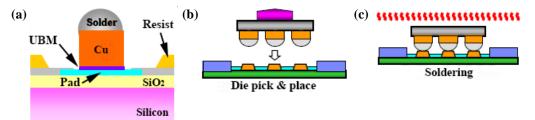

| <b>Figure 2-4</b> IC packaging process with copper pillar bumps: (a) sechmatic image of the copper pillar bump, (b) die alignment, (c) relfow process [11]9                                                                                                                        |

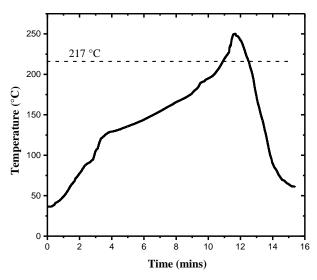

| Figure 2-5 the general reflow profile for Sn-Ag-Cu solder10                                                                                                                                                                                                                        |

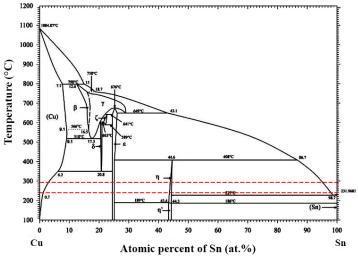

| Figure 2-6 Cu-Sn binary phase diagram [50]10                                                                                                                                                                                                                                       |

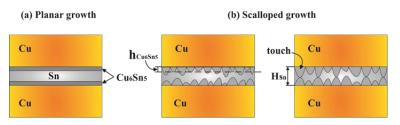

| Figure 2-7 relationship between the growth manner of interfacial IMC and the thickness of Sn-solder11                                                                                                                                                                              |

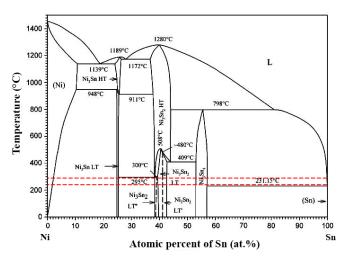

| Figure 2-8 Ni-Sn binary phase diagram [65]12                                                                                                                                                                                                                                       |

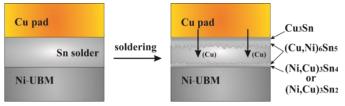

| Figure 2-9 schematic diagram for the microstructure of Ni/Sn/Cu joint after soldering                                                                                                                                                                                              |

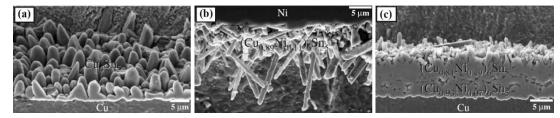

| <b>Figure 2-10</b> IMCs morphologies (a) Cu <sub>6</sub> Sn <sub>5</sub> in the Cu/Sn3.5Ag; (b) (Cu,Ni) <sub>6</sub> Sn <sub>5</sub> on Ni-side and (c) (Cu,Ni) <sub>6</sub> Sn <sub>5</sub> on Cu-side from Ni/Sn3.5Ag/Cu structures after soldering [77]                         |

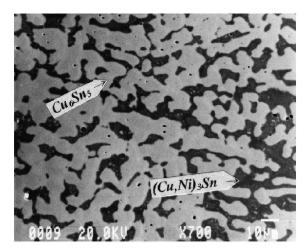

| Figure 2-11 microstructure of Sn-50 at. % Cu-10 at. % Ni alloy after equilibrium solidification [83]13                                                                                                                                                                             |

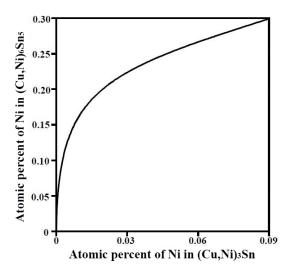

| Figure 2-12 relationship of Ni atomic percent in (Cu,Ni) <sub>6</sub> Sn <sub>5</sub> and (Cu,Ni) <sub>3</sub> Sn for balance [84]13                                                                                                                                               |

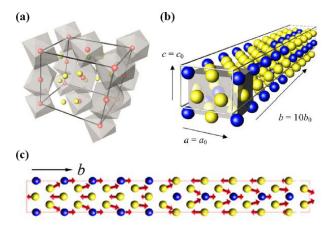

| Figure 2-13 lattice structure of Cu <sub>6</sub> Sn <sub>5</sub> and Cu <sub>3</sub> Sn [86]14                                                                                                                                                                                     |

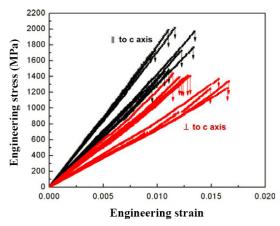

| Figure 2-14 results from compression test on Cu <sub>6</sub> Sn <sub>5</sub> single crystal [89]14                                                                                                                                                                                 |

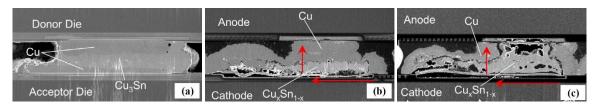

| Figure 2-15 the failure of Cu <sub>3</sub> Sn joints under EM testing (a) before testing, (b) the early failure (c) the final failure mode [110]                                                                                                                                   |

| Figure 2-16 over-view of interconnects and the corresponding EM tests                                                                                                                                                                                                              |

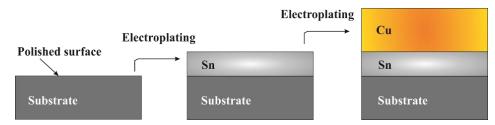

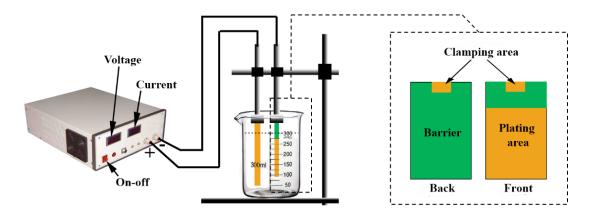

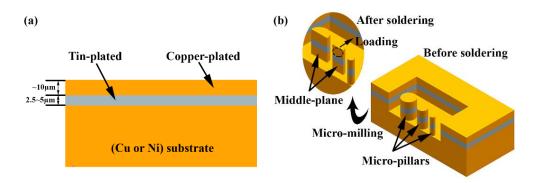

| Figure 3-1 substrate/Sn/Cu structure prepared through the continuous electroplating method                                                                                                                                                                                         |

| Figure 3-2 schematic images of the electroplating apparatus                                                                                                                                                                                                                        |

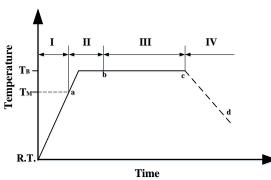

| Figure 3-3 different stages of TLP bonding process (R.Troom temperature, T <sub>M</sub> -the melting point of solder, T <sub>B</sub> -                                                                                                                                             |

| the bonding temperature)                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

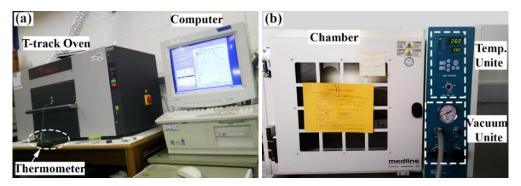

| Figure 3-4 images of two types of ovens used in experiment (a) T-track oven (b) vacuum oven21                                                                                                     |

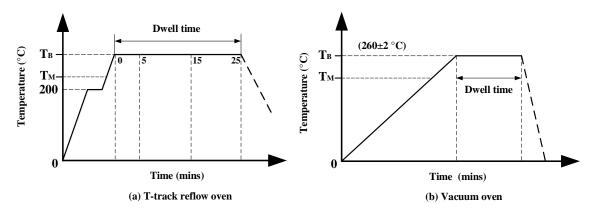

| Figure 3-5 TLP profiles used in T-track reflow oven and vacuum chamber                                                                                                                            |

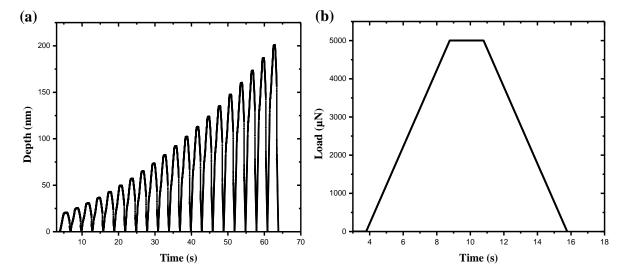

| Figure 3-6 the loading curves applied in nanoindentation test (a) multiple loading with displacement control, (b) loading with force control                                                      |

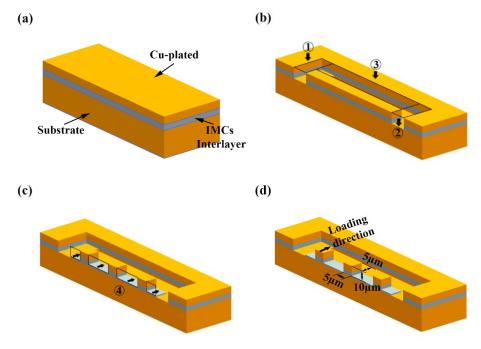

| Figure 3-7 processing sequence of micro-cantilever used for shearing test (Type I)                                                                                                                |

| Figure 3-8 processing sequence of IMCs micro-cantilever for nano-compression test (Type II)25                                                                                                     |

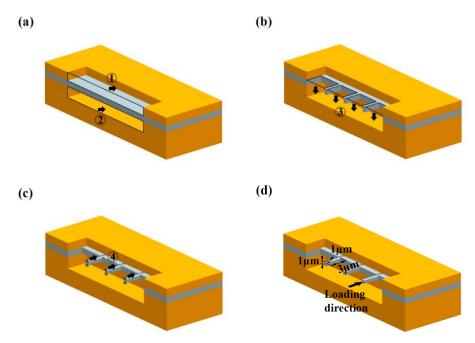

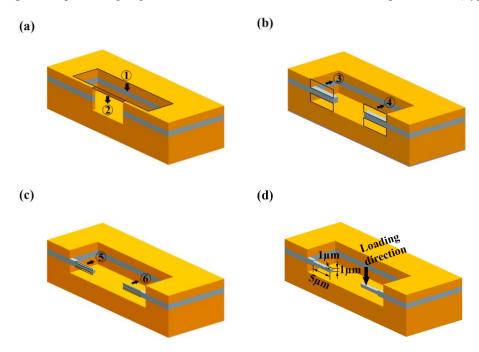

| Figure 3-9 processing sequence of IMCs micro-cantilever for nano-bending test (Type III)                                                                                                          |

| Figure 4-1 (a) schematic diagram of (Cu or Ni) substrate/Sn/Cu structure; (b) micropillars remachined by FIB                                                                                      |

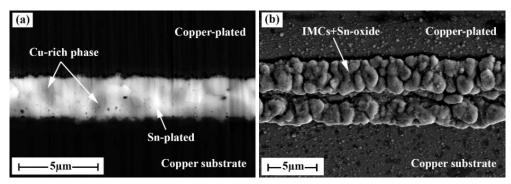

| <b>Figure 4-2</b> morphology of Cu/Sn (2.5 μm)/Cu cross-section (a) before soldering, (b) after soldering29                                                                                       |

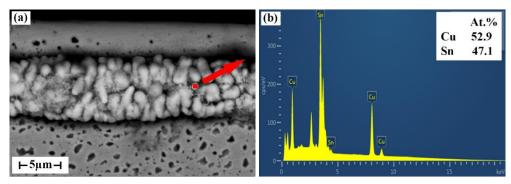

| Figure 4-3 (a) morphology of soldered Cu/Sn (2.5 $\mu$ m)/Cu without oxide covering and (b) the EDX result29                                                                                      |

| Figure 4-4 morphology of IMCs planar growing in soldered Cu/Sn (5 µm)/Cu structure                                                                                                                |

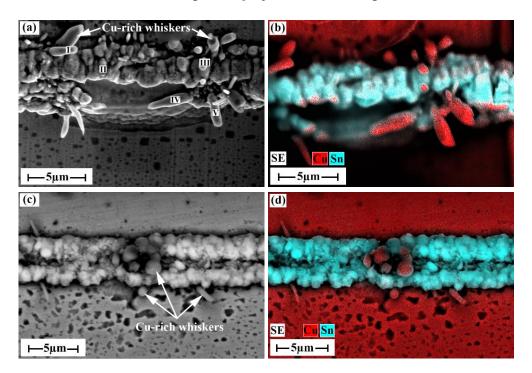

| <b>Figure 4-5</b> planar growth of whiskers in Cu/Sn (2.5 μm)/Cu structure after soldering (a) SEM image on one area, (b) EDX map of (a), (c) SEM image on the other area, and (d) EDX map of (c) |

| Figure 4-6 two types of micropillars with different diameters before and after soldering                                                                                                          |

| <b>Figure 4-7</b> FIB remachining on soldered Cu/Sn (2.5 µm)/Cu micropillar and EBSD observation on the white dotted-line rectangular area                                                        |

| <b>Figure 4-8</b> (a) mid-plane of soldered Cu/Sn (5 μm)/Cu micropillar of 10 μm diameter; (b) EBSD observation on the white dotted-line rectangular area; (c) phase map of (b)                   |

| Figure 4-9 diffusing paths of atoms in Cu/Sn/Cu micropillar and the final structure after soldering                                                                                               |

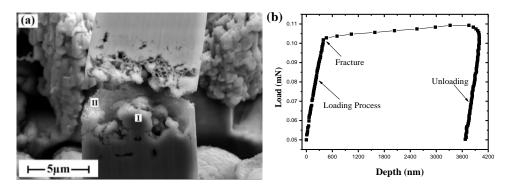

| <b>Figure 4-10</b> (a) fracture image for semi-micropillar produced from Cu/Sn (5 µm)/Cu micropillar after soldering, and (b) the loading-depth curve produced by mechanical testing              |

| Figure 4-11 morphologies of the two Ni/Sn/Cu structures after soldering                                                                                                                           |

| Figure 5-1 the architecture of 2.5D & 3D IC devices [148]                                                                                                                                         |

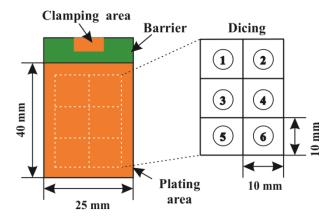

| Figure 5-2 schematic diagram of the electroplated sample and the dicing method                                                                                                                    |

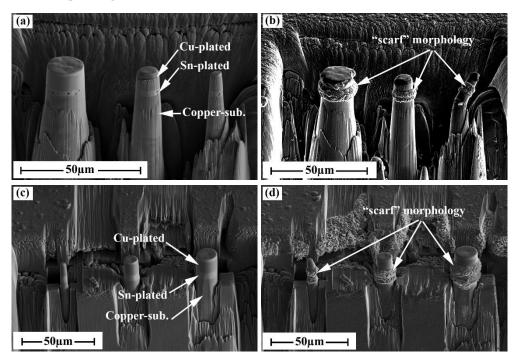

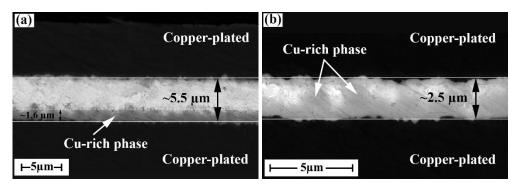

| <b>Figure 5-3</b> SEM images on the initial samples after plating (a) Cu/Sn (~5 μm)/Cu; (b) Cu/Sn (~2.5 μm)/Cu36                                                                                  |

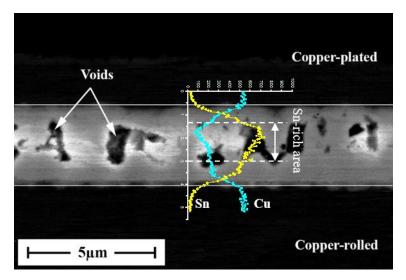

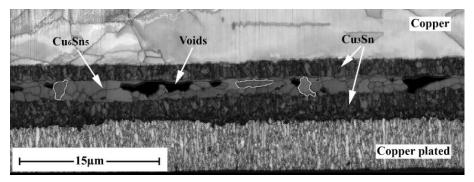

| <b>Figure 5-4</b> voids formed by scalloped Cu <sub>6</sub> Sn <sub>5</sub> merging in the Cu-rolled/Sn (~3 μm)/Cu structure after heating to 230 °C with 50 °C/min in T-track oven               |

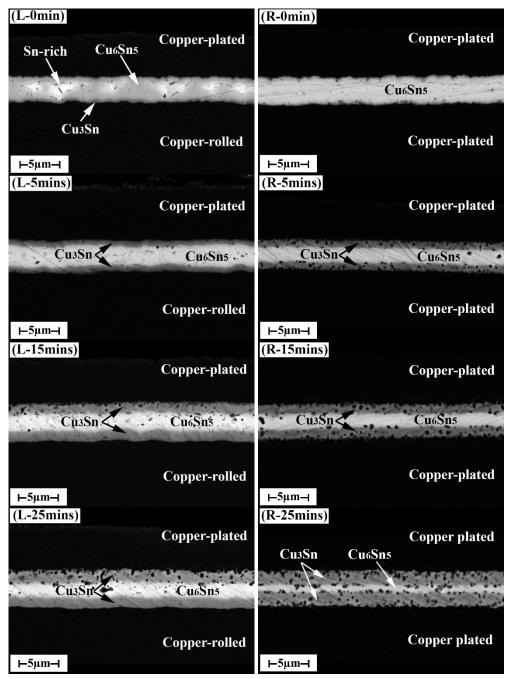

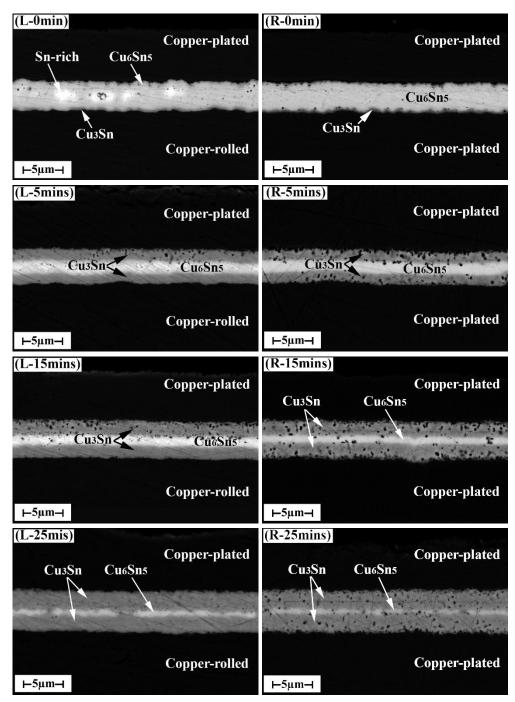

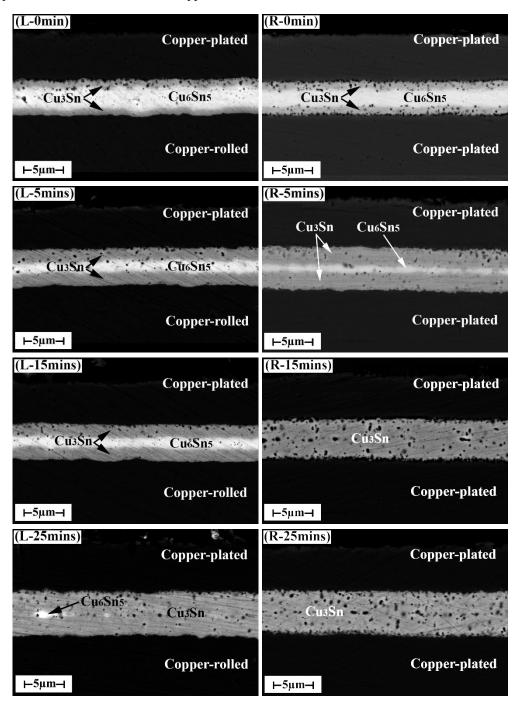

| <b>Figure 5-5</b> morphologies of IMCs interlayer on two types of Cu substrates soldered at 240 °C with different dwell time (L-Cu rolled/IMCs/Cu structure; R-Cu-plated/IMCs/Cu structure)       |

| <b>Figure 5-6</b> morphologies of IMCs interlayer on two types of Cu substrates soldered at 260 °C with different dwell time (L-Cu rolled/IMCs/Cu structure; R-Cu-plated/IMCs/Cu structure)       |

| Figure 5-7 morphologies of IMCs interlayer on two types of Cu substrates soldered at 290 °C with different                                                                                        |

| dwell time (L-Cu rolled/IMCs/Cu structure; R-Cu-plated/IMCs/Cu structure)40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

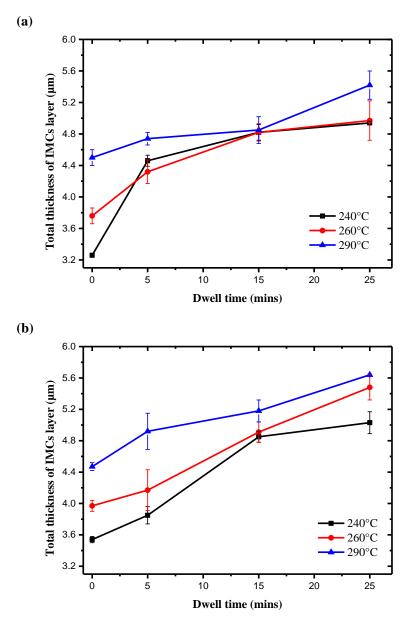

| Figure 5-8 total thickness of IMCs interlayer in the two types of micro-joints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

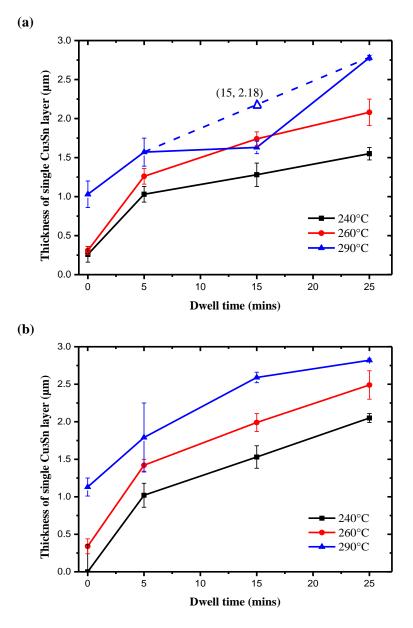

| Figure 5-9 thickness of single Cu <sub>3</sub> Sn layer on different Cu substrates within IMCs micro-joints43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

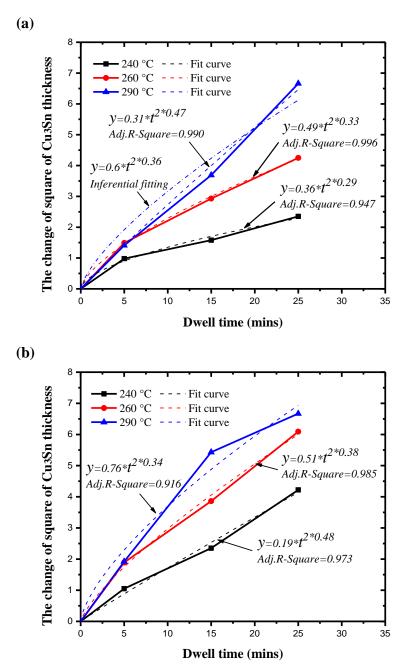

| Figure 5-10 the change of square of Cu <sub>3</sub> Sn thickness on different Cu substrates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

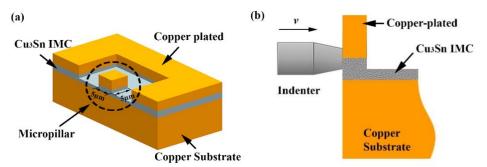

| Figure 6-1 schematic illustration: (a) testing micro-cantilever fabricated by FIB; (b) mechanical testing on micro-cantilever by nanoindenter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

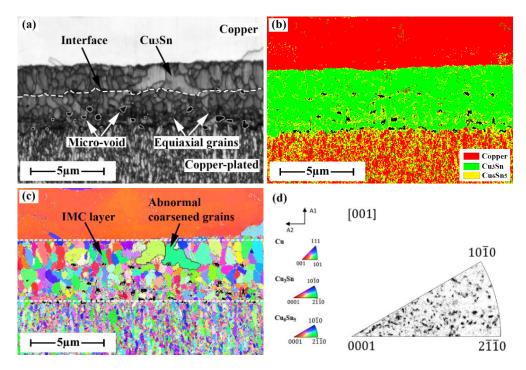

| Figure 6-2 EBSD observation on the cross-section of micro-joint with dwell time of 10 mins at 260 °C48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 6-3 EBSD observation on the cross-section of micro-joint with dwell time of 30 mins at 260 °C49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

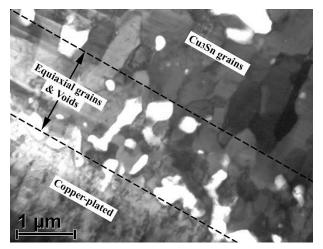

| Figure 6-4 TEM bright-field observation on the vertical section of micro-joint with 30 mins dwelling at 260 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 6-5 EBSD observation on the cross-section of micro-joint with dwell time of 70 mins at 260 °C50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

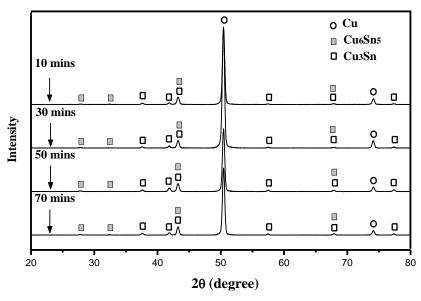

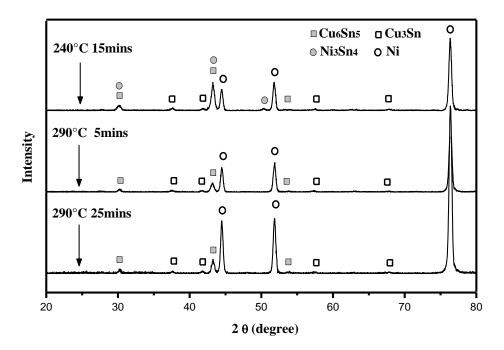

| Figure 6-6 IMCs phases identification by XRD50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

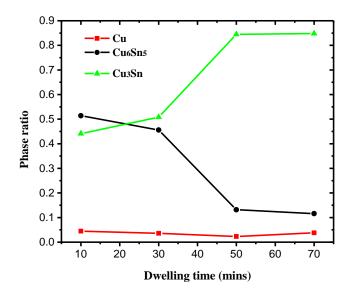

| Figure 6-7 the ratio of each phase in IMCs interlayer of micro-joints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

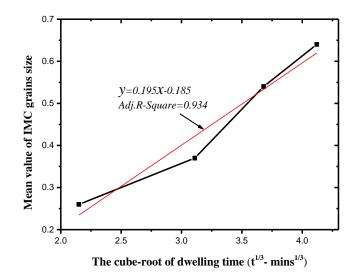

| Figure 6-8 linear relationship between mean size of IMC grains and the cube-root of dwell time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

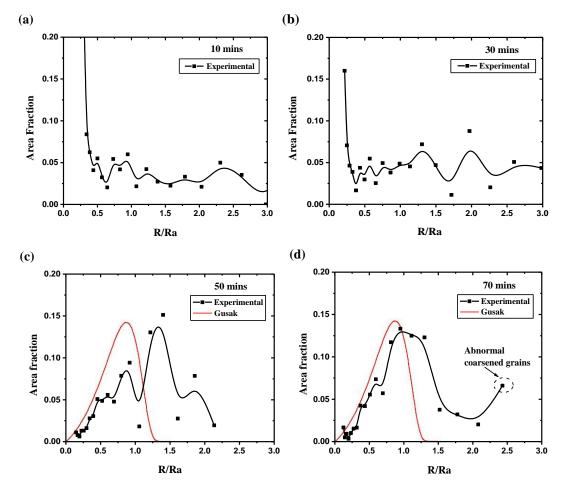

| Figure 6-9 normalized grain size distribution of IMC interlayer formed at 260 °C with different dwell time52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

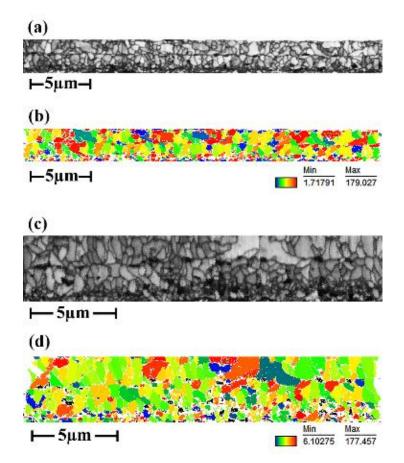

| Figure 6-10 EBSD images of Cu <sub>3</sub> Sn IMC interlayer formed with dwell time of 50 mins53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

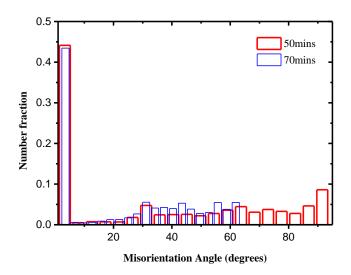

| Figure 6-11 statistical results of misorientation distribution of IMC grains after 50 mins and 70 mins dwelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

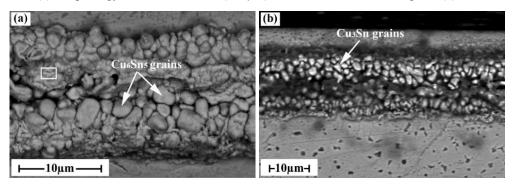

| Figure 6-12 IQ map on cross-section of Cn/Sn (~5 µm)/Cu sandwich structure after soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

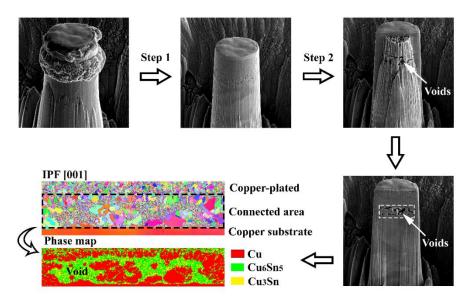

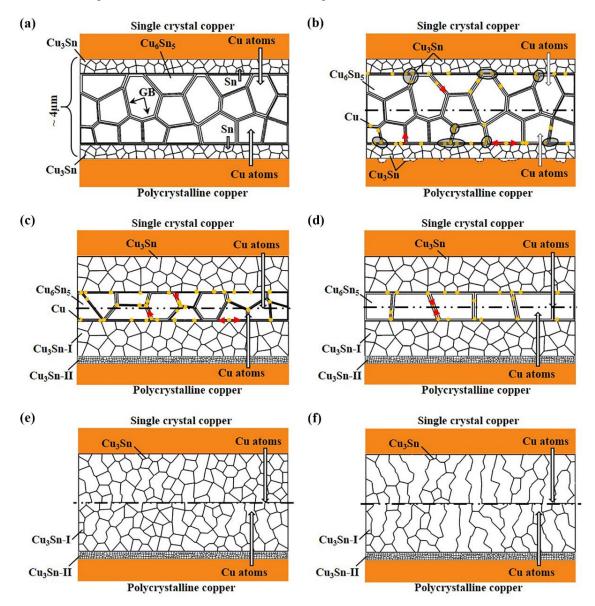

| <b>Figure 6-13</b> the schematic diagram to ascribe the microstructural evolution process of $Cu_6Sn_5$ grains in the course<br>of transformation into $Cu_3Sn$ grains: (a) the initial IMCs joints formed; (b) the Cu atoms (yellow dots) diffuse<br>from copper substrate into $Cu_6Sn_5$ layer through GB and concentrate on the triple junction forming $Cu_3Sn$ grains;<br>(c) with dwell time increasing, the $Cu_6Sn_5$ layer in the middle consumed while the $Cu_3Sn$ layers grow thicker,<br>and the $Cu_3Sn$ -II layer become continuous, mixing with some micro-voids; (d) another possible route similar to<br>(c) for the $Cu_6Sn_5$ layer to propagate from (b), but through single crystal vertically; (e) complete $Cu_3Sn$ formed<br>in the joint; (f) the ripening of $Cu_3Sn$ grains controlled by flux diffusion mechanism |

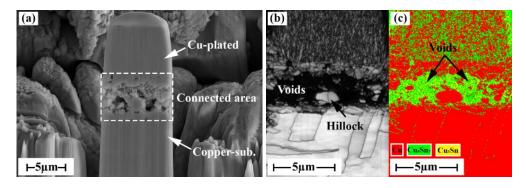

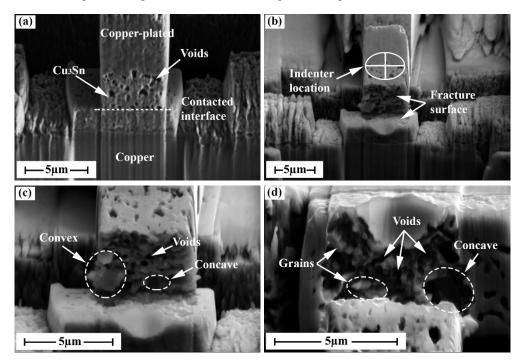

| Figure 6-14 SEM images of micro-cantilever made by FIB before and after shearing by nanoindentation57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

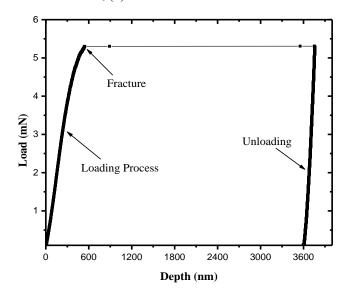

| Figure 6-15 load-depth curve during the shear testing by nanoindentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

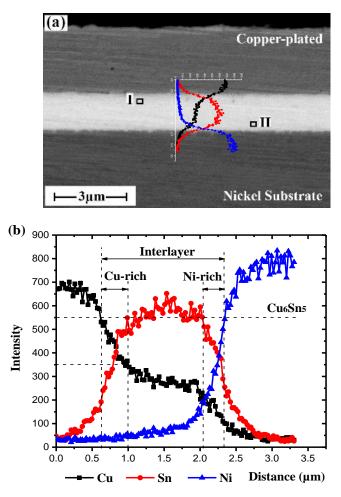

| Figure 7-1 Cu-Sn-Ni IMCs micro-joint formed after 230 °C soldering60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

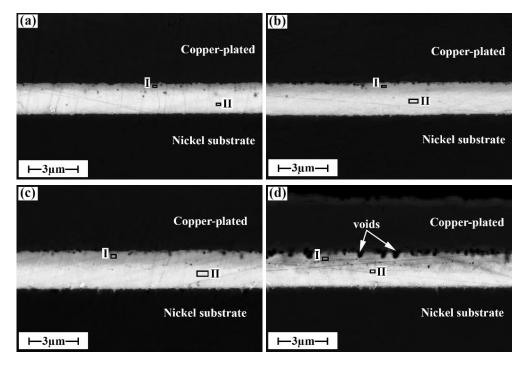

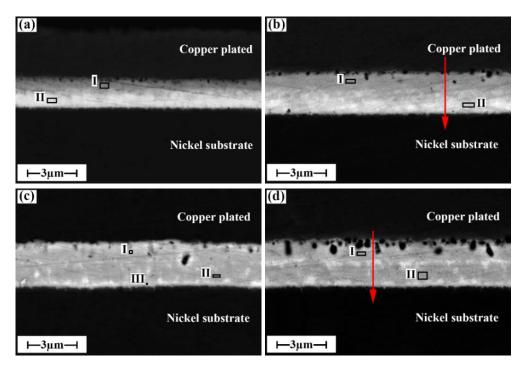

| Figure 7-2 cross-section morphologies of Cu-Sn-Ni IMCs joints formed at 240 °C with different dwell time61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

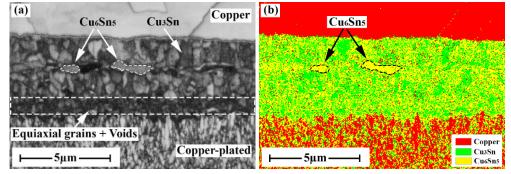

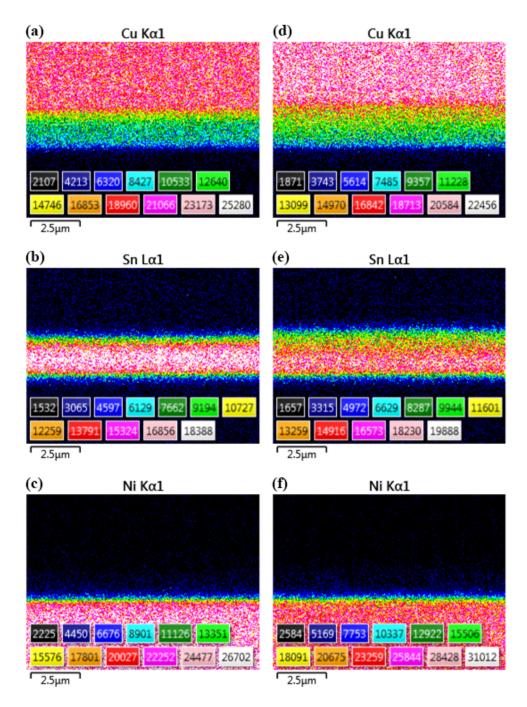

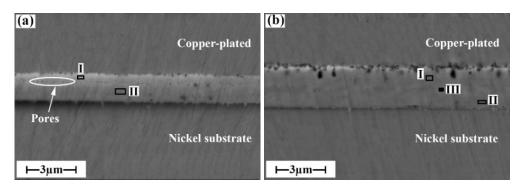

| Figure 7-3 FEG-SEM discrete mapping on Cu-Sn-Ni micro-joints formed at 240 °C with different dwell time         (Left: a-c) 0 min; (Right: d-f) 25 mins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

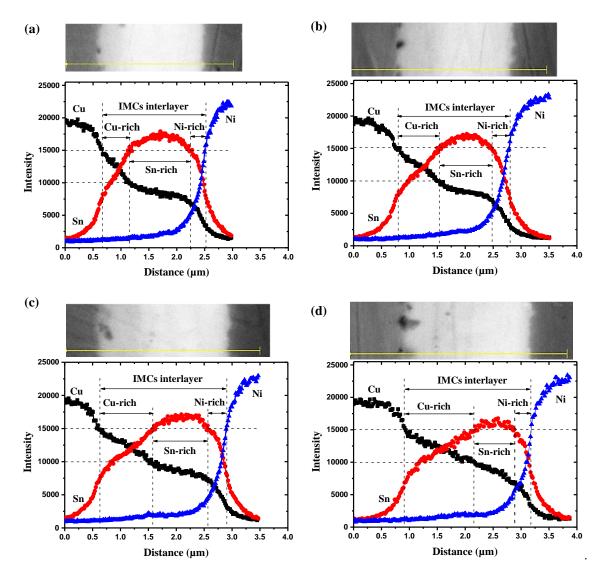

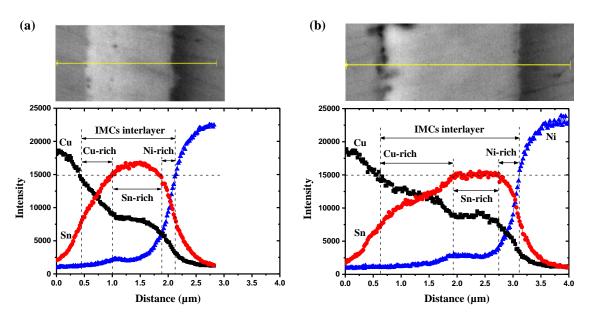

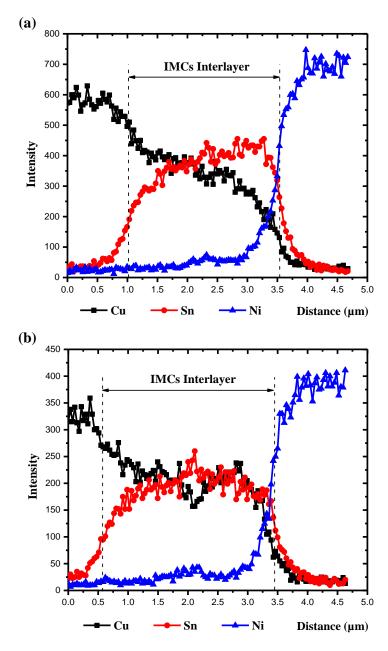

| Figure 7-4 line-scan results of Cu-Sn-Ni IMCs micro-joints formed at 240 °C with different dwell time64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

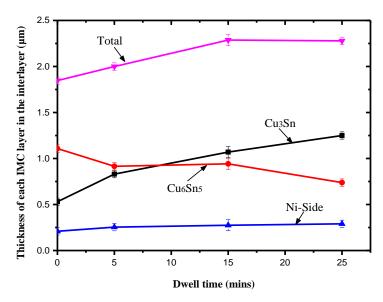

| Figure 7-5 thickness of each layers in IMCs interlayer formed at 240 °C with different dwell time65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

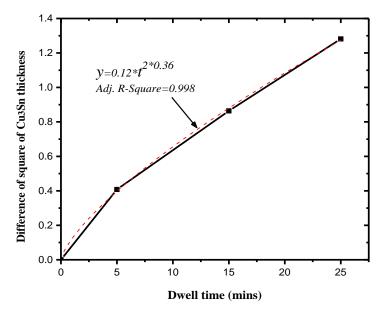

| Figure 7-6 interfacial growth kinetics of (Cu,Ni) <sub>3</sub> Sn fitted by empirical formula                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7-7 cross-sectional morphologies of Cu-Sn-Ni IMCs joints formed at 260 °C with different dwell time                                                                                                            |

| Figure 7-8 line-scanning results of Cu-Sn-Ni IMCs micro-joints formed at 260 °C with different dwell time66                                                                                                           |

| Figure 7-9 cross-sectional morphologies of Cu-Sn-Ni IMCs joints formed at 290 °C with different dwell time                                                                                                            |

| Figure 7-10 line-scan results of Cu-Sn-Ni IMCs micro-joints formed at 290 °C with different dwell time69                                                                                                              |

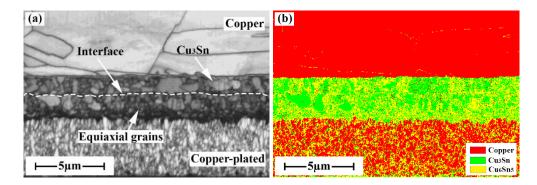

| Figure 7-11 TEM bright field image on vertical section of micro-joint formed at 290 °C for 25 mins                                                                                                                    |

| Figure 7-12 TEM discrete mapping images of Cu-Sn-Ni micro-joint formed at 290 °C for 25 mins                                                                                                                          |

| Figure 7-13 XRD detection results of the Cu-Sn-Ni IMCs interlayers                                                                                                                                                    |

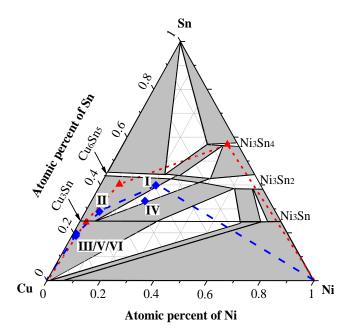

| <b>Figure 7-14</b> the evolution path of Cu-Sn-Ni IMCs in micro-joints under 240~290 °C (▲ -the results from the micro-joint formed at 240 °C/15 mins; ◆ - the results from the micro-joint formed at 290 °C/25 mins) |

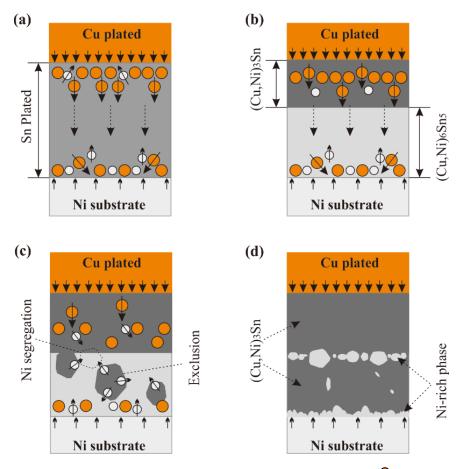

| Figure 7-15 microstructural evolution process of Cu-Sn-Ni IMCs micro-joints (O-Cu atom; O-Ni atom)73                                                                                                                  |

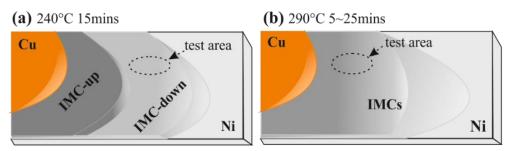

| Figure 7-16 diagrams for two types of Cu-Sn-Ni IMCs interlayers under optical microscopy                                                                                                                              |

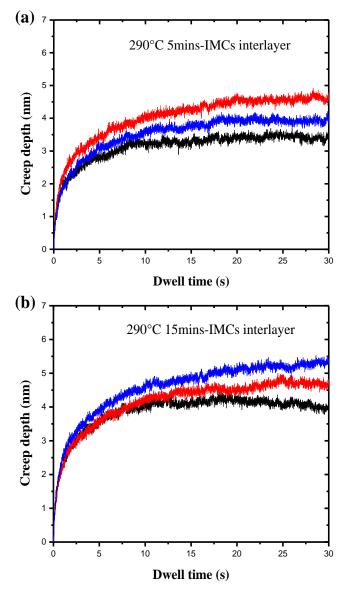

| Figure 7-17 creep depth of (Cu,Ni) <sub>3</sub> Sn under constant load versus dwell time                                                                                                                              |

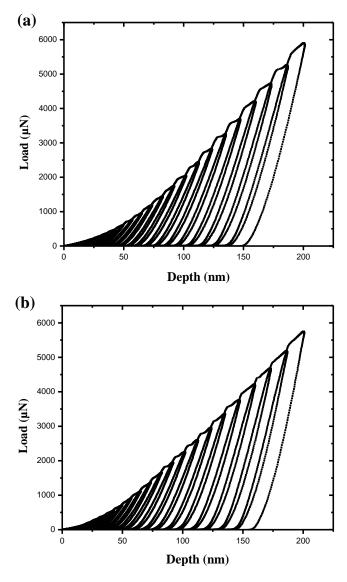

| Figure 7-18 load-depth profiles of Cu-Sn-Ni IMCs during nanoindentation test                                                                                                                                          |

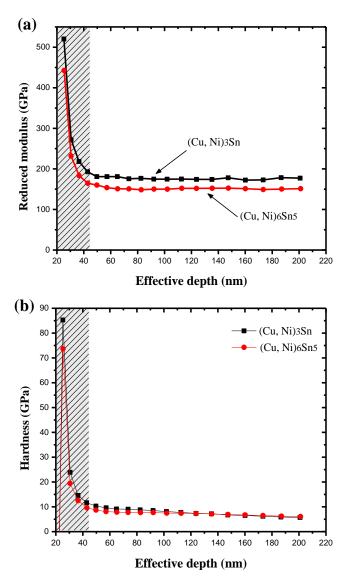

| Figure 7-19 results from nanoindentation test on Cu-Sn-Ni IMCs                                                                                                                                                        |

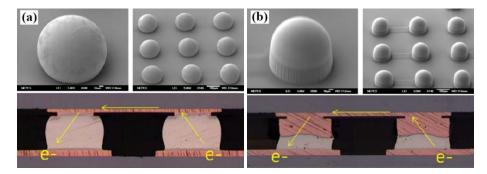

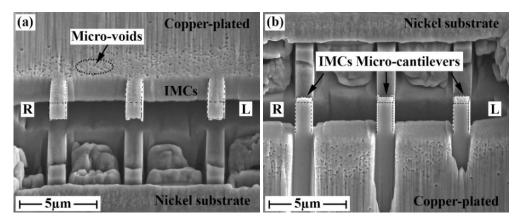

| Figure 7-20 images of micro-cantilevers prepared for nano-compression (a) front view and (b) top view77                                                                                                               |

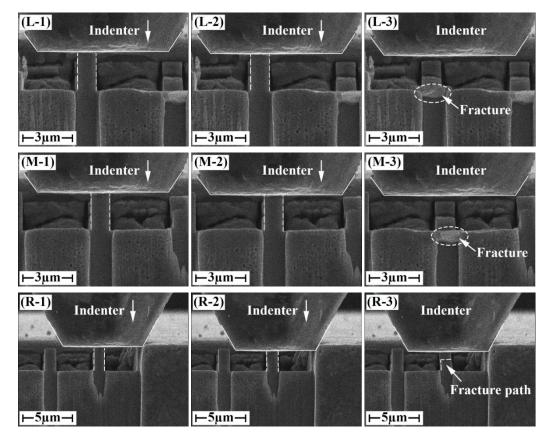

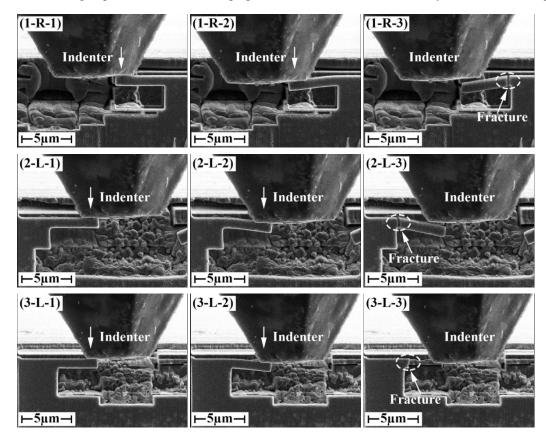

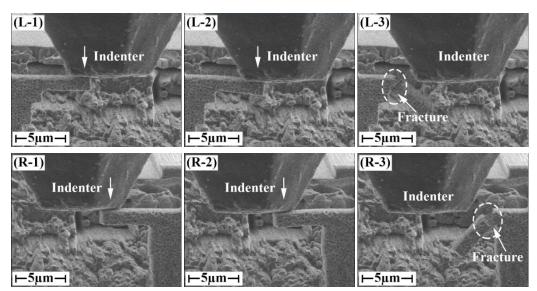

| <b>Figure 7-21</b> three major stages during the nano-compression test on three 290 °C/0 min IMCs micro-cantilevers (1) contact; (2) loading and deformation; (3) fracture                                            |

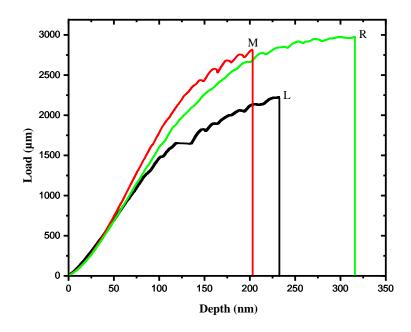

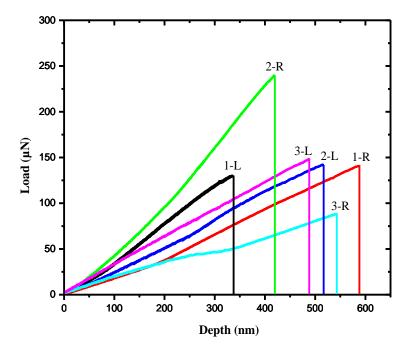

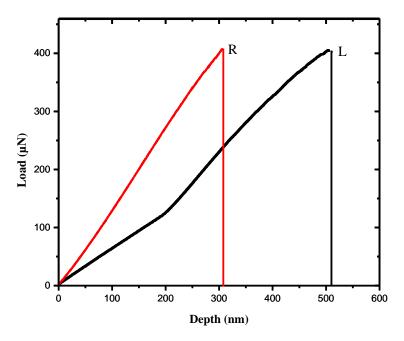

| Figure 7-22 load-depth profiles of nano-compression test on three micro-cantilevers                                                                                                                                   |

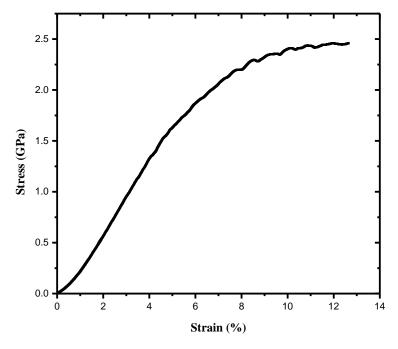

| Figure 7-23 stress-strain (%) profile of nano-compression testing on micro-cantilever R                                                                                                                               |

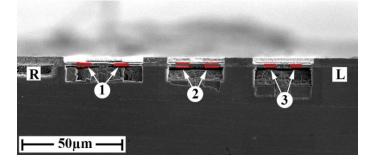

| Figure 7-24 three groups of micro-cantilevers prepared in 290 °C/0 min IMCs interlayer for nano-bending tes                                                                                                           |

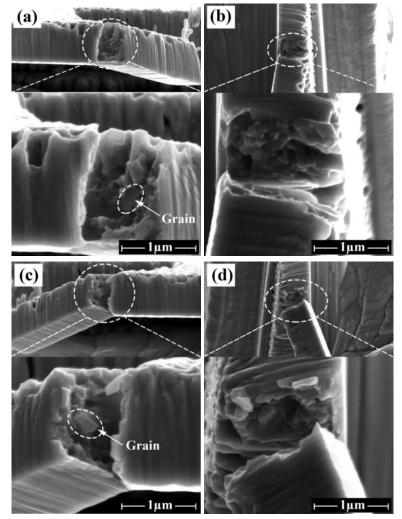

| Figure 7-25 three major stages during the process of nano-bending on three 290 °C/0 min IMCs micro-cantilever         (1) contact; (2) loading and deformation; (3) fracture                                          |

| Figure 7-26 load-depth profiles of nano-bending test on all of 290 °C/0 min IMCs micro-cantilevers                                                                                                                    |

| Figure 7-27 parameters for the in-situ bending test on IMCs micro-cantilevers                                                                                                                                         |

| Figure 7-28 IMCs micro-joint formed after 25 mins dwelling and the IMCs micro-cantilevers                                                                                                                             |

| Figure 7-29 three major stages during the process of nano-bending on two 290 °C/25 mins IMCs micro cantilevers (1) contact; (2) loading and deformation; (3) fracture                                                 |

| Figure 7-30 fracture morphologies of 290 °C/25 mins IMCs micro-cantilevers after bending test                                                                                                                         |

| Figure 7-31 load-depth profiles of 290 °C/25 mins IMC micro-cantilevers during in-situ bending test                                                                                                                   |

## List of Abbreviations

| 2.5D    | 2.5 Dimension                                   |

|---------|-------------------------------------------------|

| 3D      | 3 Dimension                                     |

| AFM     | Atomic Force Microscopy                         |

| Ag      | Silver                                          |

| Al      | Aluminium                                       |

| at.%    | Percentage of atoms                             |

| Au      | Gold                                            |

| BGA     | Ball grid array                                 |

| BIF     | Brittle Intergranular Fracture                  |

| BSE     | Back-scattered electron                         |

| C4      | Controlled-collapse chip connection             |

| CGA     | Column grid array                               |

| CoC     | Chip-on-Chip                                    |

| СР      | Copper pillar                                   |

| СТЕ     | Coefficient of thermal expansion                |

| Cu      | Copper                                          |

| EBSD    | Electron backscattered diffraction              |

| EDX     | Energy dispersive X-ray                         |

| EM      | Electromigration                                |

| FDR     | Flux-driven ripening                            |

| FEG-SEM | Field emission gun-scanning electron microscope |

| FIB     | Focus ion beam                                  |

| GB      | Grain boundary                                  |

| GSO     | Grain shape orientation map                     |

| IC      | Integrated Circuit                              |

| IMCs    | Intermetallics compounds                        |

| I/O     | Inputs/outputs                                  |

| IPF     | Inverse Pole Figure [001] quick map             |

| IQ      | Image Quality (IQ) quick map                    |

| KV      | Kilovolt                                        |

| LGA     | Land grid array                                 |

| LSW     | Lifshitz-Slezov-Wahner theory       |

|---------|-------------------------------------|

| МСМ     | Multichip module                    |

| MLC     | Multilayer ceramic                  |

| mm      | Millimetre                          |

| MPa     | Mega pascal                         |

| nA      | Nano- ampere                        |

| Ni      | Nickel                              |

| nm      | Nanometre                           |

| Pt      | Platinum                            |

| РН      | Potential Of Hydrogen               |

| R.T.    | Room temperature                    |

| SCM     | Single-chip module                  |

| SE      | Secondary electron                  |

| SLC     | Surface laminar circuit             |

| SLID    | Solid-liquid interdiffusion bonding |

| SLT     | Solid Logic Technology              |

| SOH     | Stand-off height                    |

| SOP     | System-on-Package                   |

| sp. gr. | Specific gravity                    |

| Sn      | Tin                                 |

| ТАВ     | Tape-automated bonding              |

| Тв      | The bonding temperature             |

| ta      | Dwell time                          |

| TEM     | Transmission Electron Microscopy    |

| TLP     | Transient liquid phase              |

| $T_{M}$ | The melting point temperature       |

| TSV     | Through Silicon Via                 |

| Ti      | Titanium                            |

| UBM     | Under bump metallurgy/metalization  |

| WB      | Wire bonding                        |

| wt.%    | Percentage of weight                |

| XRD     | X-ray diffraction                   |

## Chapter 1 Introduction

## 1.1 Background

### 1.1.1 Flip-chip technology in chip-level packages

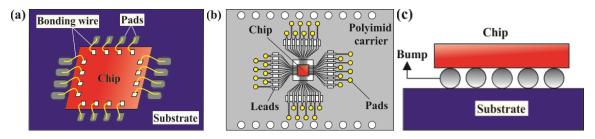

In the last decades, the satisfaction for requirements of individual electronics is the main driving force for the development and improvement made in semiconductor industry. With the increasing demand for multifunctional and miniaturized electronic manufacturing, chip-level packages (first-level packages) have been widely used in the electronic devices. Furthermore, there are three main methods to achieve the interconnection between chip and substrate, such as wire bonding (WB), tape-automated bonding (TAB), and flip-chip (FC) technology, shown in Figure 1-1. Herein, flip-chip technology refers to the chip surface (circuit) facing down on the carrier substrate, which was firstly fabricated by IBM with the controlled-collapse chip connection (C4) technology in their solid logic technology (SLT) hybrid modules for the System/360 [1, 2]. Many advantages have been gained by the application of flip-chip technology, including lower inductance, higher frequencies, better noise control, higher number of inputs/outputs (I/O) and future electronic devices miniaturization availability [3-5]. Therefore, the flip-chip technology has become the most popular method amongst all interconnection technologies.

Figure 1-1 schematic images of primary interconnection technologies for chip-level packages: (a) wire bonding, (b) tape-automated bonding, and (c) flip-chip bonding

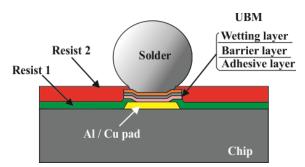

Figure 1-2 schematic image of the traditional under bump metal (UBM) structure

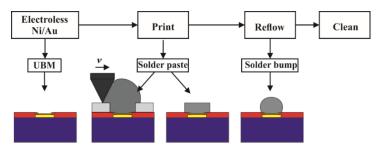

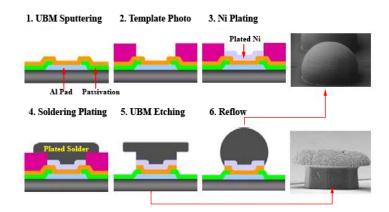

The traditional process of the flip-chip bonding consists of under bump metallurgy (UBM) and solder bump fabrication, die alignment, and reflow process, resulting in a robust interconnection between the chip and substrate. The UBM is manufactured to obtain a better integration between the solder bumps and the wafer or chip with the thickness of appropriate 1  $\mu$ m [6]. There are usually three functional layers composing of the UBM, namely an adhesive layer, a diffusion barrier layer and a wetting layer [7], as exhibited in Figure 1-2. The adhesive layer provides a good adhesion to the metal surface on the chip, while the second barrier layer prevents the device from being contaminated by the diffusion of solder components, and the wetting layer is for the following solder fabrication. Subsequently, the solder bumps can be fabricated by evaporation or electrodeposition of Sn-based alloys, or dispersing solder paste through screen printing. Finally, after the die is aligning on the carrier substrate,

the assembly process is finished by experiencing a high-temperature reflow in oven. During this process, the metallurgical reactions happen between the solder bumps and the adjacent metal pads to achieve permanent and robust bonding. Then, the solder joint will play a vital role in the following service life of the devices, which creates the conductive path to realize the electrical connection between circuit on wafer and the carrier substrate. Simultaneously, they can also be treated as a structural module to provide mechanical support in the whole package, and help conduct the heat energy produced by the working circuit.

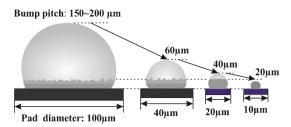

Nowadays, there is a growing demand for smaller and higher performance integrated IC electronics, and fine pitch or ultra-fine pitch flip-chip packaging with higher I/O density is becoming increasingly compulsory to meet this challenge. However, the traditional fabrication method of solder bumps for flip-chip packaging is becoming more and more difficult to achieve the ultra-fine pitch and high-count integration due to the increasing possibility of short circuits which may occur during the reflow process [8]. Therefore, several new methods have been established leading to a much lower dimension and better electrical, thermal performance semiconductor packaging [9-11]. For example, the optimized micro-C4 technology is first utilized in the fine pitch interconnection. And combining with through silicon via (TSV) technology, the micro-C4 has become one of the main challenges in the multichip module packaging area [5, 12]. Besides, some innovative interconnects such as the copper pillar bump bonding, the direct copper bonding, and nano-metal connection have also been researched and developed [13].

#### 1.1.2 Copper pillar bump bonding in 3D integration

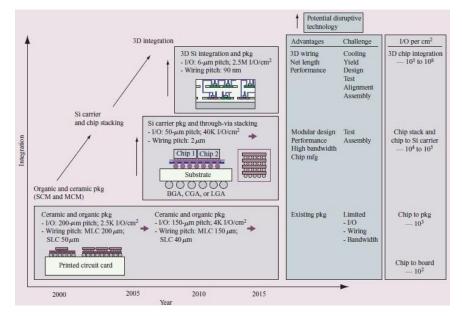

In the chip-level package, the concept of multichip module (MCM) packaging is defined with the classification of chips number mounting in an electronic package. With the comparison of single chip module (SCM), the fundamental characteristic of MCMs is owning the powerful substrate, which should has the ability to afford all the electrical connection paths for the multi-chips (or dies), including four conductive layers and 100 I/O leads for the minimum requirement [14]. As a result, the MCM technology extraordinarily improves the interconnecting density in per package

Figure 1-3 silicon integration roadmap from board-level integration to 3D chip integration (SCM- single chip module; MCM- multichip module; LGA- land grid array; BGA- ball grid array; CGA- column grid array; MLC- multilayer ceramic; SLC- surface laminar circuit) [15]

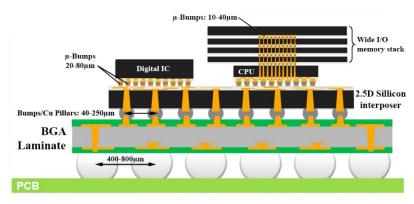

Furthermore, a new configuration to achieve the MCM packaging as 3D integration has emerged, which utilizes the space effectively and adequately within the package, especially in the vertical direction. 3D integration technology is a profound revolution of architecture within one package. It breaks the limitation of Moore's law, bringing more function with lower volume in a single package than the conventional ones [16]. The I/O density has increased significantly from 10<sup>2</sup> per cm<sup>2</sup> in the chip to board level packaging to the10<sup>5</sup>~10<sup>8</sup> per cm<sup>2</sup> in 3D chip integration, as illustrated in Figure 1-3 [15]. Several different 3D integrated structures have been classified, namely 3D wafer-level packaging, 3D ICs stacking, 3D heterogeneous and systems integration. Also, the 2.5D and 3D integration based on interposer technology are included [17].

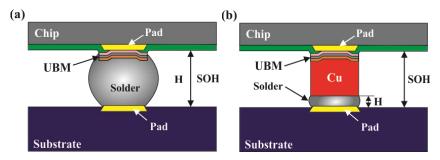

In the aspect of manufacturing technology, the copper pillar bump technology is one promising approach to satisfy the ultra-fine pitch interconnection on silicon packages [18, 19], which has attracted increasing interest and been suggested as the most promising next generation technology to achieve multichip module (MCM) packaging and in particular of 3D integration. Under 150 µm, traditional solder bump shows limitations to meet the specifications of increasing integrated circuit performances and integration scheme. Indeed, their electrical characteristics and stand-off during reflow do not allow to implement them in these new applications. Meanwhile, copper pillar bump has an outstanding performance in that area. As shown in Figure 1-4, the advantages of the copper pillar bump are obvious such as the high stand-off height to enable the fine pitch possibility, and also the solder can be controlled in a limited area with the restricted volume, instead of spreading out on wettable surfaces too much during the bonding process. However, in other aspect, the reduced collapse of solder in the copper pillar bump has become the potential main disadvantage. An extra necessary coplanarity control of bumps should be implemented to prevent the probable non-wetting with the shorter bumps [20].

Figure 1-4 comparison between two bonding structures (a) solder bump, and (b) copper pillar bump (H-Interconnected Height, SOH-Stand-off Height)

## **1.2** Problem statement and research motivation

#### A. Multi-soldering in 3D IC stacking

Compared with wire bonding and other contact interconnection methods, solder has a much broader application in electronic packaging area, especially in the growing 3D multilayer integration. However multi-reflow processes are implemented to achieve the numbers of layers interconnection on vertical direction in 3D stacking packages, and these reflow processes will result in re-melting of the residual Sn-based solder. Then, overflow will happen in the remelted solder, which increases the possibility of inaccurate contraposition or short-circuit to occur.

#### B. Full intermetallic joints formed under the miniaturization

Considering the dramatically scaling down of solder interconnection, the reaction between UBM and solder forming the intermetallic compounds (IMCs) is becoming increasingly important. For the chips with ultra-fine

pitches ranging from 20 to 10 µm, the micro-interconnection is only comprised of IMCs after reflow process without any solder residue, as shown in Figure 1-5. The typical micro-bump is under 10 µm thick, and it is quite easy for the entire solder volume to be totally transformed into an intermetallic bump [21]. Therefore, the characterisations of the IMCs itself are the dominant parameter to govern the reliability of the final interconnection. Then, in order to fabricate the reliable new generation application specific integrated circuit (ASIC) devices supported by the 3D stacking technology, the properties of the micro-IMCs interconnection must be investigated systematically to allow fundamental understanding of the interfacial bonding mechanisms.

Figure 1-5 microstructural evolution within solder joint scaling [21]

First of all, thermo-compression method is selected to realize the miniaturized connections, instead of the conventional reflow process. The typical description of the metallurgical reaction during this soldering process is solid-liquid interdiffusion (SLID) bonding [22, 23] or transient liquid phase (TLP) soldering [24, 25]. Whilst different parameters used in this process as time, temperature, and pressure, play a significant effect on the microstructure of IMC joints [26, 27]. It requires a much further study in order to improve the reliability of final interconnection. The minimum thickness of initial solder layer needed to form a pore-free joint has also been discussed in Bosco's work [28], where at least 10  $\mu$ m of initial Sn layer was suggested in his work. However the estimation was primarily based on the growth of the Cu<sub>6</sub>Sn<sub>5</sub> grain without considering the growth of Cu<sub>3</sub>Sn, which presents an obvious shortcoming, thus unrealistic for the case where the Sn layer is even thinner than 10  $\mu$ m and the growth of Cu<sub>3</sub>Sn layer can be comparable against the Cu<sub>6</sub>Sn<sub>5</sub> layer.

Due to the further reduction of joint size, not only the manufacturing process of the IMC joints, but also the reliability of such formed joints are to be concerned ever more,. For instance, Kirkendall voids are normally found in Cu<sub>3</sub>Sn layer or near the interface between Cu<sub>3</sub>Sn and plated Cu substrate after aging or during the service period [29-31], which will strongly impact the reliability of the IMC interconnection. Moreover, the IMCs are considered to be brittle since the cleavage morphology is often observed at the IMC fractured surfaces. Ghosh [32] has microscopically seen some slip bands appeared in Cu<sub>3</sub>Sn during the indentation test, which indicates the question whether the IMC is really brittle or not is still under debate [33].

## 1.3 Research aims and objectives

This project aims to promote the application of full IMCs micro-joints which may be viable for the miniaturized 3D integration. In order to guarantee the quality of interconnection accomplished by IMCs, the relationship between microstructural characteristics of these IMCs micro-joints and the issues of reliability should be established. Therefore, the aims and objectives of this project can be identified as follows:

- (1) To develop an appropriate method to prepare IMCs micro-interconnection reliably and cost-effectively, with a thickness of no more than 10 µm in laboratory. These samples should be easy to prepare and observe, meanwhile they should be representative and reflecting the true solder interconnection and miniaturization.

- (2) To reveal the effect of parameters of soldering process on the microstructural structure of IMCs micro-joints. This should be carried out by understanding the mechanism of interfacial reactions occurring in these micro-

joints.

- (3) To elaborate the process of formation and microstructural evolution to the terminal full IMCs micro-joint with stable and homogenous composition. To gain an insight into the relevant characteristic features of the interconnected microstructure.

- (4) To establish a reliable system to estimate the quality of IMCs micro-joints, such as mechanical properties, with an appropriate testing method designed purposely.

- (5) To study an alternative structure of IMCs interconnection, which may possess further advantages in terms of electrical or mechanical performance.

## 1.4 Statement of main innovation and contributions

- (1) The phenomena of planar growth of IMCs has been observed. This appearance cannot be neglected and treated as the overflow of melting Sn-solder or the volume expansion of IMCs phase transformation.

- (2) The mechanism of microstructural evolution in the Cu-Sn IMCs micro-joints has been proposed in detail. The flux-driving theory has been applied to describe the homogenizing process of Cu<sub>3</sub>Sn micro-joint, where the growth and repining occurred simultaneously.

- (3) An alternative sandwich structure as Ni/Sn/Cu has been recommended to realize the full IMCs interconnection in 3D integration. The interaction between two different interfacial reactions (Cu/Sn and Ni/Sn) has been discussed, wherein the phenomenon of Ni segregation has been observed in the Cu-Sn-Ni IMCs interlayer and the process of that has been demonstrated with the analysis of the diffusing paths of Cu and Ni atoms.

- (4) Specific types of IMCs micro-cantilevers have been designed and fabricated by focus ion beam (FIB), which makes it feasible to measure the mechanical properties of IMCs through in-situ nano-compression and nanobending tests.

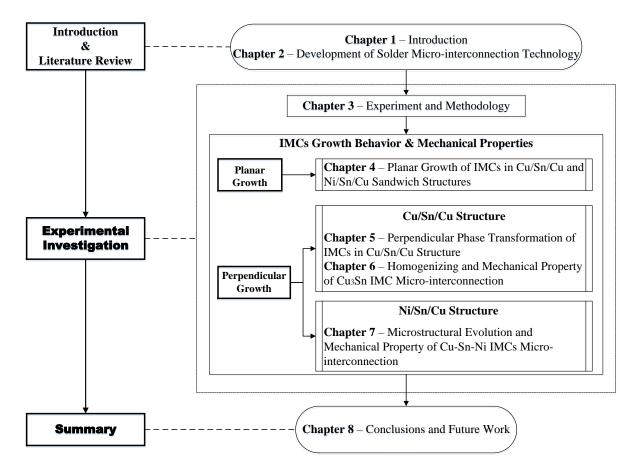

### **1.5** Thesis structure

This thesis is constituted with eight chapters, which includes three major sections, as shown in Figure 1-6. The first section contains the **chapter 1** Introduction and **chapter 2** Development of solder micro-interconnection technology. The second section is the experimental investigation focusing on the growth behaviour of IMCs and the mechanical testing, including the **chapter 3**~7. Then, the summary is given as the third section in the **chapter 8** Conclusions and future work.

In the first section, the background and the literature review have been presented, mainly focusing on the soldercopper pillar bump as the new generation of interconnection used for 3D integration. And the literatures on the common Cu-Sn and Ni-Sn intermetallics also have been introduced in chapter 2.

In chapter 3, the experimental methodology has been described. The sandwich structures as Cu/Sn/Cu and Ni/Sn/Cu have been prepared by the method of electroplating. Through the transient liquid phase (TLP) soldering, the interconnected specimens have been made as the full IMC micro-joints.

According on the growth direction of IMCs in micro-joints, there are two main sections have been included to focus on planar and perpendicular growth. Chapter 4 concentrates on the planar growth of IMCs in Cu/Sn/Cu and Ni/Sn/Cu sandwich structures. And the other perpendicular growth of IMCs has been studied in chapter 5, chapter 6 and chapter 7. Particularly, the phase transformation in Cu-Sn IMCs micro-joints has been observed in

Chapter 5, and the homogenizing process of Cu<sub>3</sub>Sn joint has been analysed by electron backscattered diffraction (EBSD) in chapter 6, where the process of microstructural evolution in Cu-Sn IMCs micro-joints has been investigated. In Chapter 6, the results from shear testing conducted by nanoindentation machine is also described. Besides, for the Ni/Sn/Cu structure, the formation and microstructural evolution have been elaborated in chapter 7. The diffusion behaviour of Ni in these IMCs micro-joints has been discussed. And the in-situ nano-mechanical system has been selected to measure the mechanical properties of Cu-Sn-Ni IMCs.

Finally, the major findings from the study are concluded in chapter 8, with some recommendations of future work and potential research.

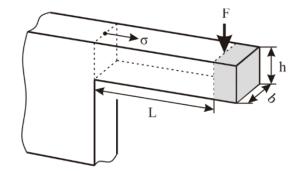

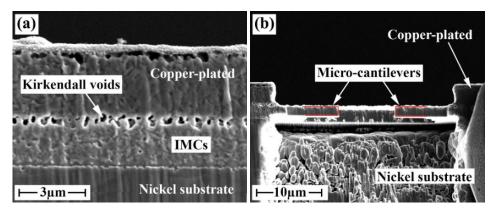

Figure 1-6 the blueprint for the whole thesis